(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property

Organization

International Bureau

(43) International Publication Date

21 April 2005 (21.04.2005)

PCT

(10) International Publication Number

WO 2005/036597 A2

(51) International Patent Classification<sup>7</sup>:

H01L

Amudha R. [IN/US]; 2022 N. Nevada Street # 2244, Chandler, AZ 85225 (US). Morrison, Jennifer H. [US/US]; 2974 W. Comstock Drive, Chandler, AZ 85224 (US).

(21) International Application Number:

PCT/US2004/028262

(74) Agents: KING, Robert, L. et al.; Corporate Law Department, Intellectual Property Section, 7700 West Parmer Lane, MD: TX32/PL02, Austin, TX 78729 (US).

(22) International Filing Date: 31 August 2004 (31.08.2004)

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

(25) Filing Language:

English

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM),

(26) Publication Language:

English

(30) Priority Data:

10/668,694 23 September 2003 (23.09.2003) US

(71) Applicant (for all designated States except US):

FREESCALE SEMICONDUCTOR, INC. [US/US];

6501 William Cannon Drive West, Austin, TX 78735 (US).

(72) Inventors; and

(75) Inventors/Applicants (for US only): CIANCIO, Anthony [US/US]; 939 E. Loma Vista Street, Gilbert, AZ 85296 (US). GRISWOLD, Mark D. [US/US]; 673 North Sicily Court, Chandler, AZ 85226 (US). IRUDAYAM,

[Continued on next page]

(54) Title: SEMICONDUCTOR DEVICE AND MAKING THEREOF

5

(57) **Abstract:** By forming a conductive smoothing layer (16, 19) over the bottom electrode (11) and/or a capacitor dielectric, a MIM capacitor with improved reliability due to reduction of geometrically enhanced electric fields and electrode smoothing is formed. In one embodiment, a first layer (16) including a refractory metal or a refractory metal-rich nitride, is formed over a first capping layer (14) formed of a refractory nitride. In addition, a second layer (19) including a refractory metal (18) or a refractory metal-rich nitride may be formed on the capacitor dielectric. The conductive smoothing layer (16, 19) could also be used in other semiconductor devices, such as transistors between a gate electrode and a gate dielectric.

WO 2005/036597 A2

European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

**Published:**

- *without international search report and to be republished upon receipt of that report*

**SEMICONDUCTOR DEVICE AND MAKING THEREOF**Field of the Invention

This invention relates, generally, to the field of semiconductor devices and more particularly to metal-insulator-metal (MIM) capacitors as used in semiconductor devices.

Background of the Invention

As semiconductor devices shrink, there is a desire to decrease the area occupied by features, such as capacitors. To accommodate, capacitors are being formed over transistors (e.g., at the metal level) as opposed to being formed at the transistor level closer to the bulk semiconductor substrate. One example of such a capacitor is a metal-insulator-metal (MIM) capacitor which includes a MIM dielectric between a top electrode and a bottom electrode.

The metal layers may be formed using aluminum, copper, or alloys thereof.

Typically, a capping layer or anti-reflective coating (ARC) is formed over the metal layers and can be used as the bottom electrode for the MIM capacitor being formed over the metal layers. In the industry, one such ARC material is TiN. While using the ARC as a bottom electrode is desirable for processing simplicity, the surface of the TiN in contact with the MIM dielectric is rough. The rough surface of the TiN creates geometrically enhanced fields which degrade the reliability of the MIM dielectric. Thus, a need exists to control the uniformity of the electric field especially when using TiN as an electrode in a MIM capacitor.

Brief Description of the Drawings

The present invention is illustrated by way of example and not by limitation in which

5 like references indicate similar elements, and in which:

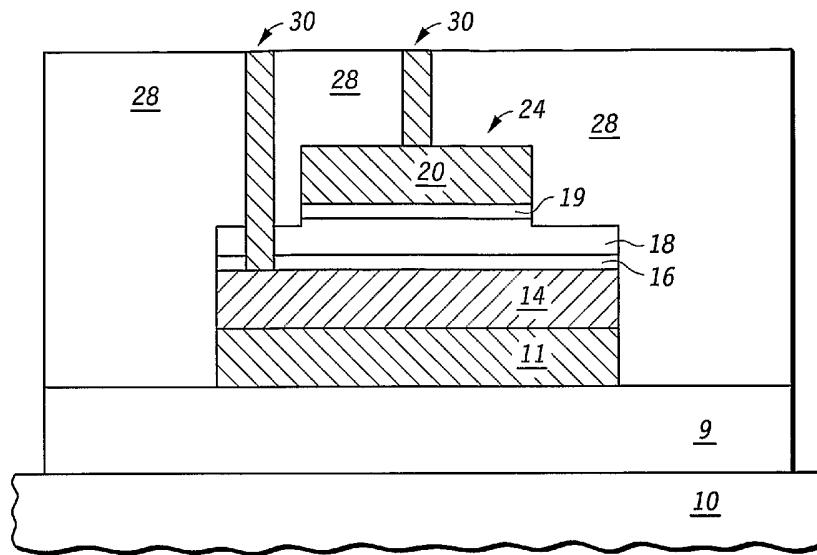

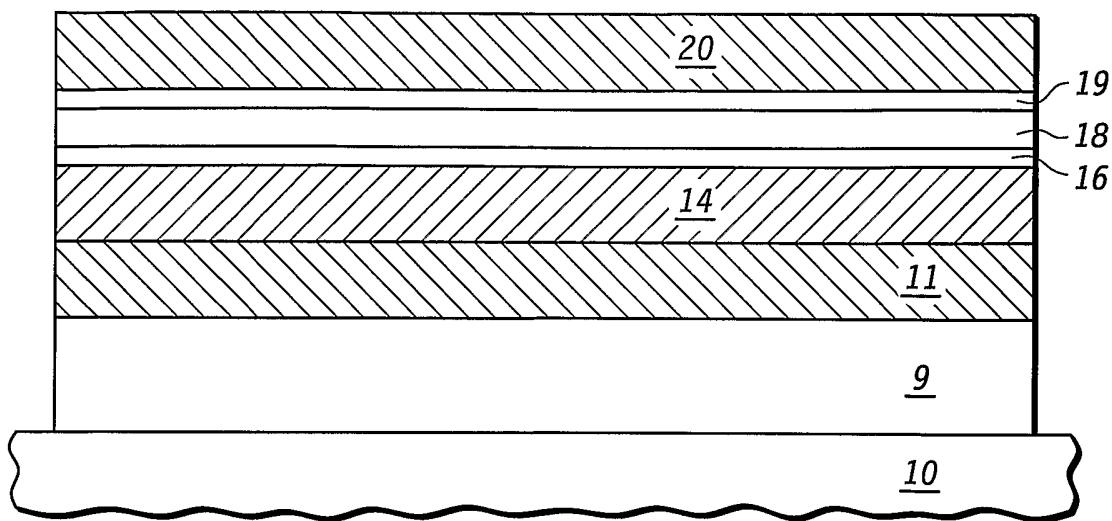

FIG. 1. illustrates a cross section of a part of a semiconductor device having a bottom electrode in accordance with an embodiment of the present invention;

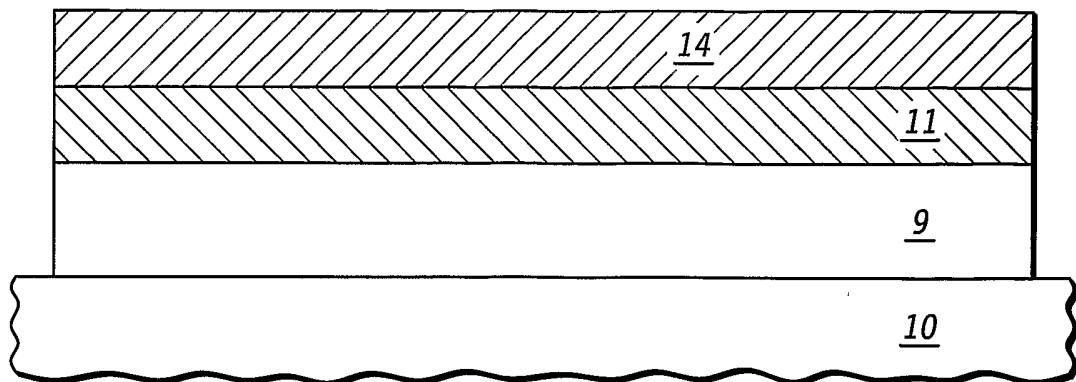

10 FIG. 2. illustrates the semiconductor device of FIG. 1 after forming a first barrier layer in accordance with an embodiment of the present invention;

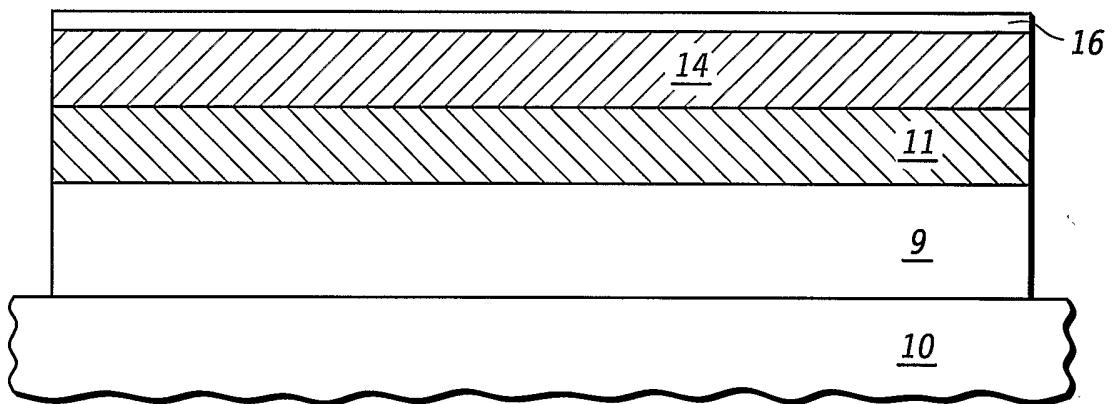

FIG. 3 illustrates the semiconductor device of FIG. 2 after forming a first dielectric layer and a second barrier layer in accordance with an embodiment of the present invention;

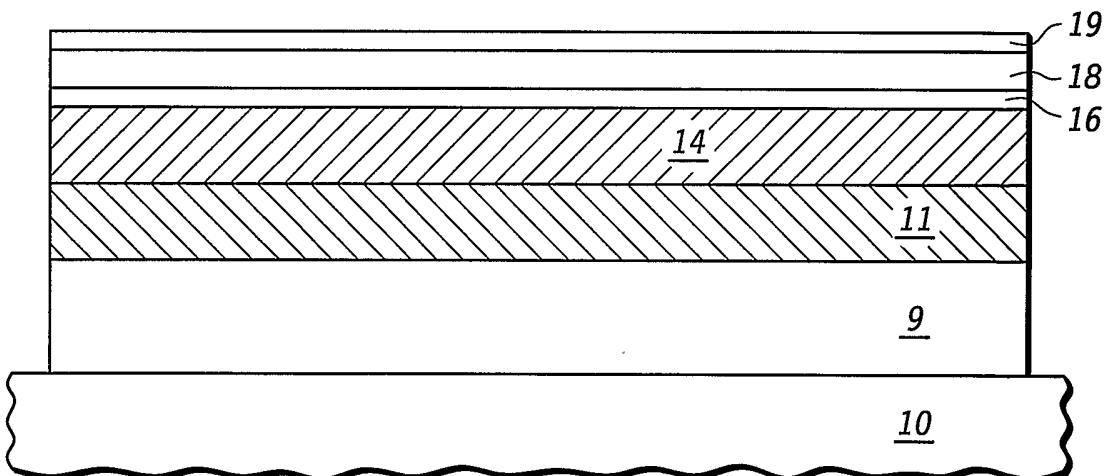

FIG. 4 illustrates the semiconductor device of FIG. 3 after forming a top electrode and a etch stop layer in accordance with an embodiment of the present invention;

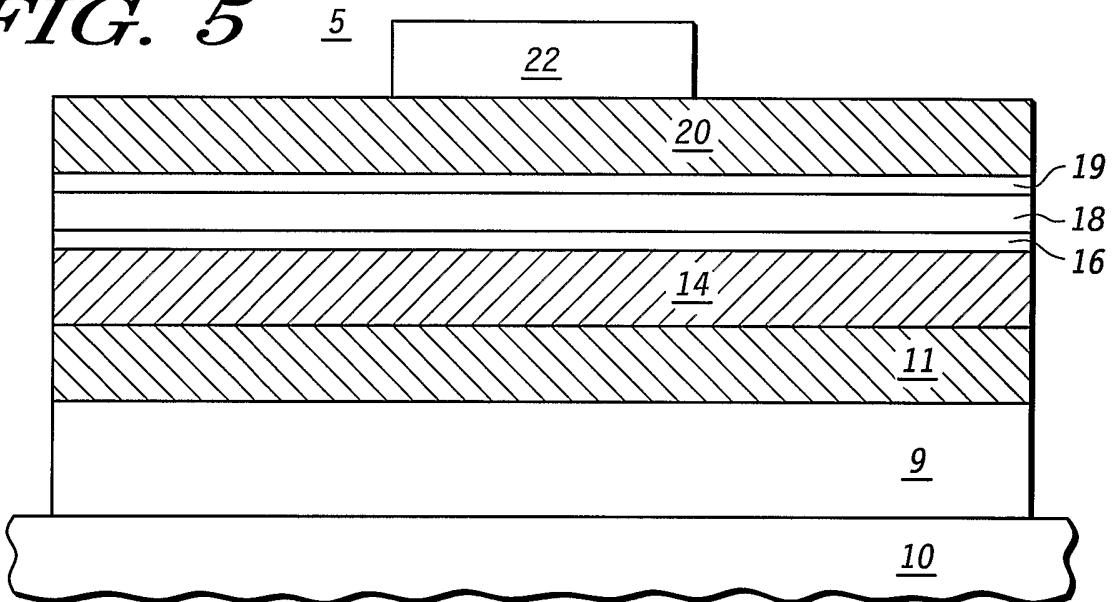

15 FIG. 5 illustrates the semiconductor device of FIG. 4 after forming a patterned photoresist layer in accordance with an embodiment of the present invention;

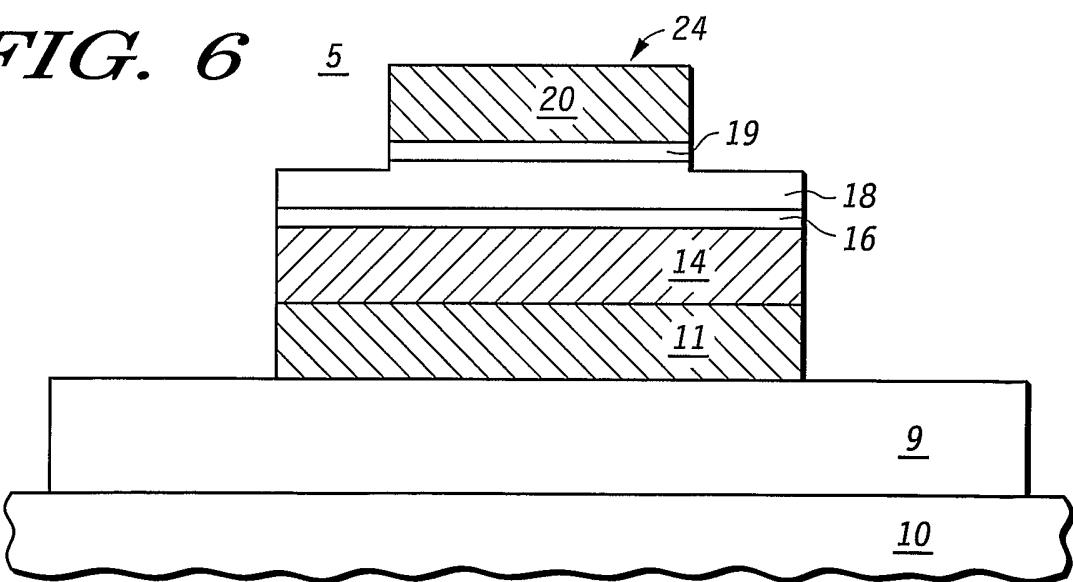

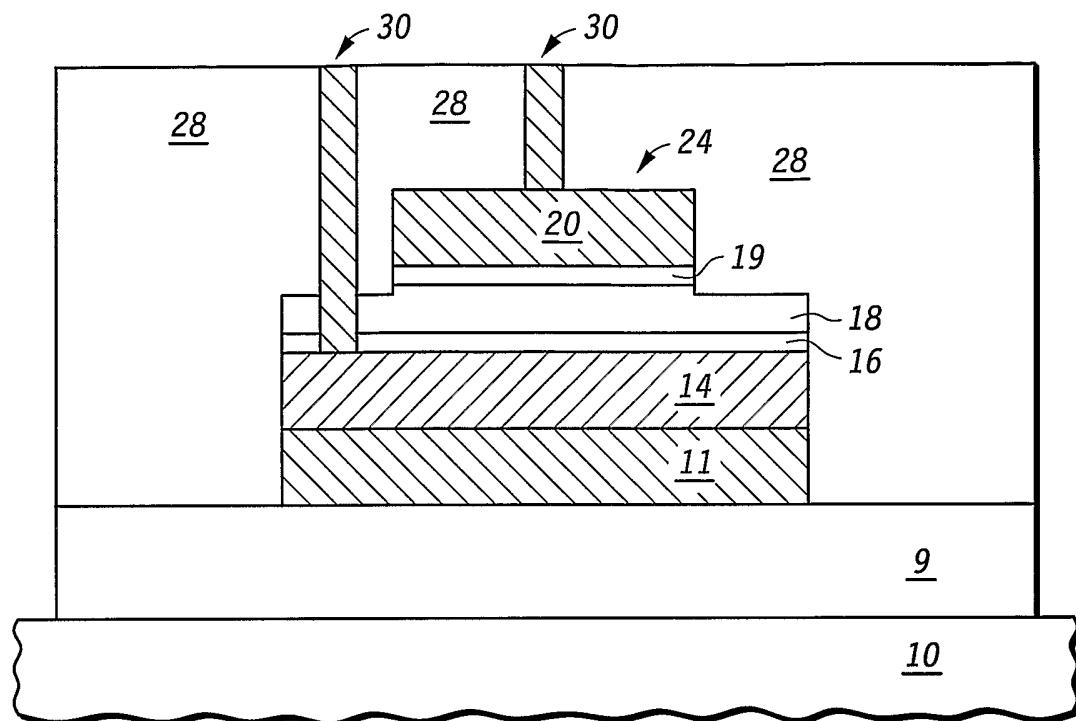

FIG. 6 illustrates the semiconductor device of FIG. 5 after patterning the etch stop layer, the top electrode and the second barrier layer in accordance with an embodiment of the present invention;

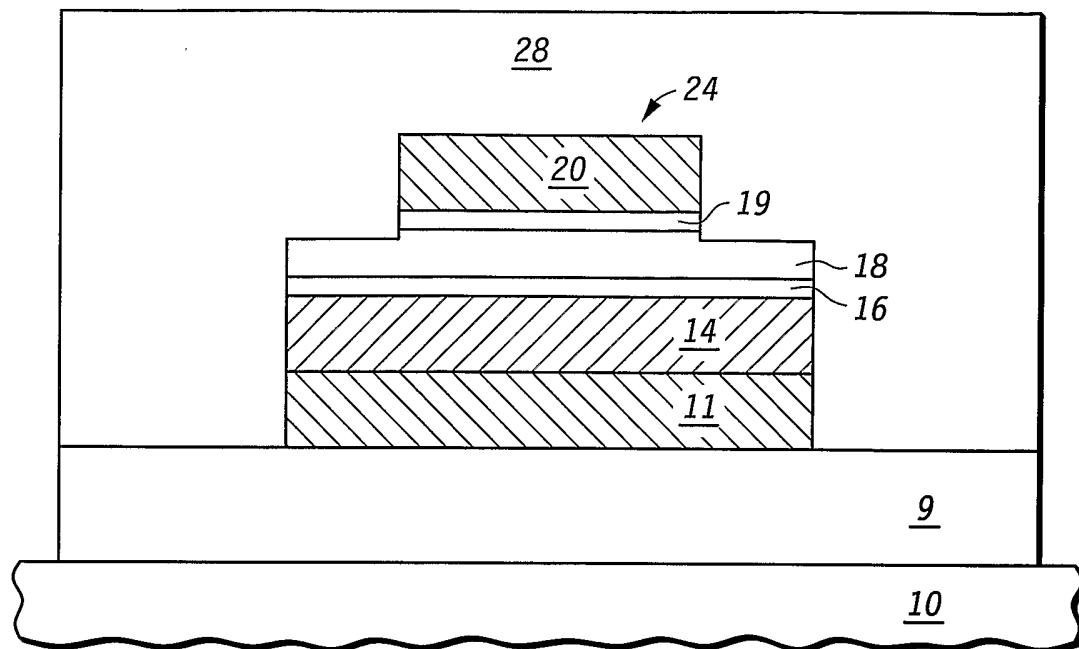

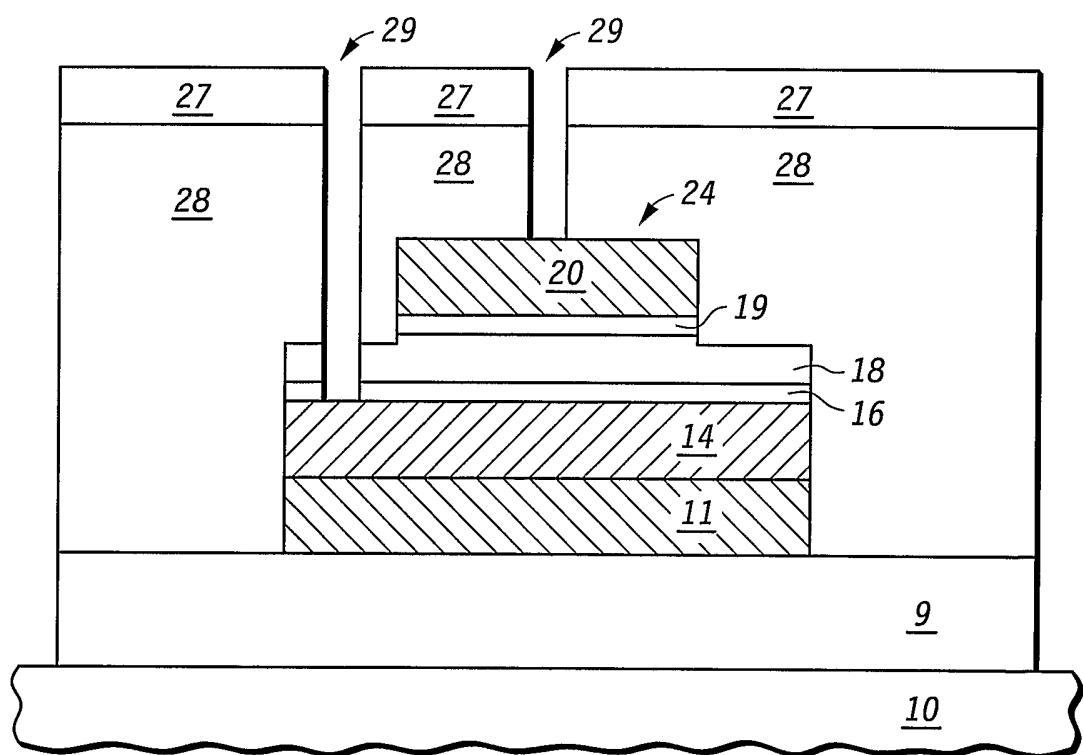

20 FIG. 7 illustrates the semiconductor device of FIG. 6 after forming a second dielectric layer in accordance with an embodiment of the present invention;

FIG. 8 illustrates the semiconductor device of FIG. 7 after forming a photoresist layer and etching vias in accordance with an embodiment of the present invention;

25 FIG. 9 illustrates the semiconductor device of FIG. 8 after filling the vias with a conductive material in accordance with an embodiment of the present invention; and

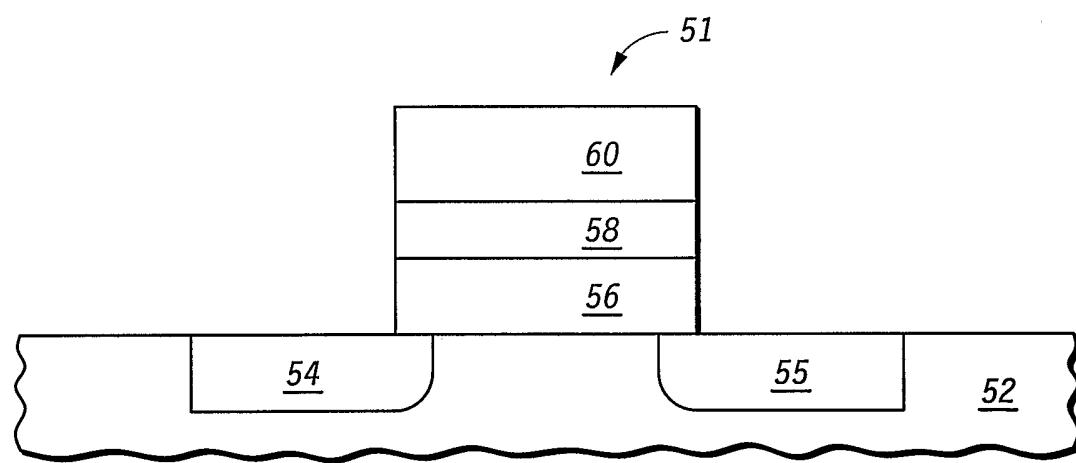

FIG. 10 illustrates a cross section of a part of a semiconductor device having a transistor formed in accordance with another embodiment of the present invention.

Skilled artisans appreciate that elements in the figures are illustrated for simplicity 30 and clarity and have not necessarily been drawn to scale. For example, the dimensions of some of the elements in the figures may be exaggerated relative to other elements to help improve the understanding of the embodiments of the present invention.

Detailed Description of the Drawings

The inventors have observed that MIM capacitors are susceptible to roughness from underlying layers. Typically, the metal line and a capping layer, which in one embodiment is a TiN layer, form the bottom electrode. (Alternatively, just the metal line or the TiN layer 5 forms the bottom electrode.) Thus, a need exists for making the bottom electrode smoother. Although the metal line can be removed from underneath the MIM capacitor at the expense of increased process complexity instead of forming a smoothing layer, alternatively the smoothing layer can be used. Thus, the smoothing layer can be used regardless of the material used for the metal lines.

10 By forming a smoothing layer, such as refractory (metal)-rich nitride layer (e.g., a titanium-rich nitride (TiRN) layer) or pure metallic layer with an appropriate smoothness over the bottom electrode and/or a capacitor dielectric in accordance with an embodiment of the present invention, a MIM capacitor with improved reliability due to reduction of 15 geometrically enhanced electric fields and electrode smoothing is formed. Embodiments of the invention will be described in regards to the figures.

FIGs. 1-9 illustrate a portion of a semiconductor device 5 as it undergoes a series of processing steps to form a MIM capacitor in accordance with the present invention. More specifically, FIG. 1 illustrates a first or bottom metal layer or interconnect layer 11 formed over an intermetal dielectric layer 9 and a semiconductor substrate 10. In a preferred 20 embodiment, semiconductor substrate 10 is silicon. However, other semiconductor materials can be used such as gallium arsenide and silicon-on-insulator (SOI). Typically, substrate 10 will include a number and variety of active semiconductor devices (such as MOS and/or bipolar transistors). However, for purposes of understanding the present invention, an 25 understanding of these devices is not necessary and thus these devices are not illustrated. The intermetal dielectric layer 9 can be any dielectric material formed by any process. For example, it may be silicon dioxide.

The first conductive layer 11 is formed over the semiconductor substrate 10 using physical vapor deposition (PVD), chemical vapor deposition (CVD), atomic layer deposition (ALD), electroplating, the like, and combinations of the above. In a preferred embodiment 30 the first conductive layer 11 includes aluminum or copper. For example, the first conductive layer 11 can be copper or an aluminum copper alloy. In one embodiment, the conductive layer 11 is approximately 6,000 Angstroms of aluminum copper. In another embodiment, the first conductive layer 11 is predominately copper. Furthermore, the first conductive layer 11

may actually be formed of multiple materials. For instance in copper inlaid metallization schemes, diffusion barriers comprising tantalum or tantalum nitride are often formed prior to forming a copper layer.

To form the structure of FIG. 1, a first capping layer or anti-reflective coating (ARC)

5 14 is optionally formed over the first conductive layer 11 by PVD, CVD, ALD, electroplating, the like, and combinations of the above. Preferably the first capping layer 14 includes titanium, tantalum, nitride, tantalum nitride (TaN), titanium nitride (TiN), or the like. The first capping layer 14, preferably, is any refractory nitride. In one embodiment the first capping layer 14 is approximately 100-1000 Angstroms or more specifically, approximately 10 200-800 Angstroms of TiN and is preferably approximately 650 Angstroms. In another embodiment, the first capping layer 14 may be organic. Furthermore, the first capping layer 14 is optional. In this embodiment, a subsequently formed first smoothing layer 16 if formed over and in contact with the first conductive layer 11. In the embodiment shown in the figures, the first capping layer 14 is a bottom electrode. However, if the first capping layer 15 14 is not present or is not conductive, then the first conductive layer 11 or another conductive layer is the bottom electrode.

As shown in FIG. 2, a first or bottom smoothing layer 16 is formed over the first capping layer 14 by PVD, CVD, ALD, electroplating, the like, and combinations of the above. In one embodiment, the first conductive smoothing layer 16 is approximately 50-500 20 Angstroms or more specifically, approximately 100-300 Angstroms of a refractory metal, such as titanium, or a refractory-rich nitride, such as titanium-rich nitride (TiRN). (The TiRN has a stoichiometric ratio of Ti:N that is greater than 1:1.) In one embodiment, the first conductive smoothing layer 16 is approximately 150 Angstroms in thickness.

The first conductive smoothing layer 16 can be any conductive material that has a 25 surface roughness less than that of the first capping layer or bottom electrode 14. Experiments have been performed that show that 800 Angstroms of TiN has a (surface) roughness of approximately 49 Angstroms, whereas 650 Angstroms of TiN as the first capping layer and 150 Angstroms of TiRN as the first conductive smoothing layer has a (surface) roughness of approximately 25 Angstroms. Thus, in one embodiment, the first 30 capping layer 14 is TiN and the first conductive smoothing layer 16 is TiRN. Preferably, the smoothing layer is a fine grain or amorphous layer because these layers typically are smoother than refractory nitrides used for the first capping layer because the refractory

nitrides when formed on the metal line typically form columnar grains which are not as smooth as fine grain layers.

In a preferred embodiment, the first capping layer 14 is TiN formed by PVD and the first conductive smoothing layer 16 is TiRN, because processing complexity is reduced. To 5 form the TiRN layer, argon (or any other nonreactive gas), flows in the PVD chamber and a plasma is formed. The argon ions bombard a poisoned TiN target. The poisoned TiN target is a titanium (Ti) target that due to a reaction with a nitrogen (N) plasma forms TiN as the top surface. When the argon ions bombard the poisoned target TiN is deposited on the semiconductor device. As the target becomes depleted of nitrogen, a deposited film has a 10 higher titanium content creating a titanium-rich layer. This technique allows one to modulate the content of the deposited film from stoichiometric TiN to titanium and control the final (surface) roughness. Thus, the first conductive smoothing layer 16 may be TiRN (a refractory-nitride) and/or titanium (a refractory metal). Furthermore, the first conductive smoothing layer 16 may be a refractory metal, such as titanium without any nitrogen present.

15 The capacitor dielectric layer 18 is formed on the first conductive smoothing layer 16 using CVD, PVD, ALD, the like or combinations of the above. In one embodiment, the capacitor dielectric layer 18 preferably comprises a metal oxide which has high linearity (e.g., a normalized capacitance variation of typically less than 100 parts per million units of voltage), such as tantalum oxide and hafnium oxide. However, for general applications in 20 which linearity may be less critical, other metal oxides such as zirconium oxide, barium strontium titanate (BST), and strontium titanate (STO) may be suitable. Alternatively, an insulator that is not a high dielectric constant material can be used, such as silicon dioxide. As used herein a high dielectric constant material is a material with a dielectric constant greater than that of silicon dioxide. The capacitor dielectric layer 18 may be a dielectric 25 layer that is not a high dielectric constant material. For example, the capacitor dielectric layer 18 may be plasma-enhanced nitride (PEN), which is  $\text{Si}_x\text{N}_y$ . However, the presence of smoothing layers is more advantageous as the capacitor dielectric is scaled to improve the capacitance density because the effects of roughness become more significant and the importance of surface smoothing increase.

30 To form the structure of FIG. 3, a second or top smoothing layer 19 is formed on the capacitor dielectric layer 18. The second conductive smoothing layer 19 can be formed by any process used to form the first conductive smoothing layer 16, may be any of the material described for the first conductive smoothing layer 16, and may be the same dimensions as

described for the first conductive smoothing layer 16. However, the first conductive smoothing layer 16 and the second conductive smoothing layer 19 need not be formed by the same process, be formed of the same material, or be the same dimensions, although using the same process and/or material may decrease processing complexity. Furthermore, the second 5 conductive smoothing layer 19 should have a roughness less than a subsequently formed second conductive layer.

As shown in FIG. 4, a second or top conductive layer 20 is formed on the second conductive smoothing layer 19 preferably using PVD, but other techniques including CVD, ALD, or combinations thereof could be used. The top conductive layer 20 will form the 10 second (top) electrode of the capacitor and thus can be formed of any conductive material such as a metal nitride (e.g., tantalum nitride and titanium nitride), a conductive oxide (e.g., ruthenium oxide and iridium oxide), metals (e.g., copper and aluminum), metal alloys, combinations of the above, and the like. In one embodiment, the top conductive layer 20 comprises nitrogen and either tantalum or titanium (in the form of titanium nitride or 15 tantalum nitride).

Turning to FIG. 5, a first photoresist layer 22 is deposited and patterned in order to subsequently etch the top conductive layer 20 and the second conductive smoothing layer 19. After etching the top conductive layer 20 and the second conductive smoothing layer 19 using conventional etching chemistries, a top electrode 24 (or second electrode 24) is formed, 20 as shown in FIG. 6.

During the top electrode 24 formation, the capacitor dielectric layer 18 may be over-etched in order to guarantee that the top conductive layer 20 and the second conductive smoothing layer 19 are completely etched. This over-etch can be tailored to decrease the capacitor dielectric layer 18 to a desired thickness outside or beyond the capacitor area, if 25 desired. Since the capacitor dielectric layer 18 will not be completely removed in areas that are not part of the MIM capacitor, the dielectric constant of the metal oxide can undesirably increase the capacitance in areas outside the MIM capacitor. Ideally, the etch would completely remove the capacitor dielectric layer 18. However, doing so in the embodiment shown in the figures could damage critical portions of the capacitor dielectric layer 18, the 30 first conductive smoothing layer 16 and/or the surface of the bottom electrode 14.

After patterning the top electrode 24, another photoresist (not shown) is formed over the semiconductor device 5 to etch the first conductive layer 11, the capping layer 14, the first

conductive smoothing layer 16 and capacitor dielectric layer 18, as known in the industry resulting in the structure shown in FIG. 6.

As shown in FIG. 7, an interlayer dielectric (ILD) 28 is deposited over the semiconductor substrate 10. The ILD can be any dielectric material, such as fluorinated silicon dioxide formed using tetraethoxysilane (TEOS). A second photoresist layer 27 is deposited and patterned in order to etch the ILD layer 28 to form via openings 29 as shown in FIG. 8. The chemistry of the via etch is selective to the second conductive layer 20. Conventional etch processes and chemistries can be used.

After forming the via openings 29, a conductive material is formed within the via openings 29 in order to form conductive vias 30 as shown in FIG. 9. A conductor is formed in the via openings 29 to form contacts to the top electrode 24 and bottom electrode 14. In a preferred embodiment, copper is electroplated and chemically mechanically polished back to form the conductive vias 30.

The resulting MIM capacitor shown in FIG. 9 has the advantage of a decreased surface roughness between the electrodes (top and bottom) and the capacitor dielectric, resulting in improved reliability. Furthermore, the smoother interface allows for greater latitude in scaling the MIM capacitor. In addition, the time dependent dielectric breakdown (TDDB) is increased.

The embodiment described as shown in the figures is a MIM capacitor wherein the top electrode 24 is smaller in size compared to the bottom electrode 14. In another embodiment, the top electrode 24 can be oversized as compared to the bottom electrode 14. In this embodiment, the contact for the bottom electrode 14 may be formed prior to the formation of the bottom electrode 14 because the contact, instead of being formed over the bottom electrode, is underneath the bottom electrode 14. Related structures are not explicitly shown in the figures, but are generally always present on-chip as an essential part of the IC interconnect circuitry.

Benefits, other advantages, and solutions to problems have been described above with regard to specific embodiments. However, the benefits, advantages, solutions to problems, and any element(s) that may cause any benefit, advantage, or solution to occur or become more pronounced are not to be construed as a critical, required, or essential feature or element of any or all the claims. As used herein, the terms "comprises," "comprising," or any other variation thereof, are intended to cover a non-exclusive inclusion, such that a process, method, article, or apparatus that comprises a list of elements does not include only those

elements but may include other elements not expressly listed or inherent to such process, method, article, or apparatus.

In the foregoing specification, the invention has been described with reference to specific embodiments. However, one of ordinary skill in the art appreciates that various 5 modifications and changes can be made without departing from the scope of the present invention as set forth in the claims below. For example, the MIM capacitor could be formed using a dual damascene integration. Furthermore, although the use of the smoothing layers are taught with respect to a MIM capacitor, the smoothing layers can be used anywhere a rough surface is in contact with a dielectric to increase reliability. For example, a smoothing 10 layer can be formed in contact with a gate dielectric and be part of a transistor 51, as shown in FIG. 10. A semiconductor device 50 includes a semiconductor substrate 52. Within the semiconductor substrate 52, source region 54 and drain region 55 are formed. The transistor includes the source region 54, the drain region 55, a gate dielectric 56 (which can be any dielectric material, such as a high dielectric constant material), a smoothing layer 58 (which 15 is preferably conductive and can be any material previously described for smoothing layers) and a gate electrode 60 (which can be a metal, polysilicon and the like.). In this embodiment, a smoothing layer is in contact with a conductive layer (i.e., the gate electrode 60) and a dielectric layer (e.g., the gate dielectric 56), wherein the smoothing layer has a surface roughness less than that of the conductive layer.

20 Accordingly, the specification and figures are to be regarded in an illustrative rather than a restrictive sense, and all such modifications are intended to be included within the scope of present invention.

## CLAIMS

What is claimed:

1. A semiconductor device comprising:

5        a semiconductor substrate;

a first electrode formed over the semiconductor substrate;

a first conductive smoothing layer formed over the first electrode, wherein the first

conducting smoothing layer has a surface roughness less than that of the first

electrode;

10      a dielectric layer formed on the first conductive smoothing layer; and

a second electrode formed over the dielectric layer.

2. The semiconductor device of claim 1, further comprising:

15      a second conductive smoothing layer formed between the dielectric layer and the

second electrode, wherein the second conductive smoothing layer has a roughness

less than that of the second electrode.

3. The semiconductor device of claim 2, wherein the second conductive smoothing layer

comprises a refractory metal.

20      4. The semiconductor device of claim 1, wherein the first electrode comprises a first layer

comprising a metal and a second layer comprising a refractory nitride and the second

electrode comprises a metal.

25      5. The semiconductor device of claim 1, wherein the first electrode and the second electrode

comprise a refractory nitride.

6. The semiconductor device of claim 5, wherein the refractory nitride comprises a material

selected from the group consisting of titanium nitride and tantalum nitride.

30      7. The semiconductor device of claim 1, wherein the first conductive smoothing layer

comprises titanium rich nitride.

8. The semiconductor device of claim 1, wherein the dielectric layer comprises a high dielectric constant material.

9. The semiconductor device of claim 1, wherein the first electrode, the first conductive smoothing layer, the dielectric layer and the second electrode are part of a metal-insulator-metal (MIM) capacitor.

5

10. The semiconductor device of claim 9, further comprising:

a capping layer over the first electrode, wherein the capping layer comprises a refractory nitride and the first electrode comprises a metal.

10

11. A semiconductor device comprising:

a conductive layer;

a smoothing layer formed in contact with the conductive layer, wherein the smoothing layer

15 has a surface roughness less than that of the conductive layer; and

a dielectric layer formed in contact with the smoothing layer.

12. The semiconductor device of claim 11, wherein the smoothing layer comprises titanium rich nitride.

20

13. The semiconductor device of claim 12, wherein the conductive layer comprises titanium nitride and the smoothing layer comprises titanium.

14. The semiconductor device of claim 11, wherein the conductive layer, the smoothing

25 layer and the dielectric layer are part of a device selected from the group consisting of a transistor and a capacitor.

15. The semiconductor device of claim 11, wherein the conductive layer comprises a first layer comprising a metal and a second layer comprising a refractory nitride.

30

16. The semiconductor device of claim 11, wherein the dielectric layer is a high dielectric constant material.

17. A semiconductor device comprising:

- a semiconductor substrate;

- a first electrode formed over the semiconductor substrate, wherein the first electrode comprises a first layer comprising metal and a second layer over the first layer, wherein the second layer comprises a refractory nitride;

- 5 a first smoothing layer formed over the first electrode, wherein the first smoothing layer comprises titanium rich nitride;

- a dielectric layer formed on the first smoothing layer; and

- a second electrode formed over the dielectric layer, wherein the second electrode comprises a third layer comprising a refractory nitride and a fourth layer over the third layer, wherein the fourth layer comprises a metal.

10 18. The semiconductor device of claim 17, wherein the refractory nitride comprises a material selected from the group consisting of titanium nitride and tantalum nitride.

15

19. The semiconductor device of claim 18, wherein the refractory metal comprises titanium.

20 20. A method for forming semiconductor device comprising:

- providing a semiconductor substrate;

- 20 forming a first electrode formed over the semiconductor substrate;

- forming a first conductive smoothing layer formed over the first electrode, wherein the first smoothing layer has a surface roughness less than that of the first electrode;

- forming a dielectric layer formed on the first smoothing layer; and

- 25 forming a second electrode formed over the dielectric layer.

1/4

***FIG. 1*** 5

***FIG. 2*** 5

***FIG. 3*** 5

**FIG. 4** 5

2/4

**FIG. 5** 5**FIG. 6** 5

3/4

*FIG. 7* 5

*FIG. 8* 5

4/4

*FIG. 9* 5

*FIG. 10* 50