(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7678673号**

**(P7678673)**

(45)発行日 令和7年5月16日(2025.5.16)

(24)登録日 令和7年5月8日(2025.5.8)

(51)国際特許分類

|         |                 |     |         |       |

|---------|-----------------|-----|---------|-------|

| H 0 4 N | 25/57 (2023.01) | F I | H 0 4 N | 25/57 |

| H 0 4 N | 25/44 (2023.01) |     | H 0 4 N | 25/44 |

請求項の数 11 (全12頁)

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2021-10625(P2021-10625)   |

| (22)出願日  | 令和3年1月26日(2021.1.26)        |

| (65)公開番号 | 特開2022-114353(P2022-114353) |

|          | A)                          |

| (43)公開日  | 令和4年8月5日(2022.8.5)          |

| 審査請求日    | 令和6年1月23日(2024.1.23)        |

|          |                                            |

|----------|--------------------------------------------|

| (73)特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74)代理人  | 110003281<br>弁理士法人大塚国際特許事務所                |

| (72)発明者  | 伊藤 真麻<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

| (72)発明者  | 大西 智也<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

|          | 審査官<br>越河 勉                                |

最終頁に続く

(54)【発明の名称】 撮像装置、電子機器、および、画像生成装置

**(57)【特許請求の範囲】****【請求項1】**

光電変換素子をそれぞれ含む複数の画素が配された撮像部と、前記撮像部から出力された画像信号を処理する信号処理部と、前記撮像部から出力された前記画像信号を記憶し、前記信号処理部に前記画像信号を転送する記憶部と、を含む撮像装置であって、

前記記憶部は、前記撮像部から出力された複数の画像信号を複数のサブフレームとして記憶し、

前記信号処理部は、

(1)各サブフレームについて、画素値が所定の閾値を超える飽和画素の数が所定の数以下であるか否かを判定し、

(2)前記記憶部に記憶された前記複数のサブフレームから、前記飽和画素の数が前記所定の数以下であるサブフレームを選択し、

(3)前記複数の画素のそれぞれの画素について、当該選択されたサブフレームのそれぞれの画素値を加算した信号に基づいて1枚のフレームを生成する、

ことを特徴とする撮像装置。

**【請求項2】**

前記信号処理部は、

前記飽和画素の数が前記所定の数以下の画像信号の数に基づいて、補正係数を生成し、

前記選択されたサブフレームを前記補正係数に従って補正することを特徴とする請求項1に記載の撮像装置。

**【請求項 3】**

前記複数の画素は、互いに異なる波長帯域の光に感度を有する複数の画素群を含み、

前記信号処理部は、前記複数の画像信号のそれぞれについて、前記複数の画素群のそれぞれの画素群ごとに、前記飽和画素の数が前記所定の数以下であるか否かを判定することを特徴とする請求項 1 又は 2 に記載の撮像装置。

**【請求項 4】**

前記閾値が、前記複数の画素群のそれぞれの画素群ごとに異なることを特徴とする請求項 3 に記載の撮像装置。

**【請求項 5】**

前記信号処理部は、

10

前記選択されたサブフレームのそれぞれについて、画素値が前記所定の閾値を超える飽和画素が存在するか否かを判定し、

前記飽和画素の画素値を、前記複数の画素のうち前記飽和画素に近接する画素の画素値に基づいて補正し、

前記選択されたサブフレームのうち前記飽和画素を含まない画像信号と、前記選択されたサブフレームのうち前記飽和画素の画素値を補正した画像信号と、に基づいて前記 1 枚のフレームのデータを生成することを特徴とする請求項 1 に記載の撮像装置。

**【請求項 6】**

前記複数の画素は、互いに異なる波長帯域の光に感度を有する複数の画素群を含み、

前記信号処理部は、前記飽和画素の信号値を、前記複数の画素群のうち前記飽和画素を含む画素群とは異なる画素群の画素の画素値に基づいて補正することを特徴とする請求項 5 に記載の撮像装置。

20

**【請求項 7】**

前記撮像装置は、積層して配された第 1 基板および第 2 基板を含み、

前記第 1 基板が、前記撮像部を含み、

前記第 2 基板が、前記信号処理部を含むことを特徴とする請求項 1 乃至 6 の何れか 1 項に記載の撮像装置。

**【請求項 8】**

前記第 2 基板が、前記記憶部を含むことを特徴とする請求項 7 に記載の撮像装置。

**【請求項 9】**

30

前記撮像装置は、前記第 1 基板と積層して配された第 3 基板をさらに含み、

前記第 3 基板が、前記記憶部を含むことを特徴とする請求項 7 に記載の撮像装置。

**【請求項 10】**

前記複数の画像信号のそれぞれの信号のビット数よりも、前記 1 枚のフレームのそれぞれの信号のビット数の方が多いことを特徴とする請求項 1 乃至 9 の何れか 1 項に記載の撮像装置。

**【請求項 11】**

請求項 1 乃至 10 の何れか 1 項に記載の撮像装置と、

前記撮像装置の動作を制御する制御装置と、

を備えることを特徴とする電子機器。

40

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、撮像装置、電子機器、および、画像生成装置に関する。

**【背景技術】****【0002】**

C M O S イメージセンサなどの、光電変換素子を使用した撮像装置において、ダイナミックレンジの拡大が求められている。特許文献 1 には、イメージセンサの画素から得られた複数のフレームの画像を、イメージセンサの外部に設けられた D S P の積分メモリで積分し、ダイナミックレンジを向上させることが示されている。

50

【先行技術文献】

【特許文献】

【0003】

【文献】特開2003-259234号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献1は、ダイナミックレンジを向上させることができるもの、飽和画素が存在するフレームがある場合に、生成される画像に輝度むらや色むらなどが生じて画質が低下する可能性がある。

10

【0005】

本発明は、撮像装置において、ダイナミックレンジを向上させ、かつ、画質を向上させるのに有利な技術を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記課題に鑑みて、本発明の実施形態に係る撮像装置は、光電変換素子をそれぞれ含む複数の画素が配された撮像部と、前記撮像部から出力された信号を処理する信号処理部と、前記撮像部から出力された信号を記憶し、前記信号処理部に転送する記憶部と、を含む撮像装置であって、前記記憶部は、前記撮像部に配された前記複数の画素が出力する複数の画像信号を複数のサブフレームとして記憶した後に、前記複数のサブフレームのうちの所定の条件を満たすサブフレームを1枚のフレームを構成するための信号として出力することを特徴とする。

20

【発明の効果】

【0007】

本発明によれば、撮像装置において、ダイナミックレンジを向上させ、かつ、画質を向上させるのに有利な技術を提供することができる。

【図面の簡単な説明】

【0008】

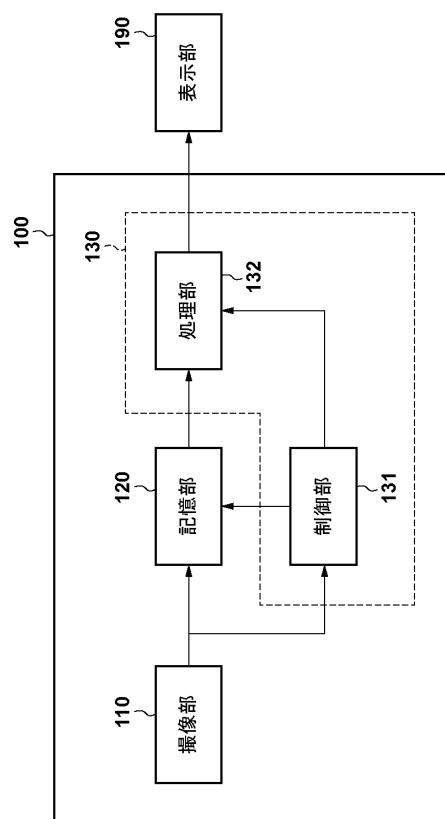

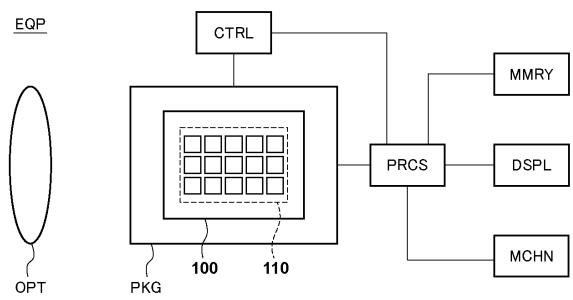

【図1】本実施形態の撮像装置の構成の概略を示すブロック図。

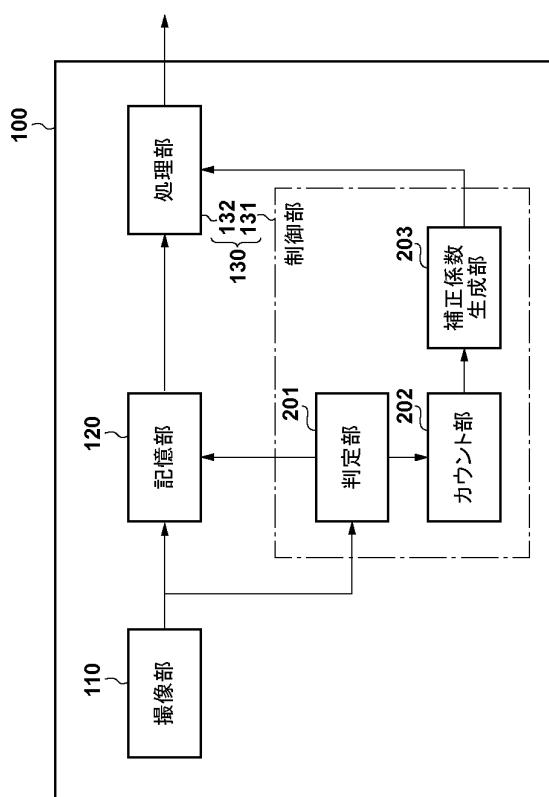

【図2】本実施形態の撮像装置の信号処理部の構成の概略を示すブロック図。

30

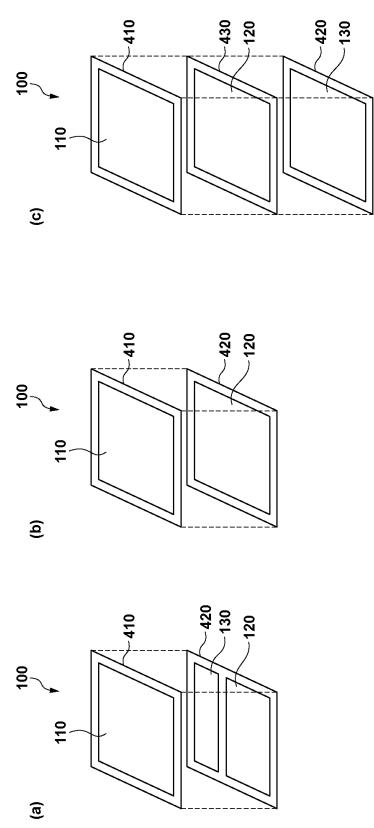

【図3】本実施形態の撮像装置の各構成の配置例を示す図。

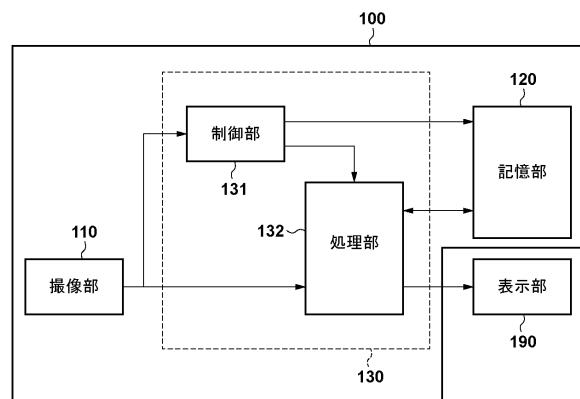

【図4】本実施形態の撮像装置の構成の概略を示すブロック図。

【図5】本実施形態の撮像装置が組み込まれたカメラの構成例を示す図。

【発明を実施するための形態】

【0009】

以下、添付図面を参照して実施形態を詳しく説明する。なお、以下の実施形態は特許請求の範囲に係る発明を限定するものではない。実施形態には複数の特徴が記載されているが、これらの複数の特徴の全てが発明に必須のものとは限らず、また、複数の特徴は任意に組み合わせられてもよい。さらに、添付図面においては、同一若しくは同様の構成に同一の参照番号を付し、重複した説明は省略する。

40

【0010】

図1～図5を参照して、本開示の実施形態による撮像装置について説明する。図1は、本実施形態の撮像装置100の構成例の概略を示すブロック図である。図1に示されるように、撮像装置100は、撮像部110、記憶部120、信号処理部130を含む。

【0011】

撮像部110には、光電変換素子をそれぞれ含む複数の画素が、平面視において2次元アレイ状に配されている。平面視とは、後述する基板の光入射面に対して垂直な方向から視ることを指す。また、断面とは、基板の光入射面と垂直な方向における面を指す。なお、微視的に見て基板の光入射面が粗面である場合は、巨視的に見たときの基板の光入射面を基準として平面視を定義する。撮像部110において、各画素に入射した光は、入射光

50

量に応じた電気信号に変換される。例えば、撮像部 110 は、MOSトランジスタを含むCMOSイメージセンサであってもよい。撮像部 110 は、例えば、アナログ / デジタル (A / D) 変換回路を含み、それぞれの画素に配された光電変換素子で生成されたアナログ信号を、デジタル信号に変換して出力しうる。

#### 【0012】

記憶部 120 は、撮像部 110 から出力される画像信号を記憶する。具体的には、撮像部 110 に配された複数の画素の各画素の画素値を含む画像信号を記憶する。そして、記憶部 120 は、記憶された画像信号を信号処理部 130 に転送する。記憶部 120 は、本実施形態において、撮像部 110 で生成された画像信号のデータを蓄積するDRAM (Dynamic Random Access Memory) などのメモリでありうる。

10

#### 【0013】

図 1 に示される構成において、信号処理部 130 は、撮像部 110 から出力される信号から画像データを生成する。信号処理部 130 は、制御部 131 および処理部 132 を含む。制御部 131 は、記憶部 120 を構成するDRAMへの画像信号の書き込みや、記憶部 120 に書き込まれた信号を処理部 132 へ読み出す制御を行う。また、制御部 131 は、処理部 132 を制御する。処理部 132 は、制御部 131 の制御に従って、記憶部 120 に一時的に記憶された複数の画像信号を用いて、加算、平均、除算、ビットシフト (ビット拡張) などの演算処理を行い、複数の画像信号から 1 つの画像データを生成する。より具体的には、処理部 132 は、ハイダイナミックレンジ合成 (High-dynamic range rendering : HDR) 処理を行い、表示用の画像データを生成する。撮像装置 100 において生成された画像データは、撮像装置 100 から出力され、例えば、図 1 に示されるように表示部 190 において表示されうる。ここで、処理部 132 における画像データの生成は必須ではなく、表示部 190 において画像が表示可能となるようなデータ (例えば、画像信号) が処理部 132 から出力される構成を有していればよい。

20

#### 【0014】

次いで、図 1 および図 2 を用いて HDR 处理および画像データの出力について説明する。図 2 は、信号処理部 130 のうち制御部 131 の構成例の概略を示すブロック図である。HDR 处理は、撮像部 110 の各画素から出力される画素値をそれぞれ含む複数の画像信号を合成し、1 回の撮像で得られる以上の階調性を得る処理である。以下の説明において、説明および演算式の例を簡単化するために、同じ階調数の N 枚の画像信号を用いて、1 枚の画像データを加算合成する例を示す。しかしながら、これに限られることはなく、撮像の条件が異なる複数の画像信号を合成する場合であっても、本開示は適用可能であり、その場合は、HDR 合成を行う際の演算式を撮像の条件などに応じて適宜、重みづけをした演算を行えばよい。

30

#### 【0015】

まず、撮像を開始すると、撮像部 110 に配された複数の画素の各画素の画素値を含む画像信号が、撮像部 110 から記憶部 120 に出力される。信号処理部 130 の制御部 131 は、記憶部 120 に蓄積される画像信号の数をカウントし、N (N は 2 以上の整数) 回分の画像信号を蓄積した後、処理部 132 から 1 枚の画像データとして 1 回で出力する。つまり、記憶部 120 は、N フレーム分の画像信号を N 個のサブフレームとして記憶、蓄積し、1 枚のフレーム (画像) を構成するための信号として処理部 131 へと出力する。1 フレームは、例えば、撮像部 110 に配された複数の画素から得られる画像信号から生成することができる。つまり、1 フレームは、複数の画素の 1 行目の画素から最終行の画素までの画像信号から生成することができる。N 回分の画像信号を蓄積することによって、複数の画像信号のそれぞれの信号のビット数よりも、画像データ (1 枚のフレームのそれぞれの信号) のビット数の方が多くなる。つまり、撮像部 110 に配された画素の容量値が小さく、信号値が飽和しやすい場合であっても、複数の画像信号の数の分、得られる画像データのダイナミックレンジを増やすことが可能となる。

40

#### 【0016】

50

しかしながら、それぞれの画像信号において、画素値が所定の閾値を超えて飽和してしまった飽和画素が存在する可能性がある。所定の閾値とは、例えば、画素に配された光電変換素子の飽和容量を超える値である。飽和画素からの出力を含む複数の画像信号を1つの画像データに合成した場合、画質が劣化してしまう可能性がある。例えば、撮像装置が複数の異なる色を透過するカラーフィルタを含み、カラーフィルタを透過した光を光電変換素子が光電変換する場合は、色ずれが生じうる。また、例えば、街頭カメラなど屋外に設置される電子カメラにおいて、蛍光灯や信号機などのLED照明は、フレームごとに輝度変動するフリッカ現象を起こすなど、明るさが不規則に変化しうる。このため、事前に撮像条件を調整していたとしても、飽和した画素値を含む画像信号が発生してしまう可能性がある。

10

#### 【0017】

そこで、本実施形態において、信号処理部130の制御部131は、記憶部120に画像信号を蓄積する際に、それぞれの画像信号（サブフレーム）を構成する各画素の画素値が所定の閾値を超えて飽和に達しているか否かを判定する。例えば、制御部131は、図2に示されるように、画像信号を構成する各画素の画素値が所定の閾値を超えて飽和に達しているか否かを判定する判定部201を含んでいてもよい。また、このとき、信号処理部130の制御部131は、飽和画素から出力された画素値を含む画像信号の数（ここでは、M枚とする）、または、閾値を超えて飽和した画素値を含まない画像信号の数（N-M枚）をカウントする。例えば、制御部131は、図2に示されるように、これらの画像信号の数をカウントするカウント部202を含んでいてもよい。さらに、信号処理部130の制御部131は、複数の画像信号のうち飽和画素から出力された画素値を含む画像信号の数、または、飽和した画素値を含まない画像信号の数に基づいて、補正係数を生成する。例えば、制御部131は、図2に示されるように、補正係数を生成するための補正係数生成部203を含んでいてもよい。本実施形態において、補正係数は、 $\{N / (N - M)\}$ となりうる。

20

#### 【0018】

次いで、信号処理部130の処理部132は、複数の画像信号のうち飽和した画素値を含まない画像信号を補正係数に従って補正し、1枚のフレームを構成するための信号を生成する。例えば、処理部132は、表示部190で表示を行うための画像用のデータでありうる1つの画像データを生成する。例えば、処理部132は、記憶部120に一時的に記憶された飽和した画素値を含まない画像信号を加算し、さらに、補正係数 $\{N / (N - M)\}$ を乗算する演算を行う。これによって、N回分の画像信号を加算することによってN倍のビット数の画像データを得る処理において、飽和した画素値を含む画像信号を除外して加算したことによって(N-M)倍のビット数に留まってしまうことを補正する。

30

#### 【0019】

以上の処理によって、撮像部110に配された画素の容量が小さい場合であっても、N回分の撮像によって、得られる画像データのビット数を増やすことができる。また、飽和した画素値を含む画像信号をHDR合成の際に用いないことによって、色ずれなどのない画像データを取得することが可能となる。結果として、本実施形態において、ダイナミックレンジを向上と画質を向上とを両立させた撮像装置100を得ることができる。

40

#### 【0020】

上述において、飽和画素から出力された画素値を含む画像信号をHDR合成に用いないことを説明した。換言すると、信号処理部130の判定部201は、画像信号中に複数の画素のうち1画素以上の飽和画素が存在するか否かで、HDR合成から画像信号を除外するか否かを判定している。しかしながら、これに限られることはない。信号処理部130は、撮像部110が出力する、複数の画素の各画素の画素値をそれぞれ含む複数の画像信号のうち、それぞれの画像信号を構成する各画素の画素値が所定の条件を満たす画像信号に基づいて1つの画像データを生成すればよい。

#### 【0021】

例えば、信号処理部130の判定部201は、複数の画像信号のそれぞれにおいて、画

50

素値が所定の閾値を超える飽和画素の数が所定の数以下であるか否かを判定してもよい。H D R合成に用いる画像信号に含まれる飽和画素からの出力の数は、撮像装置100の仕様に応じて、適宜設定すればよい。この場合、信号処理部130の処理部132は、複数の画像信号のうち飽和画素の数が所定の数以下である画像信号に基づいて1つの画像データを生成しうる。また、この場合、信号処理部130の補正係数生成部203は、複数の画像信号のうち飽和画素の数が所定の数以下の（または、所定の数を超える）画像信号の数に基づいて、補正係数を生成しうる。さらに、信号処理部130の処理部132は、複数の画像信号のうち飽和画素の数が所定の数以下の（または、所定の数を超える）画像信号を補正係数に従って補正し、1つの画像データを生成しうる。

#### 【0022】

10

また、画素値が飽和しているか否かの判定は、画像信号に含まれる各画素の画素値の任意の出力値を閾値に設定してもよい。撮像部110に配された複数の画素は、互いに異なる波長帯域の光に感度を有する複数の画素群（例えば、赤の波長域に感度を有するR画素群、緑の波長域に感度を有するG画素群、青の波長域に感度を有するB画素群）を含みうる。撮像装置100の仕様に応じて、画素の色ごと、出力チャネルごとなど、画素値が飽和しているか否かの閾値は、個別で設定してもよい。つまり、画素値が飽和しているか否かの閾値が、複数の画素群（例えば、R画素群、G画素群およびB画素群）のそれぞれの画素群ごとに異なっていてもよい。

#### 【0023】

20

上述の実施形態では、飽和している画素値を含む画像信号を用いないことによって、画質を向上させることを説明した。しかしながら、これに限られることはない。例えば、飽和画素の画素値を、撮像部110に配された複数の画素のうち飽和画素に近接する画素の画素値に基づいて補正し、飽和画素を含まない画像信号と、飽和画素の画素値を補正した画像信号と、に基づいて1つの画像データが生成されてもよい。例えば、R画素群、G画素群、B画素群を含み構成される撮像部110から取得した画像信号において、R画素群に含まれる画素が飽和している場合を考える。この場合、飽和画素を含まない画像信号のRGB出力から色ごとの出力の相対比を求め、飽和した画素に近接するG画素やB画素の出力から画素値が飽和した画素の出力を推定して補正してもよい。つまり、信号処理部130（例えば、補正係数生成部203）が、飽和画素の信号値を、複数の画素群のうち飽和画素を含む画素群（R画素群）とは異なる画素群（G画素群やB画素群）の画素の画素値に基づいて補正してもよい。また、画像信号中の位置（座標、エリアなど）を所定の条件に基づいて判定し、位置に基づいて補正が実施されてもよい。

#### 【0024】

30

本実施形態において、画像信号を取得した回数分のビット数を保持するため、画像信号を $(N - M)$ 回分、加算したデータに補正係数として $\{N / (N - M)\}$ を乗算する処理を行ったが、飽和画素から出力された画素値を含む画像信号を除外するのみにとどめてもよい。また、例えば、補正係数 $\{N / (N - M)\}$ に適当な重みづけ係数を追加して、ダイナミックレンジに対して出力が適正になるようにしてもよい。この場合、飽和画素から出力された画素値を含む画像信号の飽和画素以外の画素値を参照して重みづけ係数が、生成されてもよいし、別途、画素への入射光量を検出する検出部などを設けて重みづけ係数が、生成されてもよい。複数の画像信号を加算した後の画像データに対して、適当な重みづけができればよい。

#### 【0025】

40

また、本実施形態において、記憶部120としてDRAMを用いることを説明した。しかしながら、これに限られることはない。上述の処理が高速に行えれば、揮発性メモリや不揮発性メモリなど、適当な記憶装置が用いられればよい。また、記憶部120としてDRAMを用い、さらに撮像装置100から出力された画像データを、ハードディスクやフラッシュメモリなどの不揮発性メモリに記憶（記録）してもよい。

#### 【0026】

また、上述の演算処理は、記憶部120、制御部131および処理部132を含む信号

50

処理部 130 で実現可能であれば、いずれのブロックで機能分担してもよい。本実施形態において、制御部 131 が、記憶部 120 の書き込み読み出しの制御、撮像部 110 から出力される画像信号の数のカウント、画素値が閾値以下であるか否かの判定（飽和の判定）飽和画素から出力された画素値を含む画像信号の除外、補正係数の生成などの処理を行うとしたが、これに限られるものではない。それぞれの機能が、別々、又は適当に組み合わされた構成によって実行されてもよい。また、例えば、処理部 132 が行うし演算処理が、制御部 131 で実行されてもよい。

#### 【 0027 】

図 3 ( a ) ~ 図 3 ( c ) を用いて、本実施形態の撮像装置 100 の各構成の配置例について説明する。上述のように複数の画像信号を合成し 1 つの画像データを生成する場合、動画像の撮像など、画像データを生成する速度を維持するために、高速な処理が必要となる。このため、撮像装置 100 は、各種の信号を転送するための配線パターン長が短くなりうる積層構造を有する半導体チップを含むことが好ましい。積層構造を有する半導体チップとは、複数の半導体層が配線層を介して積層された構造である。積層構造で構成された 1 つの半導体チップに、撮像部 110 および信号処理部 130 が配されることによって、高速な画像処理が実現しうる。なお、撮像部 110 、記憶部 120 、および、信号処理部 130 のすべての構成が 1 つの半導体チップに配される必要はない。例えば、後述するように、記憶部 120 がある基板に配されており、当該基板と撮像部 110 を有する基板とが積層されていない構成としてもよい。

10

#### 【 0028 】

例えば、撮像装置 100 が、図 1 に示される構成を有する場合は、図 3 ( a ) に示される構成や、図 3 ( c ) に示される構成を採用することができる。図 3 ( a ) は、積層して配された基板 410 および基板 420 を含む、撮像装置 100 を開示している。基板 410 は撮像部 110 を含み、基板 420 は信号処理部 130 および記憶部 120 を含む。この場合、基板 410 の側から（図 3 ( a ) の上側）から光が入射しうる。なお、光の入射側は、図 3 ( b ) 、図 3 ( c ) の構成においても同様である。また、基板 410 、 420 は、シリコンなどの半導体基板と、配線パターンおよび層間絶縁層を含む配線部と、を含む。

20

#### 【 0029 】

さらに、例えば、図 3 ( c ) に示されるように、撮像装置 100 が、積層して配された基板 410 、基板 420 および基板 430 を含んでいてもよい。この場合、例えば、基板 410 が撮像部 110 を含み、基板 430 が記憶部 120 を含み、基板 420 が信号処理部 130 を含む。基板 430 は、基板 410 と基板 420 との間に配される。なお、基板 420 と基板 430 とは入れ替えて積層されてもよい。つまり、信号処理部 130 を有する基板 420 が、記憶部 120 を有する基板 430 と基板 410 との間に配されていてもよい。

30

#### 【 0030 】

また、例えば、撮像装置 100 が、図 4 に示されるような構成を有する場合、図 3 ( b ) に示されるように、基板 410 が撮像部 110 を有し、基板 420 が信号処理部 130 を有する。この場合、上述のように記憶部 120 は、異なる半導体チップに配されている。基板 410 と基板 420 とが積層された半導体チップと、記憶部 120 が配された半導体チップとは、例えば、同じ半導体パッケージ内に配されうる。

40

#### 【 0031 】

撮像装置 100 が積層チップである場合、図 3 ( a ) ~ 図 3 ( c ) に示されるようにそれぞれの構成が、1 つの基板上で完結していなくてもよい。例えば、図 3 ( a ) に示される構成において、記憶部 120 が、基板 410 と基板 420 との両方に配されていてもよい。また、例えば、図 3 ( c ) に示される構成において、信号処理部 130 が基板 420 と基板 430 とに配されていてもよい。この場合、例えば、基板 420 に信号処理部 130 のうち制御部 131 の機能が搭載され、基板 430 に信号処理部 130 のうち処理部 132 の機能が搭載されていてもよい。撮像装置 100 に求められる仕様に応じて、適當な

50

配置がそれぞれ選択されればよい。

**【 0 0 3 2 】**

図3(b)、図4に示されるように、記憶部120が配された基板を撮像部110が配された基板と積層させない場合、各基板を積層した場合よりも、撮像部110と記憶部120との間の配線数が多くなり、回路設計も複雑になりうる。しかしながら、記憶部120を有する基板と撮像部110を有する基板とを積層させないことによって、より大容量の記憶部120を用いることが可能となりうる。結果として、ダイナミックレンジの拡大に用いることができる画像信号の枚数が増え、よりダイナミックレンジが大きく、画質が向上した画像を得ることが可能となる。

**【 0 0 3 3 】**

上述の実施形態では、撮像部110によって撮像された画像信号を、信号処理部130がHDR合成を行う撮像装置100について説明したが、本開示は、これに限られることはない。例えば、信号処理部130が、単独で用いられてもよい。つまり、信号処理部130(画像生成装置とも呼ばれる。)に、撮像装置100とは別の撮像装置に配された撮像部からの画像信号が入力され、信号処理部130がHDR合成を行い、画像データが生成されてもよい。また、上述の画像データを生成する方法のそれぞれの工程が、撮像装置100の外部に配されたコンピュータなどで実施されてもよい。

10

**【 0 0 3 4 】**

上述の実施形態に係る撮像装置100の応用例を以下に説明する。図5は、撮像装置100を搭載した電子機器EQPの模式図である。図5は、電子機器EQPの一例としてカメラを示している。ここで、カメラの概念には、撮影を主目的とする装置のみならず、撮影機能を補助的に備える装置(例えば、パーソナルコンピュータや、スマートフォンなどの携帯端末)も含まれる。

20

**【 0 0 3 5 】**

撮像装置100は、撮像部110が設けられた積層構造の半導体チップでありうる。撮像装置100は、図5に示されるように、半導体パッケージPKGに収容されている。撮像装置100が、図3に示されるような構成を有する場合、記憶部120は、この半導体パッケージPKG内に配されていてもよい。パッケージPKGは、撮像装置100が固定された基体と、撮像装置100に対向するガラスなどの蓋体と、基体に設けられた端子と撮像装置100に設けられた端子とを接続するボンディングワイヤやバンプなどの導電性の接続部材と、を含みうる。機器EQPは、光学系OPT、制御装置CTR、処理装置PRCS、表示装置DSP、記憶装置MMRYの少なくともいずれかをさらに備えていてもよい。

30

**【 0 0 3 6 】**

光学系OPTは、撮像装置100に結像するものであり、例えば、レンズやシャッタ、ミラーでありうる。制御装置CTRは、撮像装置100の動作を制御するものであり、例えば、ASICなどの半導体デバイスでありうる。処理装置PRCSは、撮像装置100から出力された信号を処理するものであり、CPUやASICなどの半導体デバイスでありうる。表示装置DSPは、撮像装置100で上述のHDR合成を行い得られた画像データを表示する、EL表示装置や液晶表示装置でありうる。記憶装置MMRYは、撮像装置100で得られたHDR合成された画像データを記憶する、磁気デバイスや半導体デバイスである。記憶装置MMRYは、SRAMやDRAMなどの揮発性メモリ、あるいは、フラッシュメモリやハードディスクドライブなどの不揮発性メモリでありうる。機械装置MCHNはモーター・エンジンなどの可動部あるいは推進部を有する。カメラにおける機械装置MCHNはズーミングや合焦、シャッタ動作のために光学系OPTの部品を駆動することができる。機器EQPでは、撮像装置100から出力された画像データを表示装置DSPに表示したり、機器EQPが備える通信装置(不図示)によって外部に送信したりする。このため、機器EQPは、撮像装置100が有する信号処理部130や記憶部120などに含まれる記憶回路部や演算回路部とは別に、記憶装置MMRYや処理装置PRCSをさらに備えていてもよい。

40

50

**【 0 0 3 7 】**

撮像装置 100 が組み込まれたカメラは、監視カメラや、自動車や鉄道車両、船舶、航空機あるいは産業用ロボットなどの輸送機器に搭載される車載カメラなどにも適用されうる。加えて、撮像装置 100 が組み込まれたカメラは、輸送機器に限らず、高度道路交通システム（ITS）など、広く物体認識を利用する機器に適用することができる。

**【 0 0 3 8 】**

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア（プログラム）を、ネットワークまたは各種の記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータにおける 1 つ以上のプロセッサ（例えば、CPU や MPU。）がプログラムを読み出して実行する処理である。また、1 つ以上の機能を実現する回路（例えば、ASIC。）によっても実現可能である。

10

**【 0 0 3 9 】**

発明は上記実施形態に制限されるものではなく、発明の精神及び範囲から離脱することなく、様々な変更及び変形が可能である。従って、発明の範囲を公にするために請求項を添付する。

**【 符号の説明 】****【 0 0 4 0 】**

100：撮像装置、110：撮像部、130：信号処理部

20

30

40

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

10

20

30

40

50

【図 5】

10

20

30

40

50

---

フロントページの続き

- (56)参考文献

- 特開2007-228297 (JP, A)

特開2004-180308 (JP, A)

特開2006-333313 (JP, A)

国際公開第2017/221641 (WO, A1)

米国特許出願公開第2004/0100565 (US, A1)

特開2018-147417 (JP, A)

特開2014-170570 (JP, A)

特開2020-072410 (JP, A)

- (58)調査した分野 (Int.Cl., DB名)

- H04N 25/57

H04N 25/44