(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5417993号

(P5417993)

(45) 発行日 平成26年2月19日(2014.2.19)

(24) 登録日 平成25年11月29日(2013.11.29)

(51) Int.Cl.

H03M 1/14 (2006.01)

F 1

H03M 1/14

A

請求項の数 6 (全 30 頁)

(21) 出願番号 特願2009-132360 (P2009-132360)

(22) 出願日 平成21年6月1日 (2009.6.1)

(65) 公開番号 特開2010-278985 (P2010-278985A)

(43) 公開日 平成22年12月9日 (2010.12.9)

審査請求日 平成24年5月24日 (2012.5.24)

(73) 特許権者 390020248

日本テキサス・インストルメンツ株式会社

東京都新宿区西新宿六丁目24番1号

(72) 発明者 大山 聰一朗

東京都新宿区西新宿六丁目24番1号 日

本テキサス・インストルメンツ株式会社内

(72) 発明者 有吉 勝彦

東京都新宿区西新宿六丁目24番1号 日

本テキサス・インストルメンツ株式会社内

審査官 船越 亮

最終頁に続く

(54) 【発明の名称】アナログ-デジタル変換回路

## (57) 【特許請求の範囲】

## 【請求項 1】

入力信号をデジタル信号に変換し、上記デジタル信号に対応するアナログ信号と上記入力信号との差分を増幅し、当該増幅結果を後段に出力する複数の縦続接続された変換ステージと、

所定の動作モードにおいて上記複数の変換ステージの一部を停止させる第1の停止制御回路と、

上記所定の動作モードにおいて停止状態となる上記変換ステージへの入力信号を、当該停止状態の変換ステージの後段に入力する第1のバイパス回路と、

第1のクロック信号と当該第1のクロック信号と位相が180°ずれている第2のクロック信号とを供給するクロック生成回路と、

初段の上記変換ステージへの入力信号に基づいて上位の変換ステージから下位の変換ステージに向かって順次に生成される複数の上記デジタル信号が共通のタイミングで出力されるように上記複数のデジタル信号の各々にそれぞれ異なる遅延を与える複数の遅延回路であって、各遅延回路が対応する上記変換ステージの縦続接続中の位置に対応する数のラッチ回路を含み、当該ラッチ回路が上記変換ステージから出力される上記デジタル信号を保持する、上記複数の遅延回路と、

上記所定の動作モードにおいて、上記停止状態の変換ステージより下位の変換ステージにおける入力信号のサンプリングのタイミングとサンプリング結果の保持のタイミングとを反転させるタイミング制御回路と、

10

20

上記所定の動作モードにおいて、上記停止状態の変換ステージより下位の変換ステージの上記デジタル信号が上記遅延回路により遅延されて出力されるタイミングと、上記停止状態の変換ステージより上位の変換ステージの上記デジタル信号が上記遅延回路により遅延されて出力されるタイミングとが一致するように、当該上位の変換ステージを上記停止状態の変換ステージの数だけ下位の遅延回路にずらして接続する接続切り替え回路と、

を含み、

上記複数の変換ステージの偶数段が上記第1のクロック信号に応答して動作し、上記複数の変換ステージの奇数段が上記第2のクロック信号に応答して動作し、

上記遅延回路内の隣接する2つの上記ラッチ回路の一方が上記第1のクロック信号に応答して動作し、その他方が上記第2のクロック信号に応答して動作し、

10

上記複数の変換ステージの奇数段が入力信号をサンプリングするとともに上記デジタル信号を出力するときに上記複数の変換ステージの偶数段がサンプリング結果を保持するとともに当該サンプリング結果に応じた出力信号を生成し、上記複数の変換ステージの奇数段がサンプリング結果を保持するとともに当該サンプリング結果に応じた出力信号を生成するときに上記複数の変換ステージの偶数段が入力信号をサンプリングするとともに上記デジタル信号を出力し、

上記第1の停止制御回路が停止させるべき上記変換ステージに対する電源の供給又はクロック信号の供給を停止する、

アナログ - デジタル変換回路。

#### 【請求項2】

20

請求項1に記載のアナログ - デジタル変換回路であって、

上記タイミング制御回路が、上記所定の動作モードにおいて、上記変換ステージにおける上記タイミングの反転に合わせて、上記停止状態の変換ステージより下位の変換ステージの上記デジタル信号を保持する上記遅延回路内のラッチ回路における当該保持のタイミングを変更する、アナログ - デジタル変換回路。

#### 【請求項3】

請求項1に記載のアナログ - デジタル変換回路であって、

上記所定の動作モードにおいて、上記停止状態の変換ステージの上記デジタル信号に遅延を与える上記遅延回路への電源の供給又はクロック信号の供給を停止する第2の停止制御回路と、

30

を更に含む、アナログ - デジタル変換回路。

#### 【請求項4】

半周期位相のずれた第1及び第2のクロック信号を供給するクロック信号供給回路と、

上記第1のクロック信号に応答して入力アナログ信号をサンプルホールドして出力するサンプルホールド回路と、

前段から入力するアナログ信号をデジタル変換してデジタル値を出力し、上記アナログ信号と上記デジタル値をアナログ変換したアダログ値との差を増幅して後段に出力する変換ステージが複数個直列接続されており、初段に上記サンプルホールド回路の出力を受け、奇数段の変換ステージが上記第2のクロック信号に応答して動作し、偶数段の変換ステージが上記第1のクロック信号に応答して動作する、変換部と、

40

上記第1及び第2のクロック信号に応答して上記変換部の各変換ステージから出力される上記デジタル値を入力して各デジタル値に所定の遅延時間をそれぞれ与えて出力する遅延部であって、上記変換ステージの数に対応する複数の遅延回路を含み、各遅延回路が入力するデジタル値を出力する変換ステージの位置に対応する数のラッチ回路を含み、上記遅延回路内の隣接する2つのラッチ回路の一方が第1のクロック信号に応答して動作し、その他方が第2のクロック信号に応答して動作する、上記遅延部と、

上記遅延部から同時に出力される上記デジタル値を補正する補正部と、

上記補正部から出力されるビット信号を受けるレジスタ部と、

上記変換部の少なくとも1つの上記変換ステージをバイパスするように、バイパスされる変換ステージの入力端と出力端とを結合するバイパス回路と、

50

バイパスされる上記変換ステージの個数が奇数であるときに上記第1のクロック信号と第2のクロック信号とを入れ替えてバイパスされた上記変換ステージ以降の変換ステージに供給するクロック切り替え回路と、

上記変換部と上記遅延部との間に接続され、バイパスされる変換ステージより下位の変換ステージの上記デジタル値が上記遅延部により遅延されて出力されるタイミングと、バイパスされる変換ステージより上位の変換ステージの上記デジタル値が上記遅延部により遅延されて出力されるタイミングとが一致するように、当該上位の変換ステージをバイパスされる変換ステージの数だけ下位の遅延回路にずらして接続する接続切り替え回路と、を含み、

バイパスされる変換ステージの数に応じて上記レジスタ部から出力されるデジタル信号のビット数が変化する、

アナログ - デジタル変換回路。

#### 【請求項5】

請求項4に記載のアナログ - デジタル変換回路であって、

バイパスされる上記変換ステージへの電源電圧の供給が停止される、又はバイパスされる上記変換ステージへのクロック信号の供給が停止される、アナログ - デジタル変換回路。

#### 【請求項6】

請求項4又は5に記載のアナログ - デジタル変換回路であって、

少なくとも1つの上記変換ステージがバイパスされるときに、上記第1及び第2のクロック信号の周波数が低くなる、アナログ - デジタル変換回路。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、複数の変換ステージによって上位ビットから下位ビットへ順次に変換を行うパイプライン型のアナログ - デジタル変換回路に関する。

##### 【背景技術】

##### 【0002】

パイプライン型のアナログ - デジタル変換回路（以下、「アナログ - デジタル変換回路」を「A / Dコンバータ」と記す場合がある。）は、フラッシュ型（並列比較型）に比べて低速であるが分解能が高く、デルタシグマ型に比べて低分解能であるが高速であることから、例えば映像や通信などの比較的中速度・中分解能が求められる分野の信号処理に広く用いられている。

##### 【先行技術文献】

##### 【特許文献】

##### 【0003】

【特許文献1】特開平10-163875号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0004】

ところで、信号処理部の電力消費を削減するために、クロック信号の周波数を切り替える方法が一般に用いられている。例えばデジタルカメラの場合、メモリに記録する画像を撮影するときは、画像の解像度が高いためクロック信号の周波数を高くし、ビューファインダに被写体を映すだけの期間は、画像の解像度が低いためクロック信号を低くする。このように、ユーザの使用状況等に応じてクロック信号の周波数を切り替えることにより、主としてロジック回路の消費電流を効果的に減らすことができる。

##### 【0005】

しかしながら、一般にパイプライン型のA / Dコンバータはアナログ部とデジタル部が組み合わされた回路であり、アナログ部の増幅器等で定常に消費される電流がデジタル部の消費電流に比べて大きい。クロック信号の周波数を切り替える手法は、デジタル部に

10

20

30

40

50

おいて出力の論理値が変化する瞬間に流れる電流の削減には有効であるが、アナログ部において定常的に消費される電流の削減には全く効果がない。

【0006】

そこで、アナログ部の回路定数を動作モードに応じて変更することにより消費電流を削減する方法も考えられるが、この方法では、変更の前後において所定の性能仕様を満たすように回路定数のバランスを保つのが難しいという問題がある。

【0007】

本発明はかかる事情に鑑みてなされたものであり、その目的は、動作モードに合わせて消費電力を低減できるアナログ - デジタル変換回路を提供することにある。

【課題を解決するための手段】

10

【0008】

本発明の第1の観点に係るアナログ - デジタル変換回路は、入力信号をデジタル信号に変換し、上記デジタル信号に対応するアナログ信号と上記入力信号との差分を増幅し、当該増幅結果を後段に出力する複数の継続接続された変換ステージと、所定の動作モードにおいて上記複数の変換ステージの一部を停止させる第1の停止制御回路と、上記所定の動作モードにおいて停止状態となる上記変換ステージへの入力信号を、当該停止状態の変換ステージの後段に入力する第1のバイパス回路とを有する。

【0009】

上記アナログ - デジタル変換回路によれば、上記所定の動作モードにおいて上記複数の変換ステージが停止され、当該停止状態の変換ステージへの入力信号がその後段の変換ステージに入力される。これにより、上記アナログ - デジタル変換回路では、上記変換ステージの段数が削減された状態でアナログ - デジタル変換動作が行われる。

20

【0010】

好適に、上記第1の停止制御回路は、停止させるべき上記変換ステージに対する電源の供給又はクロック信号の供給を停止する。

【0011】

好適に、上記アナログ - デジタル変換回路は、上記複数の変換ステージの奇数段が入力信号をサンプリングするとともに上記デジタル信号を出力するとき偶数段がサンプリング結果を保持するとともに当該サンプリング結果に応じた出力信号を生成し、上記奇数段がサンプリング結果を保持するとともに当該サンプリング結果に応じた出力信号を生成するとき上記偶数段が入力信号をサンプリングするとともに上記デジタル信号を出力する。

30

この場合、上記アナログ - デジタル変換回路は、上記複数の変換ステージから出力される複数の上記デジタル信号を保持する複数のラッチ回路と、上記所定の動作モードにおいて、上記停止状態の変換ステージより下位の変換ステージにおける入力信号のサンプリングのタイミングとサンプリング結果の保持のタイミングとを反転させるタイミング制御回路とを有してよい。

また、上記タイミング制御回路は、上記所定の動作モードにおいて、上記変換ステージにおける上記タイミングの反転に合わせて、上記停止状態の変換ステージより下位の変換ステージの上記デジタル信号を保持するラッチ回路における当該保持のタイミングを変更してよい。

40

【0012】

好適に、上記アナログ - デジタル変換回路は、初段の変換ステージへの入力信号に基づいて上位の変換ステージから下位の変換ステージに向かって順次に生成される複数の上記デジタル信号が共通のタイミングで出力されるように上記複数のデジタル信号それぞれに異なる遅延を与える複数の遅延回路を有する。

【0013】

好適に、上記アナログデジタル変換回路は、上記所定の動作モードにおいて、上記停止状態の変換ステージの上記デジタル信号に遅延を与える上記遅延回路への電源の供給又はクロック信号の供給を停止する第2の停止制御回路を有する。

【0014】

50

好適に、上記アナログデジタル変換回路は、初段の変換ステージへの入力信号に基づいて上位の変換ステージから下位の変換ステージに向かって順次に生成される複数の上記デジタル信号を補正する複数の補正回路を有する。上記補正回路は、補正対象のデジタル信号の生成元の変換ステージに対して下位の変換ステージで生成されたデジタル信号の補正に伴って生じる桁上がり信号を入力し、当該入力した桁上がり信号に基づいて当該補正対象のデジタル信号を補正し、当該補正の結果に応じて発生した桁上がり信号を上記生成元の変換ステージに対して上位の変換ステージで生成されたデジタル信号の補正用に出力する。

#### 【0015】

好適に、上記アナログ - デジタル変換回路は、上記所定の動作モードにおいて、上記初段若しくは上記初段を含む一連の変換ステージが停止状態となる場合、当該停止状態の変換ステージの上記デジタル信号を補正する上記補正回路に当該デジタル信号の替わりとして各ビットの値がゼロの信号を入力する信号入力回路を有する。10

#### 【0016】

好適に、上記第1の停止制御回路は、初段若しくは初段を含む一連の変換ステージを上記所定の動作モードにおいて停止させる。

#### 【0017】

好適に、上記アナログ - デジタル変換回路は、上記所定の動作モードにおいて上記縦続接続された変換ステージに供給するクロック信号の周波数を低下させるクロック生成回路を有する。20

#### 【0018】

好適に、上記アナログ - デジタル変換回路は、上記所定の動作モードにおいて、上記停止状態の変換ステージより下位の変換ステージの上記デジタル信号が上記遅延回路により遅延されて出力されるタイミングと、上記停止状態の変換ステージより上位の変換ステージの上記デジタル信号が上記遅延回路により遅延されて出力タイミングとが一致するよう、当該上位の変換ステージと上記遅延回路との接続を切り替える切り替え回路を有する。。

#### 【0019】

好適に、上記アナログデジタル変換回路は、上記所定の動作モードにおいて、停止状態の変換ステージのデジタル信号を補正対象とする第1の上記補正回路へ入力される桁上がり信号を選択し、当該停止状態の変換ステージに対して上位の変換ステージのデジタル信号を補正対象とする第2の上記補正回路へ当該選択した桁上がり信号を入力する第2のバイパス回路を有する。30

#### 【0020】

また、本発明の第2の観点に係るアナログ - デジタル変換回路は、半周期位相のずれた第1及び第2のクロック信号を供給するクロック信号供給回路と、上記第1のクロック信号に応答して入力アナログ信号をサンプルホールドして出力するサンプルホールド回路と、前段から入力するアナログ信号をデジタル変換してデジタル値を出力し、上記アナログ信号と上記デジタル値をアナログ変換したアダログ値との差を増幅して後段に出力する変換ステージが複数個直列接続されており、初段に上記サンプルホールド回路の出力を受け、奇数段の変換ステージが上記第2のクロック信号に応答して動作し、偶数段の変換ステージが上記第1のクロック信号に応答して動作する、変換部と、上記第1及び第2のクロック信号に応答して上記変換部の各変換ステージから出力される上記デジタル値を入力して各デジタル値に所定の遅延時間をそれぞれ与えて出力する遅延部と、上記遅延部から同時に出力される上記デジタル値を補正する補正部と、上記補正部から出力されるビット信号を受けるレジスタ部と、上記変換部の少なくとも1つの上記変換ステージをバイパスするように、バイパスされる変換ステージの入力端と出力端とを結合するバイパス回路と、バイパスされる上記変換ステージの個数が奇数であるときに上記第1のクロック信号と第2のクロック信号とを入れ替えてバイパスされた上記変換ステージ以降の変換ステージに供給するクロック切り替え回路とを含み、バイパスされる変換ステージの数に応じて上記40

レジスタ部から出力されるデジタル信号のビット数が変化する。

**【発明の効果】**

**【0021】**

本発明によれば、所定の動作モードにおいて複数の変換ステージの一部を停止させた状態でアナログ - デジタル変換を行うことが可能であり、動作モードに合わせて消費電力を低減できる。

**【図面の簡単な説明】**

**【0022】**

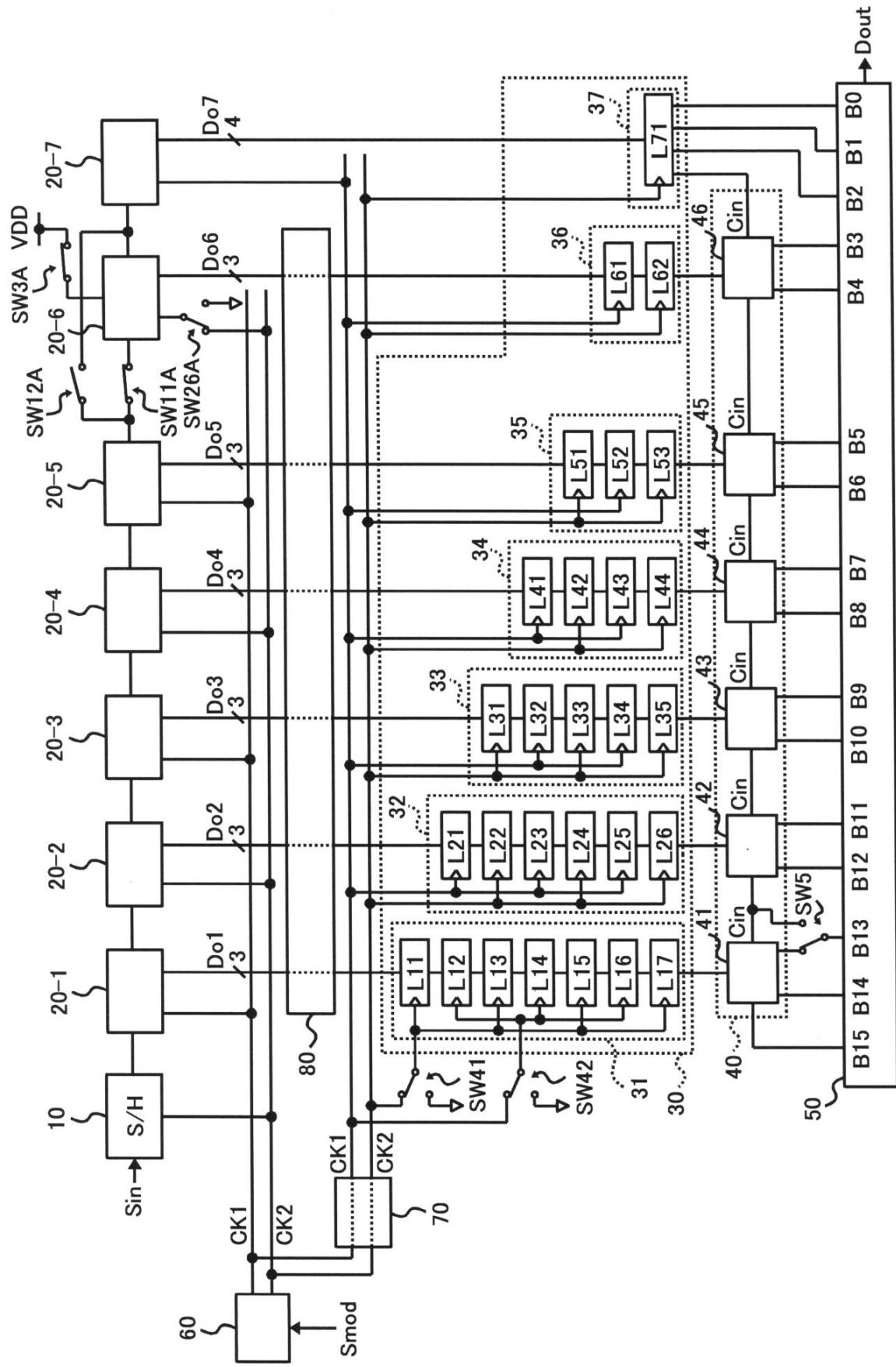

【図1】本発明の第1の実施形態に係るアナログ - デジタル変換回路の構成の一例を示す図である。 10

【図2】変換ステージの構成の一例を示す図である。

【図3】変換ステージにおけるサンプリングとホールドのタイミングを規定する2つのクロック信号のタイミングを示す図である。

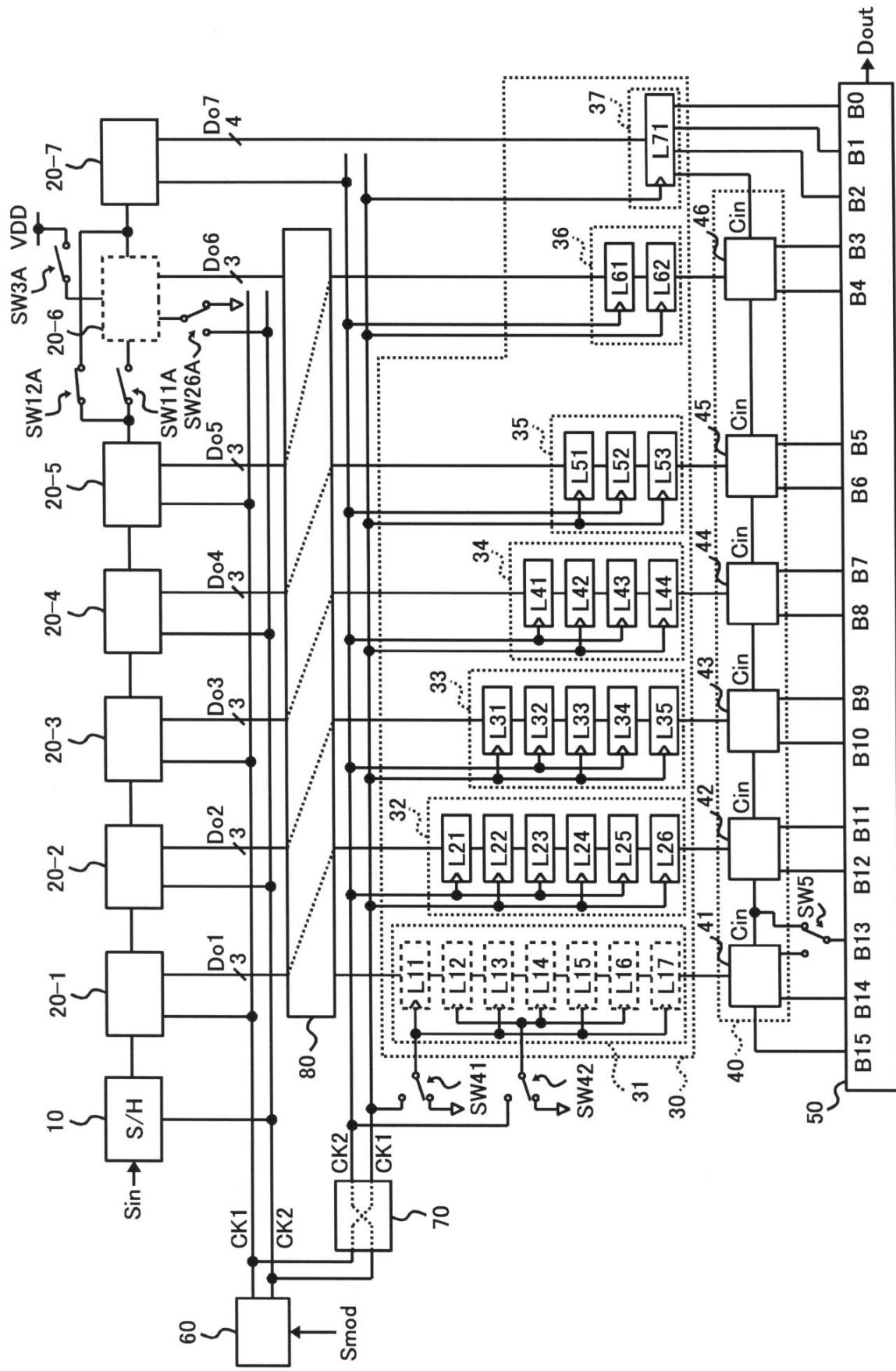

【図4】図1に示すアナログ - デジタル変換回路の省電力モード時の状態を示す図である。

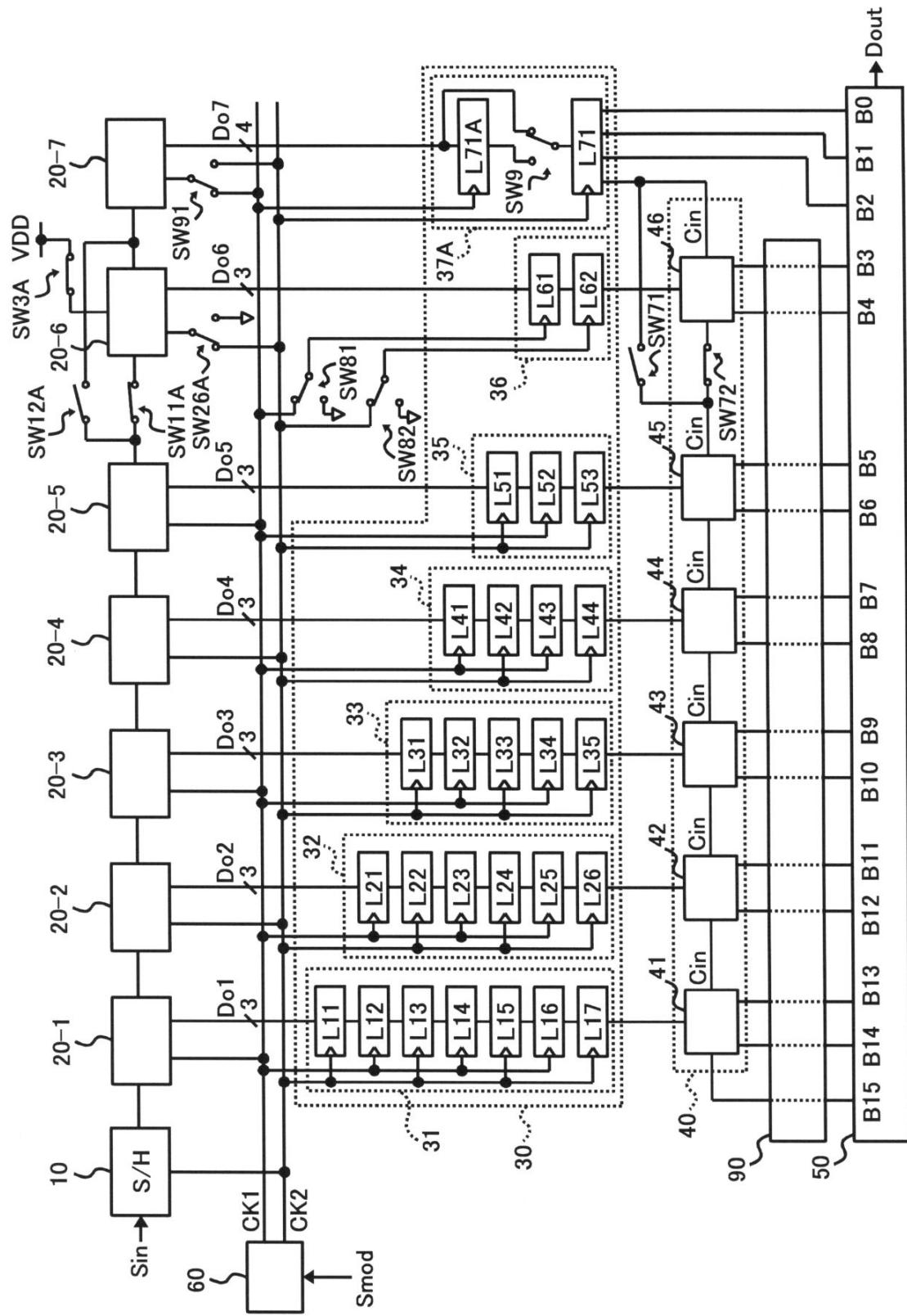

【図5】第2の実施形態に係るアナログ - デジタル変換回路の構成の一例を示す図である。

【図6】図5に示すアナログ - デジタル変換回路の省電力モード時の状態を示す図である。

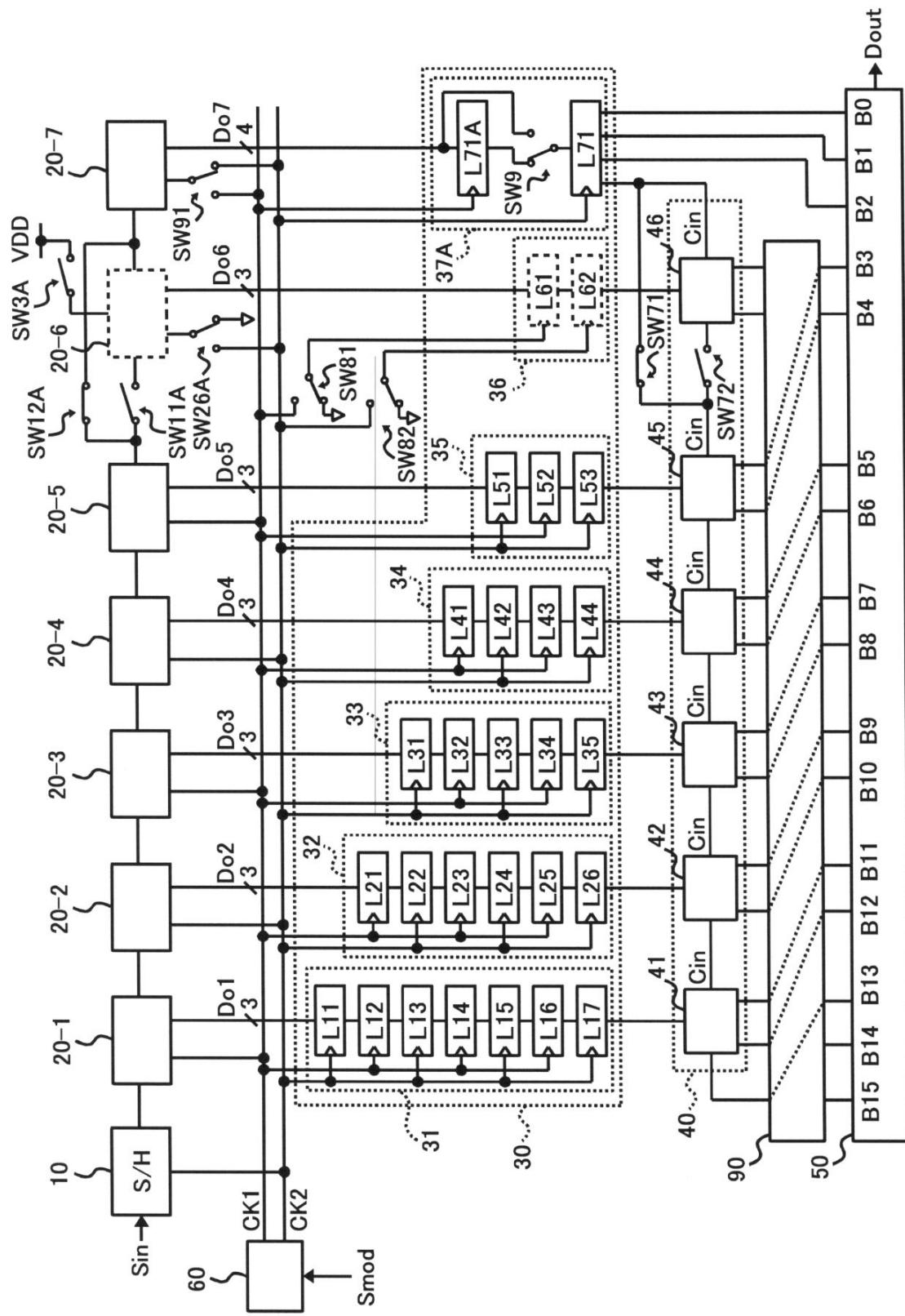

【図7】第3の実施形態に係るアナログ - デジタル変換回路の構成の一例を示す図である。 20

【図8】図7に示すアナログ - デジタル変換回路の省電力モード時の状態を示す図である。

**【発明を実施するための形態】**

**【0023】**

<第1の実施形態>

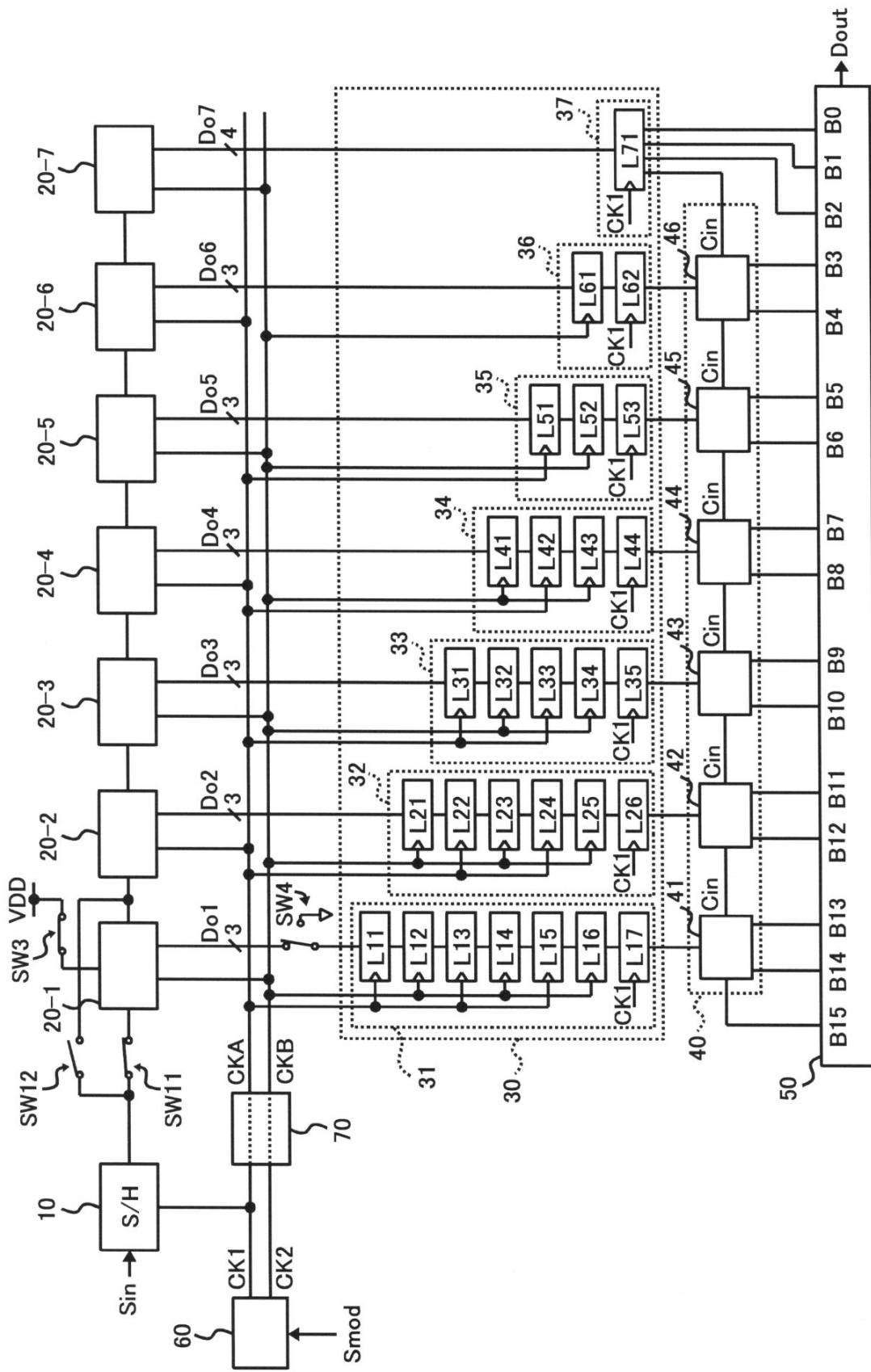

図1は、本発明の第1の実施形態に係るA / Dコンバータの構成の一例を示す図である。図1に示すA / Dコンバータは、サンプルホールド部10と、変換ステージ20 - 1 ~ 20 - 7と、遅延回路31 ~ 37を含んだ遅延部30と、補正回路41 ~ 46を含んだ補正部40と、レジスタ50と、クロック生成部60と、クロック切り替え部70と、スイッチSW11, SW12, SW3, SW4とを有する。 30

**【0024】**

変換ステージ20 - 1 ~ 20 - 6は、本発明における変換ステージの一例である。

スイッチSW3は、本発明における第1の停止制御回路の一例である。

スイッチSW11及びSW12を含む回路は、本発明における第1のバイパス回路の一例である。

クロック切り替え部70は、本発明におけるタイミング制御回路の一例である。

遅延回路31 ~ 36は、本発明における遅延回路の一例である。

補正回路41 ~ 46は、本発明における補正回路の一例である。

スイッチSW4は、本発明における信号入力回路の一例である。 40

クロック生成部60は、本発明におけるクロック生成回路の一例である。

**【0025】**

クロック生成部60は、位相が異なる2つのクロック信号CK1, CK2を生成するとともに、動作モードを示す制御信号Smodに応じてこれらの周波数を変更する。例えば、クロック生成部60は、通常モードにおいてクロック周波数を「fa」に設定し、省電力モードにおいてクロック周波数を「fa」より低い「fb」に設定する。

**【0026】**

サンプルホールド部10は、入力されるアナログの信号Sinのサンプリングと保持をクロック信号CK1に同期して行う。

**【0027】**

変換ステージ 20 - 1 ~ 20 - 7 は、サンプルホールド部 10において保持されたアナログ信号  $S_{in}$  を上位桁から下位桁に向かって順次にデジタル信号  $D_0 1 \sim D_0 7$  に変換する。

#### 【0028】

変換ステージ 20 - 1 は、サンプルホールド部 10 に保持された信号  $S_{in}$  を 3 ビットのデジタル信号  $D_0 1$  に変換し、このデジタル信号  $D_0 1$  に対応するアナログ信号と入力のアナログ信号  $S_{in}$  との差分を増幅して後段（変換ステージ 20 - 2）に出力する。この増幅ゲインは、デジタル信号  $D_0 1$  のビット長「3」に応じて 8（2 の 3 乗）倍に設定される。

変換ステージ 20 - 2 ~ 20 - 6 は、変換ステージ 20 - 1 と同様に、前段からの入力信号を 3 ビットのデジタル信号（ $D_0 2 \sim D_0 6$ ）に変換し、このデジタル信号に対応するアナログ信号と前段からの入力信号との差分を増幅して後段に出力する。10

#### 【0029】

変換ステージ 20 - 7 は、例えばフラッシュ型の A / D コンバータであり、前段（変換ステージ 20 - 6）からの入力信号を 4 ビットのデジタル信号  $D_0 7$  に変換する。

#### 【0030】

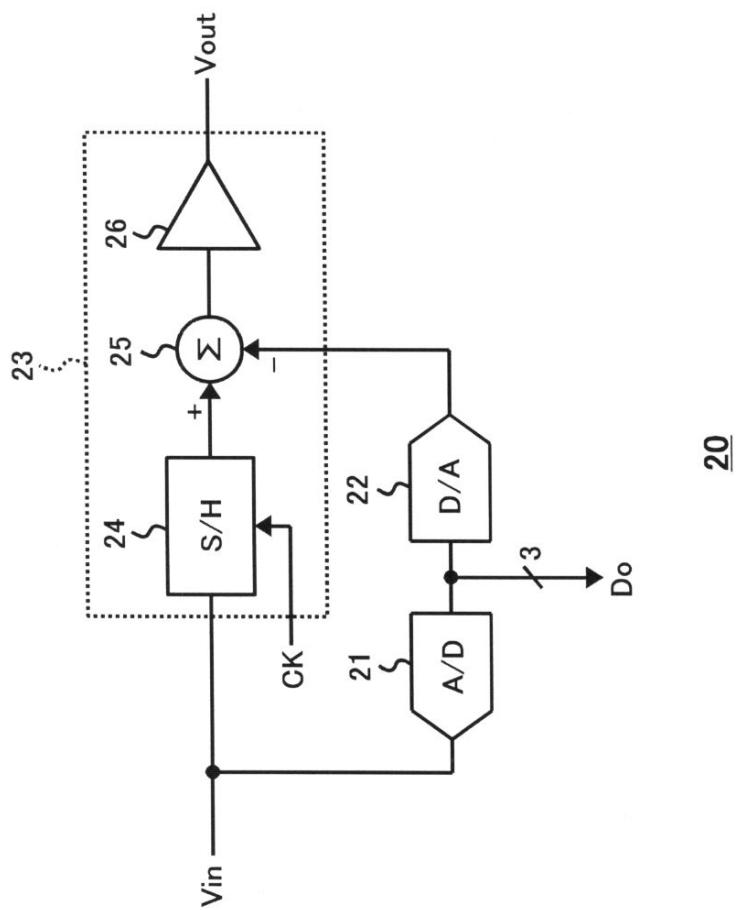

図 2 は、変換ステージ 20 - 1 ~ 20 - 6（以下、変換ステージ 20 - 1 ~ 20 - 6 の任意の 1 つを符号「20」で示す場合がある。）の構成の一例を示す図である。

#### 【0031】

変換ステージ 20 は、例えば図 2 に示すように、アナログ - デジタル変換回路 21 と、デジタル - アナログ変換回路 22 と、増幅回路 23 とを有する。20

アナログ - デジタル変換回路 21 は、入力信号  $V_{in}$  を 3 ビットのデジタル信号  $D_0$ （ $D_0 1 \sim D_0 6$ ）に変換する。

デジタル - アナログ変換回路 22 は、デジタル信号  $D_0$  をアナログ信号に変換する。

増幅回路 23 は、デジタル - アナログ変換回路 22 から出力されるアナログ信号と入力信号  $V_{in}$  との差を 8 倍に増幅し、その増幅結果をアナログ信号  $V_{out}$  として出力する。

#### 【0032】

増幅回路 23 は、例えば図 2 に示すように、サンプルホールド回路 24 と、演算回路 25 と、増幅器 26 を有する。サンプルホールド回路 24 は、クロック信号 CK（CK1 又は CK2）に同期して入力信号  $V_{in}$  のサンプリングと保持を行う。演算回路 25 は、サンプリングホールド回路 24 において保持された入力信号  $V_{in}$  とデジタル - アナログ変換回路 22 の出力信号との差分を生成する。増幅器 26 は、演算回路 25 において生成された差分を 8 倍のゲインで増幅する。30

図 2 におけるサンプルホールド回路 24、演算回路 25 及び増幅器 26 は、それぞれ独立の回路で構成してもよいし、これらの機能が複合されたスイッチトキャパシタなどの回路で構成してもよい。

#### 【0033】

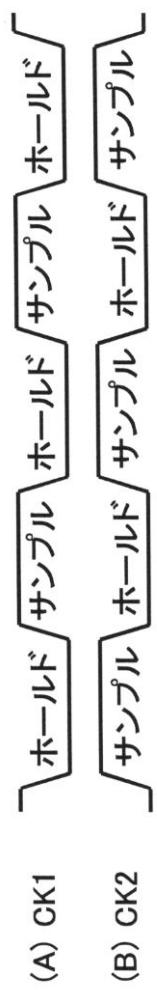

図 3 は、2 つのクロック信号 CK1, CK2（CKA, CKB）のタイミングを示す図である。図 3 に示すように、2 つのクロック信号 CK1, CK2 は位相が 180° ずれている。40

サンプルホールド部 10 は、入力するクロック信号（CK1 又は CK2）がハイレベルのとき入力信号  $S_{in}$  をサンプリングし、クロック信号がローレベルのときサンプリング結果を保持する。

#### 【0034】

図 1 に戻る。

スイッチ SW3 は、省電力モードにおいて初段の変換ステージ 20 - 1 への電源供給を遮断する。スイッチ SW3 は、変換ステージ 20 - 1 への電源供給ラインに設けられており、通常モードにおいてオンし、省電力モードにおいてオフする。

#### 【0035】

スイッチ SW4 は、省電力モードにおいて初段の変換ステージ 20 - 1 から遅延回路 31 へのデジタル信号の供給を停止する。すなわち、スイッチ SW4 は、通常モードにおいて、変換ステージ 20 - 1 から出力されるデジタル信号 D01 を遅延回路 31 に供給し、省電力モードにおいて、遅延回路に対してローレベルの信号（各ビットの値が“0”の信号）を供給する。

#### 【0036】

スイッチ SW11 及び SW12 は、省電力モードにおいてサンプルホールド部 10 の出力信号が初段の変換ステージ 20 - 1 をバイパスして第 2 段目の変換ステージ 20 - 1 に入力されるようにする。

スイッチ SW11 は、サンプルホールド部 10 の出力と変換ステージ 20 - 1 の入力とを接続する経路に設けられており、通常モードにおいてオンし、省電力モードにおいてオフする。スイッチ SW12 は、サンプルホールド部 10 の出力と変換ステージ 20 - 2 の入力とを接続する経路に設けられており、通常モードにおいてオフし、省電力モードにおいてオンする。

#### 【0037】

遅延部 30 は、変換ステージ 20 - 1 ~ 20 - 7 で生成されたデジタル信号 D01 ~ D07 をそれぞれ遅延させる遅延回路 31 ~ 37 を有する。遅延回路 31 ~ 37 は、サンプルホールド部 10 に保持される入力信号 Sin に基づいて変換ステージ 20 - 1 から変換ステージ 20 - 7 に向かって順次に生成される一組のデジタル信号 D01 ~ D07 が共通のタイミングで出力されるように、デジタル信号 D01 ~ D07 にそれぞれ異なる遅延を与える。

#### 【0038】

図 1 の例において、遅延回路 31 はデジタル信号 D01 を 7 段のラッチ回路 L11 ~ L17 により遅延させ、遅延回路 32 はデジタル信号 D02 を 6 段のラッチ回路 L21 ~ L26 により遅延させ、遅延回路 33 はデジタル信号 D03 を 5 段のラッチ回路 L31 ~ L35 により遅延させ、遅延回路 34 はデジタル信号 D04 を 4 段のラッチ回路 L41 ~ L44 により遅延させ、遅延回路 35 はデジタル信号 D05 を 3 段のラッチ回路 L51 ~ L53 により遅延させ、遅延回路 36 はデジタル信号 D06 を 2 段のラッチ回路 L61 ~ L62 により遅延させ、遅延回路 37 はデジタル信号 D07 を 1 段のラッチ回路 L71 により遅延させる。

#### 【0039】

遅延回路 31 ~ 36 において縦続接続されたラッチ回路の奇数段と偶数段には、異なるクロック信号（CKA 又は CKB）が入力される。すなわち、一方のクロック信号が奇数段に共通に入力され、他方のクロック信号が偶数段に共通に入力される。各ラッチ回路は、クロック信号の立ち上がりに同期して入力信号を保持する。尚、図 1 の実施例においては、遅延回路 31 ~ 37 の最終段のラッチ回路（L17, L26, L35, L44, L53, L62, L71）には、常にクロック信号 CK1 が供給される構成となっているが、当該遅延回路の他のラッチ回路と同様に、動作モードに応じてクロック信号 CKA 又は CKB が選択的に供給される構成としてもよい。

クロック信号 CKA と CKB の位相が半周期ずれていることから（図 3）、縦続接続されたラッチ回路をクロック信号の半周期ごとにデジタル信号がシフトする。すなわち、1 段のラッチ回路によって半周期の遅延が生じる。この半周期の遅延が、変換ステージ 20 - 1 ~ 20 - 7 においてデジタル信号 D01 ~ D07 が順次に生成される際の 1 段分の遅延に対応する。

#### 【0040】

また、遅延回路 31 ~ 37 の初段のラッチ回路（L11, L21, L31, L41, L51, L61, L71）は、ラッチすべきデジタル信号（D01 ~ D07）の出力元の変換ステージに対して前段の変換ステージ（又はサンプルホールド部 10）がホールド状態からサンプリング状態へ移行する時に、当該デジタル信号をラッチする。

#### 【0041】

10

20

30

40

50

例えば、3段目の変換ステージ20-3のデジタル信号D<sub>o</sub>3を入力するラッチ回路L31は、変換ステージ20-3に対して前段の変換ステージ20-2がホールド状態からサンプリング状態へ移行するときに、デジタル信号D<sub>o</sub>3をラッチする。通常モードにおいて、変換ステージ20-2はクロック信号CK1(CKA)を入力するため(図1)、ラッチ回路L31はクロック信号CK1(CKA)の立ち上がり(図3(B))に同期してデジタル信号D<sub>o</sub>3をラッチする。

デジタル信号D<sub>o</sub>3は、変換ステージ20-2の出力信号をA/D変換して得られる。その変換ステージ20-2の出力信号は、変換ステージ20-2の増幅部23(図2)においてサンプリング結果を保持しつつ増幅動作を行うことにより得られる。変換ステージ20-2の出力信号は、ホールド状態の終期において比較的安定なレベルとなる。従って、デジタル信号D<sub>o</sub>3は、変換ステージ20-2の出力信号が比較的安定しているホールド状態からサンプル状態への移行時、すなわちクロック信号CK1(CKA)の立ち上がりにおいてラッチ回路L31にラッチされる。

10

#### 【0042】

クロック切り替え部70は、動作モードに応じて、変換ステージ20と遅延部30に供給されるクロック信号CK1, CK2を切り替える。即ち、通常モードにおいては、クロック切り替え部70は、クロック信号CK1をクロック信号CKAとして出し、クロック信号CK2をクロック信号CKBとして出力する。一方、省電力モードにおいては、クロック切り替え部70は、クロック信号CK1をクロック信号CKBとして出し、クロック信号CK2をクロック信号CKAとして出力する。

20

#### 【0043】

具体的には、クロック切り替え部70は、通常モードにおいて、遅延回路32, 34, 36の奇数段(第1段, 第3段, ...)のラッチ回路及び遅延回路31, 33, 35の偶数段(第2段, 第4段, ...)のラッチ回路にクロック信号CK2を入力し、遅延回路32, 34の偶数段のラッチ回路及び遅延回路31, 33, 35の奇数段のラッチ回路にクロック信号CK1を入力する。

一方、クロック切り替え部70は、省電力モードにおいて、遅延回路32, 34, 36の奇数段のラッチ回路及び遅延回路31, 33, 35の偶数段のラッチ回路にクロック信号CK1を入力し、遅延回路32, 34の偶数段のラッチ回路及び遅延回路31, 33, 35の奇数段のラッチ回路にクロック信号CK2を入力する。このとき、各遅延回路31~37の最終段のラッチ回路(L17, L26, L35, L44, L53, L62, L71)には、通常モードと同様に、クロック信号CK1が供給される。

30

クロック切り替え部70がクロック信号CK1, CK2を切り替えることにより、省電力モードにおいて、停止状態の変換ステージ20-1より下位の変換ステージ20-2~20-6における入力信号のサンプリングのタイミングとサンプリング結果の保持のタイミングとが反転される。また、この変換ステージ20-2~20-6におけるタイミングの反転に合わせて、停止状態の変換ステージ20-1より下位の変換ステージ20-2~20-6のデジタル信号D<sub>o</sub>2~D<sub>o</sub>6を保持する遅延回路32~36における信号保持タイミングも変更される。

#### 【0044】

尚、図1に示す実施例においては、バイパスされる変換ステージが1個の奇数であるから、クロック切り替え部70がクロック信号CK1とクロック信号CK2とを切り替えて出力しているが、バイパスされる変換ステージが偶数の場合に、クロック信号CK1とクロック信号CK2とを切り替える必要はない。

40

#### 【0045】

補正部40は、遅延部30によって出力タイミングが揃えられたデジタル信号D<sub>o</sub>1~D<sub>o</sub>6を入力し、それらの補正を行う。補正部40は、入力信号S<sub>in</sub>の変換結果として得られる16ビットのデジタル信号D<sub>out</sub>のうちの上位13ビットを補正する。

#### 【0046】

補正部40は、変換ステージ20-1~20-6において生成されたデジタル信号D<sub>o</sub>

50

1 ~ D o 6 の補正を行う補正回路 4 1 ~ 4 6 を有する。

#### 【 0 0 4 7 】

補正回路 4 6 は、遅延回路 3 7 から出力される 4 ビットのデジタル信号 D o 7 のうちの最上位ビットを桁上がり信号として入力する。

補正回路 4 6 は、入力した桁上がり信号に基づいてデジタル信号 D o 6 を補正し、その補正結果として 3 ビットのデジタル信号を生成する。この補正では、例えば、入力した桁上がり信号と補正対象のデジタル信号 D o 6 とを加算して 3 ビットのデジタル信号を生成する。

補正回路 4 6 は、生成した 3 ビットのデジタル信号における最上位のビットを桁上がり信号として補正回路 4 5 に出力するとともに、下位の 2 ビットをデジタル信号 D o u t の第 4 桁及び第 5 桁のビット信号 B 3 , B 4 としてレジスタ 5 0 に出力する。10

#### 【 0 0 4 8 】

補正回路 4 1 ~ 4 5 は、その補正対象となるデジタル信号 ( D o 1 ~ D o 5 ) と、当該デジタル信号の生成元の変換ステージの下位の変換ステージで生成されたデジタル信号の補正に伴って生じる桁上がり信号とを入力する。

例えば補正回路 4 5 の場合、その補正対象となるデジタル信号 D o 5 の生成元が変換ステージ 2 0 - 5 であり、これに対する下位段が変換ステージ 2 0 - 6 である。変換ステージ 2 0 - 6 で生成されるデジタル信号 D o 6 が補正回路 4 6 において補正され、補正回路 4 5 は、補正回路 4 6 から桁上がり信号を入力する。

そして、補正回路 4 1 ~ 4 5 は、この入力した桁上がり信号に基づいて補正対象のデジタル信号を補正し、その補正結果として 3 ビットのデジタル信号を生成する。この補正では、例えば、下位から入力した桁上がり信号と補正対象のデジタル信号 ( D o 1 ~ D o 5 ) とを加算して 3 ビットのデジタル信号を生成する。20

#### 【 0 0 4 9 】

更に、補正回路 4 1 ~ 4 5 は、上記の補正の結果に応じて発生した桁上がり信号を、補正対象となるデジタル信号 ( D o 1 ~ D o 5 ) の生成元の変換ステージの上位の変換ステージで生成されたデジタル信号の補正用に出力する。

例えば補正回路 4 5 の場合、その補正対象となるデジタル信号 D o 5 の生成元の変換ステージ 2 0 - 5 の上位段が変換ステージ 2 0 - 4 である。この変換ステージ 2 0 - 4 で生成されるデジタル信号 D o 4 が補正回路 4 4 において補正されるので、補正回路 4 5 は、補正回路 4 4 へ桁上がり信号を出力する。30

#### 【 0 0 5 0 】

このとき、補正回路 4 1 ~ 4 5 は、生成した 3 ビットのデジタル信号のうちの最上位ビットを桁上がり信号として上位に出力し、残りの 2 ビットをデジタル信号 D o u t の一部としてレジスタ 5 0 に出力する。

例えば補正回路 4 5 は、生成した 3 ビットのデジタル信号の最上位ビットを桁上がり信号として補正回路 4 4 に出力し、残りの 2 ビットをデジタル信号 D o u t のビット信号 B 5 , B 6 ( 第 6 桁 , 第 7 桁 ) としてレジスタ 5 0 に出力する。

#### 【 0 0 5 1 】

なお、最上位の補正回路 4 1 は、デジタル信号 D o 1 の補正に伴って発生する桁上がり信号を、デジタル信号 D o u t のビット信号 B 1 5 ( 第 1 6 桁 ) としてレジスタ 5 0 に出力する。40

#### 【 0 0 5 2 】

レジスタ 5 0 は、遅延回路 3 7 から出力される 4 ビットのデジタル信号 D o 7 の下位 3 ビットをデジタル信号 D o u t のビット信号 B 0 ~ B 2 ( 第 1 桁 ~ 第 3 桁 ) として入力するとともに、補正部 4 0 から出力される 1 3 ビットの信号をデジタル信号 D o u t のビット信号 B 3 ~ B 1 5 ( 第 4 桁 ~ 第 1 6 桁 ) として入力する。レジスタ 5 0 は、入力したビット信号 B 0 ~ B 1 5 をクロック信号 C K 1 又は C K 2 に同期して保持する。

#### 【 0 0 5 3 】

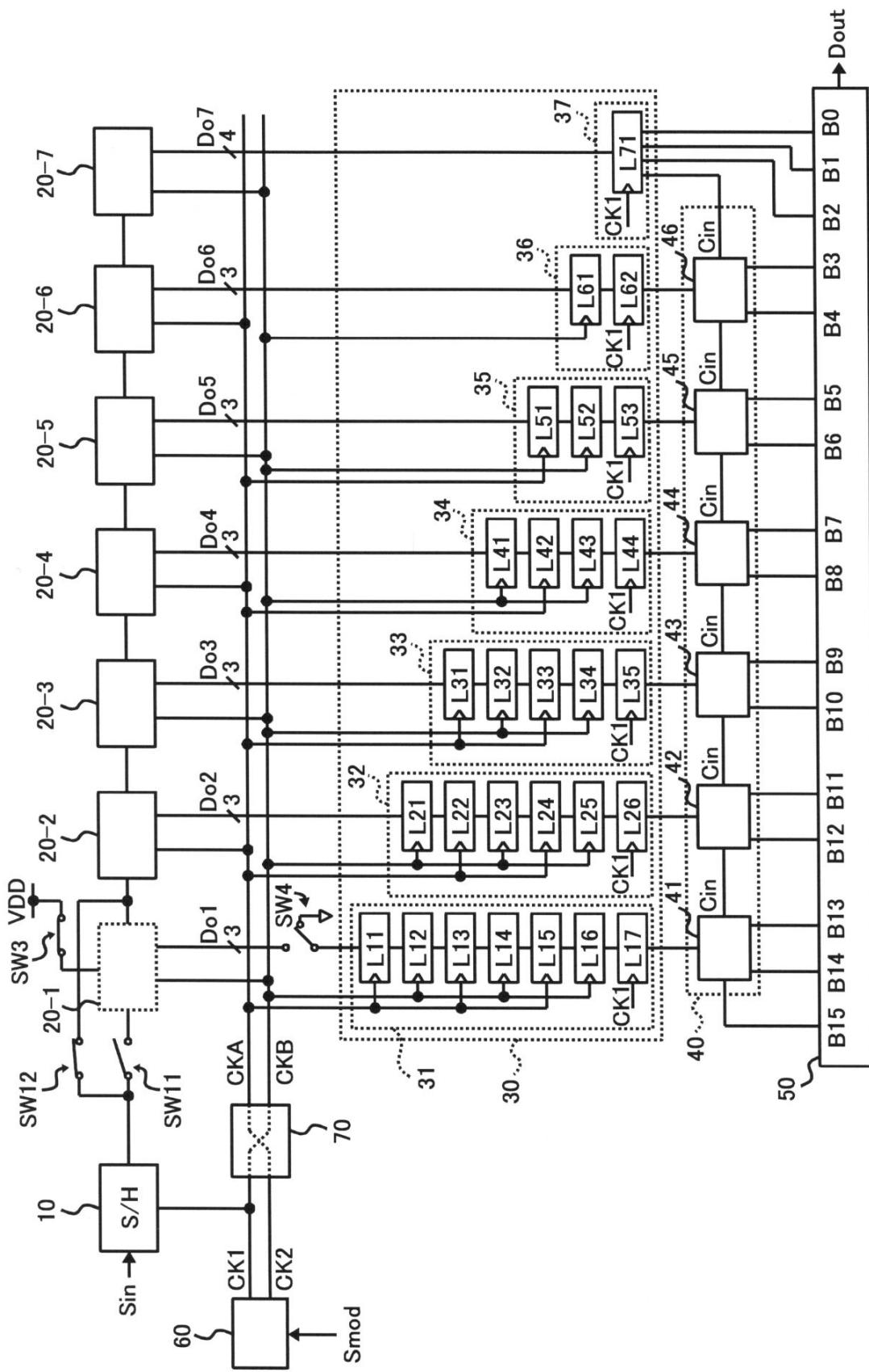

ここで、上述した構成を有する A / D コンバータの動作について、図 1 及び図 4 を参照50

して説明する。図1は通常モード、図4は省電力モードにおけるA/Dコンバータの状態をそれぞれ示す。

#### 【0054】

##### 【通常モード】

通常モードでは、図1に示すように、スイッチSW3を介して変換ステージ20-1に電源が供給されるとともに、サンプルホールド部10の出力信号がスイッチSW11を介して変換ステージ20-1に入力される。これにより、A/Dコンバータは、変換ステージ20-1を初段とする7段の変換ステージ(20-1~20-7)で動作する。

#### 【0055】

また、通常モードにおいては、奇数段の変換ステージ(20-1, 20-3, 20-5)にクロック信号CK2が入力され、偶数段の変換ステージ(20-2, 20-4, 20-6)にクロック信号CK1が入力されるように、クロック切り替え部70が設定される。これにより、奇数段の変換ステージにおいてサンプリング結果が保持されるとき、偶数段の変換ステージにおいて入力信号がサンプリングされ、偶数段の変換ステージにおいてサンプリング結果が保持されるとき、奇数段の変換ステージにおいて入力信号がサンプリングされる。

#### 【0056】

サンプルホールド部10において入力信号Sinのサンプリング結果が保持されるとき、初段の変換ステージ20-1においてその保持された入力信号Sinがサンプリングされる。

20

変換ステージ20-1では、サンプルホールド部10からの入力信号が3ビットのデジタル信号Do1に変換され、更にこのデジタル信号Do1がアナログ信号に変換される。変換ステージ20-1において入力信号のサンプリング結果が保持されるとき、デジタル信号Do1から変換されたアナログ信号が当該サンプリング結果から減算され、その残渣のアナログ信号が増幅されて後段の変換ステージ20-2に出力される。変換ステージ20-1から出力される残渣のアナログ信号は、第2段目の変換ステージ20-2においてサンプリングされる。

以下同様に、第2段~第6段の変換ステージ(20-2~20-6)においてデジタル信号(Do2~Do7)が順次に生成され、増幅された残渣のアナログ信号が順次に後段へ出力される。第6段の変換ステージ20-6から最終的に出力される残渣のアナログ信号は、変換ステージ20-7において4ビットのデジタル信号Do7に変換される。

30

#### 【0057】

サンプルホールド部10でサンプリングされた入力信号Sinに基づいて、クロック信号(CK1, CK2)の半周期ごとに、デジタル信号Do1, Do2, …, Do7の順にデジタル信号が生成される。

#### 【0058】

変換ステージ20-1~20-7において生成されたデジタル信号Do1~Do7は、遅延回路31~37に入力される。

#### 【0059】

サンプルホールド部10及び変換ステージ20-2, 20-4, 20-6がホールド状態にあるとき、これらの後段の変換ステージ(20-1, 20-3, 20-5, 20-7)では、そのホールド状態にある前段(10, 20-2, 20-4, 20-6)からの入力信号に応じてデジタル信号Do1, Do3, Do5, Do7が生成される。前段(10, 20-2, 20-4, 20-6)がホールド状態からサンプル状態へ移行するとき、すなわちクロック信号CK1の立ち上がりにおいて(図3(A))、後段の変換ステージ(20-1, 20-3, 20-5, 20-7)で生成されたデジタル信号Do1, Do3, Do5, Do7が遅延回路31, 33, 35, 37の初段のラッチ回路(L11, L31, L51, L71)にラッチされる。

40

#### 【0060】

他方、変換ステージ20-1, 20-3, 20-5がホールド状態にあるとき、これら

50

の後段の変換ステージ(20-2, 20-4, 20-6)では、そのホールド状態にある前段(20-1, 20-3, 20-5)からの入力信号に応じてデジタル信号D<sub>o</sub>2, D<sub>o</sub>4, D<sub>o</sub>6が生成される。前段(20-1, 20-3, 20-5)がホールド状態からサンプル状態へ移行するとき、すなわちクロック信号CK2の立ち上がりにおいて(図3(B))、後段の変換ステージ(20-2, 20-4, 20-6)で生成されたデジタル信号D<sub>o</sub>2, D<sub>o</sub>4, D<sub>o</sub>6が遅延回路32, 34, 36の初段のラッチ回路(L21, L41, L61)にラッチされる。

#### 【0061】

遅延回路31～37の初段のラッチ回路にラッチされたデジタル信号D<sub>o</sub>1～D<sub>o</sub>7は、クロック信号(CK1, CK2)の半周期ごとに、それぞれ後段のラッチ回路へシフトされる。10

#### 【0062】

クロック信号に従い、D<sub>o</sub>1, D<sub>o</sub>2, …の順でデジタル信号が生成されるとき、先に生成されたデジタル信号は、後に生成される全てのデジタル信号が遅延回路に入力されるまでの間、縦続接続されたラッチ回路においてシフトされ続ける。そして、最後のデジタル信号D<sub>o</sub>7が遅延回路37の初段のラッチ回路L71においてラッチされるとき、それより先に生成された上位のデジタル信号(D<sub>o</sub>1～D<sub>o</sub>6)が各遅延回路の最終段のラッチ回路(L17, L26, L35, L44, L53, L62)において一斉にラッチされる。

#### 【0063】

このようにして、変換ステージ20-1～20-7により順次に生成される7つのデジタル信号D<sub>o</sub>1～D<sub>o</sub>7は、遅延回路31～37から共通のタイミングで出力される。20

#### 【0064】

遅延回路37から出力される4ビットのデジタル信号D<sub>o</sub>7のうち、下位3ビットがビット信号B0～B2としてレジスタ50に出力され、最上位ビットが桁上がり信号として補正回路46に出力される。補正回路46では、下位から入力される桁上がり信号と遅延回路36から入力されるデジタル信号D<sub>o</sub>6とが加算されて3ビットのデジタル信号が生成され、このうち下位2ビットがデジタル信号B3, B4としてレジスタ50に出力されるとともに、最上位ビットが桁上がり信号として補正回路45に出力される。以下同様に、補正回路41～45では、下位からの桁上がり信号と遅延回路(31～35)からのデジタル信号との和として3ビットのデジタル信号が生成され、そのうち下位2ビットがレジスタ50に出力されるとともに、最上位ビットが桁上がり信号として上位の補正回路(補正回路41の場合はレジスタ50)に出力される。30

#### 【0065】

レジスタ50では、遅延回路37から入力される下位3ビット(B0～B2)と補正部40から入力される上位13ビット(B4～B15)がクロック信号CK1又はCK2の立ち上がりに同期してラッチされる。レジスタ50にラッチされた16ビットのデジタル信号D<sub>out</sub>が、入力信号S<sub>in</sub>のデジタル変換結果として出力される。

#### 【0066】

##### [省電力モード]

通常モードから省電力モードへ移行すると、制御信号S<sub>mod</sub>に応じてクロック生成回路60のクロック信号CK1, CK2の周波数が低下する。40

また、図4に示すようにスイッチSW3がオフし、変換ステージ20-1への電源供給が遮断されるため、変換ステージ20-1が停止状態となる。このとき、スイッチSW4が接地電位に接続される、即ち、遅延回路31に入力する信号の各ビットが値“0”(ローレベル)となり、補正回路41に入力される信号も各ビットが値“0”になるため、結果として、ビット信号B15, B14が“0”となる。また、スイッチSW11がオフ、スイッチSW12がオンすることにより、サンプルホールド部10の出力信号が変換ステージ20-1を迂回して変換ステージ20-2に入力される。これにより、A/Dコンバータは、変換ステージ20-2を初段とする6段の変換ステージ(20-2～20-7)50

で動作する。

**【0067】**

省電力モードにおいて、クロック切り替え部70がクロック信号CK1, CK2を入れ替えてクロック信号CKA, CKBとして出力するため、後段の変換ステージ(20-2～20-6)におけるサンプリングとホールドのタイミングが反転する。すなわち、省電力モードでは、偶数段の変換ステージ(20-2, 20-4, 20-6)にクロック信号CK2が入力され、奇数段の変換ステージ(20-1, 20-3, 20-5)にクロック信号CK1が入力されるように、クロック切り替え部70が設定される。

これにより、サンプルホールド部10において入力信号Sinのサンプリング結果を保持して出力するとき、その出力信号が変換ステージ20-2によってサンプリングされる。また、変換ステージ20-2がサンプリング結果に応じて残渣のアナログ信号を出力するとき、その出力信号が変換ステージ20-3によってサンプリングされる。以下同様に、変換ステージ20-3～20-6においてデジタル信号(Do3～Do6)が順次に生成され、変換ステージ20-6から最終的に出力される残渣のアナログ信号が変換ステージ20-7において4ビットのデジタル信号Do7に変換される。10

**【0068】**

変換ステージ20-2～20-7において生成されたデジタル信号Do2～Do7は、遅延回路32～37に入力される。

**【0069】**

遅延回路32～37の各ラッチ回路に入力されるクロック信号は、変換ステージ20-2～20-7におけるサンプリング／ホールドのタイミングの反転に合わせて、クロック切り替え部70により切り替えられる。すなわち、デジタル信号Do2, Do4, Do6がクロック信号CK1の立ち上がりに同期して遅延回路32, 34, 36の初段のラッチ回路(L21, L41, L61)にラッチされ、デジタル信号Do3, Do5, Do7がクロック信号CK2の立ち上がりに同期して遅延回路33, 35, 37の初段のラッチ回路(L31, L51, L71)にラッチされる。20

**【0070】**

遅延回路32～37の初段のラッチ回路にラッチされたデジタル信号Do2～Do7は、クロック信号(CK1, CK2)の半周期ごとに、それぞれ後段のラッチ回路へ順次にシフトされる。30

**【0071】**

クロック信号に従い、Do2, Do3, …の順に生成されるデジタル信号は、各遅延回路においてそれぞれ異なる遅延を与えられ、最終段のラッチ回路(L26, L35, L44, L53, L62, L71)から共通のタイミングで出力される。

**【0072】**

遅延回路32～37から共通のタイミングで出力されるデジタル信号Do2～Do7は、通常モードとほぼ同様に処理される。すなわち、デジタル信号Do7の下位3ビットがビット信号B0～B2としてレジスタ50に出力され、最上位ビットが桁上がり信号として補正回路46に出力される。補正回路42～46では、下位から入力される桁上がり信号と遅延回路から入力されるデジタル信号とが加算されて3ビットのデジタル信号が生成され、このうち下位2ビットがレジスタ50に出力されるとともに、最上位ビットが桁上がり信号として上位の補正回路に出力される。40

**【0073】**

一方、省電力モードでは、変換ステージ20-1からのデジタル信号Do1がローレベルに固定される。

また、デジタル信号Do1の補正を行う補正回路41には、遅延回路31からのローレベル(“0”)の3ビットの出力信号と、補正回路42の桁上がり信号とが入力され、その加算結果がレジスタ50に入力される。補正回路41から出力されるビット信号B13は、補正回路42からの桁上がり信号に応じて、“0”又は“1”となる。

**【0074】**

50

レジスタ50では、遅延回路37から入力される下位3ビット(B0～B2)と補正部40から入力される上位13ビット(B4～B15)がクロック信号CK1又はCK2の立ち上がりに同期してラッチされる。ただし、補正回路41から出力される上位2ビット(B14,B15)を除いた14ビット(B0～B13)が有効なデジタル変換結果として出力される。

#### 【0075】

以上説明したように、本実施形態に係るA/Dコンバータによれば、省電力モードにおいて変換ステージ20-1が停止し、変換ステージ20-1への入力信号が後段の変換ステージ20-2に入力される。これにより、通常モードに比べて変換ステージの段数を減らした状態でアナログ-デジタル変換が行われることから、消費電力を効果的に削減できる。10

#### 【0076】

また、本実施形態に係るA/Dコンバータによれば、省電力モードにおいて最上位の変換ステージが停止される。上位の変換ステージは、下位の変換ステージに比べて高い精度で信号を処理する必要があり、そのため上位の変換ステージほど内部のアナログ回路における消費電流が大きい。従って、最も消費電流の大きい最上位段の変換ステージ10-1を停止させることにより、消費電力をより効果的に削減できる。

#### 【0077】

また、本実施形態に係るA/Dコンバータでは、省電力モードにおけるクロック信号(CK1, CK2)の周波数が通常モードに比べて低くなる。20

クロック信号の周波数が低くなると、変換ステージにおいて要求される動作速度が遅くなることから、より小さい消費電流で必要な精度を満たすことができる。つまり、動作周波数の高い通常モードにおいては上位段で必要とされる精度を満たすことができない下位の変換ステージが、動作周波数の低い省電力モードにおいては上位段での精度を満たすことができるようになる。

従って、本実施形態に係るA/Dコンバータによれば、通常モード時における上位の変換ステージを省電力モードにおいて停止させ、下位の変換ステージを上位の変換ステージにシフトして使用する場合でも、下位の変換ステージの消費電流を通常モード時と同じにしたままで、必要な精度を満たすことができる。

これにより、下位の変換ステージの消費電流を動作モードに応じて変更・調整する必要がないため、回路を簡略化できる。また、省電力モード時の必要な精度を満たすように、下位の変換ステージに余分な消費電流を流す必要がないため、消費電力の削減効果が損なわれずに済む。30

#### 【0078】

なお、省電力モードにおいて、停止状態となる変換ステージ20-1及びデジタル信号D01の遅延回路31に対するクロック信号(CK1, CK2)の供給を停止するように回路を構成してもよい。これにより、一層の省電力を実現できる。

#### 【0079】

また、本実施形態に係るA/Dコンバータでは、奇数段の変換ステージ(20-1, 20-3, 20-5)において入力信号のサンプリングとデジタル信号の出力が行われるとき偶数段の変換ステージ(20-2, 20-4, 20-6)においてサンプリング結果が保持されるとともに当該サンプリング結果に応じた出力信号が生成され、奇数段の変換ステージにおいてサンプリング結果が保持されるとともに当該サンプリング結果に応じた出力信号が生成されるとき偶数段の変換ステージにおいて入力信号のサンプリングとデジタル信号の出力が行われる。40

そして、省電力モードへの移行により変換ステージ20-1が停止する場合、その停止した変換ステージ20-1より下位の変換ステージ(20-2～20-6)における入力信号のサンプリングのタイミングとサンプリング結果の保持のタイミングとがクロック切り替え部70により反転される。

従って、本実施形態に係るA/Dコンバータによれば、省電力モードへの移行により変50

換ステージの段数が変更しても、各変換ステージにおけるサンプリングとホールドのタイミングを適切に設定できる。

#### 【0080】

また、本実施形態に係るA/Dコンバータによれば、変換ステージ20のタイミングの反転に合わせて、遅延部30におけるラッチのタイミングがクロック切り替え部70により反転される。これにより、サンプリングとホールドのタイミングが変更されることによって各変換ステージからのデジタル信号の出力タイミングが変更されても、遅延部30において適切なタイミングでデジタル信号をラッチできる。

#### 【0081】

また、本実施形態に係るA/Dコンバータによれば、第2段目の変換ステージ20-2が省電力モードにおいて実質的に最上位段となった場合に、そのデジタル信号Dout2の補正を行う補正回路42で発生した桁上がり信号が、アナログ-デジタル変換結果(Dout)の最上位ビット(B13)として補正回路41からレジスタ50に出力される。10

通常モードから省電力モードへの移行に伴って上位の補正回路(41)の入力がローレベルに固定されることで、省電力モード時のアナログ-デジタル変換結果(Dout)の上位ビットとなるべき下位の補正回路(42)の桁上がり信号を適切にレジスタ50に入力することができる。

#### 【0082】

<第2の実施形態>

次に、本発明の第2の実施形態について説明する。20

図1に示すA/Dコンバータでは、省電力モードにおいて初段の変換ステージ(20-1)が停止される。これに対し、本実施形態に係るA/Dコンバータでは、省電力モードにおいて初段以外の変換ステージが停止される。

#### 【0083】

図5は、本実施形態に係るA/Dコンバータの構成の一例を示す図である。

図5に示すA/Dコンバータは、サンプルホールド回路10と、変換ステージ20-1～20-7と、遅延回路31～37を含む遅延部30と、補正回路41～46を含む補正部40と、レジスタ50と、クロック生成部60と、クロック切り替え部70と、スイッチSW11A, SW12A, SW3A, SW5, SW26A, SW41, SW42と、信号切り替え部80とを有する。図5に示すA/Dコンバータの各構成要素において、図1に示すA/Dコンバータと同じものについては、同一の符号が与えられている。30

#### 【0084】

スイッチSW3Aは、本発明における第1の停止制御回路の一例である。

スイッチSW11A及びSW12Aを含む回路は、本発明における第1のバイパス回路の一例である。

信号切り替え部80は、本発明における切り替え回路の一例である。

#### 【0085】

図5に示すA/Dコンバータでは、第6段目の変換ステージ20-6が省電力モードにおいて停止される。

スイッチSW3Aは、省電力モードにおいて変換ステージ20-6への電源供給を遮断する。スイッチSW3Aは、変換ステージ20-6への電源供給ラインに設けられており、通常モードにおいてオンし、省電力モードにおいてオフする。40

スイッチSW26Aは、省電力モードにおいて変換ステージ20-6に対するクロック信号の供給を停止する。すなわち、スイッチSW26Aは、変換ステージ20-6に対して、通常モードにおいてクロック信号CK2を入力し、省電力モードにおいてクロック信号CK2の替わりにローレベルの信号を入力する。

スイッチSW11A及びSW12Aは、省電力モードにおいて変換ステージ20-5の出力信号が変換ステージ20-6をバイパスして変換ステージ20-7に入力されるようになる。スイッチSW11Aは、変換ステージ20-5の出力と変換ステージ20-6の入力とを接続する経路に設けられており、通常モードにおいてオンし、省電力モードにお50

いてオフする。スイッチ SW12A は、変換ステージ 20 - 5 の出力と変換ステージ 20 - 7 の入力を接続する経路に設けられており、通常モードにおいてオフし、省電力モードにおいてオンする。

#### 【0086】

信号切り替え部 80 は、省電力モードにおいて、停止状態の変換ステージ 20 - 6 より下位の変換ステージ 20 - 7 のデジタル信号 D07 が遅延部 30 から出力されるタイミングと、停止状態の変換ステージ 20 - 6 より上位の変換ステージ 20 - 1 ~ 20 - 5 のデジタル信号 D01 ~ D05 が遅延部 30 から出力されるタイミングとが一致するように、上位の変換ステージ 20 - 1 ~ 20 - 5 と遅延回路 31 ~ 36 との接続を切り替える。

すなわち、信号切り替え部 80 は、通常モードにおいて変換ステージ 20 - 1 ~ 20 - 6 と遅延回路 31 ~ 36 とを接続し、省電力モードにおいて変換ステージ 20 - 1 ~ 20 - 5 と遅延回路 32 ~ 36 とを接続すると共に、変換ステージ 20 - 6 を遅延部 30 から切り離す。すなわち、省電力モードでは、通常モードと比較して、変換ステージ 20 - 1 ~ 20 - 5 の接続先が下位側に 1 段シフトし、デジタル信号 D01 ~ D05 に与えられる遅延がクロック信号の半周期分だけ短くなる。

#### 【0087】

クロック切り替え部 70 は、信号切り替え部 80 による変換ステージ 20 - 1 ~ 20 - 5 と遅延回路 31 ~ 36 との接続の切り替えに合わせて、各変換ステージから出力されるデジタル信号が適切なタイミングで遅延回路のラッチ回路に保持されるように、遅延回路の各ラッチ回路に入力するクロック信号 (CK1, CK2) を切り替える。通常モードでは、遅延回路 32, 34, 36 の奇数番目のラッチ回路及び遅延回路 31, 33, 35 の偶数番目のラッチ回路にクロック信号 CK1 が供給され、遅延回路 32, 34, 36 の偶数番目のラッチ回路及び遅延回路 31, 33, 35 の奇数番目のラッチ回路にクロック信号 CK2 が供給される。一方、省電力モードにおいては、クロック信号 CK1, CK2 の供給先が通常モードと反対になると共に、スイッチ SW41, SW42 により、遅延回路 31 へのクロック信号 CK1, CK2 の供給が停止される。

また、クロック切り替え部 70 は、通常モードにおいて変換回路 20 - 7 にクロック信号 CK1 を供給し、省電力モードにおいて変換回路 20 - 7 にクロック信号 CK2 を供給する。

#### 【0088】

ここで、上述した構成を有する A / D コンバータの動作について、図 5 及び図 6 を参照して説明する。図 5 は通常モード、図 6 は省電力モードにおける A / D コンバータの状態をそれぞれ示す。

#### 【0089】

##### [通常モード]

通常モードでは、図 5 に示すように、スイッチ SW3A を介して変換ステージ 20 - 6 に電源が供給されるとともに、スイッチ SW26A を介して変換ステージ 20 - 6 にクロック信号 CK2 が入力され、変換ステージ 20 - 5 の出力信号がスイッチ SW11A を介して変換ステージ 20 - 6 に入力される。これにより、A / D コンバータは 7 段の変換ステージ (20 - 1 ~ 20 - 7) で動作する。

また、通常モードにおいては、上位の変換ステージ 20 - 1 ~ 20 - 6 において生成されるデジタル信号 D01 ~ D06 が遅延回路 31 ~ 36 に入力される。

これにより、図 5 に示す A / D コンバータは、通常モードにおいて図 1 に示す A / D コンバータと同様な接続状態となり、これと同様な動作によってアナログ - デジタル変換結果 (Dout) を出力する。

#### 【0090】

##### [省電力モード]

省電力モードでは、図 6 に示すようにスイッチ SW3A がオフし、変換ステージ 20 - 6 への電源供給が遮断されるため、変換ステージ 20 - 6 が停止状態となる。このとき、停止状態の変換ステージ 20 - 6 には、クロック信号 CK2 の替わりとしてローレベルレ

10

20

30

40

50

ベルの信号がスイッチ SW26A を介して入力される。また、スイッチ SW11A がオフ、スイッチ SW12A がオンすることにより、変換ステージ 20 - 5 の出力信号が変換ステージ 20 - 6 を迂回して変換ステージ 20 - 7 に入力される。これにより、A/D コンバータは 6 段の変換ステージ (20 - 1 ~ 20 - 5, 20 - 7) で動作する。

#### 【0091】

また省電力モードでは、変換ステージ 20 - 1 ~ 20 - 5 で生成されるデジタル信号 D<sub>01</sub> ~ D<sub>05</sub> の入力先が遅延回路 32 ~ 36 に変更され、デジタル信号 D<sub>01</sub> ~ D<sub>05</sub> に遅延を与えるラッチ回路の段数がそれぞれ 1 段ずつ少なくなる。これにより、D<sub>01</sub>, …, D<sub>05</sub>, D<sub>07</sub> の順にデジタル信号が生成され、最後のデジタル信号 D<sub>07</sub> が遅延回路 37 のラッチ回路 L71 においてラッチされるとき、上位のデジタル信号 D<sub>01</sub> ~ D<sub>06</sub> 10 も遅延回路 32 ~ 36 の最終段のラッチ回路 (L26, L35, L44, L53, L62) に同一のタイミングでラッチされる。

#### 【0092】

更に、省電力モードへの移行により、遅延回路 32 ~ 37 におけるデジタル信号のラッチのタイミングが変更することに合わせて、遅延回路 32 ~ 37 の各ラッチ回路に入力されるクロック信号がクロック切り替え部 70 により変更される。

すなわち、通常モードにおいて、ラッチ回路 L11, L31, L51, L71 にはクロック信号 CK2 のホールド期間に生成されるデジタル信号 D<sub>01</sub>, D<sub>03</sub>, D<sub>05</sub>, D<sub>07</sub> が入力されるためクロック信号 CK2 が供給され、ラッチ回路 L21, L41, L61 20 にはクロック信号 CK1 のホールド期間に生成されるデジタル信号 D<sub>02</sub>, D<sub>04</sub>, D<sub>06</sub> が入力されるためクロック信号 CK1 が供給される。

一方、省電力モードにおいて、ラッチ回路 L31, L51, L71 にはクロック信号 CK1 のホールド期間に生成されるデジタル信号 D<sub>02</sub>, D<sub>04</sub>, D<sub>07</sub> が入力されるためクロック信号 CK1 が供給され、ラッチ回路 L21, L41, L61 にはクロック信号 CK2 のホールド期間に生成されるデジタル信号 D<sub>01</sub>, D<sub>03</sub>, D<sub>05</sub> が入力されるためクロック信号 CK2 が供給される。

#### 【0093】

遅延部 37 から出力されるデジタル信号 D<sub>01</sub> ~ D<sub>05</sub>, D<sub>07</sub> の処理については、図 1 に示す A/D コンバータの省電力モード時の処理と同様である。すなわち、デジタル信号 D<sub>07</sub> の下位 3 ビットがビット信号 B<sub>0</sub> ~ B<sub>3</sub> としてレジスタ 50 に出力され、最上位ビットが補正部 40 に入力される。補正部 40 において、下位からの桁上がり信号に応じて各デジタル信号 (D<sub>01</sub> ~ D<sub>05</sub>) が補正されることにより、ビット信号 B<sub>4</sub> ~ B<sub>13</sub> 30 が生成され、レジスタ 50 に出力される。レジスタ 50 には 16 ビットのデータ (B<sub>0</sub> ~ B<sub>15</sub>) がラッチされるが、このうち上位 2 ビットを除いた 14 ビット (B<sub>0</sub> ~ B<sub>13</sub>) が有効なデジタルデータ D<sub>out</sub> として出力される。尚、補正回路 42 の桁上がり信号は、スイッチ SW5 を介して、ビット信号 B<sub>13</sub> としてレジスタ 50 に出力される。

#### 【0094】

以上説明したように、本実施形態に係る A/D コンバータにおいても、省電力モードにおいて変換ステージの段数を減らすことにより、消費電力を効果的に削減できる。また、省電力モードにおいて使用されない遅延回路 31 へのクロック信号 (CK1, CK2) の供給が停止されるため、無駄な電力損失を低減できる。

#### 【0095】

##### <第 3 の実施形態>

次に、本発明の第 3 の実施形態について説明する。

#### 【0096】

図 7 は、本実施形態に係る A/D コンバータの構成の一例を示す図である。

図 7 に示す A/D コンバータは、図 5 に示す A/D コンバータにおけるスイッチ SW4 1, SW42、クロック切り替え部 70 及び信号切り替え部 80 を削除し、これらの替わりにスイッチ SW71, SW72, SW81, SW82, SW91 及び信号切り替え部 90 を新たに設け、更に、遅延回路 37 を遅延回路 37A に置き換えたものである。図 7 に 50

示すA/Dコンバータの他の構成要素は、図5に示すA/Dコンバータと同じである。

**【0097】**

スイッチSW81及びSW82を含む回路は、本発明における第2の停止制御回路の一例である。

スイッチSW71及びSW72を含む回路は、本発明における第2のバイパス回路の一例である。

**【0098】**

遅延回路37Aは、省電力モードにおいて変換ステージ30-6が停止状態になった場合に、変換ステージ30-6より上位の変換ステージ20-1～20-5において順次に生成されるデジタル信号D01～D05と、変換ステージ30-6より下位の変換ステージ20-7においてデジタル信号D06に続けて生成されるデジタル信号D07とが遅延部30から共通のタイミングで出力されるように、遅延回路37Aにおけるラッチ回路の段数を1つ増やす。

**【0099】**

遅延回路37Aは、例えば図7に示すように、ラッチ回路L71及びL71AとスイッチSW9を有する。

ラッチ回路L71Aは、クロック信号CK1の立ち上がりに同期してデジタル信号D07をラッチする。スイッチSW9は、通常モードにおいてデジタル信号D07（変換ステージ20-7の出力信号）を選択し、省電力モードにおいてラッチ回路L71Aの出力信号を選択する。ラッチ回路L71は、クロック信号CK2の立ち上がりに同期して、スイッチSW9により選択された信号をラッチする。

**【0100】**

スイッチSW81, SW82は、省電力モードにおいて遅延回路36のラッチ回路L61, L62に対するクロック信号(CK1, CK2)の供給を停止する。スイッチSW81は、ラッチ回路L61に対して、通常モードにおいてクロック信号CK1を入力し、省電力モードにおいてクロック信号CK1の替わりにローレベルの信号を入力する。スイッチSW82は、ラッチ回路L62に対して、通常モードにおいてクロック信号CK2を入力し、省電力モードにおいてクロック信号CK2の替わりにローレベルの信号を入力する。

**【0101】**

スイッチSW71及びSW72は、省電力モードにおいて、補正対象のデジタル信号D06の生成が停止される補正回路46を迂回して、下位からの桁上がり信号を補正回路45に入力する。

すなわち、スイッチSW71及びSW72は、補正回路46からの桁上がり信号又はラッチ回路L71の最上位ビットの何れか一方を選択し、補正回路45へ桁上がり信号として入力する。

スイッチSW71は、補正回路46の桁上がり信号の入力と補正回路45の桁上がり信号の入力とを接続する経路に設けられており、通常モードにおいてオフし、省電力モードにおいてオンする。

スイッチSW72は、補正回路46の桁上がり信号の出力と補正回路45の桁上がり信号の入力とを接続する経路に設けられており、通常モードにおいてオンし、省電力モードにおいてオフする。

**【0102】**

信号切り替え部90は、補正部40の出力とレジスタ50の入力との接続を動作モードに応じて切り替える。すなわち、信号切り替え部80は、通常モードにおいて、補正部40の13ビットの出力信号をビット信号B3～B15としてレジスタ50に入力し、省電力モードにおいて、補正部40の上位11ビットの出力信号をビット信号B3～B13としてレジスタ50に入力する。このとき、信号切り替え回路90は、レジスタ50のビット信号B15, B14に対してローレベル（値“0”）の信号を出力する。

**【0103】**

10

20

30

40

50

ここで、上述した構成を有するA / Dコンバータの動作について、図7及び図8を参照して説明する。図7は通常モード、図8は省電力モードにおけるA / Dコンバータの状態をそれぞれ示す。

#### 【0104】

##### [通常モード]

通常モードにおいては、図7に示すように、スイッチSW3A及びSW11Aがオン、スイッチSW12Aがオフし、スイッチSW26Aを介して変換ステージ20-6にクロック信号CK2が供給されるため、A / Dコンバータは7段の変換ステージ20-1~20-7で動作する。

#### 【0105】

また、通常モードにおいて、ラッチ回路L71の入力がスイッチSW9を介して変換ステージ20-7の出力に接続され、スイッチSW91を介して変換ステージ20-7にクロック信号CK1が供給されるため、デジタル信号D07は1段のラッチ回路により遅延される。

一方、遅延回路36の各ラッチ回路(L61, L62)にはスイッチSW81, SW82を介してクロック信号CK1, CK2が入力されるため、デジタル信号D06は2段のラッチ回路により遅延される。

#### 【0106】

更に、通常モードにおいては、スイッチSW72がオン、スイッチSW71がオフするため、補正回路45には補正回路46で発生した桁上がり信号が入力される。補正部40の各補正回路から出力される13ビットの信号は、ビット信号B3~B15としてレジスタ50に出力される。

#### 【0107】

このように、図7に示すA / Dコンバータは、通常モードにおいて図1, 図5に示すA / Dコンバータと同様な接続状態となり、これらと同様な動作によってアナログ - デジタル変換結果(Dout)を出力する。

#### 【0108】

##### [省電力モード]

省電力モードでは、第2の実施形態(図6)と同様に変換ステージ20-6が停止し、A / Dコンバータは6段の変換ステージ(20-1~20-5, 20-7)で動作する。変換ステージ20-6が停止すると、スイッチSW81, SW82によって遅延回路36へのクロック信号(CK1, CK2)の供給が停止される。スイッチSW26Aが切り替わり、変換ステージ20-6へのクロック信号CK2の供給が停止されると共に、スイッチSW91が切り替わり、変換ステージ20-7に対してクロック信号CK2が供給される。

#### 【0109】

また、このとき、変換ステージ20-5の出力信号が変換ステージ20-6を迂回して変換ステージ20-7に入力されるため、デジタル信号D07の生成タイミングが通常モード時と比較してクロック信号の半周期だけ早くなる。デジタル信号D07の生成タイミングが早くなる一方で、遅延回路31~35がデジタル信号D01~D05に与える遅延は通常モードと同じであることから、遅延回路37の遅延が通常モードと同じ場合、デジタル信号D07だけが他のデジタル信号(D01~D05)より早く遅延部30において出力されてしまう。

#### 【0110】

そこで、省電力モードでは、遅延回路37Aのラッチ回路の段数が2段に増加する。すなわち、デジタル信号D07が2段のラッチ回路L71A及びL71によって遅延される。これにより、デジタル信号D07の遅延がクロック信号の半周期だけ長くなるので、デジタル信号D01~D05とデジタル信号D07の出力タイミングが一致する。

#### 【0111】

また、省電力モードでは、変換ステージ20-6が停止するため、補正回路46における

10

20

30

40

50

るデジタル信号 D<sub>0</sub> 6 の補正動作が無効になる。そのため、補正回路 4 5 には、補正回路 4 6 において発生する桁上がり信号の替わりに、補正回路 4 6 へ入力される桁上がり信号（デジタル信号 D<sub>0</sub> 7 の最上位ビット）が入力される。この他、補正回路 4 1 ~ 4 5 の動作は通常モードと同じである。

#### 【 0 1 1 2 】

補正回路 4 6 の出力が無効になることから、補正回路 4 1 ~ 4 5 による 11 ビットの出力は下位側に 2 ビット分シフトされ、ビット信号 B<sub>3</sub> ~ B<sub>13</sub> としてレジスタ 5 0 に出力される。レジスタ 5 0 には 16 ビットのデータ（B<sub>0</sub> ~ B<sub>15</sub>）がラッピングされ、このうち上位 2 ビットを除いた 14 ビット（B<sub>0</sub> ~ B<sub>13</sub>）が有効なデジタルデータ D<sub>out</sub> として出力される。

10

#### 【 0 1 1 3 】

以上説明したように、本実施形態に係る A / D コンバータにおいても、省電力モードにおいて変換ステージの段数を減らすことにより、消費電力を効果的に削減できる。また、省電力モードにおいて使用されない遅延回路 3 6 へのクロック信号（CK1, CK2）の供給が停止されるため、無駄な電力損失を低減できる。

#### 【 0 1 1 4 】

なお、本発明は上述した実施形態のみに限定されるものではなく、更に種々のバリエーションを含んでいる。

#### 【 0 1 1 5 】

第 1 の実施形態では初段の変換ステージのみ停止されるが、本発明はこれに限定されない。例えば、初段を含む一連の複数の変換ステージを停止してもよい。上位の変換ステージを複数停止させることで、より効果的に消費電力を低減できる。

20

#### 【 0 1 1 6 】

また第 2、第 3 の実施形態では、中間の 1 段の変換ステージを停止する例を挙げているが、本発明はこれに限定されない。例えば、中間の複数段の変換ステージ、初段及び中間の変換ステージを停止してもよい。複数の変換ステージを停止する場合、これらは連続していてもよいし、連続していないなくてもよい。

#### 【 0 1 1 7 】

上述の実施形態では、省電力モードにおいて変換ステージに対する電源の供給を遮断しているが、本発明はこれに限定されない。即ち、上述の実施形態では、変換ステージ 2 0 - 1 を停止させる際に電源電圧 V<sub>DD</sub> の供給を停止しているが、この電源電圧 V<sub>DD</sub> の停止の代わりに、クロック信号 CKB (CK2) の供給を停止するようにスイッチ等の回路を設けてもよい。更には、電源電圧 V<sub>DD</sub> とクロック信号 CKB の双方の供給を停止する回路を設けてもよい。

30

#### 【 0 1 1 8 】

本発明の他の実施形態では、省電力モードにおいて変換ステージが停止状態にある場合に、そのデジタル信号を入力する遅延回路へのクロック信号の供給を停止したり、遅延回路への電源供給を遮断する回路を設けたりすることによって、消費電力の削減を図ってもよい。また、クロック信号の供給は、必ずしも停止される必要はない。

#### 【 0 1 1 9 】

40

本発明においては、各変換ステージが生成するデジタル信号のビット数や、変換ステージの段数などは任意でよい。

#### 【 符号の説明 】

#### 【 0 1 2 0 】

1 0 ...サンプルホールド部、2 0 , 2 0 - 1 ~ 2 0 - 7 ...変換ステージ、3 0 ...遅延部、3 1 ~ 3 7 , 3 7 A ...遅延回路、4 0 ...補正部、4 1 ~ 4 6 ...補正回路、5 0 ...レジスタ、6 0 ...クロック生成部、7 0 ...クロック切り替え部、8 0 , 9 0 ...信号切り替え部、SW1 1 , SW1 1 A , SW1 2 , SW1 2 A , SW2 6 A , SW3 , SW3 A , SW4 , SW4 1 , SW4 2 , SW5 , SW7 1 , SW7 2 , SW8 1 , SW8 2 , SW9 1 ...スイッチ、L1 1 ~ L1 7 , L2 1 ~ L2 6 , L3 1 ~ L3 5 , L4 1 ~ L4 4 , L5 1

50

~ L 5 3 , L 6 1 ~ L 6 2 , L 7 1 , L 7 1 A ... ラッチ回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(56)参考文献 特開平05-252121(JP,A)

特開2004-214905(JP,A)

特開2003-174364(JP,A)

特開2005-260449(JP,A)

特開2001-177408(JP,A)

特開2006-222548(JP,A)

特開2006-033304(JP,A)

特表2003-523679(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03M 1/00 - 1/88