(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4845357号

(P4845357)

(45) 発行日 平成23年12月28日(2011.12.28)

(24) 登録日 平成23年10月21日(2011.10.21)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 21/331  | (2006.01) | HO1L 29/72 | Z    |

| HO1L 29/73   | (2006.01) | HO1L 27/06 | 321E |

| HO1L 21/8249 | (2006.01) | HO1L 27/06 | 101U |

| HO1L 27/06   | (2006.01) | HO1L 27/08 | 331E |

| HO1L 21/8248 | (2006.01) |            |      |

請求項の数 6 (全 12 頁) 最終頁に続く

(21) 出願番号

特願2004-246374 (P2004-246374)

(22) 出願日

平成16年8月26日 (2004.8.26)

(65) 公開番号

特開2006-66577 (P2006-66577A)

(43) 公開日

平成18年3月9日 (2006.3.9)

審査請求日

平成18年11月24日 (2006.11.24)

(73) 特許権者

308033711

ラピスセミコンダクタ株式会社

東京都八王子市東浅川町550番地1

(74) 代理人

100085419

弁理士 大垣 孝

(74) 代理人

100141955

弁理士 岡田 宏之

(72) 発明者

藤巻 浩和

東京都港区虎ノ門1丁目7番12号 沖電

気工業株式会社内

審査官 小森 重樹

最終頁に続く

(54) 【発明の名称】半導体装置とその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

支持基板上に、第1埋め込み酸化膜、第1単結晶シリコン層、第2埋め込み酸化膜、及び第2単結晶シリコン層が順に積層された2重SOI基板を用意する工程と、

前記2重SOI基板のバイポーラトランジスタ被形成領域を画成する領域に対して、前記第2単結晶シリコン層の表面から前記第1埋め込み酸化膜の表面が露出する深さにまでエッティングを行って、ディープトレンチを形成する工程と、

前記2重SOI基板上に、シリコン窒化膜及びシリコン酸化膜を順に積層して、前記ディープトレンチを埋め込む工程と、

前記バイポーラトランジスタ被形成領域に、前記第2埋め込み酸化膜の表面が露出する深さにまでエッティングを行って開口部を設ける工程と、

前記バイポーラトランジスタ被形成領域内の前記第2埋め込み酸化膜を、ウェットエッチングにより除去して空孔部を設ける工程と、

前記開口部及び前記空孔部に、バイポーラトランジスタのコレクタとなる、第1導電型不純物が高濃度にドープされた多結晶シリコン層を堆積する工程と、

前記第2単結晶シリコン層と電気的に接続されるベース電極を形成する工程と、

前記バイポーラトランジスタ被形成領域の前記第2単結晶シリコン層上に、エピタキシャル成長シリコン層を形成し、前記第2単結晶シリコン層の前記エピタキシャル成長シリコン層と接する部分に第2導電型導電層を形成する工程と、

前記エピタキシャル成長シリコン層と、該エピタキシャル成長シリコン層と接する、前

10

20

記第2導電型導電層の一部分にエミッタを形成するとともに、前記第2導電型導電層の他の部分にベースを形成する工程と、

前記ベース電極と前記第2単結晶シリコン層を介して電気的に接続されるエミッタ電極を形成する工程と

を備えることを特徴とする半導体装置の製造方法。

【請求項2】

支持基板上に、第1埋め込み酸化膜、第1単結晶シリコン層、第2埋め込み酸化膜、及び第2単結晶シリコン層が順に積層された2重SOI基板を用意する工程と、

前記2重SOI基板のバイポーラトランジスタ被形成領域を画成する領域に対して、前記第2単結晶シリコン層の表面から前記第1埋め込み酸化膜の表面が露出する深さにまでエッチングを行って、ディープトレンチを形成する工程と、10

前記2重SOI基板上に、シリコン窒化膜及びシリコン酸化膜を順に積層して、前記ディープトレンチを埋め込む工程と、

前記バイポーラトランジスタ被形成領域に、前記第2埋め込み酸化膜の表面が露出する深さにまでエッチングを行って開口部を設ける工程と、

前記バイポーラトランジスタ被形成領域内の前記第2埋め込み酸化膜を、ウェットエッチングにより除去して空孔部を設ける工程と、

前記空孔部を、バイポーラトランジスタのコレクタとなる、第1導電型不純物が高濃度にドープされた多結晶シリコン層で埋め込む工程と、

前記開口部をメタルで埋め込む工程と、20

前記第2単結晶シリコン層と電気的に接続されるベース電極を形成する工程と、

前記バイポーラトランジスタ被形成領域の前記第2単結晶シリコン層上に、エピタキシャル成長シリコン層を形成し、前記第2単結晶シリコン層の前記エピタキシャル成長シリコン層と接する部分に第2導電型導電層を形成する工程と、

前記エピタキシャル成長シリコン層と、該エピタキシャル成長シリコン層と接する、前記第2導電型導電層の一部分にエミッタを形成するとともに、前記第2導電型導電層の他の部分にベースを形成する工程と、

前記ベース電極と前記第2単結晶シリコン層を介して電気的に接続されるエミッタ電極を形成する工程と

を備えることを特徴とする半導体装置の製造方法。30

【請求項3】

さらに、

前記第2単結晶シリコン層の、前記バイポーラトランジスタ被形成領域及び前記ディープトレンチが形成された領域以外の領域に、MOSFET被形成領域を画成する素子分離酸化膜を形成する工程と、

前記MOSFET被形成領域にMOSFETを形成する工程と

を備えることを特徴とする請求項1又は2に記載の半導体装置の製造方法。

【請求項4】

支持基板上に、第1埋め込み酸化膜、第1単結晶シリコン層、第2埋め込み酸化膜、第2単結晶シリコン層を順に積層して構成される2重SOI基板に形成されていて、前記第1埋め込み酸化膜に達するディープトレンチで画成されたバイポーラトランジスタ被形成領域に形成されたバイポーラトランジスタを備える半導体装置であって、40

前記バイポーラトランジスタは、

前記バイポーラトランジスタ被形成領域の、前記第1単結晶シリコン層及び前記第2単結晶シリコン層の間を埋め込むように、かつ、前記第2単結晶シリコン層を貫通するよう形成された、前記バイポーラトランジスタのコレクタとなる、第1導電型不純物が高濃度にドープされた多結晶シリコン層と、

前記バイポーラトランジスタ被形成領域の前記第2単結晶シリコン層上に形成されたエピタキシャル成長シリコン層と、

前記第2単結晶シリコン層の前記エピタキシャル成長シリコン層と接する部分に形成さ50

れた第2導電型導電層と、

前記エピタキシャル成長シリコン層と、該エピタキシャル成長シリコン層と接する、前記第2導電型導電層の一部分に形成されたエミッタと、

前記第2導電型導電層の他の部分に形成されたベースと

を備えることを特徴とする半導体装置。

【請求項5】

支持基板上に、第1埋め込み酸化膜、第1単結晶シリコン層、第2埋め込み酸化膜、第2単結晶シリコン層を順に積層して構成される2重SOI基板に形成されていて、前記第1埋め込み酸化膜に達するディープトレンチで画成されたバイポーラトランジスタ被形成領域に形成されたバイポーラトランジスタを備える半導体装置であって、

10

前記バイポーラトランジスタは、

前記バイポーラトランジスタ被形成領域の、前記第1単結晶シリコン層及び前記第2単結晶シリコン層の間を埋め込むように形成された、第1導電型不純物が高濃度にドープされた多結晶シリコン層と、

前記第2単結晶シリコン層を貫通するように、前記多結晶シリコン層と電気的に接続するように形成されたメタルと、

前記バイポーラトランジスタ被形成領域の前記第2単結晶シリコン層上に形成されたエピタキシャル成長シリコン層と、

前記第2単結晶シリコン層の前記エピタキシャル成長シリコン層と接する部分に形成された第2導電型導電層と、

20

前記エピタキシャル成長シリコン層と、該エピタキシャル成長シリコン層と接する、前記第2導電型導電層の一部分に形成されたエミッタと、

前記第2導電型導電層の他の部分に形成されたベースと

を備えることを特徴とする半導体装置。

【請求項6】

前記ディープトレンチが形成された領域、及び、前記ディープトレンチで画成された領域以外の前記第2単結晶シリコン層の領域部分に形成された素子分離酸化膜と、

前記素子分離酸化膜で画成された領域に形成されたMOSFETと

を備えることを特徴とする請求項4又は5に記載の半導体装置。

30

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、半導体装置とその製造方法に関するものである。

【背景技術】

【0002】

バイポーラトランジスタは、MOSFETに比べて、高速動作が可能であり、高い電流駆動能力を有している。従って、光伝送用のレーザ駆動用LSIや携帯電話用パワーアンプでの使用に適している。このバイポーラトランジスタを高集積度に優れるMOSFETと同一のチップ内に実現することにより、MOSFETによるLSIでは、実現不可能であった性能を得ることが可能となる。

40

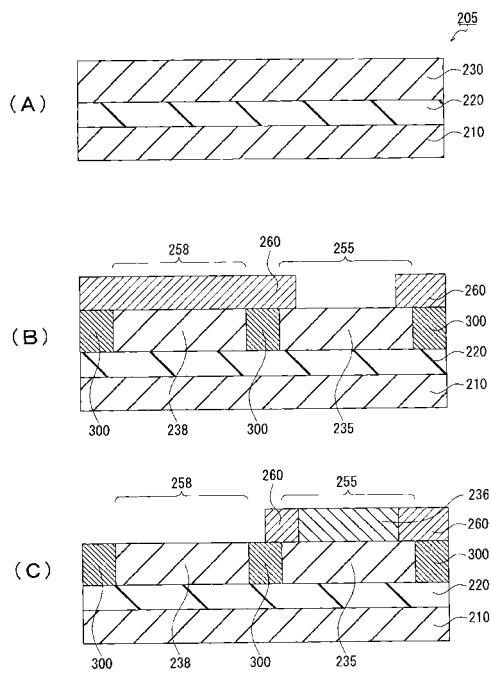

【0003】

図7を参照して、バイポーラトランジスタとCMOS、すなわちp型MOSFET及びn型MOSFETとが同一のチップに共存するBiCMOSの従来の製造方法について説明する（例えば特許文献1参照）。図7は、従来のBiCMOSの製造方法を説明するための工程図である。

【0004】

先ず、シリコン基板210上に形成されたシリコン酸化膜220と、シリコン酸化膜220上に形成された単結晶シリコン層230とを備えるSOI基板205を用意する（図7（A））。

【0005】

50

単結晶シリコン層 230 に LOCOS 膜 300 を形成して素子分離を行うことにより、単結晶シリコン層 230 を、MOSFET 被形成領域 258 の単結晶シリコン層 238 及びバイポーラトランジスタ被形成領域 255 の単結晶シリコン層 235 に分離する。単結晶シリコン層 230 に LOCOS 膜 300 を形成済みの、図 7 (A) に示す構造体の上面全体に、CVD 法により酸化膜 260 を堆積した後、バイポーラトランジスタ被形成領域 255 の単結晶シリコン層 235 を露出させる (図 7 (B))。

#### 【0006】

次に、バイポーラトランジスタ被形成領域 255 の、露出している単結晶シリコン層 235 上にシリコンを選択エピタキシャル成長させて、単結晶シリコン層 236 を形成する。単結晶シリコン層 236 を形成した後、MOSFET 被形成領域 258 に対応する酸化膜 260 の部分を除去する (図 7 (C))。

10

#### 【0007】

その後、MOSFET 被形成領域 258 の単結晶シリコン層 238 に MOSFET を形成し、及び、バイポーラトランジスタ被形成領域 255 の単結晶シリコン層 235 及び 236 にバイポーラトランジスタを形成して BiCMOS を得る。

#### 【0008】

このSOI基板にBiCMOSを形成する方法では、特に、バイポーラトランジスタを電気的に分離するために埋め込まれたLOCOS膜が、MOSFETなどの素子を形成するための熱処理によって収縮するなど、活性領域にストレインを発生させる可能性がある。

20

#### 【0009】

この問題を解決するために2重SOI構造の基板を用いたBiCMOSの製造方法が提案されている (例えば特許文献2参照)。

【特許文献1】特開平6-69430号公報

【特許文献2】特開2001-274234号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0010】

しかしながら、2重SOI構造の基板を用いたBiCMOSの製造方法では、活性領域に対するストレインを抑え、安定したBiCMOSを提供することができるものの、バイポーラトランジスタを高性能化及び高集積化に優れる縦型バイポーラトランジスタとした場合に、底部のコレクタ抵抗の低減方法については、改良すべき点がある。

30

#### 【0011】

この発明は、上述の問題点に鑑みてなされたものであり、この発明の目的は、半導体装置の製造方法として、縦型バイポーラトランジスタの底部に、形状良く低抵抗層を設ける方法を提供することにある。

#### 【課題を解決するための手段】

#### 【0012】

上述した目的を達成するために、この発明の請求項1に係る半導体装置の製造方法は、2重SOI基板を用意する工程と、ディープトレンチを形成する工程と、ディープトレンチを埋め込む工程と、開口部を設ける工程と、空孔部を設ける工程と、多結晶シリコン層を堆積する工程と、バイポーラトランジスタを形成する工程とを有している。

40

#### 【0013】

2重SOI基板を用意する工程では、支持基板上に、第1埋め込み酸化膜、第1単結晶シリコン層、第2埋め込み酸化膜、及び、第2単結晶シリコン層がこの順に積層された2重SOI基板を用意する。ディープトレンチを形成する工程では、第2単結晶シリコン層の表面から第1埋め込み酸化膜の表面が露出する深さまでエッチングを行って、バイポーラトランジスタ被形成領域を画成するディープトレンチを形成する。ディープトレンチを埋め込む工程では、ディープトレンチを形成済みの2重SOI基板上に、シリコン窒化膜及びシリコン酸化膜を積層して、ディープトレンチを埋め込む。開口部を設ける工程では、バイポーラトランジスタ被形成領域に、第2埋め込み酸化膜の表面が露出する深さにま

50

でエッティングを行う。空孔部を設ける工程では、ウェットエッティングにより、バイポーラトランジスタ被形成領域内の第2埋め込み酸化膜を除去する。多結晶シリコン層を堆積する工程では、上述の工程で形成された、互いに連通している開口部及び空孔部に多結晶シリコン層を堆積する。バイポーラトランジスタを形成する工程では、バイポーラトランジスタ被形成領域の第2単結晶シリコン層上にバイポーラトランジスタを形成する。

#### 【発明の効果】

##### 【0014】

この発明の請求項1に係る半導体装置、特にバイポーラトランジスタの製造方法によれば、第2埋め込み酸化膜を除去することで形成された空孔部に多結晶シリコンを堆積することで、ディープトレンチで画成されたバイポーラトランジスタ被形成領域の第2単結晶シリコン層の底部に、形状よく多結晶シリコン層を形成することができる。また、この多結晶シリコン層により、バイポーラトランジスタのコレクタ抵抗を減少させることができる。

10

#### 【発明を実施するための最良の形態】

##### 【0015】

以下、図を参照して、この発明の実施の形態について説明するが、構成および配置関係についてはこの発明が理解できる程度に概略的に示したものに過ぎない。また、以下、この発明の好適な構成例につき説明するが、各構成の組成(材質)および数値的条件などは、単なる好適例にすぎない。従って、この発明は以下の実施の形態に限定されない。

20

##### 【0016】

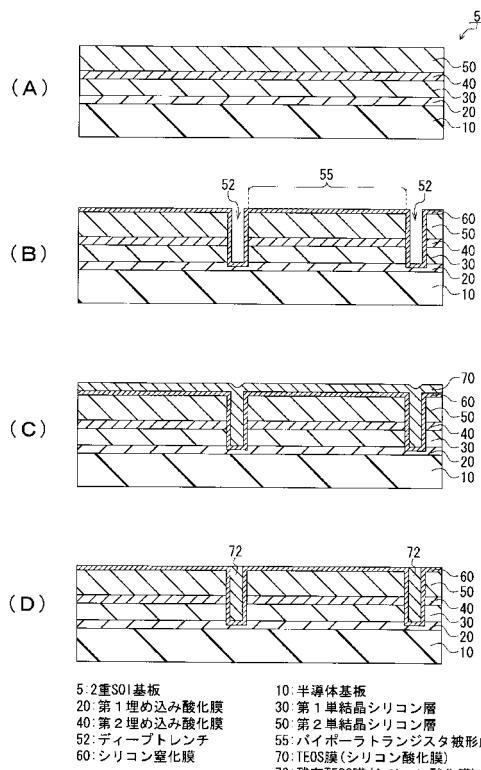

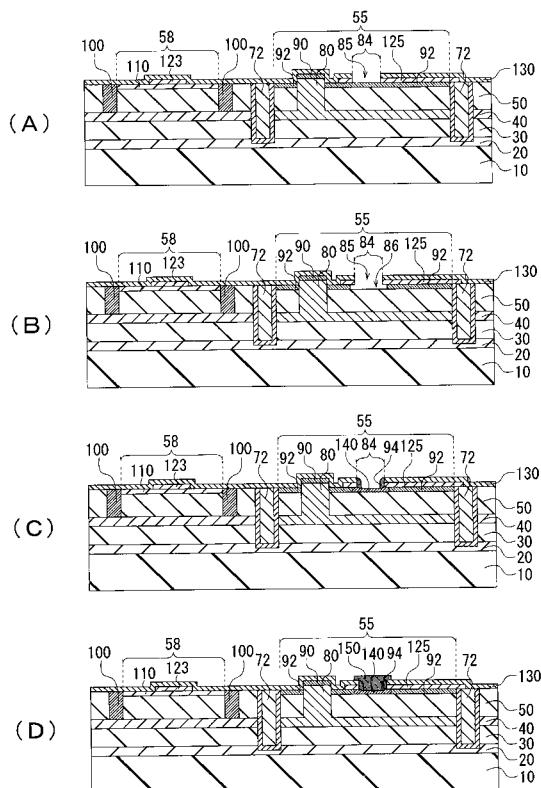

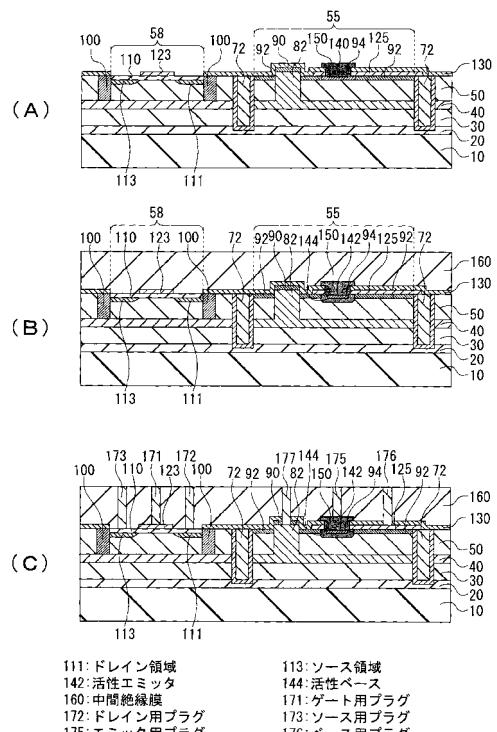

図1～6は、半導体装置として、バイポーラトランジスタとCMOSとを同一基板に備えるBiCMOSの製造方法を説明するための工程図である。

##### 【0017】

先ず、2重SOI構造を有する2重SOI基板5を用意する。2重SOI基板5は、積層構造体であって、この積層構造体は、シリコン等の半導体基板10上に、第1埋め込み酸化膜20、第1単結晶シリコン層30、第2埋め込み酸化膜40、第2単結晶シリコン層50が順に積層されて形成された構造を有している。2重SOI基板5を用意するにあたり、SOI基板を製造するのに用いられる、表面に埋め込み酸化膜を形成したシリコン膜と半導体基板との貼り合わせを2回行っても良いし、或いは、表面に埋め込み酸化膜を形成したシリコン膜と半導体基板との貼り合わせを行った後に、単結晶シリコン基板に酸素を高濃度にイオン注入するSIMOX(Separation by Implanted Oxygen)と行っても良い。ここでは、第1埋め込み酸化膜20及び第2埋め込み酸化膜40の厚さを約200nmとする。また、第1単結晶シリコン層30を、厚さが約3μmのn<sup>+</sup>単結晶シリコン層とし、また、第2単結晶シリコン層50を、厚さが約500nmのn<sup>-</sup>単結晶シリコン層50とする(図1(A))。

30

##### 【0018】

次に、2重SOI基板5に、ディープトレンチ52を形成する。ディープトレンチ52は、バイポーラトランジスタ被形成領域55を画成する基板領域に、任意好適な公知のホトリソグラフィ及びドライエッティングを用いて形成される。このディープトレンチ52の幅を約500nmとし、その深さを第1埋め込み酸化膜20が露出する程度の深さとする。従って、第1単結晶シリコン層30及び第2単結晶シリコン層50を含む積層体は、ディープトレンチ52により複数の島状領域として分離される。ディープトレンチ52の形成後、任意好適な公知のCVD(Chemical Vapor Deposition)法により、第2単結晶シリコン層50の表面上及びディープトレンチ52の内壁に、シリコン窒化膜60を形成する。シリコン窒化膜60の厚さを約15nmとする(図1(B))。

40

##### 【0019】

次に、TEOS(tetraethylorthosilicate)を用いた減圧CVD(LPCVD: Low Pressure CVD)法によって、ディープトレンチ52を埋め込むシリコン酸化膜(以下、TEOS膜とも称する。)70を形成する。TE

50

OS膜70を、被覆性に優れるTEOSを用いたCVD法で形成するので、ディープトレンチ52を隙間無く埋め込むことができる。このとき、TEOS膜70は、第2単結晶シリコン層50の上面の上側にも形成される(図1(C))。

#### 【0020】

次に、化学機械研磨(CMP: Chemical Mechanical Polishing)法により、第2単結晶シリコン層50の上面に形成されたシリコン窒化膜60上のTEOS膜70を除去し、当該第2単結晶シリコン層50の上面のシリコン窒化膜60の部分を露出させる。このとき、ディープトレンチ52内には、TEOS膜70が残存膜(以下、残存TEOS膜とも称する。)72として残存する(図1(D))。この図1(D)に示す構造体の上面は、好ましくは平坦面とする。

10

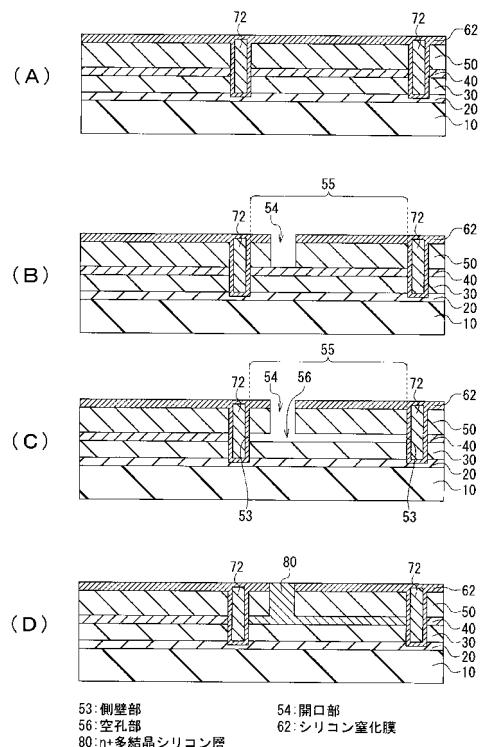

#### 【0021】

次に、図1(D)に示す構造体の上面全体にシリコン窒化膜を30nm程度追加生成して、形成済みのシリコン窒化膜60を下層として含む新たなシリコン窒化膜62で上面を覆う(図2(A))。

#### 【0022】

次に、バイポーラトランジスタ被形成領域55内に、任意好適なホトリソグラフィ及びドライエッチングでパターニングすることにより、コレクタ形成用の開口部54を開ける。このドライエッチングを、シリコン窒化膜62の表面から第2埋め込み酸化膜40が露出する程度の深さにまで行う(図2(B))。

20

#### 【0023】

次に、フッ化水素(HF)酸によるウェットエッチングを行って、バイポーラトランジスタ被形成領域55内の第2埋め込み酸化膜40を除去する。このウェットエッチングは、横方向には、ディープトレンチ52の側壁部53に形成されているシリコン窒化膜62まで進む。従って、この第2埋め込み酸化膜40は、開口部54に露出している領域はもとより、第2単結晶シリコン50の下側に延在している領域まで除去されて、コレクタ形成用の空孔部56が形成される(図2(C))。

#### 【0024】

次に、LPCVD法により、ヒ素(As)又はリン(P)を高濃度にドープしたn<sup>+</sup>多結晶シリコンを、図2(C)に示す構造体の上面全体に、ほぼ1μmの厚さになるまで堆積して形成する。n<sup>+</sup>多結晶シリコンの堆積中に、n<sup>+</sup>多結晶シリコンは、空孔部56の第2単結晶シリコン層50の下の領域部分にも回り込んで堆積し、開口部54と空孔部56が、n<sup>+</sup>多結晶シリコンで埋め込まれる。その後、エッチバックすることにより、開口部54及び空孔部56を埋め込んで表面に露出している多結晶シリコンの頂面と、シリコン窒化膜62の上面とが平坦化されて一つの平面を形成する。このようにして、開口部54と空孔部56とに、バイポーラトランジスタの埋め込みコレクタ層となるn<sup>+</sup>多結晶シリコン層80が形成される(図2(D))。なお、空孔部56をn<sup>+</sup>多結晶シリコンで埋めた後、開口部54に、CVD法でタンゲステン(W)などのメタルを堆積させて開口部54を埋め込んでも良い。この場合、メタルが第2単結晶シリコン層50中に拡散するので、第2単結晶シリコン層50が、より低抵抗になることが期待できる。

30

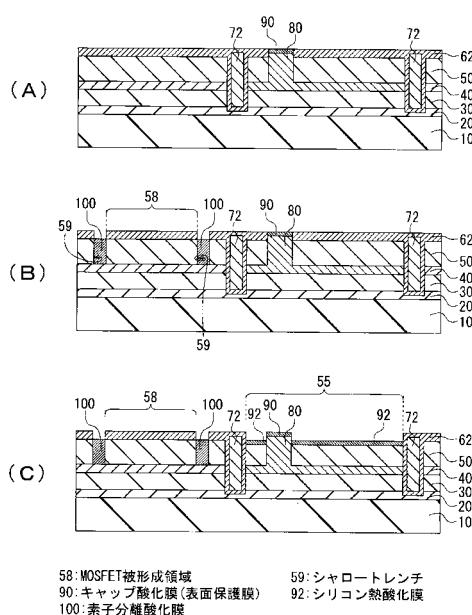

#### 【0025】

次に、n<sup>+</sup>多結晶シリコン層80の露出表面、すなわち頂面の領域を酸化して、キャップ酸化膜(表面保護膜)90を形成する(図3(A))。

40

#### 【0026】

次に、MOSFET被形成領域58を画成する領域に対して、任意好適な公知のホトリソグラフィ及びドライエッチングを行う。これにより、対応する領域部分のシリコン窒化膜62及び第2単結晶シリコン層50を除去して、第2埋め込み酸化膜40を実質的に露出させるシャロートレンチ59を形成する。このシャロートレンチ59を、例えば公知のCVD法で形成したシリコン酸化膜で埋め込み、このシリコン酸化膜で素子分離酸化膜100を形成する(図3(B))。

#### 【0027】

50

次に、任意好適なホトリソグラフィ及びドライエッチングにより、バイポーラトランジスタ被形成領域55の箇所に存在するシリコン窒化膜62の領域部分を除去して第2単結晶シリコン層50を実質的に露出させる。このとき、シリコン窒化膜62の一部分が残存する。露出した第2単結晶シリコン層50の表面領域を熱酸化することによって、約50nm厚のシリコン熱酸化膜92を形成する(図3(C))。

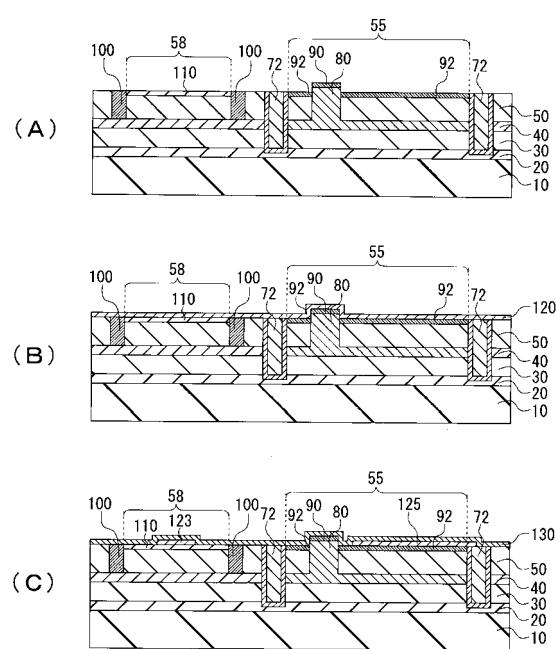

#### 【0028】

次に、残存したシリコン窒化膜(図3(C)では符号62で示す部分)を全て除去し、然る後、MOSFET被形成領域58内の第2単結晶シリコン層50の表面にMOSFETのゲート酸化膜110を形成する(図4(A))。

#### 【0029】

次に、MOSFET被形成領域58内の第2単結晶シリコン層50に対して、各導電型へのドーピングを行う。このドーピングにより注入されるイオンは、MOSFETをn型MOSFETとp型MOSFETの何れにするかに応じて決められる。その後、ドーピング済みの、図4(A)に示す構造体の上側全面に多結晶シリコン膜120を約150nmの厚さで生成する(図4(B))。この、多結晶シリコン膜120の生成は、任意好適な公知のCVD法で行えば良い。

#### 【0030】

次に、多結晶シリコン膜120を加工して、MOSFETのゲート電極123及びバイポーラトランジスタのベース電極125を形成する。その後、ベース電極125に対して、選択的に硼素(B)をイオン注入によりドーピングする。また、MOSFET被形成領域58に対して、LDD(Lightly Doped Drain)形成のためのドーピングをイオン注入により行う。さらに、ベース電極及びMOSFET被形成領域58に対するドーピング済みの、図4(B)に示す構造体の上面全体に、シリコン窒化膜130を約200nm厚で形成する(図4(C))。シリコン窒化膜の形成は、例えば、公知のCVD法により行われる。

#### 【0031】

次に、バイポーラトランジスタのエミッタ電極を形成するエミッタ電極被形成領域84内のシリコン窒化膜130及びベース電極125の積層領域部分を任意好適な公知のホトリソグラフィ及びドライエッチングにより順次に除去して、エミッタ電極用開口部85を形成する。このエミッタ電極用開口部85によりシリコン熱酸化膜92が露出する(図5(A))。

#### 【0032】

次に、フッ化水素(HF)酸によるウェットエッチングで、エミッタ電極被形成領域84内のシリコン熱酸化膜92を除去する。このウェットエッチングでは、自己整合的にシリコン熱酸化膜92が除去され、さらに、ウェットエッチングのエッチング時間を制御することにより、エミッタ電極用開口部85の側壁から水平方向に約200nmのサイドエッチが行われる。この結果、シリコン熱酸化膜92が除去された部分にエミッタ電極用空孔部86が形成される(図5(B))。

#### 【0033】

次に、エミッタ電極用開口部85及びエミッタ電極用空孔部86にシリコンを選択エピタキシャル成長させて、エミッタ電極用開口部85を埋め込む。具体的には、ウェットエッチングにより露出したベース電極125の端部の下面から第2単結晶シリコン層50に向かう方向に、シリコンを選択エピタキシャル成長させて、エピタキシャル成長シリコン層140を形成する。このエピタキシャル成長したシリコンは、エミッタ電極用空孔部86の部分であって、サイドエッチされて形成された領域部分を埋め込む。なお、このエピタキシャル成長したシリコンは、ベース電極125付近では多結晶になり、また、第2単結晶シリコン層50付近では単結晶になる。その後、エミッタ電極用開口部85の側壁に、側壁絶縁膜94を、例えばCVD法によりシリコン窒化膜で形成する。(図5(C))。エピタキシャル成長シリコン層140は、不純物として硼素(B)を $5 \times 10^{18} / \text{cc}$ 含んだp型導電層とする。このエピタキシャル成長の結果、第2単結晶シリコン層50の

10

20

30

40

50

表面付近も p 型となる。また、このエピタキシャル成長シリコン層 140 の形成は、公知の SiGe のヘテロエピタキシャル成長により、多層構成とし、その一部に SiGe 層を含んだ複合膜としてもよい。

#### 【 0034 】

次に、図 5 ( C ) に示す構造体の上面全体に、リンが高濃度にドープされた多結晶シリコン層成長させた後、この多結晶シリコンを加工してエミッタ電極 150 を形成する ( 図 5 ( D ) )。

#### 【 0035 】

次に、MOSFET 被形成領域 58 内のシリコン窒化膜 130 を除去し、然る後、ゲート電極 123 をマスクとして用いてイオン注入及び活性化アニールを行って、MOSFET のドレイン領域 111 及びソース領域 113 を形成する ( 図 6 ( A ) )。

10

#### 【 0036 】

次に、中間絶縁膜 160 を、例えば CVD 法によりシリコン酸化膜で形成する。その後、図 6 ( A ) に示す構造体に対して、ランプアニール ( R T A : Rapid Thermal Annealing ) により、900 、 30 秒程度の熱処理を行う。この R T A により、エミッタ電極 150 からリンを、エピタキシャル成長シリコン層 140 と、単結晶シリコン層 50 のエピタキシャル成長シリコン層 140 と接する表面とに浅く拡散させて、活性エミッタ 142 を形成する。また、第 2 単結晶シリコン層 50 の p 型の導電型の部分であって、R T A によりリンが拡散しない部分が、 p 型の活性ベース 144 となる。ここで、エピタキシャル成長シリコン層 140 のベース電極 125 付近の部分も、リンが拡散しない部分であり、 p 型の活性ベース 144 となる ( 図 6 ( B ) )。

20

#### 【 0037 】

次に、MOSFET のソース、ドレイン及びゲートの各電極用のコンタクトホール、並びに、バイポーラトランジスタのエミッタ、ベース及びコレクタの各電極用のコンタクトホール ( 図示を省略する。 ) を、中間絶縁膜 160 、シリコン窒化膜 130 、及びキャップ酸化膜 90 に任意好適な公知のホトリソグラフィ及びドライエッチングを行うことにより、それぞれ形成する。これらのコンタクトホールに、タングステン ( W ) プラグを埋め込みコンタクトとして形成する。W プラグは、MOSFET のゲート用プラグ 171 、ドレイン用プラグ 172 及びソース用プラグ 173 、並びに、バイポーラトランジスタのエミッタ用プラグ 175 、ベース用プラグ 176 及びコレクタ用プラグ 177 として用いられる ( 図 6 ( C ) )。これらの W プラグは、バイポーラトランジスタ及び MOSFET の金属電極とそれぞれ等価である。

30

#### 【 0038 】

W プラグの形成後は、中間絶縁膜 160 上にアルミニウム等の金属配線層を設けて、外部回路等との接続のための配線を行えば良い。

#### 【 0039 】

この発明のバイポーラトランジスタの製造方法によれば、第 2 埋め込み酸化膜を除去することで形成された空孔部に多結晶シリコンを堆積するので、ディープトレンチで画成された領域の第 2 単結晶シリコン層の底部に形状よく多結晶シリコン層を形成することができる。また、この方法で製造されたバイポーラトランジスタを備える半導体装置では、この多結晶シリコン層により、バイポーラトランジスタのコレクタ抵抗が減少する。

40

#### 【 図面の簡単な説明 】

#### 【 0040 】

【 図 1 】 BiCMOS の製造方法を説明するための工程図 ( その 1 ) である。

【 図 2 】 BiCMOS の製造方法を説明するための工程図 ( その 2 ) である。

【 図 3 】 BiCMOS の製造方法を説明するための工程図 ( その 3 ) である。

【 図 4 】 BiCMOS の製造方法を説明するための工程図 ( その 4 ) である。

【 図 5 】 BiCMOS の製造方法を説明するための工程図 ( その 5 ) である。

【 図 6 】 BiCMOS の製造方法を説明するための工程図 ( その 6 ) である。

【 図 7 】 従来の BiCMOS の製造方法を説明するための工程図である。

50

## 【符号の説明】

## 【0041】

|                 |                         |    |

|-----------------|-------------------------|----|

| 5               | 2重S O I基板               |    |

| 10              | 半導体基板                   |    |

| 20              | 第1埋め込み酸化膜               |    |

| 30              | 第1単結晶シリコン層              |    |

| 40              | 第2埋め込み酸化膜               |    |

| 50              | 第2単結晶シリコン層              |    |

| 52              | ディープトレンチ                |    |

| 53              | 側壁部                     | 10 |

| 54              | 開口部                     |    |

| 55、255          | バイポーラトランジスタ被形成領域        |    |

| 56              | 空孔部                     |    |

| 58、258          | M O S F E T被形成領域        |    |

| 59              | シャロートレンチ                |    |

| 60、62、130       | シリコン窒化膜                 |    |

| 70              | T E O S膜(シリコン酸化膜)       |    |

| 72              | 残存T E O S膜(シリコン酸化膜)     |    |

| 80              | n <sup>+</sup> 多結晶シリコン層 |    |

| 84              | エミッタ電極被形成領域             | 20 |

| 85              | エミッタ電極用開口部              |    |

| 86              | エミッタ電極用空孔部              |    |

| 90              | キャップ酸化膜(表面保護膜)          |    |

| 92              | シリコン熱酸化膜                |    |

| 94              | 側壁絶縁膜                   |    |

| 110             | ゲート酸化膜(シリコン酸化膜)         |    |

| 111             | ドレイン領域                  |    |

| 113             | ソース領域                   |    |

| 120             | 多結晶シリコン膜                |    |

| 123             | ゲート電極                   | 30 |

| 125             | ベース電極                   |    |

| 140             | エピタキシャル成長シリコン層          |    |

| 150             | エミッタ電極                  |    |

| 160             | 中間絶縁膜                   |    |

| 171             | ゲート用プラグ                 |    |

| 172             | ドレイン用プラグ                |    |

| 173             | ソース用プラグ                 |    |

| 175             | エミッタ用プラグ                |    |

| 176             | ベース用プラグ                 |    |

| 177             | コレクタ用プラグ                | 40 |

| 205             | S O I基板                 |    |

| 210             | シリコン基板                  |    |

| 220             | シリコン酸化膜                 |    |

| 230、235、236、238 | 単結晶シリコン層                |    |

| 260             | 酸化膜                     |    |

| 300             | L O C O S膜              |    |

【図1】

BiCMOSの製造方法を説明するための工程図(その1)

【図2】

BiCMOSの製造方法を説明するための工程図(その2)

【図3】

BiCMOSの製造方法を説明するための工程図(その3)

【図4】

BiCMOSの製造方法を説明するための工程図(その4)

【図5】

84:エミッタ電極被形成領域

85:エミッタ電極用開口部

86:エミッタ電極用空孔部

94:側壁絶縁膜

140:エピタキシャル成長シリコン層

150:エミッタ電極

BiCMOSの製造方法を説明するための工程図(その5)

【図6】

111:ドレイン領域

142:活性エミッタ

160:中間絶縁膜

172:ドレイン用プラグ

175:エミッタ用プラグ

177:コレクタ用プラグ

113:ソース領域

144:活性ベース

171:ゲート用プラグ

173:ソース用プラグ

176:ベース用プラグ

BiCMOSの製造方法を説明するための工程図(その6)

【図7】

従来のBiCMOSの製造方法を説明するための工程図

---

フロントページの続き

(51)Int.Cl. F I

H 01L 21/8222 (2006.01)

H 01L 27/08 (2006.01)

(56)参考文献 特開平07-122719 (JP, A)

特開平01-189154 (JP, A)

特開2001-274234 (JP, A)

特開2000-082680 (JP, A)

特開平08-102530 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01L 21 / 331

H 01L 21 / 8222

H 01L 21 / 8248

H 01L 21 / 8249

H 01L 27 / 06

H 01L 27 / 08

H 01L 29 / 73