(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

16 June 2011 (16.06.2011)

(10) International Publication Number

WO 2011/071637 A1

(51) International Patent Classification:

H05B 33/08 (2006.01)

(21) International Application Number:

PCT/US2010/055971

(22) International Filing Date:

9 November 2010 (09.11.2010)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

12/634,911 10 December 2009 (10.12.2009) US

(71) Applicant (for all designated States except US): GENERAL ELECTRIC COMPANY [US/US]; 1 River Road, Schenectady, NY 12345 (US).

(72) Inventors; and

(75) Inventors/Applicants (for US only): AURONGZEB, Deeder [BD/US]; 1975 Noble Road, Cleveland, OH 44112 (US). ROBERTS, Bruce, Richard [US/US]; 1975 Noble Road, Cleveland, OH 44112 (US).

(74) Agents: DIMAURO, Peter, T. et al.; General Electric Company, Global Patent Operation, 2 Corporate Drive, Suite 648, Shelton, CT 06484 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ,

CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NL, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Declarations under Rule 4.17:

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

Published:

- with international search report (Art. 21(3))

(54) Title: ELECTRONIC DRIVER DIMMING CONTROL USING RAMPED PULSED MODULATION FOR LARGE AREA SOLID-STATE OLEDs

FIG. 3F

(57) Abstract: An electronic driver apparatus and methods are disclosed for driving power an organic LED or other large area solid state light source, in which a switch mode DC current source provides DC current to drive the light source according to a control input and a controller provides a ramped pulse modulated control input to the current source for at least some values of a dimming setpoint signal or value to mitigate damaging current spikes by controlling  $di/dt$  of the drive current.

WO 2011/071637 A1

## ELECTRONIC DRIVER DIMMING CONTROL USING RAMPED PULSED MODULATION FOR LARGE AREA SOLID-STATE OLEDS

### BACKGROUND OF THE DISCLOSURE

[0001] Large area solid-state lighting devices, such as organic light-emitting diodes (OLEDS), are becoming more popular for illuminating buildings, roads, and in other area lighting applications, as well as in a variety of signage and optical display applications. Such applications require long service life without color shift or lumen degradation to be commercially viable. Thus, there remains a need for improved OLED driver apparatus and techniques to control consistent illumination with dimming capabilities while mitigating flicker and premature device degradation for extended usable device service lifetime.

### SUMMARY OF THE DISCLOSURE

[0002] The present disclosure provides drivers and methods for powering OLEDs and other large area solid-state light sources in which a switch mode DC current source provides DC current to drive the light source according to a control input and a controller provides a ramped pulse modulated control input to the current source for all or a portion of a range of a dimming setpoint signal or value. The ramped modulation involves controlled transitions between drive current levels to limit high rates of change of the device current ( $di/dt$ ) to avoid or mitigate premature lumen degradation and color shift.

[0003] A driver apparatus is provided, which includes a switch mode DC current source to provide current to power one or more large area solid-state light sources according to a control input, as well as a controller that provides the control input to the current source according to a setpoint signal or value. The controller provides the control input as a ramped pulse modulated waveform for at least some values of a setpoint signal or value. The modulated waveform includes transitions between two or more control input values with controlled increasing profiles having a rise time value of about 100  $\mu$ s or more and about 2 ms or less between control input values, and also includes controlled decreasing

profiles having a fall time value of about 100  $\mu$ s or more and about 2 ms or less between control input values. In some embodiments, the rise time value and the fall time value are the same, such as about 1 ms in some implementations. In other embodiments, the rise time value and the fall time value are unequal. The increasing and/or decreasing profiles are linear in some embodiments. In certain embodiments, all or a portion of at least one of the increasing profile and the decreasing profile is nonlinear. The driver in some embodiments includes a feedback circuit that senses the light source current and provides a feedback signal to the controller, with the controller providing the pulse modulated control input to the current source at least partially according to the feedback signal. In certain embodiments, moreover, the controller provides the pulse modulated control input at a modulation frequency of about 100-2000 Hz.

[0004] A method is provided for powering at least one large area solid-state light source. The method includes controlling a switch mode DC current source to provide DC electrical current to power at least one large area solid-state light source according to a control input. The method further includes providing a pulse modulated control input to the current source as a pulse modulated waveform for at least some values of a setpoint signal or value. The pulse modulated waveform includes transitions between control input values with controlled increasing profiles having a rise time value of about 100  $\mu$ s or more and about 2 ms or less between control input values and with controlled decreasing profiles having a fall time value of about 100  $\mu$ s or more and about 2 ms or less between control input values. In some embodiments, the rise time value and the fall time value are about 1 ms, and in certain embodiments the rise time value and the fall time value are unequal. One or both of the profiles may be linear, and all or a portion of the increasing and/or decreasing profiles can be nonlinear.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0005] One or more exemplary embodiments are set forth in the following detailed description and the drawings, in which:

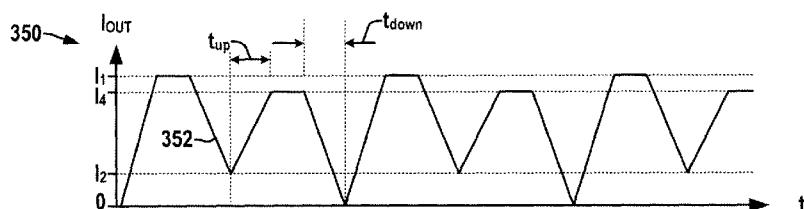

[0006] Fig. 1A is a schematic diagram illustrating a driver apparatus with a switch-mode DC current source and a controller providing ramped pulse modulation control for driving large area solid-state light sources;

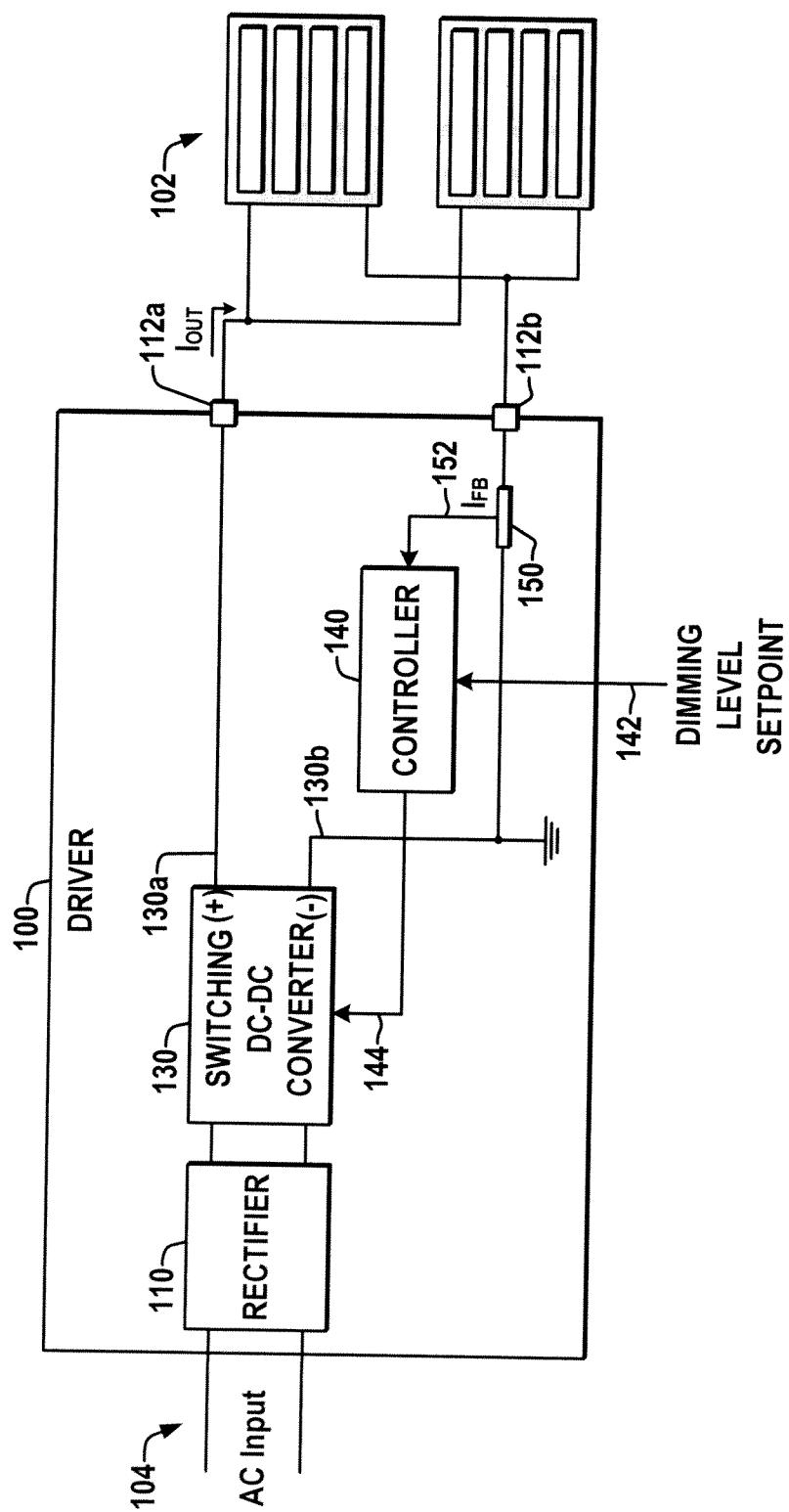

[0007] Fig. 1B is a schematic diagram illustrating another exemplary driver apparatus with a switch-mode DC current source including a buck converter and an output switch, as well as a controller providing ramped pulse modulation control for the switch to drive the large area solid-state light sources;

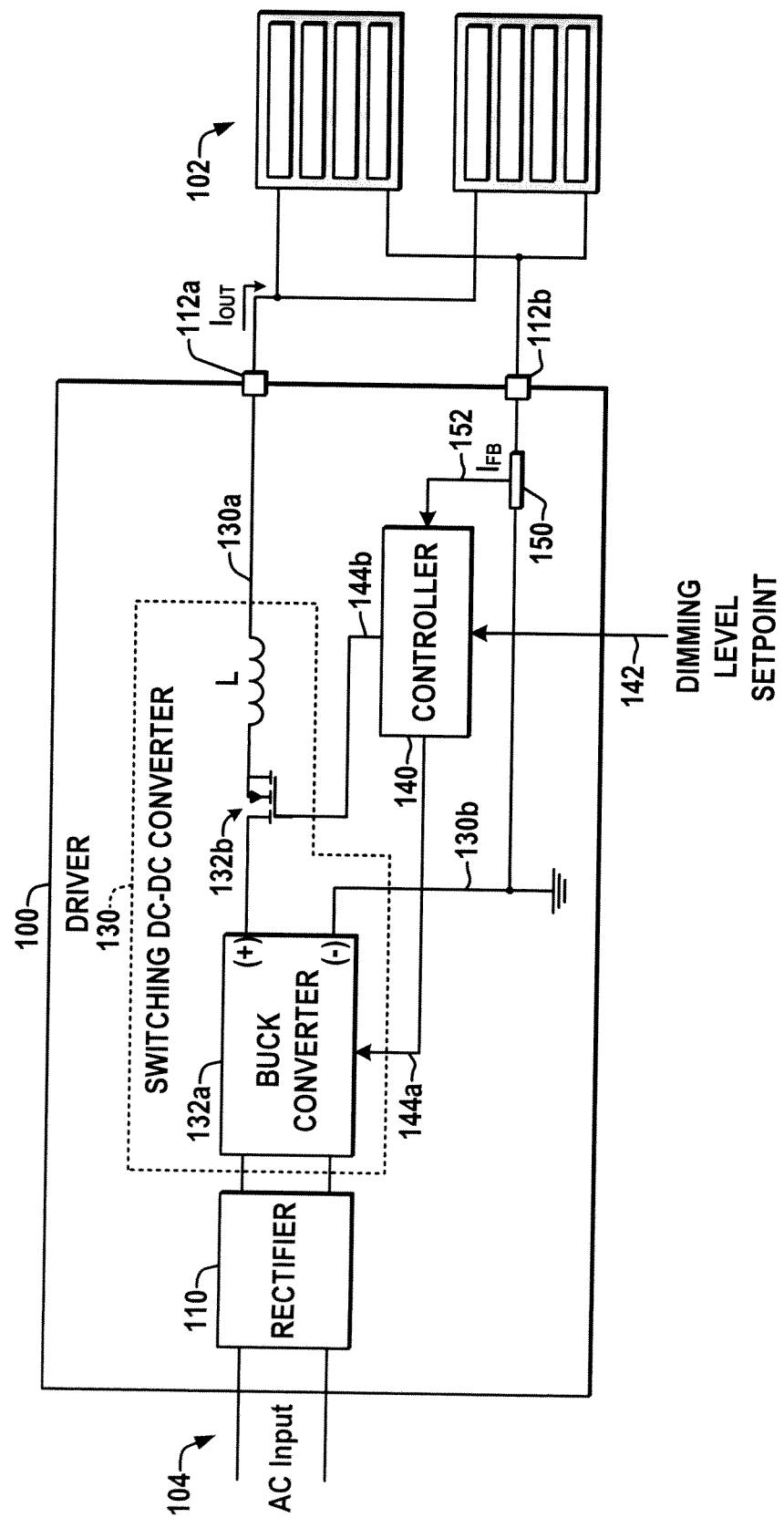

[0008] Fig. 2 is a graph showing corresponding dimming level setpoint values and selectively modulated control input for controlling the DC current source in the driver apparatus of Figs. 1A and 1B; and

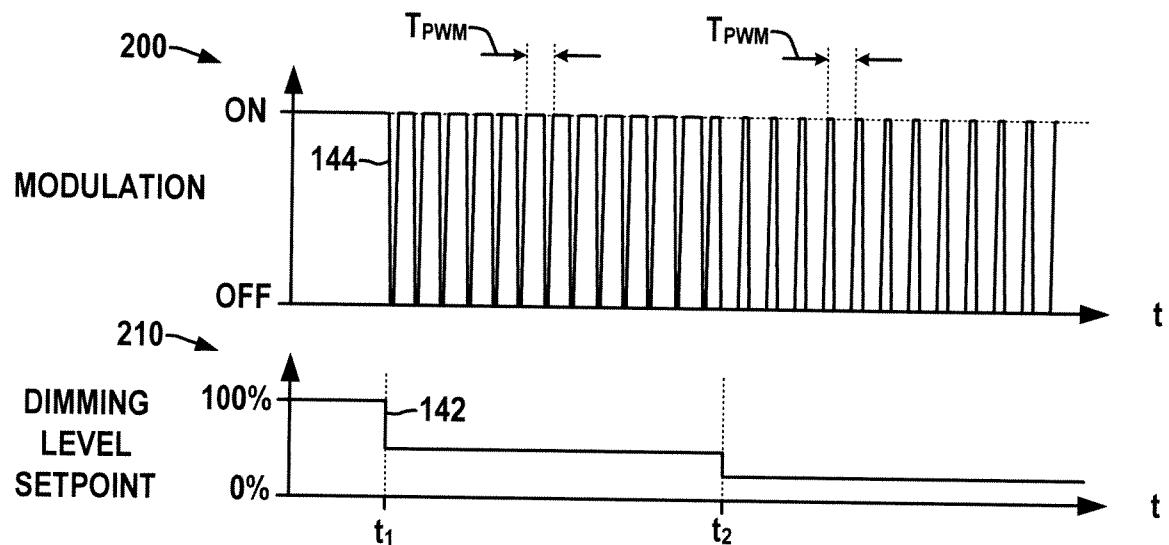

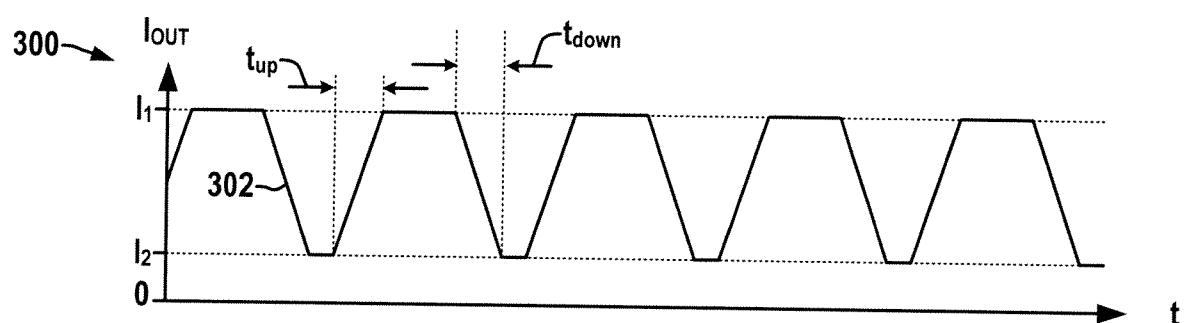

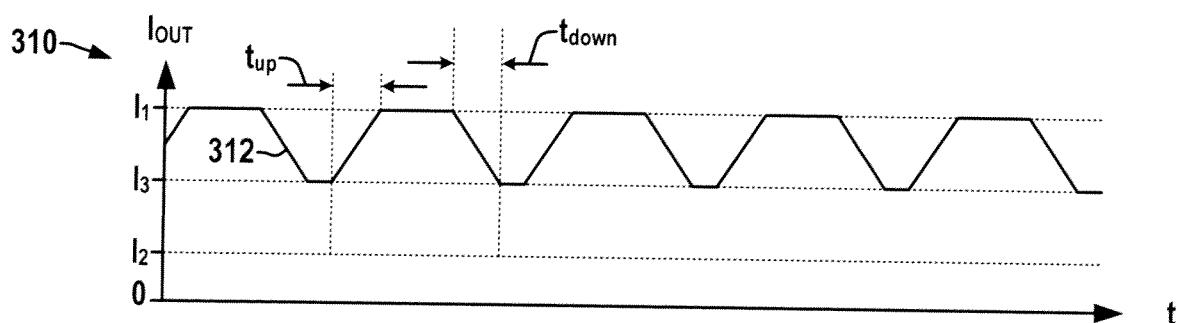

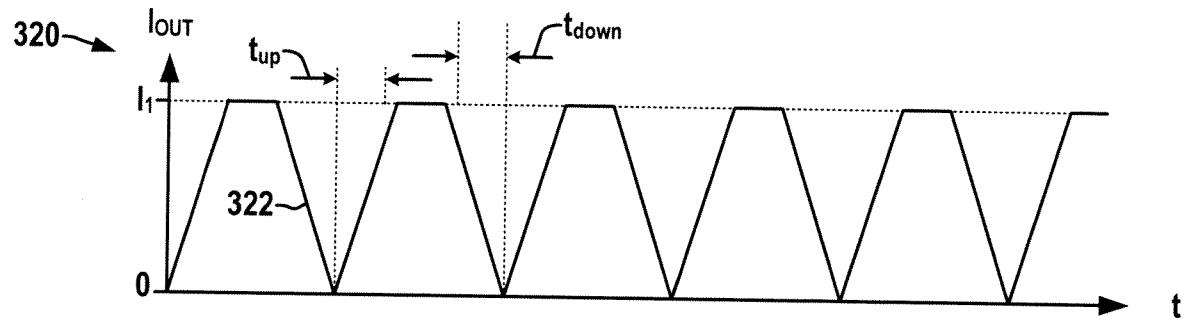

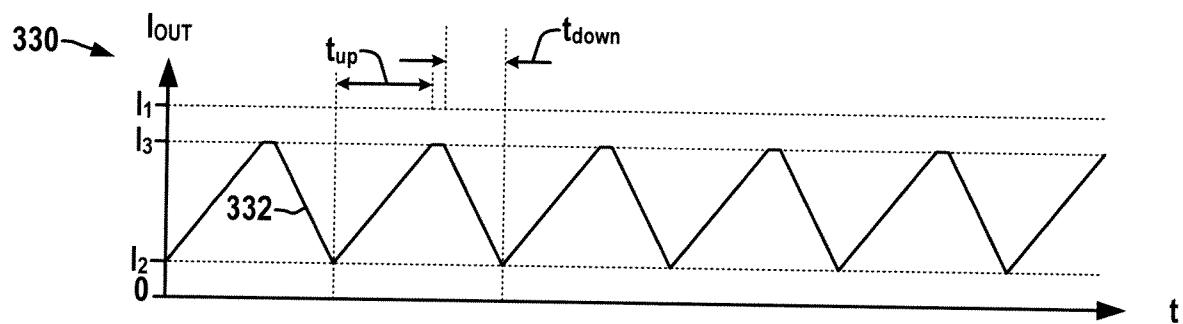

[0009] Figs. 3A-3H are graphs illustrating exemplary ramped pulse modulated driver current in dimming operation of the driver apparatus of Figs. 1A and 1B.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0010] Referring now to the drawings, where like reference numerals are used to refer to like elements throughout, and wherein the various features are not necessarily drawn to scale, the present disclosure relates to electronic drivers and methods for powering large area solid-state light sources which may be used in connection with various types and series/parallel configurations of such light sources. The disclosed concepts may be employed in association with organic LED (OLED) light sources or other solid-state lighting devices having large cross-sectional areas.

[0011] Referring initially to Figs. 1A, 1B and 2, an electronic driver apparatus 100 is illustrated in Fig. 1A for powering one or more large area solid-state light sources 102, in this case a parallel combination of two panels, each including four series-coupled 4 volt, 50 mA OLED panels for a lighting application. The driver 100 includes a switch mode DC current source 130 operative to provide DC electrical current to the light source 102 according to a control input 144 provided by a controller 140. The DC source 130 is a switch-mode DC-DC converter in one embodiment that receives input DC power from a rectifier 110, which converts input AC power from input terminals 104. The converter 130 provides DC electrical current for energizing one or more large solid-state light sources 102, such as OLED(s). Any suitable switch-mode DC power source 130 may be employed in the driver 100, which may be internally powered (e.g., via batteries, solar cells, etc.) or which may generate DC output power by conversion from an input supply (e.g., rectifier 110 converting input AC power received at the input 104). The source 130 provides DC output voltage at output terminals 130a (+) and 130b (-) and is operative to supply DC current to a load coupled across the terminals 130a, 130b, in this case including the OLED panels 102. The controller 140 can be an analog circuit or a processor-based circuit (e.g., including a microcontroller, microprocessor, logic circuit, etc.) or combinations thereof which provide one or more control inputs 144 to the DC source 130 based at least in part on the received setpoint 142. The driver 100 provides output terminals 112a and 112b for connection of one or more large area solid-state light sources 102, such as one or more OLEDs for lighting applications when electrical current is provided by the driver 100.

[0012] Fig. 1B illustrates another exemplary driver apparatus 100 in which the switch-mode DC current source 130 includes a buck converter 132a controlled by a first control input 144a from the controller 140. The DC-DC converter 130 in this embodiment also includes an output switch 132b operated by a second control input 144b from the controller 140 and a series choke L. The output switch 132b is operable in a first ('ON') state to allow electrical current to flow from the power source 130 to the light source(s) 102, and in a second ('OFF') state to prevent current from flowing from the power source 130 to the load

102. In one exemplary form of operation, the buck converter 132a operates according to a regulation loop around the input 144a while the switch 132b is operated according to the second control input 144b. In this case, the controller 140 selectively provides ramped pulse modulation control of the output switch 132b via the input 144b for the switch to drive the large area solid-state light sources during dimming operation.

[0013] One or more feedback signals 152 may be generated by feedback circuitry 150 in the driver apparatus of Figs. 1A and 1B, which are provided to the controller 140 in certain embodiments. A shunt device 150 in the illustrated examples allows sensing of the load current flowing through the light source load 102, and provides a current feedback signal 152 ( $I_{FB}$ ) to the controller 140. The controller 140 can use the feedback signal 152 to infer or compute one or more aspects of the performance of the light source 102 and/or of the power source 130 and make any necessary adjustments to the control input(s) 144.

[0014] Fig. 2 provides a graph 200 showing the control input 144 and a corresponding graph 210 showing corresponding exemplary dimming level setpoint values 142. In one example, the controller 140 implements selective pulse width modulation (PWM) control of the current source 130 for at least some values of a setpoint signal or value 142 for controlling the DC current source in the driver apparatus of Fig. 1A. In this exemplary form of operation, the controller 140 provides the control input 144 to the source 130 as a constant value for 100% output, and receives the dimming setpoint signal or value 142 from an external source (e.g., from a user-operated wall dimmer knob or slide control). When the dimming level setpoint 142 indicates less than 100% light output is desired, the controller 140 provides a pulse modulated control input 144 to the current source 130 according to the setpoint signal or value 142.

[0015] As the user changes the dimming setpoint 142 to less than 100% of rated power (e.g., at  $t_1$  in graph 210), the controller 140 modulates the control input 144 at a modulation period  $T_{PWM}$  to provide portions of each period  $T_{PWM}$  at a first level of current (e.g., 100% in one example with the converter 132a providing 100% of the rated current and with the

switch 132b “ON” or closed), and the remaining portions at a second level of output current  $I_{OUT}$  (e.g., switch 132b “OFF”). In this manner, the OLED light sources 102 are driven at less than 100% rated current and the light output is dimmed. At  $t_2$  in Fig. 2, the user-selected dimming level 142 is further decreased, and the controller 140 adjusts the pulse with modulation by decreasing the on-time within each PWM period  $T_{PWM}$ , and the controller 140 operates in similar fashion to provide any desired level of dimming according to the setpoint 142 by adjusting the pulse modulated control input 144 provided to the DC current source 130.

[0016] In some embodiments, the DC source 130 is controlled to provide 100% rated current without pulse modulation and modulated control inputs 144 are provided for some range of lower dimming levels, and in other embodiments pulse modulated signals 144 are used throughout the dimming range 0%-100%, wherein all such embodiments are contemplated that provide pulse modulated control inputs 144 to the source 130 for at least some values of a setpoint signal or value 142. In the example of Fig. 1A, the modulated control input 144 is provided as a setpoint for the source 130, which regulates its output to that level. In the example of Fig. 1B, the converter 132a is regulated to a single DC current level, and modulated control inputs 144b are provided to the output switch 132b to selectively couple/decouple the converter output to/from the OLED load 102. Any form of modulation techniques can be used, including without limitation pulse width modulation (PWM), frequency modulation (FM), time division multiplexing (TDM), etc. In certain embodiments, the controller 140 provides the pulse modulated control input 144 to the current source 130 at a modulation frequency of about 100 Hz or more and about 2 kHz or less for at least some values of the setpoint signal or value 142. In this regard, the modulation is preferable performed at a frequency above about 100 Hz to avoid or mitigate undesirable user-perceptible flicker in the light output provided by the OLED sources 102. Pulsed dimming, moreover, advantageously avoids color shift typically experienced with linear dimming techniques in which non-modulated DC current levels are adjusted to dim

the light output. In addition, pulsed dimming of OLED devices 102 eliminates the problem of individual portions of the device turning off before others when linearly dimmed.

[0017] The controller 140, moreover, provides ramped pulse modulation (RPM) signals 144 to the DC source 130 for at least some values of a setpoint signal or value 142. In this regard, the inventors have appreciated that OLED type and other large area solid-state lighting devices 102 may be of substantial capacitance, and further that such devices 102 may be susceptible to excessive current surges during transitions between driven current levels in pulsed dimming situations. Absent the novel RPM driving techniques employed by the controller 140, fast changes to the drive current  $I_{OUT}$  could lead to a high current spike (including current overshoot and undershoot conditions) due to the capacitive load 102. Such excessive current transitions (high  $di/dt$  at the output 112) may degrade the OLED 102 by dissociating the organic interface, leading to reduced operational lifetime, lumen degradation, color shift, and/or early device failure. Thus, while modulated dimming *per se* helps to combat color shift, the large capacitance causes a spike in the current for every on and off cycle of traditional pulsed dimming methods. This can damage the device 102 and lead to very poor lumen depreciation, color shifting, and ultimately to device failure. The RPM dimming provided by the controller 140 allows for 0 to 100% dimming capability while maintaining color uniformity over all light levels without premature device degradation. RPM allows the use of all pulsed modulation methods in large area OLED devices to gain these benefits without the damages normally caused by traditional pulsing methods.

[0018] Ramped Pulse Modulation (RPM) advantageously controls the  $dv/dt$  and the resulting  $di/dt$  for every switching cycle of the pulse modulation dimming, and may be used with any form of pulse modulation. In this regard, the controller 140 controls the ramp up and ramp down times ( $t_{up}$ ,  $t_{down}$  in Figs. 3A-3H below) of each transition between levels (each switching event) independent of the method of modulation. In some embodiments, a trapezoid modulation shape is used with transition times in both directions being maintained at about 1 ms, but other forms of wave shapes, transition profiles, etc. may be

used, in which the transition times are controlled to be within about 100  $\mu$ s and 2 ms. In this manner, the controller 140 limits the  $di/dt$  experienced by the OLED devices 102 and thus controls the size of the current spike induced by attempting to change the voltage quickly. In this regard, conventional pulse modulation efforts were directed to instead minimizing the transition time in order to optimize efficiency in the DC source 130. The controller 140 of the present disclosure, on the other hand, actively enforces limitations on the rise and fall times of the drive current  $I_{OUT}$  in order to mitigate the above mentioned problems of OLED degradation, color shift, perceptible flicker, etc. In practice, the controller 140 can achieve these goals by means of the control input 144 using any suitable wave shapes to limit  $dv/dt$  and the resultant  $di/dt$ , such as linear transitions, non-linear transitions, exponential or logarithmic curve transitions, s-curve transitions, etc. Moreover, digital implementations of the controller 140 can provide discrete steps in the control input 144 to transition from state to state, preferably having a large enough number of discrete levels of sufficient duration such that the end result was a close approximation of the slowly changing analog transition of states.

[0019] Referring also to Figs. 3A-3H, the pulsed modulation control of the switch-mode DC current source 130 provides ramped pulse modulation implemented by the controller 140 over all or at least a portion of the range of the dimming level setpoint 142. In this regard, the controller 140 provides the control input 144 as a pulse modulated waveform having transitions between at least two control input values with controlled increasing (rising) profiles having a rise time value  $t_{up}$  of about 100  $\mu$ s or more and about 2 ms or less between control input values and with controlled decreasing (falling) profiles having a fall time value  $t_{down}$  of about 100  $\mu$ s or more and about 2 ms or less between control input values. In some embodiments, the rise time value  $t_{up}$  and the fall time value  $t_{down}$  are the same, for example, with the rise time value  $t_{up}$  and the fall time value  $t_{down}$  being within about +/- 2% of 1 ms. In other embodiments, the rise time value  $t_{up}$  and the fall time value  $t_{down}$  are unequal, where the rise time value  $t_{up}$  in some cases can be longer than the fall time value  $t_{down}$  and in other examples the rise time value  $t_{up}$  is shorter than the fall time value  $t_{down}$ . In

some embodiments, moreover, one or both of the increasing profile and the decreasing profile can be linear (e.g., substantially straight transition as a function of time), and in other embodiments, at least a portion of one or both of the increasing profile and the decreasing profile is nonlinear.

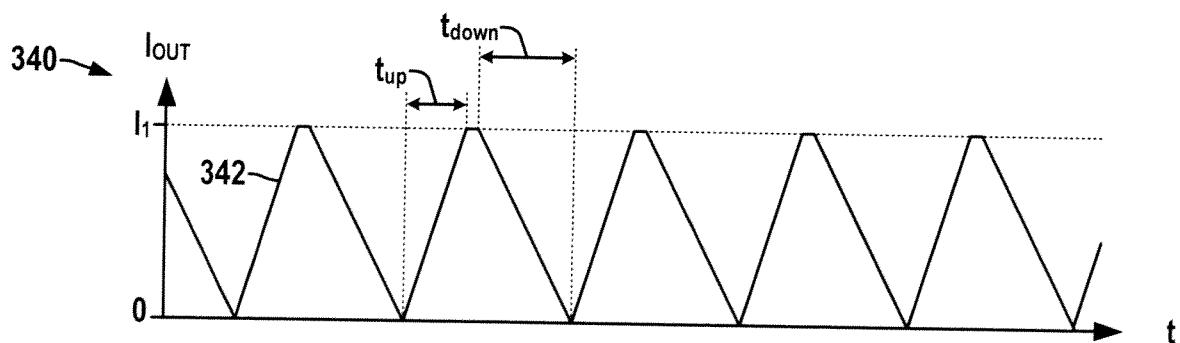

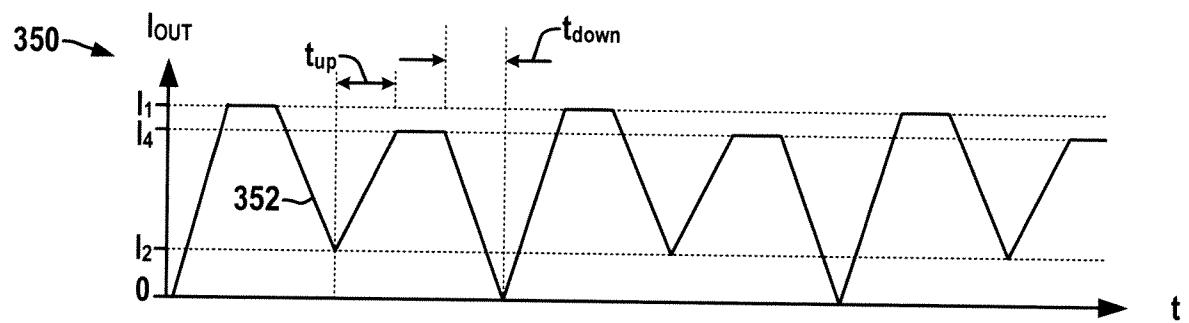

[0020] Figs. 3A-3H provide several non-exhaustive examples of possible ramped pulse modulation in the drivers 100 above, in which the examples are shown for some non-100% value of the dimming level setpoint 142. Figs. 3A-3C provide graphs 300, 310, and 320, respectively, showing a driver output current ( $I_{OUT}$ ) curves 302, 312, and 322 as a function of time in which the controller 140 modulates either the buck converter control input or an output switch 132b to generate an output current that varies between a first current level  $I_1$  and a second lower level  $I_2$  with linear rising and falling transitions of generally equal durations  $t_{up}$  and  $t_{down}$  between about 100  $\mu$ s and 2. The modulation techniques in these examples may provide for non-zero dwell times at one or both levels  $I_1$  and  $I_2$ , although not a strict requirement, wherein one or both levels may involve zero dwell times (e.g., Fig. 3C) and wherein the dwell times may vary according to the value of the dimming setpoint 142. Moreover, the upper and lower current levels  $I_1$  and  $I_2$  may, but need not correspond to the 0% and 100% output levels of the source 130.

[0021] The graphs 330 and 340 in Figs. 3D and 3E illustrate examples in which the waveform output curves 332 and 342 have unequal rising and falling durations  $t_{up}$  and  $t_{down}$ . As shown in graph 350 of Fig. 3F, moreover, the curve ramped modulation waveform 352 may involve transitions to and from any number of different current levels  $I_1$ - $I_4$ .

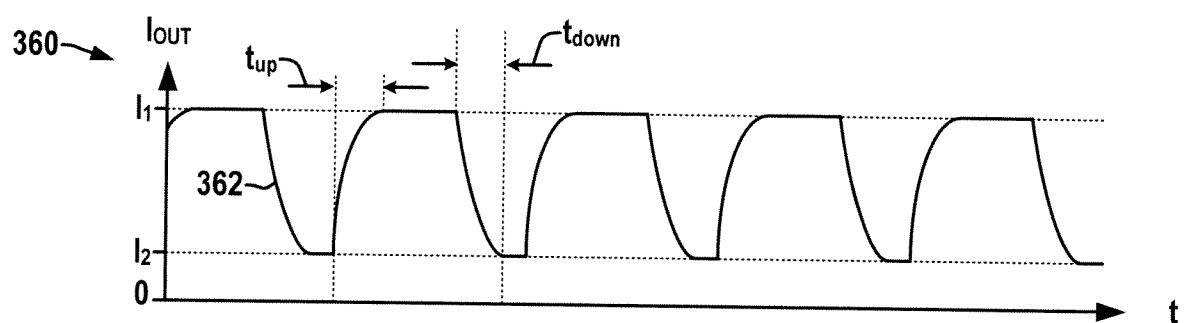

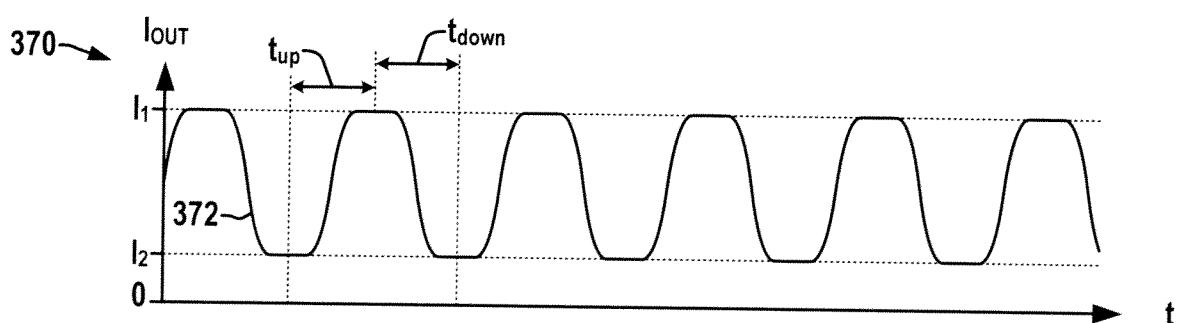

[0022] Other exemplary embodiments are shown in the graphs 360 and 370 of Figs. 3G and 3H, in which exponential, logarithmic, and/or s-shaped transition profiles may be used, preferably having smooth (i.e., low  $di/dt$ ) portions near the ends of the transitions to alleviate current overshoot and/or undershoot, wherein the transitions may, but need not, include linear portions, and wherein the transition times  $t_{up}$  and  $t_{down}$  may, but need not, be equal. The curve 362 in Fig. 3G, for example, provides rising and falling transitions having

logarithmic profiles in which the rates of change decrease at the ends of the transitions. The curve 372 in Fig. 3H includes s-shaped rising and falling transition profiles where the illustrated modulation level/technique includes non-zero dwell times at the first and second current levels  $I_1$  and  $I_2$ , where other examples (or other modulation levels of the same embodiment) need not have non-zero dwell times at one or both levels  $I_1$  and  $I_2$ , such that the modulation may become wholly or partially sinusoidal.

[0023] The above examples are merely illustrative of several possible embodiments of various aspects of the present disclosure, wherein equivalent alterations and/or modifications will occur to others skilled in the art upon reading and understanding this specification and the annexed drawings. In particular regard to the various functions performed by the above described components (assemblies, devices, systems, circuits, and the like), the terms (including a reference to a "means") used to describe such components are intended to correspond, unless otherwise indicated, to any component, such as hardware, software, or combinations thereof, which performs the specified function of the described component (i.e., that is functionally equivalent), even though not structurally equivalent to the disclosed structure which performs the function in the illustrated implementations of the disclosure. In addition, although a particular feature of the disclosure may have been illustrated and/or described with respect to only one of several implementations, such feature may be combined with one or more other features of the other implementations as may be desired and advantageous for any given or particular application. Furthermore, references to singular components or items are intended, unless otherwise specified, to encompass two or more such components or items. Also, to the extent that the terms "including", "includes", "having", "has", "with", or variants thereof are used in the detailed description and/or in the claims, such terms are intended to be inclusive in a manner similar to the term "comprising". The invention has been described with reference to the preferred embodiments. Obviously, modifications and alterations will occur to others upon reading and understanding the preceding detailed description. It is intended that the invention be construed as including all such modifications and alterations.

The following is claimed:

1. An electronic driver apparatus for powering one or more large area solid-state light sources, the driver apparatus comprising:

- a DC current source operative to provide DC electrical current to power at least one large area solid-state light source according to a control input;

- a controller operative for at least some values of a setpoint signal or value to provide a pulse modulated control input to the current source according to the setpoint signal or value, the controller providing the control input as a pulse modulated waveform having transitions between at least two control input values with controlled increasing profiles having a rise time value of about 100  $\mu$ s or more and about 2 ms or less between control input values and with controlled decreasing profiles having a fall time value of about 100  $\mu$ s or more and about 2 ms or less between control input values.

2. The electronic driver apparatus of claim 1, wherein the rise time value and the fall time value are the same.

3. The electronic driver apparatus of claim 2, wherein the rise time value and the fall time value are about 1 ms.

4. The electronic driver apparatus of claim 3, wherein at least one of the increasing profile and the decreasing profile is linear.

5. The electronic driver apparatus of claim 3, wherein at least a portion of at least one of the increasing profile and the decreasing profile is nonlinear.

6. The electronic driver apparatus of claim 5, wherein at least a portion of both the increasing profile and the decreasing profile is nonlinear.

7. The electronic driver apparatus of claim 1, further comprising a feedback circuit operative to sense the DC electrical current provided to the at least one large area solid-state light source and to provide a feedback signal to the controller indicative of the DC electrical current provided to the at least one large area solid-state light source, wherein the controller provide a pulse modulated control input to the current source at least partially according to the feedback signal for at least some values of the setpoint signal or value.

8. The electronic driver apparatus of claim 1, wherein the rise time value and the fall time value are unequal.

9. The electronic driver apparatus of claim 8, wherein the rise time value is longer than the fall time value.

10. The electronic driver apparatus of claim 8, wherein the rise time value is shorter than the fall time value.

11. The electronic driver apparatus of claim 8, wherein at least one of the increasing profile and the decreasing profile is linear.

12. The electronic driver apparatus of claim 8, wherein at least a portion of at least one of the increasing profile and the decreasing profile is nonlinear.

13. The electronic driver apparatus of claim 1, wherein the controller provides the pulse modulated control input to the current source at a modulation frequency of about 100 Hz or more and about 2kHz or less for at least some values of the setpoint signal or value.

14. The electronic driver apparatus of claim 1, wherein at least one of the increasing profile and the decreasing profile is linear.

15. The electronic driver apparatus of claim 1, wherein at least a portion of at least one of the increasing profile and the decreasing profile is nonlinear.

16. A method of powering at least one large area solid-state light source, the method comprising:

controlling a DC current source to provide DC electrical current to power at least one large area solid-state light source according to a control input;

for at least some values of a setpoint signal or value, providing a pulse modulated control input to the current source according to the setpoint signal or value as a pulse modulated waveform having transitions between at least two control input values with controlled increasing profiles having a rise time value of about 100  $\mu$ s or more and about 2 ms or less between control input values and with controlled decreasing profiles having a fall time value of about 100  $\mu$ s or more and about 2 ms or less between control input values.

17. The method of claim 16, wherein the rise time value and the fall time value are about 1 ms.

18. The method of claim 16, wherein the rise time value and the fall time value are unequal.

19. The method of claim 16, wherein at least one of the increasing profile and the decreasing profile is linear.

20. The method of claim 16, wherein at least a portion of at least one of the increasing profile and the decreasing profile is nonlinear.

1 / 5

FIG. 1A

2 / 5

FIG. 1B

3 / 5

FIG. 2

FIG. 3A

FIG. 3B

4 / 5

**FIG. 3C****FIG. 3D****FIG. 3E**

5 / 5

FIG. 3F

FIG. 3G

FIG. 3H

# INTERNATIONAL SEARCH REPORT

International application No

PCT/US2010/055971

**A. CLASSIFICATION OF SUBJECT MATTER**

INV. H05B33/08

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

H02M H05B G09G

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                        | Relevant to claim No. |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 4 325 021 A (MCMACKIN JOHN B)<br>13 April 1982 (1982-04-13)                                                                            | 1-3,5,6,<br>15-17,20  |

| Y         | the whole document                                                                                                                        | 4,7-14,<br>18,19      |

| Y         | -----<br>WO 2006/013035 A2 (TRIDONICATCO GMBH & CO<br>KG [AT]; BOECKLE REINHARD [AT]<br>TRIDONICATCO GMB)<br>9 February 2006 (2006-02-09) | 4,11,14,<br>19        |

| Y         | the whole document                                                                                                                        | -----                 |

| Y         | -----<br>GB 2 318 467 A (INT RECTIFIER CORP [US])<br>22 April 1998 (1998-04-22)                                                           | 8-12,18               |

| Y         | the whole document                                                                                                                        | -----                 |

| Y         | -----<br>US 2008/074060 A1 (YE BYOUNG-DAE [KR] ET<br>AL) 27 March 2008 (2008-03-27)                                                       | 7,13                  |

|           | the whole document                                                                                                                        | -----                 |

|           |                                                                                                                                           | -/-                   |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

"A" document defining the general state of the art which is not considered to be of particular relevance

"E" earlier document but published on or after the international filing date

"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

"O" document referring to an oral disclosure, use, exhibition or other means

"P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

"&" document member of the same patent family

|                                                           |                                                    |

|-----------------------------------------------------------|----------------------------------------------------|

| Date of the actual completion of the international search | Date of mailing of the international search report |

| 4 March 2011                                              | 25/03/2011                                         |

|                                                                                                                                                                      |                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| Name and mailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016 | Authorized officer<br><br>Gardella, Simone |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

**INTERNATIONAL SEARCH REPORT**

|                              |

|------------------------------|

| International application No |

| PCT/US2010/055971            |

C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                      | Relevant to claim No. |

|-----------|---------------------------------------------------------------------------------------------------------|-----------------------|

| A         | US 6 441 596 B1 (INOUE KOICHI [JP] ET AL)<br>27 August 2002 (2002-08-27)<br>the whole document<br>----- | 1-20                  |

| A         | US 2008/122758 A1 (KIM IN-HWAN [KR] ET AL)<br>29 May 2008 (2008-05-29)<br>the whole document<br>-----   | 1-20                  |

# INTERNATIONAL SEARCH REPORT

Information on patent family members

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2010/055971 |

|---------------------------------------------------|

| Patent document cited in search report | Publication date | Patent family member(s)                                                                                                     |  |                                                                                                |

|----------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------|--|------------------------------------------------------------------------------------------------|

| US 4325021                             | A 13-04-1982     | NONE                                                                                                                        |  |                                                                                                |

| WO 2006013035                          | A2 09-02-2006    | AT 489764 T<br>AU 2005268968 A1<br>CN 101002388 A<br>DE 102004036958 A1<br>EP 1771934 A2<br>EP 2256927 A1<br>ZA 200700812 A |  | 15-12-2010<br>09-02-2006<br>18-07-2007<br>23-03-2006<br>11-04-2007<br>01-12-2010<br>25-09-2008 |

| GB 2318467                             | A 22-04-1998     | DE 19745218 A1<br>FR 2754958 A1<br>IT 1295361 B1<br>JP 3212924 B2<br>JP 10173500 A<br>TW 437084 B                           |  | 23-04-1998<br>24-04-1998<br>12-05-1999<br>25-09-2001<br>26-06-1998<br>28-05-2001               |

| US 2008074060                          | A1 27-03-2008    | KR 20080010948 A<br>US 2009134815 A1                                                                                        |  | 31-01-2008<br>28-05-2009                                                                       |

| US 6441596                             | B1 27-08-2002    | JP 3998394 B2<br>JP 2001251848 A                                                                                            |  | 24-10-2007<br>14-09-2001                                                                       |

| US 2008122758                          | A1 29-05-2008    | KR 20080048876 A                                                                                                            |  | 03-06-2008                                                                                     |