(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5634318号

(P5634318)

(45) 発行日 平成26年12月3日(2014.12.3)

(24) 登録日 平成26年10月24日(2014.10.24)

(51) Int.Cl.

F 1

H01L 29/78 (2006.01)

H01L 29/739 (2006.01)H01L 29/78 652 F

H01L 29/78 652 C

H01L 29/78 653 A

H01L 29/78 653 C

H01L 29/78 652 J

請求項の数 11 (全 29 頁) 最終頁に続く

(21) 出願番号

特願2011-93121(P2011-93121)

(22) 出願日

平成23年4月19日(2011.4.19)

(65) 公開番号

特開2012-227335(P2012-227335A)

(43) 公開日

平成24年11月15日(2012.11.15)

審査請求日

平成25年6月4日(2013.6.4)

(73) 特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人 110001195

特許業務法人深見特許事務所

(72) 発明者 大宅 大介

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72) 発明者 中村 勝光

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 土谷 慎吾

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

互いに対向する第1主面および第2主面を有する半導体基板と、

それが前記第1主面側に絶縁ゲート構造を有し、かつ前記第1主面に形成された第1導電型のエミッタ領域を有し、かつ前記第1主面と前記第2主面との間で主電流を流すための第1および第2の絶縁ゲート型電界効果トランジスタ部と、

前記第1および第2の絶縁ゲート型電界効果トランジスタ部に挟まれる前記第1主面の領域に形成された安定化プレート部と、

前記第1主面上に設けられたエミッタ電極とを備え、

前記安定化プレート部は、前記第1の絶縁ゲート型電界効果トランジスタ部の最も近くに配置された第1の安定化プレートと、前記第2の絶縁ゲート型電界効果トランジスタ部の最も近くに配置された第2の安定化プレートとを含み、

前記エミッタ電極は、前記第1および第2の絶縁ゲート型電界効果トランジスタ部の各々の前記エミッタ領域と電気的に接続され、かつ前記第1および第2の安定化プレートの各々と電気的に接続され、かつ前記第1および第2の安定化プレートに挟まれる前記第1主面の全面上において絶縁層を介在して配置されており、

前記第1および第2の絶縁ゲート型電界効果トランジスタ部の各々は、前記半導体基板の第1主面に形成された第2導電型のボディコンタクト領域と、ゲート電極とを含み、

前記第1および第2の安定化プレートの各々は、前記第1の絶縁ゲート型電界効果トランジスタ部の前記エミッタ領域およびボディコンタクト領域の形成領域と前記第2の絶縁

10

20

ゲート型電界効果トランジスタ部の前記エミッタ領域およびボディコンタクト領域の形成領域とに挟まれる領域から、前記挟まれる領域よりも前記ゲート電極の平面視における長手方向の端部側に位置する端部領域まで延びるように形成されており、

前記第1および第2の安定化プレートを繋ぐように前記第1主面上に前記絶縁層を介在して延在する導電層をさらに備え、

前記導電層は、前記端部領域に位置しており、

前記エミッタ電極は、前記挟まれる領域において前記第1および第2の安定化プレートの各々と直接的に接続されておらず、

前記エミッタ電極は、前記端部領域において少なくとも前記導電層と前記第1および第2の安定化プレートの各々とが重なる領域、および前記端部領域における前記第1の安定化プレートと前記第2の安定化プレートとの間に挟まれる領域において前記導電層を介して前記第1および第2の安定化プレートの各々と電気的に接続されている、半導体装置。

10

#### 【請求項2】

前記半導体基板の内部に形成された第1導電型領域と、

前記第1導電型領域の前記第1主面側に形成され、かつ前記ボディコンタクト領域よりも低い第2導電型の不純物濃度を有する第2導電型のボディ領域とをさらに備え、

前記第1および第2の安定化プレートの各々は、前記半導体基板の前記第1主面から前記ボディ領域を突き抜けて前記第1導電型領域に達するように形成された安定化プレート用溝の内部を埋め込むように形成されており、

前記第1および第2の絶縁ゲート型電界効果トランジスタ部の各々の前記ゲート電極は、前記半導体基板の前記第1主面から前記ボディ領域を突き抜けて前記第1導電型領域に達するように形成されたゲート用溝の内部を埋め込むように形成されている、請求項1に記載の半導体装置。

20

#### 【請求項3】

前記安定化プレート用溝は、前記第1の安定化プレートが埋め込むように形成されている第1安定化プレート用溝と、前記第2の安定化プレートが埋め込むように形成されている第2安定化プレート用溝とを含み、

前記第1安定化プレート用溝および前記第2安定化プレート用溝は、前記ゲート電極の長手方向に沿って延びるように形成されており、前記端部領域においてそれぞれ端部を有している、請求項2に記載の半導体装置。

30

#### 【請求項4】

前記安定化プレート用溝の数量を、前記ゲート用溝の数量と前記安定化プレート用溝の数量との合計数量で割った値をダミートレンチ比率とした場合、

前記ダミートレンチ比率は、0.5以上0.92以下である、請求項2または請求項3に記載の半導体装置。

#### 【請求項5】

前記ゲート用溝の深さ、および前記安定化プレート用溝の深さは、

前記第1導電型領域と前記ボディ領域との接合部から前記第2主面側に1.5μm以上である、請求項2～請求項4のいずれか1項に記載の半導体装置。

40

#### 【請求項6】

前記ゲート用溝の先端形状、および前記安定化プレート用溝の先端形状がラウンド形状である、請求項2～請求項5のいずれか1項に記載の半導体装置。

#### 【請求項7】

前記安定化プレート用溝と前記ゲート用溝とを含む複数のトレンチの各ピッチが互いに同じである、請求項2～請求項6のいずれか1項に記載の半導体装置。

#### 【請求項8】

前記第1導電型領域は、第1導電型の第1領域と、前記第1領域よりも前記第1主面側に形成されかつ前記第1領域よりも高い第1導電型の不純物濃度を有する第1導電型の第2領域とを含み、

前記安定化プレート用溝および前記ゲート用溝の双方は、前記第2領域を突き抜けて前

50

記第1領域に達するように形成されている、請求項2～請求項7のいずれか1項に記載の半導体装置。

**【請求項9】**

前記第1の安定化プレートと前記第2の安定化プレートとの間の前記第1正面に形成され、かつ前記ボディ領域よりも高い第2導電型の不純物濃度を有する第2導電型領域をさらに備えた、請求項2～請求項8のいずれか1項に記載の半導体装置。

**【請求項10】**

互いに対向する第1正面および第2正面を有する半導体基板と、

それぞれが前記第1正面側に絶縁ゲート構造を有し、かつ前記第1正面に形成された第1導電型のエミッタ領域を有し、かつ前記第1正面と前記第2正面との間で主電流を流すための第1および第2の絶縁ゲート型電界効果トランジスタ部と、

前記第1および第2の絶縁ゲート型電界効果トランジスタ部に挟まれる前記第1正面の領域に形成された安定化プレート部と、

前記第1正面に設けられたエミッタ電極とを備え、

前記安定化プレート部は、前記第1の絶縁ゲート型電界効果トランジスタ部の最も近くに配置された第1の安定化プレートと、前記第2の絶縁ゲート型電界効果トランジスタ部の最も近くに配置された第2の安定化プレートとを含み、

前記第1および第2の絶縁ゲート型電界効果トランジスタ部の各々は、前記半導体基板の第1正面に形成されたゲート電極と、複数の第2導電型のボディコンタクト領域とを含み、

前記エミッタ電極は、前記第1および第2の絶縁ゲート型電界効果トランジスタ部の各々の前記エミッタ領域および前記ボディコンタクト領域と電気的に接続され、かつ前記第1および第2の安定化プレートの各々と電気的に接続され、かつ前記第1および第2の安定化プレートに挟まれる前記第1正面の全面上において絶縁層を介在して配置されており

前記第1および第2の絶縁ゲート型電界効果トランジスタ部の各々において前記ゲート電極の平面視における長手方向に沿って前記複数のボディコンタクト領域が並んでおり、

前記第1および第2の安定化プレートを繋ぐように前記第1正面に前記絶縁層を介在して延在する導電層をさらに備え、

前記第1の絶縁ゲート型電界効果トランジスタ部の前記ゲート電極の平面視における長手方向の最端部に配置された前記ボディコンタクト領域と、前記第2の絶縁ゲート型電界効果トランジスタ部の前記ゲート電極の平面視における長手方向の最端部に配置された前記ボディコンタクト領域との間に挟まれる領域、および前記最端部に配置された前記ボディコンタクト領域の一部と重なる領域上において前記エミッタ電極は前記導電層を介して前記第1および第2の安定化プレートの各々と電気的に接続されており、

前記エミッタ電極は、前記第1および第2の絶縁ゲート型電界効果トランジスタ部の各々において、前記重なる領域以外の領域に位置する前記エミッタ領域および前記ボディコンタクト領域と電気的に接続されている、半導体装置。

**【請求項11】**

互いに対向する第1正面および第2正面を有する半導体基板と、

それぞれが前記第1正面側に絶縁ゲート構造を有し、かつ前記第1正面に形成された第1導電型のエミッタ領域を有し、かつ前記第1正面と前記第2正面との間で主電流を流すための第1および第2の絶縁ゲート型電界効果トランジスタ部と、

前記第1および第2の絶縁ゲート型電界効果トランジスタ部に挟まれる前記第1正面の領域に形成された安定化プレート部と、

前記第1正面に設けられたエミッタ電極とを備え、

前記安定化プレート部は、前記第1の絶縁ゲート型電界効果トランジスタ部の最も近くに配置された第1の安定化プレートと、前記第2の絶縊ゲート型電界効果トランジスタ部の最も近くに配置された第2の安定化プレートとを含み、

前記エミッタ電極は、前記第1および第2の絶縊ゲート型電界効果トランジスタ部の各

10

20

30

40

50

々の前記エミッタ領域と電気的に接続され、かつ前記第1および第2の安定化プレートの各々と電気的に接続され、かつ前記第1および第2の安定化プレートに挟まれる前記第1主面の全面上において絶縁層を介在して配置されており、

前記第1および第2の絶縁ゲート型電界効果トランジスタ部の各々は、前記半導体基板の第1主面に形成されたゲート電極と、複数の第2導電型のボディコンタクト領域とを含み、

前記第1および第2の絶縁ゲート型電界効果トランジスタ部の各々において前記ゲート電極の平面視における長手方向に沿って前記複数のボディコンタクト領域が並んでおり、

前記第1および第2の安定化プレートを繋ぐように前記第1主面上に前記絶縁層を介在して延在する導電層をさらに備え、

10

前記導電層は、前記第1安定化プレートから前記第1の絶縁ゲート型電界効果トランジスタ部側に、および前記第2安定化プレートから前記第2の絶縁ゲート型電界効果トランジスタ部側にそれぞれ突出するように形成されており、

前記第1の絶縁ゲート型電界効果トランジスタ部の前記ゲート電極の平面視における長手方向に沿って並んだ前記複数のボディコンタクト領域のうち最端部に配置された前記ボディコンタクト領域以外の前記ボディコンタクト領域と、前記第2の絶縁ゲート型電界効果トランジスタ部の前記ゲート電極の平面視における長手方向に沿って並んだ前記複数のボディコンタクト領域のうち最端部に配置された前記ボディコンタクト領域以外の前記ボディコンタクト領域との間に挟まれる領域において前記エミッタ電極は前記導電層を介して前記第1および第2の安定化プレートの各々と電気的に接続されており、

20

前記エミッタ電極と前記第1および第2の安定化プレートとが電気的に接続されている部分と、前記エミッタ電極と前記エミッタ領域とが電気的に接続されている部分とは、連なるように形成されている、半導体装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体装置に関し、特に、半導体基板の互いに対向する主面の間で主電流を流すための少なくとも2つの絶縁ゲート型電界効果トランジスタ部を有する半導体装置に関するものである。

#### 【背景技術】

30

#### 【0002】

数百Vを超える電圧を制御する高耐圧半導体装置の分野では、その取扱う電流も大きいことから、発熱、すなわち損失を抑えた素子特性が要求される。また、それらの電圧・電流を制御するゲートの駆動方式としては、駆動回路が小さく、そこでの損失の小さな電圧駆動素子が望ましい。

#### 【0003】

現在、上記のような理由で、この分野では電圧駆動が可能で、損失の少ない素子として、絶縁ゲートバイポーラトランジスタ、すなわちIGBT(Insulated Gate Bipolar Transistor)が主流となっている。このIGBTの構造は、MOS(Metal Oxide Semiconductor)トランジスタのドレインの不純物濃度を低くして耐圧を保たせるとともに、ドレイン抵抗を低くするためにドレイン側をダイオードとしたものとみなすことができる構造である。

40

#### 【0004】

このようなIGBTにおいてはダイオードがバイポーラ動作をするため、本明細書においては、IGBTのMOSトランジスタのソースをエミッタと呼び、ドレイン側をコレクタ側と呼ぶ。

#### 【0005】

電圧駆動素子であるIGBTでは一般に、コレクタとエミッタとの間に数百Vの電圧が印加され、その電圧が±数V~数十Vのゲート電圧によって制御される。IGBTはインバータの中のスイッチング素子として用いられることが多い。IGBTがオン状態にある

50

場合にはコレクタ・エミッタ間に大電流が流れ、コレクタ・エミッタ間の電圧は低くなる。IGBTがオフ状態にある場合には、コレクタ・エミッタ間にほとんど電流は流れずコレクタ・エミッタ間の電圧は高くなる。

#### 【0006】

通常は、上記のようにIGBTの動作が行なわれるため、IGBTにおける損失は、オン状態での電流・電圧積である定常損失と、オン状態とオフ状態とが切り替わる過渡時のスイッチング損失とに分けられる。オフ状態でのリーク電流・電圧積は非常に小さいため無視することができる。

#### 【0007】

一方、例えば負荷が短絡した場合など異常な状態にあっても、素子の破壊を防ぐことも重要である。このような場合は、コレクタ・エミッタ間に数百Vの電源電圧が印加されたまま、ゲートがオンし、大電流が流れることになる。

10

#### 【0008】

MOSトランジスタとダイオードとを直列に接続した構造を持つIGBTでは、MOSトランジスタの飽和電流で最大電流が制限される。このため、上記のような短絡時にも電流制限が働き、一定の時間内であれば発熱による素子の破壊を防ぐことができる。

#### 【0009】

近年のIGBTでは、さらに損失を小さくするため、素子の表面に溝を形成しその中にゲート電極を埋込んだトレーニングートを採用したトレーニングート型IGBTが主流となりつつある（例えば、特許文献1から特許文献6を参照）。トレーニングート型IGBTは、MOSトランジスタ部分の微細化を行なった素子であるため、ゲート容量が大きくなっている。また短絡時に飽和電流が非常に大きくなるため、発熱が大きく短い時間で破壊してしまう傾向にある。

20

#### 【0010】

さらに、近年、例えば非特許文献1に記載のように、IGBTの帰還容量に起因し、短絡時にゲート電圧、ゲート電流、コレクタ／エミッタ電圧、およびコレクタ電流に発振が生じ、誤動作を引き起こす現象が知られている。このような帰還容量に起因した発振現象は、トレーニングート型IGBTのような、ゲート容量の大きな素子では深刻な問題となっている。

#### 【0011】

30

これらの問題に対しては、ゲート電極に電気的接続を行わないトレーニングートであるダミートレーニングートを用いることで、ゲート容量を抑制する構造が提案されている。また、特許文献7には、短絡時の発振を抑制することを可能とする構造が提案されている。

#### 【先行技術文献】

#### 【特許文献】

#### 【0012】

【特許文献1】特開平9-331063号公報

【特許文献2】特開平8-167711号公報

【特許文献3】特開平11-330466号公報

【特許文献4】特開2010-10556号公報

40

【特許文献5】特開2002-16252号公報

【特許文献6】特開2001-244325号公報

【特許文献7】国際公開第02/058160号

#### 【非特許文献】

#### 【0013】

【非特許文献1】Proceedings of 1998 International Symposium on Power Semiconductor Devices & ICs, p.89

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0014】

50

上記の従来例では、トレンチゲート型IGBT等の高耐圧半導体装置において、短絡時の発振抑制を目的としてダミートレンチ（以下、安定化プレートまたは安定化プレート用溝ともいう）の割合を増やしていくと、オン電圧（ $V_{ce(sat)}$ ）および定常損失が増加してしまうため、十分にダミートレンチを増やすことができないという問題がある。

#### 【0015】

本発明は、上記のような課題を鑑みてなされたものであり、その目的は、短絡時の発振抑制を目的として安定化プレート用溝の割合を増やしても、オン電圧を小さくでき、かつ短絡耐量の向上が容易な半導体装置を提供することである。

#### 【課題を解決するための手段】

#### 【0016】

本発明の半導体装置は、半導体基板と、第1および第2の絶縁ゲート型電界効果トランジスタ部と、安定化プレート部と、エミッタ電極とを備えている。半導体基板は、互いに対向する第1主面および第2主面を有している。第1および第2の絶縁ゲート型電界効果トランジスタ部は、それぞれが第1主面側に絶縁ゲート構造を有し、かつ第1主面に形成された第1導電型のエミッタ領域を有し、かつ第1主面と第2主面との間で主電流を流すためのものである。安定化プレート部は、第1および第2の絶縁ゲート型電界効果トランジスタ部に挟まれる第1主面の領域に形成されている。エミッタ電極は、第1主面上に設けられている。安定化プレート部は、第1の絶縁ゲート型電界効果トランジスタ部の最も近くに配置された第1の安定化プレートと、第2の絶縁ゲート型電界効果トランジスタ部の最も近くに配置された第2の安定化プレートとを含んでいる。エミッタ電極は、第1および第2の絶縁ゲート型電界効果トランジスタ部の各々のエミッタ領域と電気的に接続され、かつ第1および第2の安定化プレートに挟まれる第1主面の全面上において絶縁層を介在して配置されている。第1および第2の絶縁ゲート型電界効果トランジスタ部の各々は、半導体基板の第1主面に形成された第2導電型のボディコンタクト領域と、ゲート電極とを含み、第1および第2の安定化プレートの各々は、第1の絶縁ゲート型電界効果トランジスタ部のエミッタ領域およびボディコンタクト領域の形成領域と第2の絶縁ゲート型電界効果トランジスタ部のエミッタ領域およびボディコンタクト領域の形成領域とに挟まれる領域から、挟まれる領域よりもゲート電極の平面視における長手方向の端部側に位置する端部領域まで延びるように形成されている。第1および第2の安定化プレートを繋ぐように第1主面上に絶縁層を介在して延在する導電層をさらに備える。導電層は、端部領域に位置している。エミッタ電極は、挟まれる領域において第1および第2の安定化プレートの各々と直接的に接続されていない。エミッタ電極は、端部領域において少なくとも導電層と第1および第2の安定化プレートの各々とが重なる領域、および端部領域における第1の安定化プレートと第2の安定化プレートとの間に挟まれる領域において導電層を介して第1および第2の安定化プレートの各々と電気的に接続されている。

#### 【発明の効果】

#### 【0017】

本発明によれば、エミッタ電極は、第1および第2の安定化プレートに挟まれる第1主面の全面上において絶縁層を介在して配置されている。つまりエミッタ電極は、第1および第2の安定化プレートに挟まれる第1主面にはコンタクトホールを通じて接続されてはいない。このため、オン状態において電流は安定化プレート部にはほとんど流れず、絶縁ゲート型電界効果トランジスタ部に集中して流れることとなり、オン電圧が低くなる。

#### 【0018】

また、本発明の半導体装置における安定化プレートとエミッタ電極の接続構造により、トランジスタ部の微細化が可能となる。このため、トランジスタ部へ電流がさらに集中して流れオン電圧をさらに低くすることができる。半導体装置の微細化が可能となるため、安定化プレート用溝の割合を容易に増加することができる。このため、さらにオン電圧を低減することが可能となるとともに、実効的なゲート幅を低減することも容易となり飽和電流を減少させ短絡耐量を向上させることができる。また、本発明の半導体装置における

10

20

30

40

50

安定化プレートとエミッタ電極の接続構造によれば、半導体装置を微細化しても安定化プレートをエミッタ電位とすることができますため、ゲート容量を小さくでき短絡時の発振抑制が可能となる。

**【0019】**

以上より、オン電圧を小さくでき、さらに短絡耐量の向上が容易な半導体装置を得ることが可能となる。

**【図面の簡単な説明】**

**【0020】**

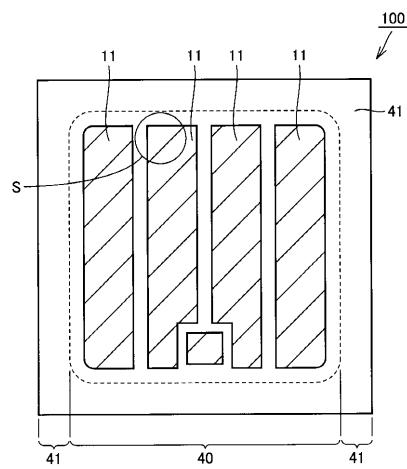

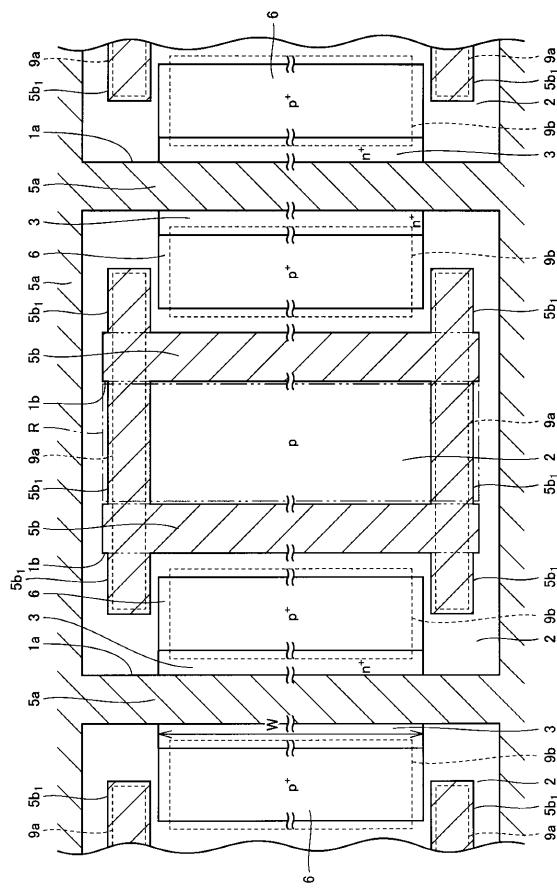

【図1】本発明の実施の形態1における半導体装置のチップ状態の構成を模式的に示す概略平面図である。

10

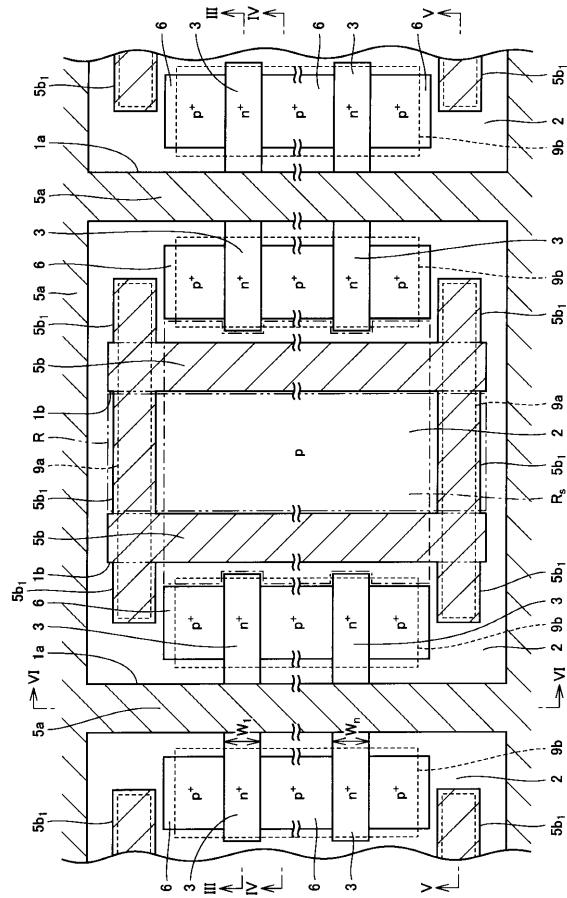

【図2】図1の領域Sを拡大して示す、本発明の実施の形態1における半導体装置の構成を概略的に示す部分平面図である。

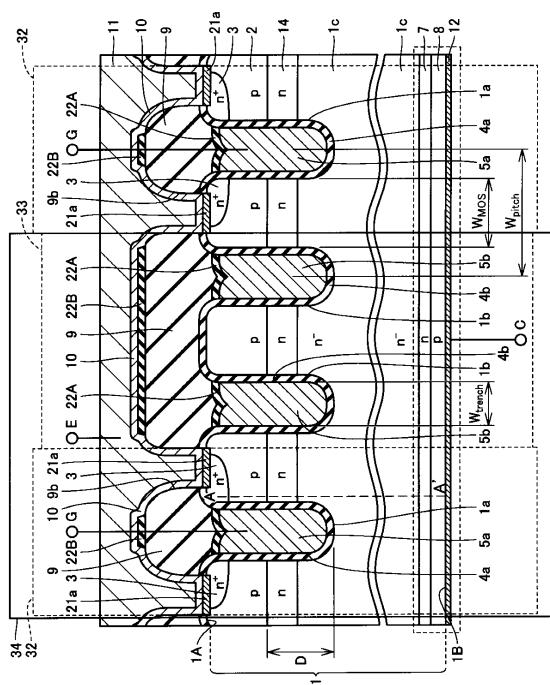

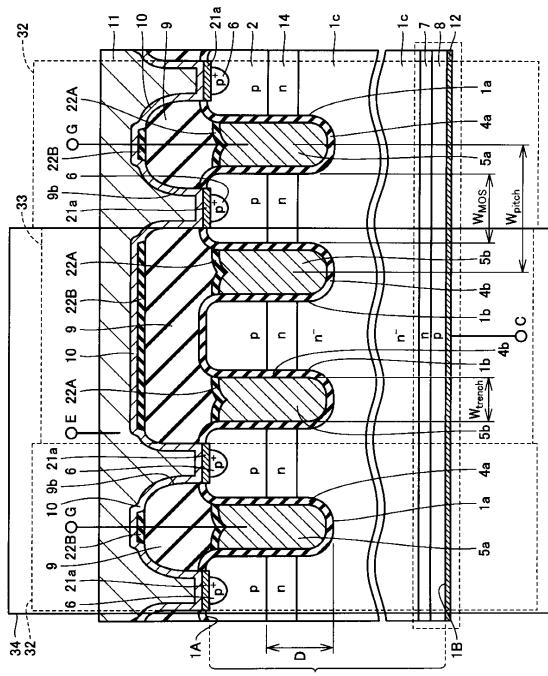

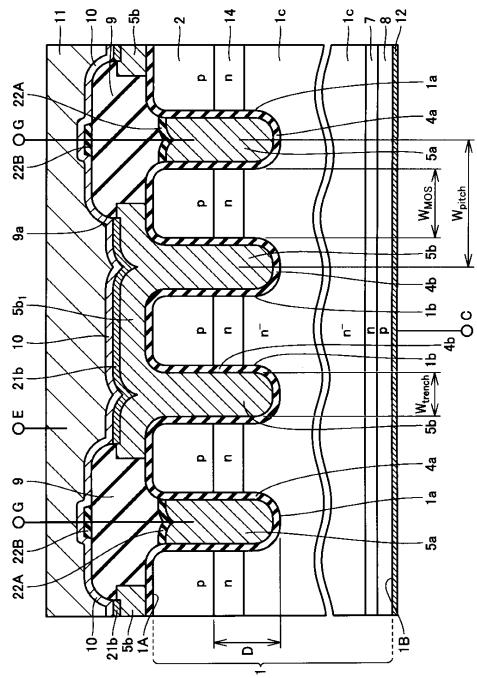

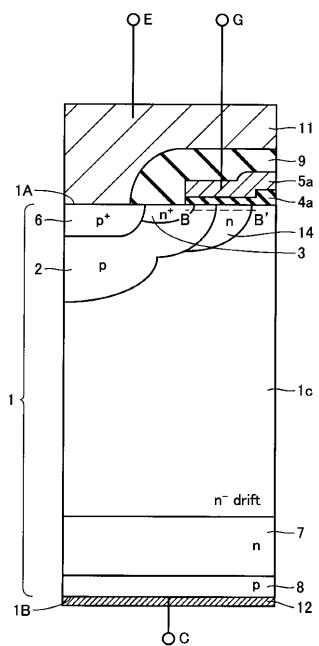

【図3】図2中のIII-I线に沿う矢視断面図である。

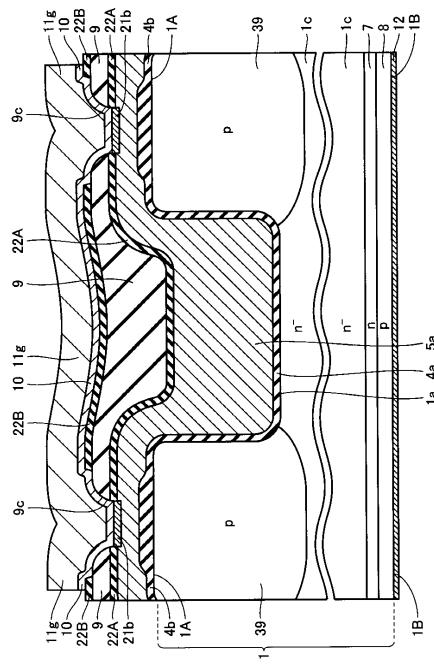

【図4】図2中のIV-I线に沿う矢視断面図である。

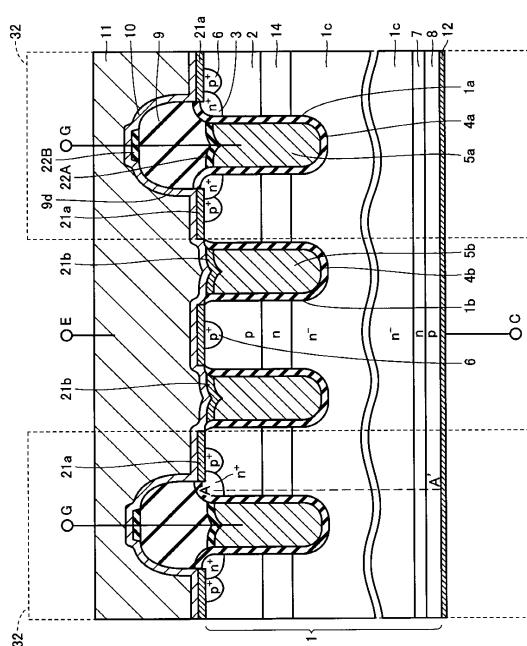

【図5】図2中のV-V线に沿う矢視断面図である。

【図6】図2中のVI-VI线に沿う矢視断面図である。

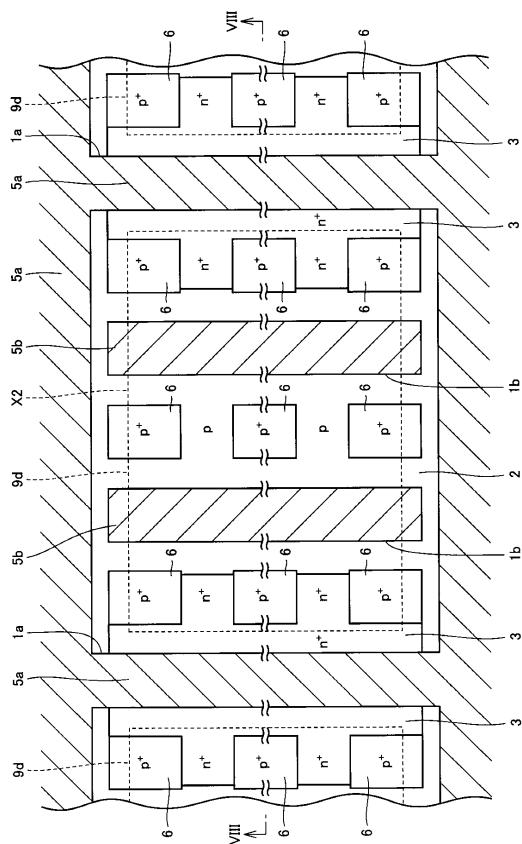

【図7】比較例における半導体装置の構成を概略的に示す部分平面図である。

【図8】図7中のVII-VII线に沿う矢視断面図である。

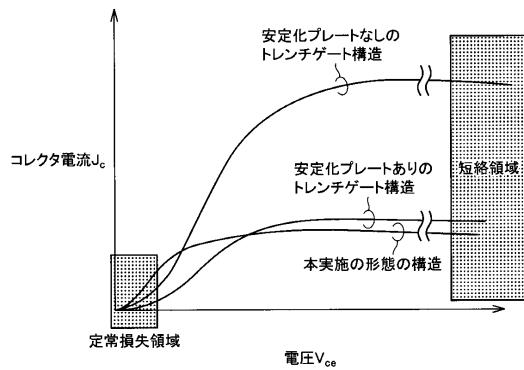

【図9】飽和電流とオン電圧との関係を示す図である。

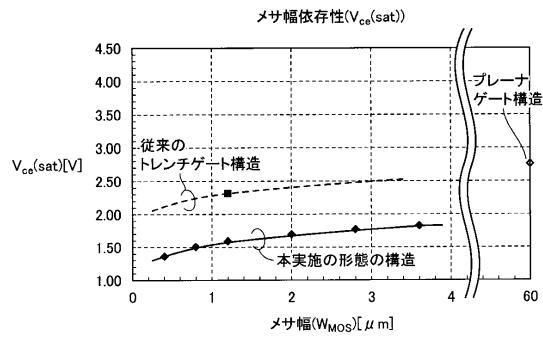

【図10】オン電圧低減効果のメサ幅依存性を示す図である。

20

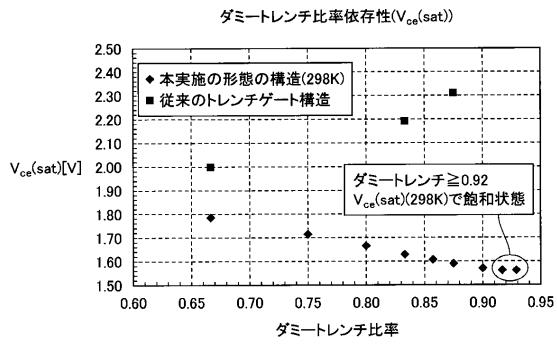

【図11】安定化プレート用溝比率とオン電圧との関係を示す図である。

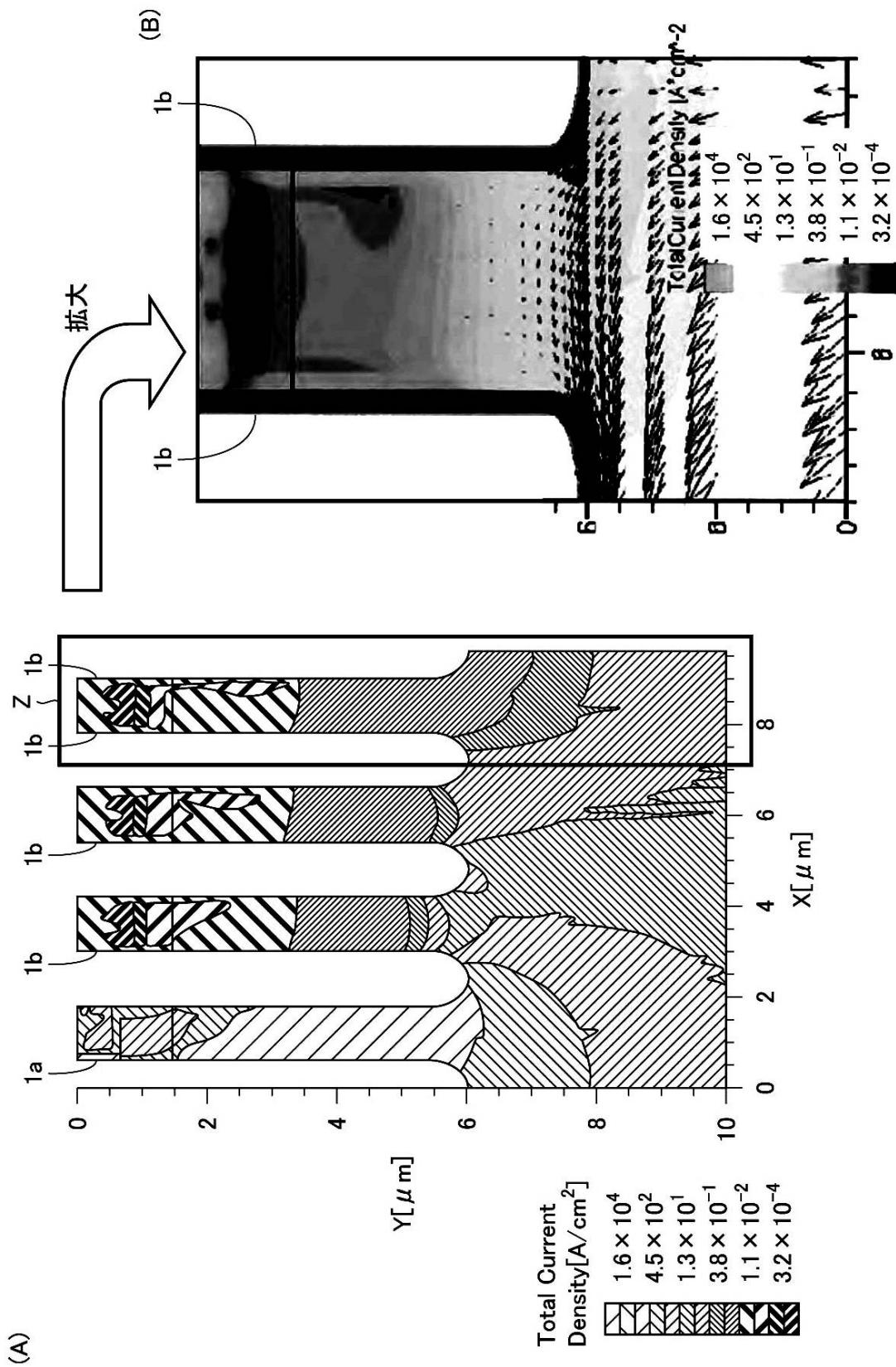

【図12】本発明の実施の形態1における半導体装置のデバイス内の電流密度(A)と電流経路(B)とを示す図である。

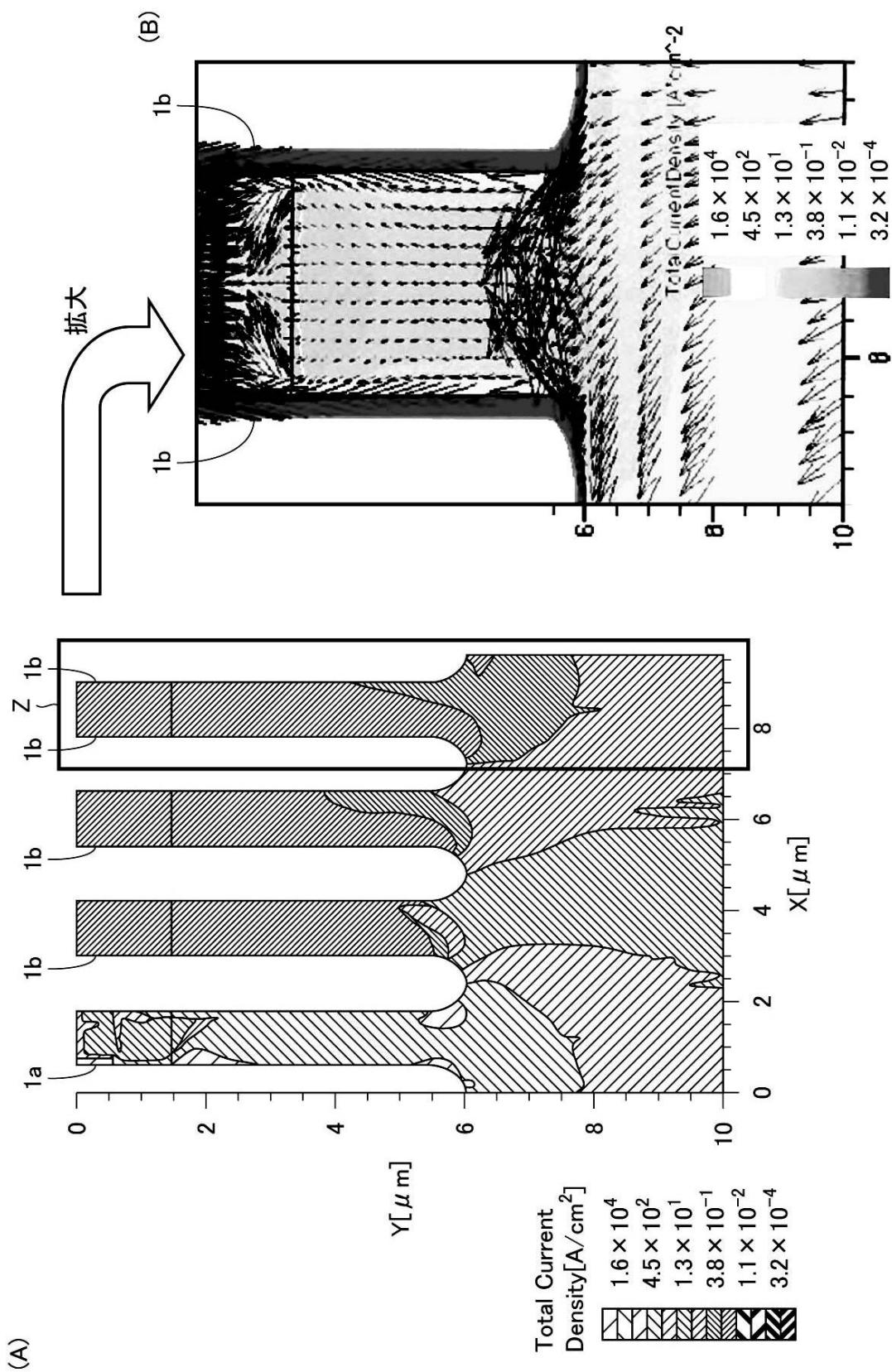

【図13】比較例における半導体装置のデバイス内の電流密度(A)と電流経路(B)とを示す図である。

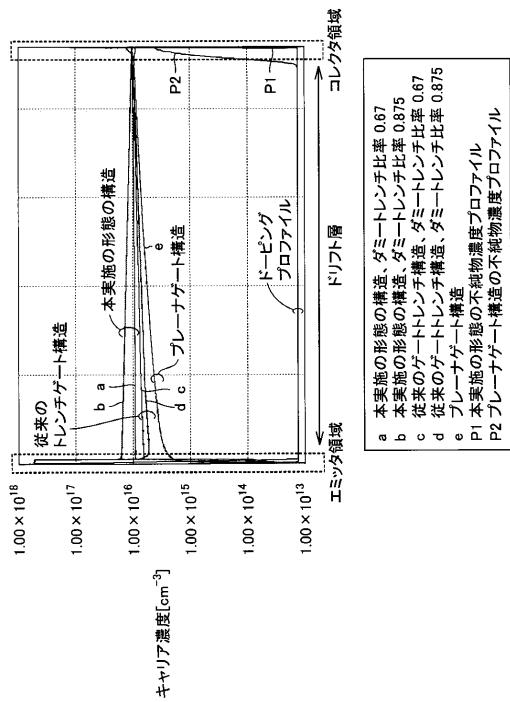

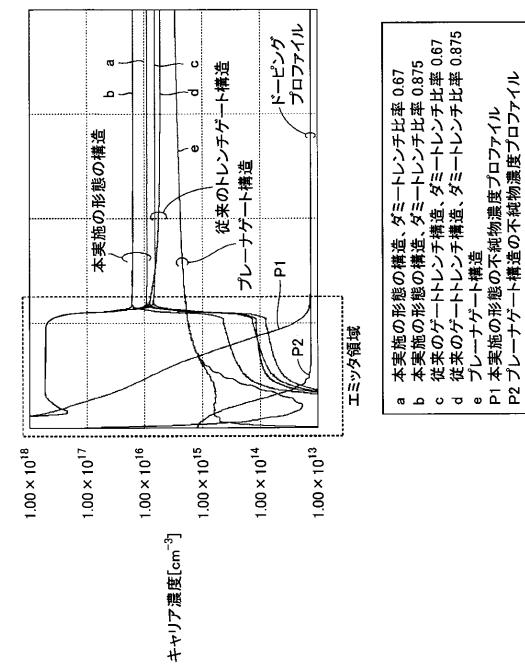

【図14】各デバイス構造におけるキャリア濃度分布を示す図である。

【図15】図14中のエミッタ領域側の拡大図である。

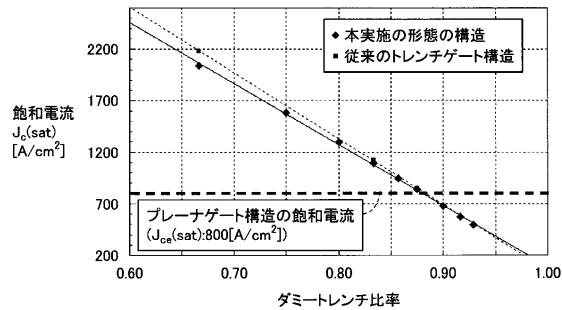

【図16】安定化プレート用溝比率と飽和電流との関係を示す図である。

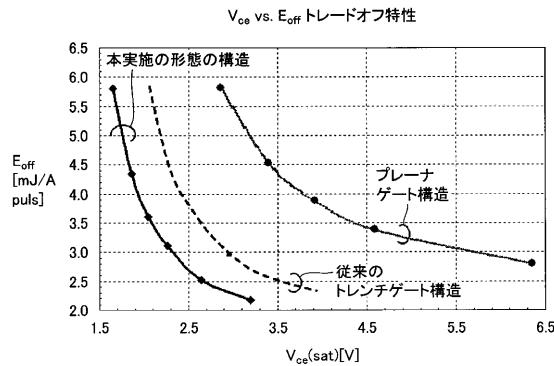

【図17】オン電圧Vce(sat)とスイッチング損失Eoffとの関係を示す図である。

30

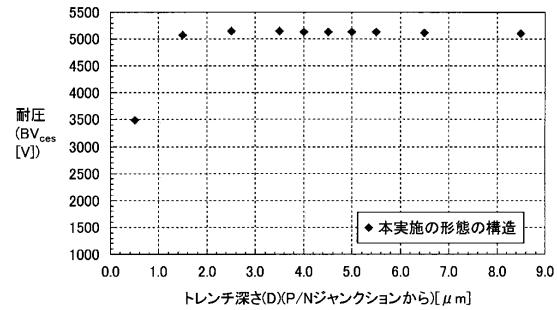

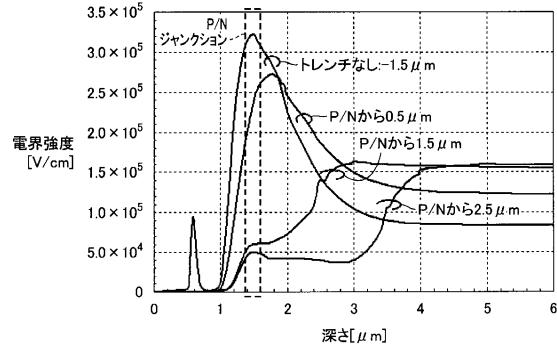

【図18】P/Nジャンクションからのトレンチ深さと耐圧との関係を示す図である。

【図19】深さ方向の電界強度分布を示す図である。

【図20】P/Nジャンクションからのトレンチ深さとオン電圧との関係を示す図である。

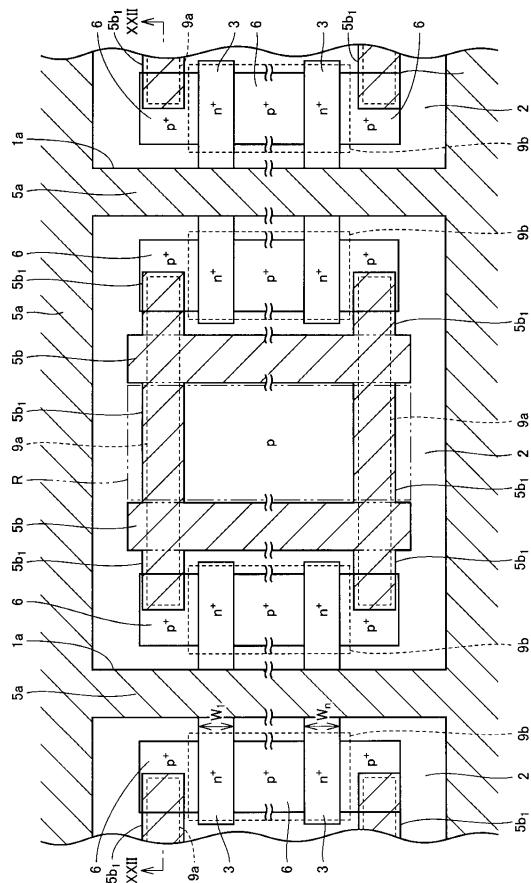

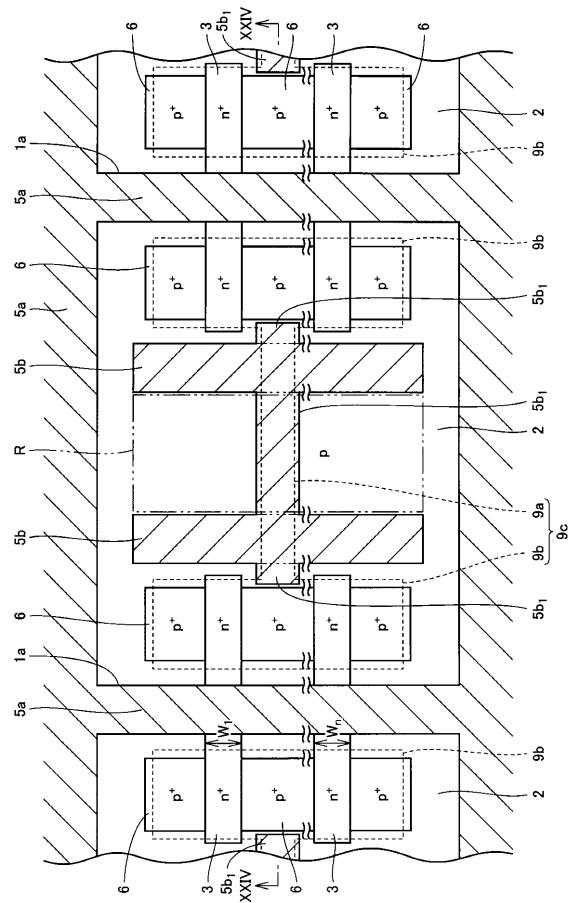

【図21】エミッタ電極とダミートレンチ内の導電層5b<sub>1</sub>との電気的接続のためのコンタクトホールをp<sup>+</sup>不純物拡散領域6の間に挟まれる領域に配置した構成の本発明の一実施の形態における半導体装置の一の変形例を概略的に示す部分平面図である。

【図22】図21中のXXII-XII线に沿う矢視断面図である。

【図23】エミッタ電極とダミートレンチ内の導電層5b<sub>1</sub>との電気的接続のためのコンタクトホールをp<sup>+</sup>不純物拡散領域6の間に挟まれる領域に配置した構成の本発明の一実施の形態における半導体装置の他の変形例を概略的に示す部分平面図である。

40

【図24】図23中のXXIV-XIV线に沿う矢視断面図である。

【図25】他の実施の形態における半導体装置の構成を示す概略平面図である。

【図26】さらに他の実施の形態における半導体装置の構成を示す概略平面図である。

【図27】さらに他の実施の形態における半導体装置の構成を示す概略平面図である。

【図28】プレーナーゲート構造のIGBTの断面図である。

**【発明を実施するための形態】**

**【0021】**

本発明に基づいた実施の形態における半導体装置について、以下、図を参照しながら説明する。なお、以下に説明する実施の形態において、個数、量などに言及する場合、特に

50

記載がある場合を除き、本発明の範囲は必ずしもその個数、量などに限定されない。また、同一の部品、相当部品に対しては、同一の参照番号を付し、重複する説明は繰り返さない場合がある。

〔 0 0 2 2 〕

### ( 実施の形態 1 )

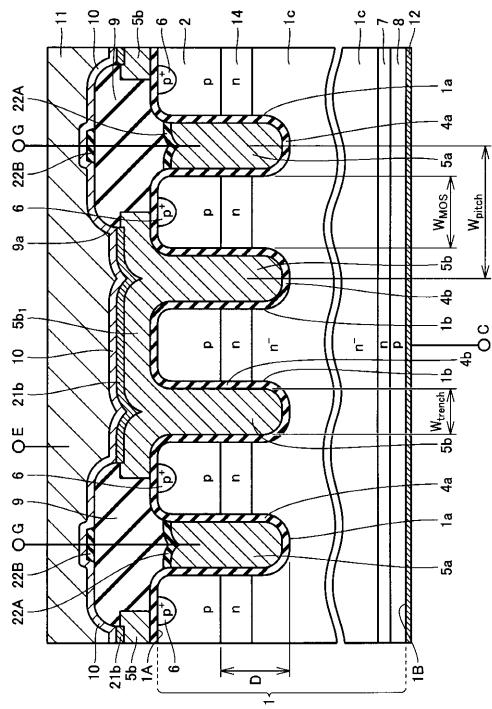

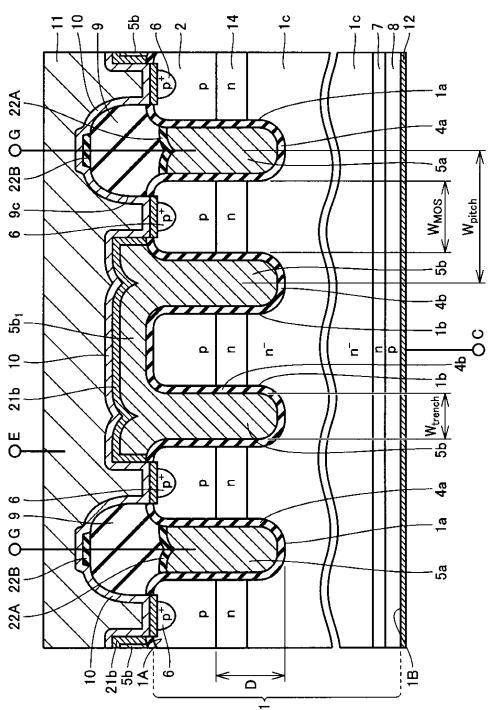

まず本実施の形態の半導体装置の構成について図1～図6を用いて説明する。なお、図1は本実施の形態における半導体装置のチップ状態の構成を模式的に示す概略平面図、図2は図1の領域Sを拡大して示す部分平面図である。また図3、図4、図5および図6は、それぞれ図2中のIII-III線、IV-IV線、V-V線およびVI-VI線に沿う矢視断面図である。

10

【 0 0 2 3 】

まず図1を参照して、半導体チップ100の平面視において、IGBT形成領域40は半導体チップ100の中央部に形成されており、そのIGBT形成領域40の周囲を取り囲むようにエッジターミネーション領域41が配置されている。IGBT形成領域40には、複数のエミッタ電極11が形成されている。

[ 0 0 2 4 ]

主に図2および図3を参照して、この半導体装置は、例えば $40\text{ }\mu\text{m} \sim 700\text{ }\mu\text{m}$ の厚みを有する半導体基板1に形成されたトレンチゲート型IGBTである。半導体基板1は互いに対向する第1正面(上面)1Aおよび第2正面(下面)1Bを有している。半導体基板1であるシリコン基板は、例えば約 $1 \times 10^{12} \sim 1 \times 10^{16}\text{ cm}^{-3}$ の不純物濃度のn-領域(n-ドリフト領域)1c(第1領域)を有している。

30

[ 0 0 2 5 ]

このn<sup>-</sup>領域1cの第1主面1A側の半導体基板1内には、例えば濃度が約 $1 \times 10^{16}$ ~ $1 \times 10^{18} \text{ cm}^{-3}$ で第1主面1Aからの深さが約3μmのp型半導体からなるp型ボディ領域2が形成されている。n<sup>-</sup>領域1cとp型ボディ領域2との間には、n<sup>-</sup>領域1cよりも不純物濃度が高くかつp型ボディ領域2よりも不純物濃度が低いn型不純物拡散領域14(第2領域)が形成されている。p型ボディ領域2内の第1主面1Aには、例えば濃度が $1 \times 10^{19} \text{ cm}^{-3}$ 以上で、第1主面1Aからの深さが約0.5μmのn型半導体からなるn型エミッタ領域3が形成されている。

30

一〇〇二〇

主に図2および図4を参照して、H型エミッタ領域5と隣り合つように第1正面TAには、p型ボディ領域2への低抵抗コンタクトをとるためのp<sup>+</sup>不純物拡散領域(p<sup>+</sup>ボディコンタクト領域)6が、例えば $1 \times 10^{20} \text{ cm}^{-3}$ 程度の濃度で形成されている。

〔 0 0 2 7 〕

主に図3および図4を参照して、半導体基板1の第1主面1Aには、p型ホテイ領域2とn型不純物拡散領域14とを突き抜けてn-領域1cに達するゲート用溝1aが形成されている。このゲート用溝1aは、第1主面1Aから例えば3μm～10μmの深さを有している。

【 0 0 2 8 】

ゲート用溝 1 a の内表面には、例えば 30 nm ~ 200 nm の厚みのシリコン酸化膜からなるゲート絶縁膜 4 a が形成されている。ゲート用溝 1 a の内部を埋め込むように低抵抗材料（例えばリンが高濃度に導入された多結晶シリコン）からなるゲート電極 5 a が形成されている。

40

【 0 0 2 9 】

このようにゲート用溝 1 a とゲート絶縁膜 4 a とゲート電極 5 a とから、半導体基板 1 の第 1 主面 1 A 側に絶縁ゲート構造が構成されている。また n<sup>-</sup>領域 1 c と n 型エミッタ領域 3 とゲート用溝 1 a とから、n<sup>-</sup>領域 1 c をドレインとし、n 型エミッタ領域 3 をソースとする絶縁ゲート型電界効果トランジスタ部（ここでは、MOSトランジスタ部）3 2 が構成されている。このMOSトランジスタ部 3 2 は、半導体基板 1 の第 1 主面 1 A と第 2 主面 1 Bとの間で主電流を流すものである。

50

## 【0030】

第1主面1AにはMOSトランジスタ部32が複数個配置されており、2つのMOSトランジスタ部32に挟まれる第1主面1Aの領域に、安定化プレート部33が形成されている。この安定化プレート部33は、例えば2つのダミートレンチを有している。この2つのダミートレンチの各々は、安定化プレート用溝1bと、安定化プレート用絶縁膜4bと、安定化プレート5bとを有している。なお安定化プレート部33に形成されるダミートレンチの個数は2個に限定されるものではなく、3個以上であってもよい。

## 【0031】

安定化プレート用溝1bは、第1主面1Aからp型ボディ領域2とn型不純物拡散領域14とを突き抜けてn<sup>-</sup>領域1cに達するように形成されており、半導体基板1の第1主面1Aから例えば3μm～10μmの深さを有している。安定化プレート用溝1b同士の間、および隣り合うゲート用溝1aと安定化プレート用溝1bとの間のピッチ( $W_{pitch}$ )は、例えば0.5μm～6.0μmである。

10

## 【0032】

安定化プレート用溝1b同士の間のピッチは、耐圧向上のため隣り合うゲート用溝1aと安定化プレート用溝1bとの間のピッチと同じであることが好ましい。またダミートレンチの個数が3個以上あるときには、安定化プレート用溝1b同士の間のピッチが互いに同じであることが好ましい。つまりゲート用溝1aと安定化プレート用溝1bとを含む複数の溝の各ピッチが互いに同じであることが好ましい。

## 【0033】

20

この安定化プレート用溝1bの内表面に沿うように、ゲート用溝1aと同様に、例えば30nm～200nmの厚みのシリコン酸化膜からなる安定化プレート用絶縁膜4bが形成されている。安定化プレート用溝1bの内部を埋め込むように、ゲート用溝1aと同様に、例えばリンが高濃度に導入された多結晶シリコンからなり、安定化プレート5bとなる導電層が形成されている。

## 【0034】

主に図2および図5を参照して、2つのダミートレンチの各々の安定化プレート5b同士は、導電層5b<sub>1</sub>により互いに電気的に接続されている。この導電層5b<sub>1</sub>は、半導体基板1の第1主面1A上に安定化プレート用絶縁膜4bと同一の層からなる絶縁層を介在して形成されており、半導体基板1とは電気的に絶縁されている。

30

## 【0035】

導電層5b<sub>1</sub>は、例えばリンが高濃度に導入された多結晶シリコンからなっており、安定化プレート5bと同一の層から構成されている。導電層5b<sub>1</sub>は、図2に示すようにゲート用溝1aおよび安定化プレート用溝1bの平面視における長手方向の端部に配置されており、かつ平面視にてその長手方向においてn型エミッタ領域3およびp<sup>+</sup>不純物拡散領域6よりも端部側に配置されている。つまり導電層5b<sub>1</sub>は、一方(例えば図2中左側)のMOSトランジスタ部32のn型エミッタ領域3およびp<sup>+</sup>不純物拡散領域6の形成領域と他方(例えば図2中右側)のMOSトランジスタ部32のn型エミッタ領域3およびp<sup>+</sup>不純物拡散領域6の形成領域とに挟まれる領域R<sub>s</sub>(図2中において1点鎖線で囲まれた領域)よりもゲート電極5aの長手方向の端部側に位置することが好ましい。

40

## 【0036】

主に図3～図5を参照して、半導体基板1の第1主面1A上には、絶縁層22A、層間絶縁膜9、および絶縁層22Bが順に形成されている。絶縁層22Aは、ゲート電極5aまたは安定化プレート5bに対して、例えば熱酸化またはCVD(Chemical Vapor Deposition)酸化を行うことにより形成される。絶縁層22Bは層間絶縁膜9上に選択的に形成されている。層間絶縁膜9は、シリケート、すなわち例えばボロンやリンがドーピングされているシリコン酸化膜を用いCVD(Chemical Vapor Deposition)などにより形成されている。層間絶縁膜9にはコンタクトホール9aとコンタクトホール9bとが形成されている。

## 【0037】

50

コンタクトホール9aは、図5に示すように導電層5b<sub>1</sub>に達するように形成されている。コンタクトホール9aの底部に位置する導電層5b<sub>1</sub>の表面にはシリサイド層21bが形成されている。またコンタクトホール9bは、図3および図4に示すように第1主面1Aに位置するn型エミッタ領域3およびp<sup>+</sup>不純物拡散領域6に達するように形成されている。コンタクトホール9aの底部に位置するn型エミッタ領域3、p<sup>+</sup>不純物拡散領域6およびp型ボディ領域2の表面にはシリサイド層21aが形成されている。

#### 【0038】

主に図2を参照して、コンタクトホール9aはゲート用溝1aおよび安定化プレート用溝1bの平面視における長手方向の端部側（つまり上記領域Rよりもゲート電極5aの長手方向の端部側）に配置されている。コンタクトホール9bは平面視において2つの安定化プレート用溝1bに挟まれる領域R（図2中において2点鎖線で囲まれた領域）には配置されておらず、安定化プレート用溝1bとゲート用溝1aとに挟まれる領域に配置されている。10

#### 【0039】

以上により2つの安定化プレート用溝1bに挟まれる領域Rの全体は絶縁層4bにより覆われており、この領域Rには半導体基板1の第1主面1A（p型ボディ領域2）に達するコンタクトホールは形成されていない。安定化プレート部33が3個以上のダミートレンチを含む場合には、3個以上の安定化プレート用溝1bのうち一方（図2中例えれば左側）のMOSトランジスタ部32に最も近い安定化プレート用溝1bと他方（図2中例えれば右側）のMOSトランジスタ部32に最も近い安定化プレート用溝1bとに挟まれる半導体基板1の第1主面1Aの領域が上記領域Rに対応する。20

#### 【0040】

主に図3～図5を参照して、層間絶縁膜9上にはコンタクトホール9a、9bの側部および底部と、層間絶縁膜9の上面と、絶縁層22Bの上面とに沿うようにバリアメタル層10が形成されている。バリアメタル層10の半導体基板1と接する部分には、コンタクト抵抗を低くするために上述のシリサイド層21aが形成されている。半導体基板1の第1主面1A上にはエミッタ電極11が形成されている。このエミッタ電極11は、バリアメタル層10上にてバリアメタル層10と接するように形成されている。

#### 【0041】

これにより、エミッタ電位Eを与えるエミッタ電極11はコンタクトホール9aを通じて2つの安定化プレート5bの各々に電気的に接続されており、かつコンタクトホール9bを通じてn型エミッタ領域3およびp<sup>+</sup>不純物拡散領域6の各々に電気的に接続されている。つまりエミッタ電極11は、2つの安定化プレート用溝1bに挟まれる領域Rにはコンタクトホールなどを通じて接続されておらず、その領域Rの全面上において少なくとも安定化プレート用絶縁膜4bを介在して配置されている。30

#### 【0042】

主に図6を参照して、ゲート用溝1aの平面視における長手方向の両側における半導体基板1の第1主面1Aにはp型ウエル39が形成されている。ゲート電極5aは、このp型ウエル39が形成された半導体基板1の第1主面1A上にゲート絶縁膜4aを介在して伸びている。層間絶縁膜9にはコンタクトホール9cが形成されている。このコンタクトホール9cは、ゲート電極5aのp型ウエル39上に伸びた部分に達している。40

#### 【0043】

コンタクトホール9cの底部におけるゲート電極5aの表面には、シリサイド層21bが形成されている。バリアメタル層10はコンタクトホール9cの側部および底部に沿うように形成されており、このバリアメタル層10上にはゲート電位Gを与える制御電極11gが形成されている。この制御電極11gは、エミッタ電極11と同一の層からパターニングによって分離して形成された層である。これによりゲート電極5aは、その長手方向の端部において、コンタクトホール9cを通じてゲート電位Gを与える制御電極11gに電気的に接続されている。

#### 【0044】

10

20

30

40

50

主に図3～図6を参照して、n<sup>-</sup>領域1cの第2正面1B側にはn型バッファ領域7と、p型コレクタ領域8とが順に形成されている。このp型コレクタ領域8には、コレクタ電位Cを与えるコレクタ電極12が電気的に接続されている。このコレクタ電極12の材質は、例えばアルミニウム化合物である。

#### 【0045】

次に、本実施の形態の半導体装置におけるメサ幅( $W_{MOS}$ )、トレンチピッチ( $W_{pitch}$ )、およびトレンチ幅( $W_{trench}$ )について図2～図5を用いて説明する。

#### 【0046】

エミッタ電極11は、図2に示す平面視において上記領域R<sub>s</sub>よりもゲート電極5aの長手方向の端部側にて導電層5b<sub>1</sub>に電気的に接続されている。安定化プレート5bは低抵抗材料で形成されているため、安定化プレート5bの全体がエミッタ電位となる。安定化プレート5bをエミッタ電位とするのは、ゲート容量を小さくしてIGBTの短絡時ににおける発振を抑制し、デバイス破壊を防ぐためである。上記領域R<sub>s</sub>よりもゲート電極5aの長手方向の端部側でエミッタ電極11を安定化プレート5bに電気的に接続するのは以下の理由による。つまり、メサ幅( $W_{MOS}$ )および/またはトレンチピッチ( $W_{pitch}$ )を小さくしてオン電圧を低減するときに、導電層5b<sub>1</sub>が上記領域R<sub>s</sub>に配置されると、図22、図24を用いて後述するように、エミッタ電極11をn型エミッタ領域3またはp型不純物拡散領域6に接続するための領域が狭くなってしまい、エミッタ電極11とn型エミッタ領域3またはp型不純物拡散領域6との確実な電気的に接続が困難になるおそれがあるからである。

10

20

#### 【0047】

本実施の形態において、メサ幅( $W_{MOS}$ )は、ゲート用溝1aと安定化プレート用溝1bとの間、および安定化プレート用溝1b同士の間の距離を示している。ゲート用溝1aと安定化プレート用溝1bとの間のメサ幅、および安定化プレート用溝1b同士の間のメサ幅は同じ幅となるように設けられている。また、トレンチピッチ( $W_{pitch}$ )は、ゲート用溝1aと安定化プレート用溝1bとの配置ピッチ、および安定化プレート用溝1b同士の配置ピッチを示している。ゲート用溝1aと安定化プレート用溝1bとのトレンチピッチ、および安定化プレート用溝1b同士のトレンチピッチは同じ距離となるように設けられている。また、トレンチ電極幅( $W_{trench}$ )は、ゲート電極5aおよび安定化プレート5bの各々の幅を示している。ゲート電極5aのトレンチ電極幅および安定化プレート5bのトレンチ電極幅は同じ幅となるように設けられている。

30

#### 【0048】

本実施の形態におけるトレンチゲート型IGBTにおいては、メサ幅( $W_{MOS}$ )、トレンチピッチ( $W_{pitch}$ )、およびトレンチ幅( $W_{trench}$ )の関係が、 $W_{MOS} = W_{pitch} - W_{trench} > 0$ (式1)の関係を満足するように形成されている。

#### 【0049】

次に、本実施の形態の半導体装置の作用効果について従来例と対比して説明する。

図7および図8に、従来のトレンチゲート型IGBTの構造を示す。図7の領域X2は、従来のトレンチゲート型IGBTにおいて層間絶縁膜9に形成されたコンタクトホール9dの平面形状を示している。このコンタクトホール9dを通じて、エミッタ電極11はn型エミッタ領域3、p<sup>+</sup>不純物拡散領域6、p型ボディ領域2および安定化プレート5bと電気的に接続されている。つまり安定化プレート5bに挟まれる半導体基板1の第1正面1Aにあるp型ボディ領域2およびp<sup>+</sup>不純物拡散領域6にもエミッタ電極11は電気的に接続されている。

40

#### 【0050】

また2つの安定化プレート5bに挟まれる半導体基板1の第1正面1Aにもp<sup>+</sup>不純物拡散領域6が形成されている。またn型エミッタ領域3は、ゲート電極5aの長手方向に沿ってゲート電極5aとp<sup>+</sup>不純物拡散領域6との間に形成されている。

#### 【0051】

また、ゲート用溝1aおよび安定化プレート用溝1bは、上面から見ると、それぞれ図

50

1 または図 4 に示すゲート電極 5 a および安定化プレート 5 b と同じパターンとなつてゐる。

【 0 0 5 2 】

なお、これ以外の従来例の構成は本実施の形態の構成とほぼ同じであるため、同一の要素については同一の符号を付し、その説明を省略する。

【 0 0 5 3 】

従来構造ではエミッタ電極 11 が安定化プレート 5b に挟まれる半導体基板 1 の第 1 主面にある p 型ボディ領域 2 および p<sup>+</sup>不純物拡散領域 6 にも電気的に接続されている。このため、トレンチMOSトランジスタ部のオン状態のキャリア濃度が低下し、オン抵抗が高くなることが後述の実施例における検討により分かった。

10

[ 0 0 5 4 ]

これに対して、本実施の形態における構造は、図2に示すように、エミッタ電極11は平面視において安定化プレート5bに挟まれる領域Rのp型ボディ領域2には電気的に接続されてはいない。エミッタ電極11は、安定化プレート5bとゲート電極5aとに挟まれる領域にコンタクトホール9bを介して電気的に接続され、領域Rsの外側にある導電層5b<sub>1</sub>に電気的に接続されているだけである。つまり図3～図5に示すようにエミッタ電極11は安定化プレート部33では半導体基板1の第1正面1Aには電気的に接続されおらず、MOSトランジスタ部32にて半導体基板1の第1正面1Aに電気的に接続されている。このため、オン状態において電流は安定化プレート部33にはほとんど流れず、MOSトランジスタ部32に集中して流れることとなり、従来例よりもオン電圧が低くなることが後述の実施例における検討により分かった。

20

【 0 0 5 5 】

また上記のオン電圧の低減効果は、本実施の形態の構成では単位セルに占める安定化プレート部33の安定化プレート用溝1bの割合が増えるに従い強化されるため、さらにオン電圧を低減できることも後述の実施例における検討により分かった。本実施の形態の構成は、安定化プレート用溝5bに挟まれる領域Rに1p<sup>+</sup>不純物拡散領域6を設けていないことと、導電層5b<sub>1</sub>の配置の工夫により、単位セルに占める安定化プレート用溝1bの割合を増加させやすい構造である。さらにこの安定化プレート用溝1bの割合を増加させることで実効的なゲート幅W(図2におけるW<sub>1</sub>+···+W<sub>n</sub>)を低減することも容易となる。このため、飽和電流を減少させることも容易となり、短絡耐量を向上させることが容易となる。以下、そのことを説明する。

30

【 0 0 5 6 】

MOSトランジスタの飽和領域におけるドレイン電流  $I_D$ （飽和電流）を表す下記の式2から分かるように、実効的なゲート幅  $W$  が小さくなると MOSトランジスタのドレイン電流  $I_D$  が減少する。本実施の形態では、ゲート配線を行なわない安定化プレート用溝1bの本数の割合を増加させることでMOSトランジスタ部32の有効セルサイズに占める実効的なゲート幅  $W$ （図2における  $W_1 + \dots + W_n$ ）が小さくされている。これにより、IGBTの短絡電流が抑制されて短絡耐量が向上されている。さらに後述するよう、安定化プレート用溝1bの本数の割合を増加させることで、オン電圧をさらに低減することもできるので、短絡耐量を向上もしくは維持しつつオン電圧を小さくすることができる。

40

【 0 0 5 7 】

【数1】

$$I_D = \frac{1}{2} \cdot \frac{W}{L} \cdot \mu \cdot C_{ox} (V_G - V_{th})^2 \quad \cdots (\text{式2})$$

【 0 0 5 8 】

上記の式 2において、 $I_D$ は飽和領域におけるドレイン電流（飽和電流）を意味し、 $W$ は実効的なゲート幅を意味し、 $\mu$ は移動度を意味し、 $C_{ov}$ は単位面積当たりのゲート絶縁

50

膜容量を意味し、 $V_G$ はゲート電圧を意味し、 $V_{th}$ はしきい値電圧を意味する。Lはチャネル長を意味し、本実施の形態の半導体装置においては、n型エミッタ領域3の下端からp型ボディ領域2とn型不純物拡散領域14との境界面までのゲート用溝1aに沿う距離に該当する。

#### 【0059】

負荷が短絡した時にデバイスを流れる電流は、デバイスの飽和電流によって決まる。飽和電流が小さいと短絡時に流れる電流も小さくなり、デバイスにかかるエネルギー負荷も小さくなる。よって、飽和電流を抑制することにより短絡耐量を向上することが可能となる。

#### 【0060】

また本実施の形態における構造では、エミッタ電極11は安定化プレート5bに挟まれた領域ではp型ボディ領域2に接続されていないため、MOSトランジスタ部32に電流を集中させることができる。また、安定化プレート用溝1bの本数を容易に増加することができるため、オン電圧を低減する効果も得られる（図9に示す定常損失領域において、同一のコレクタ電流Jcに対するオン電圧Vceが減少している）。つまり、本構造を用いることにより、短絡耐量を維持した上で、定常損失を低減することが可能である。

#### 【0061】

またMOSトランジスタ部32の微細化が容易であるため、MOSトランジスタ部32を微細化することにより実効的なゲート幅を低減することができ、飽和電流を減少させ短絡耐量を向上させることができるとなるため、半導体装置の歩留まりを向上させることができます。

#### 【0062】

さらに上述した従来例においては、p型ボディ領域2とエミッタ電極11との間のコンタクト抵抗を下げるために、隣り合う安定化プレート5bの間にp<sup>+</sup>不純物拡散領域6が設けられている。しかし、このp<sup>+</sup>不純物拡散領域6が設けられた箇所は、IGBTがターンオフする時にホールが抜けるパスとなり、IGBTのターンオフ遮断能力、すなわちターンオフ可能な電流密度や電圧が低下する。

#### 【0063】

これに対して本実施の形態の構成では、上述したようにエミッタ電極11は安定化プレート5bに挟まれたp型ボディ領域2にコンタクトホールを通じて接続されていない。このため、オン電圧の低減に加えて、IGBTがターンオフする時に安定化プレート5bに挟まれた領域にホールが抜けるパスができることもなく、ターンオフ可能な電流密度や電圧の低下を防止することができる。

#### 【0064】

また本実施の形態における構造は、図2に示したように、エミッタ電極11は平面視において安定化プレート5bに挟まれる領域Rではp型ボディ領域2には電気的に接続されていない。このため、図23、図24に示す構成のようにエミッタ電極11とn型エミッタ領域3またはp<sup>+</sup>不純物拡散領域6との接続を考慮してゲート用溝1aと安定化プレート用溝1bとの間のメサ幅を大きくする必要はない。よって本実施の形態では、ゲート用溝1aと安定化プレート用溝1bとの間のメサ幅を小さくすることができるとともに、このメサ幅の設計の自由度が向上する。またメサ幅を小さくできるため、さらにオン電圧を低減することもできる。

#### 【0065】

また上記のトレチピッチが各部において異なっていると、各トレチ1a、1b付近の電界の分布が不均一となり電界集中が生じ、耐圧が低下する。このため本実施の形態においてはゲート用溝1aと安定化プレート用溝1bとのトレチピッチ、および安定化プレート用溝1b同士のトレチピッチは同じとなるように設けられている。これによりトレチ周囲の電界集中を防ぎ、耐圧を向上させることができるとなる。つまり上記においてゲート用溝1aと安定化プレート用溝1bとの間のメサ幅を小さくできるため、それに合わせてゲート用溝1aと安定化プレート用溝1bとのトレチピッチを小さくできる。さ

10

20

30

40

50

らにゲート用溝 1 a と安定化プレート用溝 1 b とのトレンチピッチの縮小に合わせて安定化プレート用溝 1 b 同士のトレンチピッチも小さくすることで、電界集中による耐圧低下を防ぎつつ、デバイスの小型化を図ることもできる。

#### 【 0 0 6 6 】

( 実施例 )

上記構成を有するトレンチゲート型 I G B T の具体的な一例について、以下に説明する。

。

#### 【 0 0 6 7 】

トレンチゲート型 I G B T のシミュレーションパラメータは、下記の表 1 に示すとおりである。また、本データで使用しているダミートレンチ比率については、表 2 に示すとおりである。ダミートレンチ比率は、1 セル（単位ユニットセル部 3 4 ）あたりのダミートレンチ（安定化プレート用溝）の本数を、1 セル（単位ユニットセル部 3 4 ）あたりの全トレンチ本数（ゲート用溝本数 + ダミートレンチ本数）で割った値、すなわち、安定化プレート本数 / 全トレンチ本数と定義する。

10

#### 【 0 0 6 8 】

【表 1】

| 領域                           | 不純物濃度                                  |

|------------------------------|----------------------------------------|

| n <sup>-</sup> 領域1c          | $1.313 \times 10^{13} \text{ cm}^{-3}$ |

| p型ボディ領域2                     | $9.45 \times 10^{17} \text{ cm}^{-3}$  |

| n型エミッタ領域3                    | $20 \times 10^{19} \text{ cm}^{-3}$    |

| トレンチ酸化膜（ゲート絶縁膜4a、エミッタ用絶縁膜4b） | $0.12 \mu\text{m}$                     |

| p <sup>+</sup> 不純物拡散領域6      | $5.71 \times 10^{19} \text{ cm}^{-3}$  |

| n型バッファ領域7                    | $30 \times 10^{16} \text{ cm}^{-3}$    |

| p型コレクタ領域8                    | $1 \times 10^{18} \text{ cm}^{-3}$     |

| n型不純物拡散領域14                  | $6.5 \times 10^{16} \text{ cm}^{-3}$   |

#### 【 0 0 6 9 】

【表 2】

| ダミートレンチ比率 | 安定化プレート本数/全トレンチ本数 |

|-----------|-------------------|

| 0.5       | 1/2               |

| 0.67      | 2/3               |

| 0.75      | 3/4               |

| 0.8       | 4/5               |

| 0.875     | 7/8               |

| 0.9       | 9/10              |

| 0.92      | 11/12             |

| 0.93      | 13/14             |

#### 【 0 0 7 0 】

なお、本実施の形態においては、ゲート用溝 1 a の本数および安定化プレート用溝 1 b の本数の絶対値ではなく、これらの比率が重要である。すなわち、ゲート用溝 1 a と安定化プレート用溝 1 b の本数がいくつであっても、デバイスの特性はダミートレンチ比率に大きく依存する。

40

#### 【 0 0 7 1 】

50

20

30

40

50

( i ) メサ幅 ( $W_{MOS}$ )

トレンチ電極の間（ゲート用溝 1 a と安定化プレート用溝 1 bとの間、安定化プレート用溝 1 b と安定化プレート用溝 1 bとの間）のメサ幅 ( $W_{MOS}$ ) を狭くすることで、オン電圧と定常損失との低減効果を得ることができる。その関係を図 1 0 に示す。

【 0 0 7 2 】

図 1 0 は、横軸にメサ幅 ( $W_{MOS}$ ) [  $\mu m$  ] 、縦軸にオン電圧 ( $V_{ce(sat)}$ ) [ V ] を示している。図 1 0 においてトレンチ幅 ( $W_{trench}$ ) は一定としている。参考のため、図 2 8 に示す従来のプレーナーゲート構造 I G B T のデータを、同じパラメータ（ユニットセル寸法）として図 1 0 中にプロットする。図 2 8 を参照して、プレーナーゲート構造では、ゲート電極 5 a は半導体基板 1 の第 1 主面 1 A 上に位置しており、n 型エミッタ領域 3 と n 型不純物拡散領域 1 4 とに挟まれる p 型ボディ領域 2 上にゲート絶縁膜 4 a を介在して形成されている。エミッタ電極 1 1 は n 型エミッタ領域 3 および p<sup>+</sup> 不純物拡散領域 6 に電気的に接続されている。なおこれ以外のプレーナーゲート構造 I G B T の構成は図 2 に示すトレンチゲート構造の M O S トランジスタ部 3 2 の構成とほぼ同じであるため、同一の要素については同一の符号を付し、その説明を省略する。

【 0 0 7 3 】

なお、図 1 0 に示すデータは、代表例として 2 9 8 K ( 2 5 ) でのデータを示しているが、その他の温度でも同様の傾向を示す。また、1 セルあたりのトレンチ電極のゲート電極と安定化プレートとの割合は、ゲート電極を 1 本、安定化プレートを 7 本としたダミートレンチ比率 0 . 8 7 5 にてシミュレーションを行なった結果である。

【 0 0 7 4 】

本実施の形態における構造では、エミッタ電極 1 1 が安定化プレート部 3 3 の p 型ボディ領域 2 にコンタクトホールを通じて接続されておらず、M O S トランジスタ部 3 2 のキャリア濃度を高めることができるために、図 7 、図 8 に示す従来例よりオン電圧が低減できている。本実施の形態における構造を用いると、メサ幅 ( $W_{MOS}$ ) をより狭くすることができ、M O S トランジスタ部 3 2 のキャリア密度をさらに高めることができるために、従来例よりもさらにオン電圧が低減できていることが分かる。

【 0 0 7 5 】

また、メサ幅 ( $W_{MOS}$ ) とオン電圧低減効果との関係については、従来のトレンチ構造（図 7 、図 8 を参照）でも同様の傾向を示す。ただし、先述のように従来構造ではエミッタ電極 1 1 と p 型ボディ領域 2 のコンタクトを安定化プレート 5 b の領域全面で取っているため、トレンチ M O S トランジスタ部のオン状態のキャリア濃度が低下し、オン抵抗が高くなる。

【 0 0 7 6 】

これに対して、本実施の形態における構造は、エミッタ電極 1 1 が安定化プレート部 3 3 の p 型ボディ領域 2 にコンタクトホールを通じて接続されていない。このため、トレンチ M O S トランジスタ部 3 2 におけるオン状態のキャリア濃度が増大し高いオン電圧低減効果を得ることができる。

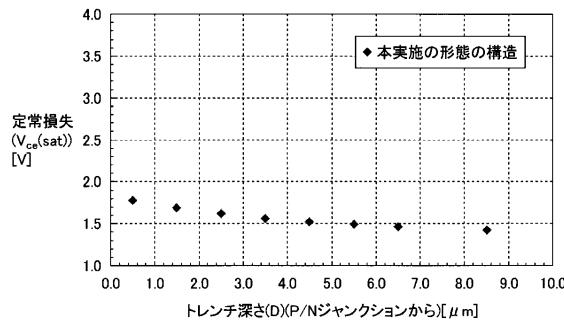

【 0 0 7 7 】

( i i ) ダミートレンチ比率

本実施の形態における構造において、ゲート電極 5 a に対して安定化プレート 5 b の割合を増加していく（ダミートレンチ比率を増加させる）ことで、オン電圧の低減、ひいては定常損失を低減する効果を得ることができる。この関係を図 1 1 に示す。横軸はダミートレンチ比率、縦軸はオン電圧 ( $V_{ce(sat)}$ ) を示している。デバイスにおけるエネルギー損失は、（デバイスを流れる電流）×（デバイスにかかる電圧）で表されるため、オン電圧が減少するほど定常損失が小さくなる。

【 0 0 7 8 】

このオン電圧が低減する原理を、図 1 2 ( A ) 、図 1 2 ( B ) 、図 1 3 ( A ) 、図 1 3 ( B ) および図 1 4 に示す。図 1 2 ( A ) 、図 1 3 ( A ) は I G B T がオン状態である場合におけるデバイス内の電流密度を示し、図 1 2 ( B ) 、図 1 3 ( B ) は、I G B T がオ

ン状態である場合における安定化プレートで挟まれた領域における電流経路を示し、図14はオン状態におけるデバイス内のキャリア濃度を示している。なお、図12(A)、図12(B)は、本実施の形態の構造の場合を示し、図13(A)、図13(B)は、図7および図8に示した従来のトレンチ電極構造の場合を示しており、それぞれ図3および図8に示す断面に対応する。

#### 【0079】

図12(A)および図13(A)の各々において、左端( $X = 0 \mu m$ )はゲート用溝1aであり、所定のピッチで安定化プレート用溝1bが並んでいる( $X > 0$ )。また、図12(B)、図13(B)は図12(A)、図13(A)中のZで囲まれた領域の拡大図であり、図12(B)、図13(B)中の矢印の向きは電流の流れる向きを示し、矢印の長さは電流密度の大きさを示している。10

#### 【0080】

図12(A)、図12(B)に示す本実施の形態の構造(図2)のオン状態では、安定化プレート部33の横にあるトレンチMOSトランジスタ部32のゲート電極に電圧バイアス(本構造はnチャネルMOSトランジスタのためゲートに正バイアス)が印加され、チャネル部(p型ボディ領域2においてゲート用溝1aと接する部分)を通じて電子がn<sup>-</sup>領域1cに注入される。その際、コレクタ側は順バイアスされているため同時にコレクタ側からホールがn<sup>-</sup>領域1cに注入される。

#### 【0081】

ここで本実施の形態の構造では、安定化プレート部33、すなわち隣り合う安定化プレート用溝1bの間ににおいて、エミッタ電極11はp型ボディ領域2に接続されておらず、MOSトランジスタ部32、すなわちゲート用溝1aと安定化プレート用溝1bの間ににおいて、コンタクトホール9bを通じてp型ボディ領域2と接続されている。したがって、本構造においては、ホールがエミッタ側へ流れるパスはトレンチMOSトランジスタ部32のみとなるため、安定化プレート部33にはほとんど電流は流れずに、トレンチMOSトランジスタ部32に集中して電流が流れ込む。20

#### 【0082】

トレンチMOSトランジスタ部32に電流が集中するため、トレンチMOSトランジスタ部32のオン状態のキャリア濃度が増大しオン電圧が低くなる。その効果は図11に示すように、単位セルに占めるダミートレンチの割合が増えるに従い強化され(すなわちトレンチMOSトランジスタ部32のオン状態のキャリア濃度がより増大し)、オン電圧がより低くなり定常損失が低減される。30

#### 【0083】

これに対して、図13(A)、図13(B)に示すように、従来のトレンチ電極構造では、エミッタ電極11は安定化プレート5bの間のp型ボディ領域2にも接続されているため、安定化プレート5bの間にも電流が流れ、トレンチMOSトランジスタ部32への電流集中は起きにくくなる。

#### 【0084】

すなわち従来の構造では、安定化プレート部33にホールの抜ける接続部分があるため、ダミートレンチ間にホールのパスが形成される。その結果、図12(B)および図13(B)に示すような電流集中の度合いの違いが発生する。その影響により図14に示すように本実施の形態と従来例とでトレンチMOSトランジスタ部32のエミッタ側キャリア濃度分布が変化し、オン電圧Vce(sat)の違いが生じる。40

#### 【0085】

図14は、図2～図6に示した本実施の形態と図7、図8に示した従来例との半導体装置において、トレンチMOSトランジスタ部32のIGBTがオン状態のときのキャリア濃度分布を比較したグラフである。図14に示すキャリア密度分布は、図3、図8のA-A'線部、および図28のB-B'線部に対応する。

#### 【0086】

図14および図15に、このデバイス構造と電流集中の関係を示す。図14および図150

5は、横軸にエミッタ領域からコレクタ領域までの距離、縦軸にキャリア濃度を示す。図15は、図14中のエミッタ側の拡大図である。また、本データは図3、図8のA-A'線部および図28のB-B'線部に対応し、チャネルが形成される箇所を含むものである。

#### 【0087】

なお図14は各半導体装置のダミートレンチ比率が同じ場合（プレーナーゲート構造を除く）を比較したものである。図2～図6に示した本実施の形態の構造では、電流経路がゲート用溝1aに隣接するトレンチMOSトランジスタ部32のみとなり、その結果オン状態におけるエミッタ側のキャリア濃度が図14に示すように増大する。逆に図7、図8に示した従来例の構造のように安定化プレート部のp型ボディ領域2にエミッタ電極11が接続されると、隣り合う安定化プレート用溝1bの間ににおけるp型ボディ領域2およびp<sup>+</sup>不純物拡散領域6にも電流パスが発生する。これにより、トレンチMOSトランジスタ部以外にも電流パスが形成されるため、トレンチMOSトランジスタ部のオン状態のキャリア濃度が低下する。したがって、従来の半導体装置は本実施の形態よりオン電圧が高くなる。

#### 【0088】

図14および図15を参照して、本実施の形態におけるトレンチ電極構造では、コレクタ領域側から注入されたホールがn<sup>-</sup>領域（n<sup>-</sup>ドリフト領域）1c内でその密度を低下することなくエミッタ側へ到達している。さらに、安定化プレート5bを増やすことによりエミッタ側でキャリアの集中が起こり、n<sup>-</sup>領域（n<sup>-</sup>ドリフト領域）1c内のエミッタ側のキャリア濃度が上昇する。これに対し、従来のトレンチ電極構造およびプレーナーゲート構造の双方では、エミッタ側へ進むにつれてキャリア濃度が低下している。

#### 【0089】

つまり、本実施の形態におけるトレンチ電極構造では、n<sup>-</sup>ドリフト領域からエミッタ側にかけてのキャリア濃度増大効果により、ダミートレンチ比率が増加するにつれてオン電圧低減効果を得ることができる。ただし、ダミートレンチ比率が0.92を超えるとキャリア集中効果が飽和する（図11参照）。

#### 【0090】

本実施の形態同士を比べると、ダミートレンチ比率が0.875は0.67と比べてキャリア濃度が大きい。IGBTがオン状態では、安定化プレート部33の直下をホールがトレンチMOSトランジスタ部32に向かって移動する。その移動距離が大きくなる方が、安定化プレート部33の直下のホール濃度が高くなる。その結果、唯一のホールのバスであるトレンチMOSトランジスタ部32でのキャリア濃度は、安定化プレート部33の距離が大きくなるほど（ダミートレンチ比率が増加するほど）キャリアが集中するため高い濃度となる。キャリア濃度が高くなると、当該箇所のキャリア濃度が増大し抵抗が下がるため、オン電圧が低くなる。

#### 【0091】

図14と図15に示すように、エミッタ領域を除きホールの密度と電子の密度はほぼ同じである。また、図15に示すようにエミッタ領域では、電子密度の方がホール密度よりも高くなる。

#### 【0092】

なお、従来のトレンチゲート構造やプレーナーゲート構造で、エミッタに近づくにつれキャリア濃度が下がるのは、電子の供給能力（注入能力）が低下しているためである。

#### 【0093】

以上より、安定化プレート5bによるオン電圧低減効果を得ることができるダミートレンチ比率は、安定化プレートの最小本数時の0.5からキャリア集中効果が飽和する0.92までの範囲（つまり0.5以上0.92以下の範囲）が好ましい。

#### 【0094】

また、図16を参照して、ダミートレンチ比率と飽和電流との関係を示す図からも分かるように、安定化プレート5bを増加することにより、ゲート幅が小さくなり、飽和電流

を抑制することができる。

#### 【0095】

本実施の形態のトレンチゲート構造でのユニットセル単位は、トレンチMOSトランジスタ部32と安定化プレート部33とが一体となった領域（図3、4に示す単位ユニットセル部34）である。また、ダミートレンチ比率が増加すると単位ユニットセル部34に占めるトータルゲート幅Wが小さくなる。

#### 【0096】

本実施の形態の構造により、飽和電流を抑制することで短絡耐量を維持しつつオン電圧を小さくすることができるIGBTを実現することができる。しかし、本実施の形態の構造では、ダミートレンチ比率を任意に設定できるため、飽和電流抑制と低オン電圧化の両立が可能になる（図11、図16を参照）。 10

#### 【0097】

図17に、オン電圧（ $V_{ce(sat)}$ ）とスイッチング損失（ $E_{off}$ ）との関係を示す。オン電圧が低いほど定常損失は小さくなるという関係がある。本実施の形態について示すデータ点はp型コレクタ領域8の不純物濃度（コレクタ濃度）を $1 \times 10^{16} \sim 5 \times 10^{20}$ と振り分けたものであり、コレクタ濃度が高いほどオン電圧は低くなる。

#### 【0098】

オン電圧とスイッチング損失がトレードオフの関係にある理由を説明する。IGBTでは、オン電圧とスイッチング損失との2つのデバイス特性がデバイス構造以外に共通な制御パラメータを用いて制御される。本実施の形態では、例えば該当パラメータはコレクタ濃度である。 20

#### 【0099】

オン電圧を低くして定常損失を小さくする場合、コレクタ側のキャリア濃度を上げるためにコレクタ濃度が高濃度化される。そうすると、IGBTがオン状態時にn<sup>-</sup>領域1c中に高濃度のホールがコレクタ側から注入され、IGBTがターンオフする際に注入されたホールを吐き出すための時間が必要となり、スイッチング損失が増加する。スイッチング損失を小さくする場合は逆にコレクタ濃度を低くするが、オン電圧は高くなる。以上から、オン電圧とスイッチング損失とはトレードオフの関係にある。

#### 【0100】

しかし、本実施の形態においては、コレクタ側のキャリア濃度が同じであっても、従来の構造の半導体装置と比較してオン電圧（ $V_{ce(sat)}$ ）を低減することができるため、図17に示すトレードカーブを低オン電圧側へ移動させ、トレードオフ特性の改善が可能となる。 30

#### 【0101】

したがって、本実施の形態のトレンチ電極構造によれば、定常損失低減を可能としたことにより、トータル損失（スイッチング損失 + 定常損失）も低減することができる。

#### 【0102】

なお、図11～図17に示すデータは、シミュレーションにて半導体基板1の厚みt<sub>sub</sub>

$t_{sub} = 470 \mu m$ 、メサ幅（ $W_{MOS}$ ）= 1.2 μm、トレンチ幅（ $W_{trench}$ ）= 1.2 μmの条件下でのものである。また、代表として298K(25°C)のデータを示しているが、その他の温度でも同様の傾向を示す。 40

#### 【0103】

また、これまで述べてきたダミートレンチ比率との関係について、n型エミッタ領域3の有無（図3と図4において相違する部分）に関わらず同様の効果を得ることができる。

#### 【0104】

（iii）トレンチ深さ（D）

図18に、トレンチ深さ（D:p型ボディ領域2とn型不純物拡散領域14により形成されるエミッタ側のP/Nジャンクションからの深さ；図3参照）と耐圧の関係を示し、図19に様々なトレンチ深さ（D）について、半導体基板の第1主面からの深さと電界強度との関係を示す。図18から、本実施の形態におけるトレンチ電極構造において、トレ 50

ンチ深さ( D )をエミッタ側の P / N ジャンクション間で生じる電界集中を緩和できる長さ以上に設計することで十分な耐圧を得ることができる。図 19 に示すように、エミッタ側の P / N ジャンクションの電界集中を緩和できるトレンチ深さ( D )は、P / N ジャンクションから 1 . 5  $\mu\text{m}$  以上のものである。

#### 【 0105 】

トレンチ深さを大きくすると電界集中が緩和するメカニズムを説明する。IGBTが耐圧を保持するときはゲートおよび安定化プレートのトレンチ部はソース電位と同じ 0 V となる。その結果、これらのトレンチ部はフィールドプレートのように電荷を誘起して等電位線をコレクタ側へ押しやり、エミッタ側の P / N ジャンクションにおける電界を緩和させる効果が得られる。

10

#### 【 0106 】

耐圧が向上するトレンチ深さは、トレンチやメサの幅、ダミートレンチ率、不純物濃度にほとんど依存しない。一方、耐圧が向上するトレンチ深さはトレンチMOSトランジスタ部 32 の各不純物深さ、すなわち p 型ボディ領域 2 と n 型不純物拡散領域 14 により形成される P / N ジャンクションとの位置関係に依存する。

#### 【 0107 】

また、1 . 5  $\mu\text{m}$  よりさらにトレンチを深くすることで、図 20 で示すようにオン電圧(  $V_{ce(sat)}$  )低減効果を得ることができる。例えば、5 . 5  $\mu\text{m}$  以上にすれば、 $V_{ce(sat)}$  を 1 . 5 V 以下にすることができる。

20

#### 【 0108 】

なお、図 18 ~ 図 20 に示すデータは、ダミートレンチ比率 0 . 875 、半導体基板 1 の厚み  $t_{sub} = 470 \mu\text{m}$  、メサ幅(  $W_{MOS}$  ) = 1 . 2  $\mu\text{m}$  、トレンチ幅(  $W_{trench}$  ) = 1 . 2  $\mu\text{m}$  にて評価を行なった。また、代表として 298 K ( 25 ) のデータを示しているが、その他の温度でも同様の傾向を示す。

30

#### 【 0109 】

##### ( i v ) トレンチ電極の先端形状

再び、図 3 を参照して、ゲート用溝 1a および安定化プレート用溝 1b の各々の先端の断面形状をラウンド形状( 例えは半円形状 ) にすることで、耐圧向上を図ることができる。ゲート用溝 1a および安定化プレート用溝 1b の先端形状が角型のものでは、その角部にて電界集中が発生し、耐圧が低下する。そのため、ゲート用溝 1a および安定化プレート用溝 1b の先端の断面形状は丸みを持たせた形状であることが好ましい。

30

#### 【 0110 】

##### ( 他の実施の形態 )

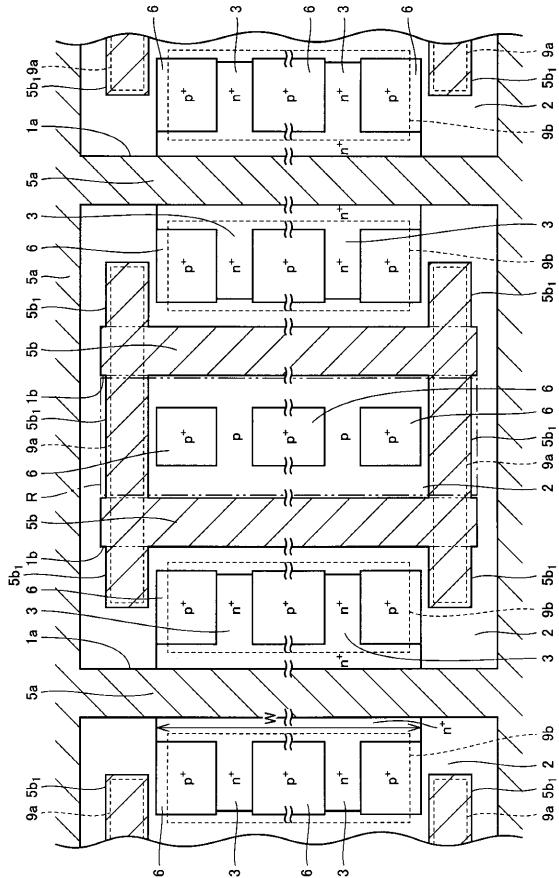

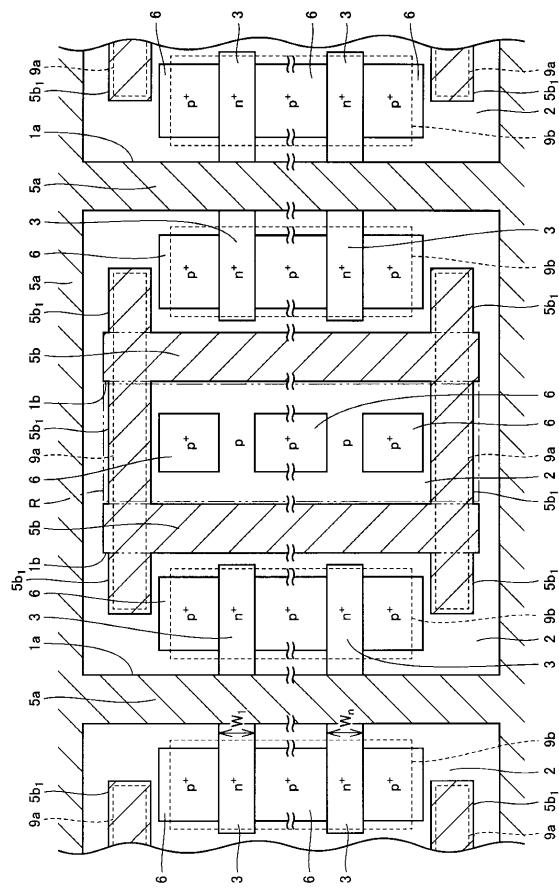

なお図 2 に示すように 2 つの安定化プレート 5b 同士を繋ぐ導電層 5b<sub>1</sub> の平面視における配置位置は、領域 R<sub>s</sub> よりもゲート電極 5a の長手方向の端部側に位置することが好ましいが、図 21 および図 23 に示すように領域 R<sub>s</sub> 内であってもよい。

#### 【 0111 】

図 21 に示すように導電層 5b<sub>1</sub> は、ゲート電極 5a の長手方向に並んだ n 型エミッタ領域 3 および p<sup>+</sup> 不純物拡散領域 6 のうち長手方向の最も端部に位置する最端部の p<sup>+</sup> 不純物拡散領域 6 同士に挟まれる領域内に配置され、かつ導電層 5b<sub>1</sub> の一部が平面的に見て最端部の p<sup>+</sup> 不純物拡散領域 6 の一部と重なっていてもよい。この構成における導電層 5b<sub>1</sub> が形成された部分の断面構成は図 22 に示す構成となる。

40

#### 【 0112 】

図 23 に示すように導電層 5b<sub>1</sub> は、ゲート電極 5a の長手方向に並んだ n 型エミッタ領域 3 および p<sup>+</sup> 不純物拡散領域 6 のうち最端部の p<sup>+</sup> 不純物拡散領域 6 以外の n 型エミッタ領域 3 同士もしくは p<sup>+</sup> 不純物拡散領域 6 同士に挟まれる領域内に配置されていてもよい。図 23 の構成では、導電層 5b<sub>1</sub> は最端部の p<sup>+</sup> 不純物拡散領域 6 以外の p<sup>+</sup> 不純物拡散領域 6 同士に挟まれる領域内に配置されている。この構成における導電層 5b<sub>1</sub> が形成された部分の断面構成は図 24 に示す構成となる。

#### 【 0113 】

50

図22および図24から分かるように、導電層5b<sub>1</sub>が上記領域R<sub>s</sub>内にある場合には、導電層5b<sub>1</sub>によりエミッタ電極11を半導体基板1の第1主面1Aに接続するための領域の幅が小さくなる。これに対して図2～図6に示す構成では、導電層5b<sub>1</sub>が上記領域R<sub>s</sub>外にあるため、この導電層5b<sub>1</sub>によってエミッタ電極11がp<sup>+</sup>不純物拡散領域6およびn型エミッタ領域3との接触する部分の面積が小さくなることはない。

#### 【0114】

また本実施の形態における半導体装置の平面視におけるn型エミッタ領域3およびp<sup>+</sup>不純物拡散領域6のパターン構造は、図2に示すパターンだけでなく、図7の従来構造に示すようなパターン構造でもよい。つまり図7の従来構造におけるコンタクトホール9dに代えて図2に示すコンタクトホール9a、9bが用いられれば、図7の従来構造に示すn型エミッタ領域3およびp<sup>+</sup>不純物拡散領域6のパターン構造が用いられてもよい。この図7の従来構造に示すn型エミッタ領域3およびp<sup>+</sup>不純物拡散領域6のパターン構造に図2に示すコンタクトホール9a、9bを適用した構成を図25に示す。この図25の構成においても、図2～図6に示す構成と同様の効果を得ることができる。10

#### 【0115】

また、図2に示すパターン構造において、安定化プレート5bと安定化プレート5bとの間に、図26に示すようなp<sup>+</sup>不純物拡散領域6があっても、図2～図6に示す構成と同様の効果を得ることができる。また、図27に示すように、平面視においてn型エミッタ領域3およびp<sup>+</sup>不純物拡散領域6の各々がゲート電極5aの長手方向に沿って並走するように延びる短冊状のパターン構造であっても、同様の効果を得ることができる。20

#### 【0116】

なお上記においてはMOSトランジスタ部を例に挙げて説明したが、ゲート絶縁膜の材質はシリコン酸化膜に限定されるものではない。このため、本発明はMISトランジスタ部全般に適用することができる。

#### 【0117】

なお、今回開示された上記各実施の形態および実施例はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

#### 【符号の説明】

30

#### 【0118】

1 半導体基板、1a ゲート用溝、1b 安定化プレート用溝、1c n<sup>-</sup>領域(n<sup>-</sup>ドリフト領域)、1A 第1主面、1B 第2主面、2 p型ボディ領域、3 n型エミッタ領域、4a ゲート絶縁膜、4b 安定化プレート用絶縁膜、5a ゲート電極、5b 安定化プレート、5b<sub>1</sub> 導電層、6 p<sup>+</sup>不純物拡散領域(p<sup>+</sup>ボディコンタクト領域)、7 n型バッファ領域、8 p型コレクタ領域、9 層間絶縁膜、9a, 9b, 9c, 9d コンタクトホール、10 バリアメタル層、11 エミッタ電極、11g 制御電極、12 コレクタ電極、14 n型不純物拡散領域、21a, 21b シリサイド層、22A, 22B 絶縁層、31 層間絶縁膜、32 MOSトランジスタ部、33 安定化プレート部、34 単位ユニットセル部、39 p型ウエル、40 IGBT形成領域、41 エッジターミネーション領域、100 半導体チップ。40

【図1】

【図2】

【図3】

【図4】

【 四 5 】

【図6】

【四七】

【図8】

【図9】

【図11】

【図10】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図 1 2】

【図 13】

---

フロントページの続き

(51)Int.Cl.

F I

H 01 L 29/78 652M

H 01 L 29/78 652K

H 01 L 29/78 655G

(56)参考文献 特開2010-050211(JP, A)

国際公開第02/061845(WO, A1)

特開2001-102579(JP, A)

特開2002-016252(JP, A)

米国特許出願公開第2003/0160270(US, A1)

特開2001-332728(JP, A)

特開2009-277792(JP, A)

特開2004-273921(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 06

H 01 L 29 / 08

H 01 L 29 / 10

H 01 L 29 / 40

H 01 L 29 / 66

H 01 L 29 / 739

H 01 L 29 / 78