(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4072426号

(P4072426)

(45) 発行日 平成20年4月9日(2008.4.9)

(24) 登録日 平成20年1月25日(2008.1.25)

(51) Int.Cl.

F 1

|             |             |                  |      |      |         |

|-------------|-------------|------------------|------|------|---------|

| <b>G09G</b> | <b>3/22</b> | <b>(2006.01)</b> | G09G | 3/22 | H       |

| <b>G09G</b> | <b>3/20</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 1 1 J |

| <b>H04N</b> | <b>5/66</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 1 2 U |

|             |             |                  | G09G | 3/20 | 6 2 3 C |

|             |             |                  | G09G | 3/20 | 6 4 1 A |

請求項の数 8 (全 48 頁) 最終頁に続く

(21) 出願番号

特願2002-361282 (P2002-361282)

(22) 出願日

平成14年12月12日 (2002.12.12)

(65) 公開番号

特開2003-241707 (P2003-241707A)

(43) 公開日

平成15年8月29日 (2003.8.29)

審査請求日

平成17年11月24日 (2005.11.24)

(31) 優先権主張番号

特願2001-379276 (P2001-379276)

(32) 優先日

平成13年12月12日 (2001.12.12)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100085006

弁理士 世良 和信

(74) 代理人 100100549

弁理士 川口 嘉之

(74) 代理人 100106622

弁理士 和久田 純一

(72) 発明者 阿部 直人

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社 内

(72) 発明者 稲村 浩平

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社 内

最終頁に続く

(54) 【発明の名称】 画像表示装置

(57) 【特許請求の範囲】

## 【請求項 1】

複数の走査配線と、

複数の変調配線と、

該走査配線と変調配線によってマトリクス接続される複数の電子放出素子と、該電子放出素子が放出する電子によって発光する蛍光体と、

前記走査配線に接続される走査回路と、

前記変調配線に接続される変調回路と、

入力される画像データに対して、前記蛍光体の発光特性の非線形性を補正する変換を施す階調変換手段と、

該階調変換手段から出力される画像データに対応して、前記走査配線における電圧降下の影響を補正した画像データを出力する補正画像データ算出手段と、

前記変調回路の入力範囲を超える値が前記変調回路に入力されることを抑制するための係数であって、前記補正した画像データ、もしくは、前記階調変換手段から出力された画像データであって前記補正が施される前の画像データ、に乗算される係数を算出する算出手段と、

を有しており、

前記階調変換手段は、前記係数に応じた変換を行うことを特徴とする画像表示装置。

## 【請求項 2】

前記階調変換手段は、入力される画像データに対して前記係数を乗算する乗算器を有す

る請求項 1 に記載の画像表示装置。

【請求項 3】

前記階調変換手段は、入力される画像データに対して、異なる値を有する複数の前記係数に対応した異なる値を出力する補正テーブルを有する請求項 1 に記載の画像表示装置。

【請求項 4】

前記階調変換手段は、前記補正テーブルから出力される複数の異なる値を補間して出力する請求項 3 に記載の画像表示装置。

【請求項 5】

前記算出手段は、前記補正画像データ算出手段によって補正された画像データの値に基づいて前記係数を算出する請求項 1 に記載の画像表示装置。

10

【請求項 6】

前記階調変換手段は、前記係数によって定まる動作範囲における該蛍光体の飽和特性を打ち消すように、前記係数に応じて階調変換特性を変更する機能を有することを特徴とする請求項 1 に記載の画像表示装置。

【請求項 7】

前記算出手段は、フレームごとに前記補正画像データ算出手段の出力の最大値を検出し、該最大値が前記変調回路の入力範囲の上限に対応するように適応的に前記係数を算出することを特徴とする請求項 1 に記載の画像表示装置。

20

【請求項 8】

更に、前記変調回路の入力範囲を超える値が前記変調回路に入力されないようにするリミッタを有することを特徴とする請求項 1 に記載の画像表示装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、マトリクス配線された複数の画像形成素子を備える表示パネルを用いてテレビジョン信号やコンピュータなどの表示信号を受信し画像を表示するテレビジョン受信機やディスプレイ装置などの画像表示装置に関するものである。

【0002】

【従来の技術】

従来、 $m$  本の行配線及び  $n$  本の列配線に配線されてマトリクス状に配列された  $n \times m$  個の画像形成素子を有し、行配線に対して順次走査を行うと共に、列方向に変調を行うことによって、1行分の素子群を同時に駆動していた。

30

【0003】

このように駆動する場合には、行配線において、配線の電気抵抗により発生する電圧降下によって、表示素子の両端に印加される電圧の低下による不具合が問題となっている。

【0004】

そこで、このような表示素子への電気的な接続配線などの配線抵抗による電圧降下に起因する輝度低下を補正するために、統計演算によりその補正データを算出し、電子線要求値と補正值を合成する構成を有する画像表示装置に関する技術が、特開平 8 - 248920 号公報に開示されている。

40

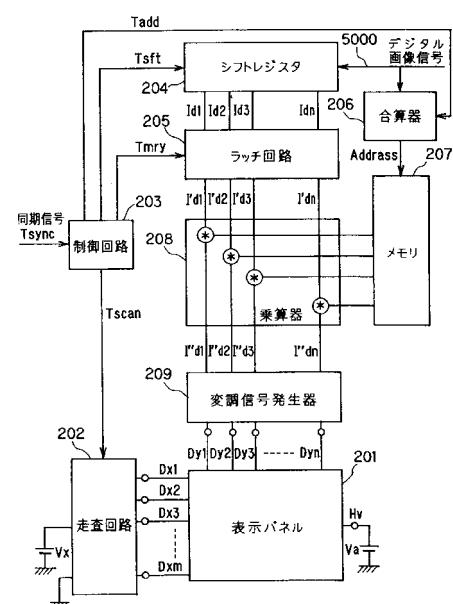

【0005】

この公報記載の画像表示装置の構成を図 38 に示す。本装置におけるデータの補正に係わる構成は概略以下の通りである。まず、ディジタル画像信号の 1 ライン分の輝度データを合算器 206 で合算し、この合算値に対応する補正率データをメモリ 207 から読み出す。一方、ディジタル画像信号はシフトレジスタ 204 においてシリアル / パラレル変換され、ラッチ回路 205 において所定時間保持された後、所定のタイミングで各列配線毎に備えられる乗算器 208 に入力される。乗算器 208 において各列配線毎に輝度データとメモリ 207 から読み出された補正データを乗算し、得られた補正後のデータは変調信号発生器 209 に転送され、補正後のデータに対応する変調信号が変調信号発生器 209 において生成され、この変調信号に基づいて表示パネルに画像が表示される。ここでは、合

50

算器 206 におけるディジタル画像信号の 1 ライン分の輝度データの合算処理のように、ディジタル画像信号に対して総和や平均を算出するというような統計的な演算処理を行い、この値に基づいて補正を行っている。

【 0006 】

【発明が解決しようとする課題】

しかしながら、上述した従来の構成においては、各列配線毎の乗算器、補正データを出力するためのメモリ、メモリにアドレス信号を与えるための合算器など大規模なハードウェアが必要であった。

【 0007 】

本発明の目的とするところは、少ないハードウェアで、表示パネルのマトリクス配線が有する電気抵抗による駆動条件の変動による輝度変動および色度変動を好適に補正できる画像表示装置を提供することにある。 10

【 0008 】

【課題を解決するための手段】

上記目的を達成するために、本発明の画像表示装置にあっては、

複数の走査配線と、

複数の変調配線と、

該走査配線と変調配線によってマトリクス接続される複数の電子放出素子と、該電子放出素子が放出する電子によって発光する蛍光体と、

前記走査配線に接続される走査回路と、

前記変調配線に接続される変調回路と、

入力される画像データに対して、前記蛍光体の発光特性の非線形性を補正する変換を施す階調変換手段と、

該階調変換手段から出力される画像データに対応して、前記走査配線における電圧降下の影響を補正した画像データを出力する補正画像データ算出手段と、 20

前記変調回路の入力範囲を超える値が前記変調回路に入力されることを抑制するための係数であって、前記補正した画像データ、もしくは、前記階調変換手段から出力された画像データであって前記補正が施される前の画像データ、に乗算される係数を算出する算出手段と、を有しており、

前記階調変換手段は、前記係数に応じた変換を行うことを特徴とする。 30

【 0014 】

【発明の実施の形態】

以下に図面を参照して、この発明の好適な実施の形態を例示的に詳しく説明する。ただし、この実施の形態に記載されている構成部品の寸法、材質、形状、その相対配置などは、特に特定的な記載がない限りは、この発明の範囲をそれらのみに限定する趣旨のものではない。

【 0015 】

( 第 1 の実施の形態 )

( 全体概要 )

冷陰極素子を単純マトリクスに配置した表示装置においては、走査配線に流れ込む電流と、走査配線の配線抵抗により電圧降下が発生し、表示画像が劣化するという現象がある。そこで、本発明の実施形態に係る画像表示装置では、このような走査配線における電圧降下が表示画像に与える影響を好適に補正する処理回路を設け、それを比較的小さな回路規模で実現するように構成した。 40

【 0016 】

補正回路は、入力画像データに応じて電圧降下のために生じる表示画像の劣化を予測計算し、それを補正する補正データを求め、入力された画像データに補正を施すものである。

【 0017 】

このような補正回路を内蔵した画像表示装置として、発明者らは以下に示すような方式の画像表示装置について鋭意検討を行ってきた。 50

## 【0018】

以下、まず、本発明の実施形態に係る画像表示装置の表示パネルの概観、表示パネルの電気的接続、表面伝導型放出素子の特性、表示パネルの駆動方法、走査配線の電気抵抗に起因する電圧降下のメカニズム、電圧降下の影響に対する補正方法及び装置について説明する。

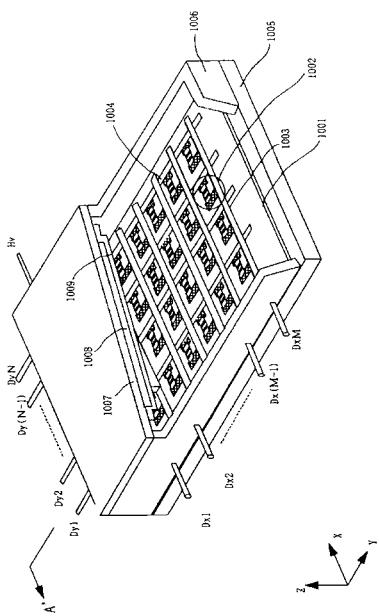

## 【0019】

(画像表示装置の概観)

図1は、本実施形態に係る画像表示装置に用いた表示パネルの斜視図であり、内部構造を示すためにパネルの一部を切り欠いて示している。図中、1005はリアプレート、1006は側壁、1007はフェースプレートであり、1005～1007により表示パネルの内部を真空に維持するための気密容器を形成している。

10

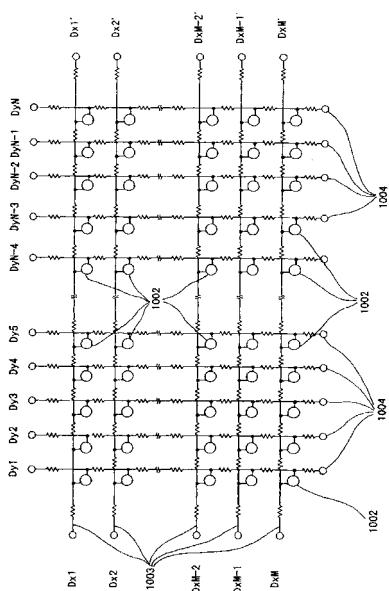

## 【0020】

リアプレート1005には、基板1001が固定されているが、該基板上には冷陰極素子1002がN×M個形成されている。行配線(走査配線)1003、列配線(変調配線)1004及び冷陰極素子は図2のように接続されている。

## 【0021】

このような結線構造を単純マトリクスと呼んでいる。

## 【0022】

また、フェースプレート1007の下面には、蛍光膜1008が形成されている。本実施形態に係る画像表示装置はカラー表示装置であるため、蛍光膜1008の部分にはCRTの分野で用いられる赤、緑、青、の3原色の蛍光体が塗り分けられている。蛍光体は、リアプレート1005の各画素(絵素)に対応してマトリクス状に形成された、冷陰極素子からの放出電子(放出電流)の照射される位置に対して、画素を形成するように構成されている。

20

## 【0023】

蛍光膜1008の下面にはメタルバック1009が形成されている。

## 【0024】

Hvは高圧端子でありメタルバック1009に電気的に接続されている。Hv端子に高電圧を印加することによりリアプレート1005とフェースプレート1007の間に高電圧が印加される。

30

## 【0025】

本実施形態では、以上のような表示パネルの中に冷陰極素子として表面伝導型放出素子を作製した。冷陰極素子としては電界放出型の素子を用いることもできる。また、冷陰極素子以外のEL素子のような自ら発光する素子をマトリクス状配線に接続して駆動する画像表示装置にも本発明を適用することができる。

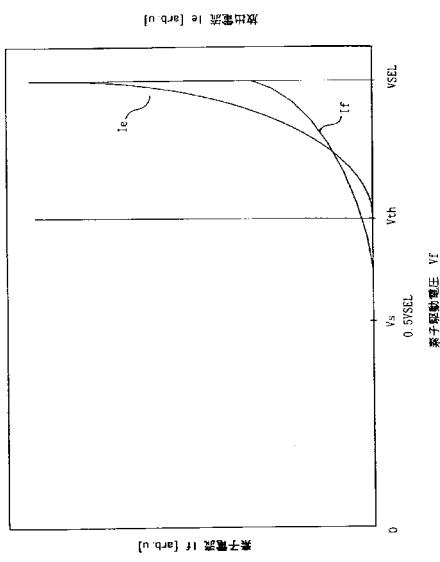

## 【0026】

(表面伝導型放出素子の特性)

表面伝導型放出素子は、図3に示すような(放出電流Ie)対(素子印加電圧Vf)特性、および(素子電流If)対(素子印加電圧Vf)特性を有する。なお、放出電流Ieは素子電流Ifに比べて著しく小さく、同一尺度で図示するのが困難であるため、2つのグラフは各々異なる尺度で図示した。

40

## 【0027】

表面伝導型放出素子は、放出電流Ieに関して以下に述べる3つの特性を有している。

## 【0028】

第一に、ある電圧(これを閾値電圧Vthと呼ぶ)以上の電圧を素子に印加すると急激に放出電流Ieが増加するが、一方、閾値電圧Vth未満の電圧では放出電流Ieはほとんど検出されない。

## 【0029】

すなわち、放出電流Ieに関して、明確な閾値電圧Vthを持った非線形素子である。

## 【0030】

50

また第二に、放出電流  $I_e$  は素子に印加する電圧  $V_f$  に依存して変化するため、電圧  $V_f$  を可変することにより、放出電流  $I_e$  の大きさを制御できる。

【0031】

また第三に、冷陰極素子は高速な応答性を有しているため、電圧  $V_f$  の印加時間により放出電流  $I_e$  の放出時間を制御できる。

【0032】

以上のような特性の利用により、表面伝導型放出素子を表示装置に好適に用いることができる。例えば、図1に示した表示パネルを用いた画像表示装置において、第一の特性を利用すれば、表示画面を順次走査して表示を行うことが可能である。すなわち、駆動中の素子には所望の発光輝度に応じて閾値電圧  $V_{th}$  以上の電圧を適宜印加し、非選択状態の素子には閾値電圧  $V_{th}$  未満の電圧を印加する。駆動する素子を順次切り替えることにより、表示画面を順次走査して表示を行うことが可能である。10

【0033】

また、第二の特性を利用することにより、素子に印加する電圧  $V_f$  により、蛍光体の発光輝度を制御することができ、画像表示を行うことが可能である。

【0034】

また、第三の特性を利用することにより、素子に電圧  $V_f$  を印加する時間により、蛍光体の発光時間を制御することができ、画像の表示を行うことができる。

【0035】

本発明の実施の形態に係る画像表示装置では上記第三の特性を用いて変調を行った。20

【0036】

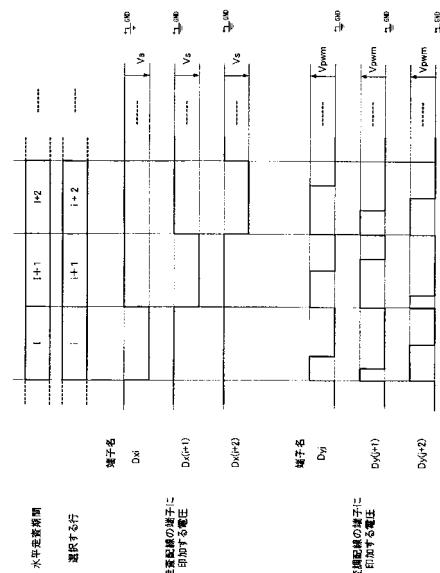

(表示パネルの駆動方法)

図4は本発明の実施の形態に係る画像表示装置の表示パネルを駆動した際に走査配線及び変調配線の電圧供給端子に印加した電圧の一例である。

【0037】

いま、水平走査期間  $T$  は  $i$  行目のピクセルを発光させる期間とする。

【0038】

$i$  行目のピクセルを発光させるためには、 $i$  行目の走査配線を選択状態とし、その電圧供給端子  $D_{x,i}$  に選択電位  $V_s$  を印加する。また、それ以外の走査配線の電圧供給端子  $D_{x,k}$  ( $k = 1, 2, \dots, N$ 、但し  $k \neq i$ ) は非選択状態とし、非選択電位  $V_{ns}$  を印加する。30

【0039】

本例では、選択電位  $V_s$  を図3に記載の電圧  $V_{SEL}$  の半分の  $-0.5 V_{SEL}$  に設定し、非選択電位  $V_{ns}$  は GND 電位とした。

【0040】

また、変調配線の電圧供給端子には、電圧振幅  $V_{pwm}$  のパルス幅変調信号を供給した。 $j$  番目の変調配線に供給するパルス幅変調信号のパルス幅は、従来、補正を行わない場合は、表示する画像の第  $i$  行第  $j$  列のピクセルの画像データの大きさに応じて決定し、すべての変調配線に各々のピクセルの画像データの大きさに応じたパルス幅変調信号を供給していた。40

【0041】

なお、本発明の実施の形態においては、後述するように、電圧降下の影響による、輝度の低下を補正するために、 $j$  番目の変調配線に供給するパルス幅変調信号のパルス幅は、表示する画像の第  $i$  行第  $j$  列のピクセルの画像データの大きさと、その補正量に応じて決定し、すべての変調配線にパルス幅変調信号を供給する。

【0042】

本実施形態では、電圧  $V_{pwm}$  の電圧は  $+0.5 V_{SEL}$  に設定した。

【0043】

表面伝導型放出素子は、図3に示したように素子の両端に電圧  $V_{SEL}$  が印加されると電子を放出させるが、印加電圧が  $V_{th}$  よりも小さい電圧では全く電子を放出しない。

10

20

30

40

50

## 【0044】

また、電圧  $V_{th}$  は図3に示すように、 $0.5 V_{SEL}$  よりも大きいという特徴がある。

## 【0045】

このため、非選択電位  $V_{ns}$  が印加されている走査配線に接続された表面伝導型放出素子からは電子は放出されない。

## 【0046】

また、同じように、パルス幅変調手段の出力がグランド電位である期間（以降、出力が“L”の期間と呼ぶ）は、選択された走査配線上の表面伝導型放出素子の両端に印加される電圧は  $V_s$  であるため、電子は放出されない。

## 【0047】

選択電位  $V_s$  が印加された走査配線上の表面伝導型放出素子からは、パルス幅変調手段の出力が  $V_{pwm}$  である期間（以降、出力が“H”の期間と呼ぶ）に応じて電子が放出される。電子が放出されれば放出された電子ビームの量に応じて前述の蛍光体が発光するため、放出された時間に応じた輝度を発光させることができる。

10

## 【0048】

本発明の実施形態に係る画像表示装置は、上述したような線順次走査、パルス幅変調することによって画像を表示している。

## 【0049】

## (走査配線での電圧降下について)

上述したように、画像表示装置の抱える根本的な課題は、表示パネルの走査配線における電圧降下によって、走査配線の電位が上昇することにより、表面伝導型放出素子に印加される電圧が減少するため、表面伝導型放出素子からの放出電流が低下してしまうことである。以下、この電圧降下の機構について説明する。

20

## 【0050】

表面伝導型放出素子の設計仕様や製法によっても異なるが、表面伝導型放出素子の1素子分の素子電流は電圧  $V_{SEL}$  を印加した場合に数  $100 \mu A$  程度である。

## 【0051】

このため、ある水平走査期間において選択された走査線の1ピクセルのみを発光させ、それ以外のピクセルは発光させない場合には、変調配線から選択行の走査配線に流入する素子電流は1ピクセル分の電流（すなわち上述の数  $100 \mu A$ ）だけであるため、電圧降下はほとんど生じることはなく、発光輝度が低下することはない。

30

## 【0052】

しかし、ある水平走査期間において、選択された行の全ピクセルを発光させる場合には、全変調配線から選択状態としている走査配線に対し、全ピクセル分の電流が流入するため、電流の総和は数  $100 mA$  ~ 数  $A$  となり、走査配線の配線抵抗によって走査配線上に電圧降下が発生していた。

## 【0053】

走査配線上に電圧降下が発生すれば、表面伝導型放出素子の両端に印加される電圧が低下する。このため表面伝導型放出素子から発光される放出電流が低下してしまい、結果として発光輝度が低下していた。

40

## 【0054】

また、さらに複雑なことに、電圧降下の大きさはパルス幅変調によって変調を行うことにより1水平走査期間の中でも変化する性質を持っている。

## 【0055】

各列に供給するパルス幅変調信号が、図4に示したように入力されるデータに対し、そのデータの大きさに依存したパルス幅の、立ち上がりが同期したパルス幅変調信号を出力する場合を考えてみる。このような場合、入力画像データにもよるが一般的には、1水平走査期間内では、パルスの立ち上がり直後ほど点灯しているピクセルの数が多く、その後輝度の低い箇所から順に消灯していくため、点灯するピクセルの数は1水平走査期間の中では、時間を追って減少する。

50

## 【0056】

したがって、走査配線上に発生する電圧降下の大きさも、1水平走査期間の初めほど大きく次第に減少していく傾向がある。

## 【0057】

パルス幅変調信号は変調の1階調に相当する時間ごとに出力が変化するため、電圧降下の時間的な変化もパルス幅変調信号の1階調に相当する時間毎に変化する。

## 【0058】

以上、走査配線における電圧降下について説明した。

## 【0059】

(電圧降下の計算方法)

10

次に、電圧降下の影響に対する補正の方法について詳述する。

## 【0060】

電圧降下の影響を低減するための補正量を求めるには、まずその第一段階として、電圧降下の大きさとその時間変化をリアルタイムに予測するハードウェアを開発することが必要とされるが、本発明のような画像表示装置の表示パネルとしては、数千本もの変調配線を備えることが一般的であり、変調配線のすべてと走査配線との交点の電圧降下を計算することは非常に困難であるとともに、それをリアルタイムに計算するハードウェアを作製することはあまり現実的ではない。

## 【0061】

そこで、同一行の位置に関して、ブロック化するとともに、画像データの振幅方向へもブロック化することにより、電圧降下量を求める。

20

## 【0062】

このようなブロック化は電圧降下における以下の特徴に基づくものである。

## 【0063】

i) 一水平走査期間のある時点においては、走査配線上に発生する電圧降下は走査配線上で空間的に連続的な量であり非常に滑らかなカーブである。

## 【0064】

i i) 電圧降下の大きさは表示画像によっても異なるが、パルス幅変調の1階調に相当する時間毎に変化し、概略的にはパルスの立ち上がり部分ほど大きく、時間的には次第に小さくなるか、もしくはその大きさを維持するかのどちらかである。

30

## 【0065】

すなわち、図4のような駆動方法では1水平走査期間内で電圧降下の大きさが増加することはない。

## 【0066】

具体的には以下で説明する縮退モデルによる電圧降下の計算を複数の時刻に対して計算することによって、電圧降下の時間変化を概略的に予測した。

## 【0067】

(縮退モデルによる電圧降下の計算)

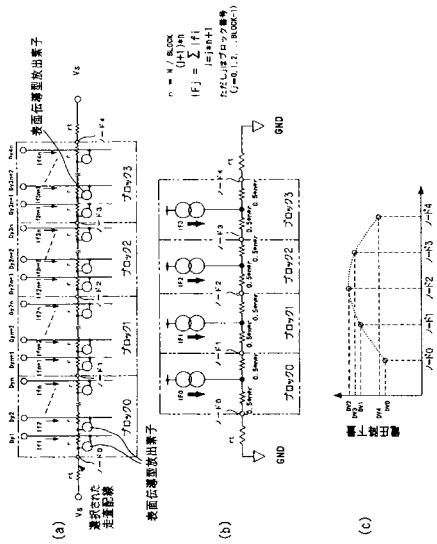

図5(a)は、縮退を行う際のブロック及びノードを説明するための図である。

40

## 【0068】

同図では図を簡略化するため、選択された走査配線と各変調配線およびその交差部に接続される表面伝導型放出素子のみを記載した。

## 【0069】

いま一水平走査期間の中のある時刻であって、選択された走査配線上の各ピクセルの点灯状態(すなわち変調手段の出力が”H”であるか、”L”であるか)が分かっているものとする。

## 【0070】

この点灯状態において、各変調配線から選択された走査配線へ流れ込む素子電流を $I_{fi}$ ( $i = 1, 2, \dots, N$ ,  $i$ は列番号)と定義する。

## 【0071】

50

また、同図に示すように、 $n$  本の変調配線と選択された走査配線のそれと交差する部分及び、その交点に配置される表面伝導型放出素子を 1 つのグループとしてブロックを定義する。本例では、ブロック分けを行うことで 4 つのブロックに分割した。

【0072】

また、各々のブロックの境界位置においてノードという位置を設定した。ノードとは、縮退モデルにおいて走査配線上に発生する電圧降下量を離散的に計算するための水平位置（基準点）である。

【0073】

本例ではブロックの境界位置に、ノード 0 ~ ノード 4 の 5 つのノードを設定した。

【0074】

図 5 (b) は縮退モデルを説明するための図である。

【0075】

縮退モデルでは同図 (a) の 1 ブロックに含まれる  $n$  本の変調配線を 1 本に縮退化し、縮退化された 1 本の変調配線が、走査配線のブロックの中央に位置するように接続した。

【0076】

また、縮退化された各々のブロックの変調配線には電流源が接続されており、各電流源から各々のブロック内の電流の総和  $I_F 0 ~ I_F 3$  が流れ込むものとした。

【0077】

即ち、 $I_F j$  ( $j = 0, 1, \dots, 3$ ) は、

【数 1】

$$I_F j = \sum_{i=j \times n+1}^{(j+1) \times n} I_F i \quad (\text{式 1})$$

として表される電流である。

【0078】

また、走査配線の両端の電位が同図 (a) の例では  $V_s$  であるのに対し、同図 (b) では GND 電位としているのは、縮退モデルでは、変調配線から選択した走査配線に流れ込む電流を上記電流源によりモデリングしたことにより、走査配線上の各部の電圧降下量は、その給電部を基準 (GND) 電位として各部の電圧 (電位差) を算出することにより計算できるためである。

【0079】

つまり、電圧降下を算出する上で基準電位として規定した。

【0080】

また、表面伝導型放出素子を省略しているのは、選択された走査配線から見た場合に、列配線から同等の電流が流れ込めば、表面伝導型放出素子の有無によらず、発生する電圧降下自体は変わらないためである。従って、ここでは、各ブロックの電流源から流れ込む電流値を各ブロック内の素子電流の総和の電流値 (式 1) に設定することで表面伝導型放出素子を省略した。

【0081】

また、各ブロックの走査配線の配線抵抗は一区間の走査配線の配線抵抗  $r$  の  $n$  倍とした（ここで一区間とは走査配線の、ある列配線との交差部とその隣の列配線との交差部の間のことを指している。また本例では、一区間の走査配線の配線抵抗は均一であるものとした。）。

【0082】

このような縮退モデルにおいて、走査配線上の各ノードにおいて発生する電圧降下量  $DV_0 ~ DV_4$  は以下のような積和形式の式、

【数 2】

10

20

30

40

50

$$\begin{aligned}

DV0 &= a_{00} \times IF0 + a_{01} \times IF1 + a_{02} \times IF2 + a_{03} \times IF3 \\

DV1 &= a_{10} \times IF0 + a_{11} \times IF1 + a_{12} \times IF2 + a_{13} \times IF3 \\

DV2 &= a_{20} \times IF0 + a_{21} \times IF1 + a_{22} \times IF2 + a_{23} \times IF3 \\

DV3 &= a_{30} \times IF0 + a_{31} \times IF1 + a_{32} \times IF2 + a_{33} \times IF3 \\

DV4 &= a_{40} \times IF0 + a_{41} \times IF1 + a_{42} \times IF2 + a_{43} \times IF3

\end{aligned}$$

により簡単に計算することができる。

【0083】

すなわち、

【数3】

$$DV_i = \sum_{j=0}^3 a_{ij} \times IF_j \quad (\text{式2})$$

$$(i = 0, 1, 2, 3, 4)$$

10

が成立する。

【0084】

ただし、 $a_{ij}$  は縮退モデルにおいて  $j$  番目のブロックだけに単位電流を注入したときに、 $i$  番目のノードに発生する電圧である（以下、これを  $a_{ij}$  と定義する。）。

【0085】

上記の  $a_{ij}$  はキルヒホフの法則により導出され、一度計算した結果をテーブルとして記憶しておけばよい。

【0086】

さらに、式1で定めた各ブロックの総和電流  $IF_0 \sim IF_3$  に対し、式3に示すような近似を行う。

【0087】

【数4】

$$IF_j = \sum_{i=j \times n+1}^{(j+1) \times n} If_i = IFS \times \sum_{i=j \times n+1}^{(j+1) \times n} Count_i \quad (\text{式3})$$

30

ただし、上式において  $Count_i$  は選択された走査線上の  $i$  番目のピクセルが点灯状態である場合には 1 をとり、消灯状態である場合には 0 をとる変数である。

【0088】

40

$IFS$  は表面伝導型放出素子 1 素子の両端に電圧  $V_{SEL}$  を印加したときに流れる素子電流  $IF$  に対し、0 ~ 1 の間の値をとる係数 をかけた量である。

【0089】

すなわち、

【数5】

$$IFS = \alpha \times IF \quad (\text{式4})$$

と定義した。

【0090】

50

式3は選択された走査配線に対し各ブロックの列配線から該ブロック内の点灯数に比例した素子電流が流れ込むものとしている。この際1素子の素子電流IFに係数 $\alpha$ をかけたものを1素子の素子電流IFSとしたのは以下の理由による。本来、電圧降下量を計算するためには、電圧降下による走査配線の電圧上昇とそれによる素子電流の減少量とを繰り返し計算することが必要であるが、この収束計算をハードウェアで計算するのは現実的でない。そこで、本発明においては、IFの収束値として近似的にIFを用いる。具体的には、電圧降下量が最大となるとき(全白のとき)のIFの低下率( $=1$ )と、電圧降下量が(最小=0)となるときのIFの低下率( $=2$ )を予め見積もっておいて、 $1$ と $2$ の平均値または $0.8 \times 1$ として求められる。

【0091】

10

図5(c)は、ある点灯状態において、縮退モデルにより各ノードの電圧降下量DV0~DV4を計算した結果の一例である。

【0092】

電圧降下は非常に滑らかなカーブとなるため、ノードとノードの間の電圧降下は近似的には図の点線に示したような値をとると想定される。

【0093】

このように、本縮退モデルを用いれば、入力された画像データに対し所望の時点でのノードの位置での電圧降下を計算することが可能である。

【0094】

以上、ある点灯状態における電圧降下量を縮退モデルを用いて簡単に計算した。

20

【0095】

選択された走査配線上に発生する電圧降下は一水平走査期間内で時間的に変化するが、これについては前述したように一水平走査期間中のいくつかの時刻に対して、その時の点灯状態を求め、その点灯状態に対し縮退モデルを用いて電圧降下を計算することにより予測した。

【0096】

なお、一水平走査期間のある時点での各ブロック内の点灯数は各ブロックの画像データを参照すれば簡単に求めることができる。

【0097】

いま、1つの例としてパルス幅変調回路への入力データのビット数が8ビットであるものとし、パルス幅変調回路は入力データの大きさに応じたパルス幅を出力する。

30

【0098】

すなわち、入力データが0のときは、出力は”L”となり、入力データが255のとき一水平走査期間の間は”H”を出力し、入力データが128のときには一水平走査期間のうち初めの半分の期間は”H”を出力し、後の半分の期間は”L”を出力するものとする。

【0099】

このような場合、パルス幅変調信号の開始時刻(本例の変調信号の例では立ち上がりの時刻)の点灯数は、パルス幅変調回路への入力データが0よりも大きいものの数をカウントすれば簡単に検出できる。

【0100】

40

同様に一水平走査期間の中央の時刻の点灯数は、パルス幅変調回路への入力データが128よりも大きいものの数をカウントすれば簡単に検出できる。

【0101】

このように画像データをある閾値に対してコンパレートし、コンパレータの出力が真である数をカウントすれば、任意の時間における点灯数が簡単に計算することができる。

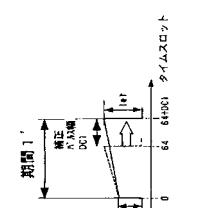

【0102】

ここで以降の説明を簡単化するため、タイムスロットという時間量を定義する。

【0103】

すなわち、タイムスロットとは、一水平走査期間のなかのパルス幅変調信号の立ち上がりからの時間を表しており、タイムスロット=0とは、パルス幅変調信号の開始時刻直後の

50

時刻を表すものと定義する。

【0104】

タイムスロット = 64 とは、パルス幅変調信号の開始時刻から、64 階調分の時間が経過した時刻を表すものと定義する。

【0105】

なお、本例ではパルス幅変調は立ち上がり時刻を基準として、そこからのパルス幅を変調した例を示したが、同様に、パルスの立ち下がり時刻を基準として、パルス幅を変調する場合でも、時間軸の進む方向とタイムスロットの進む方向が逆となるが、同様に適用することができることはいうまでもない。

【0106】

(電圧降下量から補正データの計算)

上述したように、縮退モデルを用いて繰り返し計算を行うことで一水平走査期間中の電圧降下の時間変化を近似的かつ離散的に計算することができた。

【0107】

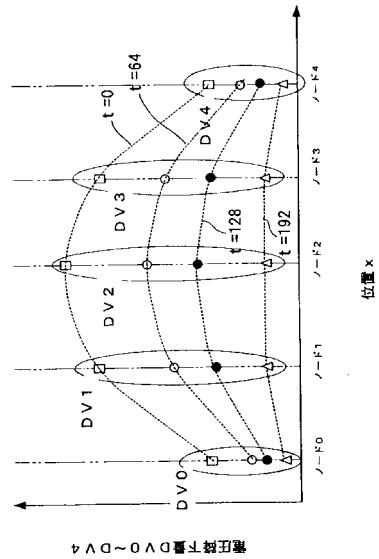

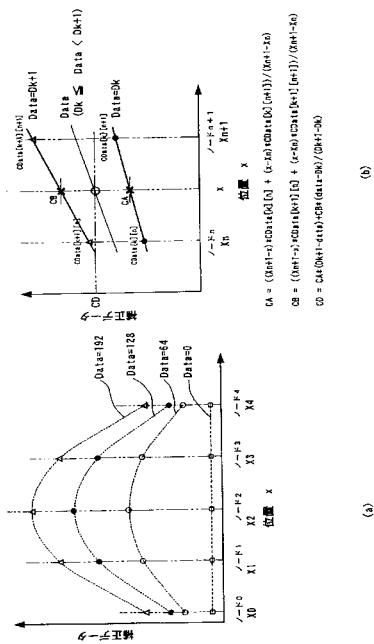

図6は、ある画像データに対して、電圧降下を繰り返し計算し、走査配線での電圧降下の時間変化を計算した例である(ここに示されている電圧降下及びその時間変化は、ある画像データに対する一例であって、別の画像データに対する電圧降下は、また別の変化をすることは当然である。)。

【0108】

同図ではタイムスロット = 0, 64, 128, 192 の4つの時点に対して、各々縮退モデルを適用して計算を行うことに、それぞれの時刻の電圧降下を離散的に計算した。

【0109】

図6では各ノードにおける電圧降下量を点線で結んでいるが、点線は図を見やすくするために記載したものであって、本縮退モデルにより計算された電圧降下は、、、、で示した各ノードの位置において離散的に計算した。

【0110】

発明者らは、電圧降下の大きさとその時間変化を計算可能となった次の段階として、電圧降下量から画像データを補正する補正データを算出する方法について検討を行った。

【0111】

図7は、選択した走査配線上に図6に示した電圧降下が発生した際に、点灯状態にある表面伝導型放出素子から放出される放出電流を見積もったグラフである。

【0112】

縦軸は電圧降下がないときに放出される放出電流の大きさを100%として、各時間、各位置の放出電流の量を百分率で表しており、横軸は水平位置を表している。

【0113】

図7に示すように、ノード2の水平位置(基準点)において、

タイムスロット = 0 の時の放出電流を  $I_{e0}$  ,

タイムスロット = 64 の時の放出電流を  $I_{e1}$  ,

タイムスロット = 128 の時の放出電流を  $I_{e2}$  ,

タイムスロットが 192 の時の放出電流を  $I_{e3}$  とする。

【0114】

図7は図6の電圧降下量と図3の“駆動電圧対放出電流”のグラフから計算した。具体的には電圧  $V_{SEL}$  から電圧降下量を引いた電圧が印加された際の放出電流の値を機械的にプロットしたものである。

【0115】

したがって、同図はあくまで点灯状態にある表面伝導型放出素子から放出される電流を意味しており、消灯状態にある表面伝導型放出素子が電流を放出することはない。

【0116】

以下に、電圧降下量から画像データを補正する補正データを算出する方法として、以下に説明を行う。

10

20

30

40

50

## 【0117】

(補正データ算出方法)

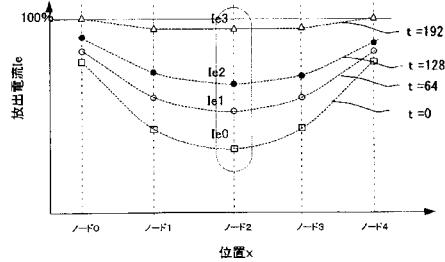

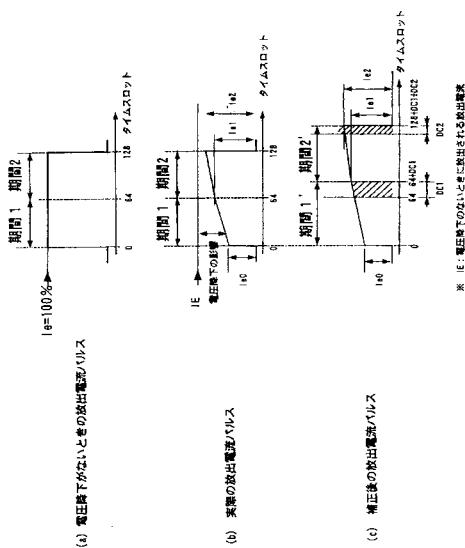

図8(a), (b), (c)は図7の放出電流の時間変化から、電圧降下量の補正データを計算する方法を説明するための図である。同図は大きさが64の画像データに対する補正データを算出した例である。

## 【0118】

輝度の発光量は、放出電流パルスによる放出電流を時間的に積分した、放出電荷量に他ならない。したがって以降では、電圧降下による輝度の変動を考えるのにあたって、放出電荷量をもとに説明を行う。

## 【0119】

いま、電圧降下の影響がない場合の放出電流をIEとし、パルス幅変調の1階調に相当する時間をtとするならば、画像データが64のときの、放出電流パルスによって放出されるべき放出電荷量Q0は放出電流パルスの振幅IEにパルス幅(64×t)をかけて、

## 【数6】

$$Q_0 = IE \times 64 \times \Delta t \quad (\text{式5})$$

として表すことができる。

## 【0120】

しかし、実際には、走査配線上の電圧降下によって放出電流が低下する現象が発生する。

## 【0121】

電圧降下の影響を考慮した放出電流パルスによる放出電荷量は、近似的には次のように計算できる。すなわち、ノード2のタイムスロット=0, 64の放出電流をそれぞれIe0, Ie1とし、0~64の間の放出電流はIe0とIe1の間を直線的に変化するものと近似すれば、この間の放出電荷量Q1は図8(b)の台形の面積となる。

## 【0122】

すなわち、

## 【数7】

$$Q_1 = (Ie0 + Ie1) \times 64 \times \Delta t \times 0.5 \quad (\text{式6})$$

として計算できる。

## 【0123】

次に、図8(c)に示すように、電圧降下による放出電流の低下分を補正するために、パルス幅をDC1だけ伸ばしたとき、電圧降下の影響を除去できたとする。

## 【0124】

また、電圧降下の補正を行い、パルス幅を伸ばした場合には、各タイムスロットにおける放出電流量は変化すると考えられるが、ここでは簡単化のため、図8(c)のように、タイムスロット=0では、放出電流がIe0、タイムスロット=(64+DC1)における放出電流がIe1になるものとする。

## 【0125】

また、タイムスロット0とタイムスロット(64+DC1)の間の放出電流は、2点の放出電流を直線で結んだ線上の値をとるものと近似する。

## 【0126】

すると、補正後の放出電流パルスによる放出電荷量Q2は、

## 【数8】

$$Q_2 = (Ie0 + Ie1) \times (64 + DC1) \times \Delta t \times 0.5 \quad (\text{式7})$$

として計算できる。

【0127】

これが前述のQ0と等しいとすれば、

【数9】

$$IE \times 64 \times \Delta t = (Ie0 + Ie1) \times (64 + DC1) \times \Delta t \times 0.5$$

となる。

【0128】

これをDC1について解けば、

【数10】

$$DC1 = ((2 \times IE - Ie0 - Ie1) / (Ie0 + Ie1)) \times 64 \quad (式8)$$

となる。

【0129】

このようにして、画像データが64の場合の補正データを算出した。

【0130】

すなわち、ノード2の位置の大きさが64の画像データに対しては式8に記載のように、

CData = DC1だけ補正量CDataを加算すればよい。

【0131】

同様に、大きさが128の画像データに対しては図9のように2つの期間に対して、また

大きさが192の画像データに対しては、図10のように、3つの期間の各々に対して補

正量を求めることができる。

【0132】

また、パルス幅が0の時には、当然ながら放出電流に対する電圧降下の影響はないため、

補正データは0とし画像データに加算する補正データCDataも0とした。

【0133】

なお、このように0, 64, 128, 192というように、とびとびの画像データに対して

補正データを計算しているのは、計算量を減らすことを狙ったものである。

【0134】

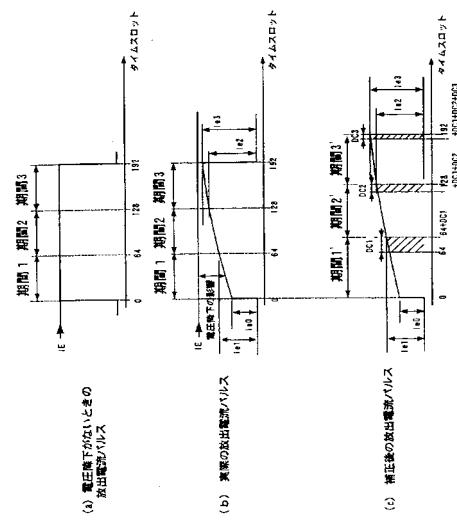

本方法により求めた、ある入力画像データに対する離散補正データの例を図11(a)に

示す。同図において横軸は水平表示位置に対応しており、各ノードの位置が記載されて

いる。また、縦軸は補正データの大きさである。

【0135】

離散補正データは図の 、 、 、 で記載したノードの位置と画像データDataの大きさ

(画像データ基準値 = 0, 64, 128, 192)に対して計算されているものである。

【0136】

(離散補正データの補間方法)

離散的に算出された補正データは、各ノードの位置に対する離散的なものであって、任意

の水平位置(列配線番号)における補正データを与えるものではない。またそれと同時に

、各ノード位置においていくつかの予め定められた画像データの基準値の大きさをもつ

画像データに対する補正データであって実際の画像データの大きさに応じた補正データをあ

たえるものではない。

【0137】

そこで、発明者らは、各列配線における入力画像データの大きさに適合した補正データを

、離散的に算出した補正データを補間することにより算出した。

【0138】

図11(b)はノードnとノードn+1の間に位置するxにおける、画像データData

10

20

30

40

50

に相当する補正データを算出する方法を示した図である。

【0139】

なお前提として、補正データはすでにノードn及びノードn+1の位置Xn及びXn+1において離散的に計算されているものとする。

【0140】

また、入力画像データであるDataは画像データ基準値のDkとDk+1の間の値をとるものとする。

【0141】

いま、ノードnのk番目の画像データの基準値に対する離散補正データをCData[k][n]と表記するならば、位置xにおけるパルス幅Dkの補正データCAは、CData[k][n]とCData[k][n+1]の値を用いて、直線近似により、以下のように計算できる。

【0142】

すなわち、

【数11】

$$CA = \frac{(X_{n+1} - x) \times CData[k][n] + (x - X_n) \times CData[k][n+1]}{X_{n+1} - X_n} \quad (式9)$$

10

20

となる。

【0143】

ただし、Xn、Xn+1はそれぞれノードn、(n+1)の水平表示位置であって、前述したブロックを決定するときに定められる定数である。

【0144】

また、位置xにおける画像データDk+1の補正データCBは以下のように計算できる。

【0145】

すなわち、

【数12】

$$CB = \frac{(X_{n+1} - x) \times CData[k+1][n] + (x - X_n) \times CData[k+1][n+1]}{X_{n+1} - X_n} \quad (式10)$$

30

となる。

【0146】

CAとCBの補正データを直線近似することにより、位置xにおける画像データDataに対する補正データCDは、以下のように計算できる。

【0147】

すなわち、

【数13】

$$CD = \frac{CA \times (D_{k+1} - Data) + CB \times (Data - D_k)}{D_{k+1} - D_k} \quad (式11)$$

40

となる。

【0148】

以上のように、離散補正データから実際の位置や画像データの大きさに適合した補正データ

50

タを算出するためには、式9～式11に記載した方法により簡単に計算できる。

【0149】

図11(a)のノード間を結ぶ破線は以上の計算により、離散的補正データが補間された結果である。図からわかるように、本発明の電圧降下補正法においては、画像データが0のときは電圧降下が起こらないので、位置xについて同じ補正データを算出するが（もちろん補正データが0であることも含む）、画像データが0でない同一の画像データに対しては、位置x、即ち画面の水平方向について、なだらかな分布をもつ補正データを算出する。但し、走査線の方向が画面の垂直方向である場合は、画面の垂直方向について、なだらかな分布をもつ補正データとなる。

【0150】

このようにして算出した補正データを画像データに加算して画像データを補正し、補正後の画像データ（補正画像データと呼ぶ）に応じてパルス幅変調を行えば、従来からの課題であった表示画像における、電圧降下による影響を低減することができ、画質を向上させることができる。

【0151】

また、予てからの課題であった補正のためのハードウェアも、これまで説明してきた縮退化などの近似を導入することにより、計算量を低減化することができるため非常に小規模なハードウェアで構成することができるという優れたメリットがあった。

【0152】

（システム全体と各部分の機能説明）

次に、補正データ算出手段を内蔵した画像表示装置のハードウェアについて説明する。

【0153】

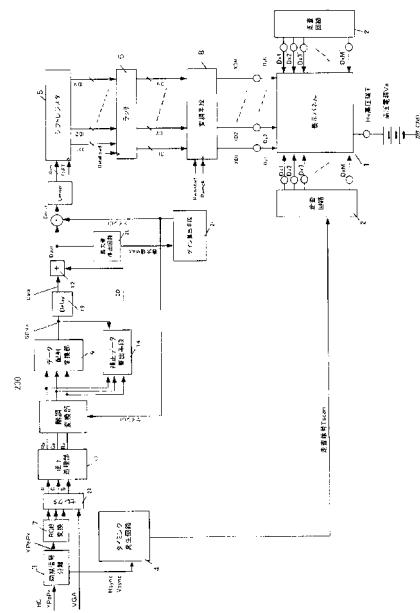

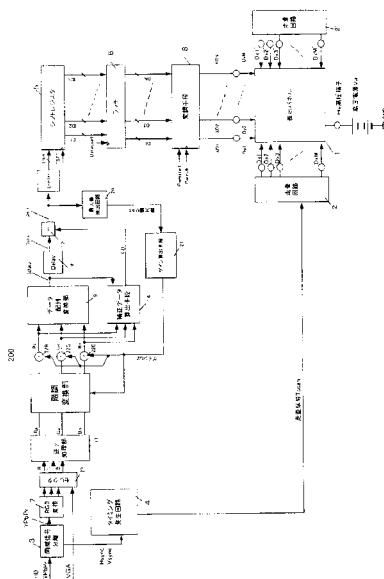

図12はその回路構成の概略を示すブロック図である。図において1は図1の表示パネル、D<sub>x</sub>1～D<sub>x</sub>M及びD<sub>x</sub>1'～D<sub>x</sub>M'は表示パネルの走査配線の電圧供給端子、D<sub>y</sub>1～D<sub>y</sub>Nは表示パネルの変調配線の電圧供給端子、H<sub>v</sub>はフェースプレートとリアプレートの間に加速電圧を印加するための高圧供給端子、V<sub>a</sub>は高圧電源、2は走査回路、3は同期信号分離回路、4はタイミング発生回路、7は同期分離回路3によりY P b P r信号をR G Bに変換するための変換回路、23はテレビジョンの映像信号とコンピュータの映像信号を切り替えるためのセレクタ、17は逆処理部、5は画像データ1ライン分のシフトレジスタ、6は画像データ1ライン分のラッチ回路、8は表示パネルの変調配線に変調信号を出力するパルス幅変調手段、12は加算器、14は補正データ算出手段、20は最大値検出手段、21はゲイン算出手段、200は階調変換部である。

【0154】

階調変換部200の説明は後述するので、以下の説明では階調変換部200が無いものとして説明していく。

【0155】

また、同図においてR、G、BはR G Bパラレルの入力映像データ、R<sub>a</sub>、G<sub>a</sub>、B<sub>a</sub>は後述する逆変換処理を施したR G Bパラレルの映像データ、Dataはデータ配列変換部によりパラレル・シリアル変換された画像データ、CDは補正データ算出手段により算出された補正データ、Do utは加算器により画像データに補正データを加算することにより、補正された画像データ（補正画像データ）である。

【0156】

（同期分離回路、セレクタ）

本実施形態の画像表示装置は、NTSCや、PAL、SECAM、HDTVなどのテレビジョン信号や、コンピュータの出力であるVGAなどをともに表示することができる。

【0157】

HDTV方式の映像信号は、まず同期分離回路3により同期信号V sync, H syncを分離し、タイミング発生回路に供給する。同期分離された映像信号は、R G B変換手段に供給される。R G B変換手段の内部には、Y P b P rからR G Bへの変換回路の他に、不図示のローパスフィルタやA/D変換器などが設けられており、Y P b P rをディジタル

10

20

30

40

50

ル R G B 信号へと変換し、セレクタ 2 3 へと供給されている。

【 0 1 5 8 】

V G A などのコンピュータの出力する映像信号は、不図示の A / D 変換器により A / D 変換され、セレクタ 2 3 へと供給される。

【 0 1 5 9 】

セレクタ 2 3 はユーザが表示したい映像信号がいずれであるかに基づいて、テレビジョン信号と、コンピュータ信号を適宜切り替えて出力する。

【 0 1 6 0 】

( タイミング発生回路 )

タイミング発生回路は、P L L 回路を内蔵しており、様々な映像フォーマットに対応したタイミング信号を発生し、各部の動作タイミング信号を発生する回路である。 10

【 0 1 6 1 】

タイミング発生回路 4 が発生するタイミング信号としては、シフトレジスタ 5 の動作タイミングを制御する T s f t 、シフトレジスタから、ラッチ回路 6 へデータをラッチするための制御信号 D a t a l o a d 、変調手段 8 のパルス幅変調開始信号 P w m s t a r t , パルス幅変調のためのクロック P w m c l k 、走査回路 2 の動作を制御する T s c a n などがある。

【 0 1 6 2 】

( 走査回路 )

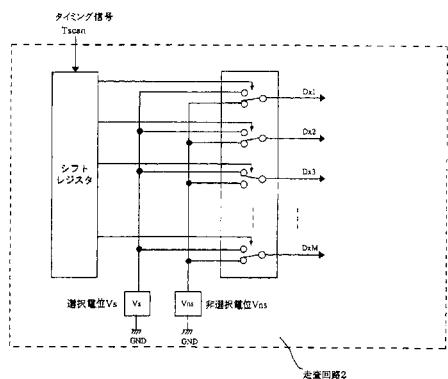

図 1 3 に示すように、走査回路 2 及び 2 ' は、表示パネルを一水平走査期間に 1 行ずつ順次走査するために、接続端子 D x 1 ~ D x M に対して選択電位 V s または非選択電位 V n s を出力する回路である。 20

【 0 1 6 3 】

走査回路 2 及び 2 ' はタイミング発生回路 4 からのタイミング信号 T s c a n に同期して、一水平期間ごとに選択している走査配線を順次切り替え、走査を行う回路である。

【 0 1 6 4 】

なお、T s c a n は垂直同期信号及び水平同期信号などから作られるタイミング信号群である。

【 0 1 6 5 】

走査回路 2 及び 2 ' は、図 1 3 に示すようにそれぞれ M 個のスイッチとシフトレジスタなどから構成される。これらのスイッチはトランジスタや F E T により構成するのが好ましい。 30

【 0 1 6 6 】

なお、走査配線での電圧降下を低減するためには、走査回路は図 1 2 に示したように、表示パネルの走査配線の両端に接続され、両端からドライブされることが好ましい。

【 0 1 6 7 】

一方、本発明の実施の形態では、走査回路が走査配線の両端に接続されていない場合でも有効であり、式 2 のパラメータを変更するだけで適用できる。

【 0 1 6 8 】

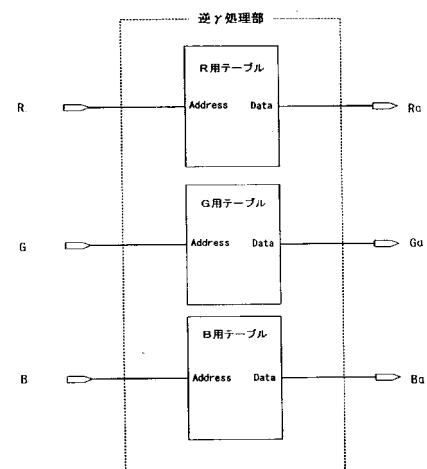

( 逆 处理部 )

C R T は入力に対しほぼ 2 . 2 乗の発光特性（以降逆 特性とよぶ）を備えている。 40

【 0 1 6 9 】

入力映像信号は C R T のこのような特性が考慮されており、C R T に表示した際にリニアな発光特性となるように一般に 0 . 4 5 乗の 特性にしたがって変換される。

【 0 1 7 0 】

一方、本発明の実施の形態に係る画像表示装置の表示パネルは駆動電圧の印加時間により変調を施す場合、印加時間に対しほぼリニアな発光特性を有しているため、入力映像信号を逆 特性にもとづいて変換（以降逆 変換とよぶ）する必要がある。

【 0 1 7 1 】

図 1 2 に記載した逆 处理部は、入力映像信号を逆 変換するためのブロックである。 50

## 【0172】

本実施形態の逆 处理部は、上記逆 変換処理をメモリによって構成した。

## 【0173】

逆 处理部は、映像信号 R , G , B のビット数を 8 ビットとし、逆 处理部の出力である映像信号 R a , G a , B a のビット数を同じく 8 ビットとして、アドレス 8 ビット、データ 8 ビットのメモリを各色ごと用いることにより構成した（図 14）。

## 【0174】

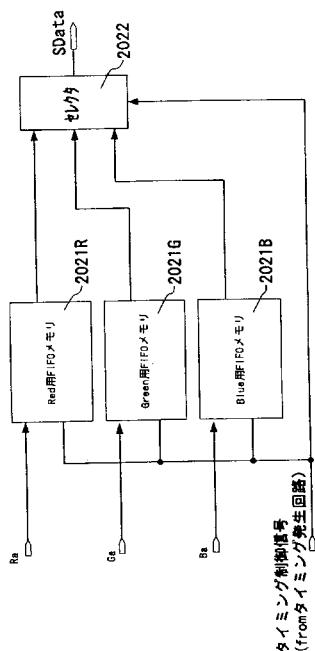

## （データ配列変換部）

データ配列変換部 9 は R G B パラレルな映像信号である R a , G a , B a を表示パネルの画素配列に合わせてパラレル・シリアル変換する回路である。データ配列変換部 9 の構成は図 15 に示したように R G B 各色ごとの F I F O ( F i r s t I n F i r s t O u t ) メモリ 2 0 2 1 R , 2 0 2 1 G , 2 0 2 1 B とセレクタ 2 0 2 2 から構成される。

10

## 【0175】

同図では図示していないが、F I F O メモリは水平画素数ワードのメモリを奇数ライン用と偶数ライン用の 2 本備えている。奇数行目の映像データが入力された際には、奇数ライン用の F I F O にデータが書き込まれる一方、偶数ライン用の F I F O メモリから一つ前の水平走査期間に蓄積された画像データが読み出される。偶数行目の映像データが入力された際には偶数ライン用の F I F O にデータが書き込まれる一方、奇数ライン用 F I F O メモリから一つ前の水平期間に蓄積された画像データが読み出される。

## 【0176】

20

F I F O メモリから読み出されたデータは、セレクタにより表示パネルの画素配列にしたがって、パラレル・シリアル変換され、R G B のシリアル画像データ S D a t a として出力される。詳細については記載しないが、タイミング発生回路 4 からのタイミング制御信号に基づいて動作する。

## 【0177】

## （遅延回路 19）

データ配列変換部により並び替えが行われた画像データ S D a t a は補正データ算出手段と遅延回路 19 に入力される。後述する補正データ算出手段の補正データ補間部はタイミング制御回路からの水平位置情報 x と画像データ S D a t a の値を参照して、それらにあった補正データ C D を算出する。

30

## 【0178】

遅延回路 19 は、補正データ算出（前述の補正データの補間処理）にかかる時間を吸収するため設けられており、加算器で画像データに補正データが加算される際に、画像データにそれに対応した補正データが正しく加算されるよう遅延を行う手段である。同手段はフリップフロップを用いることにより構成できる。

## 【0179】

## （加算器 12）

加算器 12 は補正データ算出手段からの補正データ C D と画像データ D a t a を加算する手段である。加算を行うことにより画像データ D a t a は補正が施され、補正画像データ D o u t として最大値検出回路及び乗算器へ転送される。

40

## 【0180】

なお加算器の出力である補正画像データのビット数は画像データに補正データを加算した際にオーバーフローが起きないように決定することが好ましい。

## 【0181】

より具体的には、画像データ D a t a が 8 ビットのデータ幅であって、最大値が 2 5 5 、補正データ C D は 7 ビットのデータ幅を持っていて、最大値が 1 2 0 であったとする。

## 【0182】

このとき加算結果の最大値は、 $255 + 120 = 375$  になった。

## 【0183】

## （オーバーフロー処理）

50

本発明の実施の形態では、算出した補正データを画像データに加算した補正画像データによって補正を実現することについてはすでに述べたとおりである。

【0184】

いま、変調手段のビット数が8ビットであって、加算器の出力である補正画像データDoutのビット数が10ビットであるものとする。

【0185】

すると、補正画像データを変調手段の入力にそのまま接続してしまうと、オーバーフローがおきることになる。

【0186】

そこで変調手段に入力される前に、補正画像データの振幅を調整する必要がある。

10

【0187】

オーバーフローを防止するための構成として、入力画像データが最大である全白パターン（画像データのビット数を8ビットとすると、(R, G, B) = (FFh, FFh, FFh)）を入力した際の、補正画像データの最大値を予め見積もり、それが変調手段の入力範囲に収まるようなゲインを補正画像データに乗算してもよい。

【0188】

以下、本方法を固定ゲイン法と呼ぶ。

【0189】

固定ゲイン法では、オーバーフローは発生しないが、平均輝度が低い画像については、より大きなゲインで表示ができるのにもかかわらず、小さなゲインが乗算されてしまうため、表示画像の輝度が暗くなることがある。

20

【0190】

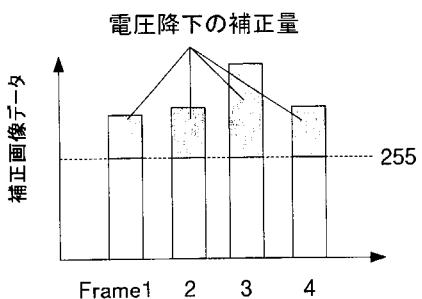

これに対し、フレームごとの補正画像データの最大値を検出し、この最大値が変調手段の入力範囲におさまるようなゲインを算出し、ゲインと補正画像データを乗算してオーバーフローを防止してもよい。

【0191】

以下、本方法を適応型ゲイン法と呼ぶ。

【0192】

適応型ゲイン法では、補正画像データDoutのフレームごとの最大値MAXを検出するための最大値検出手段20と、最大値から補正画像データに乗算するためのゲインG1を算出するためのゲイン算出手段21、及び補正画像データDoutとゲインG1を乗算するための乗算器などが必要である。

30

【0193】

なお、適応型ゲイン法では、オーバーフローを防止するためのゲインを算出するのは、フレームを単位として算出することが好ましい。

【0194】

たとえば1水平ラインごとにゲインを算出してオーバーフローを防止することもできるが、その場合1水平ラインごとのゲインの違いにより、表示画像に違和感が発生するため好ましくない。

【0195】

40

以上、固定ゲイン法、および適応型ゲイン法の概略について説明した。

【0196】

発明者らは、いずれの方法でゲインを算出しても好適に補正画像データの振幅を調整できることを確認している。

【0197】

そこで本実施形態では、適応型ゲイン法により振幅調整を行うこととした。

【0198】

以降、本実施形態では適応型ゲイン法により補正画像データの振幅調整を行うための、回路構成について詳しく説明する。

【0199】

50

## (最大値検出手段 20)

本発明の最大値検出手段 20 は図 12 に示すように、各部と接続されている。

## 【0200】

同手段は、コンパレータとレジスタなどによって簡単に構成できる回路である。同手段は、レジスタに記憶されている値と、順次転送されてくる補正画像データの大きさを比較し、補正画像データの方がレジスタの値よりも大きければ、レジスタの値をそのデータ値で更新する回路である。

## 【0201】

レジスタの値は、フレームの先頭で 0 にクリアすれば、フレームの終了時には、そのフレーム中の補正画像データの最大値がレジスタに格納される。

10

## 【0202】

このようにして検出された補正画像データの最大値は、ゲイン算出手段 21 へと転送される。

## 【0203】

## (ゲイン算出手段)

ゲイン算出手段 21 は、適応型ゲイン法に基づいて補正画像データ  $D_{out}$  が変調手段の入力範囲におさまるように振幅調整を行うためのゲインを算出する手段である。

## 【0204】

ゲインは、最大値検出手段 20 の検出した最大値を MAX、変調手段の入力範囲の最大値を INMAX とすると、

20

## 【数 14】

$$\text{ゲイン } G \leq \text{INMAX} / \text{MAX} \quad (\text{式 12})$$

となるように決定すればよい(第 1 の方法)。

## 【0205】

ゲイン算出手段 21 では、垂直帰線期間においてゲインを更新して 1 フレーム毎にゲインの値が変更される。

## 【0206】

なお、本発明の実施の形態に係る画像表示装置の構成では、1 フレーム前の補正画像データの最大値を用いて、現在のフレームの補正画像データに乗算するゲインを算出する構成となっている。

30

## 【0207】

したがって、厳密には、フレームごとの補正画像データの違いから、オーバーフローが起きることある。

## 【0208】

このような課題に対し、補正画像データとゲインを乗算する乗算器の出力に対し後述するリミッタ手段を設け、乗算器の出力が変調手段の入力範囲に収まるように回路を設計したところ好ましかった。

## 【0209】

上記のオーバーフロー処理は、隣接するフレーム間の補正画像データ(画像データ)の相関を利用してオーバーフロー処理を行っていると考えることができる。

40

## 【0210】

なお、最大値検出手段と、乗算器の間にフレームメモリを設ければ、時間的な遅延のない構成でオーバーフローを防止することができる。

## 【0211】

また、本発明者らは、適応型ゲイン法のゲイン決定方法は、以下のような方法によってゲインを算出してもよいことを確認している。

## 【0212】

すなわち、現在のフレームの補正画像データに施すゲインとしては、現在のフレームより

50

も以前のフレームで検出された補正画像データの最大値をフレーム方向に平滑化（平均化）し、その平均値  $A_{MAX}$  に対し、

【数15】

$$\text{ゲイン } G \leq I_{NMAX} / A_{MAX} \quad (\text{式13})$$

となるように決定すればよい（第2の方法）。

【0213】

また、3番目の方法は、式12により各々のフレームごとのゲイン  $G_1$  を算出し、それを平均化して現在のゲインを算出してもよい。

10

【0214】

発明者らは、これら3つの方法のうち、どの方法も好ましいことを確認しているが、その一方で第1の方法よりも、第2、第3の方法の方が、表示画像におけるフリッカが大きく減少されるという別の効果があり非常に好適である（これについては後で図16を用いて説明する。）。

【0215】

発明者らは、第2の方法、第3の方法に対して、平均化するフレームの枚数について検討を行ったが、たとえば16フレーム～64フレームを平均化したところフリッカの少ない、好ましい画像が得られた。

【0216】

なお、第2、第3の方法の場合においても、第1の方法と同様に（補正）画像データにフレーム間の相関があることにより、オーバーフローが発生する確率を減少させることができが、完全にオーバーフローを防止することができない。

20

【0217】

このための対策としては、上述の方法で概略的にオーバーフローを防止するとともに、乗算器の出力にリミッタを設けて完全にオーバーフローを防止したところ、さらに好ましかった。

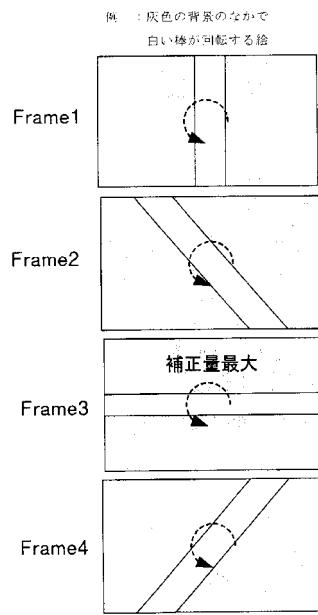

【0218】

図16は、第1の方法と、第2の方法を例に挙げて、フリッカについて説明するための図である。

30

【0219】

同図は、グレーの背景のなかで、白い棒が反時計周りに回転する動画像の例である。このような画像を表示する場合、棒が回転するのに合わせて、フレーム毎に補正データ  $C_D$  の大きさが変化する。

【0220】

図17はこのような動画像を補正した際の補正画像データを説明するための図である。同図では各々の補正画像データのうち、各々のフレームで最大となったものを抜き出してグラフ化したものである。

【0221】

なお、同図の白の部分は元々の画像データ、灰色の部分は補正を行うことによって伸長された部分に相当する。

40

【0222】

図16のような画像を表示した場合、連続するフレームの補正画像データの最大値が図17に示すように変動する。

【0223】

したがって、式12に示したようにフレームごとにゲインを設定すると、図18（a）に示すようにフレーム毎のゲインの変動が激しくなるため、結果として表示画像の輝度変動が激しくなり、フリッカ感が発生する。

【0224】

これに対し式13によってゲインを決定した場合は、ゲインが平均化されるため、図18

50

(b) に示したように、ゲインの変動が小さくなり、輝度の変動が少なくなるためフリッカ感が減少するという優れた効果があった。

【0225】

なお、同図 (b) では白丸のグラフが式 12 によるゲイン、黒丸のグラフが式 13 による平均化されたゲインである。

【0226】

第 3 の方法についてはここでは詳しく考察しなかったが、第 2 の方法と同様にゲインの変動が小さくなるためフリッカが減少することを発明者らは確認している。

【0227】

また、ゲイン算出手段 21 は、上述のような連続的なシーンの画面に対しては、ゲインを平均化するが、一方、画像のシーンが変わった際には、シーンが変わったあのゲインに速やかに変化させることができた。

【0228】

これに対しゲイン算出手段 21 は、シーン切り替えしきい値  $G_{th}$  なる、あらかじめ設定された閾値を設けておき、式 12 によって計算した 1 つ前のフレームのゲインを  $G_B$ 、前のフレームの最大値検出手段 20 の検出した前記補正画像データの最大値から式 12 によって計算されるゲインを  $G_N$ 、 $G_N - G_B$  の差の絶対値を  $G$  とすると、

$$G = |G_N - G_B| > G_{th} \text{ ならば、}$$

ゲイン  $G_1 = (G_N - G_B) \times A + G_B$  として演算する一方、

$$G = |G_N - G_B| \leq G_{th} \text{ ならば、}$$

$$\text{ゲイン } G_1 = (G_N - G_B) \times B + G_B$$

(ただし  $A, B$  は、 $1 - A - B > 0$  なる値を持つ実数) として次のフレームのゲインを平滑化して算出したところ好ましかった。

【0229】

特に  $A$ 、及び  $B$  の値としては、 $A = 1$ 、 $B = 1 / 16 \sim 1 / 64$  程度に設定したところ好ましかった。

【0230】

(乗算器)

ゲイン算出手段で算出されたゲイン  $G_1$  と加算器の出力である補正画像データ  $D_{out}$  は、図 12 の乗算器によって乗算され、振幅が調整された補正画像データ  $D_{mul}$  としてリミッタ回路へ転送される。

【0231】

(リミッタ手段)

以上のようにして、オーバーフローがおきないようにゲインを決定できれば問題ないが、上述したいくつかのゲイン決定方法によれば、必ずオーバーフローがおきないようにゲインを決定することは困難であるので、リミッタ (Limiter) を設けておくこともできる。

【0232】

リミッタは、予め設定されたリミット値を有し、リミッタに入力される出力データ  $D_{mul}$  とリミット値を比較し、出力データよりもリミット値が小さければ、リミット値を出力し、出力データよりもリミット値が大きければ、出力データを出力する (図 12 における信号名は補正画像データ  $D_{lim}$ )。

【0233】

リミッタ手段によって、変調手段の入力範囲に完全に制限された補正画像データ  $D_{lim}$  は、シフトレジスタ、ラッチを介して変調手段へと供給される。

【0234】

(階調変換手段)

図 12 の階調変換部 200 の動作の詳細を示す前に、電圧低下の影響の補正を行わず階調変換部 200 を使わない画像表示装置を実現した場合について説明する。

【0235】

10

20

30

40

50

本発明者らは、電圧降下の影響の補正を行わず階調変換部 200 が無い構成の画像表示装置では、以下の現象を確認した。

【0236】

すなわち、

A. 画像データの階調数（駆動するパルス幅）が 255（8ビットデータ幅において）で微小領域を表示させた場合に比べ、階調数が少ない画像データ（暗い絵）は、赤みがかって表示される

B. 画像データの階調数（駆動するパルス幅）が 255（8ビットデータ幅において）で微小領域を表示させた場合に比べ、画面全体を画像データの階調数が 255 で表示させた場合に赤みがかって表示されるという現象である。

10

【0237】

本発明者らは、これらの現象を以下のような理由であると解析した。

【0238】

すなわち、赤の蛍光体は投入電荷量が多いとき発光効率が飽和する傾向があった。そのため画像データの階調数が 255 で微小領域を表示させた場合、飽和が大きくなつた。つまり走査配線の電圧降下が少ないため放出電流が大きく、相対的に長い時間にわたって蛍光体に電子が衝突しているため、投入電荷量が多く赤の蛍光体は飽和している。そのため、画像データの階調数が 255 で微小領域を表示させた場合を基準にすると、上記 A. B. の場合は、赤の蛍光体に投入する電荷量は小さいため、赤の蛍光体の飽和が少なく、相対的に赤の発光強度が大きくなり、その結果、表示画像が赤みがかって表示されていた。

20

【0239】

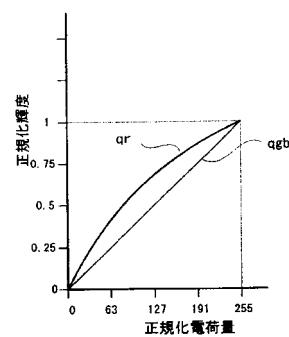

図 19 に、電圧降下の補正を行わず、階調変換部が無い時の階調特性を模式的な図を示す。

【0240】

図 19 において、横軸は変調手段が変調配線を駆動するパルス幅、縦軸は画像データの階調数が 255 で微小領域を表示させた場合（走査配線の電圧降下がほとんど無い場合）の各色の輝度で正規化した正規化輝度である。図 19 において、a1gb は、走査配線の電圧降下がほとんど無い場合の緑と青の階調特性、a1r は、走査配線の電圧降下がほとんど無い場合の赤の階調特性である。

30

【0241】

また、図 19 において、c1gb は、走査配線上の全表示素子が点灯した場合の最大の電圧降下が発生した時の緑と青の階調特性、c1r は、走査配線上の全表示素子が点灯した場合の最大の電圧降下が発生した時の赤の階調特性である。

【0242】

c1gb、c1r は、画像データの階調数が 255 で微小領域を表示させた場合の輝度で正規化した。同図では、駆動パルス幅が 255 の時に緑と青の正規化輝度が 1/4 になつたとして図示してある。

【0243】

図 19 において、b1gb は、a1gb の輝度と c1gb の輝度の中間の輝度が出る電圧降下が発生した時の緑と青の階調特性、b1r は、同電圧における赤の階調特性である。同様に、画像データの階調数が 255 で微小領域を表示させた場合の輝度で正規化した。

40

【0244】

図 19 に示す輝度と駆動パルス幅（補正画像データの値）の特性は、電圧降下量で変化し、実際の画像を表示している時の電子放出素子の駆動電圧は、画像・素子の位置により変化し、上記特性を完全に打ち消す変換を実現するのは難しかつた。

【0245】

本発明者らは、鋭意検討を重ねた結果、表面伝導型電子放出素子を用いた表示パネルの電圧降下の影響を補正した駆動において以下のことが分かった。

【0246】

（1）電圧降下の影響を補正する本発明の実施の形態に係る方法は、入力される画像デー

50

タに対して、電圧降下が無い場合の放出電流量  $I_E$  に画像データで決まるパルス幅を乗じた放出電荷量になるように、パルス幅を調整したデータ（補正画像データ）を算出し、前記パルス幅で変調手段は表示パネルを駆動する。

【0247】

(2) そして、前記補正画像データの最大値が変調手段の入力範囲を超える時、オーバーフロー処理を行い、ゲインが補正画像データに乗じられる。そして、補正画像データを変調手段の入力範囲に収める。

【0248】

(3) 蛍光体の飽和特性（特に赤の蛍光体の特性）は、実際に表示パネルを駆動する条件のパルス幅や電子放出素子の放出電流値においては、ほぼ放出電荷量により決まる特性であつた。

10

【0249】

すなわち、(1) は、「電圧降下の影響を補正した場合、実際の表示パネルで発生している電圧降下や、実際の駆動しているパルス幅にかかわらず、電圧降下が無い場合の放出電流  $I_E$  に画像データで決まるパルス幅を乗じた放出電荷量が蛍光体に入射する。」ことを示している（すなわち画像データに対応した電荷量になるように放出電荷量の変動を補正する放出電荷量補正を行うことを示している）。

【0250】

(2) は、「オーバーフロー処理した場合、電圧降下が無い場合の放出電流  $I_E$  に画像データのゲイン倍した値で決まるパルス幅を乗じた放出電荷量が蛍光体に入射する。」ことを示している。

20

【0251】

さらに、(3) は、蛍光体の飽和特性（特に赤の蛍光体の特性）は放出電荷量のみにより決定できることを示している。

【0252】

以上、(1), (2), (3) の特徴を熟考し、階調変換部 200 を持つ構成の画像表示装置を発明した。

【0253】

実際の階調変換部 200 の構成を説明する前に、階調変換部 200 の階調変換特性の概略を説明する。

30

【0254】

図 20 に、横軸は表面伝導型電子放出素子が放出する放出電荷量、縦軸は各色の輝度を示す。図 20 において説明を簡略化するために、電圧降下が無い場合の放出電流量  $I_E$  をパルス幅変調の 1 階調分の時間  $t$  だけ投入した電荷量を 1 として、横軸の放出電荷量を正規化して示している。正規化した結果、放出電荷量の最大値は 255 となる。すなわち、変調手段の駆動パルス幅が 255（最大）で微小領域を表示させた場合（走査配線の電圧降下がほとんど無い場合）の放出電荷量（最大放出電荷量）は 255 である。

【0255】

また、縦軸は電圧降下が無い場合の放出電流量  $I_E$  でパルス幅が 255 階調（ $255 \times t$ ）の時の各色の輝度が 1 になるように正規化して示した。

40

【0256】

本発明の実施の形態における電圧降下の影響を補正することによって、電圧降下が無い場合の放出電流量  $I_E$  に画像データで決まるパルス幅を乗じた放出電荷量が蛍光体に入射される様にパルス幅が調整される（(1) の特徴）。

【0257】

そのため、電圧降下の影響を補正した場合、横軸は画像データの 0 から 255 に対応する。

【0258】

図 20 で  $q_g$   $q_b$  は緑・青の階調特性であり、 $q_r$  は赤の階調特性である。図 20 は、例えばパルス幅や、放出電流（駆動電圧）を変化させ実測し求めると良い。

50

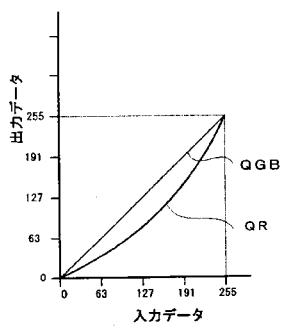

## 【0259】

オーバーフロー処理を行わない場合は、放出電荷量と画像データが等価なため、図20の特性を打ち消す階調変換を画像データに対して行えばよいことがわかる。そこで、階調変換部200の特性として図20の階調特性を打ち消す変換特性を持つことにより、前述した赤みがかかる表示される不具合を打ち消すことが可能となる。

## 【0260】

実際の図20の特性を打ち消すための階調変換特性を図21に示す。同図は入出力が8ビットのデータの場合を示している。図21において、QGBは、緑・青の蛍光体の飽和特性を打ち消す特性曲線（本例では飽和していないとし直線で示してある）、QRは、図20のqrで示した赤の蛍光体の飽和特性を打ち消す特性曲線である。

10

## 【0261】

そして、前述したように、画像データは放出電荷量に対応しているので（（1）の特徴）、放出電荷量に依存する飽和特性を持つ赤の蛍光体の特性を打ち消すことが、画像データの階調変換によって実現することができた。

## 【0262】

すなわち、前記画像データの階調変換は、輝度要求値である画像データに対し、蛍光体の発光特性を考慮した放出電荷量要求値に変換することを意味する。

## 【0263】

そして、前記放出電荷量要求値になるように放出電荷量の変動を補正する放出電荷量の補正を行うことを示している。

20

## 【0264】

次に、オーバーフロー処理を行っている場合を説明する。前述した（2）の特徴により、電圧降下が無い場合の放出電流量IEに画像データのゲイン（係数）倍した値で決まるパルス幅を乗じた放出電荷量が蛍光体に入射する。

## 【0265】

すなわち、入力される画像データが同じであっても、オーバーフロー処理が行われた場合は行われなかった場合に比べ放出電荷量がゲイン倍されることになる。

## 【0266】

詳細を説明するために、正規化電荷量対輝度の特性を図22に示す。図22も図20同様に、電圧降下が無い場合の放出電流量IEをパルス幅変調の1階調分の時間tだけ投入した電荷量を1として、横軸の放出電荷量を正規化して示している。また、縦軸は電圧降下が無い場合の放出電流量IEでパルス幅が255階調（255×t）の時の各色の輝度が1になるように正規化して示した。

30

## 【0267】

図22のqgb、qrの特性は、前述した図20の特性と同じであり、qgbは緑と青の階調特性、qrは赤の階調特性である。図22においてGAで示した正方形の領域は、ゲインが1の時の放出電荷量対輝度を示す領域であり、横軸の正規化電荷量の0から255が、画像データの0から255に対応する（前述したオーバーフロー処理を行わない場合に相当）。

## 【0268】

また、ゲインが1/2の時は、蛍光体に放出される電荷量は画像データをゲイン倍（1/2倍）した電荷量となるので、画像データ0から255は正規化電荷量0から127に対応する。図22においてGBで示した正方形の領域は、ゲインが1/2の時の実際に放出される放出電荷量対輝度を示す領域になる。

40

## 【0269】

同様にゲインが1/4の時は、蛍光体に放出される電荷量は画像データをゲイン倍（1/4倍）した電荷量となるので、画像データ0から255は正規化電荷量0から63に対応する。図22においてGCで示した正方形の領域は、ゲインが1/4の時の実際に放出される放出電荷量対輝度を示す領域になる。

## 【0270】

50

ゲインがG 1の時は、蛍光体に放出される電荷量は画像データをゲイン倍（G 1倍）した電荷量となるので、画像データ0から255は正規化電荷量0から（255×G 1）に対応する。図22においてGGで示した正方形の領域は、ゲインがG 1の時の実際に放出される放出電荷量対輝度を示す領域になる。

【0271】

前述したように、実際に放出される放出電荷量は、画像データにゲインを乗じた値に対応する（ゲインによって決まる動作点）。

【0272】

そのため、画像データを以下のように階調変換することにより、蛍光体の飽和特性を打ち消すことが実現できる。

10

【0273】

ゲインが1の時は、正規化電荷量の0から255が、画像データの0から255に対応しているので、図23に示す変換特性をもつ補正テーブルにより、赤の蛍光体の飽和特性を打ち消すことができる。

【0274】

図23において、QGBは、緑と青の蛍光体の飽和特性を打ち消す特性曲線（本例では飽和していないとし直線で示してある）、QR（×1）は、図22のqrで示した赤の蛍光体の飽和特性を打ち消す特性曲線である。

【0275】

同様に、ゲインが1/2の時は、正規化電荷量の0から127が、画像データの0から255に対応しているので、図24に示す変換特性をもつ補正テーブルにより、赤の蛍光体の飽和特性を打ち消すことができる。

20

【0276】

図24において、QGBは、緑と青の蛍光体の飽和特性を打ち消す特性曲線（本例では飽和していないとし直線で示してある）、QR（×1/2）は、図22のqrのGB領域で示した赤の蛍光体の飽和特性を打ち消す特性曲線である。

【0277】

画像データによる階調変換は、QGBのような飽和していない場合を基準にすれば、画像データ（入力データ）の0から255を出力データの0から255のレンジで変換する（以降、QGBのような飽和していない場合を基準にレンジを記述する。）。

30

【0278】

0から255のレンジの出力データは、電圧降下の影響を補正後、ゲインが乗じられ、蛍光体に放出する正規化電荷量が0から127の範囲となる。

【0279】

このようにして、ゲインに対応する動作点の蛍光体の飽和特性を打ち消す変換が行われる。

【0280】

言い換れば、蛍光体の飽和特性を打ち消す変換特性はゲインにかかわらず、画像データ（入力データ）の0から255を出力データの0から255のレンジで変換することによって行える。

40

【0281】

同様に、ゲインが1/4の時は、正規化電荷量の0から63が、画像データの0から255に対応しているので、図25に示す変換特性をもつ補正テーブルにより、赤の蛍光体の飽和特性を打ち消すことができる。

【0282】

図25において、QGBは、緑と青の蛍光体の飽和特性を打ち消す特性曲線（本例では飽和していないとし直線で示してある）、QR（×1/4）は、図22のqrのGC領域で示した赤の蛍光体の飽和特性を打ち消す特性曲線である。

【0283】

同様に、ゲインがG 1の時は、正規化電荷量の0から（255×G 1）が、画像データの

50

0 から 255 に対応しているので、画像データをゲイン倍 (G 1 倍) し、図23のQGR、QR (×1) で示した特性をもつ 補正テーブルにより変換し、蛍光体の飽和の影響を補正する。さらに 補正テーブルによって変換された出力を 1 / ゲイン倍 (1 / G 1 倍) し、電圧降下の補正を行うための 0 から 255 のレンジの出力データとする。

## 【0284】

上述した特性はゲインにより決まる動作点での階調変換特性を選んでいるともいえる。

## 【0285】

上述した階調変換手段200の特性によって、オーバーフロー処理を行った場合であっても、前述した赤みがかかる表示される不具合を打ち消すことができた。

## 【0286】

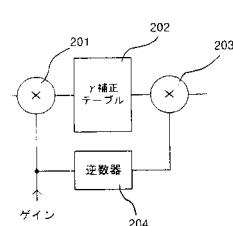

次に、実際の階調変換部200の構成を説明する。

## 【0287】

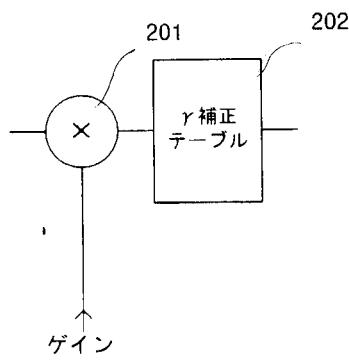

図26に階調変換部200の構成を示した。図26において201, 203は乗算器、202はメモリ等で実現される 補正テーブル、204は逆数器である。この構成によって前述した機能を実現する。図26では、簡便化のため、ひとつの色に対応する構成を示した。当然、赤・緑・青毎に同一構成を三組で階調変換部200は構成される。この時、補正テーブルの内容は各色ごとに蛍光体の飽和特性に応じて対応する。

## 【0288】

入力される画像データは乗算器201によりゲイン (G 1 ) 倍される。前述したように、入力画像データをゲイン倍した放出電荷量に変換し、最大放出電荷量で正規化 (1 から 255 レンジ、) した蛍光体の飽和特性を打ち消す階調変換を 補正テーブル202で行う。

## 【0289】

実際に放出される放出電荷量で蛍光体の飽和特性を打ち消す階調変換を 補正テーブル202で行う。

## 【0290】

このままであると、 補正テーブルの出力がゲイン倍されたままであるので実際の電圧降下補正を行うデータに戻すため、乗算器203により 1 / ゲイン倍 (1 / G 1 倍) する。逆数器204はゲインの逆数を出力する。

## 【0291】

ゲインは一般に 1 より小さいため、ゲイン倍された画像データが 補正テーブル202に入力されるので、有効桁数が落ちないように、 補正テーブル202のビット数を画像データのビット数より多くする必要があった。

## 【0292】

上記、構成により、前述した機能を実現し、ハードウェアによって前述した赤みがかかる表示される不具合を打ち消すことができた。さらに、前述したゲインの算出法 (式12) を満たす  $G = K_g \times INMAX / MAXKg$  1 の定数の関係があるとき、  $1 / G = MAX / (K_g \times INMAX)$  である。  $K_g \times INMAX$  は定数であるので  $K_g' = 1 / (K_g \times INMAX)$  と  $K_g'$  を新たな定数とすると、  $1 / G = K_g' \times MAX$  となる。

## 【0293】

すなわち、ゲインの逆数を求める逆数器204は補正画像データの最大値MAXに定数  $K_g'$  を乗算し求めることができる。このことはROMなどで構成される逆数器を乗算器に置き換えができる、ハードウェア量を少なくすることを可能にする。

## 【0294】

さらに、2番目のゲインの算出法 (式13) に対しても同様に、前述したゲインの算出法 (式13) を満たす  $G_1 = K_{g1} \times INMAX / AMAXK_{g1}$  1 の定数の関係があるとき、  $1 / G = AMAX / (K_{g1} \times INMAX)$  である。

## 【0295】

$K_{g1} \times INMAX$  は定数であるので  $K_{g1}' = 1 / (K_{g1} \times INMAX)$  と  $K_{g1}'$  を新たな定数とすると、  $1 / G = K_{g1}' \times AMAX$  となる。

10

20

30

40

50

## 【0296】

すなわち、ゲインの逆数を求める逆数器204は現在のフレームよりも以前のフレームで検出された補正画像データの最大値をフレーム方向に平滑化（平均化）したA M A Xに定数Kg1'を乗算し求めることができる。このことはR O Mなどで構成される逆数器を乗算器に置き換えることができ、ハードウェア量を少なくするこを可能にする。

## 【0297】

さらに、3番目のゲインの算出法では、ゲインを式12で求めさらに平均化する方法である、この場合、第2の方法と同じ計算で逆数器を乗算器に置き換えることができる。ただし平均化はゲイン及び補正画像データの最大値の両方に対して別々に行う必要がある。そのため平均化処理のためのハードウェアは増加する、しかしながらこの増加を考慮しても逆数器を使用する方法よりも全体のハードウェア量は少なくなる。10

## 【0298】

次に、蛍光体の飽和を打ち消す補正テーブル202は、以下のような構成であっても良い。補正テーブル202の特性を、要求輝度Lr、蛍光体に投入すべき電荷量qrとすると、要求輝度Lr、電荷量qrを共に正規化すれば、 $qr = fr(Lr)$ ここで $fr(Lr)$ は蛍光体の飽和を補正する補正テーブル202に記憶されている特性である。

## 【0299】

ここで、 $gr(Lr) = Lr - fr(Lr)$ となる関数 $gr(Lr)$ を定義する。すなわち $gr(Lx)$ は輝度と電荷量が比例する特性からの差分の関数である。このとき、蛍光体の飽和を打ち消すためには $qr = Lr - gr(Lr)$ の関係が必要となる。20

## 【0300】

前述した実施の形態の補正テーブル202は $gr(Lr)$ の特性をもつテーブルと、 $Lr$ から $gr(Lr)$ の特性をもつテーブルの出力を減算する減算器から構成するとよい。このとき、ハードウェア構成として減算器が増えるが、同一の容量のメモリにおいては $gr(Lr)$ の特性をもつテーブルを使用する場合に、階調数が増加し、処理精度が向上する利点がある。

## 【0301】

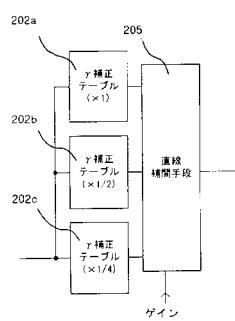

図27に他の階調変換部の実施形態を示す。図27でも、簡便化のため、ひとつの色に対応する構成を示した。当然、赤・緑・青毎に同一構成を三組で階調変換部200は構成される。この時、補正テーブルのそれぞれの内容は各色ごとに蛍光体の飽和特性に応じて対応する。30

## 【0302】

図27において、202a, 202b, 202cは補正テーブルであり、それぞれゲインが1倍、1/2倍、1/4倍の時に、実際に放出される放出電荷量に相当する蛍光体の飽和特性を打ち消す変換テーブルが記憶されている。実際には、前述した図23, 図24, 図25に示した特性である。205は直線補間手段であり、ゲインG1を入力し、各補正テーブル202a, 202b, 202cのゲインG1を挟む2つのテーブルの出力から直線補間によってゲインG1に対する補間値を求める手段である。

## 【0303】

ゲインにより決まる蛍光体の飽和特性を打ち消す特性は、単調に変化するので、上記構成によって、各補正テーブル202a, 202b, 202cの特性を直線補間し求めるこことで任意のゲインG1に対する変換特性を得ることができる。40

## 【0304】

当然、補正テーブルの数を多くすることで精度は上がるが、ハードウェアコストは上昇する。補正テーブルは3以上で表示画質の明らかな劣化を防ぐことができた。

## 【0305】

上記、構成によっても、前述した機能を実現し、ハードウェアによって前述した赤みがかかる表示される不具合を打ち消すことができた。

## 【0306】

さらに、本実施形態の説明では、緑と青の蛍光体の階調特性はリニアリティーが高く飽和50

特性を持たないとして説明したが、実際には赤の蛍光体に比べ非常に小さいが、輝度は電荷量に対して飽和する飽和特性を持つ。この場合、各色の中で飽和が少ないもので上述した正規化階調特性を求めこの特性を打ち消すテーブルを色毎に作成することによって、各色の蛍光体の飽和特性を補正することができる。さらに、蛍光体の飽和特性は、フェースプレートとリアプレートの間の加速電圧（高圧電源の電位）や蛍光体に投入される最大電荷量によって変化する。パネルを駆動する場合、各電子放出素子の駆動する時間は決まっているため、蛍光体に投入される最大電荷量は電子放出素子の放出電流 I\_E、すなわち走査手段の電位（V\_s）、変調手段の電位（V\_pwm）に依存する。蛍光体の飽和特性は、高圧電源の電位や、走査手段の電位（V\_s）、変調手段の電位（V\_pwm）により変化する。表示装置の個体差を吸収するための初期調整や、ユーザが行う調整などのために、高圧電源の電位、走査手段の電位（V\_s）、変調手段の電位（V\_pwm）を可変する場合、対応する電位における蛍光体の飽和特性を打ち消す 補正テーブルに変更すると良い。

## 【0307】

(シフトレジスタ、ラッチ回路)

リミッタ回路の出力である補正画像データ D\_l\_i\_m は、シフトレジスタ 5 により、シリアルなデータフォーマットから、各変調配線毎のパラレルな画像データ I\_D\_1 ~ I\_D\_N へとシリアル/パラレル変換されラッチ回路へ出力される。ラッチ回路では 1 水平期間が開始される直前にタイミング信号 Data\_load により、シフトレジスタからのデータをラッチする。ラッチ回路 6 の出力は、パラレルな画像データ D\_1 ~ D\_N として変調手段へと供給される。

## 【0308】

本実施形態では画像データ I\_D\_1 ~ I\_D\_N、D\_1 ~ D\_N はそれぞれ 8 ビットの画像データとした。これらの動作タイミングはタイミング発生回路 4（図 12）からのタイミング制御信号 T\_S\_F\_T 及び Data\_load に基づいて動作する。

## 【0309】

(変調手段の詳細)

ラッチ回路 6 の出力であるパラレル画像データ D\_1 ~ D\_N は変調手段 8 へと供給される。

## 【0310】

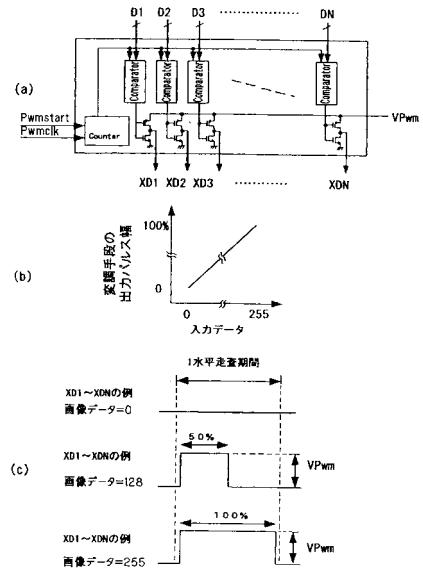

変調手段は、図 28 (a) に示したように、PWM カウンタと、各変調配線ごとにコンパレータとスイッチ（同図では FET）を備えたパルス幅変調回路（PWM 回路）である。

## 【0311】

画像データ D\_1 ~ D\_N と変調手段の出力パルス幅の関係は、図 28 (b) のようなリニアな関係にある。

## 【0312】

同図 (c) に変調手段の出力波形の例を 3 つ示す。

## 【0313】

同図において上側の波形は、変調手段への入力データが 0 の時の波形、中央の波形は、変調手段への入力データが 128 の時の波形、下側の波形は、変調手段への入力データが 255 の時の波形である。

## 【0314】

なお、本例では変調手段への入力データ D\_1 ~ D\_N のビット数は 8 ビットとした。

## 【0315】

なお、前述の説明では、変調手段の入力データが 255 のときは、一水平走査期間に相当するパルス幅の変調信号が出力されると記載した箇所があるが、詳細には同図 (c) のように非常に短い時間ではあるがパルスの立ち上がる前と、立ち下がった後にわずかではあるが駆動しない期間を設けタイミング的な余裕を持たせている。

## 【0316】

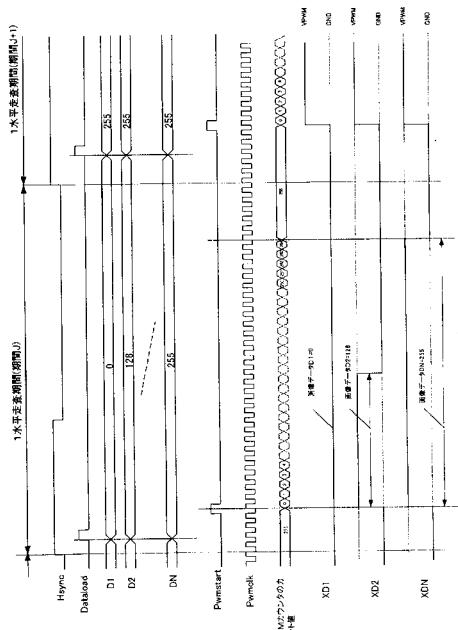

図 29 は、本発明の実施の形態における変調手段の動作を示すタイミングチャートである。

## 【0317】

10

20

30

40

50

同図において、**H sync**は水平同期信号、**Data load**はラッチ回路6へのロード信号、**D1 ~ DN**は前述の変調手段の列1~Nへの入力信号、**Pwm start**はPWMカウンタの同期クリア信号、**Pwm clk**はPWMカウンタのクロックである。また、**XD1 ~ XDN**は変調手段の第1~第N列の出力を表している。

【0318】

同図にあるように1水平走査期間が始まると、ラッチ回路6は画像データをラッチするとともに変調手段へデータを転送する。

【0319】

PWMカウンタは、同図に示したように、**Pwm start**、**Pwm clk**に基づいてカウントを開始し、カウント値が255になるとカウンタをストップしカウント値255を保持する。

10

【0320】

各列毎に設けられているコンパレータは、PWMカウンタのカウント値と各列の画像データを比較し、PWMカウンタの値が画像データ以上のとき**HIGH**を出力し、それ以外の期間は**LOW**を出力する。

【0321】

コンパレータの出力は、各列のスイッチのゲートに接続されており、コンパレータの出力が**LOW**の期間は同図の上側(**V pwm**側)のスイッチがON、下側(**GND**側)のスイッチがOFFとなり、変調配線を電圧**V pwm**に接続する。

20

【0322】

逆にコンパレータの出力が**HIGH**の期間は、同図の上側のスイッチがOFFし、下側のスイッチがONするとともに、変調配線の電圧を**GND**電位に接続する。

【0323】

各部が以上のように動作することで、変調手段が出力するパルス幅変調信号は、図29の**D1**、**D2**、**DN**に示したような、パルスの立ち上がりが同期した波形となる。

【0324】

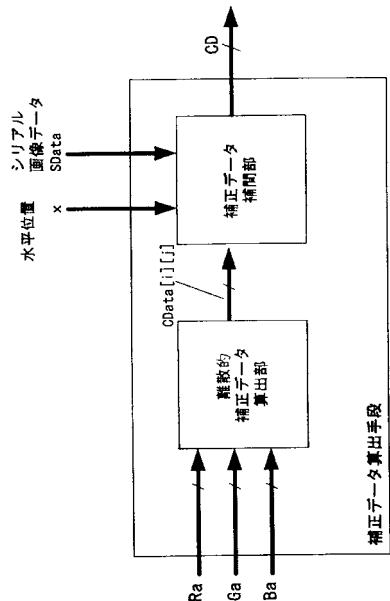

(補正データ算出手段)

補正データ算出手段は前述した補正データ算出方法により、電圧降下の補正データを算出する回路である。補正データ算出手段は図30に示すように離散補正データ算出部と補正データ補間部の2つのブロックから構成される。

30

【0325】

離散補正データ算出部では入力された映像信号から電圧降下量を算出し、電圧降下量から補正データを離散的に計算する。同算出部は計算量やハードウェア量を減少させるために、前述の縮退モデルの概念を導入して、補正データを離散的に算出する。

【0326】

離散的に算出された補正データは補正データ補間部により補間され、画像データの大きさやその水平表示位置xに適合した補正データCDが算出される。

【0327】

(離散補正データ算出部)

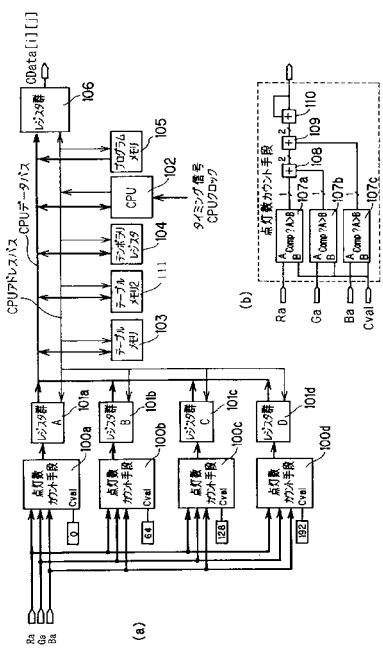

図31は本発明の実施の形態における離散的に補正データを算出するための離散補正データ算出部である。

40

【0328】

離散補正データ算出部は、以下に述べるように、画像データをブロックわけし、ブロックごとの統計量(点灯数)を算出するとともに、統計量から各ノードの位置における、電圧降下量の時間変化を計算する電圧降下量算出部としての機能と、各時間ごとの電圧降下量を発光輝度量に変換する機能、および発光輝度量を時間方向に積分して、発光輝度総量を算出する機能、およびそれから離散的な基準点における、画像データの基準値に対する補正データを算出する手段である。

【0329】

同図において**100a ~ 100d**は点灯数カウント手段、**101a ~ 101d**は各プロッ

50

クごとの、各時刻における点灯数を格納するレジスタ群、102はCPU、103は式2で記載したパラメータ*a i j*を記憶するためのテーブルメモリ、104は計算結果を一時記憶するためのテンポラリレジスタ、105はCPUのプログラムが格納されているプログラムメモリ、111は、電圧降下量を放出電流量に変換する変換データが記載されたテーブルメモリ、106は、前述した離散補正データの計算結果を格納するためのレジスタ群である。

【0330】

点灯数カウント手段100a～100dは、同図(b)に記載したようなコンパレータと加算器などから構成されている。映像信号Ra, Ga, Baはそれぞれコンパレータ107a～cに入力され、逐次Cvalの値と比較される。

10

【0331】

なお、Cvalは前述してきた画像データに対して設定した、画像データ基準値に相当する。

【0332】

コンパレータ107a～cはCvalと画像データの比較を行い画像データの方が大きければHighを出力し小さければLowを出力する。

【0333】

コンパレータの出力は加算器108及び109により互いに足し算され、さらに加算器110によりブロックごとに加算を行い、ブロックごとの加算結果を各々のブロックごとの点灯数としてレジスタ群101a～cへと格納する。

20

【0334】

点灯数カウント手段100a～dにはコンパレータの比較値Cvalとしてそれぞれ0、64、128、192が入力されている。

【0335】

結果として、点灯数カウント手段100aは画像データのうち、0より大きい画像データの個数をカウントしそのブロックごとの総計をレジスタ101aに格納する。

【0336】

同様に、点灯数カウント手段100bは画像データのうち、64より大きい画像データの個数をカウントし、そのブロックごとの総計をレジスタ101bに格納する。

【0337】

同様に、点灯数カウント手段100cは画像データのうち、128より大きい画像データの個数をカウントし、そのブロックごとの総計をレジスタ101cに格納する。

30

【0338】

同様に、点灯数カウント手段100dは画像データのうち、192より大きい画像データの個数をカウントし、そのブロックごとの総計をレジスタ101d格納する。

【0339】

ブロックごと、時間ごとの点灯数カウントされると、CPUはテーブルメモリ103に格納されたパラメータテーブル*a i j*を随時読み出して、式2～4に従い、電圧降下量を計算し、計算結果をテンポラリレジスタ104に格納する。

【0340】

本例ではCPUに式2の計算を円滑におこなうための積和演算機能を設けた。

40

【0341】

式2に挙げた演算を実現する手段としては、CPUで積和演算を行わないでもよく、例えば、その計算結果をメモリに入れておいてもよい。

【0342】

すなわち、各ブロックの点灯数を入力とし、考えられるすべての入力パターンに対し、各ノード位置の電圧降下量をメモリに記憶させておいても構わない。

【0343】

電圧降下量の計算が完了するとともに、CPUはテンポラリレジスタ104から、各時間、各ブロックごとの電圧降下量をよみだし、テーブルメモリ2(111)を参照して、電

50

圧降下量を放出電流量に変換し、式 6 ~ 8 に従って、離散補正データを算出した。

【0344】

計算した離散補正データは、レジスタ群 106 に格納した。

【0345】

(補正データ補間部)

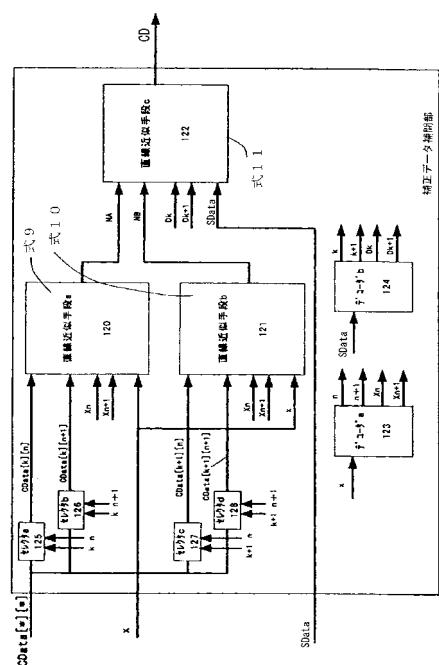

補正データ補間部は画像データの表示される位置（水平位置）及び、画像データの大きさに対応した補正データを算出するための手段である。同手段は離散的に算出された補正データを補間することにより、画像データの表示位置（水平位置）及び、画像データの大きさに応じた補正データを算出する。

【0346】

10

図 32 は補正データ補間部を説明するための図である。

【0347】

同図において 123 は画像データの表示位置（水平位置） $x$  から、補間に用いる離散補正データのノード番号  $n$  及び  $n + 1$  を決定するためのデコーダであり、124 は画像データの大きさから、式 9 ~ 式 11 の  $k$  および  $k + 1$  を決定するためのデコーダである。

【0348】

また、セレクタ 125 ~ 128 は、離散補正データを選択して、直線近似手段に供給するためのセレクタである。

【0349】

20

また、121 ~ 123 は、それぞれ式 9 ~ 式 11 の直線近似を行うための直線近似手段である。

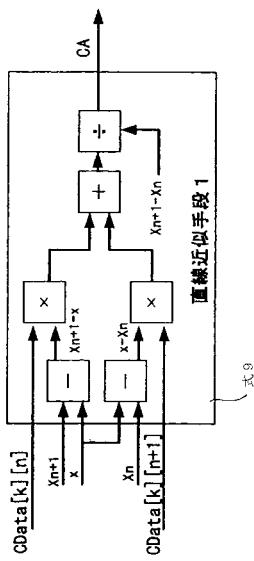

【0350】

図 33 に直線近似手段 121 の構成例を示す。一般に直線近似手段は式 9 ~ 11 の演算子にあらわされるように、減算器、積算器、加算器、割り算器などによって構成可能である。

【0351】

しかし、望ましくは離散補正データを算出するノードとノードの間の列配線本数や、離散補正データを算出する画像データ基準値の間隔（すなわち電圧降下を算出する時間間隔）が 2 のべき乗になるように構成するとハードウェアを非常に簡単に構成できるというメリットがある。それらを 2 のべき乗に設定すれば、図 33 に示した割り算器において、 $X_{n+1} - X_n$  は 2 のべき乗の値となり、ビットシフトすればよい。

30

【0352】

$X_{n+1} - X_n$  の値がいつも一定の値であって、2 のべき乗で表される値であるならば、加算器の加算結果をべき乗の乗数分だけシフトして出力すればよく、あえて割り算器を作製する必要がない。

【0353】

また、これ以外の箇所でも離散補正データを算出するノードの間隔や、画像データの間隔を 2 のべき乗とすることにより、たとえばデコーダ 123 ~ 124 を簡単に作製することができるなどとともに、図 33 の減算器で行っている演算を簡単なビット演算に置き換えることができるなど、非常にメリットが多い。

40

【0354】

(各部の動作タイミング)

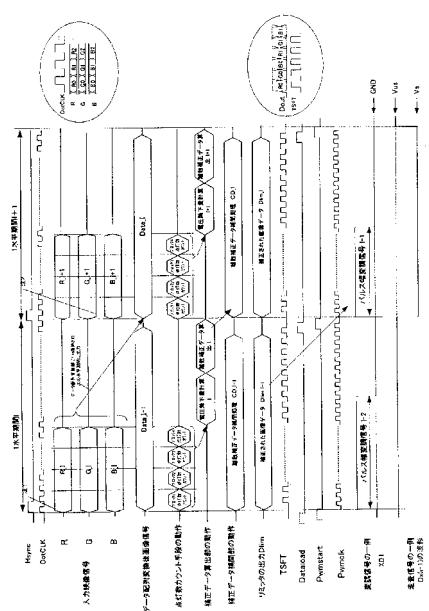

図 34 に各部の動作タイミングのタイミングチャートを示す。

【0355】

なお、同図において  $H_{sync}$  は水平同期信号、 $DotCLK$  はタイミング発生回路の中の PLL 回路により水平同期信号  $H_{sync}$  から作成したクロック、 $R$ 、 $G$ 、 $B$  は入力切り替え回路からのデジタル画像データ、 $Data$  はデータ配列変換後の画像データ、 $Dim$  はリミッタ手段の出力であって、電圧降下補正を施された補正画像データ、 $TSFT$  はシフトレジスタ 5 へ補正画像データ  $Dim$  を転送するためのシフトクロック、 $Data10ad$  はラッチ回路 6 へデータをラッチするためのロードパルス、 $Pwmstart$

50

$t$  は前述のパルス幅変調の開始信号、変調信号 X D 1 は変調配線 1 へ供給されるパルス幅変調信号の一例である。

【 0 3 5 6 】

1 水平期間の開始とともに、セレクタ 2 3 からディジタル画像データ R G B が転送される。同図では水平走査期間 I において、入力される画像データを R\_I, G\_I, B\_I で表すと、それらは、データ配列変換回路 9 では 1 水平期間の間、画像データを蓄えられ、水平走査期間 I + 1 において、表示パネルの画素配置に合わせてディジタル画像データ D a t a\_I として出力される。

【 0 3 5 7 】

R\_I, G\_I, B\_I は、水平走査期間 I において補正データ算出手段に入力される。同手段では、前述した点灯数をカウントし、カウントの終了とともに、電圧降下量が算出される。

【 0 3 5 8 】

電圧降下量が算出されるのにつづいて、離散補正データが算出され、算出結果がレジスタに格納される。

【 0 3 5 9 】

走査期間 I + 1 に移り、データ配列変換部から、1 水平走査期間前の画像データ D a t a\_I が出力されるのに同期して、補正データ補間手段では離散補正データが補間され、補正データが算出される。補間された補正データは、加算器 1 2 に供給される。

【 0 3 6 0 】

加算器 1 2 では、画像データ D a t a と補正データ C D を順次加算し、補正された補正画像データ D l i m をシフトレジスタへ転送する。シフトレジスタは T s f t にしたがって、一水平期間分の補正画像データ D l i m を記憶するとともにシリアル・パラレル変換をおこなってパラレルな画像データ I D 1 ~ I D N をラッチ回路 6 に出力する。ラッチ回路 6 は D a t a l o a d の立ち上がりにしたがってシフトレジスタからのパラレル画像データ I D 1 ~ I D N をラッチし、ラッチされた画像データ D 1 ~ D N をパルス幅変調手段 8 へと転送する。

【 0 3 6 1 】

パルス幅変調手段 8 は、ラッチされた画像データに応じたパルス幅のパルス幅変調信号を出力する。本実施形態の画像表示装置では、結果として、変調手段が出力するパルス幅は、入力された画像データに対し、2 水平走査期間分おくれて表示される。

【 0 3 6 2 】

このような画像表示装置により画像の表示を行ったところ、従来からの課題であった走査配線における電圧降下量を補正することができ、それに起因する表示画像の劣化を改善することができ、非常に良好な画像を表示することができた。

【 0 3 6 3 】

また、いくつかの近似を導入したことにより、電圧降下を補正するための、画像データの補正量を簡単に好適に計算することができ、非常に簡単なハードウェアでそれを実現することができるなど、非常に優れた効果があった。

【 0 3 6 4 】

( 第 2 の実施形態 )

補正画像データ D o u t は、画像データ D a t a と補正データ C D を加算した結果である。

【 0 3 6 5 】

この加算の結果が、変調手段の入力範囲におさまらないと、補正を施したことにより、オーバーフローが起きてしまい、表示画像において別の違和感が発生することが懸念されていた。

【 0 3 6 6 】

このような課題に対し、上記第 1 の実施形態では、補正画像データの最大値を検出し、該最大値が、変調手段の入力範囲の最大値に対応するように、ゲインを算出し、該ゲインと

10

20

30

40

50

補正画像データを乗算し、オーバーフローを防止していた。

【0367】

これに対し本実施形態では、補正画像データの最大値を検出するのは同様であるが、該最大値が変調手段の入力範囲の最大値に対応するように、補正を施す前の画像データの大きさを制限することとした。

【0368】

すなわち、オーバーフローがおきないように、予め入力された画像データにゲインを乗算してその振幅範囲を小さくしておき、オーバーフローを防止する。

【0369】

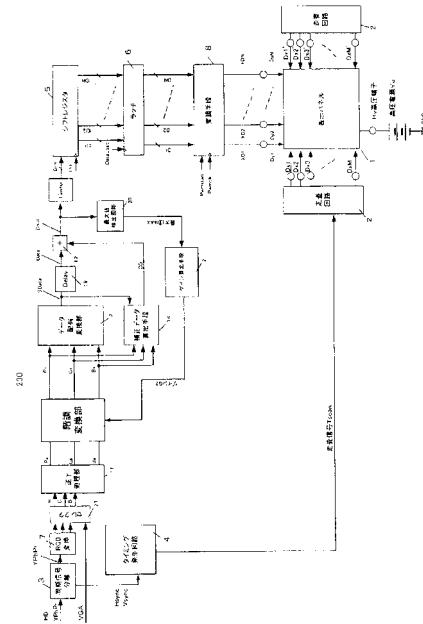

以降、図35を用いて、本実施形態のオーバーフロー処理について説明する。

10

【0370】

図において22R, 22G, 22Bは乗算器、9はデータ配列変換部、5は画像データ1ライン分のシフトレジスタ、6は画像データ1ライン分のラッチ回路、8は表示パネルの変調配線に変調信号を出力するパルス幅変調手段、12は加算器、14は補正データ算出手段、20はフレーム内の補正画像データDoutの最大値を検出するための最大値検出回路(手段)、21はゲイン算出手段、200は階調変換部である。階調変換部200の説明は後述するので、以下の説明では階調変換部200が無いものとして説明していく。

【0371】

また、R、G、BはRGBパラレルの入力映像データ、Ra, Ga, Baは逆変換処理を施したRGBパラレルの映像データ、Rx, Gx, Bxは乗算器により、ゲインG2が乗算された画像データ、ゲインG2は、ゲイン算出手部が算出したゲイン、Dataはデータ配列変換部によりパラレル・シリアル変換された画像データ、CDは補正データ算出手段により算出された補正データ、Doutは加算器により画像データに補正データを加算することにより、補正された画像データ(補正画像データ)、DlimはリミッタによってDoutを変調手段の入力範囲の上限以下に制限した補正画像データである。

20

【0372】

(乗算器22R、22G、22B)

乗算器22R, 22G, 22Bは逆変換後の画像データRa, Ga, Baに対し、ゲインG2を乗算するための手段である。

【0373】

30

より詳しくは、乗算器はゲイン算出手段が決定したゲインに従って画像データにゲインG2を乗算し、乗算後の画像データRx, Gx, Bxを出力する。

【0374】

ゲインG2は、ゲイン算出手段が算出する値であって、後述する加算器での画像データDataと補正データの加算結果である補正画像データDoutが、変調手段の入力範囲におさまるように決定される値である。

【0375】

(最大値検出手段20)

最大値検出回路20について説明を行う。

【0376】

40

本発明の実施の形態における最大値検出手段は図35に示すように、各部と接続されている。

【0377】

最大値検出手段は、1フレーム分の補正画像データDoutのなかで、最大となる値を検出する手段である。

【0378】

同手段は、コンパレータとレジスタなどによって簡単に構成できる回路である。同手段は、レジスタに記憶されている値と、順次転送されてくる補正画像データDoutの大きさを比較し、補正画像データDoutの方がレジスタの値よりも大きければ、レジスタの値をそのデータ値で更新する回路である。

50

## 【0379】

レジスタの値は、フレームの先頭で0にクリアすれば、フレームの終了時には、そのフレーム内の補正画像データの最大値MAXがレジスタに格納される。

## 【0380】

このようにして検出された補正画像データの最大値MAXは、ゲイン算出手段へと転送される。

## 【0381】

## (ゲイン算出手段)

ゲイン算出手段は、最大値検出手段の検出値MAXを参照して、補正画像データDoutが変調手段の入力範囲におさまるようにゲインを算出する手段である。本実施形態においても、ゲイン算出手段は適応型ゲイン法に基づいて補正画像データの振幅を調整するためのゲインを算出する。10

## 【0382】

一方、本実施形態(図35)の構成において補正画像データのオーバーフローを防止する上では、ゲインは固定ゲイン法によって算出しても良い。

## 【0383】

ゲインの決定方法は、1フレーム内の補正画像データDoutの最大値をMAX、変調手段の入力範囲の最大値をINMAX、前のフレームに対してゲイン算出手段が算出したゲインG2をGBとすると、20

## 【数16】

$$\text{ゲインG2} \leq (\text{INMAX}/\text{MAX}) \times \text{GB} \quad (\text{式14})$$

となるように決定すればよい。

## 【0384】

このゲイン算出手段では、垂直帰線期間においてゲインを更新して1フレーム毎にゲインの値が変更される。

## 【0385】

なお、本発明の実施の形態に係る画像表示装置の構成では、1フレーム前の補正画像データの最大値を用いて、現在のフレームの補正画像データに乗算するゲインを算出する構成となっている。30

## 【0386】

すなわち、フレーム間の補正画像データ(画像データ)の相関を利用して、オーバーフローを防止する構成になっている。

## 【0387】

したがって、厳密には、フレームごとの補正画像データの違いから、オーバーフローが起きることある。

## 【0388】

このような課題に対し、補正画像データとゲインを乗算する乗算器の出力に対しリミッタ手段を設け、乗算器の出力が必ず変調手段の入力範囲に収まるように回路を設計したところ、さらに好ましかった。40

## 【0389】

また、本発明者らは、上述したゲインの決定方法のほかに、以下のような別の方法によってゲインを算出してもよいことを確認している。

## 【0390】

すなわち、現在のフレームの補正画像データに施すゲインとしては、現在のフレームよりも以前のフレームで検出された補正画像データの最大値を平均し、その平均値AMAXに対し、45

## 【数17】

$$\text{ゲイン } G_2 \leq (\text{INMAX} / \text{AMAX}) \times G_B \quad (\text{式 } 15)$$

となるように決定すればよい。

【0391】

ただし  $G_B$  は、前のフレームに対してゲイン算出手段が算出したゲイン  $G_2$  である。

【0392】

また、別 の方法は、式14により各々のフレームごとのゲイン  $G_2$  を算出し、それを平均化して現在のゲインを算出してもよい。

【0393】

発明者らは、これら3つの方法のうち、どの方法でもオーバーフローを防止する意味では好ましいことを確認しているが、第1の実施形態で述べたようにフリッカが発生することを考慮すれば、式15の方法で算出することが好ましい。

【0394】

発明者らは、式15のゲイン算出法において、補正画像データの最大値を平均化するフレームの枚数について検討をおこなったが、現在のフレームから16~64フレーム前までの補正画像データの最大値を平均化したところ、好ましかった。

【0395】

なお、本方法でも、より好ましくは図35に示したように、加算器の出力を制限するリミッタを設けて完全にオーバーフローを防止することが好ましいことはいうまでもない。

【0396】

また、第1の実施形態と同様にシーンチェンジの検出を行って、ゲインの算出の方法を変更してもよい。

【0397】

(階調変換手段)

第2の実施形態においても、階調変換部200が無い時、第1の実施形態同様の現象を確認した。

【0398】

第2の実施形態はオーバーフロー処理におけるゲインを乗じる場所が異なるだけであるので、第1の実施形態と同様な構成の階調変換部200を設けた。階調変換部の特性、構成は第1の実施形態と同様に図26または図27の構成、図21、図23、図24、図25の特性である。この構成によって、蛍光体の飽和の影響を打ち消すことができ、前述した赤みがかった表示される不具合を打ち消すことができた。階調変換手段200の構成が図26に示す構成の時、第1の実施例で示したように、輝度と電荷量が比例する特性からの差分の関数である  $g_r(L_r)$  の特性をもつテーブルと、 $L_r$  から  $g_r(L_r)$  の特性をもつテーブルの出力を減算する減算器から構成してもよい。

【0399】

また、第2の実施形態で階調変換手段200の構成が図26に示す構成の時、図35の乗算器22R, 22G, 22Bと図26の乗算器203、逆数器204は、省略することができる。なぜならば乗算器203に入力されるデータは乗算器203により1/ゲイン倍され、さらに乗算器22R, 22G, 22Bでゲイン倍されるため、乗算器203に入力されるデータと乗算器22R, 22G, 22Bの出力データは同じになるためである。

【0400】

この時の構成を図36、図37に示す。構成及び動作は同じなので説明は省略する。

【0401】

さらに、第1の実施形態と同様に、第2の実施形態でも、緑と青の蛍光体の階調特性はリニアリティーが高く飽和特性を持たないとして説明したが、実際には赤の蛍光体に比べ非常に小さいが、輝度は電荷量に対して飽和する飽和特性を持つ。この場合、各色の中で飽和が少ないので上述した正規化階調特性を求めこの特性を打ち消すテーブルを色毎に作成することによって、各色の蛍光体の飽和特性を補正することができる。

【0402】

10

20

30

40

50

また、逆 处理部 17 の特性を考慮して、図 27 の テーブル 202a, 202b, 202c の特性を決定し逆 处理部 17 を削除し、ハードウェア量を少なくすることも可能である。第 1 の実施の形態で示したように、蛍光体の飽和特性は、フェースプレートとリアプレートの間の加速電圧（高圧電源の電位）や蛍光体に投入される最大電荷量によって変化する。パネルを駆動する場合、各電子放出素子の駆動する時間は決まっているため、蛍光体に投入される最大電荷量は電子放出素子の放出電流  $I_E$ 、すなわち走査手段の電位（ $V_s$ ）、変調手段の電位（ $V_{pwm}$ ）に依存する。

#### 【 0 4 0 3 】

蛍光体の飽和特性は、高圧電源の電位や、走査手段の電位（ $V_s$ ）、変調手段の電位（ $V_{pwm}$ ）により変化する。表示装置の個体差を吸収するための初期調整や、ユーザが行う調整などのために、高圧電源の電位、走査手段の電位（ $V_s$ ）、変調手段の電位（ $V_{pwm}$ ）を可変する場合、対応する電位における蛍光体の飽和特性を打ち消す 補正テーブルに変更すると良い。

10

#### 【 0 4 0 4 】

更に、本発明の実施の形態に係る画像表示装置において、0でない、均一な各色同一の画像データを入力した場合に、電圧降下の影響を打ち消す処理によって、前記走査手段の出力端子に近い変調手段の出力するパルスのパルス幅が、同走査手段の出力端子から遠い変調手段の出力するパルスのパルス幅よりも、短くなる様に駆動される。

#### 【 0 4 0 5 】

更に、電子放出素子の放出電荷量に依存した蛍光体の飽和特性を打ち消す結果、均一な各色同一のどのような画像データであっても、表示される色の輝度バランスがずれない、言い換えれば白色の色温度がほぼ均一に駆動される。

20

#### 【 0 4 0 6 】

また、本発明の実施の形態では、蛍光体の飽和特性を打ち消す補正する例を示したが、本発明の実施の形態と同じ構成で、電子放出素子の駆動電圧波形の劣化（波形なまり）等の影響によって、電子放出量が異なり階調特性が変化することに対しても、補正可能である。

#### 【 0 4 0 7 】

#### 【発明の効果】

以上説明したように、本発明の画像表示装置によれば、従来からの課題であった、走査配線上の電圧降下による表示画像の劣化を好適に改善することができた。

30

#### 【 0 4 0 8 】

また、いくつかの近似を導入したことにより、電圧降下の影響を補正した、補正画像データを簡単に好適に計算することができ、非常に簡単なハードウェアでそれを実現することができるなど、非常に優れた効果があった。

#### 【 0 4 0 9 】

さらに、補正後の画像データが変調手段の入力範囲をオーバーフローしないように、オーバーフロー処理回路を備えゲインにより、オーバーフローを防止することができた。

#### 【 0 4 1 0 】

そして、ゲインによって階調変換特性を変化させる階調変換部を電圧降下の影響を補正する構成の前段に構成することによって、蛍光体の飽和特性を打ち消すことができ、それにより高品位に画像を表示することができた。

40

#### 【図面の簡単な説明】

【図 1】本発明の実施の形態に係る画像表示装置の概観を示す図である。

【図 2】表示パネルの電気的な接続を示す図である。

【図 3】表面伝導型放出素子の特性を示す図である。

【図 4】表示パネルの駆動方法を示す図である。

【図 5】縮退モデルを説明する図である。

【図 6】離散的に算出した電圧降下量を示すグラフである。

【図 7】離散的に算出した放出電流の変化量を示すグラフである。

50

【図8】補正データの他の算出方法を説明するための図である。

【図9】画像データの大きさが128の場合の補正データの算出例を示す図である。

【図10】画像データの大きさが192の場合の補正データの算出例を示す図である。

【図11】補正データの補間方法を説明するための図である。

【図12】第1の実施形態の階調変換部を内蔵した画像表示装置の概略構成を示すブロック図である。

【図13】画像表示装置の走査回路の構成を示すブロック図である。

【図14】画像表示装置の逆処理部の構成を示すブロック図である。

【図15】画像表示装置のデータ配列変換部の構成を示すブロック図である。

【図16】連続するフレームの例を示す図である。

10

【図17】連続するフレームでの画像データの大きさを示すグラフである。

【図18】連続するフレームでのゲインを示すグラフである。

【図19】電圧降下の補正を行わず、階調変換部が無い時の階調特性を示す図である。

【図20】電荷量対輝度の特性を示す図である。

【図21】オーバーフロー処理を行わない場合の、蛍光体の飽和を打ち消す特性を示す図である。

【図22】電荷量対輝度の特性とゲインとの関係を示す図である。

【図23】ゲインが1の場合の、蛍光体の飽和を打ち消す特性を示す図である。

【図24】ゲインが1/2の場合の、蛍光体の飽和を打ち消す特性を示す図である。

20

【図25】ゲインが1/4の場合の、蛍光体の飽和を打ち消す特性を示す図である。

【図26】階調変換部の構成例1を示すブロック図である。

【図27】階調変換部の構成例2を示すブロック図である。

【図28】画像表示装置の変調手段の構成及び動作を説明する図である。

【図29】画像表示装置の変調手段のタイミングチャートである。

【図30】画像表示装置の補正データ算出手段の構成を示すブロック図である。

【図31】画像表示装置の離散補正データ算出部の構成を示すブロック図である。

【図32】補正データ補間部の構成を示すブロック図である。

【図33】直線近似手段の構成を示すブロック図である。

【図34】画像表示装置のタイミングチャートである。

【図35】第2の実施形態の画像表示装置の概略構成を示すブロック図である。

30

【図36】ハードウェアを少なくした第2の実施形態の画像表示装置の構成を示すブロック図である。

【図37】第2の実施形態のハードウェアを少なくした階調変換部の構成例を示すブロック図である。

【図38】従来の画像表示装置の構成を示すブロック図である。

【符号の説明】

1 表示パネル

2 走査回路

8 パルス幅変調手段

12 加算器

40

14 補正データ算出手段

17 逆処理部

19 遅延回路

20 最大値検出手段

21 ゲイン算出手段

22、22R、22G、22B 乗算器

23 セレクタ

100a, 100b, 100c, 100d 点灯数カウント手段

101a, 101b, 101c, 101d レジスタ群

103 テーブルメモリ

50

1 1 1 テーブルメモリ

1 0 7 a , 1 0 7 b , 1 0 7 c コンパレータ

1 2 3 , 1 2 4 デコーダ

2 0 0 階調変換部

2 0 1 , 2 0 3 乗算器

2 0 2 , 2 0 2 a , 2 0 2 b , 2 0 2 c 補正テーブル

2 0 4 逆数器

2 0 5 直線補間器

1 0 0 1 基板

1 0 0 2 冷陰極素子

1 0 0 3 行配線 (走査配線)

1 0 0 4 列配線 (変調配線)

1 0 0 7 フェースプレート

1 0 0 8 蛍光膜

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【 四 8 】

実際の放出電流ノ

(1) 電圧降下がない時の

放出電流パルス

※ IE：電圧降下のないときに放出される放電电流

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

○: ゲインを均一化しない場合 (式1.2)

●: ゲインを平均化した場合 (式1.3)

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

---

フロントページの続き

(51)Int.Cl.

| F I    |      |         |

|--------|------|---------|

| G 09 G | 3/20 | 6 4 1 C |

| G 09 G | 3/20 | 6 4 1 P |

| G 09 G | 3/20 | 6 4 1 Q |

| G 09 G | 3/20 | 6 4 2 A |

| G 09 G | 3/20 | 6 4 2 J |

| G 09 G | 3/20 | 6 4 2 P |

| H 04 N | 5/66 | A       |

(72)発明者 嵐嶋野 治

東京都大田区下丸子3丁目30番2号 キヤノン株式会社 内

(72)発明者 斎藤 裕

東京都大田区下丸子3丁目30番2号 キヤノン株式会社 内

(72)発明者 池田 武

東京都大田区下丸子3丁目30番2号 キヤノン株式会社 内

審査官 福村 拓

(56)参考文献 特開平10-319922 (JP, A)

特開平10-198307 (JP, A)

特開平02-257553 (JP, A)

特開平09-134145 (JP, A)

特開平03-018821 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/22

G09G 3/20

H04N 5/66