(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5355363号

(P5355363)

(45) 発行日 平成25年11月27日(2013.11.27)

(24) 登録日 平成25年9月6日(2013.9.6)

(51) Int.Cl.

H01L 23/12 (2006.01)

H05K 3/46 (2006.01)

F 1

H01L 23/12 501P

H05K 3/46 Q

請求項の数 12 (全 24 頁)

(21) 出願番号 特願2009-271902 (P2009-271902)

(22) 出願日 平成21年11月30日 (2009.11.30)

(65) 公開番号 特開2011-114304 (P2011-114304A)

(43) 公開日 平成23年6月9日 (2011.6.9)

審査請求日 平成24年8月30日 (2012.8.30)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 小林 敏男

長野県長野市小島田町80番地 新光電気

工業株式会社内

(72) 発明者 山野 孝治

長野県長野市小島田町80番地 新光電気

工業株式会社内

(72) 発明者 栗原 孝

長野県長野市小島田町80番地 新光電気

工業株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置内蔵基板及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体集積回路に形成された電極パッド上に接続端子が形成され、前記半導体集積回路上に前記接続端子の一部を露出する第1絶縁層が形成された半導体装置と、

前記半導体装置の少なくとも側面部を埋め、前記接続端子の露出部側の面に凹部が形成された第2絶縁層と、

前記第1絶縁層の前記接続端子の露出部側の面、及び前記第2絶縁層の前記凹部を含む領域に形成され、前記第2絶縁層の前記凹部の形状に対応する凹部を有し前記接続端子の露出部と電気的に接続する配線パターンと、

前記第1絶縁層の前記接続端子の露出部側の面、及び前記第2絶縁層の前記凹部を含む領域に、前記第2絶縁層の前記凹部に形成された前記配線パターンの一部のみを露出する開口部が設けられた第3絶縁層と、を有する半導体装置内蔵基板。

## 【請求項 2】

前記開口部は、前記配線パターンの凹部の底面及び内側面の一部を露出するように前記第3絶縁層に設けられている請求項1記載の半導体装置内蔵基板。

## 【請求項 3】

前記開口部は、前記配線パターンの凹部の全面を露出するように前記第3絶縁層に設けられている請求項1記載の半導体装置内蔵基板。

## 【請求項 4】

前記第2絶縁層は、前記半導体装置の側面部及び裏面部を覆うように形成されている請

10

20

求項 1 乃至 3 の何れか一項記載の半導体装置内蔵基板。

**【請求項 5】**

半導体集積回路に形成された電極パッド上に接続端子を形成する工程と、前記接続端子を覆うように前記半導体集積回路上に第1絶縁層を形成する工程と、前記第1絶縁層上に、前記第1絶縁層と対向する側の面が粗面とされた板状体を配設する工程と、前記板状体の前記粗面を前記第1絶縁層に圧着することにより、前記接続端子の一部を前記第1絶縁層から露出させる工程と、前記板状体を除去する工程と、を含む工程により半導体装置を製造する第1工程と、

一方の面に凸部が設けられた支持体を前記接続端子の露出部側に配置し、前記半導体装置の少なくとも側面部を埋めるように、前記接続端子の露出部側の面に前記凸部によって凹部が設けられた第2絶縁層を形成する第2工程と、

前記第1絶縁層の前記接続端子の露出部側の面、及び前記第2絶縁層の前記凹部を含む領域に、前記第2絶縁層の前記凹部の形状に対応する凹部を有し前記接続端子の露出部と電気的に接続する配線パターンを形成する第3工程と、を有する半導体装置内蔵基板の製造方法。

**【請求項 6】**

前記第2工程は、一方の面に凸部が設けられた支持体を準備し、前記接続端子の露出部が前記支持体の前記一方の面と対向するように、前記半導体装置を前記支持体の前記一方の面の前記凸部を含まない領域に配置する第2A工程と、

前記支持体の前記一方の面に配置された前記半導体装置の少なくとも側面部を埋めるように、前記支持体の前記一方の面の前記凸部を含む領域に第2絶縁層を形成する第2B工程と、

前記支持体を除去し、前記第2絶縁層に前記凸部に対応する前記凹部を形成する第2C工程と、を有する請求項5記載の半導体装置内蔵基板の製造方法。

**【請求項 7】**

前記第2工程は、第1支持体を準備し、前記接続端子の露出部が前記第1支持体の一方の面と対向するように、前記半導体装置を前記第1支持体の前記一方の面に配置する第2D工程と、

一方の面に凸部が設けられた第2支持体を準備し、前記半導体装置が配置された前記第1支持体の他方の面を前記第2支持体の前記一方の面と対向させ、前記第2支持体の前記凸部を含まない領域に前記半導体装置が配置されるように、前記第1支持体を前記第2支持体の前記一方の面に吸着保持させ、前記第1支持体の前記一方の面に前記第2支持体の前記凸部の形状に対応する凸部を形成する第2E工程と、

前記第1支持体の前記一方の面に配置された前記半導体装置の少なくとも側面部を埋めるように、前記第1支持体の前記一方の面の前記凸部を含む領域に第2絶縁層を形成する第2F工程と、

前記第1支持体及び前記第2支持体を除去し、前記第2絶縁層に前記第1支持体の前記凸部に対応する前記凹部を形成する第2G工程と、を有する請求項5記載の半導体装置内蔵基板の製造方法。

**【請求項 8】**

前記第1絶縁層の前記接続端子の露出部側の面、及び前記第2絶縁層の前記凹部を含む領域に、前記第2絶縁層の前記凹部に形成された前記配線パターンの少なくとも一部を露出する開口部が設けられた第3絶縁層を形成する第4工程を更に有する請求項5乃至7の何れか一項記載の半導体装置内蔵基板の製造方法。

**【請求項 9】**

前記第3絶縁層上に、前記開口部内に露出する前記配線パターンと電気的に接続される外部接続端子を形成する第5工程を更に有する請求項8記載の半導体装置内蔵基板の製造方法。

**【請求項 10】**

前記第4工程では、前記第2絶縁層の前記凹部に形成された前記配線パターンの一部の

10

20

30

40

50

みを前記開口部から露出する請求項8又は9記載の半導体装置内蔵基板の製造方法。

【請求項 1 1】

前記第4工程では、前記第2絶縁層の前記凹部の底面に形成された前記配線パターンのみを前記開口部から露出する請求項10記載の半導体装置内蔵基板の製造方法。

【請求項 1 2】

前記第2工程において、前記半導体装置の前記側面部及び裏面部を埋めるように、前記第2絶縁層を形成する請求項5乃至11の何れか一項記載の半導体装置内蔵基板の製造方法。

【発明の詳細な説明】

【技術分野】

10

【0001】

本発明は、半導体装置を内蔵する半導体装置内蔵基板及びその製造方法に関する。

【背景技術】

【0002】

従来から、半導体装置を内蔵する配線基板（以降、半導体装置内蔵基板とする）が知られている。半導体装置内蔵基板の製造方法としては、例えば、半導体装置に、半導体装置の有する半導体集積回路と電気的に接続される接続端子であるバンプを形成して配線基板に埋め込み、絶縁層で半導体装置の周囲を被覆した後、絶縁層にレーザで孔明けしてバンプを露出させ、露出したバンプに配線パターン（再配線）を形成する方法が知られている（例えば、特許文献1参照）。

20

【0003】

又、半導体装置に、半導体装置の有する半導体集積回路と電気的に接続される接続端子であるバンプを形成する第1の工程と、バンプ上に絶縁層を形成する第2の工程と、絶縁層にレーザで孔明けしてバンプに到達するビアホールを形成する第3の工程と、ビアホールに充填されるビア配線と、ビア配線に接続される配線パターン（再配線）とを形成する第4の工程と、を有し、ビアホールを形成する場合にバンプをレーザのストップ層として用いる方法が知られている。

【先行技術文献】

【特許文献】

30

【0004】

【特許文献1】特許第2842378号

【特許文献2】特開2005-332887号公報

【特許文献3】特開2006-222164号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、従来の半導体装置内蔵基板の製造方法では、半導体装置の有する半導体集積回路と配線パターン（再配線）とを電気的に接続する接続端子であるバンプが隠れるように半導体装置上に絶縁層を形成して半導体装置を埋め込み、レーザで孔明けしてバンプを露出させる。このため、レーザで孔明けする工程に時間がかかり、半導体装置内蔵基板の製造コストを上昇させるという問題があった。

40

【0006】

又、レーザは所定のスポット径（例えば、直径70μm程度）で照射されるので、半導体装置の有する半導体集積回路と配線パターン（再配線）とを電気的に接続する接続端子であるバンプの間隔を150μm程度までしか微細化できないという問題があった。

【0007】

上記の点に鑑み、製造コストの上昇を抑制するとともに、半導体装置の有する半導体集積回路と配線パターン（再配線）とを電気的に接続する接続端子の間隔の微細化が可能な半導体装置内蔵基板及びその製造方法を提供することを課題とする。

【課題を解決するための手段】

50

## 【0008】

本半導体装置内蔵基板の製造方法は、半導体集積回路に形成された電極パッド上に接続端子を形成する工程と、前記接続端子を覆うように前記半導体集積回路上に第1絶縁層を形成する工程と、前記第1絶縁層上に、前記第1絶縁層と対向する側の面が粗面とされた板状体を配設する工程と、前記板状体の前記粗面を前記第1絶縁層に圧着することにより、前記接続端子の一部を前記第1絶縁層から露出させる工程と、前記板状体を除去する工程と、を含む工程により半導体装置を製造する第1工程と、一方の面に凸部が設けられた支持体を前記接続端子の露出部側に配置し、前記半導体装置の少なくとも側面部を埋めるように、前記接続端子の露出部側の面に前記凸部によって凹部が設けられた第2絶縁層を形成する第2工程と、前記第1絶縁層の前記接続端子の露出部側の面、及び前記第2絶縁層の前記凹部を含む領域に、前記第2絶縁層の前記凹部の形状に対応する凹部を有し前記接続端子の露出部と電気的に接続する配線パターンを形成する第3工程と、を有することを要件とする。

10

## 【発明の効果】

## 【0009】

開示の技術によれば、製造コストの上昇を抑制するとともに、半導体装置の有する半導体集積回路と配線パターン（再配線）とを電気的に接続する接続端子の間隔の微細化が可能な半導体装置内蔵基板及びその製造方法を提供することができる。

## 【図面の簡単な説明】

20

## 【0010】

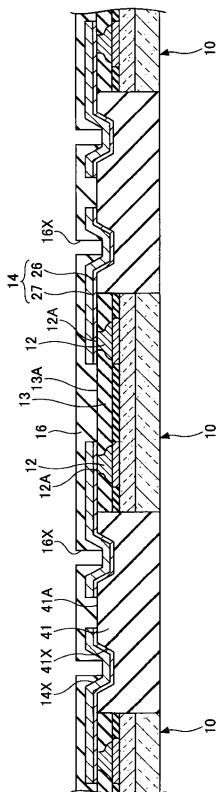

【図1】第1の実施の形態に係る半導体装置内蔵基板の断面図である。

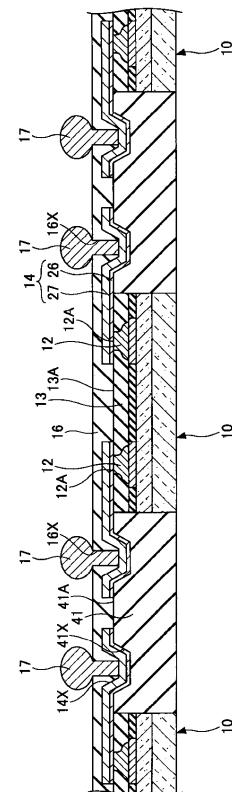

【図2】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その1）である。

【図3】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その2）である。

【図4】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その3）である。

【図5】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その4）である。

30

【図6】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その5）である。

【図7】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その6）である。

【図8】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その7）である。

【図9】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その8）である。

【図10】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その9）である。

40

【図11】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その10）である。

【図12】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その11）である。

【図13】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その12）である。

【図14】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その13）である。

【図15】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その14）である。

50

【図16】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その15）である。

【図17】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その16）である。

【図18】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その17）である。

【図19】第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その18）である。

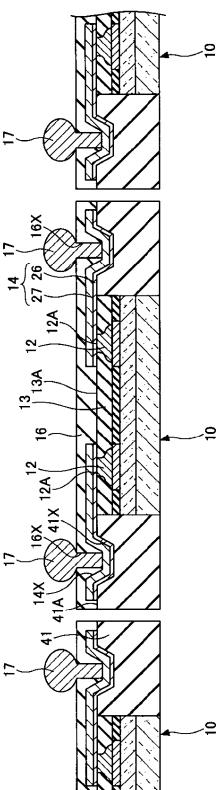

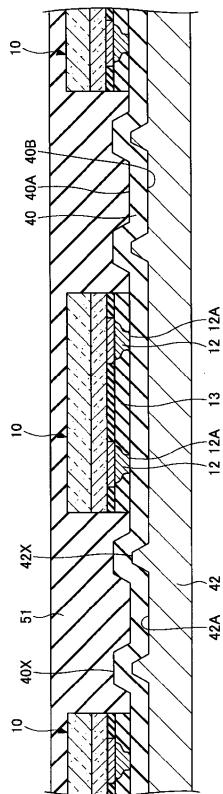

【図20】第2の実施の形態に係る半導体装置内蔵基板の断面図である。

【図21】第2の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その19）である。

10

【図22】第2の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その20）である。

【図23】第3の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その21）である。

【図24】第3の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図（その22）である。

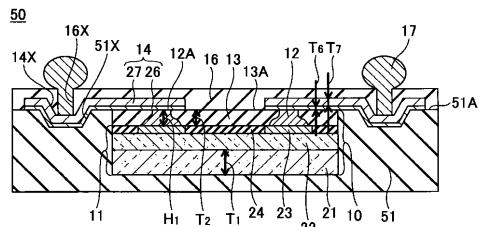

【図25】第4の実施の形態に係る半導体装置内蔵基板の断面図である。

【図26】第5の実施の形態に係る半導体装置内蔵基板の断面図である。

【発明を実施するための形態】

20

【0011】

以下、図面を参照して、本発明を実施するための形態の説明を行う。

【0012】

第1の実施の形態

[第1の実施の形態に係る半導体装置内蔵基板の構造]

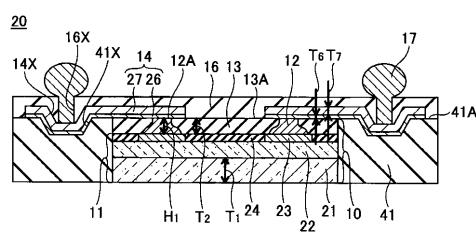

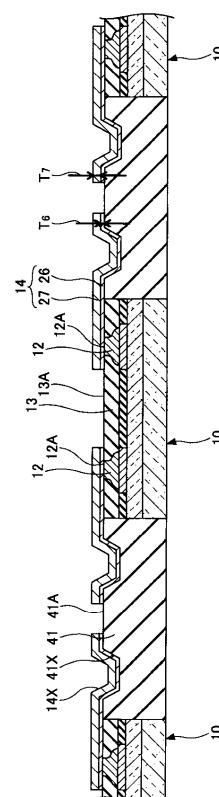

始めに、第1の実施の形態に係る半導体装置内蔵基板の構造について説明する。図1は、第1の実施の形態に係る半導体装置内蔵基板の断面図である。図1を参照するに、半導体装置内蔵基板20は、半導体装置10と、配線パターン14と、ソルダーレジスト層16と、外部接続端子17と、絶縁層41とを有する。

【0013】

30

半導体装置10は、半導体チップ11と、接続端子12と、絶縁層13とを有する。半導体装置10において、半導体チップ11は、半導体基板21と、半導体集積回路22と、電極パッド23と、保護膜24とを有する。半導体基板21は、半導体集積回路22を形成するための基板である。半導体基板21は、薄板化されている。半導体基板21の厚さT<sub>1</sub>は、例えば、50μm～500μmとすることができます。半導体基板21は、例えば、薄板化されたSiウエハが個片化されたものである。

【0014】

半導体集積回路22は、半導体基板21の一方の面に設けられている。半導体集積回路22は、半導体基板21に形成された拡散層（図示せず）、半導体基板21上に積層された絶縁層（図示せず）、及び積層された絶縁層（図示せず）に設けられたピアホール（図示せず）及び配線等（図示せず）から構成されている。

40

【0015】

電極パッド23は、半導体集積回路22上に複数設けられている。電極パッド23は、半導体集積回路22に設けられた配線（図示せず）と電気的に接続されている。電極パッド23の材料としては、例えば、Al等を用いることができる。電極パッド23の材料として、Cu層の上にAl層を形成したもの、Cu層の上にSi層を形成し、その上に更にAl層を形成したもの等を用いても構わない。

【0016】

保護膜24は、半導体集積回路22上に設けられている。保護膜24は、半導体集積回路22を保護するための膜であり、パッシベーション膜と呼ばれる場合もある。保護膜2

50

4としては、例えばSiN膜、PSG膜等を用いることができる。又、SiN膜やPSG膜等からなる層に、更にポリイミド等からなる層を積層しても構わない。

【0017】

接続端子12は、電極パッド23上に設けられている。接続端子12は、突起部を有する形状である。接続端子12の面12Aは絶縁層13の面13Aから露出しており、配線パターン14と電気的に接続されている。すなわち、接続端子12は、半導体装置10の有する半導体集積回路22と配線パターン14とを、電極パッド23を介して電気的に接続する機能を有する。

【0018】

接続端子12の高さH<sub>1</sub>は、例えば、10μm～60μmとすることができます。接続端子12としては、例えばAuバンプ、Auめっき膜、無電解めっき法により形成されたNi膜とそれを覆うAu膜から構成される金属膜等を用いることができる。Auバンプは、例えばワイヤボンディング装置を用いて、ボンディングワイヤにより形成することができる。又、めっき法により形成することもできる。

10

【0019】

絶縁層13は、半導体チップ11の回路形成面(主面)を封止保護すると共に、配線パターン14を形成する際のベース材の一部となるものである。絶縁層13は、接続端子12の面12Aを除く接続端子12及び半導体チップ11を覆うように設けられている。絶縁層13の面13Aは、接続端子12の面12Aと略面一とされている。

【0020】

20

絶縁層13の材料としては、感光性を有する材料、感光性を有しない材料の何れを用いても構わない。絶縁層13としては、例えば、粘着性を有するB-ステージ状態(半硬化状態)のシート状の絶縁樹脂(例えば、NCF(Non Conductive Film))、ペースト状の絶縁樹脂(例えば、NCP(Non Conductive Paste))、粘着性を有するシート状の異方性導電樹脂(例えば、ACF(Anisotropic Conductive Film))、ペースト状の異方性導電樹脂(例えば、ACP(Anisotropic Conductive Paste))、ビルドアップ樹脂(フィラー入りのエポキシ樹脂又はフィラーなしのエポキシ樹脂)、液晶ポリマー(liquid crystal polymer)等を挙げることができる。ACP及びACFは、エポキシ系樹脂をベースとする絶縁樹脂にNi/Auに被膜された小径球状の樹脂が分散されたものであり、鉛直方向に対しては導電性を有し、水平方向には絶縁性を有する樹脂である。絶縁層13の厚さT<sub>2</sub>は、例えば10μm～60μmとすることができます。

30

【0021】

絶縁層41は、半導体装置10の側面部を埋めるように設けられている。絶縁層41には、凹部41Xが形成されている。凹部41Xの形状は、例えば、最大開口部(ソルダーレジスト層16側)の径が底面の径よりも大きい逆円錐台形状とすることができます。但し、凹部41Xの形状は逆円錐台形状には限定されず、例えば、半球状や円柱状等であっても構わない。凹部41Xが逆円錐台形状である場合の最大開口部の径及び底面の径は、例えば、100μm～500μm程度とすることができます。凹部41Xの深さは、例えば、50μm～250μm程度とすることができます。絶縁層41は、配線パターン14を形成する際のベース材の一部となるものである。絶縁層41の材料としては、エポキシ系樹脂、ポリイミド系樹脂等の樹脂材を用いることができる。

40

【0022】

配線パターン14は、接続端子12の面12Aと接触するように、絶縁層13の面13A及び絶縁層41の面41A(凹部41X内も含む)に設けられている。以降、配線パターン14の凹部41X内に設けられている部分を、凹部14Xと称する。凹部14Xの形状は、凹部41Xの形状に対応している。

【0023】

配線パターン14は、接続端子12及び電極パッド23を介して、半導体集積回路22と電気的に接続されている。配線パターン14は、いわゆる再配線と呼ばれる場合があり、電極パッド23の位置と、外部接続端子17の位置とを異ならせるため(ファンアウト

50

及び任意の位置への端子配置をするため、所謂ピッチ変換のため)に設けられる。

【0024】

配線パターン14は、金属層26及び金属層27を有する。金属層26としては、例えばCu層、Cu層及びCr層からなる積層体、Cu層及びTi層からなる積層体等を用いることができる。又、無電解Cuメッキ層でもよいし、蒸着法、塗布法又は化学気相成長法(CVD)等により形成された金属薄膜層であってもよいし、上記の金属層形成方法を組み合わせてもよい。金属層26の厚さT<sub>6</sub>は、例えば2μmとすることができる。金属層27としては、例えばCu層等を用いることができる。金属層27の厚さT<sub>7</sub>は、例えば10μmとすることができる。

【0025】

ソルダーレジスト層16は、配線パターン14、絶縁層13A及び絶縁層41の面41Aを覆うように設けられている。ソルダーレジスト層16は、配線パターン14の凹部14Xの底面の一部を露出する開口部16Xを有する。ソルダーレジスト層16の材料は、例えば感光性樹脂組成物である。

【0026】

外部接続端子17は、ソルダーレジスト層16の開口部16X内に露出する配線パターン14の凹部14Xの底面に固定されている。外部接続端子17の一部はソルダーレジスト層16の表面(開口部16Xの内側面も含む)と接しているが、外部接続端子17はソルダーレジスト層16には固定されていない。外部接続端子17は、配線パターン14と電気的に接続されている。

【0027】

外部接続端子17は、例えばマザーボード等の実装基板(図示せず)に設けられたパッドと電気的に接続される端子である。外部接続端子17としては、例えば、はんだバンプ等を用いることができる。外部接続端子17の材料としては、例えばPbを含む合金、SnとCuの合金、SnとAgの合金、SnとAgとCuの合金等を用いることができる。又、樹脂(例えばジビニルベンゼン等)をコアとするはんだボール(Sn-3.5Ag)等を用いても構わない。なお、外部接続端子17は、所謂ファンアウト型であり、半導体装置10の内蔵されている領域よりも外側を含む領域に設けられている。

【0028】

このように、外部接続端子17を配線パターン14の凹部14Xの底面にのみ固定することにより、外部接続端子17のソルダーレジスト層16と接する部分は自由に動くことができる。そのため、例えば半導体装置内蔵基板20がマザーボード等の実装基板等に接続され、それぞれの熱膨張係数が異なるような場合であっても、熱膨張係数の違いによって生じる応力を緩和することができる。又、配線パターン14に凹部14Xを設けることにより、外部接続端子17を構成する材料の体積を増やすことが可能になるため、応力を緩和する能力を高めることができる。

【0029】

なお、ソルダーレジスト層16の表面から突起する部分の外部接続端子17の形状を大きくすることにより外部接続端子17を構成する材料の体積を増やしても応力を緩和する能力を高める効果は生じるが、外部接続端子17の配設ピッチを狭くできなくなる点で好ましくない。本実施の形態では、配線パターン14に凹部14Xを設けることにより、ソルダーレジスト層16の表面から突起する部分の外部接続端子17の形状を大きくすることなく外部接続端子17を構成する材料の体積を増やしているため、外部接続端子17の配設ピッチを狭くできないという問題は生じない。

【0030】

以上が、第1の実施の形態に係る半導体装置内蔵基板の構造である。

【0031】

[第1の実施の形態に係る半導体装置内蔵基板の製造方法]

続いて、第1の実施の形態に係る半導体装置内蔵基板の製造方法について説明する。図2～図19は、第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図であ

10

20

30

40

50

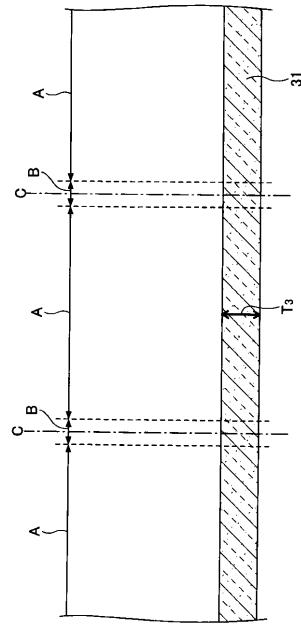

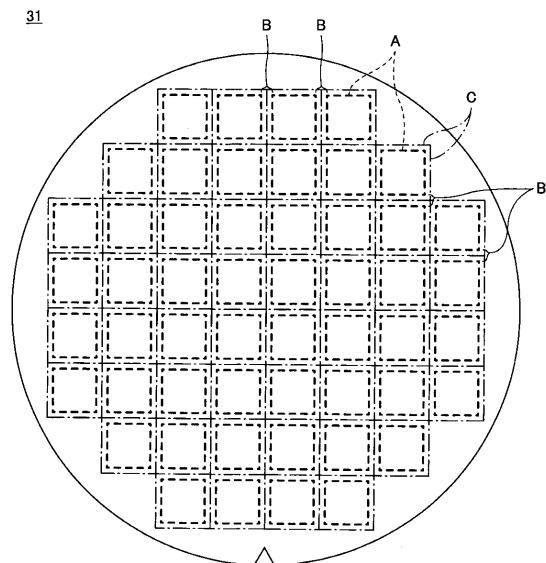

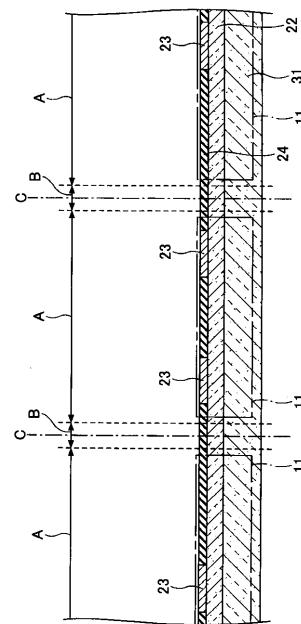

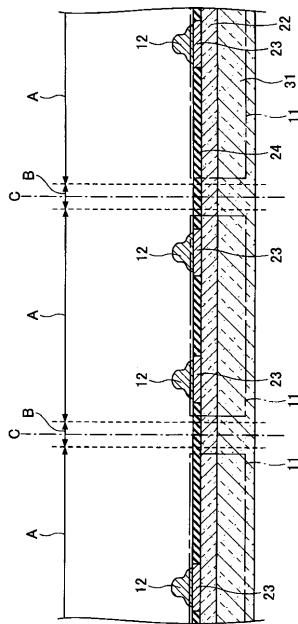

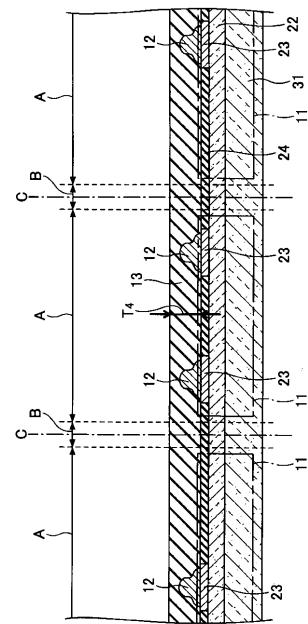

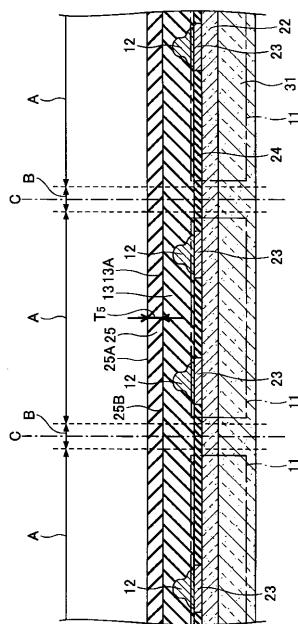

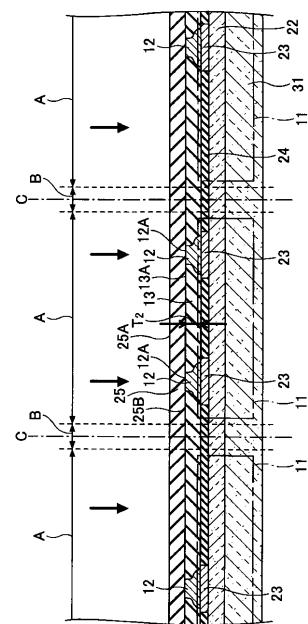

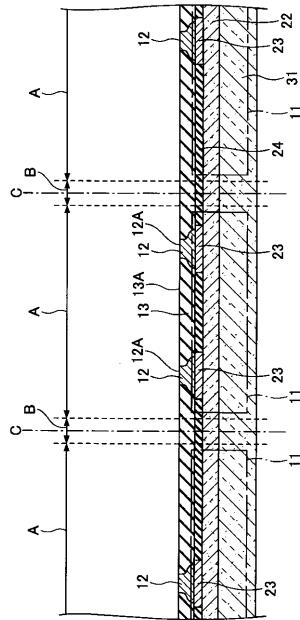

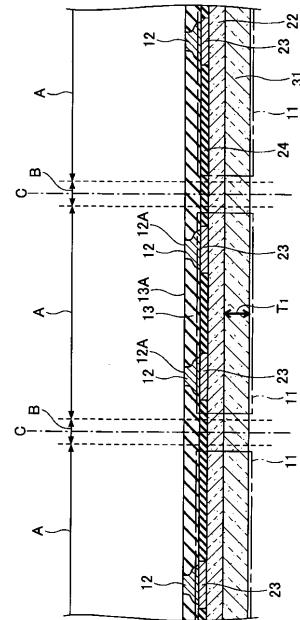

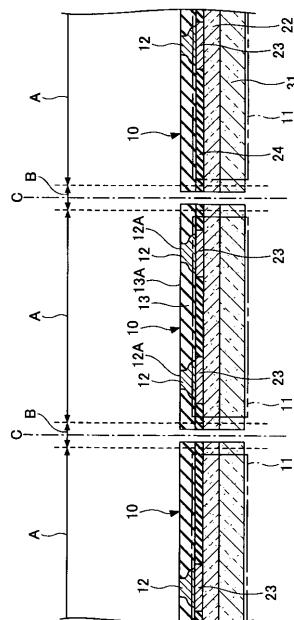

る。図2～図19において、図1に示す半導体装置内蔵基板20と同一構成部分には同一符号を付し、その説明を省略する場合がある。図2～図11において、Cはダイシングブレードが半導体基板31を切断する位置（以下、「基板切断位置C」とする）、Aは複数の半導体装置形成領域（以下、「半導体装置形成領域A」とする）、Bは複数の半導体装置形成領域Aを分離する、基板切断位置Cを含むスクライプ領域（以下、「スクライプ領域B」とする）を示している。

#### 【0032】

始めに、図2及び図3に示す工程では、複数の半導体装置形成領域Aと、複数の半導体装置形成領域Aを分離する、基板切断位置Cを含むスクライプ領域Bとを有する半導体基板31を準備する。図2は半導体基板を例示する断面図であり、図3は半導体基板を例示する平面図である。図2及び図3に示す半導体基板31は、薄板化され、かつ基板切断位置Cにおいて切断されることにより、先に説明した半導体基板21（図1参照）となるものである。半導体基板31としては、例えばSiウエハ等を用いることができる。半導体基板31の厚さT<sub>3</sub>は、例えば、500μm～775μmとすることができる。

10

#### 【0033】

次いで、図4に示す工程では、半導体装置形成領域Aに対応する半導体基板31の一方の面に、周知の手法により、半導体集積回路22、電極パッド23、及び保護膜24を有する半導体チップ11を形成する。電極パッド23の材料としては、例えばAl等を用いることができる。電極パッド23の材料として、Cu層の上にAl層を形成したもの、Cu層の上にSi層を形成し、その上に更にAl層を形成したもの等を用いても構わない。保護膜24としては、例えばSiN膜やPSG膜等を用いることができる。又、SiN膜やPSG膜等からなる層に、更にポリイミド等からなる層を積層しても構わない。

20

#### 【0034】

次いで、図5に示す工程では、半導体装置形成領域Aに設けられた複数の電極パッド23上にそれぞれ接続端子12を形成する。接続端子12としては、例えばAuバンプ、Auめっき膜、無電解めっき法やAlジンケート法により形成されたNi膜とNi膜上に積層されるAu膜から構成される金属膜等を用いることができる。Auバンプは、例えばワイヤボンディング装置を用いて、ボンディングワイヤにより形成することができる。又、めっき法により形成することもできる。なお、図5に示す工程で形成された複数の接続端子12には、高さばらつきが存在する。

30

#### 【0035】

次いで、図6に示す工程では、接続端子12が設けられた側の複数の半導体チップ11及び接続端子12を覆うように絶縁層13を形成する。絶縁層13の材料としては、感光性を有する材料、感光性を有しない材料の何れを用いても構わない。絶縁層13としては、例えば、粘着性を有するB-ステージ状態（半硬化状態）のシート状の絶縁樹脂（例えば、NCF（Non Conductive Film）、ペースト状の絶縁樹脂（例えば、NCP（Non Conductive Paste））、粘着性を有するシート状の異方性導電樹脂（例えば、ACF（Anisotropic Conductive Film））、ペースト状の異方性導電樹脂（例えば、ACP（Anisotropic Conductive Paste））、ビルドアップ樹脂（フィラー入りのエポキシ樹脂又はフィラーなしのエポキシ樹脂）、液晶ポリマー（liquid crystal polymer）等を挙げることができる。ACP及びACFは、エポキシ系樹脂をベースとする絶縁樹脂にNi/Auに被膜された小径球状の樹脂が分散されたものであり、鉛直方向に対しては導電性を有し、水平方向には絶縁性を有する樹脂である。

40

#### 【0036】

絶縁層13として粘着性を有したシート状の絶縁樹脂を用いた場合は、図5に示す構造体の一方の面側にシート状の絶縁樹脂を貼り付ける。又、絶縁層13としてペースト状の絶縁樹脂を用いた場合は、図5に示す構造体の一方の面側に印刷法等によりペースト状の絶縁樹脂を形成し、その後、プリベークして絶縁樹脂を半硬化させる。この半硬化した絶縁樹脂は接着性を有する。絶縁層13の厚さT<sub>4</sub>は、例えば20μm～100μmとすることができる。

50

## 【0037】

次いで図7に示す工程では、絶縁層13の面13Aに板状体25を配設する。板状体25は、絶縁層13の面13Aと対向する側の面25Bが粗面とされている。板状体25の厚さT<sub>5</sub>は、例えば10μmとすることができます。板状体25としては、例えばCu箔等の金属箔を用いることができる。又、板状体25として、PET等よりなるテンポラリーフィルムを用いても構わない。更に、予め樹脂フィルムの片面にCu箔が設けられた、片面銅箔付き樹脂フィルムを用いることも可能である。ここでは、板状体25として、金属箔を用いた場合を例にとり、以下の工程を説明する。

## 【0038】

次いで図8に示す工程では、図7に示す構造体を加熱した状態で、板状体25の面25A側から板状体25を押圧して、板状体25を絶縁層13に圧着する。これにより絶縁層13は押圧され、接続端子12の面12Aは絶縁層13の面13Aから露出する。又、絶縁層13の面13Aに、板状体25の面25Bの粗面が転写される。図7に示す構造体を加熱することにより、絶縁層13は硬化する。圧着後の絶縁層13の厚さT<sub>2</sub>は、例えば10μm～60μmとすることができます。

10

## 【0039】

次いで図9に示す工程では、図8に示す板状体25をエッティング等により全て除去する。図7～図9に示す工程により、後述する図15に示す工程において、金属層26と接続端子12との密着性を高めることができる。

## 【0040】

20

次いで図10に示す工程では、半導体基板31の裏面側から半導体基板31を研磨又は研削して、半導体基板31を薄板化する。半導体基板31の薄板化には、例えばバックサイドグラインダー等を用いることができる。薄板化後の半導体基板31の厚さT<sub>1</sub>は、例えば、50μm～500μmとすることができます。なお、図10に示す工程は削除される場合もある。

## 【0041】

次いで図11に示す工程では、スクライブ領域Bに対応する半導体基板31を基板切断位置Cに沿って切断することで、複数の半導体装置10が製造される。半導体基板31の切断は、例えば、ダイシング等によって行う。

## 【0042】

30

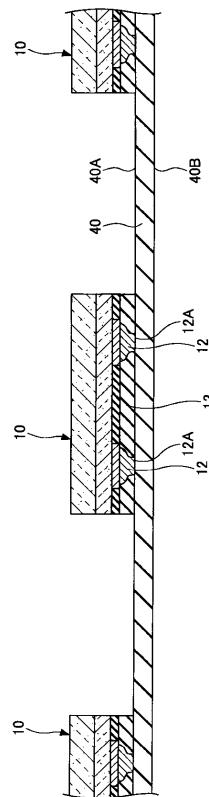

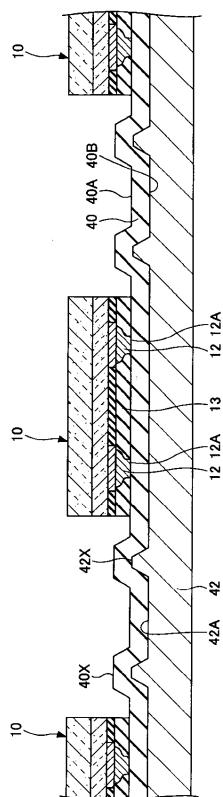

次いで図12に示す工程では、第1支持体40を準備する。そして、接続端子12の面12Aが第1支持体40の面40Aと対向するように、複数の半導体装置10を第1支持体40の面40Aに配置する。第1支持体40の面40Aは、例えば粘着性を有しており、配置された半導体装置10は仮固定される。第1支持体40の面40Aが粘着性を有していない場合には、例えば接着用テープ等により、配置された半導体装置10を仮固定する。

## 【0043】

第1支持体40としては、例えばPETフィルム、ポリイミドフィルム、金属箔等を用いることができる。第1支持体40の厚さは、PETフィルムやポリイミドフィルムを用いる場合には、例えば10μm～100μm程度とすることができます。又、金属箔(Cu箔等)を用いる場合には、例えば10μm～30μm程度とすることができます。但し、第1支持体40はPETフィルム、ポリイミドフィルム、金属箔には限定されず、後述する図13に示す工程において、第2支持体42の凸部42Xに対応して変形可能であれば、他の物を用いても構わない。

40

## 【0044】

次いで図13に示す工程では、面42Aに複数の凸部42Xが形成された第2支持体42を準備する。第2支持体42としては、例えば金属製やセラミック製の金型等を用いることができる。そして、第1支持体40の面40Bが第2支持体42の面42Aと対向するように、図12に示す構造体を第2支持体42の面42Aに配置する。そして、真空吸着等により、図12に示す構造体を第2支持体42の面42Aに吸着保持し仮固定する。

50

これにより、第1支持体40の一部が変形し、第2支持体42の凸部42Xに対応する凸部40Xが形成される。

【0045】

凸部40Xは、後述する図15に示す工程で絶縁層41の凹部41Xに転写される。凸部40Xの形状は、例えば円錐台形状とすることができます。但し、凸部40Xの形状は円錐台形状には限定されず、例えば半球状や円柱状等であっても構わない。凸部40Xが円錐台形状である場合の頂面の径及び底面の径は、例えば、100μm～500μm程度とすることができます。凸部40Xの高さは、例えば、50μm～250μm程度とすることができます。

【0046】

凸部40Xは、凸部42Xに対応した形状となるので、凸部40Xの形状を円錐台形状にしたい場合は、凸部42Xも円錐台形状にする必要がある。凸部42Xが円錐台形状である場合の頂面の径及び底面の径並びに高さは、所望の凸部40Xの寸法を決定して、それに対して第1支持体40の厚さ等を考慮して決定することができる。以降、凸部40X及び42Xの形状が円錐台形状である場合を例に説明する。

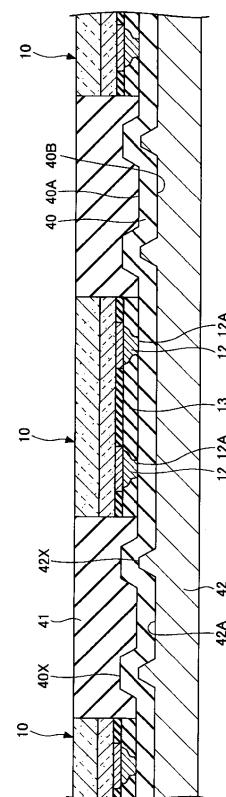

【0047】

次いで図14に示す工程では、隣接して配置された半導体装置10の、少なくとも側面部を埋めるように、第1支持体40の面40Aに絶縁層41を形成する。絶縁層41の材料としては、エポキシ系樹脂、ポリイミド系樹脂等の樹脂材を用いることができる。絶縁層41の形成方法の一例としては、第1支持体40の面40Aにエポキシ系樹脂、ポリイミド系樹脂等の樹脂フィルムをラミネートした後に、樹脂フィルムをプレス（押圧）し、その後、例えば190°C程度の温度で熱処理して硬化させることにより絶縁層41を得ることができる。又、第1支持体40の面40Aにエポキシ系樹脂、ポリイミド系樹脂等の液状の樹脂を塗布した後に、例えば190°C程度の温度で熱処理して硬化させることにより絶縁層41を得ることもできる。

【0048】

次いで図15に示す工程では、図14に示す第1支持体40と第2支持体42との吸着を解除した後、第1支持体40を除去する。これにより、凸部40Xの形状が絶縁層41に転写され、凹部41Xが形成される。凹部41Xの形状は、凸部40Xに対応する円錐台形状となる。

【0049】

次いで図16に示す工程では、絶縁層13の面13A及び絶縁層41の面41A（凹部41X内も含む）に、接続端子12の面12Aと接触するように金属層26及び金属層27を有する配線パターン14を形成する。凹部14Xは、配線パターン14の凹部41X内に形成された部分である。配線パターン14は、接続端子12及び電極パッド23を介して、半導体集積回路22と電気的に接続される。配線パターン14の厚さは、例えば12μmとすることができます。なお、図16は、図15とは上下が反転して描かれているため、凹部41Xの形状は逆円錐台形状となる。

【0050】

配線パターン14は、具体的には以下に示すように形成する。始めに、絶縁層13の面13A及び絶縁層41の面41A（凹部41X内も含む）にスパッタ法等により金属層26を形成する。金属層26と接続端子12とは、電気的に接続される。金属層26としては、例えばCu層、Cu層及びCr層からなる積層体、Cu層及びTi層からなる積層体等を用いることができる。又、無電解Cuメッキ層でもよいし、蒸着法、塗布法又は化学気相成長法（CVD）等により形成された金属薄膜層であってもよいし、上記の金属層形成方法を組み合わせてもよい。金属層26の厚さT<sub>6</sub>は、例えば2μmとすることができます。

【0051】

次いで、金属層26の面を覆うように、例えば金属層26を給電層として、電解メッキ法等により金属層27を形成する。金属層27としては、例えばCu層等を用いることが

10

20

30

40

50

できる。金属層 27 の厚さ  $T_7$  は、例えば  $10 \mu\text{m}$  とすることができます。次いで、金属層 27 の面にレジストを塗布し、このレジストをフォトリソグラフィ法により露光、現像することで配線パターン 14 の形成領域に対応する部分の金属層 27 の上部にレジスト膜を形成する。

【0052】

次いで、レジスト膜をマスクとして金属層 26 及び金属層 27 をエッチングし、レジスト膜が形成されていない部分の金属層 26 及び金属層 27 を除去することで、配線パターン 14 を形成する。その後、レジスト膜を除去する。その後、配線パターン 14 の粗化処理を行う。配線パターン 14 の粗化処理は、黒化処理又は粗化エッチング処理等の方法により行うことができる。上記粗化処理は、配線パターン 14 の上面及び側面に形成されるソルダーレジスト層 16 と配線パターン 14 との密着性を向上させるためのものである。10

【0053】

次いで、図 17 に示す工程では、配線パターン 14、絶縁層 13 の面 13A 及び絶縁層 41 の面 41A を覆うように、配線パターン 14 の凹部 14X の底面の一部を露出する開口部 16X を有するソルダーレジスト層 16 を形成する。具体的には、始めに配線パターン 14、絶縁層 13 の面 13A 及び絶縁層 41 の面 41A (凹部 41X 内も含む) を覆うように、例えば感光性樹脂組成物を塗布する。次いでフォトリソグラフィ法により感光性樹脂組成物を露光、現像し、配線パターン 14 の凹部 14X の底面の一部を露出するよう感光性樹脂組成物の一部をエッチングにより除去し、開口部 16X を形成する。20

【0054】

次いで、図 18 に示す工程では、開口部 16X 内に露出する配線パターン 14 の凹部 14X の底面に接続される外部接続端子 17 を形成する。外部接続端子 17 は、ソルダーレジスト層 16 の開口部 16X 内に露出する配線パターン 14 の凹部 14X の底面に固定される。外部接続端子 17 の一部はソルダーレジスト層 16 の表面 (開口部 16X の内側面も含む) と接するが、外部接続端子 17 はソルダーレジスト層 16 には固定されていない。外部接続端子 17 は、配線パターン 14 と電気的に接続される。20

【0055】

外部接続端子 17 としては、例えば、はんだバンプ等を用いることができる。外部接続端子 17 の材料としては、例えば Pb を含む合金、Sn と Cu の合金、Sn と Ag の合金、Sn と Ag と Cu の合金等を用いることができる。又、樹脂 (例えばジビニルベンゼン等) をコアとするはんだボール (Sn - 3.5Ag) 等を用いても構わない。これにより、半導体装置内蔵基板 20 に相当する複数の構造体が形成される。30

【0056】

次いで、図 19 に示す工程では、図 18 に示す構造体を絶縁層 41 の略中央で切断することで、複数の半導体装置内蔵基板 20 が製造される。図 18 に示す構造体の切断は、例えばダイシング等によって行う。

【0057】

以上が、第 1 の実施の形態に係る半導体装置内蔵基板の製造方法である。

【0058】

第 1 の実施の形態によれば、始めに、接続端子 12 の面 12A が絶縁層 13 から露出した半導体装置 10 を製造する。そして、少なくとも半導体装置 10 の側面部を埋めるように絶縁層 41 を形成する。更に、接続端子 12 の面 12A と接触するように、接続端子 12 と電気的に接続される配線パターン 14 (再配線) を形成する。その結果、絶縁層にレーザで孔明けし接続端子を露出する工程が必要ないため、半導体装置内蔵基板 20 の製造コストの上昇を抑制することができる。40

【0059】

又、絶縁層にレーザで孔明けし接続端子を露出する工程が必要ないため、接続端子 12 の間隔はレーザのスポット径 (例えば、直径  $70 \mu\text{m}$  程度) に制限されない。その結果、半導体装置 10 の有する半導体集積回路 22 と配線パターン 14 (再配線) とを電気的に接続する接続端子 12 の間隔の微細化が可能となる。接続端子 12 の間隔は、配線パター50

ンのL/S(ライン/スペース)と同程度まで微細化(例えば、間隔100μm以下。最短間隔1μm程度)できる。

#### 【0060】

又、配線パターン14の一部に絶縁層41の凹部41Xに対応する凹部14Xを形成し、外部接続端子17を配線パターン14の凹部14Xの底面の一部にのみ固定することにより、外部接続端子17のソルダーレジスト層16と接する部分は自由に動くことができる。そのため、例えば半導体装置内蔵基板20がマザーボード等の実装基板等に接続され、それぞれの熱膨張係数が異なるような場合であっても、熱膨張係数の違いによって生じる応力を緩和することができる。又、配線パターン14に凹部14Xを形成することにより、外部接続端子17を構成する材料の体積を増やすことが可能になるため、応力を緩和する能力を高めることができる。

10

#### 【0061】

なお、ソルダーレジスト層16の表面から突起する部分の外部接続端子17の形状を大きくすることにより外部接続端子17を構成する材料の体積を増やしても応力を緩和する能力を高める効果は生じるが、外部接続端子17の配設ピッチを狭くできなくなる点で好ましくない。本実施の形態では、配線パターン14に凹部14Xを設けることにより、ソルダーレジスト層16の表面から突起する部分の外部接続端子17の形状を大きくすることなく外部接続端子17を構成する材料の体積を増やしているため、外部接続端子17の配設ピッチを狭くできないという問題は生じない。

#### 【0062】

20

#### 第2の実施の形態

##### 【第2の実施の形態に係る半導体装置内蔵基板の構造】

始めに、第2の実施の形態に係る半導体装置内蔵基板の構造について説明する。図20は、第2の実施の形態に係る半導体装置内蔵基板の断面図である。図20に示す半導体装置内蔵基板50において、図1に示す半導体装置内蔵基板20と同一構成部分には同一符号を付し、その説明を省略する場合がある。図20を参照するに、第2の実施の形態に係る半導体装置内蔵基板50は、第1の実施の形態に係る半導体装置内蔵基板20の絶縁層41が絶縁層51に置換された以外は、半導体装置内蔵基板20と同様である。以下、半導体装置内蔵基板20と異なる部分についてのみ説明する。

#### 【0063】

30

半導体装置内蔵基板20において、絶縁層41は半導体装置10の側面部のみを埋めるように形成されていたが、半導体装置内蔵基板50において、絶縁層51は半導体装置10の側面部及び裏面部を埋めるように形成されている。絶縁層51の材料としては、エポキシ系樹脂、ポリイミド系樹脂等の樹脂材を用いることができる。このような構造にすることにより、半導体装置10の裏面部を保護することができる。

#### 【0064】

以上が、第2の実施の形態に係る半導体装置内蔵基板の構造である。

#### 【0065】

##### 【第2の実施の形態に係る半導体装置内蔵基板の製造方法】

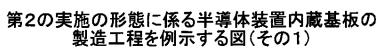

続いて、第2の実施の形態に係る半導体装置内蔵基板の製造方法について説明する。図21及び図22は、第2の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図である。図21及び図22において、図20に示す半導体装置内蔵基板50と同一構成部分には同一符号を付し、その説明を省略する場合がある。

40

#### 【0066】

始めに、第1の実施の形態の図2～図13と同様の工程を行う。次いで、図21に示す工程では、第1支持体40の面40Aに、半導体装置10の側面部及び裏面部を埋めるように絶縁層51を形成する。絶縁層51の材料としては、エポキシ系樹脂、ポリイミド系樹脂等の樹脂材を用いることができる。絶縁層51の形成方法の一例としては、第1支持体40の面40A及び半導体装置10の裏面部にエポキシ系樹脂、ポリイミド系樹脂等の樹脂フィルムをラミネートした後に、樹脂フィルムをプレス(押圧)し、その後、例えば

50

190 程度の温度で熱処理して硬化させることにより絶縁層51を得ることができる。又、第1支持体40の面40A及び半導体装置10の裏面にエポキシ系樹脂、ポリイミド系樹脂等の液状の樹脂を塗布した後に、例えば190 程度の温度で熱処理して硬化させることにより絶縁層51を得ることもできる。

【0067】

次いで、第1の実施の形態の図15～図18と同様の工程を行う。次いで、図22に示す工程では、図18に相当する構造体を半導体装置10の側面を埋める絶縁層51の略中央で切断することで、複数の半導体装置内蔵基板50が製造される。図18に相当する構造体の切断は、例えばダイシング等によって行う。

【0068】

以上が、第2の実施の形態に係る半導体装置内蔵基板の製造方法である。

【0069】

第2の実施の形態によれば、第1の実施の形態と同様の効果を奏する。又、第2の実施の形態に係る半導体装置内蔵基板50は、半導体装置10の発生する熱の放熱性に関しては、第1の実施の形態に係る半導体装置内蔵基板20に劣るが、半導体装置10の裏面を保護したいような用途には有用である。

【0070】

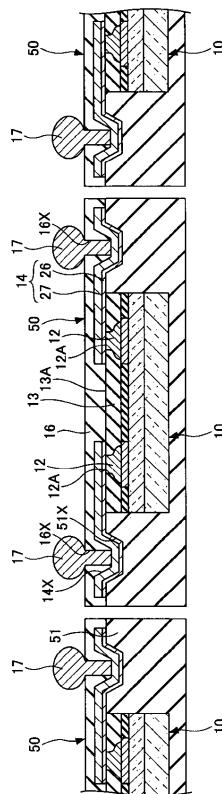

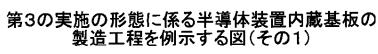

第3の実施の形態

第3の実施の形態では、第1及び第2の実施の形態の図12～図14に示す工程を、異なる工程(図23及び図24参照)に変更する例を示す。

【0071】

図23及び図24は、第3の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図である。図23及び図24において、図12～図14と同一構成部分には同一符号を付し、その説明を省略する場合がある。

【0072】

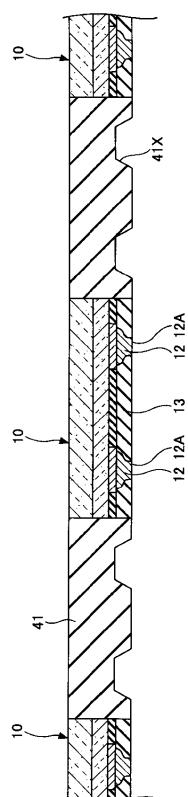

始めに、第1の実施の形態の図2～図11と同様の工程を行う。次いで、図23に示す工程では、面43Aに複数の凸部43Xが形成された第3支持体43を準備する。そして、接続端子12の面12Aが第3支持体43の面43Aと対向するように、複数の半導体装置10を第3支持体43の面43Aに配置する。第3支持体43の面43Aは、例えば粘着性を有しており、配置された半導体装置10は仮固定される。第3支持体43の面43Aが粘着性を有していない場合には、例えば接着用テープ等により、配置された半導体装置10を仮固定する。第3支持体43としては、金属板やガラス板等を用いることができる。第3支持体43には、金型等とは異なり、1回使用した後に廃棄できるような安価な材料を用いても良い。

【0073】

凸部43Xの形状は、例えば円錐台形状とすることができます。但し、凸部43Xの形状は円錐台形状には限定されず、例えば半球状や円柱状等であっても構わない。凸部43Xが円錐台形状である場合の頂面の径及び底面の径は、例えば、100 μm～500 μm程度とすることができます。凸部43Xの高さは、例えば、50 μm～250 μm程度とすることができます。以降、凸部43Xの形状が円錐台形状である場合を例に説明する。

【0074】

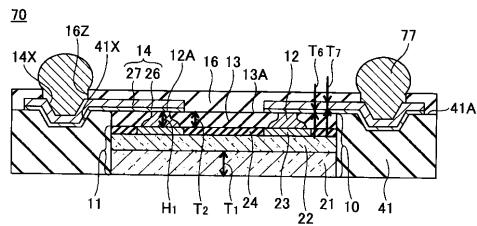

次いで図24に示す工程では、隣接して配置された半導体装置10の、少なくとも側面を埋めるように、第3支持体43の面43Aに絶縁層41を形成する。絶縁層41の材料としては、エポキシ系樹脂、ポリイミド系樹脂等の樹脂材を用いることができる。絶縁層41の形成方法の一例としては、第3支持体43の面43Aにエポキシ系樹脂、ポリイミド系樹脂等の樹脂フィルムをラミネートした後に、樹脂フィルムをプレス(押圧)し、その後、例えば190 程度の温度で熱処理して硬化させることにより絶縁層41を得ることができる。又、第1支持体43の面43Aにエポキシ系樹脂、ポリイミド系樹脂等の液状の樹脂を塗布した後に、例えば190 程度の温度で熱処理して硬化させることにより絶縁層41を得ることもできる。

10

20

30

40

50

## 【0075】

次いで、第3支持体43を除去することにより、第1の実施の形態の図15と同様の構造体が作製される。すなわち、第3支持体43の凸部43Xの形状が絶縁層41に転写され、凹部41Xが形成される。凹部41Xの形状は、凸部43Xに対応する円錐台形状となる。なお、第3支持体43は、容易に機械的に剥離することができる。

## 【0076】

第3の実施の形態によれば、第1及び第2の実施の形態と同様の効果を奏するが、更に以下の効果を奏する。すなわち、凸部を有する第3支持体上に接着用テープ等により半導体装置を仮固定することにより、金型等を用いて半導体装置を真空吸着する必要がなくなったため、第1及び第2の実施の形態に係る第1及び第2支持体を第3支持体のみに置換することが可能となり、製造工程を削減することができる。

10

## 【0077】

## 第4の実施の形態

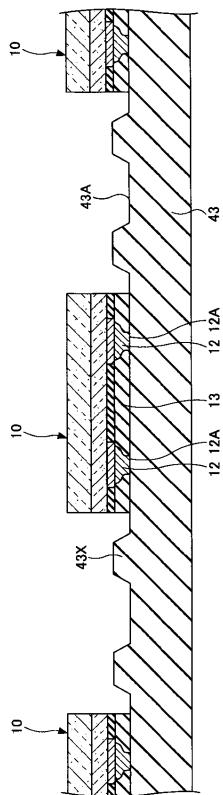

第4の実施の形態では、第1の実施の形態に係る半導体装置内蔵基板とは異なる半導体装置内蔵基板の例を示す。

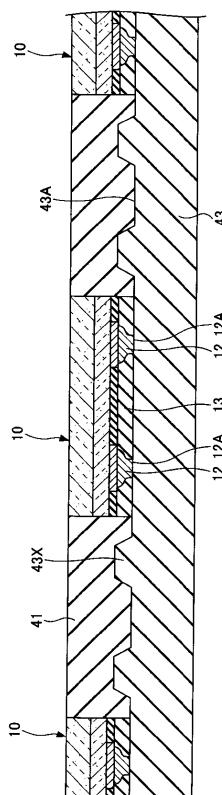

## 【0078】

図25は、第4の実施の形態に係る半導体装置内蔵基板の断面図である。図25を参照するに、半導体装置内蔵基板60は、半導体装置内蔵基板20のソルダーレジスト層16の開口部16Xが開口部16Yに置換され、外部接続端子17が外部接続端子67に置換されたものである。なお、半導体装置内蔵基板60の製造方法は、半導体装置内蔵基板20又は50の製造方法と同様であるため、その説明は省略する。

20

## 【0079】

ソルダーレジスト層16は、配線パターン14、絶縁層13の面13A及び絶縁層41の面41Aを覆うように設けられている。ソルダーレジスト層16は、配線パターン14の凹部14Xの底面及び内側面（傾斜面）の一部を露出する開口部16Yを有する。ソルダーレジスト層16の材料は、例えば感光性樹脂組成物である。

## 【0080】

外部接続端子67は、ソルダーレジスト層16の開口部16Y内に露出する配線パターン14の凹部14Xの底面及び内側面（傾斜面）に固定されている。外部接続端子67の一部はソルダーレジスト層16の表面（開口部16Yの内側面も含む）と接しているが、外部接続端子67はソルダーレジスト層16には固定されていない。外部接続端子67は、配線パターン14と電気的に接続されている。

30

## 【0081】

外部接続端子67は、例えばマザーボード等の実装基板（図示せず）に設けられたパッドと電気的に接続される端子である。外部接続端子67としては、例えば、はんだバンプ等を用いることができる。外部接続端子67の材料としては、例えばPbを含む合金、SnとCuの合金、SnとAgの合金、SnとAgとCuの合金等を用いることができる。又、樹脂（例えばジビニルベンゼン等）をコアとするはんだボール（Sn-3.5Ag）等を用いても構わない。なお、外部接続端子67は、所謂ファンアウト型であり、半導体装置10の内蔵されている領域よりも外側を含む領域に設けられている。

40

## 【0082】

このように、外部接続端子67を配線パターン14の凹部14Xの底面及び内側面（傾斜面）にのみ固定することにより、外部接続端子67のソルダーレジスト層16と接する部分は自由に動くことができる。そのため、例えば半導体装置内蔵基板60がマザーボード等の実装基板等に接続され、それぞれの熱膨張係数が異なるような場合であっても、熱膨張係数の違いによって生じる応力を緩和することができる。又、配線パターン14に凹部14Xを設けることにより、外部接続端子67を構成する材料の体積を増やすことが可能になるため、応力を緩和する能力を高めることができる。

## 【0083】

但し、第1～第3の実施の形態に係る外部接続端子と比べると、外部接続端子67は自

50

由に動くことができる部分が少ないため、応力を緩和する能力は、第1～第3の実施の形態よりも低くなる。

【0084】

なお、ソルダーレジスト層16の表面から突起する部分の外部接続端子67の形状を大きくすることにより外部接続端子67を構成する材料の体積を増やしても応力を緩和する能力を高める効果は生じるが、外部接続端子67の配設ピッチを狭くできなくなる点で好ましくない。本実施の形態では、配線パターン14に凹部14Xを設けることにより、ソルダーレジスト層16の表面から突起する部分の外部接続端子67の形状を大きくすることなく外部接続端子67を構成する材料の体積を増やしているため、外部接続端子67の配設ピッチを狭くできないという問題は生じない。

10

【0085】

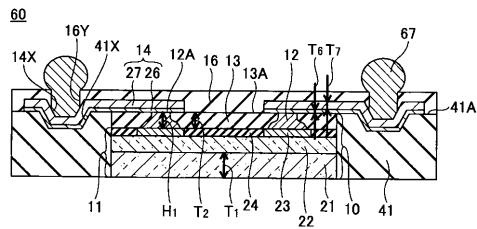

第5の実施の形態

第5の実施の形態では、第1の実施の形態に係る半導体装置内蔵基板とは異なる半導体装置内蔵基板の例を示す。

【0086】

図26は、第5の実施の形態に係る半導体装置内蔵基板の断面図である。図26を参照するに、半導体装置内蔵基板70は、半導体装置内蔵基板20のソルダーレジスト層16の開口部16Xが開口部16Zに置換され、外部接続端子17が外部接続端子77に置換されたものである。半導体装置内蔵基板70の製造方法は、半導体装置内蔵基板20又は50の製造方法と同様であるため、その説明は省略する。

20

【0087】

ソルダーレジスト層16は、配線パターン14、絶縁層13の面13A及び絶縁層41の面41Aを覆うように設けられている。ソルダーレジスト層16は、配線パターン14の凹部14Xの全部を露出する開口部16Zを有する。ソルダーレジスト層16の材料は、例えば感光性樹脂組成物である。

【0088】

外部接続端子77は、ソルダーレジスト層16の開口部16Z内に露出する配線パターン14の凹部14Xを含む領域に固定されている。外部接続端子77の一部はソルダーレジスト層16の開口部16Zの内側面と接しているが、外部接続端子77はソルダーレジスト層16には固定されていない。外部接続端子77は、配線パターン14と電気的に接続されている。

30

【0089】

外部接続端子77は、例えばマザーボード等の実装基板(図示せず)に設けられたパッドと電気的に接続される端子である。外部接続端子77としては、例えば、はんだバンプ等を用いることができる。外部接続端子77の材料としては、例えばPbを含む合金、SnとCuの合金、SnとAgの合金、SnとAgとCuの合金等を用いることができる。又、樹脂(例えばジビニルベンゼン等)をコアとするはんだボール(Sn-3.5Ag)等を用いても構わない。なお、外部接続端子77は、所謂ファンアウト型であり、半導体装置10の内蔵されている領域よりも外側を含む領域に設けられている。

【0090】

40

このように、配線パターン14に凹部14Xを設け、外部接続端子77を配線パターン14の凹部14Xを含む領域に固定することにより、外部接続端子77を構成する材料の体積を増やすことが可能になるため、応力を緩和する能力を高めることができる。

【0091】

但し、第1～第4の実施の形態に係る外部接続端子と比べると、外部接続端子77は自由に動くことができる部分が少ないため、応力を緩和する能力は、第1～第4の実施の形態よりも低くなる。

【0092】

なお、ソルダーレジスト層16の表面から突起する部分の外部接続端子77の形状を大きくすることにより外部接続端子77を構成する材料の体積を増やしても応力を緩和する

50

能力を高める効果は生じるが、外部接続端子 77 の配設ピッチを狭くできなくなる点で好ましくない。本実施の形態では、配線パターン 14 に凹部 14X を設けることにより、ソルダーレジスト層 16 の表面から突起する部分の外部接続端子 77 の形状を大きくすることなく外部接続端子 77 を構成する材料の体積を増やしているため、外部接続端子 77 の配設ピッチを狭くできないという問題は生じない。

#### 【0093】

以上、本発明の好ましい実施の形態について詳説したが、本発明は、上述した実施の形態に制限されることはなく、本発明の範囲を逸脱することなく、上述した実施の形態に種々の変形及び置換を加えることができる。

#### 【0094】

例えば、第 2 の実施の形態と、第 4 又は第 5 の実施の形態とを組み合わせても構わない。

#### 【符号の説明】

#### 【0095】

|                                             |           |    |

|---------------------------------------------|-----------|----|

| 10                                          | 半導体装置     | 10 |

| 11                                          | 半導体チップ    |    |

| 12                                          | 接続端子      |    |

| 12A, 13A, 25A, 25B, 40A, 40B, 41A, 42A, 43A | 面         |    |

| 13, 41, 51                                  | 絶縁層       |    |

| 14                                          | 配線パターン    | 20 |

| 14X, 41X                                    | 凹部        |    |

| 16                                          | ソルダーレジスト層 |    |

| 16X, 16Y, 16Z                               | 開口部       |    |

| 17, 67, 77                                  | 外部接続端子    |    |

| 20, 50, 60, 70                              | 半導体装置内蔵基板 |    |

| 21, 31                                      | 半導体基板     |    |

| 22                                          | 半導体集積回路   |    |

| 23                                          | 電極パッド     |    |

| 24                                          | 保護膜       |    |

| 25                                          | 板状体       | 30 |

| 26, 27                                      | 金属層       |    |

| 40                                          | 第 1 支持体   |    |

| 40X, 42X, 43X                               | 凸部        |    |

| 42                                          | 第 2 支持体   |    |

| 43                                          | 第 3 支持体   |    |

| A                                           | 半導体装置形成領域 |    |

| B                                           | スクライブ領域   |    |

| C                                           | 基板切断位置    |    |

| T <sub>1</sub> ~ T <sub>7</sub>             | 厚さ        |    |

| H <sub>1</sub>                              | 高さ        | 40 |

【 図 1 】

## 【 図 2 】

### 第1の実施の形態に係る半導体装置内蔵基板の断面図

### 第1の実施の形態に係る半導体装置内蔵基板の 製造工程を例示する図(その1)

【図3】

【 図 4 】

## 第1の実施の形態に係る半導体装置内蔵基板の 製造工程を例示する図(その2)

### 第1の実施の形態に係る半導体装置内蔵基板の 製造工程を例示する図(その3)

【図5】

第1の実施の形態に係る半導体装置内蔵基板の

製造工程を例示する図(その4)

【図6】

第1の実施の形態に係る半導体装置内蔵基板の

製造工程を例示する図(その5)

【図7】

第1の実施の形態に係る半導体装置内蔵基板の

製造工程を例示する図(その6)

【図8】

第1の実施の形態に係る半導体装置内蔵基板の

製造工程を例示する図(その7)

【図9】

【 図 1 0 】

### 第1の実施の形態に係る半導体装置内蔵基板の 製造工程を例示する図(その8)

### 第1の実施の形態に係る半導体装置内蔵基板の 製造工程を例示する図(その9)

### 【図 1 1】

【図12】

### 第1の実施の形態に係る半導体装置内蔵基板の 製造工程を例示する図(その10)

### 第1の実施の形態に係る半導体装置内蔵基板の 製造工程を例示する図(その11)

【図13】

第1の実施の形態に係る半導体装置内蔵基板の

製造工程を例示する図(その12)

【図14】

第1の実施の形態に係る半導体装置内蔵基板の

製造工程を例示する図(その13)

【図15】

第1の実施の形態に係る半導体装置内蔵基板の

製造工程を例示する図(その14)

【図16】

第1の実施の形態に係る半導体装置内蔵基板の

製造工程を例示する図(その15)

【図17】

第1の実施の形態に係る半導体装置内蔵基板の

製造工程を例示する図(その16)

【図18】

第1の実施の形態に係る半導体装置内蔵基板の

製造工程を例示する図(その17)

【図19】

第1の実施の形態に係る半導体装置内蔵基板の

製造工程を例示する図(その18)

【図20】

第2の実施の形態に係る半導体装置内蔵基板の断面図

【図21】

## 第2の実施の形態に係る半導体装置内蔵基板の 製造工程を例示する図(その2)

### 【図23】

### 第3の実施の形態に係る半導体装置内蔵基板の 製造工程を例示する図(その2)

## 【図25】

第4の実施の形態に係る半導体装置内蔵基板の断面図

## 【図26】

第5の実施の形態に係る半導体装置内蔵基板の断面図

---

フロントページの続き

審査官 川内野 真介

(56)参考文献 特開2004-95836 (JP, A)

特開2005-79431 (JP, A)

特開2002-231577 (JP, A)

特開2001-185444 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12

H05K 3/46

H05K 1/18