【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第3区分

【発行日】平成25年1月10日(2013.1.10)

【公開番号】特開2011-108135(P2011-108135A)

【公開日】平成23年6月2日(2011.6.2)

【年通号数】公開・登録公報2011-022

【出願番号】特願2009-264631(P2009-264631)

【国際特許分類】

G 06 T 1/20 (2006.01)

G 09 G 5/00 (2006.01)

G 09 G 5/377 (2006.01)

H 04 N 5/66 (2006.01)

【F I】

G 06 T 1/20 B

G 09 G 5/00 5 5 0 H

G 09 G 5/00 5 3 0 H

G 09 G 5/36 5 2 0 L

H 04 N 5/66 Z

【手続補正書】

【提出日】平成24年11月16日(2012.11.16)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】請求項8

【補正方法】変更

【補正の内容】

【請求項8】

複数の画素により構成された画像を表す画像データを、前記画像データに対応した表示画像を分割した各部分画像に対応して設けられ、該部分画像に対応した画像データを入力し、該部分画像を構成する各画素のデータを該画素の周辺画素のデータを参照して処理する複数の画像処理ユニットを用いて処理をする画像処理方法であって、

前記複数の画像処理ユニットのうち、

第1の画像処理ユニットを用いて、第1の部分画像について前記画像処理を行う際、当該第1の部分画像と隣り合った他の部分画像を構成する画素のうち、少なくとも前記第1の部分画像に隣接する領域の画素のデータを取得して、前記周辺画素のデータとして、前記画像処理に用い、

第2の画像処理ユニットを用いて、前記第1の部分画像とは異なる第2の部分画像について前記画像処理を行うと共に、前記第1の画像処理ユニットが前記周辺画素として扱う画素の少なくとも一部のデータを、前記第1の画像処理ユニットが扱う部分画像に隣り合った部分画像を処理する画像処理ユニットから、前記第1の画像処理ユニットに向けて仲介し、

前記複数の画像処理ユニットによって前記画像処理が行われた後の画素のデータを用いて、表示用画像データを出力する

画像処理方法。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0014

【補正方法】変更

【補正の内容】

## 【0014】

## [適用例8]

複数の画素により構成された画像を表す画像データを、前記画像データに対応した表示画像を分割した各部分画像に対応して設けられ、該部分画像に対応した画像データを入力し、該部分画像を構成する各画素のデータを該画素の周辺画素のデータを参照して処理する複数の画像処理ユニットを用いて処理をする画像処理方法であって、前記複数の画像処理ユニットのうち、第1の画像処理ユニットを用いて、第1の部分画像について前記画像処理を行う際、当該第1の部分画像と隣り合った他の部分画像を構成する画素のうち、少なくとも前記第1の部分画像に隣接する領域の画素のデータを取得して、前記周辺画素のデータとして、前記画像処理に用い、第2の画像処理ユニットを用いて、前記第1の部分画像とは異なる第2の部分画像について前記画像処理を行うと共に、前記第1の画像処理ユニットが前記周辺画素として扱う画素の少なくとも一部のデータを、前記第1の画像処理ユニットが扱う部分画像に隣り合った部分画像を処理する画像処理ユニットから、前記第1の画像処理ユニットに向けて仲介し、前記複数の画像処理ユニットによって前記画像処理が行われた後の画素のデータを用いて、表示用画像データを出力する画像処理方法。

## 【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0020

【補正方法】変更

【補正の内容】

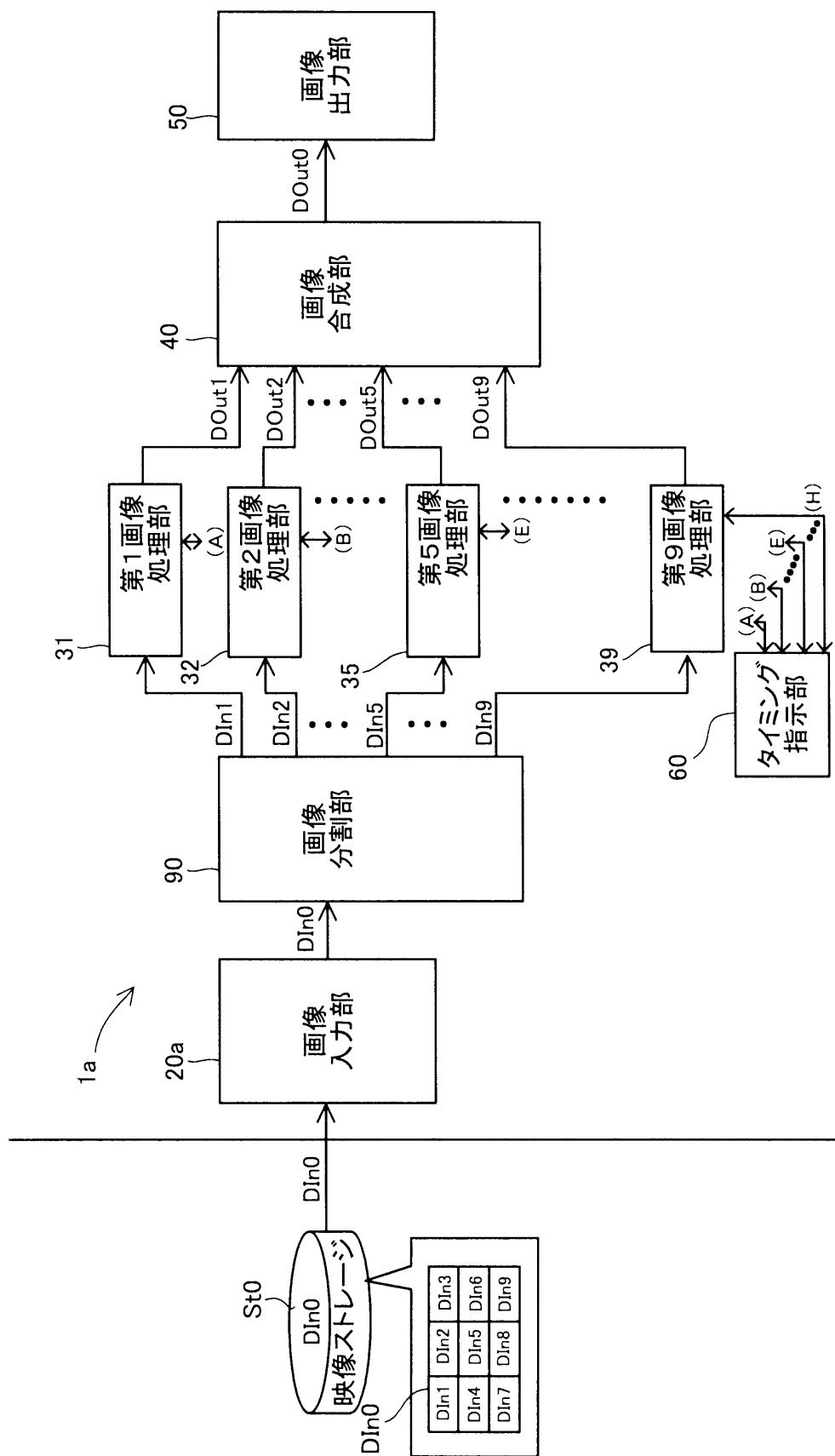

## 【0020】

図2は、第5画像処理部35の内部構成を示すブロック図である。第5画像処理部35は、デジタル信号処理プロセッサー(DSP)としての機能を有するCPU71、動作プログラムなどを記憶したROM73、ワークエリアとして利用されるRAM75、画像データDIn0を分割した画像データ、つまり画像ブロックDIn5より若干大きな記憶容量を有するフレームメモリー80、映像ストレージSt5から画像ブロックDIn5を受け取る入力インタフェース81、画像合成部40に画像データDOut5を出力する出力インタフェース83、タイミング指示部60からのタイミング信号を受け取る指示入力インタフェース85を備える。CPU71は、第5画像処理部35の全体の動作を統御するが、特にフレームメモリー80に高速にアクセスして、所定の画像処理(フィルター処理)を行なうことができる専用のプロセッサーである。なお、CPU71の機能は、FPGA(Field Programmable Array)や、画像処理専用LSIなどを用いて実現してもよい。

## 【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0024

【補正方法】変更

【補正の内容】

## 【0024】

各画像処理部のデータ交換部によって周辺画素データの交換が終了すると、各フレームメモリー制御部が、フレームメモリーに記憶されている画像ブロックDInと周辺画素データ交換処理によって取得した周辺画素データとを、各フィルター処理部に出力し、各フィルター処理部はそれら2つのデータを用いて、フィルター処理を行う(ステップS150)。フィルター処理部はフィルター処理を終了すると、処理後のデータを各分割画像出力部を介して画像合成部40に出力する。画像合成部40は、各分割画像出力部から受信した画像データDOut1~9を合成し(ステップS160)、画像データDOut0として画像出力部50に出力する。画像出力部50は入力された画像データDOut0を液晶パネル駆動部に出力信号として出力し(ステップS170)する。このような画像処理を、入力されてくる画像ブロックDIn1~9に対して繰り返し行い、画像処理装置1は画像処理を行う。

## 【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0029

【補正方法】変更

【補正の内容】

【0029】

この時、例えば、画像ブロックDIn1は、画像ブロックDIn4が画像処理に必要とする周辺画像データをDIn4に送信するとともに、画像ブロックDIn5が画像処理に必要な周辺画素データのうち、画像ブロックDIn1に含まれる周辺画素データ（図8（b）の横線ハッチング部分）も同時に、画像ブロックDIn4に送信する。画像ブロックDIn4に対応する第4画像処理部34のデータ交換部341は、それらの周辺画素データを取得すると一時的に、第4画像処理部が備えるフレームメモリー344に記憶する。この場合、画像ブロックDIn1が画像ブロックDIn4に送信した周辺画素データのうち、画像ブロックDIn5が処理に必要とする周辺画素データは、画像ブロックDIn4が処理に必要とする周辺画素データの中に含まれる。つまり、説明の便宜上、この二つの周辺画素データは別個のものとして説明したが、実際は、画像ブロックDIn1は画像ブロックDIn4に対して、画像ブロックDIn4が処理に必要な周辺画素データを送信する。

【手続補正6】

【補正対象書類名】明細書

【補正対象項目名】0044

【補正方法】変更

【補正の内容】

【0044】

（C3）変形例3：

上記実施例2では、図9に示した周辺画素データの交換経路によって周辺画素データを交換したが、これに限ることなく、DIn0を、 $3 \times 3$ や、それ以外の分割数に分割することが可能である。例えば図10に示した交換経路を構成して周辺画素データを交換することが可能である。図10（a）および図10（b）に示した交換経路は、各画像ブロックDIn間を、1つの経路で、かつ、同じ経路を2度通ることなく結ぶように構成されている。図10（b）は、上記で説明した「閉路」の経路構成である。このように構成した交換経路によって周辺画素データを交換する場合、上述したように、各データ交換部は、周辺画素データを経路上の一方向のみに送信すればよい。このような経路構成としても、上記第2実施例と同様の効果を得ることが可能である。

【手続補正7】

【補正対象書類名】図面

【補正対象項目名】図11

【補正方法】変更

【補正の内容】

【図 11】