### (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 8 January 2004 (08.01,2004)

**PCT**

# (10) International Publication Number $WO\ 2004/003620\ A1$

(51) International Patent Classification<sup>7</sup>: 26/02

G02B 26/00,

(21) International Application Number:

PCT/US2003/015213

(22) International Filing Date: 14 May 2003 (14.05.2003)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

10/187,159 28 June 2002 (28.06.2002) US

(71) Applicant: SILICON LIGHT MACHINES [US/US]; Suite 115, 385 Moffett Park Drive, Sunnyvale, CA 94089 (US).

(72) Inventors: HUNTER, James, A.; 253 Victor Avenue, Campbell, CA 95002 (US). STAKER, Bryan; 2108 Raven Road, Pleasanton, CA 94566 (US).

(74) Agents: HAVERSTOCK, Thomas, B. et al.; Haverstock & Owens LLP, 162 North Wolfe Road, Sunnyvale, CA 94086 (US).

(81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VC, VN, YU, ZA, ZM, ZW.

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PT, RO, SE, SI, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

with international search report

[Continued on next page]

#### (54) Title: REDUCED FORMATION OF ASPERITIES IN CONTACT MICRO-STRUCTURES

(57) Abstract: The device comprising movable micro-structures (802) configured to contact a substrate (801) is disclosed. The substrate (801) has a metal-insulator-metal construction with a upper metal layer and an insulator being patterned to provide substrate (801) contact regions to a lower metal layer. The micro-structures (802) have metal under layers for providing ribbon contact regions (809). In use, a bias voltage is applied across the micro-structures (802) and the top metal layer (825) causing the micro-structures and the substrate to contact through the contact regions. During contact, the contact regions are maintained at a potential that is substantially less than the applied bias voltage, thereby reducing the formation of asperities structures in an optical MEM device configured to modulate light.

####

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

#### Field of the Invention:

5

10

15

20

25

30

35

40

The present invention is related to micro-structures which are configured to move. More particularly, the present invention is related to micro-structures which are configured to move and contact.

### Background of the Invention:

A number of micro-machines utilize movable cantilevers, ribbon structures or other similar micro-structures. Typically, these micro-structures are extremely thin; on the order of hundreds or thousands of Angstroms, and are formed through release etch processes.

Optical MEM (micro-electro-mechanical) devices are used to modulate one or more wavelengths of light. Optical MEM devices can have applications in display, print and electrical device technologies. Examples of an optical MEM device which utilize suspended micro-ribbon structures to modulate light are disclosed in the U.S. Patent Nos. 5,311,360, 5,841,579 and 5,808,797, all issued to Bloom et al., the contents of which are hereby incorporated by reference.

Briefly, an optical MEM device described in the above referenced patents has one or more sets of movable ribbons that comprise a support layer and a reflective top-layer. The support layer is preferably a silicon nitride layer and the reflective top-layer is preferably an aluminum layer. The ribbon structures are typically secured to a substrate through opposite ends of the ribbon, whereby center portions of the ribbons, referred to herein as the active portions, move up and down to modulate an incident light source.

The ribbons are configured to move by applying a bias voltage across the ribbons and the substrate. In order to effectively modulate light, the distance that the ribbons are moved must be controllable and reproducible. In one construction, an optical MEM device has ribbons that are suspended at a fixed distance from the substrate and the ribbons are selectively moved to contact the substrate. Unfortunately, this results in weld spots or surface artifacts generally referred to herein as asperities. Asperities which develop over time can greatly effect the ability of the ribbons to move in a controllable and/or reproducible manner and can cause the ribbons to stick to the substrate. There are many MEM devices, including cantilever devices and oscillator devices, where movable structures which contact the substrate, or other micro-structure, is advantageous if the formation asperities and sticking of the contacting parts can be avoided or reduced.

### Summary of the Invention:

A device, in accordance with the embodiments of the invention, comprises one or more micro-structures suspended over a substrate. The micro-structures can be, but are not limited to, cantilevers, ribbons and combs structures configured to move relative to the substrate and contact a portion of the substrate. Preferably, the micro-structures are ribbons

a range of about 300 to about 3000 nanometers.

5

10

15

20

25

30

35

In accordance with the embodiments of the invention, the substrate has a metal-insulator-metal construction comprising a lower metal layer and an upper metal layer with an insulator layer sandwiched therebetween. Preferably, the upper metal layer and the insulator layer are patterned with vias to expose portions of the lower metal layer and to provide contact regions for complimentary contact regions on the ribbons. In a preferred embodiment, the substrate has a metal-insulator-metal construction comprising titanium nitride metal layers and a silicon oxide insulator layer.

The ribbons have at least one metal under layer. The metal under layer comprises contact regions and non-contact regions. In accordance the with embodiments of the invention, the ribbons also have a metal-insulator-metal construction. For example, the ribbons have an under layer of titanium nitride, a top layer of aluminum and a silicon nitride insulator layer sandwiched therebetween.

In operation, a bias voltage is applied across selected micro-structures, or ribbons, and the upper metal layer of the metal-insulator-metal construction on the substrate. The lower metal layer is maintained at a reduced potential relative to the applied bias voltage and is preferably maintained at a zero, or near to zero, potential relative to the applied bias voltage. The bias voltage between the selected micro-structures and the upper metal layer of the metal-insulator-metal construction on the substrate urges the selected micro-structures to move towards the substrate and to contact the substrate. The micro-structures and substrate make contact through the contact regions in the lower metal layer of the metal-insulator-metal construction of the substrate and contact regions on the under layer of the micro-structures.

Contact regions of the micro-structures preferably protrude, such that the contact regions of the micro-structures insert, or fit, into the vias patterned through the upper metal layer and the insulator layer of the metal-insulator-metal construction of the substrate. Because the potential difference between the contact regions of the micro-structures and the contact regions of the substrate are minimized, or reduce, the formation of asperities and sticking of contacting parts is also minimized or reduced.

In accordance with the method of the invention, a micro-device is made by forming a substrate structure comprising a metal-insulator-metal construction. In accordance with the embodiments of the invention, a lower metal layer of titanium nitride is deposited to a thickness in range of about 200 to about 2000 Angstroms. Over the lower metal layer, a insulator layer of silicon oxide and an upper metal layer of titanium nitride are deposited to a thickness in a range of about 200 to about 2000 Angstrom. The insulator layer and the upper metal layer of the metal-insulator-metal construction are patterned with contact vias. The metal-insulator-metal construction can be patterned with the contact vias using selective deposition processes, etch process or a combination thereof.

for coupling a device layer to the substrate. The device layer is then formed over the patterned poly-silicon layer and is cut into ribbons with the appropriate dimension using any suitable process, such as a reactive ion etch process. After the device layer is cut into ribbons, the underlying poly-silicon is etched using any suitable processes, such as a xenon diflouride etch process to release the ribbons.

## Brief Description of the Drawings:

5

10

15

20

25

30

35

40

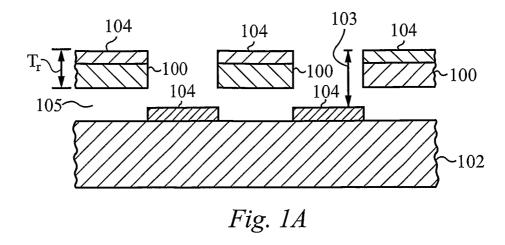

Figures 1a-b are cross-sectional representations of a micro-structure having a plurality of moveable ribbon structures, in accordance with the invention.

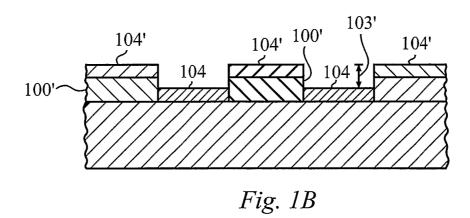

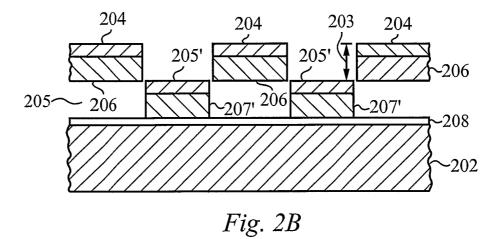

Figures 2a-b are cross-sectional representations of a micro-structure having two sets of ribbon structures, in accordance with the invention.

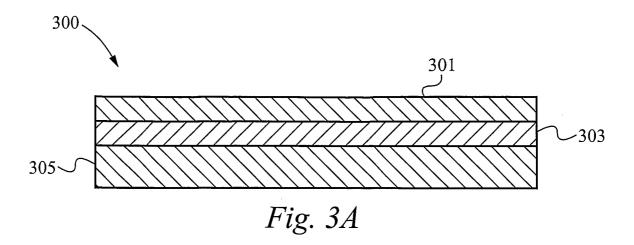

Figure 3a is a cross-sectional representation of a ribbon structure, in accordance with the invention.

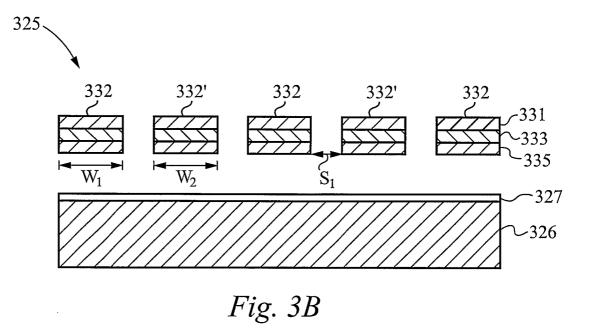

Figure 3b is cross-sectional representation of a micro-structure having a plurality of ribbon structures, such as the one shown in Figure 3a.

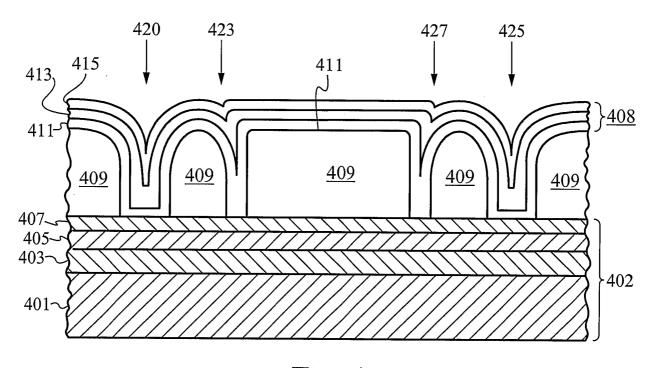

Figure 4 shows a cross-sectional view of a micro-device with support regions for supporting a ribbon structure near both ends of the ribbon structure, in accordance with the invention.

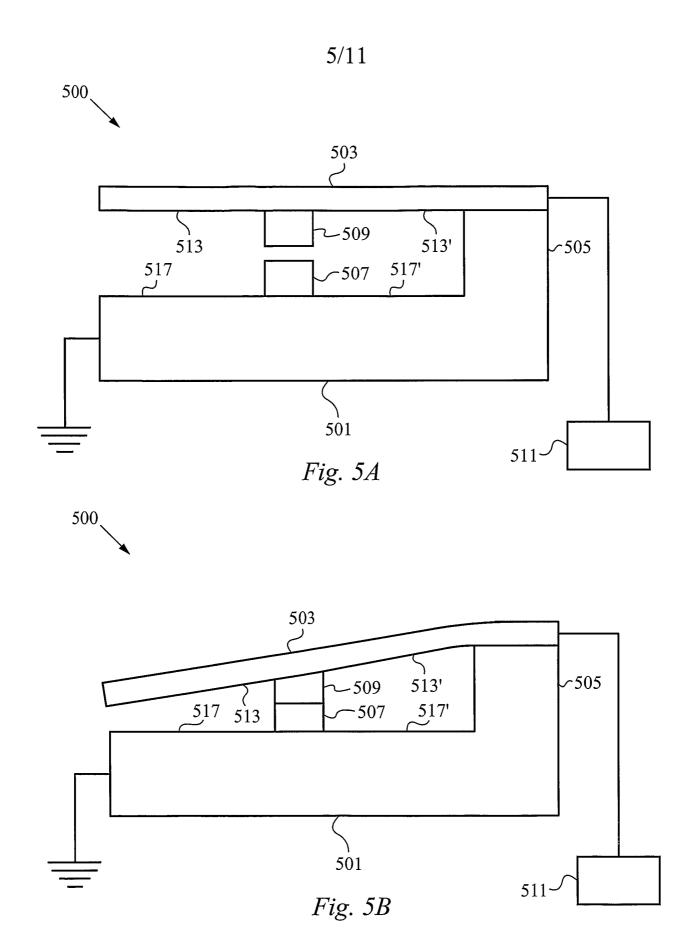

Figures 5a-b show a cantilever micro-structure configured to contact a substrate, in accordance with the invention.

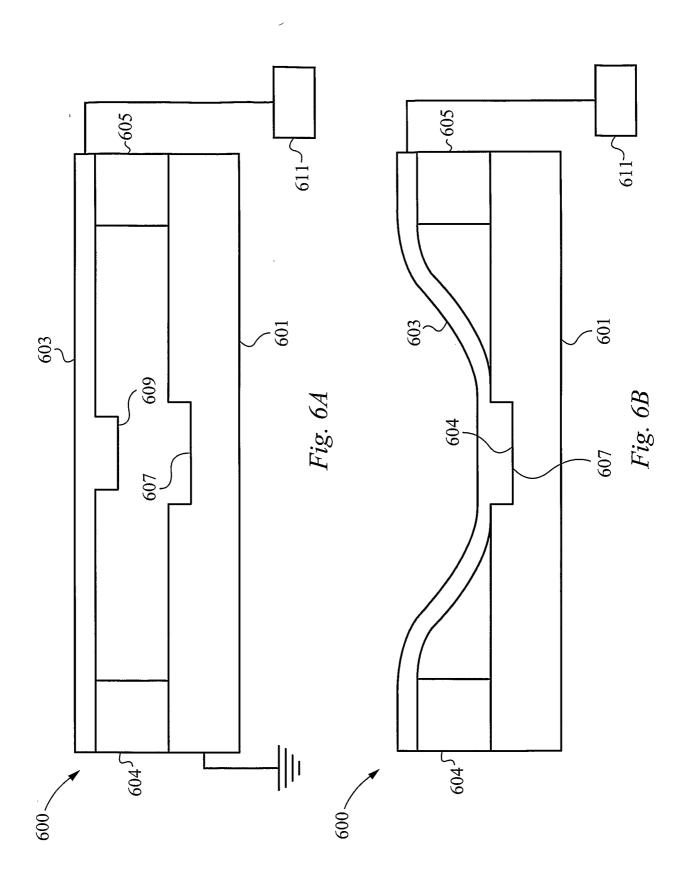

Figures 6a-b show a ribbon structure configured to contact a substrate, in accordance with the method of the invention.

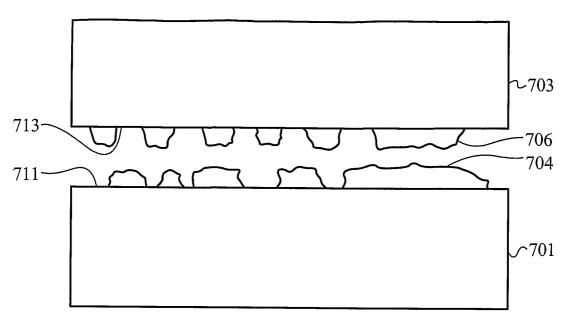

Figures 7a-b show the formation asperities on contact surfaces.

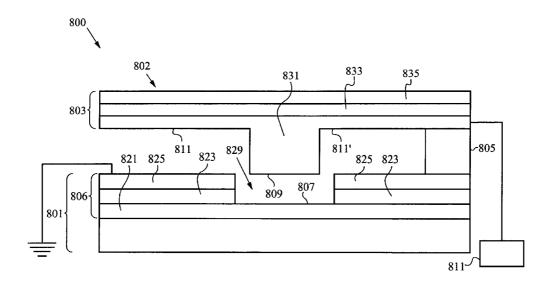

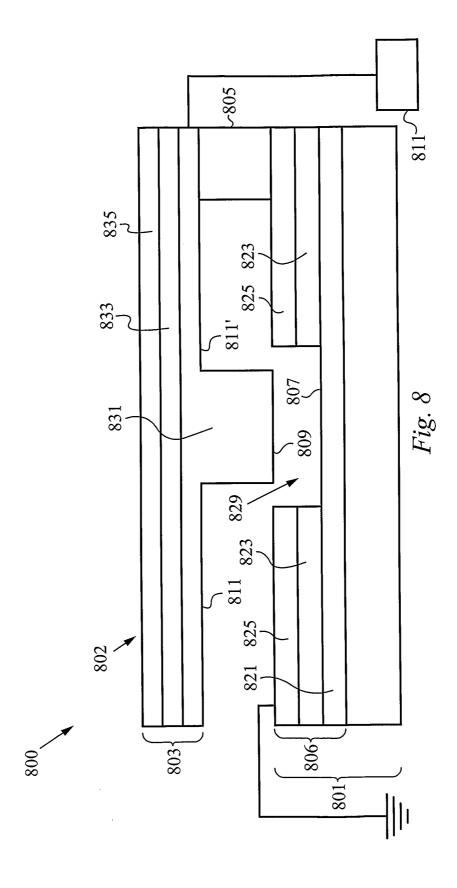

Figure 8 shows a micro-device with a metal-insulator-metal construction, in accordance with the invention.

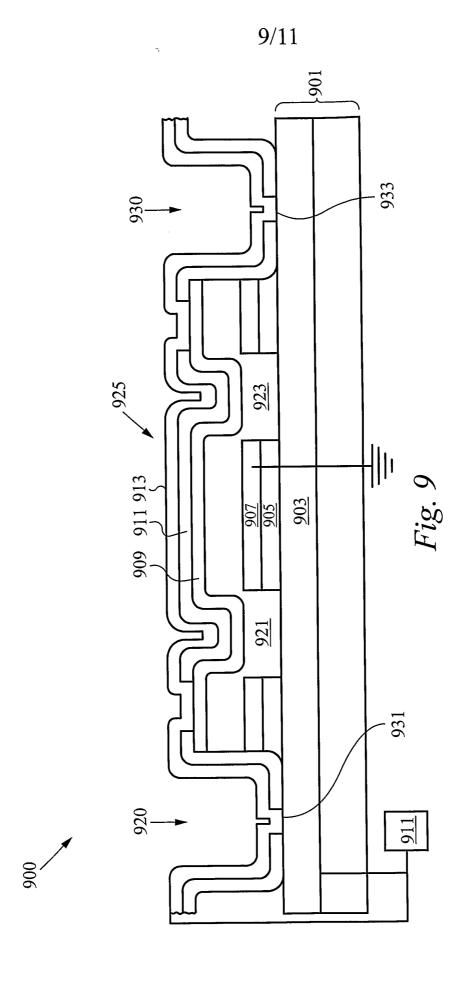

Figure 9 shows a ribbon micro-structure with a metal-insulator-metal construction, in accordance with the invention

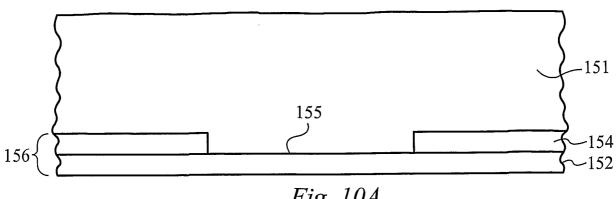

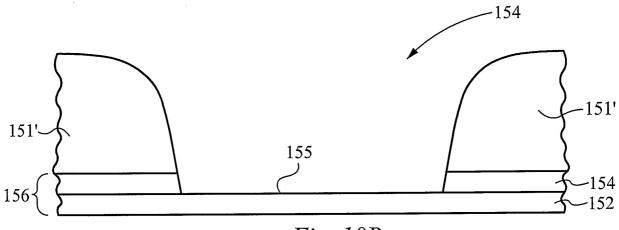

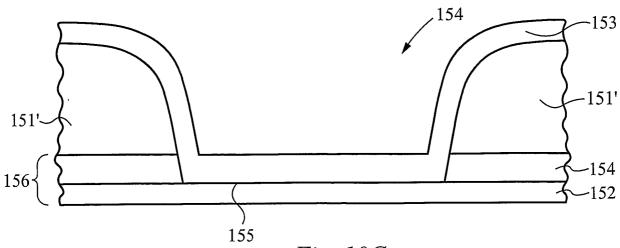

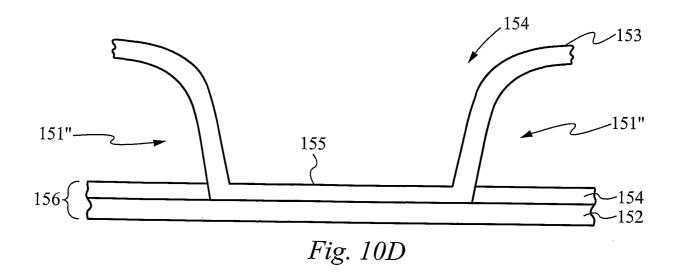

Figures 10a-e show forming support features, in accordance with the method of the invention.

## Detailed Description of the Embodiments

Referring to Figure 1a, an optical MEM device can have a plurality of movable ribbons 100 that are spatially arranged over a substrate 102. The surfaces 104, corresponding to the ribbon tops and the regions of the substrate between the ribbons, are reflective. The surfaces 104 are made to be reflective by depositing a thin film of reflective material, such as silver or aluminum on the substrate 102 and the ribbons 100. The ribbons and the substrate structure are fabricated from silicon-based materials. The height difference 103 between the reflective surfaces 104 of the substrate 102 and the reflective surfaces 104 of the ribbons 100

comprising ribbon and substrate surfaces 104, light that is reflected from the surfaces 104 of the substrate 102 and ribbons 100 will be in phase. Light which strikes the reflective surfaces 104 of the substrate 102 travels  $\lambda/2$  further than the light striking the reflective surfaces 104 of the ribbons 100. Then the portion of light that is reflected back from the reflective surfaces 104 of the substrate 102 returns traveling an addition  $\lambda/2$  for a total of one complete wavelength  $\lambda$ . Therefore, the compliment of the reflective surfaces 104 function as a mirror to the incident light source with a wavelength  $\lambda$ .

5

10

15

20

25

30

35

By applying an appropriate bias voltage across the ribbons 100 and the substrate 102, a portion of the ribbons 100 move towards and contact the substrate 102, as shown in Figure 1b. The thickness  $T_r$  of the ribbons 100 is designed to be  $\lambda/4$  such that the distance 103' is also  $\lambda/4$ . When light having a wavelength  $\lambda$  impinges on surfaces 104 and 104' with the ribbons 100 in the down position, as shown in Figure 1b, the portion of light reflected from the surfaces 104' of the ribbons 100 will be out of phase with the portion of light reflected from the surfaces 104 of the substrate 102, thereby generating the conditions for destructive interference. By alternating the ribbons between the positions for constructive interference, as shown in Figure 1a, and the positions for destructive interference, as shown in Figure 1b, the grating light valve is capable of modulating the intensity of reflected light from an impinging light source having a wavelength  $\lambda$ .

Figures 2a-b illustrate cross sectional views of an alternative optical MEM device construction. In accordance with this construction, the optical MEM device has at least two sets of alternating ribbons 206 and 207 that are approximately in the same reflective plane. Referring to Figure 2a, the ribbons 206 and 207 are suspended over a substrate structure 202 by a distance 203. The ribbons 206 and 207 are provided with reflective surfaces 204 and 205, respectively. Preferably, the surface of the substrate 202, or a portion thereof, also has a reflective surface 208. The reflective surfaces of the substrate 208 and the reflective surfaces of the ribbons 204 and 205 are preferably configured to be separated by a distance approximately equal to a multiple of  $\lambda/2$  of the impinging light source. Thus, the portion of light that is reflected from the compliment of surfaces 204, 205 and 208 are all in phase, constructively interfere and the maximum intensity is observed. In operation, the flat diffraction grating light valve alternates between the conditions for constructive and destructive interference by moving the first set of ribbons 206 or the second set of ribbons 207 relative to each other by a distance corresponding to  $\lambda/4$ .

In one mode of operation, light is modulated by moving one set of alternating ribbons relative to a stationary set of alternating ribbons. The ribbons that are moved are referred to as the active ribbons and the stationary ribbons are referred to as the bias ribbons. The active

generate Coulombic attractions and/or repulsions between the active ribbons and the substrate.

5

10

15

20

25

30

35

40

Now referring to Figure 2b, when a sufficient bias voltage is applied across the active ribbons 207 and the substrate 202, the ribbons 207 are displaced relative to the bias ribbons 206 by a distance 203 that is approximately equal to a multiple of  $\lambda/4$ . Accordingly, the portions of light that are reflected from the surfaces 205' of the active ribbons 207 will destructively interfere with the portion of light that is reflected of the surfaces 204 of the bias ribbons 206. It will be clear to one skilled in the art that a grating light valve may be configured to modulate an incident light source with a wavelength  $\lambda$  in other operative modes. For example, both sets of ribbons 206 and 207 may be configured to move and separate by multiples of  $\lambda/4$  in order to alternate between the conditions for constrictive and destructive interference.

The ribbons of the MEM devices, described in Figures 1a-b and Figures 2a-b are preferably hermetically sealed within a die structure. Methods and materials used for providing a hermetically sealed die are described in the U.S. Patent Application No. 09/124710, filed July 29, 2001, entitled "METHOD OF AND APPARATUS FOR SEALING AN HERMETIC LID TO A SEMI CONDUCTOR DIE", now U.S. Patent No. 6,303,986, the contents of which are hereby incorporated by reference.

Figure 3a shows a cross-sectional view of a portion of a micro-structure 300 formed in accordance with the embodiments. The micro-structure 300 has a silicon based under-layer or support layer 305 that is preferably silicon nitride with a thickness in a range of about 800 to about 1200 Angstroms. The micro-structure 300 also has a reflective top-layer 301 that is preferably formed from a metal and has thickness in a range of about 700 to about 1200 Angstroms. The reflective top-layer 301 can be formed from any number of metals and metal alloys, but is preferably formed from aluminum or other metal that can be deposited using sputtering techniques at relatively low temperatures. The reflective top-layer 301 is preferably deposited to a thickness in a range of about 500 to about 1500 Angstroms.

Still referring to Figure 3a, the micro-structure 300 can also have an oxide layer 303 that is preferably silicon dioxide with a thickness in a range of about 800 to about 1800 Angstroms. The silicon dioxide layer 303 is preferably interposed between reflective top-layer 301 and the under-layer 305. Alternatively, or in addition to the silicon dioxide layer 303, a silicon dioxide layer can be formed below the under-layer 305.

Figure 3b shows a portion of a micro-device 325, in accordance with the embodiments. The micro-device 325 preferably has a plurality of ribbon structures 332 and 332' geometrically suspended over a substrate 326. Each of the ribbon structures 332 and 332' preferably has a multi-layer structure comprising an under-layer 335, a top-layer 331 and an compensating layer 333, such as those described above. The plurality of ribbons 332 and 332' can comprise an alternating first set of ribbons 332 and second set of ribbons 332' which

are moved relative to each other, such as explained above. In accordance with the embodiments, the ribbons 332 and 332' move in opposite direction. In alternative embodiments, one set of the ribbons 332 or 332' moves while the other set of ribbons remains stationary. In yet other embodiments, the micro-device 325 is configured to operate in two or more modes of operation, whereby the micro-device is configured to move one set of ribbons 322 and 322' in one of the modes of operation and both sets of the ribbons 322 and 322' in another of the modes of operation.

5

10

15

20

25

30

35

The substrate 326 can have a layer 327 of reflective material or any other suitable material to assist in the functionality of the micro-device 325. Also, while the ribbon structures 332 and 332', shown in Figure 3b, all have uniform widths W<sub>1</sub> and W<sub>2</sub> and spacings S<sub>1</sub>, any number of ribbons constructions and arrangements with varied widths W<sub>1</sub> and W<sub>2</sub> and varied spacings S<sub>1</sub> are contemplated. For example, ribbon structure arrangements having varying widths W<sub>1</sub> and W<sub>2</sub> and optimized spacings S<sub>1</sub> are described in U.S. Patent Application No. 09/802,619, filed March 08, 2001, entitled "HIGH CONTRAST GRATING LIGHT VALVE", the contents of which is hereby incorporated by reference. Also, while the preferred micro-structure(s) comprise a silicon nitride under-layer, reflective metal top-layer and oxide layer(s), such as silicon dioxide, it is understood that the composition the nitride under-layer, a reflective metal top-layer and a silicon dioxide layer(s) can be varied without departing from the spirit and scope of the embodiments. For example, the reflective metal top-layer may be formed from an alloy and the silicon nitride and silicon dioxide layers can contain impurities and/or dopants such a boron, phosphorus and the like.

Figure 4 illustrates a cross-sectional representation of a micro-device comprising a multi-layer ribbon structure 408, in accordance with a preferred construction. The micro-device comprises a substrate 402, which can comprises a wafer layer 401, and silicon oxide layers 403 and 407, with a poly-silicon layer 405 therebetween. The thicknesses of the layers 401, 403, 405, and 407 are varied depending of the application at hand. However, it is preferable that the oxide layer 407 is present to couple to a ribbon structure 408, as previously described. The ribbon structure 408 preferably comprises a layer of silicon nitride 411, and a layer reflective top layer 415 of aluminum, as previously described. In some applications, a layer of silicon oxide 413, with a layer thickness in a range of about 500 to about 2000 Angstrom, can be provided to reduce strain between the silicon nitride layer 411 and the reflective top layer 415.

Still referring to Figure 4, the ribbon structure 408 is preferably suspended over the substrate structure 402, such that there is one or more gaps 409 between the ribbon structure 408 and the substrate structure 402. Preferably, the ribbon structure 408 is supported to or

couples to the substrate structure 402 through anchor support features 420 and 425 and post support features 423 and 427, as previously described, wherein an anchor support features and a plurality of post support features support each end of the ribbon structure 408.

5

10

15

20

25

30

35

Referring now to Figure 5a, a device 500 in accordance with the embodiments of the invention comprises a movable micro-structure 503. The micro-structure 503, may be a ribbon, a cantilever, a comb or other movable micro-structure that is suspended over a substrate 501 and coupled to the substrate 501 through one or more support features 505. The substrate 501 comprises a metal-insulator-metal construction, such as described below. The micro-structure 503 has a contact region 509 and one or more non-contact regions 513 and 513'. The substrate also has a contact region 507 and one or more non-contact regions 517 and 517'. In operation, a bias voltage is applied across the micro-structure 503 and the substrate 501 using a driver circuit 511 in electrical communication with the micro-structure 503.

Referring to Figure 5b, when a sufficient bias voltage (a switching voltage) is applied across the micro-structure 503 and the substrate 501, the micro-structure 503 is deflected towards the substrate 501 and contacts the substrate 501 through the contact regions 509 and 507.

Referring now to Figure 6a, a device 600 in accordance with the embodiments of the invention comprises a ribbon structure 603 and a substrate 601 comprises a metal-insulator-metal construction, as described below.

The ribbon structure 603 is preferably suspended over the substrate 601 and is coupled to the substrate 601 through support features 604 and 605 at or near the ends of the ribbon structure 603. The ribbon structure 603 is preferably a multi-layer structure comprising a layer of silicon nitride, a reflective top layer of aluminum and a conductive under layer of titanium nitride, as described below.

The ribbon structure 603 and the substrate 601 have contact regions 609 and 607, respectively. In operation, a sufficient bias voltage is applied across the ribbon structure 603 using a driver circuit 611 in electrical communication with the ribbon structure 603, such that the active portion of the ribbon structure 603 is deflected toward the substrate 601 and makes contact with the substrate 601 through the contact regions 609 and 607, as shown in Figure 6b.

In accordance with the embodiments of the invention, a device comprises an array of ribbon structures, wherein a first set of the ribbons are configured to move relative to a second set of ribbons to modulate a light source with one or more wavelengths in a range of about 300 to about 3000 nanometers, as explained above.

Figures 7a-b illustrate a pair of contact regions 701 and 703, that represent contact regions of a micro-structures and a substrate, as described above. In conventional

approaches, the surfaces 711 and 713 of the contact regions 701 and 703 are at different potentials during the operation of the device. Because the surfaces 711 and 713 of the contact regions 701 and 703 operate at different potentials, there is a propensity for small welding spots or asperities 704 and 706 to form on the surfaces 711 and 713. As the asperities 704 and 706 are formed on the surfaces 711 and 713, the surfaces 711 and 713 have a propensity to stick together and/or can not be contacted in a controlled and/or reproducible manner

5

10

15

20

25

30

35

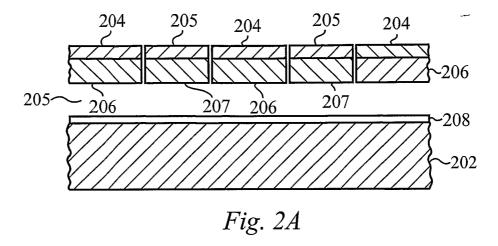

Now referring to Figure 8, in order to solve aforementioned problems with contact MEM devices, a device 800 in accordance with the embodiments of the invention, has one or more micro-structures 802 suspended over a substrate 801. The substrate 801 includes a metal-insulator-metal construction 806 comprising a lower metal layer 821 and an upper metal layer 825 with the insulator layer 823 sandwiched therebetween. In a preferred embodiment, the substrate 801 has a metal-insulator-metal construction 806 comprising titanium nitride metal layers 821 and 825 and a silicon oxide insulator layer 823.

Still referring to Figure 8, the upper metal layer 825 and the insulator layer 823 are preferably patterned with a contact via 829 to expose a portion of the lower metal layer 821 and provide a region 807 for contacting a complimentary region 809 on the under side of the micro-structure 802. The contact region 809 of the micro-structure 802 preferably protrudes, as shown, such that the contact region 809 inserts into the via 829 patterned through the upper metal layer 825 and the insulator layer 823.

The micro structure 802 has at least one metal layer 831 on the under side of the micro-structure 802. The metal under layer 831 forms the contact region 809 and non-contact regions 811 and 811'. In accordance with the embodiments of the invention, the micro-structure 802 has a metal-insulator-metal construction 803. Preferably, the metal-insulator-metal construction 803 comprises an under layer 831 of titanium nitride and top layer 835 of aluminum and a silicon nitride-based layer 833 sandwiched therebetween.

In operation, a bias voltage is applied across the micro-structure 802, or micro-structures, and the upper metal layer 825 of the substrate 801 with a driver circuit 811 coupled to the micro-structure 802 and the lower metal layer 821. The Culombice attraction between the micro-structure 802 and the upper metal layer 825 causes the micro-structure 802 to move towards the substrate 801 and contact the substrate 801 through the contact regions 807 and 809, such as shown in Figure 5b and Figure 6b. Because the potential difference between the contact regions 807 and 809 is minimized, or reduced, the formation of asperities and/or sticking is also minimized, or reduce.

Figure 9 shows a cross-sectional view of an optical MEM device 900 comprising a ribbon 925, configured to modulate light in accordance with the embodiments of the

invention. Preferably, the device 900 comprises a plurality of ribbons (not shown) with a first set of the ribbon configured to move relative to a second set of ribbons for modulating light, as described above.

Still referring to Figure 9, the substrate 901 comprises a metal-insulator-metal construction. The metal insulator-metal construction preferably comprises a lower metal layer 903 and an upper metal layer 907 formed from titanium nitride with an insulator layer 905 of silicon oxide sandwiched therebetween. The preferred thicknesses of the layers 903, 905 and 907 depends on the intended application, but are preferably in a range of about 500 to about 4000 Angstroms thick.

5

10

15

20

25

30

35

Still referring to Figure 9, the upper metal layer 907 and the insulator layer 905 are fashioned with vias 921 and 923 such that contact regions on the surface of the lower metal layer 903 are exposed. The vias 921 and 923 provide gaps between the contact surfaces of the ribbon 925 and the substrate 901, through which the ribbon 925 and the lower metal layer 903 make contact during operation. The vias 921 and 923 are formed by selectively depositing the insulator layer 905 and the top metal layer 907, by using suitable etching processes and/or a combination thereof.

Still referring to Figure 9, the ribbon 925 also comprises a metal-insulator-metal construction. The ribbon 925, for example, comprises a metal under layer 909, that is preferably formed from titanium nitride. The ribbon also comprises a metal top layer 913, that is preferably formed from aluminum. Sandwiched between the metal under layer 909 and the metal top layer 913, is an insulator layer 911 that is preferably formed from silicon nitride, silicon-oxide or a combination thereof. The preferred thicknesses of the ribbon layers 909, 911 and 913 depend on the intended application, but are preferably in a range of about 2000 to about 2000 Angstroms thick.

In operation, a bias voltage is applied to the metal layers 909 and 913 of the ribbon 925 and the lower metal layer 903 of the substrate 901 with a driver circuit 911 urging the ribbon 925 to deflect toward the substrate 901 and contact the substrate 901 through the vias 921 and 923, while an adjacent ribbon (not shown) remains substantially stationary. The contact regions of the ribbon 925 preferably protrude to fit into the vias 921 and 923, as shown. The ribbon 925 is preferably coupled to the substrate through support features 920 and 930 attached to the substrate 901 through coupling regions 931 and 933.

Figures 10a-e will be used to illustrate the formation a micro-structure on a substrate 156 comprising a wafer layer 152 and a patterned metal-insulator-metal layer 155, as described above. The wafer layer 152 can comprise silicon dioxide, silicon nitride and polysilicon, doped, un-doped silicon or any combination thereof. The patterned metal-insulator-metal layer 155 is preferably patterned with contact vias 912 and 923 and a plurality of coupling regions 931 and 933, shown in Figure 9. Figures 10a-e are used to illustrate the

formation of a single support structure. However, it is understood that the method described can be used to form any number of support structures. In fact, ribbon structures are preferably supported through several support structures positioned near or at the ends of the ribbon structures.

5

Referring now to Figures 10a-c, a layer 151 of sacrificial material, such as polysilicon, is deposited over the patterned metal-insulator-metal layer 154 and the coupling region 155. The sacrificial layer 151 is etched to form a patterned sacrificial layer 151' having a support trench 154 and exposing the support region 155 on the wafer layer 152. After the support trench 154 is formed, the device layer 153 is formed over the patterned sacrificial layer 151' such that a portion of the device layer 153 couples to the wafer layer 152 through the support region 155. The device layer 153 preferably comprises a layer of titanium nitride, silicon nitride and aluminum, as described above, and can also comprises one or more layers of silicon oxide.

15

10

Now referring to Figure 10d, after the device layer 153 is formed, then the patterned sacrificial layer 151' is etched away to form voids 151" and release portions of the device layer 153, while portions of the device layer 153 remains coupled to the wafer layer 152 through the support region 155. Preferably, the sacrificial layer 151' is etched using a dry etch process, such as described in the U.S. Patent Application 09/952,626, entitled MICRO-ELECTRONIC MECHANICAL SYSTEM AND METHODS, filed September 13, 2001, the contents of which are hereby incorporated by reference.

20

In a preferred method of the invention, the device layer 153 is cut or divided into ribbon structures prior to etching the sacrificial layer 151', whereby each ribbon structure remains coupled to the substrate layer 152 through a plurality of support features 161, such as the one shown in Figure 10e.

25

The present invention provides for a MEM device and/or an optical MEM device which operates in a contact manner, but which has reduced formation asperities formation on and/or sticking of contacting parts. The present invention has been described in terms of specific embodiments incorporating details to facilitate the understanding of the principles, construction and operation of the invention. While the MEM device is an optical MEM device, other MEM devices, including cantilever devices and oscillator devices are contemplated. As such, references, herein, to specific embodiments and details thereof are not intended to limit the scope of the claims appended hereto. It will be apparent to those skilled in the art that modifications can be made in the embodiment chosen for illustration without departing from the spirit and scope of the invention.

35

30

## **CLAIMS**

2

What is Claimed is:

| 1<br>2<br>3<br>4<br>5<br>6 | 1.  | A device comprising a micro-structure suspended over a substrate, the micro-structure and the substrate comprising contact regions and non-contact regions, the micro-structure being configured to move relative to the substrate by applying a bias voltage between the non-contact regions of the substrate and micro-structure while maintaining a constant voltage between the contact regions of the substrate and the micro-structure. |

|----------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2                     | 2.  | The device of claim 1, wherein the substrate comprises an insulator layer sandwiched between metal layers.                                                                                                                                                                                                                                                                                                                                    |

| 1                          | 3.  | The device of claim 2, wherein the insulator layer comprises an oxide.                                                                                                                                                                                                                                                                                                                                                                        |

| 1<br>2                     | 4.  | The device of claim 2, wherein at least one of the metal layers comprises titanium nitride.                                                                                                                                                                                                                                                                                                                                                   |

| 1 2                        | 5.  | The device of claim 1, wherein the micro-structure comprise an insulator layer sandwiched between metal layers.                                                                                                                                                                                                                                                                                                                               |

| 1 2                        | 6.  | The device of claim 5, wherein at least one of the metal layers comprises titanium nitride.                                                                                                                                                                                                                                                                                                                                                   |

| 1                          | 7.  | The device of claim 5, wherein at least one of the metal layers comprises aluminum.                                                                                                                                                                                                                                                                                                                                                           |

| 1                          | 8.  | The device of claim 1, wherein the micro-structure is a ribbon structure.                                                                                                                                                                                                                                                                                                                                                                     |

| 1<br>2<br>3<br>4<br>5<br>6 | 9.  | <ul> <li>An optical MEM device comprising:</li> <li>a. means to modulate light, the means comprising ribbons suspended over metal-insulator-metal substrate; and</li> <li>b. means to move a first set of the ribbons relative to a second set of the ribbons, wherein one of the first and second set of ribbons and the substrate contact through contact regions that have substantially the same potential.</li> </ul>                    |

| 1                          | 10. | The optical MEM device of claim 9, wherein the ribbons comprise metal layers of                                                                                                                                                                                                                                                                                                                                                               |

titanium nitride and aluminum.

1 11. The optical MEM device of claim 10, wherein the ribbons comprise a layer of siliconnitride sandwiched between the layers of titanium nitride and aluminum.

- 1 12. The optical MEM device of claim 9, wherein metal-insulator-metal substrate, comprises metal layers of titanium nitride and an insulator layer of oxide.

- 1 13. The optical MEM device of claim 9, wherein the means for moving the first set of the ribbons relative to the second set of the ribbons comprises a circuit configured to apply a bias voltage across an upper metal layer of the metal-insulator-metal substrate and the one of the first set and second set of the ribbons.

- 1 14. The optical MEM device of claim 13, wherein the regions of contact correspond to

2 portions of a metal under layer on the one of the first set and the second set of the

3 ribbons and a lower metal layer of the metal-insulator-metal substrate.

- 1 15. The optical MEM device of claim 14, wherein the regions of contact comprise titanium nitride.

- 1 16. A method of making a micro-device comprising:

2

3

4

5

6

7

1

2

3

4

5

6

- a. forming a substrate comprising an upper metal layer, a lower metal layer with contact regions and an insulator layer between the upper and the lower metal layers, wherein the upper metal layer and the insulator layer are patterned to expose substrate contact regions on a surface of the lower metal layer; and

- b. forming ribbons, with alternating ribbons comprising a metal under layer with ribbon contact regions and non-contact regions.

- 17. The method of claim 16, further comprising coupling the ribbons and the lower metal layer to a voltage source configured for applying a potential between the upper metal layer and the metal under layer that is sufficient to cause the alternating ribbons and the substrate to contact through the substrate contact regions and the ribbon contact regions, with a potential less than the applied potential between the upper metal layer and the metal under layer.

| 2 | a. depositing |                                                                                 | depositing titanium nitride on a silicon wafer to form the lower metal layer;     |

|---|---------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 3 |               |                                                                                 | and                                                                               |

| 4 |               | b.                                                                              | selectively depositing silicon oxide and titanium nitride to form the insulator   |

| 5 |               |                                                                                 | layer and the upper metal layer, respectively,                                    |

| 6 |               |                                                                                 | wherein the insulator layer and the upper metal layer are patterned with the      |

| 7 |               |                                                                                 | substrate contact regions.                                                        |

| 1 | 19.           | The                                                                             | method of claim 18, wherein forming the ribbons comprises:                        |

| 2 |               | a.                                                                              | depositing a layer of poly-silicon on the substrate;                              |

| 3 |               | <b>b</b> .                                                                      | forming a device layer comprising the metal under layer;                          |

| 4 |               | c.                                                                              | cutting the device layer into the ribbons; and                                    |

| 5 |               | d.                                                                              | etching the poly-silicon to release the ribbons.                                  |

| 1 | 20.           | The                                                                             | method of claim 20, wherein the poly-silicon layer is etched prior to forming the |

| 2 |               | ce layer such that the ribbon contact regions protrude, and wherein the ribbons |                                                                                   |

| 3 |               | attac                                                                           | h to the substrate.                                                               |

The method of claim 16, wherein forming a substrate comprises:

1

18.

Fig. 4

Fig. 7A

Fig. 10A

Fig. 10B

Fig. 10C

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/US03/15213

| A. CLASSIFICATION OF SUBJECT MATTER  IPC(7) : G02B 26/0; G02B 26/02  US CL : 359/291, 292, 295, 223, 224, 231, 566, 572  According to International Patent Classification (IPC) or to both national classification and IPC  B. FIELDS SEARCHED  Minimum documentation searched (classification system followed by classification symbols)  U.S.: 359/291, 292, 295, 223, 224, 231, 566, 572.  Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched |                                                                                                                                          |                                                                                                                                                                                                     |                                   |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|--|

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) USPTO DATABASE                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                          |                                                                                                                                                                                                     |                                   |  |  |  |  |  |

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                          |                                                                                                                                                                                                     |                                   |  |  |  |  |  |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Citation of document, with indication, where ap                                                                                          | ppropriate, of the relevant passages                                                                                                                                                                | Relevant to claim No.             |  |  |  |  |  |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | US 6,327,071 B1 (KIMURA) 04 December 2001 (04                                                                                            | 1.12.2001) see entire reference.                                                                                                                                                                    | 1                                 |  |  |  |  |  |

| <br>Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                          |                                                                                                                                                                                                     |                                   |  |  |  |  |  |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                          |                                                                                                                                                                                                     | 8, 2-7                            |  |  |  |  |  |

| X,P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | US 6,466,354 B1 (Gudeman) 15 October 2002 (15.1)                                                                                         | 1, 8                                                                                                                                                                                                |                                   |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                          |                                                                                                                                                                                                     |                                   |  |  |  |  |  |

| Y,P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                          |                                                                                                                                                                                                     | 9-15,16-20                        |  |  |  |  |  |

| x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | US 6,147,789 A (Gelbart) 14 November 2000 (14 November 2000) see entire reference.                                                       |                                                                                                                                                                                                     |                                   |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                          |                                                                                                                                                                                                     |                                   |  |  |  |  |  |

| Further                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | documents are listed in the continuation of Box C.                                                                                       | See patent family annex.                                                                                                                                                                            |                                   |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | pecial categories of cited documents:                                                                                                    | "T" later document published after the inte                                                                                                                                                         | rnational filing date or priority |  |  |  |  |  |

| "A" document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | defining the general state of the art which is not considered to be                                                                      | date and not in conflict with the applic<br>principle or theory underlying the inve                                                                                                                 | ation but cited to understand the |  |  |  |  |  |

| "E" earlier ap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | plication or patent published on or after the international filing date                                                                  | "X" document of particular relevance; the considered novel or cannot be consider when the document is taken alone                                                                                   |                                   |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | which may throw doubts on priority claim(s) or which is cited to<br>the publication date of another citation or other special reason (as | "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination |                                   |  |  |  |  |  |

| "O" document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | referring to an oral disclosure, use, exhibition or other means                                                                          | being obvious to a person skilled in the                                                                                                                                                            |                                   |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | t published prior to the international filing date but later than the ate claimed                                                        | "&" document member of the same patent is                                                                                                                                                           | family                            |  |  |  |  |  |

| Date of the a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ctual completion of the international search                                                                                             | Date of mailing of the international search                                                                                                                                                         | ch report                         |  |  |  |  |  |

| 17 June 2003                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (17.06.2003)                                                                                                                             | 100                                                                                                                                                                                                 | ED 2003                           |  |  |  |  |  |

| Name and m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ailing address of the ISA/US                                                                                                             | Authorized officer                                                                                                                                                                                  | E17 2000                          |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nmissioner of Patents and Trademarks PCT                                                                                                 | Hung Dang (Assistant Examiner: Tuyen                                                                                                                                                                | fratte /                          |  |  |  |  |  |

| Was                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | shington, D.C. 20231                                                                                                                     |                                                                                                                                                                                                     | AS I                              |  |  |  |  |  |

| Facsimile No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | o. (703)305-3230                                                                                                                         | Telephone No. 703-308-0550                                                                                                                                                                          |                                   |  |  |  |  |  |

Form PCT/ISA/210 (second sheet) (July 1998)