(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5987004号

(P5987004)

(45) 発行日 平成28年9月6日(2016.9.6)

(24) 登録日 平成28年8月12日(2016.8.12)

|                      |                |

|----------------------|----------------|

| (51) Int.Cl.         | F 1            |

| HO2M 3/07 (2006.01)  | HO2M 3/07      |

| HO4N 5/378 (2011.01) | HO4N 5/335 780 |

| HO4N 5/357 (2011.01) | HO4N 5/335 570 |

請求項の数 20 (全 14 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2013-548572 (P2013-548572)  |

| (86) (22) 出願日 | 平成24年1月6日(2012.1.6)           |

| (65) 公表番号     | 特表2014-504844 (P2014-504844A) |

| (43) 公表日      | 平成26年2月24日(2014.2.24)         |

| (86) 国際出願番号   | PCT/US2012/020468             |

| (87) 国際公開番号   | W02012/094585                 |

| (87) 国際公開日    | 平成24年7月12日(2012.7.12)         |

| 審査請求日         | 平成26年12月24日(2014.12.24)       |

| (31) 優先権主張番号  | 12/986,038                    |

| (32) 優先日      | 平成23年1月6日(2011.1.6)           |

| (33) 優先権主張国   | 米国(US)                        |

|               |                                                                                                                       |

|---------------|-----------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者     | 390020248<br>日本テキサス・インスツルメンツ株式会社<br>東京都新宿区西新宿六丁目24番1号                                                                 |

| (73) 特許権者     | 507107291<br>テキサス インスツルメンツ インコーポ<br>レイテッド<br>アメリカ合衆国 テキサス州 75265<br>-5474 ダラス メイル ステイショ<br>ン 3999 ピーオーボックス 655<br>474 |

| (74) 上記1名の代理人 | 100098497<br>弁理士 片寄 恒三                                                                                                |

最終頁に続く

(54) 【発明の名称】チャージポンプにより導入されるアナログフロントエンドノイズを抑制するための装置及びシステム

## (57) 【特許請求の範囲】

## 【請求項1】

チャージポンプと、

光信号をサンプルするサンプラーであって、ブラックサンプラーとビデオサンプラーと

アナログデジタルコンバータ(ADC)とを含む、前記サンプラーと、a) 前記チャージポンプに結合されるチャージポンプロジェクトと、b) 前記光信号をサン

プルする前記サンプラーに結合されるサンプラーロジックとに結合され、それらにクロ

ック信号を提供する、單一クロックと、

を含む装置であって、

前記單一クロックが少なくとも5つのクロック信号の生成を生じさせ、

10

前記少なくとも5つのクロック信号が、前記チャージポンプロジェクトから前記チャージ

ポンプの第1のゲートへの第1のクロック信号と、前記チャージポンプロジェクトから前記

チャージポンプの第2のゲートへの第2のクロック信号と、前記サンプラーロジックから

前記ブラックサンプラーへのブラックサンプルクロック信号と、前記サンプラーロジック

から前記ビデオサンプラーへのビデオサンプルクロック信号と、前記サンプラーロジック

から前記ADCへのADCクロック信号とであり、i) 前記第1のクロック信号が前記第2のクロック信号が立ち上がる前に3クロックサ

イクル立ち上がり、

i i) 前記第2のクロック信号が17クロックサイクルの間に高であり、

i i i) 前記第2のクロック信号が前記第1のクロック信号が立ち下がる前に5クロック

20

クサイクル立ち下がり、

i v ) 前記第1のクロック信号が17クロックサイクルの間に低であり、その後立ち上がる、装置。

【請求項2】

請求項1に記載の装置であって、

前記單一クロックと前記チャージポンプロジックと前記チャージポンプと前記サンプラーとロジックと前記光信号をサンプルする前記サンプラーとが、單一チップ内で統合され、共通電気的接地を共有する、装置。

【請求項3】

請求項1に記載の装置であって、

前記チャージポンプが電圧ダブル(doubler)である、装置。

10

【請求項4】

請求項1に記載の装置であって、

前記光信号をサンプルする前記サンプラーが相關ダブルサンプリングを用い、前記相關ダブルサンプリングが前記ビデオサンプラーと前記ブラックサンプラーとを用いることを含む、装置。

【請求項5】

請求項1に記載の装置であって、

a) 前記ADCクロック信号の立ち上がりエッジが、前記ブラックサンプルクロック信号の立ち下がりエッジ後に複数のクロックサイクル生じ、

20

b) 前記ADCクロック信号の立ち下がりエッジが、前記ビデオサンプルクロック信号の立ち下がりエッジ後に複数のクロックサイクル生じる、装置。

【請求項6】

請求項5に記載の装置であって、

c) 前記第1のクロック信号の立ち上がりエッジが、前記ビデオクロック信号の立ち上がりエッジと整合され、

d) 前記第2のクロック信号の立ち下がりエッジが、前記ビデオクロック信号の立ち上がりエッジと整合される、装置。

【請求項7】

システムであって、

30

第1のスイッチの第1のゲートと第2のスイッチの第2のゲートと第3のスイッチの第3のゲートと第4のスイッチの第4のゲートとを有する、チャージポンプと、

光信号をサンプルするサンプラーであって、ブラックサンプラーとビデオサンプラーとアナログデジタルコンバータ(ADC)とを含む、前記サンプラーと、

a) チャージポンプロジックとb) サンプリングロジックとに結合される單一クロックであって、前記チャージポンプロジックが、第1のクロック信号ラインにより前記第1のゲートに結合され、第2のクロック信号ラインにより前記第2のゲートに結合され、第3のクロック信号ラインにより前記第3のゲートに結合され、そして、第4のクロック信号ラインにより記第4のゲートに結合され、前記サンプリングロジックが前記サンプラーに結合される、前記單一クロックと、

40

を含み、

前記第1のクロック信号ラインの第1のクロック信号の立ち上がりエッジと前記第2のクロック信号ラインの第2のクロック信号の立ち下がりエッジとが各々、前記ADCに結合されるADCラインのアナログデジタルクロック信号の立ち下がりエッジと整合される、システム。

【請求項8】

請求項7に記載のシステムであって、

前記單一クロックと前記サンプリングロジックと前記サンプラーと前記チャージポンプロジックと前記チャージポンプとが、單一チップ内で統合され、共通電気的接地を共有する、システム。

50

**【請求項 9】**

請求項 7 に記載のシステムであって、

前記チャージポンプが電圧ダグラである、システム。

**【請求項 10】**

請求項 7 に記載のシステムであって、

前記サンプラーが相關ダブルサンプリングを用い、前記相關ダブルサンプリングが前記

ブラックサンプラーと前記ビデオサンプラーとを用いる、システム。

**【請求項 11】**

請求項 7 に記載のシステムであって、

前記 A D C のアナログデジタル変換が、前記アナログデジタルクロック信号の立ち上が

リエッジによりトリガされる、システム。 10

**【請求項 12】**

請求項 7 に記載のシステムであって、

前記アナログデジタルクロック信号の前記立ち上がりエッジが、ブラックサンプルクロ

ック信号の立ち下がりエッジ後に複数のクロックサイクル生じ、

前記アナログデジタルクロック信号の前記立ち上がりエッジが、ビデオサンプルクロ

ック信号の立ち下がりエッジ後に複数のクロックサイクル生じる、システム。

**【請求項 13】**

システムであって、

第 1 のスイッチの第 1 のゲートと第 2 のスイッチの第 2 のゲートと第 3 のスイッチの第

3 のゲートと第 4 のスイッチの第 4 のゲートとを有する、チャージポンプと、 20

光信号をサンプルするためのサンプラーであって、ブラックサンプラーとビデオサンプ

ラーとアナログデジタルコンバータ ( A D C ) とを含む、前記サンプラーと、

a ) チャージポンプロジックと b ) 前記サンプラーと c ) 前記 A D C とに結合される單

一クロックであって、前記チャージポンプロジックが、第 1 のクロックラインにより前記

第 1 のゲートに結合され、第 2 のクロックラインにより前記第 2 のゲートに結合され、第

3 のクロックラインにより前記第 3 のゲートに結合され、第 4 のクロックラインにより前

記第 4 のゲートに結合される、前記單一クロックと、

を含み、

前記第 1 のクロックラインの第 1 のクロック信号の立ち下がりエッジと、前記第 2 のク

ロックラインの第 2 のクロック信号の立ち上がりエッジとの両方が、ビデオサンプルクロ

ック信号の立ち上がりエッジと整合される、システム。 30

**【請求項 14】**

請求項 13 に記載のシステムであって、

前記單一クロックと前記チャージポンプロジックと前記チャージポンプと前記光信号を

サンプルする前記サンプラーとが、單一集積チップ内で統合され、共通電気的接地を共有

する、システム。

**【請求項 15】**

請求項 13 に記載のシステムであって、

前記チャージポンプが電圧ダグラである、システム。 40

**【請求項 16】**

請求項 13 に記載のシステムであって、

前記光信号をサンプルする前記サンプラーが相關ダブルサンプリングを用い、前記相關

ダブルサンプリングが前記ブラックサンプラーと前記ビデオサンプラーとを用いることを

含む、システム。

**【請求項 17】**

請求項 13 に記載のシステムであって、

a ) 前記第 1 のクロック信号が、前記第 2 のクロック信号が立ち上がる前に 3 クロック

サイクル立ち上がり、

b ) 前記第 2 のクロック信号が 17 クロックサイクルの間に高であり、 50

c ) 前記第 2 のクロック信号が、前記第 1 のクロック信号が立ち下がる前に 5 クロックサイクル立ち下がり、

d ) 前記第 1 のクロック信号が 17 クロックサイクルの間に低であり、その後立ち上がる、システム。

**【請求項 18】**

請求項 7 に記載のシステムであって、

前記第 1 のクロック信号と前記第 3 のクロック信号ライン上の第 3 のクロック信号とが同じクロック信号であり、前記第 3 のクロック信号と前記第 4 のクロック信号ライン上の第 4 のクロック信号とが同じクロック信号である、システム。

**【請求項 19】**

10

請求項 1 に記載の装置であって、

上記の少なくとも幾つかが、少なくとも第 1 のチャージポンプ状態機械と第 1 のサンプリング状態機械との中に構成され、

前記サンプラー内に組み込まれた第 2 のサンプリング状態機械が、前記ブラックサンプルクロック信号とビデオサンプルクロック信号と第 2 のクロック信号とを実装して発生することができる、装置。

**【請求項 20】**

請求項 7 又は 13 に記載のシステムであって、

上記の少なくとも幾つかが、少なくとも第 1 のチャージポンプ状態機械と第 1 のサンプリング状態機械との中に構成され、

20

前記サンプリングロジック内に組み込まれた第 2 のサンプリング状態機械が、前記ブラックサンプルクロック信号とビデオサンプルクロック信号と第 2 のクロック信号とを実装して発生することができる、システム。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本願はアナログフロントエンド (A F E) におけるノイズ抑制に関し、更に具体的には、A F E におけるチャージポンプのクロックにより導入されるノイズ抑制に関連する。

**【背景技術】**

**【0002】**

30

チャージポンプは、種々の回路構成要素の外部キャパシタを駆動するため高い立ち上がり / 立ち下がりレート (約 3.3 ボルト / ナノ秒など) のレール・トゥー・レールクロック信号を提供することができる。従来のシステムにおいて、チャージポンプクロックスイッチングノイズが、特に、「接地バウンス」として知られている現象及び電磁放電の他の形式を介して、他の高感度センサ入力に電気的に結合されることを避けるため印刷回路基板 (P C B) 上のアグレシブな接地及びシールド設計ストラテジーが好ましい可能性がある。接地バウンスは、特に、ビデオ入力、リセットレベルクランプ (R L C) 、及びアナログデジタルコンバータ (A D C) 基準ピンにとって問題となる。

**【0003】**

しかし、対抗する考え方として、結合されたチャージポンプを備えた「スキャンヘッド」のためなどのコスト主導 P C B 設計は、単一接地平面を用い得る。これは典型的に、P C B 及び回路ジオメトリ制約のような考え方起因して阻害された性能を有する。そのため、チャージポンプがダイ上のセンシティブなアナログ回路から内部で物理的に隔離され得る場合でも、チャージポンプのスイッチングノイズが、接地バウンスを介する外部電気的結合のような要因に起因して A F E の信号対雑音比 (S N R) を容易に悪化させる恐れがある。

**【0004】**

1 つの初期実装において、チャージポンプがイネーブルされたとき A F E の S N R が 6.2 d B から 4.0 d B まで悪化したことが分かっている。変化する A F E サンプリングされたレートに関与する更なる調査により、A D C の変換データでのノイズは、A F E のチャ

40

50

ージポンプクロックとサンプリングされた周波数間の相互変調積であることが分かった。この結論は、チャージポンプクロックエッジが、ビデオ入力、R L C 信号、及びA F E 基準信号に種々に結合されていることを見ることによっても支持されている。

【 0 0 0 5 】

チャージポンプのノイズを低減するための 1 つのアプローチは、1 ナノ秒 ( n s ) から 3 n s までなど、チャージポンプの立ち上がり / 立ち下がり時間を増大させることである。この増大は S N R の著しい改善は提供しないことが分かっている。また、最小クロック立ち上がり / 立ち下がり時間がチャージポンプの効率及び貫通懸念により要求されるため、更なる増大はダイ上で実際には可能ではない。

【 0 0 0 6 】

従って、当業界において、A F E 及びチャージポンプに関連付けられる少なくとも幾つかの上述の問題に対処する、チャージポンプを用いるA F E におけるノイズ抑制が必要とされている。

【発明の概要】

【 0 0 0 7 】

第 1 の側面が或る装置を提供し、この装置は、チャージポンプと、光信号をサンプルするサンプラーとを含み、サンプラーは、ブラックサンプラー、ビデオサンプラー、及びアナログデジタルコンバータを含む。第 1 の側面は更に單一クロックを提供し、單一クロックは、a ) 前記チャージポンプに結合されるチャージポンプロジェクトと、b ) 前記光信号をサンプルする前記サンプラーに結合されるサンプラー・ロジックとに結合され、それらにクロック信号を提供する。

【 0 0 0 8 】

第 2 の側面が或るシステムを提供し、このシステムは、チャージポンプであって、第 1 のスイッチの第 1 のゲートと、第 2 のスイッチの第 2 のゲートと、第 3 のスイッチの第 3 のゲートと、第 4 のスイッチの第 4 のゲートとを有する前記チャージポンプを含む。第 2 の側面は更に、光信号をサンプルするサンプラーであって、ブラックサンプラーと、ビデオサンプラーと、アナログデジタルコンバータとを含む前記サンプラーを提供する。單一クロックが、a ) 第 1 のクロック信号ラインにより前記第 1 のゲートに、第 2 のクロック信号ラインにより前記第 2 のゲートに、第 3 のクロック信号ラインにより前記第 3 のゲートに、及び第 4 のクロック信号ラインにより前記第 4 のゲートに、及び b ) 光信号をサンプルする前記サンプラーに結合される。前記第 1 のクロック信号ラインの第 1 のクロック信号の立ち上がりエッジと前記第 2 のクロック信号ラインの第 2 のクロック信号の立ち下がりエッジとが各々、前記A D C に結合されるA D C ラインのアナログデジタルクロック信号の立ち下がりエッジと整合される。

【 0 0 0 9 】

第 3 の側面が或るシステムを提供し、このシステムが、チャージポンプであって、第 1 のスイッチの第 1 のゲートと、第 2 のスイッチの第 2 のゲートと、第 3 のスイッチの第 3 のゲートと、第 4 のスイッチの第 4 のゲートとを有する前記チャージポンプを含む。光学的光センサをサンプルするためのサンプラーが、ブラックサンプラーと、ビデオサンプラーと、アナログデジタルコンバータ ( A D C ) とを含む。單一クロックが、a ) チャージポンプロジェクトであって、第 1 のクロックラインにより前記第 1 のゲートに、第 2 のクロックラインにより前記第 2 のゲートに、第 3 のクロックラインにより結合される前記第 3 のゲートに、及び第 4 のクロックラインにより前記第 4 のゲートに結合される、前記チャージポンプロジェクトに、b ) 前記サンプラーに、及び c ) 前記A D C に、結合される。前記第 1 のクロックラインの第 1 のクロック信号の立ち下がりエッジと、前記第 2 のクロックラインの第 2 のクロック信号の立ち上がりエッジとの両方が、ビデオサンプルクロック信号の立ち上がりエッジと整合される。

【 図面の簡単な説明】

【 0 0 1 0 】

例示の実施例を添付の図面を参照して説明する。

10

20

30

40

50

## 【0011】

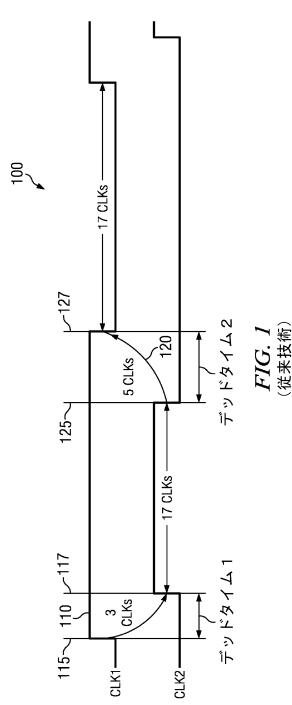

【図1】図1は、従来技術のオーバーラップするチャージポンプ信号のタイミング図である。

## 【0012】

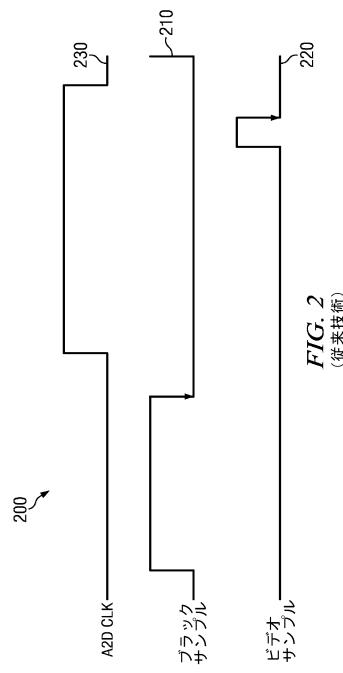

【図2】図2は、従来技術のAFE相関ダブルサンプリング信号のタイミング図である。

## 【0013】

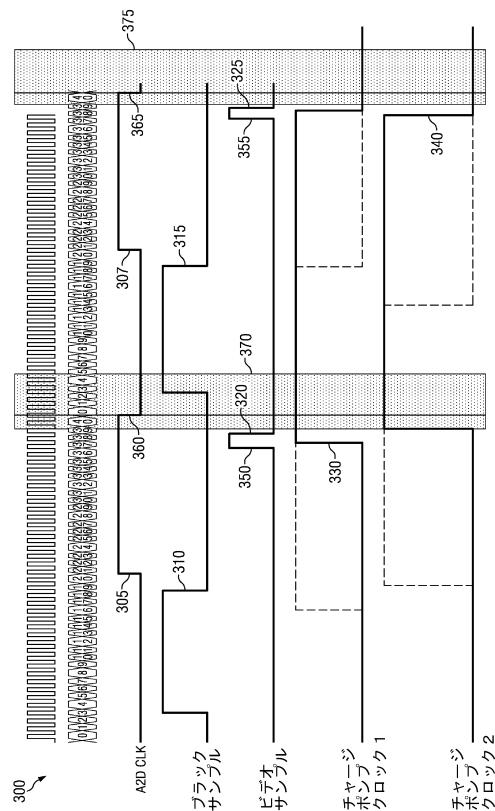

【図3A】図3Aは、第1の側面に従った、チャージポンプクロックのビデオサンプルの立ち上がりエッジとの整合のタイミング図である。

## 【0014】

【図3B】図3Bは、第1の実施例に従った、チャージポンプ及びブラックサンプラー、ビデオサンプラー、及びADCに結合される單一クロックドライバロジックを含むシステムを示す。 10

## 【0015】

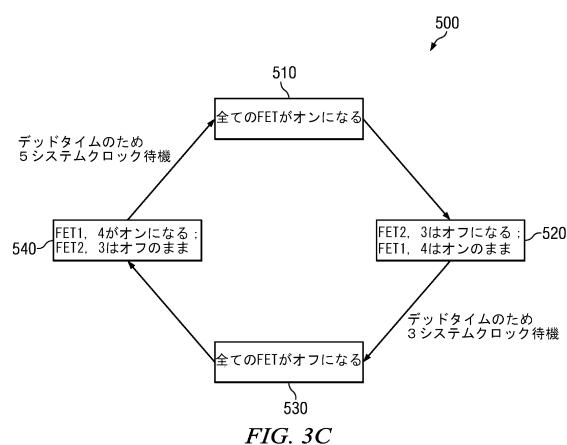

【図3C】図3Cは、図3Bのチャージポンプロジックと共に用いるためのチャージポンプ状態機械の図である。

## 【0016】

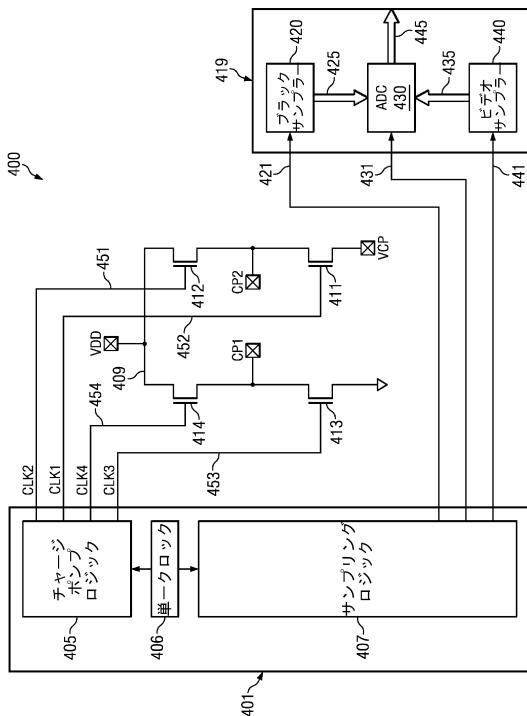

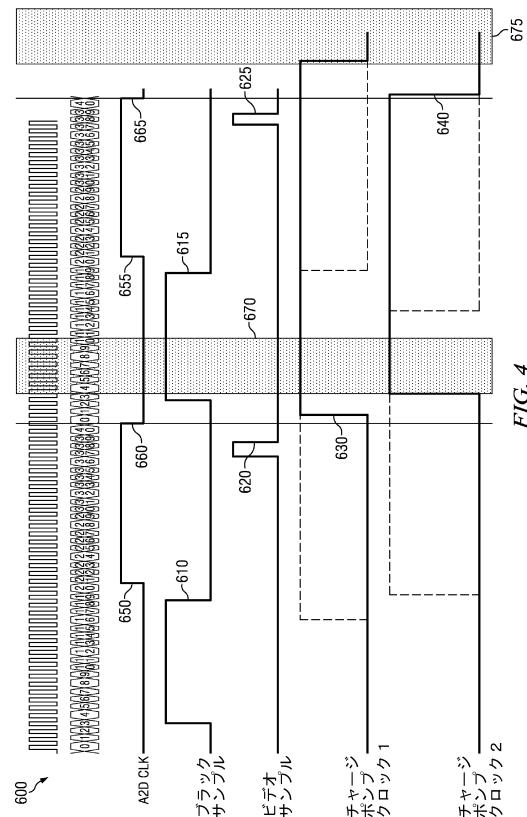

【図4】図4は、第2の側面に従った、チャージポンプクロックのADCクロック信号の立ち下がりエッジとの整合のタイミング図である。

## 【0017】

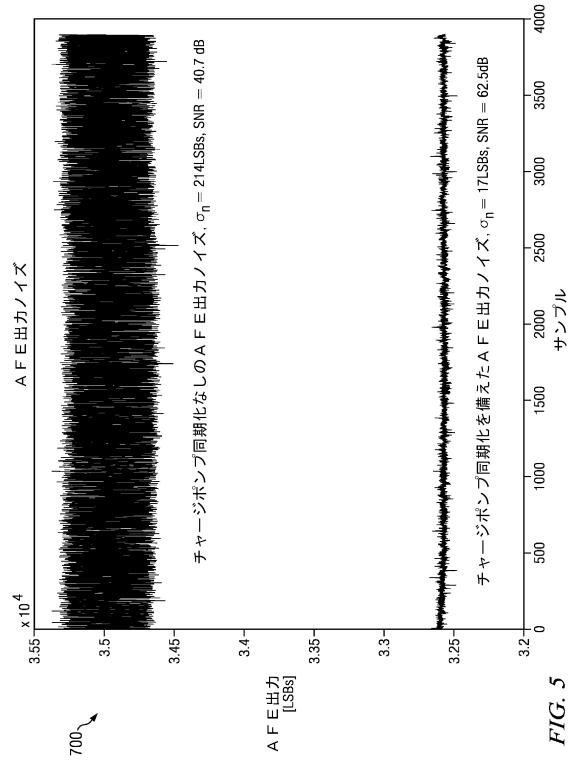

【図5】図5は、チャージポンプ及びAFE両方を駆動するため、單一口ロジックを備えた及び備えない、AFEノイズ性能のグラフである。 20

## 【発明を実施するための形態】

## 【0018】

図1は、チャージポンプのための複数の従来技術のオーバーラップするチャージポンプクロック信号のタイミングチャート100を図示する。チャージポンプは、図1に図示するように、2つのオーバーラップするチャージポンプクロック信号により支配され得る。

## 【0019】

図1に図示するように、一実施例において、オペレーションの間、チャージポンプのためのサイクル毎に2つのデッドタイム、第1のデッドタイム110及び第2のデッドタイム120、がある。CLK1が高でありCLK2が低である第1のデッドタイム110は、CLK1の立ち上がりエッジ115からCLK2の立ち上がりエッジ117までの3クロックサイクルであり、CLK1が高でありCLK2が低である第2のデッドタイム120は、CLK2の立ち下がりエッジ125からCLK1の立ち下がりエッジ127までの5クロックサイクルである。これらの従来技術のクロック信号はチャージポンプがフルにイネーブルされると連続的であり、チャージポンプがディセーブルされるまでイネーブルのままである。 30

## 【0020】

図2は、従来技術のAFE相関ダブルサンプリング信号のタイミングチャート200を図示する。従来技術のAFEがAFE状態機械(図示せず)を用いて3つのクロック信号、ブラックサンプルクロック信号210、ビデオサンプルクロック信号220、及びADCサンプルクロック信号230、を制御する。ブラックサンプルクロック信号210及びビデオサンプルクロック信号220は、所与の光信号の相関ダブルサンプリング(CDS)に用いられる。 40

## 【0021】

図3Aは、第1の側面に従ったチャージポンプクロックのビデオサンプルの立ち上がりエッジとの整合のタイミングチャート300である。

## 【0022】

タイミングチャート300において、ブラックサンプルクロック信号の立ち下がりエッジ310とビデオサンプルクロック信号の立ち下がりエッジ320、325は、CCDサンプリングの利用と共に、ブラック信号レベル及びビデオ信号レベル間の差をサンプルす 50

るために用いられる。この差は、アナログ入力信号として A D C ( 図示せず ) に印加され、デジタル変換データがその後生成される。タイミングチャート 3 0 0 において、A F E 性能を改善する目的で、タイミングは、サンプリングされた光信号の読み出し時、特に、ブラックサンプルクロック信号の立ち下がりエッジ 3 1 0 及びビデオサンプルクロック信号の立ち下がりエッジ 3 2 0 、 3 2 5 の読み出し時又はその辺りで、チャージポンプからのスイッチングノイズが抑制されるようになっている。

【 0 0 2 3 】

タイミングチャート 3 0 0 において、アナログデジタルクロック信号 ( A D 2 C L K ) の立ち上がりエッジ 3 0 5 、 3 0 7 でアナログデジタル変換が生じる。A 2 D C L K の立ち上がりエッジ 3 0 5 、 3 0 7 は、ブラックサンプル 3 1 0 、 3 1 5 の立ち下がりエッジ後複数のクロックサイクル生じる。また、図 3 A に示すように、ビデオサンプルクロック信号の立ち下がりエッジ 3 2 0 、 3 2 5 は、A 2 D C L K の立ち下がりエッジ 3 6 0 、 3 6 5 前に複数のクロックサイクル生じる。ブラックサンプルの立ち下がりエッジ 3 1 0 、 3 1 5 が生じた後、A 2 D C L K の立ち上がりエッジ 3 0 5 、 3 0 7 によりトリガされるように A D C がアナログデジタル変換を実行する。後に説明するシステム 4 0 0 のサンプリングロジック 4 0 5 に組み込まれるなどの、第 1 のサンプリング状態機械が、タイミングチャート 3 0 0 のブラックサンプリング信号、A D 2 C L K 、及びビデオサンプリング信号を実装及び生成することができる。

【 0 0 2 4 】

更なる実施例において、クロック 1 信号 ( C L K 1 ) の立ち上がりエッジ 3 3 0 とクロック 2 信号 ( C L K 2 ) の立ち下がりエッジ 3 4 0 は、それぞれ、ビデオサンプルクロック信号の立ち上がりエッジ 3 5 0 、 3 5 5 と整合される。幾つかの実装において、「整合」は、整合されたクロック信号のエッジの遷移の間に 1 つのクロックサイクルが生じていることと定義することができることに留意されたい。一実施例において、後に説明する図 3 C の状態機械 5 0 0 などのチャージポンプクロック状態機械が、タイミングチャート 3 0 0 のチャージポンプクロック信号を実装する第 1 のサンプリング状態機械とタンデム式に用いられる。

【 0 0 2 5 】

タイミングチャート 3 0 0 の実装は、それが、ブラックレベルクランプ精度に重要なあるブラックサンプルのかなりの幅を提供する点で有利であり得る。タイミングチャート 3 0 0 は、ブラックサンプルクロック信号の立ち下がりエッジ 3 1 0 に対して広範囲のプログラマビリティを提供することができる。

【 0 0 2 6 】

灰色で示す領域 3 7 0 、 3 7 5 は、センシティブな信号がチャージポンプ切り替えに起因してリギングする時間の実験的に観察される期間を示す。これらの期間の間、ブラックサンプリング及びビデオサンプリングは制限されるべきである。この制限のあり得る欠点は、一実施例において、ビデオサンプルが 2 クロックサイクルより幅広くないことがある。しかし、典型的な A F E 実装において、ビデオクロック信号の立ち下がりエッジ 3 2 0 は、ビデオクロック信号の立ち上がりエッジ 3 5 0 よりビデオ信号サンプリングに関して一層重要である。概して、第 1 のタイミングチャート 3 0 0 の実装は、A F E のフロントエンドノイズを抑制するのを助け、システム 4 0 0 などにおいて用いることができる。

【 0 0 2 7 】

図 3 B は、チャージポンプ 4 0 9 が、サンプラー 4 1 9 を備えたドライバロジック 4 0 1 の單一クロック 4 0 6 を共有する、システム 4 0 0 を図示する。システム 4 0 0 の要素は、すべて共通電気的接地を共有することができ、单一チップに結合され得るか又は单一チップ内で統合され得る。一実施例において、システム 4 0 0 は A F E である。説明を簡潔にするため、システム 4 0 0 は、第 1 のタイミングチャート 4 0 0 との組み合わせにおいて用いられるように説明している。しかし、システム 4 0 0 は、第 2 のタイミングチャート 6 0 0 との組み合わせにおいて用いることもできる。

【 0 0 2 8 】

10

20

30

40

50

システム 400において、ドライバロジック 401は、チャージポンプロジェクト 405、単一クロック 406、及びサンプリングロジック 407を含む。チャージポンプロジェクト 405はチャージポンプ 409に結合され、サンプリングロジック 407はサンプラー 419に結合される。単一クロック 406は、チャージポンプロジェクト 405及びサンプリングロジック 407両方に対してクロック信号を提供し、これらはシステム 400の他の構成要素に対してクロック信号を提供する。

【0029】

回路 400において、サンプリングロジック 407は、ブラックサンプルクロックライン 421により、サンプリング回路であり得るサンプラー 419のブラックサンプラー 420に結合される。サンプリングロジック 407は、ADC クロックライン 431によりサンプラー 419のADC 430にも結合される。サンプリングロジック 407は、ビデオクロックライン 441によりサンプラー 419のビデオサンプラー 440にも結合される。

【0030】

ブラックサンプラー 420は、バス 425によりADC 430に結合される。ビデオサンプラー 440は、バス 435によりADC 420に結合される。サンプラー 419のADC 430は出力バス 445を有する。

【0031】

チャージポンプロジェクト 405は、第1のクロックライン 451を介して第1の電界効果トランジスタ (FET) 411の第1のゲートに結合される。チャージポンプロジェクト 405は、第2のクロックライン 452を介して第2のFET 412の第2のゲートに結合される。チャージポンプロジェクト 405は、第3のクロックライン 443を介して第3のフィールドFET 413の第3のゲートに結合される。チャージポンプロジェクト 405は、第4のクロックライン 444を介して第4のFET 414の第4のゲートに結合される。

【0032】

一実施例において、システム 400はスキャンヘッド AFE を含む。チャージポンプ 409は、接地を介してサンプラー 419に結合され、チャージポンプ 409は、システム 400の発光ダイオード (LED) (図示せず) を駆動するためにも用いられる。

【0033】

更なる実施例において、システム 400のスキャンヘッド AFE が、ブラックサンプラー 420及びビデオサンプラー 440内に又はそれらに関連して用いられ得るものなどの相関ダブルサンプリングプログラマブルゲートアレイ (CDS-PGA)、16ビットパイプライン ADC などのADC 430、赤緑青 (RGB) LED ドライバ (図示せず)、電圧ダブラー (doubler) であり得るチャージポンプ 409、及びドライバロジック 410を含む。システム 400のスキャンヘッド AFE のサンプリングレートが、種々のスキャナーシステムに対応するため 1~4 メガサンプル毎秒 (MSPS) でプログラム可能である。

【0034】

以下に述べるように、システム 400の1つのオペレーションは、タイミングチャート 300を用いて説明することができる。ドライバロジック 410のチャージポンプロジェクト 405及びサンプリングロジック 407両方が、タイミングチャート 400により用いられる種々のクロック信号を生成する。

【0035】

ブラックサンプルクロックライン 421はブラックサンプルクロックを搬送し、ブラックサンプルクロックは、ブラックサンプルの立ち下がりエッジ 310を含む。ADC クロックライン 431はADC CLK 303を搬送する。ビデオサンプルライン 441はビデオサンプルクロック信号を搬送し、ビデオサンプルクロック信号はビデオクロック信号の立ち下がりエッジ 320、325及びビデオクロック信号の立ち上がりエッジ 350、355を含む。

## 【0036】

チャージポンプ409のスタートアップが終了した後、第3のライン443の第3のクロック信号(CLK3)は、第1のライン441のCLK1信号と同じクロックパターンタイミングを有し、第4のライン444の第4のクロック信号(CLK4)は、第2のライン442のCLK2信号と同じ信号パターンを有する。

## 【0037】

更なる実施例において、システム400は、サンプラー419がアクティブにされないときのデフォルト「システム」クロック(図示せず)と、回路400を駆動するための單一クロック406との間で、チャージポンプ409により用いられるクロックをシームレスに切り替えることができる。チャージポンプ409はまず、サンプラー419など、AFEの側面が実行していないときシステムクロック(図示せず)からそのクロック信号を引き出す。チャージポンプ409はその後、AFEサンプリングがイネーブルされているときは必ず、ドライバロジック410の單一クロックに切り替わる。この仕組みの結果、チャージポンプ409の効率は、上述のように、チャージポンプデッドサイクルの一層効率的な利用に起因して増大される。

10

## 【0038】

システム400の一実施例において、ブラックサンプラー420、ADC430、及びビデオサンプラー440に対する3つのクロック信号の各エッジ(全部で6つのクロック信号エッジ遷移に対し)は、6つの8ビットレジスタを用いてプログラムされ得、これらのエッジは、サンプリングロジック405に組み込まれる第1のサンプリング状態機械(図示せず)を用いて制御される。第1のサンプリング状態機械は、CLK1及びCLK2信号、ブラックサンプル信号、及びビデオサンプル信号など、状態エンジンの個々の出力間でタイミング関係があり得るが、チャージポンプ状態機械から物理的に独立し得る。一実施例において、ADCコンバータ430によるADC変換の開始が、ロジック410の、チャージポンプ状態機械又は第1のサンプリング状態機械などの、状態機械によって決まり、これは、ロジック410への入力ピンの一つの上の信号によりトリガされる。

20

## 【0039】

タイミングチャート300を実装する種々の状態機械を用いるときのシステム400の一実施例において、ビデオサンプルが單一クロック406の2つのクロックサイクルより幅広くない。しかし、これは典型的に、ビデオ信号サンプリングに関連して重要であるビデオ信号の立ち下がりエッジである。

30

## 【0040】

図3Cは、上述のように、システム400のチャージポンプ409のFETのゲートに印加されるクロック信号と共に用いられる状態機械500の一実施例を図示する。状態機械510及びブラックサンプラー420のための第1のサンプリング状態機械、ADC430、及びビデオサンプラー440は全て、システム400の單一クロック406などの單一クロックによりクロックされる。状態機械500において、システム400のスタートアップが終了した後、FET3 413はFET2 412のように機能し、FET4 414はFET1 411のように機能する。

40

## 【0041】

状態機械500はチャージポンプロジック405内に組み込まれ得る。

## 【0042】

スタート状態510において、全てのFET、FET1 411、FET2 412、FET3 413、FET4 414がオンである。その後、状態機械500は状態520に遷移する。

## 【0043】

状態520において、FET2 412及びFET3 413はオフに切り替わる。FET1 411及びFET4 414はオンのままである。その後、状態機械500は3クロックサイクル待機し、その後、状態機械500は状態530に進む。

## 【0044】

50

状態 530において、全ての F E T 1 411、F E T 2 412、F E T 3 413、及び F E T 4 414 はオフである。状態機械 500 は状態 540 に遷移する。

#### 【0045】

状態 540において、F E T 1 411 及び F E T 4 414 がオンである。F E T 2 412 及び F E T 3 413 はオフのままである。その後、状態機械 500 は 5 クロックサイクル待機する。状態機械 500 はその後巡回して状態 510 に戻る。

#### 【0046】

図 4 は、システム 400 の利用と共に用いることもでき、更に、ロジック 410 において実装され得るものなど、タイミングチャート 600 の第 2 の側面を図示する。タイミングチャート 300 に類似するタイミングチャート 600 において、ブラックサンプルクロック信号の立ち下がりエッジ 610、615 とビデオサンプルクロック信号の立ち下がりエッジ 620、625 が、CCDサンプリングの利用と共に、ブラック信号レベルとビデオ信号レベルとの間の光学的入力信号上の差をサンプルするために用いられる。この差は、アナログ入力信号として ADC ( 図示せず ) に印加され、デジタル変換データがその後生成される。アナログデジタル変換が、AD2CLK の立ち上がりエッジ 650、655 で生じる。

10

#### 【0047】

タイミングチャート 600 において、AD2CLK の立ち上がりエッジ 650、655 は、ブラックサンプルクロック信号の立ち下がりエッジ 610、615 後複数のクロックサイクル生じる。また、図 4 に示すように、ビデオサンプルクロック信号の立ち下がりエッジ 620、625 が、AD2CLK の立ち下がりエッジ 660、665 前に複数のクロックサイクル生じる。ブラックサンプルクロック信号の立ち下がりエッジ 610、615 が生じた後、ADC が AD2CLK の立ち上がりエッジ 650、655 時にアナログデジタル変換を実行する。一実施例において、サンプリングロジック 405 に組み込まれる第 2 のサンプリング状態機械が、タイミングチャート 600 のブラックサンプルクロック信号、ビデオサンプルクロック信号、及び AD2CLK を実装及び生成することができる。

20

#### 【0048】

更なる好ましい実施例において、チャージポンプクロック、CLK1 及び CLK2 は、AD2CLK の立ち下がりエッジ 660、665 とも整合される。この更に好ましい実施例において、AD2CLK の立ち下がりエッジ 660、665 に関し、CLK1 及び CLK2 のパターンが続き、その場合でも 3 及び 5 クロックサイクルデッドタイム期間を維持する。タイミングチャート 600 において、CLK1 の立ち上がりエッジ 630 と CLK2 の立ち下がりエッジ 640 は、それぞれ、AD2CLK 信号の立ち下がりエッジ 660、665 と整合される。幾つかの実装において、「整合」は、異なるクロック信号の整合されたエッジ間に 1 クロックサイクルが生じていることと定義することができることに留意されたい。

30

#### 【0049】

状態機械 500 などのチャージポンプクロック状態機械が、CLK1 及び CLK2 を生成するためシステム 400 により用いられ得る。第 2 のサンプリング状態機械は、タイミングチャート 600 を実装するため、及びブラックサンプルクロック信号、ビデオサンプルクロック信号、及び ADC クロック信号を生成するためシステム 400 により用いられ得る。

40

#### 【0050】

灰色で示す領域 670、675 は、センシティブな信号がチャージポンプ切り替えに起因してリンクする第 2 の側面のための時間の実験的に観察される期間を示す。これらの期間の間、ブラックサンプリング及びビデオサンプリングは制限されるべきである。この制限のあり得る欠点は、AFE 性能のために利用可能なブラックサンプル位置の範囲が幾分限定されることである。

#### 【0051】

図 5 は、單一クロックドメイン 710 を利用した及び單一クロックドメイン 720 を利

50

用しない、AFEノイズ性能700を図示する。ノイズ測定結果から、チャージポンプがイネーブルされる間でも、AFEのSNR性能が40dBから62dBまで改善されたことが分かった。チャージポンプ單一クロックを備えたAFEのノイズ性能は、チャージポンプが完全にディセーブルされる間生じるSNRの品質と同程度高効率である。

【0052】

本発明に関連する技術に習熟した者であれば、説明した例示の実施例に変形が成され得ること、及び本発明の特許請求の範囲内で他の実施例を実装し得ることが分かるであろう。

【図1】

【図2】

【図3A】

FIG. 3A

【図3B】

FIG. 3B

【図3C】

FIG. 3C

【図4】

FIG. 4

【図5】

FIG. 5

---

フロントページの続き

(72)発明者 スアルプ アラス

アメリカ合衆国 75206 テキサス州 ダラス, エイピーティー 2717, サウスウエ

スタン ブールバード 8650

(72)発明者 グハプラカシュ アムダン

アメリカ合衆国 75082 テキサス州 リチャードソン, エイピーティー 191, ダブ

リュー レンナー ロード 2600

(72)発明者 エムディー アビドゥール ラフマン

アメリカ合衆国 75013 テキサス州 アレン, キングスリー コート 1321

(72)発明者 シャオチュン ジャオ

アメリカ合衆国 75013 テキサス州 アレン, キャメロット ドライブ 2006

審査官 桑 原 恭雄

(56)参考文献 特開2008-099370 (JP, A)

特開2004-006987 (JP, A)

特開平10-215564 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/07

H04N 5/357

H04N 5/378