(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-166565

(P2008-166565A)

(43) 公開日 平成20年7月17日(2008.7.17)

| (51) Int.Cl.                | F 1        | テーマコード (参考) |

|-----------------------------|------------|-------------|

| <b>H01L 25/10</b> (2006.01) | H01L 25/14 | Z 5 E 3 3 6 |

| <b>H01L 25/11</b> (2006.01) | H05K 1/14  | B 5 E 3 4 4 |

| <b>H01L 25/18</b> (2006.01) | H05K 1/18  | R           |

| <b>H05K 1/14</b> (2006.01)  |            |             |

| <b>H05K 1/18</b> (2006.01)  |            |             |

審査請求 未請求 請求項の数 5 O L (全 18 頁)

|           |                              |          |                                              |

|-----------|------------------------------|----------|----------------------------------------------|

| (21) 出願番号 | 特願2006-355461 (P2006-355461) | (71) 出願人 | 000001889<br>三洋電機株式会社<br>大阪府守口市京阪本通2丁目5番5号   |

| (22) 出願日  | 平成18年12月28日 (2006.12.28)     | (71) 出願人 | 506227884<br>三洋半導体株式会社<br>群馬県邑楽郡大泉町坂田一丁目1番1号 |

|           |                              | (74) 代理人 | 110000176<br>一色国際特許業務法人                      |

|           |                              | (72) 発明者 | 小林 健一<br>大阪府守口市京阪本通2丁目5番5号 三<br>洋電機株式会社内     |

|           |                              | (72) 発明者 | 中野 敦史<br>大阪府守口市京阪本通2丁目5番5号 三<br>洋電機株式会社内     |

最終頁に続く

(54) 【発明の名称】回路装置及びデジタル放送受信装置

## (57) 【要約】

【課題】接続電極の増加に伴うサイズの増大を抑制する

。

【解決手段】少なくとも一方の面側に配線層を有する配線基板と、配線基板の一方の面に配設され、配線層と接続される回路素子と、配線基板の一方の面に配設され、配線層と接続される複数の接続電極と、を備え、複数の接続電極の配線基板の一方の面から突出する高さが、回路素子の配線基板の一方の面から突出する高さより低く、複数の接続電極が他の配線基板の一方の面に配設された複数の接続部と当接されるとともに、回路素子が他の配線基板の一方の面と干渉しない位置に配設されることにより接続可能である。

【選択図】図 6

**【特許請求の範囲】****【請求項 1】**

少なくとも一方の面側に配線層を有する配線基板と、

前記配線基板の前記一方の面に配設され、前記配線層と接続される回路素子と、

前記配線基板の前記一方の面に配設され、前記配線層と接続される複数の接続電極と、

を備え、

前記複数の接続電極の前記配線基板の前記一方の面から突出する高さが、前記回路素子

の前記配線基板の前記一方の面から突出する高さより低く、

前記複数の接続電極が他の配線基板の一方の面上に配設された複数の接続部と当接されるとともに、前記回路素子が前記他の配線基板の前記一方の面と干渉しない位置に配設され

ることにより接続可能であること、

を特徴とする回路装置。

**【請求項 2】**

請求項 1 に記載の回路装置であって、

前記複数の接続電極の夫々が略球状に形成されてなること、

を特徴とする回路装置。

**【請求項 3】**

請求項 1 又は 2 に記載の回路装置であって、

前記複数の接続電極は、前記配線基板の前記一方の面の対向する少なくとも 2 つの側辺

に配設されてなること、

を特徴とする回路装置。

**【請求項 4】**

請求項 1 ~ 3 の何れか一項に記載の回路装置であって、

前記複数の接続電極が前記他の配線基板の前記複数の接続部と当接されるとともに、前

記回路素子が前記他の配線基板の前記一方の面から前記他方の面に向かって切除された切

除部に挿入されることにより接続可能であること、

を特徴とする回路装置。

**【請求項 5】**

所望のチャンネルのデジタル放送信号を出力するチューナーと、

前記チューナーから出力される前記デジタル放送信号に基づいてアナログ映像信号を出

力するデジタル放送処理装置と、

前記デジタル放送処理装置から出力される前記アナログ映像信号に基づいて映像表示処

理を行うアナログ映像処理装置と、

を含む装置が第 1 配線基板に実装されてなるデジタル放送受信装置であって、

前記第 1 配線基板は、

一方の面に配設された複数の接続部を有し、

前記デジタル放送処理装置は、

少なくとも一方の面側に配線層を有する第 2 配線基板と、

前記第 2 配線基板の前記一方の面に配設され、前記配線層と接続され、前記デジタル放

送信号に基づく処理に係る回路素子と、

前記第 2 配線基板の前記一方の面に配設され、前記配線層と接続される複数の接続電極

と、

を備え、

前記複数の接続電極の前記第 2 配線基板の前記一方の面から突出する高さが、前記回路

素子の前記第 2 配線基板の前記一方の面から突出する高さより低く、

前記複数の接続電極が前記複数の接続部と当接されるとともに、前記回路素子が前記第

1 配線基板の前記一方の面と干渉しない位置に配設されることにより前記第 1 配線基板と

接続可能であること、

を特徴とするデジタル放送受信装置。

**【発明の詳細な説明】**

10

20

30

40

50

**【技術分野】****【0001】**

本発明は、回路装置及びデジタル放送受信装置に関する。

**【背景技術】****【0002】**

半導体装置が搭載される機器の小型化を実現するためには、半導体装置を含んで構成される回路装置のサイズを小さくすることが重要である。回路装置のサイズを小さくする手法として、1チップ内に様々な機能を格納するS o C (System on a Chip) やS i P (System in Package) が用いられている。

**【0003】**

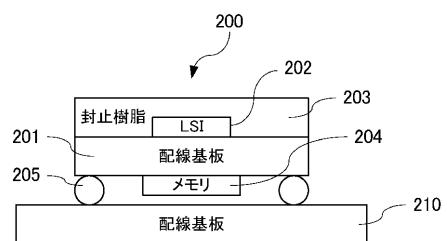

図8は、S i Pを用いて構成された回路装置の構成例を示す図である。回路装置200は、多層の配線層を有する配線基板201を含んで構成されている。配線基板201の一方の面には、ペアチップのL S I (Large Scale Integration) 202が配設され、L S I 202が配設された面は封止樹脂203によって封止されている。また、配線基板201の他方の面には、L S I 202が処理を実行する際に使用されるデータが格納されるメモリ204が配設されている。さらに、配線基板201の他方の面には、回路装置200を配線基板210と接続するための複数の接続電極205が配設されている。このように、1つの回路装置200に複数の回路素子を搭載することにより、全ての回路素子を別々に配線基板210に接続する場合と比較して、外部装置とのインターフェースに必要となる接続電極205の数を少なくすることが可能となり、回路装置200のサイズを小さくすることができる。

10

20

30

**【0004】**

さらに、回路装置200の配線基板210への実装面積を小さくするために、回路装置200を面実装(フリップチップ実装)することが一般的に行われている。図8に例示するように、接続電極205は例えば半田ボール等により構成されており、配線基板201のメモリ204と同一面に配設されている。そして、接続電極205が配線基板210に当接され、例えば接続電極205の外周を構成する半田が溶融されることにより、回路装置200が配線基板210に実装される。このように回路装置200を面実装する場合、メモリ204が実装時の障害とならないように、接続電極205の高さを、メモリ204の厚みよりも大きくする必要がある(例えば、特許文献1参照)。

40

**【特許文献1】特開2006-129255号公報****【発明の開示】****【発明が解決しようとする課題】****【0005】**

ところで、例えばデジタル放送受信装置のフルハイビジョン対応やデジタルカメラの高解像度化等に伴い、これらの機器に搭載される回路装置200と外部装置との間で送受信されるデータのビット数が増加することがある。このような場合、接続電極205の数を増やす必要があるが、メモリ204の厚みの制約により接続電極205を小さくすることができず、接続電極205の増加に伴って回路装置200のサイズも大きくなってしまう。

40

**【0006】**

本発明は上記課題を鑑みてなされたものであり、接続電極の増加に伴うサイズの増大を抑制可能な回路装置及びデジタル放送受信装置を提供することを目的とする。

**【課題を解決するための手段】****【0007】**

上記目的を達成するため、本発明の回路装置は、少なくとも一方の面側に配線層を有する配線基板と、前記配線基板の前記一方の面に配設され、前記配線層と接続される回路素子と、前記配線基板の前記一方の面に配設され、前記配線層と接続される複数の接続電極と、を備え、前記複数の接続電極の前記配線基板の前記一方の面から突出する高さが、前記回路素子の前記配線基板の前記一方の面から突出する高さより低く、前記複数の接続電

50

極が他の配線基板の一方の面に配設された複数の接続部と当接されるとともに、前記回路素子が前記他の配線基板の前記一方の面と干渉しない位置に配設されることにより接続可能であることとする。

【0008】

また、前記回路装置は、前記複数の接続電極の夫々が略球状に形成されてなることとすることもできる。

【0009】

また、前記回路装置は、前記複数の接続電極は、前記配線基板の前記一方の面の対向する少なくとも2つの側辺に配設されてなることとすることもできる。

【0010】

また、前記回路装置は、前記複数の接続電極が前記他の配線基板の前記複数の接続部と当接されるとともに、前記回路素子が前記他の配線基板の前記一方の面から前記他方の面に向かって切除された切除部に挿入されることにより接続可能であることとすることもできる。

10

【0011】

また、本発明のデジタル放送受信装置は、所望のチャンネルのデジタル放送信号を出力するチューナーと、前記チューナーから出力される前記デジタル放送信号に基づいてアナログ映像信号を出力するデジタル放送処理装置と、前記デジタル放送処理装置から出力される前記アナログ映像信号に基づいて映像表示処理を行うアナログ映像処理装置と、を含む装置が第1配線基板に実装されてなるデジタル放送受信装置であって、前記第1配線基板は、一方の面に配設された複数の接続部を有し、前記デジタル放送処理装置は、少なくとも一方の面側に配線層を有する第2配線基板と、前記第2配線基板の前記一方の面に配設され、前記配線層と接続され、前記デジタル放送信号に基づく処理に係る回路素子と、前記第2配線基板の前記一方の面に配設され、前記配線層と接続される複数の接続電極と、を備え、前記複数の接続電極の前記第2配線基板の前記一方の面から突出する高さが、前記回路素子の前記第2配線基板の前記一方の面から突出する高さより低く、前記複数の接続電極が前記複数の接続部と当接されるとともに、前記回路素子が前記第1配線基板の前記一方の面と干渉しない位置に配設されることにより前記第1配線基板と接続可能であることとする。

20

【発明の効果】

30

【0012】

接続電極の増加に伴うサイズの増大を抑制可能な回路装置及びデジタル放送受信装置を提供することができる。

【発明を実施するための最良の形態】

【0013】

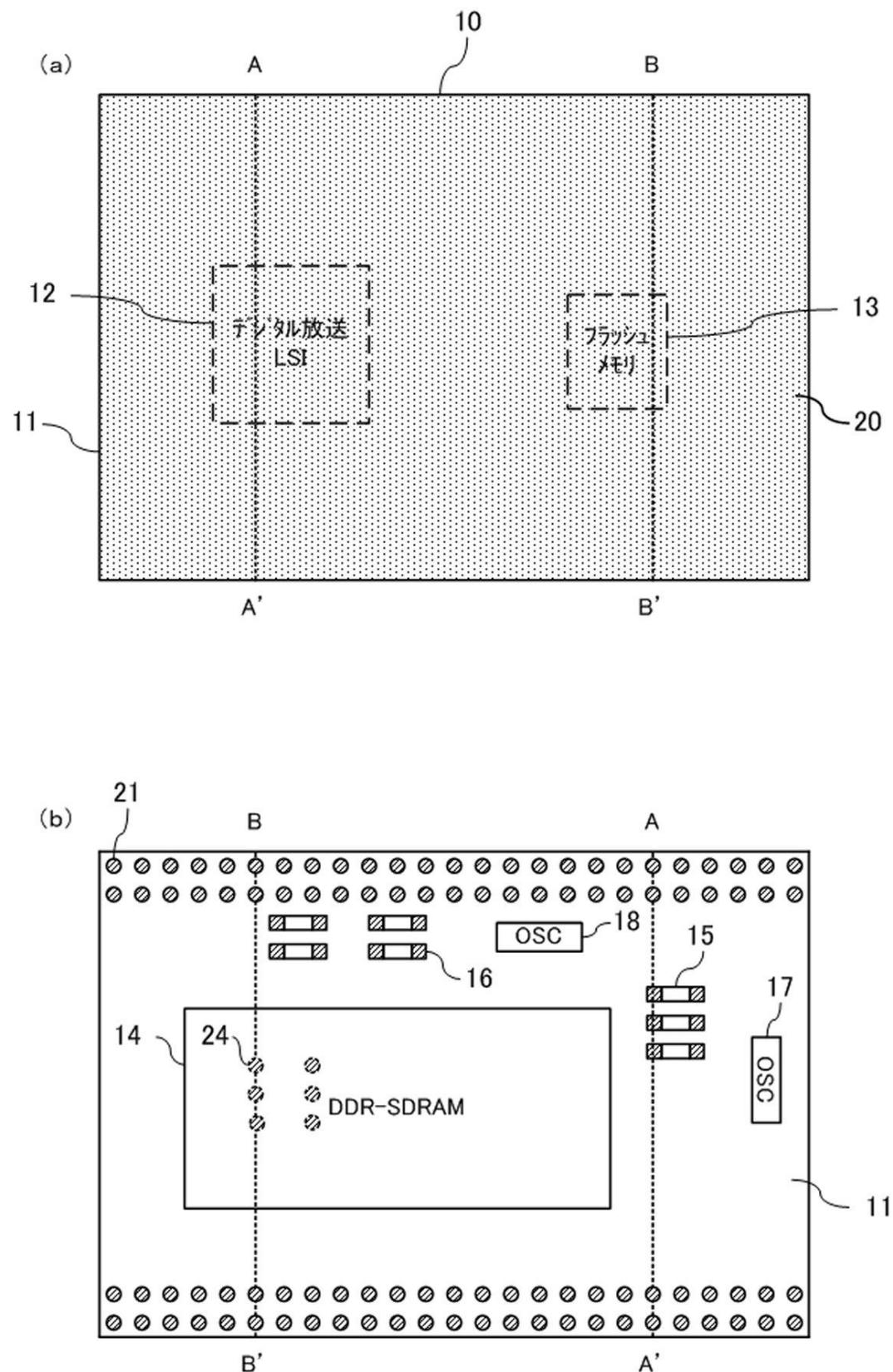

まず、本発明の回路装置の一実施形態であるデジタル放送処理装置の構成について説明する。図1は、デジタル放送処理装置10の構成を示す平面図である。デジタル放送処理装置10は、配線基板11に実装されており、図1(a)が配線基板11の一方の面側から見た平面図、図1(b)が配線基板11の他方の面側から見た平面図である。

40

【0014】

デジタル放送処理装置10は、配線基板11、デジタル放送LSI(Large Scale Integration)12、フラッシュメモリ13、DDR-SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory)14、チップ素子15,16、及び水晶発振子17,18を含んで構成されている。

【0015】

配線基板11は、多層配線構造となっており、一方の面(図2(a)に示される面)側の配線層(第1配線層)にデジタル放送LSI12及びフラッシュメモリ13が接続され、他方の面(図2(b)に示される面)側の配線層(第2配線層)にDDR-SDRAM14、チップ素子15,16、及び水晶発振子17,18が接続されている。

50

【0016】

デジタル放送 L S I 1 2 (集積回路) は、デジタル放送信号の復調や復号等の処理を行うベアチップである。また、フラッシュメモリ 1 3 (集積回路) は、デジタル放送 L S I 1 2 において実行されるプログラムや、各種処理において必要となる定義データ等が格納される記憶領域を有するベアチップである。そして、図 2 (a) に示すように、配線基板 1 1 の一方の面上には、ベアチップであるデジタル放送 L S I 1 2 及びフラッシュメモリ 1 3 を被覆するように封止樹脂 2 0 が設けられている。封止樹脂 2 0 は、例えば、加熱した金型にモールド樹脂のタブレットを流し込むモールド方法であるトランスファー・モールドにより形成される。

【0017】

DDR - SDRAM 1 4 (回路素子) は、デジタル放送 L S I 1 2 が各種処理を実行する際に使用されるデータが一時的に格納される記憶領域を有し、樹脂封止されたパッケージである。チップ素子 1 5, 1 6 は、バイパスコンデンサやチップ抵抗等である。特に、バイパスコンデンサであるチップ素子 1 5 は、デジタル放送 L S I 1 2 における電源ノイズの影響を抑制するために用いられる。水晶発振子 1 7, 1 8 は、夫々周波数の異なるクロックを生成するパッケージである。例えば、水晶発振子 1 8 により生成されるクロックは、デジタル放送処理装置 1 0 におけるシステムクロックとして用いられ、水晶発振子 1 7 により生成されるクロックは、デジタル放送信号の復調処理を行う際に用いられる。

【0018】

そして、配線基板 1 1 の他方の面には、対向する 2 つの側辺 (図 2 (b) における上下の側辺) に、それぞれ 2 列に配列された複数の接続電極 2 1 が設けられている。接続電極 2 1 は、例えば半田ボール等の略球状の接続部材を用いて構成することができる。半田ボールを用いて接続電極 2 1 を構成する場合、接続電極 2 1 が他の配線基板の接続部に当接された後、接続電極 2 1 の外周を構成する半田が溶融されることにより、デジタル放送処理装置 1 0 が他の配線基板に接続される。なお、本実施形態では、配線基板 1 1 の他方の面の対向する 2 つの側辺のみに接続電極 2 1 を設けることとしたが、他の側辺 (図 2 (b) における左右の側辺) にも接続電極 2 1 を設けることとしてもよい。また、接続電極 2 1 は各側辺において 2 列に配列されているが、1 列のみであってもよいし、3 列以上であってもよい。さらに、配線基板 1 1 の他方の面において、側辺とは異なる位置に接続電極 2 1 が設けられることとしてもよい。

【0019】

また、配線基板 1 1 上の DDR - SDRAM 1 4 が配置される位置には、テスト用の複数の接続端子 2 4 (テスト端子) が設けられている。この接続端子 2 4 は、DDR - SDRAM 1 4 が配線基板 1 1 に接続された状態では表面から見えない状態となっており、DDR - SDRAM 1 4 が配線基板 1 1 に接続されていない状態において、デジタル放送 L S I 1 2 やフラッシュメモリ 1 3 の動作テスト用の端子として用いられる。なお、本実施形態においては、DDR - SDRAM 1 4 の裏側に接続端子 2 4 を設けることとしたが、DDR - SDRAM 1 4 が配置されている状態においても利用可能な位置に接続端子 2 4 を設けることも可能である。

【0020】

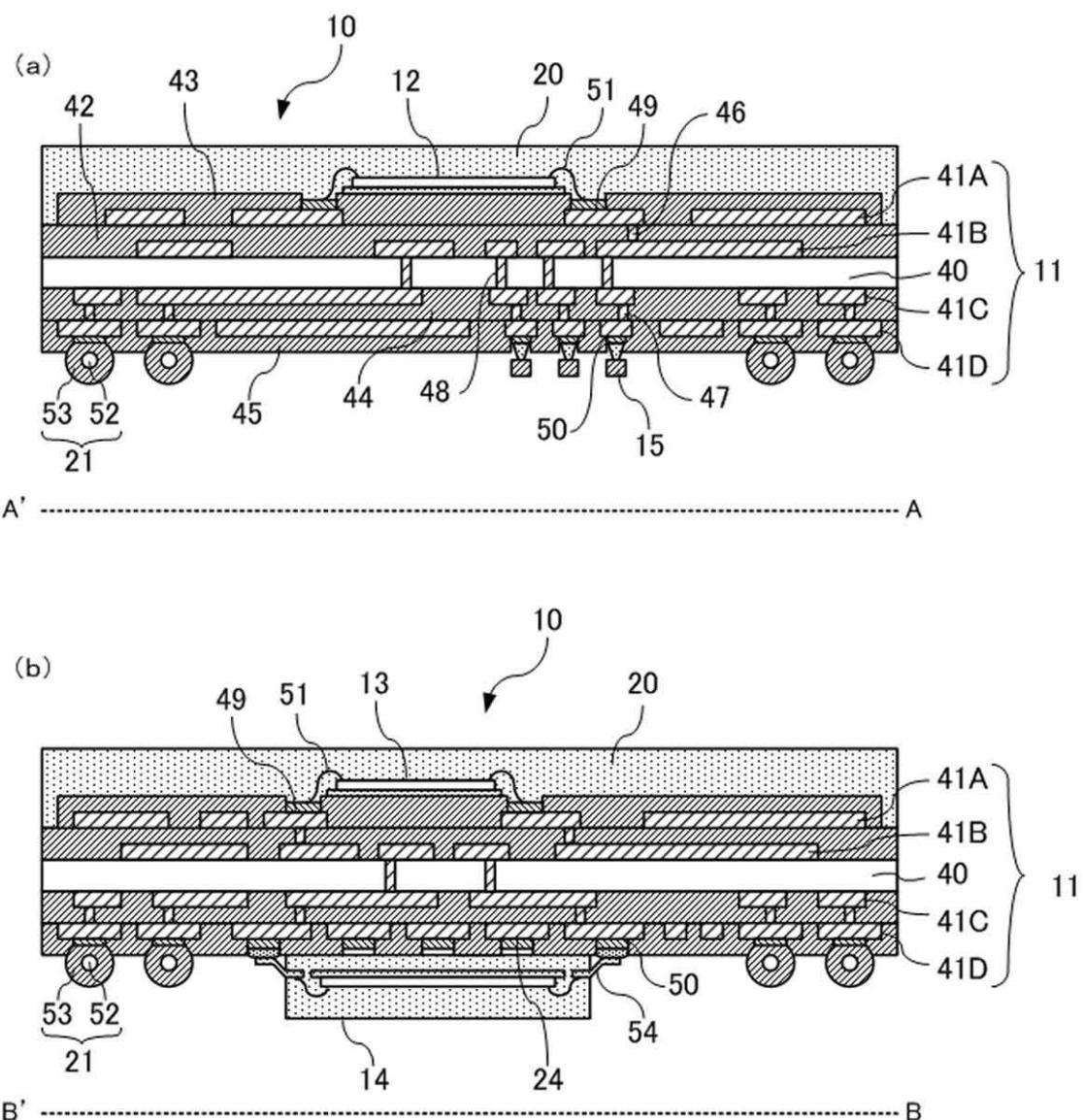

図 2 は、デジタル放送処理装置 1 0 の断面図である。図 2 (a) は、図 1 に示した A - A' 線での断面を示す図であり、図 2 (b) は、図 1 に示した B - B' 線での断面を示す図である。配線基板 1 1 は、基材 4 0 と、基材 4 0 の両面に形成された配線層 4 1 A ~ 4 1 D を含んで構成されている。基材 4 0 には、例えばガラスクロスを重ねたものにエポキシ樹脂を含浸させたガラスエポキシ基板等を用いることができる。そして、基材 4 0 の一方の面側 (図 2 における上面側) には配線層 4 1 B が設けられており、配線層 4 1 B の上には絶縁層 4 2 を介して配線層 4 1 A (第 1 配線層) が積層されている。さらに、配線層 4 1 A は、被膜樹脂 4 3 により覆われている。また、基材 4 0 の他方の面側 (図 2 における下面側) には配線層 4 1 C が設けられており、配線層 4 1 C の下側には絶縁層 4 4 を介して配線層 4 1 D が積層されている。さらに、配線層 4 1 D は、被膜樹脂 4 5 により覆われている。また、接続電極 2 1 は、半田ボール等により形成されている。なお、本実施形

10

20

30

40

50

態では配線基板 11 が 4 層であることとしたが、配線基板 11 の層数はこれに限られず 2 層以上であれば良い。

【0021】

図 2 (a) に示すように、配線層 41A, 41B は、絶縁層 42 を貫通する接続部 46 を介して所定の位置で電気的に接続されている。また、配線層 41C, 41D は、絶縁層 44 を貫通する接続部 47 により所定の位置で電気的に接続されている。さらに、配線層 41B, 41C は、基材 40 を貫通する接続部 48 により電気的に接続されている。

【0022】

また、配線層 41A の一部は電気的接続領域であるパッド 49 となっており、パッド 49 は被覆樹脂 43 により覆われておらず、例えば金メッキ処理等がなされている。同様に、配線層 41D の一部は電気的接続領域であるパッド 50 となっており、パッド 50 は被覆樹脂 45 により覆われておらず、例えば金メッキ処理等がなされている。そして、図 2 (a) に示すように、ペアチップであるデジタル放送 LSI 12 の端子は、金属細線 51 を介してパッド 49 と接続されている。また、バイパスコンデンサであるチップ素子 15 の端子は、半田等の導電性接着剤を介してパッド 50 と接続されている。そして、図 2 (b) に示すように、ペアチップであるフラッシュメモリ 13 の端子は、金属細線 51 を介してパッド 49 と接続されている。また、パッケージである DDR-SDRAM 14 は、端子と接続されたリード 54 が半田等の導電性接着剤を介してパッド 50 と接続されている。

10

【0023】

また、図 2 (a) 及び図 2 (b) に示すように、配線層 41D の両側辺には、2 つのパッド 50 が設けられており、各パッド 50 に接続電極 21 が接続されている。接続電極 21 は、中心部には樹脂により形成されたコア 52 を有し、コア 52 の外周には導電性金属層及び半田層からなる導電部材 53 を有しており、略球状に形成されている。そして、図 2 (b) からわかるように、接続電極 21 の配線基板 11 の他方の面から突出する高さは、DDR-SDRAM 14 の配線基板 11 の他方の面から突出する高さより低くなっている。つまり、接続電極 21 は DDR-SDRAM 14 の厚みと比較して小さいものとなっており、配線基板 11 上における 1 つの接続電極 21 の配設に必要となる面積を小さくすることができる。換言すると、接続電極 21 の高さを DDR-SDRAM 14 の厚みより大きくする場合と比較して、配線基板 11 の面積を広げることなく、より多くの接続電極 21 を配設することができる。

20

【0024】

また、図 2 (a) に示すように、バイパスコンデンサであるチップ素子 15 は、デジタル放送 LSI 12 の端子のほぼ直下に配置されている。そして、デジタル放送 LSI 12 の端子（電源端子）からバイパスコンデンサであるチップ素子 15 の端子までの配線においては、各層 41A ~ 41D での配線の長さが非常に短くなっていることがわかる。したがって、デジタル放送 LSI 12 の電源端子からバイパスコンデンサであるチップ素子 15 の端子までの配線の長さも非常に短くなっている。例えば、デジタル放送 LSI 12 の他の端子から DDR-SDRAM 14 の端子までの配線よりも短くなっている。

30

【0025】

つまり、デジタル放送 LSI 12 の端子間隔が狭い場合であっても、バイパスコンデンサであるチップ素子 15 をデジタル放送 LSI 12 の端子のほぼ直下に配置することにより、デジタル放送 LSI 12 の電源端子からバイパスコンデンサであるチップ素子 15 の端子までの距離を短くすることができる。そして、デジタル放送 LSI 12 の電源端子からバイパスコンデンサであるチップ素子 15 の端子までの配線の長さを短くすることにより、電源ノイズの影響を効果的に抑制することが可能となる。

40

【0026】

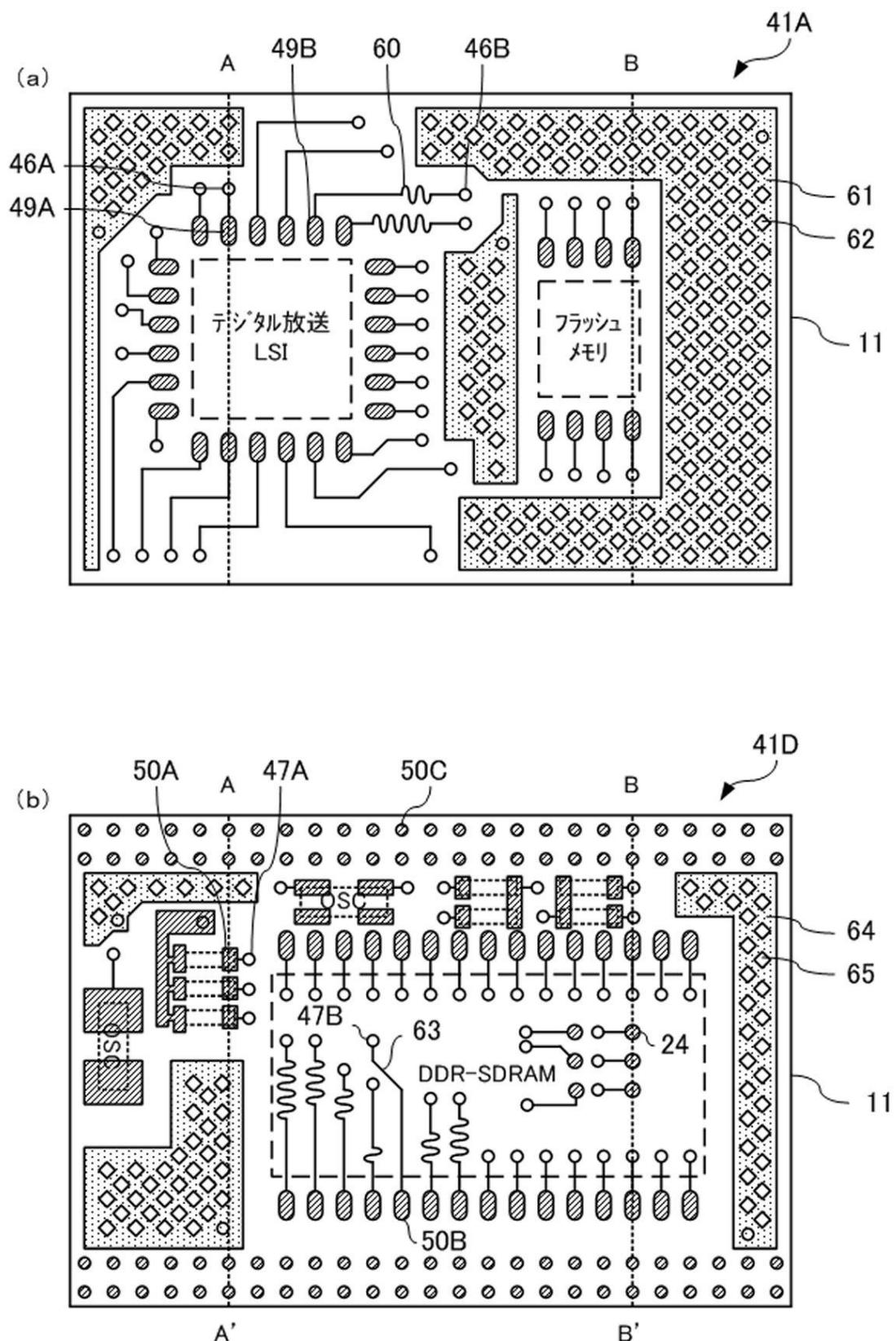

図 3 は、デジタル放送処理装置 10 における配線パターンを示す図である。図 3 (a) は、配線層 41A の配線パターンを封止樹脂 20 が設けられた側から見た図である。また、図 3 (b) は、配線層 41D の配線パターンを封止樹脂 20 が設けられた側から見た図

50

である。

【0027】

図3(a)に示すように、配線層41Aは、前述した接続部46(46A, 46B等)及びパッド49(49A, 49B等)に加え、配線60及び導電パターン61を形成している。配線60は、パッド49と接続部46との間、または、複数の接続部46の間等を接続するためのものである。導電パターン61は、例えば電源電位や接地電位等の所定電位に接続されており、デジタル放送処理装置10において発生するノイズを吸収するシールド層を形成している。また、導電パターン61が形成されることにより、放熱性に優れる銅等により構成される配線層41Aの面積が大きくなり、デジタル放送処理装置10における放熱性能が向上することとなる。さらに、導電パターン61が例えば菱形に除去されることにより、複数の除去部62が設けられている。この除去部62は、導電パターン61の全域にほぼ等間隔に設けられている。導電パターン61上に除去部62が形成されることにより、配線層41Aを覆う被覆樹脂43の厚みを均一にすることができる。また、除去部62を設けることにより、はんだリフロー等の加熱時に、配線基板11に含まれる水分の圧力でデラミネーションと呼ばれる層間剥離現象が発生することを抑制することができる。同様に、図3(b)に示すように、配線層41Dは、前述した接続端子24、接続部47(47A, 47B等)及びパッド50(50A, 50B, 50C等)に加え、配線63及び導電パターン64を形成している。また、導電パターン64には導電パターン61と同様に除去部65が設けられている。

【0028】

ここで、例えば、配線層41Aのパッド49Aに、デジタル放送LSI12の電源端子が金属細線51を介して接続されることとする。パッド49Aは、配線60を介して接続部46Aと接続され、配線層41B, 41Cを介して配線層41Dの接続部47Aと接続される。配線層41Dの接続部47Aは配線63を介してパッド50Aに接続されている。そして、バイパスコンデンサであるチップ素子15の一方の端子がパッド50Aと接続されることにより、デジタル放送LSI12の電源端子とバイパスコンデンサであるチップ素子15の一方の端子とが電気的に接続されることとなる。前述したように、バイパスコンデンサであるチップ素子15の一方の端子が接続されるパッド50Aは、デジタル放送LSI12の電源端子が接続されるパッド49Aのほぼ直下に設けられているため、パッド49Aからパッド50Aまでの配線の長さを短くすることが可能となり、電源ノイズの影響を効果的に抑制することができる。

【0029】

また、例えば、配線層41Aのパッド49Bに、デジタル放送LSI12のデータ入出力端子の一つが金属細線51を介して接続されることとする。パッド49Bは、配線60を介して接続部46Bと接続され、配線層41B, 41Cを介して配線層41Dの接続部47Bと接続される。配線層41Dの接続部47Bは配線63を介してパッド50Bに接続されている。そして、DDR-SDRAM14のデータ入出力端子の一つがパッド50Bと接続されることにより、デジタル放送LSI12のデータ入出力端子の一つとDDR-SDRAM14のデータ入出力端子の一つとが電気的に接続されることとなる。ここで、DDR-SDRAM14を用いる場合、スキューの発生を抑制するために、データ及びストローブ信号を送受信する配線の長さを等しくすることがJEDEC(Joint Electron Device Engineering Council)標準として要求されている。そこで、デジタル放送処理装置10では、デジタル放送LSI12のデータ及びストローブ信号の入出力端子と、DDR-SDRAM14のデータ及びストローブ信号の入出力端子とを接続する複数の配線の長さが等しくなるように、配線層41A～41Dの配線が形成されている。例えば、配線層41Aの配線60や配線層41Dの配線63、配線層41B, 41Cの配線をミアンダーパターン(蛇行形状)とすること等により、等配線長が実現されている。

【0030】

また、配線層41Dの対向する2つの側辺(図3(b)における上下の側辺)には、接続電極21の数に応じた複数のパッド50Cが設けられている。そして、パッド50Cに

10

20

30

40

50

接続された接続電極 21 は、配線層 41A ~ 41D に設けられた配線を介してデジタル放送 LSI 12 やフラッシュメモリ 13、DDR - SDRAM 14 等と接続される。

【0031】

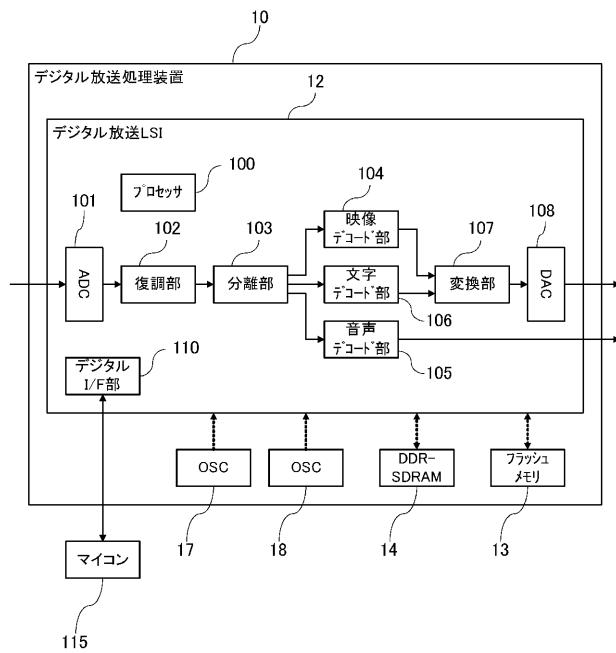

図4は、デジタル放送 LSI 12 の構成を示すブロック図である。デジタル放送 LSI 12 は、プロセッサ 100、ADC コンバータ (ADC) 101、復調部 102、分離部 103、映像デコード部 104、音声デコード部 105、文字デコード部 106、変換部 107、DAC コンバータ (DAC) 108、及びデジタルインターフェース部 (デジタル I/F 部) 110 を備えている。ここで、アナログ信号のインターフェースとなる ADC 101 及び DAC 108 が、本発明のアナログ処理装置に相当し、デジタル信号処理を行う復調部 102、分離部 103、映像デコード部 104、音声デコード部 105、文字デコード部 106、変換部 107、及びデジタル I/F 部 110 が、本発明のデジタル処理装置に相当する。なお、復調部 102、分離部 103、映像デコード部 104、音声デコード部 105、文字デコード部 106、及び変換部 107 は、プロセッサ 100 がフラッシュメモリ 13 に記憶されたプログラムを実行することにより実現することができる。

10

【0032】

ADC 101 には、デジタル放送のチューナーから出力される所望のチャンネルの受信信号が、アナログ信号を入力する接続電極 21 を介して入力される。ADC 101 は、入力される受信信号 (アナログ信号) をデジタル信号に変換して出力する。

20

【0033】

復調部 102 は、水晶発振子 18 で生成される所定周波数のクロックを用いて、ADC 101 から出力されるデジタル信号を、例えば VSB (Vestigial Side Band) 方式や QAM (Quadrature Amplitude Modulation) 方式等に基づいて復調する。また、復調部 102 は、復調されたデジタル信号に対して誤り訂正を行い、例えばトランスポートストリーム形式のデータを生成して出力する。

30

【0034】

分離部 103 は、復調部 102 から出力されるトランスポートストリーム形式等のデータから映像データのパケット、音声データのパケット、文字データのパケットを抽出し、夫々、映像デコード部 104、音声デコード部 105、文字デコード部 106 に出力する。なお、文字データのパケットには、例えば、字幕等を表示するためのクローズドキャプションデータ等が含まれる。

30

【0035】

映像デコード部 104 は、分離部 103 から出力される映像データのパケットに対して、例えば MPEG - 2 (Moving Picture Experts Group phase 2) の復調処理を施し、デジタル映像データとして出力する。

40

音声デコード部 105 は、分離部 103 から出力される音声データのパケットに対して、例えば AAC - 3 (Audio Code number 3) の復調処理を施し、アナログ音声データとして出力する。

文字デコード部 106 は、分離部 105 から出力される文字データから、ディスプレイに表示する文字を示すデジタル映像データを生成して出力する。

【0036】

変換部 107 は、映像デコード部 104 及び文字デコード部 106 から出力されるデジタル映像データを合成することによって映像に文字を重畠した後、例えば NTSC (National Television System Committee) 形式のデジタル映像データに変換して出力する。

【0037】

DAC 108 は、変換部 107 から出力されるデジタル映像データをアナログ映像データに変換し、アナログ信号を出力する接続電極 21 を介して出力する。DAC 108 から出力されるアナログ映像データが NTSC 形式である場合、一般的なアナログ放送受信装置 (アナログテレビ) において行われる処理によって映像を表示することが可能となる。

【0038】

デジタル I/F 部 110 は、外部のマイコン 115 等との間でデジタル信号を送受信す

50

るためのインターフェースである。デジタルI/F 110を介して入出力されるデジタル信号は、例えば、クロック信号や割込信号、シリアル通信であるU A R T (Universal Asynchronous Receiver Transmitter)において送受信される信号等である。これらのデジタル信号は、デジタルI/F部 110を介してプロセッサ 100とマイコン 115との間で送受信され、デジタル放送 L S I 12において行われる様々な処理の制御等に用いられる。

#### 【0039】

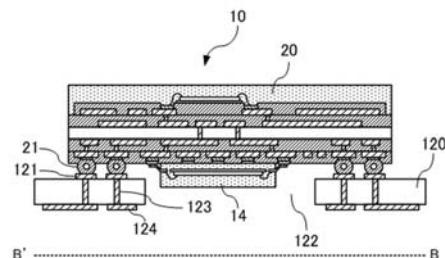

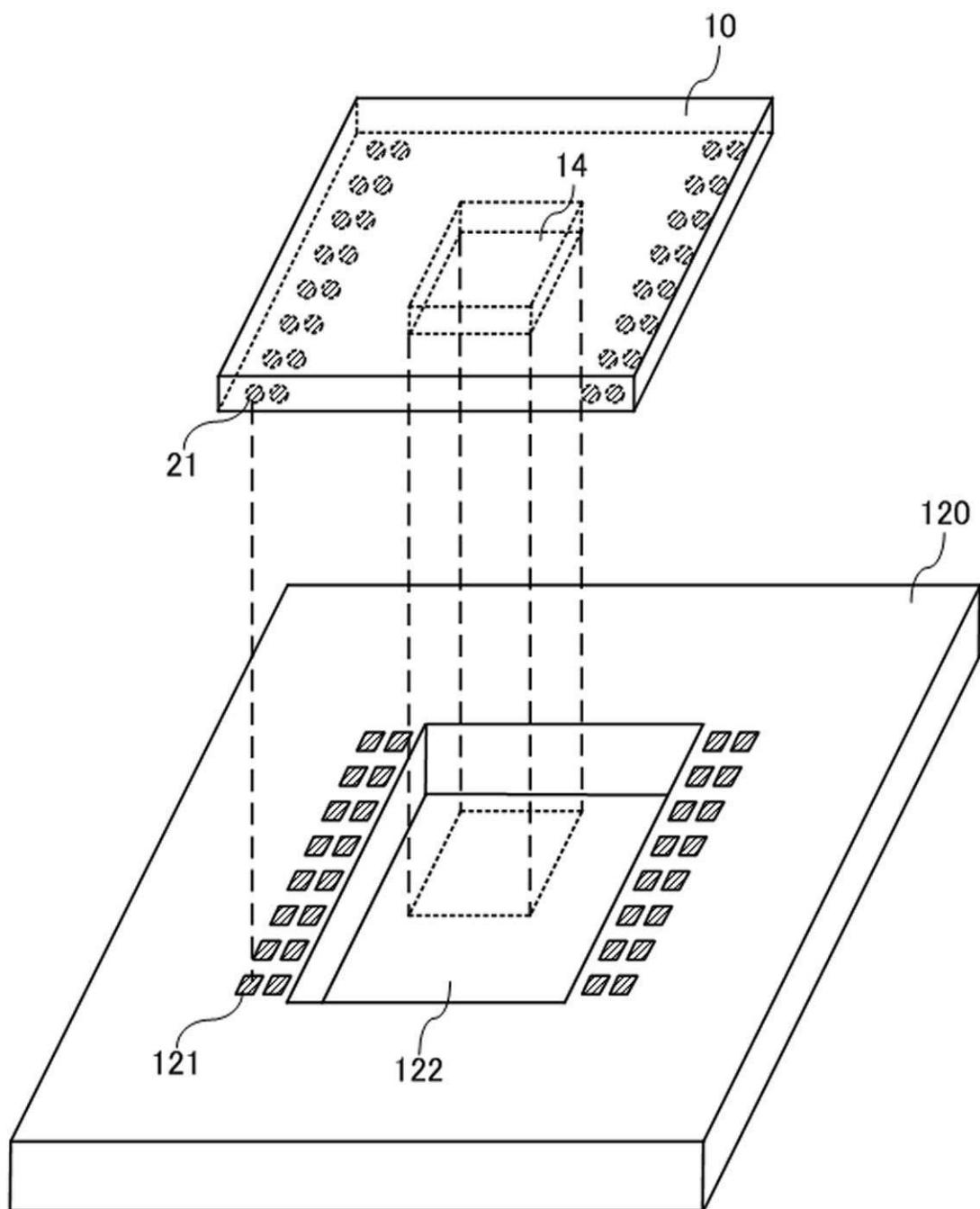

図 5 は、デジタル放送処理装置 10 を他の配線基板に挿入する際の様子を示す斜視図である。配線基板 120 は、少なくとも一方の面に配線層を有しており、配線層の一部により形成される複数の接続部 121 を備えている。また、配線基板 120 の一部には、開口部 122 (切除部) が設けられている。開口部 122 は、幅 (図 5 における左右方向の長さ) が、デジタル放送処理装置 10 の幅よりも狭く、面積が D D R - S D R A M 14 の面積よりも広くなっている。そして、D D R - S D R A M 14 が開口部 122 に挿入され、開口部 122 により形成された空間に収められるとともに、各接続電極 21 が対応する接続部 121 に当接されることにより、デジタル放送処理装置 10 が配線基板 120 に実装される。

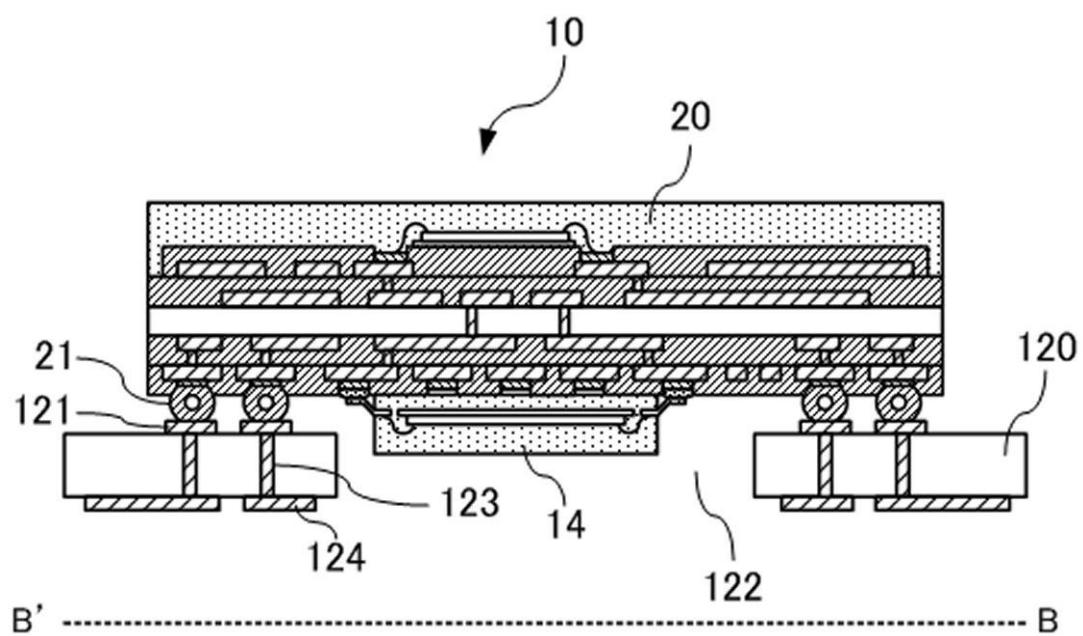

#### 【0040】

図 6 は、デジタル放送処理装置 10 が配線基板 120 と接続された様子を示す断面図である。前述したように、D D R - S D R A M 14 は、配線基板 120 の一部に設けられた開口部 122 に挿入された状態となっている。そして、接続電極 21 は、配線基板 120 の一方の面に設けられた接続部 121 と接続され、接続部 121 は、例えば配線基板 120 を貫通する接続部 123 を介して、配線基板 120 の他方の面に設けられた配線 124 と接続されている。なお、配線基板 120 の両面に配線層が設けられるのではなく、接続電極 21 と接続される面のみに配線層が設けられることとしてもよいし、3層以上の配線層が形成されることとしてもよい。

#### 【0041】

また、本実施形態では、配線基板 120 の開口部 122 に D D R - S D R A M 14 が挿入されることとしたが、デジタル放送処理装置 10 と配線基板 120 との接続態様はこれに限らず、D D R - S D R A M 14 が配線基板 120 の一方の面と干渉しなければよい。例えば、例えば、配線基板 120 の一方の面から他方の面に向かって貫通せずに切除された凹部 (切除部) が設けられ、接続電極 21 が配線基板 120 の接続部 121 に当接された状態において、D D R - S D R A M 14 が凹部に挿入されることによりデジタル放送処理装置 10 と配線基板 120 とが接続されることとしてもよい。また、例えば、配線基板 120 の周囲の一部に切り欠き (切除部) を設け、D D R - S D R A M 14 が切り欠きに挿入されることによりデジタル放送処理装置 10 と配線基板 120 とが接続されることとしてもよい。さらに、配線基板 120 に切除部を設けずに、接続電極 21 が配線基板 120 の接続部 121 と当接されるとともに、D D R - S D R A M 14 が配線基板 120 と干渉しない位置に配設されることとしてもよい。例えば、D D R - S D R A M 14 を配線基板 11 の配線基板 120 と向き合う面の一方の側 (例えば図 6 の右寄り) に配設し、接続電極 21 を他方の側 (例えば図 6 の左寄り) のみに配設し、D D R - S D R A M 14 が配線基板 120 の側辺からみ出るようにデジタル放送処理装置 10 と配線基板 120 とが接続されることとしてもよい。

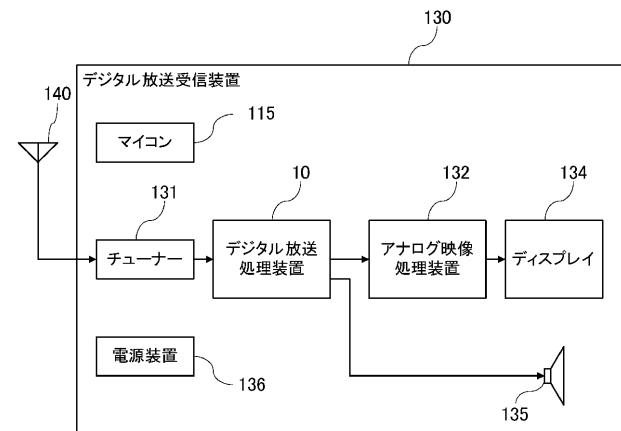

#### 【0042】

次に、本発明のデジタル放送受信装置の一実施形態について説明する。図 7 は、デジタル放送受信装置 130 の構成を示すブロック図である。デジタル放送受信装置 130 は、全体を統括制御するマイコン 115、チューナー 131、デジタル放送処理装置 10、アナログ映像処理装置 132、ディスプレイ 134、スピーカ 135、及び各部に電源を供給する電源装置 136 を含んで構成されている。

#### 【0043】

チューナー 131 は、アンテナ 140 を介して受信されるデジタル放送信号から所望の

10

20

30

40

50

チャンネルの信号を抽出して出力する。チューナー 131 から出力される信号はデジタル放送処理装置 10 に入力され、前述した処理によりアナログ映像データ及びアナログ音声データが出力される。アナログ映像処理装置 132 は、デジタル放送処理装置 10 から出力される例えばNTSC 形式のアナログ映像データに基づいてディスプレイ 134 に映像を出力する。また、デジタル放送処理装置 10 から出力されるアナログ音声データは、スピーカ 135 から音声として出力される。

【0044】

このように、デジタル放送処理装置 10 と、アナログ映像処理装置 132 を組み合わせることにより、デジタル放送を受信可能なデジタル放送受信装置 130 を構成することが可能となる。そして、デジタル放送処理装置 10 では、接続電極 21 の高さが DDR-SDRAM 14 の厚みより低いため、サイズの増大を抑えた上で接続電極 21 の数を増やすことが可能となる。すなわち、デジタル放送受信装置 130 は、入出力されるデータの多いフルスペックハイビジョン等に対応する場合において、接続電極 21 の増加に伴うサイズの増大を抑えることができる。

10

【0045】

以上、本発明の実施形態について説明した。前述したように、デジタル放送処理装置 10 では、接続電極 21 の高さが DDR-SDRAM 14 の厚みより低くなっている、接続電極 21 の配設に必要な面積を小さくすることが可能となる。つまり、接続電極 21 の数の増加に伴うデジタル放送処理装置 10 のサイズ増大を抑制することが可能となる。

20

【0046】

特に、接続電極 21 を半田ボール等の略球状の形状とする場合、柱状とする場合と比較して幅が広くなりやすいが、デジタル放送処理装置 10 では接続電極 21 の高さを低くすることが可能であるため、接続電極 21 の配設に必要な面積が広くなることを抑えることができる。つまり、接続電極 21 を半田ボール等の略球状の形状とする場合であっても、接続電極 21 の数の増加に伴うデジタル放送処理装置 10 のサイズ増大を抑制することが可能となる。

20

【0047】

また、デジタル放送処理装置 10 では、配線基板 11 の対向する 2 つの側辺に接続電極 21 が配設されている。このように配線基板 11 の対向する側辺に接続電極 21 を配設することにより、他の配線基板 120 にデジタル放送処理装置 10 を実装する場合に、デジタル放送処理装置 10 のがたつきを抑え、容易かつ確実に接続することが可能となる。

30

【0048】

また、デジタル放送処理装置 10 では、配線基板 120 が有する切除部（開口部 122）に DDR-SDRAM 14 が挿入された状態で、デジタル放送処理装置 10 と配線基板 120 とが接続されている。これにより、DDR-SDRAM 14 が配線基板 120 の側辺からはみ出さない状態で、デジタル放送処理装置 10 と配線基板 120 とを接続することができるとなり、デジタル放送処理装置 10 が接続された状態における安定度を増すことができる。そして、図 6 に例示したように DDR-SDRAM 14 の少なくとも 2 つの側辺と相対する位置に接続電極 21 が配設されることにより、配線基板 120 にデジタル放送処理装置 10 を実装する場合のがたつきを抑えることができる。なお、本実施形態においては、DDR-SDRAM 14 の対向する 2 つの側辺と相対する位置に接続電極 21 が配設されることとしたが、DDR-SDRAM 14 の隣り合う側辺と相対する位置（例えば図 2 (b) における右側と下側）に接続電極 21 が配設されることとしてもよい。

40

【0049】

また、前述した実施形態は本発明の理解を容易にするためのものであり、本発明を限定して解釈するためのものではない。本発明は、その趣旨を逸脱することなく、変更、改良され得ると共に、本発明にはその等価物も含まれる。

【図面の簡単な説明】

【0050】

【図 1】デジタル放送処理装置の構成を示す平面図である。

50

【図2】デジタル放送処理装置の断面図である。

【図3】デジタル放送処理装置における配線パターンを示す図である。

【図4】デジタル放送LSIの構成を示すブロック図である。

【図5】デジタル放送処理装置を他の配線基板に挿入する際の様子を示す斜視図である。

【図6】デジタル放送受信装置が他の配線基板に接続された様子を示す断面図である。

【図7】デジタル放送受信装置の構成を示すブロック図である。

【図8】SiPを用いて構成された回路装置の構成例を示す図である。

【符号の説明】

【0051】

|           |            |        |               |

|-----------|------------|--------|---------------|

| 10        | デジタル放送処理装置 | 11     | 配線基板          |

| 12        | デジタル放送LSI  | 13     | フラッシュメモリ      |

| 14        | DDR-SDRAM  | 15, 16 | チップ素子         |

| 17, 18    | 水晶発振子      | 20     | 封止樹脂          |

| 21        | 接続電極       | 40     | 基材            |

| 41A ~ 41D | 配線層        | 42, 44 | 絶縁層           |

| 43, 45    | 被覆樹脂       | 46, 47 | 接続部           |

| 49, 50    | パッド        | 51     | 金属細線          |

| 52        | コア         | 53     | 導電部材          |

| 54        | リード        | 60, 63 | 配線            |

| 61, 64    | 導電パターン     | 62, 65 | 切除部           |

| 100       | プロセッサ      | 101    | ADコンバータ       |

| 102       | 復調部        | 103    | 分離部           |

| 104       | 映像デコード部    | 105    | 音声デコード部       |

| 106       | 文字デコード部    | 107    | 変換部           |

| 108       | DAコンバータ    | 110    | デジタルインターフェース部 |

| 115       | マイコン       | 120    | 配線基板          |

| 121, 123  | 接続部        | 122    | 開口部           |

| 124       | 配線         | 130    | デジタル放送受信装置    |

| 131       | チューナー      | 132    | アナログ映像処理装置    |

| 134       | ディスプレイ     | 135    | スピーカ          |

| 136       | 電源装置       | 140    | アンテナ          |

10

20

30

【図4】

【図7】

【図8】

【図1】

【図2】

【図3】

【図5】

【図6】

---

フロントページの続き

F ターム(参考) 5E336 AA04 AA08 AA16 BC26 BC34 CC32 CC55 EE03 GG30

5E344 AA04 AA22 AA26 AA28 BB02 BB06 CC05 CC13 CC23 DD03

EE12