(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2018년05월31일

(11) 등록번호 10-1863354

(24) 등록일자 2018년05월25일

(51) 국제특허분류(Int. Cl.)

H01L 21/336 (2006.01) H01L 29/78 (2006.01)

(21) 출원번호 10-2012-0057680

(22) 출원일자 2012년05월30일

심사청구일자 2016년07월19일

(65) 공개번호 10-2012-0135473

(43) 공개일자 2012년12월14일

(30) 우선권주장

13/359,385 2012년01월26일 미국(US)

61/492,207 2011년06월01일 미국(US)

(56) 선행기술조사문현

JP08340104 A

US20100127335 A1

JP2000031296 A

(73) 특허권자

에이에스엠 아이피 홀딩 비.브이.

네덜란드 에이피 알메르 1322 베르스테르케르스트라아트 8

(72) 발명자

맥카우트산 블라디미르

벨기에 루뱅 3000 프레디커렌스트라아트 10 버스 6

마에스 얀 빌렘

벨기에 빌릭 2610 에벨렌프리엘 5

시에 치

네덜란드 알메르 1322 에이피 베르스테르케르스트라아트 8

(74) 대리인

리엔목특허법인

전체 청구항 수 : 총 16 항

심사관 : 김종호

(54) 발명의 명칭 높은 유효 일함수를 갖는 전극 퇴적 프로세스

**(57) 요 약**

일부 실시예들에 따르면, 높은 유효 일함수를 갖는 전극이 형성된다. 전극은 트랜지스터의 게이트 전극일 수 있고, 도전성 물질의 제1 층을 퇴적하는 단계, 수소-함유 가스에 제1 층을 노출시키는 단계, 및 제1 층 상으로 도전성 물질의 제2 층을 퇴적하는 단계에 의해 하이-k 게이트 유전체 상에 형성될 수 있다. 제1 층은 기판이 플라즈마 또는 플라즈마-생성된 래디칼들에 노출되지 않는 비-플라즈마 공정을 사용하여 퇴적될 수 있다. 제1 층이 노출되는 수소-함유 가스는 여기된 수소 종들을 포함할 수 있고, 이는 수소-함유 플라즈마의 일부일 수 있으며, 수소-함유 래디칼들일 수 있다. 또한, 제1 층은 제2 층을 퇴적하기 전에 산소에도 노출될 수 있다. 일부 실시예들에서 게이트 스택 내 게이트 전극의 일함수는 약 5 eV 이상일 수 있다.

**대 표 도** - 도1a

선 HiK+MG 플로우

## 명세서

### 청구범위

#### 청구항 1

기판 상으로 제1 층 및 제2 층을 포함하는 게이트 전극을 형성하는 단계를 포함하고,

상기 게이트 전극을 형성하는 단계는,

반응 챔버 내로, 게이트 유전체를 포함하는 상기 기판을 제공하는 단계;

상기 게이트 유전체 상에 전이 금속 화합물을 포함하는 상기 제1 층을 퇴적하는 단계로서, 상기 제1 층의 퇴적은 플라즈마 또는 플라즈마에 의해서 생성된 래디컬들에 상기 기판을 노출시키지 않고 수행되는, 단계;

상기 제1 층을 여기된 수소가 함유된 종들에 노출시킴으로써, 상기 게이트 전극의 일함수를 증가시키는 단계로서, 상기 여기된 수소가 함유된 종들을 생성하기 위한 플라즈마를 생성하는 피크 투 피크 전압( $V_{pp}$ )은 110V 이상인, 단계; 및

후속하여 전이 금속 화합물을 포함하는 상기 제2 층을 퇴적하는 단계를 포함하고,

상기 제1 층을 퇴적하는 단계 및 후속하여 상기 제2 층을 퇴적하는 단계 사이에,

산소 플라즈마는 상기 반응 챔버에 유동되지 않고 산소 가스는 상기 반응 챔버에 유동되지 않는 것을 특징으로 하는 반도체 처리 공정.

#### 청구항 2

제1항에 있어서,

상기 제1 층을 상기 여기된 수소가 함유된 종들에 노출시키는 단계는,

- 수소가 함유된 가스 및 적어도 하나의 비활성 캐리어 가스를 갖는 수소가 함유된 가스로 구성된 그룹으로부터 선택된 가스를 상기 반응 챔버로 유동하고, 상기 가스로 상기 반응 챔버 내부에 인 시튜(in-situ) 플라즈마를 형성하는 단계; 또는

- 수소가 함유된 가스 및 적어도 하나의 비활성 캐리어 가스를 갖는 수소가 함유된 가스로 구성된 그룹으로부터 선택된 가스를 원격 플라즈마 생성기로 유동하여 원격 플라즈마를 형성하고, 상기 원격 플라즈마를 상기 반응 챔버로 유동하는 단계를 포함하는 것을 특징으로 하는 반도체 처리 공정.

#### 청구항 3

제1항에 있어서,

상기 게이트 전극 및 상기 게이트 유전체는 게이트 스택을 구성하고,

상기 게이트 스택 내 상기 게이트 전극의 일함수는 4.85 eV 이상인 것을 특징으로 하는 반도체 처리 공정.

#### 청구항 4

제1항에 있어서,

상기 여기된 수소가 함유된 종들을 생성하기 위한 플라즈마 전력은 175 W 이상인 것을 특징으로 하는 반도체 처리 공정.

#### 청구항 5

제1항에 있어서,

상기 여기된 수소가 함유된 종들을 생성하기 위한 플라즈마 전력은 2초 이상의 펄스들로 인가되는 것을 특징으로 하는 반도체 처리 공정.

## 청구항 6

제1항에 있어서,

상기 제1 층을 상기 여기된 수소가 함유된 종들로 노출시키는 것은, 상기 제2 층의 퇴적 이전에 플라즈마 인핸스드 원자층 증착(PEALD)에 의해 상기 제1 층 상에 막을 퇴적하는 것의 일부인 것을 특징으로 하는 반도체 처리 공정.

## 청구항 7

제6항에 있어서,

플라즈마 인핸스드 원자층 증착(PEALD)에 의해 퇴적된 상기 막은 탄탈륨 함유 막인 것을 특징으로 하는 반도체 처리 공정.

## 청구항 8

제1항에 있어서,

상기 제1 층은 원자층 증착에 의해 퇴적되는 것을 특징으로 하는 반도체 처리 공정.

## 청구항 9

제8항에 있어서,

상기 제2 층은 플라즈마 인핸스드 원자층 증착(PEALD)에 의해 퇴적되는 것을 특징으로 하는 반도체 처리 공정.

## 청구항 10

제1항에 있어서,

- a) 상기 제1 층을 퇴적하는 단계와 상기 제1 층을 상기 여기된 수소가 함유된 종들에 노출시키는 단계 사이에,

- b) 상기 제1 층을 상기 여기된 수소가 함유된 종들에 노출시키는 단계와 상기 제2 층을 퇴적하는 단계 사이에,

- 또는 c) 상기 제1 층을 퇴적하는 단계와 상기 제1 층을 상기 여기된 수소가 함유된 종들에 노출시키는 단계 사이에 그리고 상기 제1 층을 상기 여기된 수소가 함유된 종들에 노출시키는 단계와 상기 제2 층을 퇴적하는 단계 사이에, 상기 기판을 상기 반응 챔버 외부에서 산소-함유 가스에 노출시키는 단계를 더 포함하는 반도체 처리 공정.

## 청구항 11

제10항에 있어서,

상기 기판을 상기 산소-함유 가스에 노출시키는 단계는,

상기 기판을 상기 반응 챔버로부터 언로딩하는 단계; 및

상기 기판을 클린룸 에어(cleanroom air)에 노출시키는 단계를 포함하는 것을 특징으로 하는 반도체 처리 공정.

## 청구항 12

제1항에 있어서,

상기 제1 및 제2 층들 중 적어도 하나는 복수의 서브 물질층들을 포함하는 박층(laminate layer)인 것을 특징으로 하는 반도체 처리 공정.

## 청구항 13

금속성 전극을 유전층을 포함하는 기판 상에 퇴적하는 단계를 포함하고,

상기 금속성 전극을 퇴적하는 단계는,

상기 유전층 상에 금속성 물질을 퇴적하는 단계로서, 상기 금속성 물질을 퇴적하기 위한 전구체들은 플라즈마로 활성화되지 않은 것을 특징으로 하는 단계;

상기 금속성 물질을 여기된 수소가 함유된 종들에 노출시킴으로써, 상기 금속성 전극의 일함수를 증가시키는 단계로서, 상기 여기된 수소가 함유된 종들을 생성하기 위한 플라즈마를 생성하는 플라즈마 전력은 175 W 이상인, 단계; 및

상기 금속성 물질을 노출시키는 단계 이후, 이어서 상기 금속성 물질 상에 추가 금속성 물질을 퇴적하는 단계를 포함하고,

상기 금속성 물질을 퇴적하는 단계 및 후속하여 상기 추가 금속성 물질을 퇴적하는 단계 사이에, 산소 플라즈마는 반응 챔버에 유동되지 않고 산소 가스는 상기 반응 챔버에 유동되지 않는 것을 특징으로 하는 반도체 처리 공정.

#### 청구항 14

제13항에 있어서,

상기 금속성 물질을 상기 여기된 수소가 함유된 종들에 노출시키는 단계는,

- a) 수소가 함유된 가스 및 적어도 하나의 비활성 캐리어 가스를 갖는 수소가 함유된 가스로 구성된 그룹으로부터 선택된 가스를 상기 기판을 갖는 반응 챔버로 유동하고, 상기 가스로 상기 반응 챔버 내부에 인 시튜(*in-situ*) 플라즈마를 형성하는 단계; 또는

- b) 수소가 함유된 가스 및 적어도 하나의 비활성 캐리어 가스를 갖는 수소가 함유된 가스로 구성된 그룹으로부터 선택된 가스를 원격 플라즈마 생성기로 유동하여 원격 플라즈마를 형성하고, 상기 원격 플라즈마를 상기 기판을 갖는 반응 챔버로 유동하는 단계를 포함하는 것을 특징으로 하는 반도체 처리 공정.

#### 청구항 15

제13항에 있어서,

상기 여기된 수소가 함유된 종들을 생성하기 위한 플라즈마를 생성하는 피크 투 피크 전압( $V_{pp}$ )은 110V 이상이고, 상기 여기된 수소가 함유된 종들을 생성하기 위한 플라즈마 전력은 2초 이상의 필스들로 인가되는 것을 특징으로 하는 반도체 처리 공정.

#### 청구항 16

제13항에 있어서,

상기 금속성 전극은 게이트 스택의 일부를 구성하고,

상기 게이트 스택 내 상기 금속성 전극의 일함수는, 상기 금속성 물질을 상기 여기된 수소가 함유된 종들에 노출시키는 단계 없이 동일한 공정을 수행하는 경우에 비하여 0.2 eV 이상 증가된 것을 특징으로 하는 반도체 처리 공정.

#### 청구항 17

삭제

#### 청구항 18

삭제

#### 청구항 19

삭제

#### 청구항 20

삭제

#### 청구항 21

삭제

청구항 22

삭제

청구항 23

삭제

청구항 24

삭제

청구항 25

삭제

청구항 26

삭제

청구항 27

삭제

청구항 28

삭제

청구항 29

삭제

청구항 30

삭제

청구항 31

삭제

청구항 32

삭제

청구항 33

삭제

청구항 34

삭제

청구항 35

삭제

### 발명의 설명

### 기술 분야

[0001] 본 공개서는 반도체 공정 분야에 관한 것으로서, 더욱 구체적으로는, 금속 게이트 전극과 같은, 트랜지스터들의 게이트 스택들 내 금속 게이트 전극들을 포함하는 도전성 구조물들의 퇴적에 관한 것이다.

## 배경 기술

[0002]

증가된 컴퓨팅 전력 및 감소된 집적 회로 크기들의 지속적인 요구 때문에, 집적 회로들을 형성하는 전자 장치들의 크기들을 감소시키고자 하는 지속적인 요구 또한 존재한다. 예를 들어, 트랜지스터들의 크기들은, 예를 들어 집적 회로 내 트랜지스터들의 밀도를 증가시키기 위해, 컴퓨팅 전력을 증가시키기 위해 지속적으로 감소된다. 트랜지스터들이 소형화됨에 따라, 상기 트랜지스터들의 채널 영역들로부터 상기 트랜지스터들의 게이트 전극들을 분리시키는 게이트 유전층들과 같은, 트랜지스터들의 구성 요소들도 또한 소형화된다. 박막 게이트 유전층들은 게이트 유전층을 통한 원치 않는 전류 누설을 방지하기 위해 전형적으로 고유전율(하이- $k$ (high- $k$ )) 물질들의 사용을 요구한다. 그러나, 이러한 하이- $k$  물질들을 갖는 트랜지스터들은, 일부 종래의 실리콘-기반의 게이트 전극 물질들과 함께 사용되는 경우 조악한 성능 특성을 갖는다. 따라서, 트랜지스터와 같은 전자 장치들 내에서 하이- $k$  게이트 유전 물질들과 함께 사용되기에 적합한, 도전성 게이트 전극들과 같은 도전성 전극들에 대한 지속적인 요구가 존재한다.

## 발명의 내용

### 해결하려는 과제

[0003]

본 발명이 해결하려는 과제는, 트랜지스터와 같은 전자 장치들 내에서 하이- $k$  게이트 유전 물질들과 함께 사용되기에 적합한, 도전성 게이트 전극들과 같은 도전성 전극의 퇴적 방법을 제공하는 것이다.

### 과제의 해결 수단

[0004]

일부 실시예들에 따르면, 반도체 처리 공정이 제공된다. 상기 프로세스는 기판 상으로 게이트 전극을 형성하는 단계를 포함한다. 상기 게이트 전극을 형성하는 단계는 반응 챔버 내로 상기 기판을 제공하는 단계를 포함하며, 상기 기판은 게이트 유전체를 갖는다. 전이 금속 화합물을 포함하는 제1 층이 상기 게이트 유전체 상에 퇴적되며, 상기 퇴적 동안 플라즈마 또는 플라즈마-생성된 래디컬들에 상기 기판을 노출시키지 않는다. 이후, 상기 제1 층은 수소-함유 가스에 노출된다. 이후, 전이 금속 화합물을 포함하는 제2 층이 퇴적된다.

[0005]

다른 일부 실시예들에서, 반도체 처리 공정이 제공된다. 상기 공정은 금속성 전극을 퇴적하는 단계를 포함한다. 상기 금속성 전극을 퇴적하는 단계는 게이트 유전층 상에 금속성 물질을 퇴적하는 단계를 포함한다. 상기 금속성 물질을 퇴적하기 위한 전구체들은 플라즈마-활성화되지 않는다. 상기 금속성 물질은 여기된 수소-함유 종들에 노출된다. 이어서 상기 금속성 물질을 상기 여기된 수소-함유 종들에 노출시키는 단계 이후 추가 금속성 물질이 상기 금속성 물질 상에 퇴적된다.

## 발명의 효과

[0006]

본 발명의 기술적 사상에 의한 실시예들에 따른 프로세스는, 금속 전극 또는 상기 금속 전극을 포함하는 게이트 스택에 대한 공격적인 어닐 없이도 상기 금속 전극 또는 상기 게이트 스택의 유효 일함수를 증가시킬 수 있다. 또한, 공정 파라미터 등을 변화시킴으로써 상기 유효 일함수가 조절될 수 있다.

## 도면의 간단한 설명

[0007]

본 발명의 비-제한적이고 비-포괄적인 실시예들이 이하의 도면들을 참조하여 설명되며, 전 부분에 걸쳐 유사한 부재 번호들은 유사한 부분들을 지칭한다.

도 1a 내지 도 1c는 금속 게이트 전극들을 형성하기 위한 다양한 공정 플로우들의 예들을 나타낸다.

도 2는 도전성 물질을 퇴적하기 위한 다양한 공정 시퀀스들의 예들을 나타낸다.

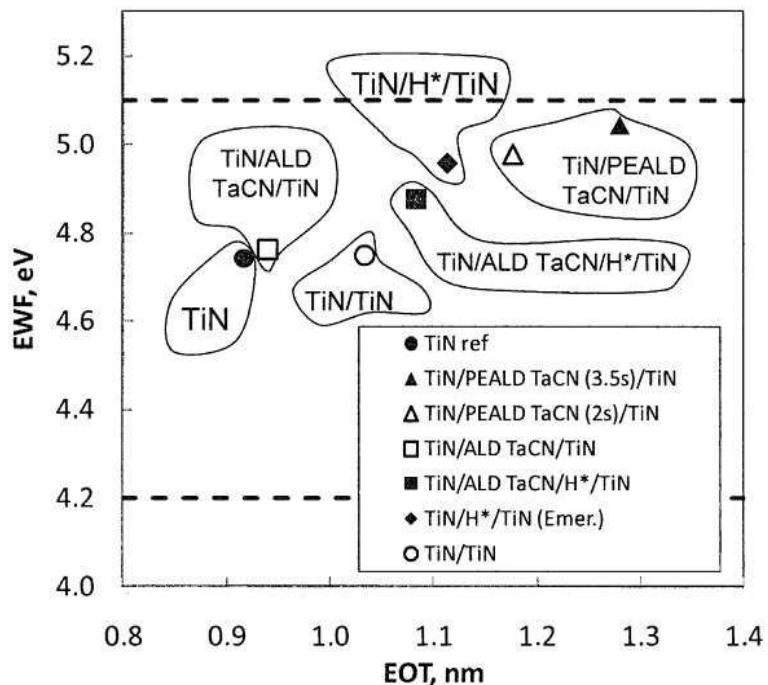

도 3은 도 2에 나타난 시퀀스들의 결과들을 그래프로 나타낸 예이다.

도 4는 도전성 물질을 퇴적하기 위한 공정 시퀀스들의 추가적인 예들을 나타낸다.

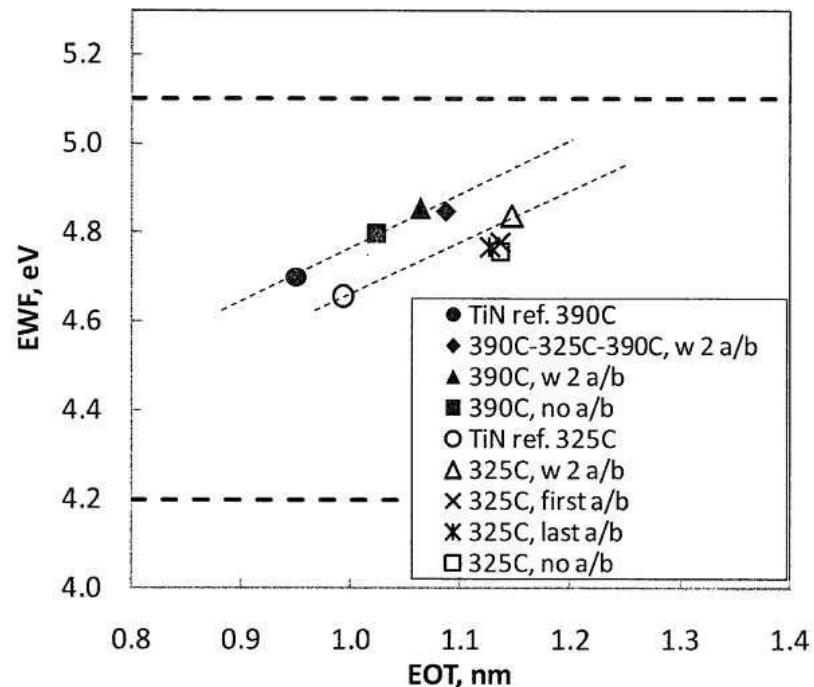

도 5는 도 4에 나타난 시퀀스들의 결과들을 그래프로 나타낸 예이다.

도 6은 도 2 및 도 4의 공정 시퀀스들에 대한 일부 조건들을 나타낸다.

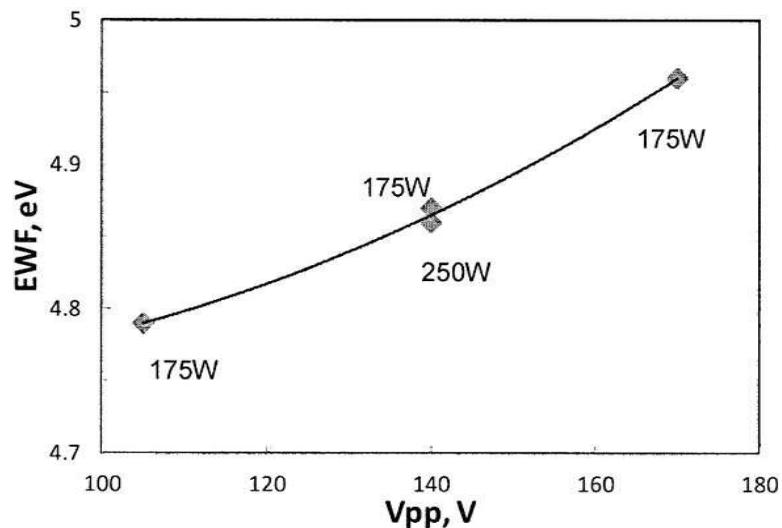

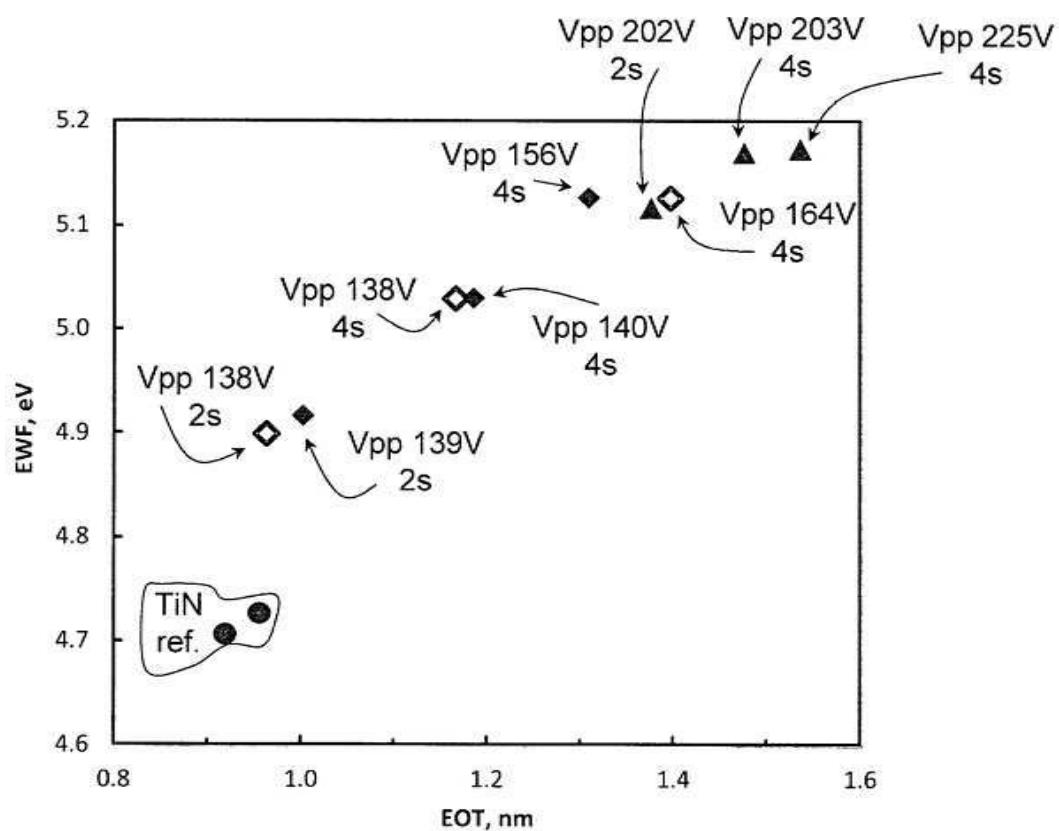

도 7은 여기된 수소-함유 종들을 생성하기 위한 피크-투-피크 전압의 변화에 따른 유효 일함수의 변화들을 그래프로 나타낸 예이다.

도 8은 여기된 수소-함유 종들의 각각의 펠스를 생성하기 위해 인가된 전력의 지속 기간의 변화들과 함께 여기된 수소-함유 종들을 생성하기 위한 피크-투-피크 전압이 변화함에 따른 유효 일함수의 변화들을 그래프로 나타낸 예이다.

도 9a 내지 도 12는 게이트 전극 스택들의 개략적인 단면도들의 예들을 나타낸다.

### 발명을 실시하기 위한 구체적인 내용

[0008]

일부 실시예들에 따르면, 도전성 구조물은, 도전성 물질의 제1 층을 퇴적하고, (가스-유사 상태에서 수소-함유 종들을 포함하는) 수소-함유 가스에 제1 층을 노출시키며, 상기 제1 층 상으로 도전 물질의 제2 층을 퇴적함으로써, 기판 상에 형성된다. 일부 실시예들에서, 상기 도전성 구조물은 유전층 상에 형성된다. 예를 들어, 상기 도전성 구조물은, 트랜지스터의 부분으로서, 예를 들어 하이-k 게이트 유전체와 같은 게이트 유전체 상에 형성된 게이트 전극일 수 있다. 상기 제1 층은, 기판이 플라즈마 또는 플라즈마-생성된 래디컬들(즉, 플라즈마에 의해 생성된 래디컬들)에 노출되지 않는, 비-플라즈마 또는 비-래디컬(radical) 공정을 사용하여 퇴적될 수 있다. 이후, 상기 제1 층은 수소-함유 종들에 노출된다. 일부 실시예들에서, 상기 수소-함유 종들은 여기된 (excited) 수소-함유 종들일 수 있고, 이는 수소-함유 플라즈마의 일부일 수 있다. 일부 실시예들에서, 수소-함유 종들은, 원격 플라즈마 생성기에서 생성되고 이후 상기 제1 층을 포함하는 반응 챔버(reaction chamber)내로 유입될 수 있는 수소-함유 래디컬들을 포함한다.

[0009]

바람직하게는, 도전 물질이 트랜지스터 내 금속 게이트를 형성하는데 사용되는 경우에 있어서, 게이트 스택 내 게이트 전극의 일함수는 약 4.85 eV 이상 또는 약 5 eV 이상일 수 있다. 일부 실시예들에서, 상기 제1 층의 두께는 약 5 nm 미만, 약 4 nm 미만, 약 3 nm 미만, 또는 약 1-3 nm일 수 있다. 바람직하게는, 상기 제1 층은 그 것을 형성하는 물질의 단일층보다 두껍다.

[0010]

일부 실시예들에서, 비-플라즈마 공정에 의해 상기 제1 층을 형성하는 것뿐만 아니라, 제2 층도, 기판이 플라즈마 또는 플라즈마-생성된 래디컬들에 노출되지 않는 비-플라즈마 공정에 의해 형성될 수 있다. 일부 실시예들에서, 상기 제2 층은 플라즈마 또는 래디컬들에 노출됨으로써 형성될 수 있다.

[0011]

도전성 구조물을 형성하는 도전성 물질은 전이 금속 화합물과 같은 금속성 물질일 수 있다. 본 발명을 한정하지 않는 예로서, 상기 전이 금속은 티타늄, 탄탈륨, 니오븀(niobium), 몰리브데늄(molybdenum), 하프늄, 지르코늄, 및 텉스텐과 같은 내열성 금속일 수 있다. 일부 실시예들에서, 도전성 물질은 금속을 질화시킴으로써 형성된 질화물일 수 있다. 일부 실시예들에서, 예를 들어, 탄소와 같은 다른 원소들이 상기 도전성 물질 내로 포함될 수 있고, 그에 따라 상기 도전성 물질은 금속 카바이드(metal carbide), 또는 금속 카보나이트라이드(metal carbonitride)일 수 있다. 그러한 금속들의 비-한정적인 예들은 탄탈륨 나이트라이드, 탄탈륨 카바이드, 탄탈륨 카보나이트라이드, 티타늄 나이트라이드, 티타늄 카바이드, 및 티타늄 카보나이트라이드를 포함한다. 물질들의 다른 비-한정적인 예들은 니오븀 나이트라이드, 니오븀 카바이드, 니오븀 카보나이트라이드, 몰리브데늄 나이트라이드, 몰리브데늄 카바이드, 몰리브데늄 카보나이트라이드, 하프늄 나이트라이드, 지르코늄 나이트라이드, 텉스텐, 및 텉스텐 나이트라이드를 포함한다.

[0012]

또한, 상기 제1 층은, 상기 제2 층의 퇴적 전에, 예를 들어 산소와 같은 다양한 다른 화학 종들에 노출될 수도 있다. 일부 실시예들에서, 1개 이상의 다른 도전 물질 층들이 상기 제1 및 제2 층들 사이에 퇴적될 수 있다.

[0013]

일부 실시예들에서, 금속 게이트들 또는 금속 전극들은 실질적으로 유사한 구성들의 제1 층 및 제2 층으로 형성될 수 있고, 여기서 상기 제1 및 상기 제2 층들은 금속성 물질의 단일 층을 형성하며, 이는 금속성 물질의 동종층(homogenous layer)일 수 있다. 일부 다른 실시예들에서, 상기 제1 및 상기 제2 층들은 다른 전이 금속 화합물들을 포함하는 다른 금속성 물질들로 형성될 수 있다. 상기 다른 전이 금속 화합물들은 다른 전이 금속들을 포함할 수 있고, 및/또는, 상기 층들과 상이한 다른 요소들을 포함할 수 있다. 일부 다른 실시예들에서, 상기 제1 및 상기 제2 층들 중 하나 또는 이를 모두는 다른 물질들의 서브층들로 형성된 박층들(laminate layers)일 수 있다. 예를 들어, 상기 박층들은 다른 전이 금속 화합물들의 서브층들로 형성될 수 있다. 일부 실시예들에서, 상기 제1 및 제2 층들은 유사한 박층들 또는 다른 박층들로 형성될 수 있다.

[0014]

하이-K(HiK) 금속 게이트(Metal Gate, MG) 씨모스(Complementary metal-oxide-semiconductor, CMOS) 기술은, 집적 회로들의 대량 생산에 있어서 종래 폴리-실리콘 옥시나이트라이드(poly-SiON) 트랜지스터 소자의 대안을 제공한다는 점이 이해될 것이다. 하이-k 유전체들은 트랜지스터들의 게이트 유전체들을 형성하는데 사용되고, 여기에 언급된 전이 금속 화합물들과 같은 금속성 물질들은 트랜지스터들의 게이트 금속들을 형성하는데 사용될 수 있다. 이러한 하이-k 유전체들 및 게이트 전극들은 다양한 하이K-금속 게이트(이하 'HiK-MG'라 지칭함) 집

적 플로우들(flows)을 사용하여 트랜지스터 소자들 내로 포함될 수 있고, 이들 플로우들 중 2가지는 소위 "선-게이트(gate-first)" 플로우 및 "후-게이트(gate-last)" 플로우를 포함한다. 후자의 접근법은 대체가능 금속 게이트(Replaceable Metal Gate, RMG)로도 불리울 수 있고, 교대로 "선-하이K(HiK-first)" 및 "후-하이K(HiK-last)"과 같은 2개의 하부 접근법들을 갖는다.

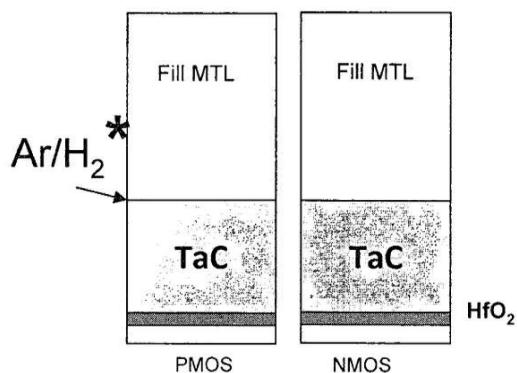

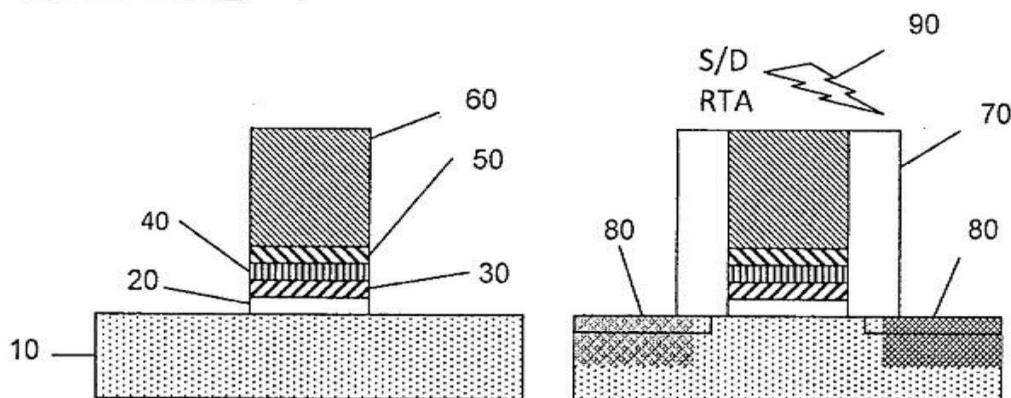

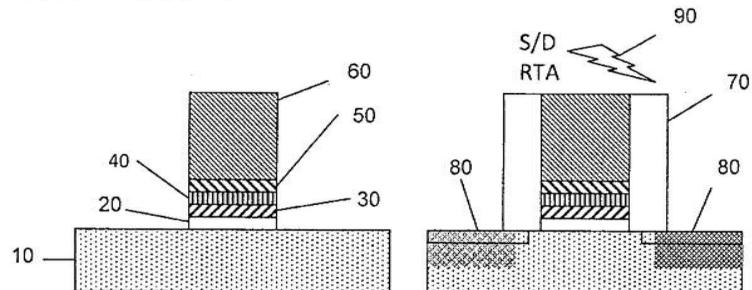

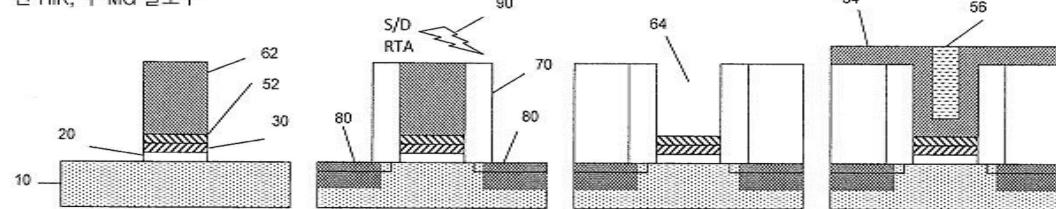

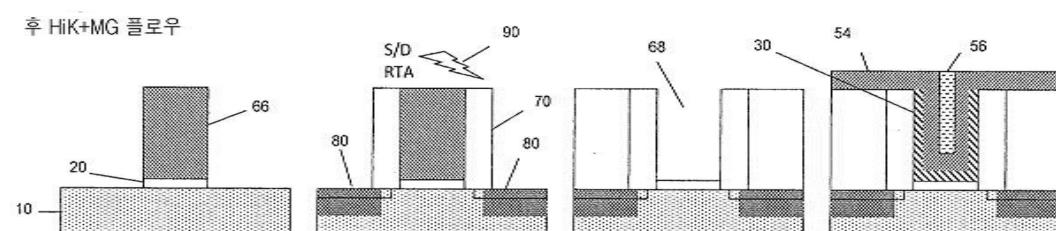

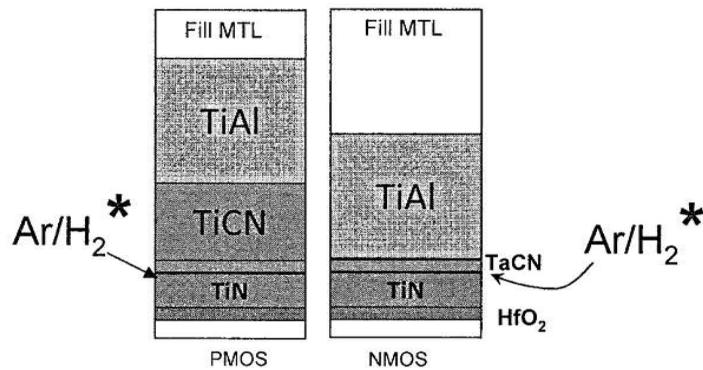

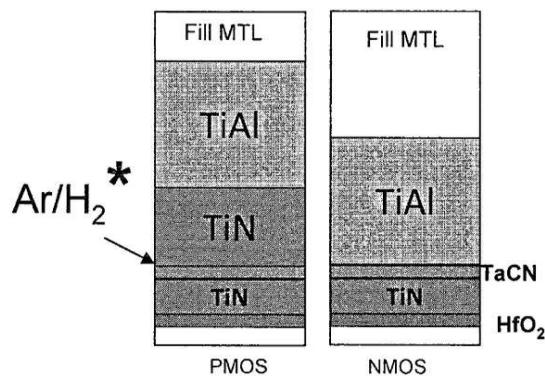

[0015] 다양한 HiK-MG 플로우들이 도 1a 내지 도 1c에 도시된다. 모든 이러한 HiK-MG 공정 플로우들은 공통적으로 금속 전극을 갖고, 상기 금속 전극은 하이K 유전층의 상부에 퇴적된다. 이하에서 더욱 구체적으로 설명된 바와 같이, 상기 플로우들 사이의 차이점 중 하나는 (기판이 높은 온도에 노출되는 공정 단계들인) 고 씨밀 베짓 단계(High Thermal Budget steps)의 발생 시점이다. 전형적으로 금속 열처리(Rapid Thermal Anneal, RTA)와 같은 고온 어닐이 소스 및 드레인 영역들을 형성하기 위해 수행된다. "선-게이트" 공정 플로우에서, 금속 전극은 고온 어닐 단계 이전에 퇴적되고 이후 상기 금속 전극에 대한 고온 어닐 단계가 수행되는 반면에, "후-게이트" 플로우에서는, 상기 고온 어닐 단계 이후에 금속 전극이 퇴적된다. 상기 두 공정 플로우들 사이의 다른 차이는, "후-게이트" 플로우의 경우, 높은 금속 게이트 콘포말리티(conformality)를 위한 요건들이 더욱 높은데, 이는 이 플로우에서 금속 전극 층이 높은 종횡비(aspect ratio)를 갖는 상대적으로 좁은 트렌치 내에 퇴적되기 때문이다(도 1b 참조).

[0016] 이제 도 1a 내지 도 1c가 더욱 구체적으로 설명될 것이다. 도시된 각각의 구조물들은, 각각의 공정 플로우에 따른 것으로서, 공정 플로우의 다양한 시점들에서의 트랜지스터의 단면도를 나타내고, 좌측에서 우측으로 감에 따라 시간이 진행된다. 최-좌측 구조물들은 도시된 구조물들 중 가장 먼저 형성된 것이고, 최-우측 구조물들은 도시된 구조물들 중 가장 나중에 형성된 것이다.

[0017] 도 1a는 "선 게이트" 공정 플로우를 도시한다. 첫째로 도시된 부분에서, 기판(10)은, 이산화규소 계면층(silicon dioxide interface layer)(20), 하이-k 유전층(30), 일함수 조절을 위한 유전캡(40), 금속 전극 층(50), 및 폴리실리콘 층(60)으로 형성된 상부 게이트 스택을 갖도록 제공된다. 두번째로 도시된 부분에서, 측벽 스페이서들(70) 및 소스/드레인 영역들(80)이 순차적으로 형성된다. 상기 소스/드레인 영역들의 형성 및 활성화를 위한 금속 열처리가 부재번호(90)에 의해 나타난다.

[0018] 도 1b는 하이-k 유전체가 먼저 형성되는 "후 게이트" 공정 플로우를 도시한다. 도 1b에 도시된 첫 번째 부분에서, 기판(10)은, 이산화규소 계면층(20), 하이-k 유전층(30), 식각 저지층(52) 및 폴리실리콘 층(62)을 갖는 상부 스택과 함께 제공된다. 도 1b에 도시된 두 번째 부분에서, 측벽 스페이서들(70) 및 소스/드레인 영역들(80)이 순차적으로 형성된다. 상기 소스/드레인 영역들은 금속 열처리에 의해 형성될 수 있으며, 상기 금속 열처리는 부재번호(90)에 의해 나타난다. 도 1b에 도시된 세 번째 부분에서, 폴리실리콘 층(62)이 제거되어 후에 트렌치(64)가 남는다. 도 1b에 도시된 네 번째 부분에서, 금속 전극(54)이 트렌치(64) 내에 퇴적되고, 금속 필(metal fill)(56)이 상기 트렌치의 남은 부분을 채우도록 퇴적된다.

[0019] 도 1c는 하이-k 유전체가 나중에 형성되는 "후 게이트" 공정 플로우를 도시한다. 도 1c에 도시된 첫 번째 부분에서, 기판(10)은 이산화규소 계면층(20) 및 폴리실리콘 층(66)을 갖는 상부 스택과 함께 제공된다. 도 1c에 도시된 두 번째 부분에서, 측벽 스페이서들(70) 및 소스/드레인 영역들(80)이 형성된다. 상기 소스/드레인 영역들은 금속 열처리에 의해 형성될 수 있으며, 상기 금속 열처리는 부재번호(90)에 의해 나타난다. 도 1c에 도시된 세 번째 부분에서, 폴리실리콘 층(66)이 제거되어 후에 트렌치(68)가 남는다. 도 1c에 도시된 네 번째 부분에서, 하이-k 유전층(30)이 상기 트렌치 내에 퇴적되고, 금속 전극 층(54)이 상기 하이-k 유전층(30) 상으로 퇴적되며, 금속 필(56)이 상기 트렌치의 남은 부분을 채우도록 퇴적된다.

[0020] 도 1a 내지 도 1c를 참조하면, 이산화규소 계면층(20)은, 산소 종들과 함께 기-존재하는(pre-existing) 실리콘의 반응(reaction) 및/또는 퇴적(deposition)을 포함하는 다양한 공정들에 의해 형성될 수 있다. 예를 들어, 이산화규소 계면층(20)은, 상기 이산화규소 계면층의 요구되는 특성들 및 사용된 공정 플로우에 따라, 화학적 산화물(chemical oxide), CVD(chemical vapor deposition) 산화물, 또는 열 산화물일 수 있다.

[0021] CMOS 동작을 위한 목표 임계 전압(V<sub>t</sub>)을 달성하기 위해, 적절한 유효 일함수(Effective Work Functions, EWF)를 갖는 금속 게이트들이 요구된다. 예를 들어, 평면 고성능(High Performance, HP) CMOS 논리 장치들의 경우, NMOS 및 PMOS 유효 일함수 목표들은 각각 4.2 eV와 5.1 eV일 수 있다. 그러한 일함수 값들은, 그들의 실리콘의 컨덕션 및 밸런스 밴드 에지들(conduction and valence band edges)로의 각각의 근접성 때문에, 종종 "밴드-에지(band-edge)"로 지칭된다. 단일 PMOS 밴드-에지 금속성 물질들, 특히, "후 게이트" 플로우를 사용하여 형성된 트랜지스터 소자들의 콘포말리티 요건들을 만족할 수 있는 금속성 물질들의 알려진 예들이 없다고 여겨진다.

- [0022] 예로서, 티타늄 나이트라이드(TiN)는 일반적으로 사용되는 HiK-MG 소자들용 금속성 물질이다.  $TiCl_4-NH_3$  베이스의 ALD TiN(ALD(atomic layer deposition) 공정 및 내에서  $TiCl_4$ 를 Ti 전구체로 사용하고  $NH_3$ 를 N 전구체로 사용하여 퇴적된 TiN은, 단일 웨이퍼 또는 배치-타입 반응기 내에서 대체 가능 금속 게이트 소자(RMG device)의 좁은 트렌지 내로 고르게(conformally) 퇴적될 수 있다. 그러나, 퇴적 방법 및/또는 공정 조건들과 무관하게, TiN의 4.7-4.75 eV의 전형적인 유효 일함수(EWF) 값은, 저-임계전압(low-Vt) 평면 고성능(HP) 장치들에 필요한 5.1 eV 미만이라는 것이 알려졌다. 힙클 등(Hinkle et al.)의 논문 ECS Transactions, 35(2) 285-295 (2011)에서,  $N_2$  내 잔여의(residual) 또는 10%의  $O_2$ 를 갖는 산소-함유 분위기(ambient)에서 어닐을 수행하고, 텡스텐(W)의 상부 금속 층(클래딩(cladding) 층)을 퇴적함으로써, TiN 막들의 유효 일함수가 5 eV 이상의 값들로 증가될 수 있다는 것이 밝혀졌다. 450°C 또는 500°C의 어닐 온도 및/또는 10%의  $O_2$  농도를 포함하는 분위기를 사용한 공격적인 어닐이 유효 일함수를 증가시켰다는 것이 보고되었다. 그러나, TiN은 산화되기 쉽기 때문에, 450°C에서  $N_2$  내 10%의  $O_2$  내에서의 공격적인 어닐은 전체 TiN 층을 산화시킬 수 있다고 여겨지고, 이는 바람직하지 않다.

- [0023] 바람직하게는, 여기에 설명된 일부 실시예들은 금속 전극 또는 상기 금속 전극의 금속성 하부 층을 사용하여 게이트 스택의 유효 일함수를 조절 가능하게 하면서도, 전체 금속성 층을 발표된 450°C 또는 그 이상의 온도들의 산화 조건들로 노출시킬 필요가 없게 한다. 일부 실시예들에서, 그러한 조절은 약 450°C 이하, 약 420°C 이하, 또는 약 400°C 이하의 온도들에서 수행될 수 있다.

- [0024] 일부 실시예들에서, 금속성 물질(예를 들어, 전이 금속 화합물)의 제1 층은 기판 상에 퇴적되며, 상기 퇴적 동안, 상기 기판은 플라즈마 또는 래디컬들과 같은 여기된 종들에 노출되지 않는다. 일부 실시예들에서, 상기 제1 층은 약 5 nm 미만이고, 약 4 nm 미만이며, 약 3 nm 미만이고, 또는 약 1-3 nm이다. 일부 실시예들에서, 상기 두께는 약 2 nm이다. 이후, 상기 제1 층이 처리된다. 상기 처리(들)는, 금속성 박막 층(thin metallic layer)을 수소-함유 가스, 더욱 바람직하게는 수소-함유 래디컬 또는 수소-함유 플라즈마와 같은 여기된 수소-함유 종들에, 헬륨(He) 또는 아르곤(Ar)과 같은 비활성 가스와 조합되는 지와 관계 없이, 노출시키는 단계를 포함한다. 상기 여기된 종들로의 노출은 바람직한 시간 동안 바람직한 온도 및 플라즈마 전력으로 수행될 수 있다. 일부 실시예들에서, 상기 플라즈마-전력은 4 초 이하의 펄스들로 인가될 수 있다. 상기 여기된 종들은 상기 기판과 동일한 반응 챔버에서 형성된 플라즈마의 일부일 수 있고, 또는 원격 생성되어 상기 반응 챔버 내로 유동될 수도 있다. 일부 실시예들에서, 상기 수소-함유 가스는, 예를 들어, 수소 또는 암모니아일 수 있다. 이후, 금속성 물질(예를 들어, 제2 전이 금속 화합물)의 제2 층이 금속성 물질의 상기 제1 층 상으로 퇴적된다. 이러한 3개의 단계들은, 동일한 온도 또는 다른 온도에서, 동일한 반응기에서 또는 다른 반응기들에서 수행될 수 있다.

- [0025] 상기 여기된 종들로의 노출 이전 및/또는 이후에, 상기 기판의 산소-함유 가스로의 노출이 수행될 수 있거나, 또는 상기 처리가 산소-함유 가스로의 노출 없이 행해질 수 있다. 선택적으로, 산소-함유 가스로의 상기 노출은 제어되는 방식으로, 바람직한 조건들 하에서 그리고 바람직한 기간 동안 반응 챔버 내에서 수행될 수 있다. 일부 실시예들에서, 상기 산소-함유 가스는 산소 가스 및 질소 가스의 혼합물(mixture)일 수 있다. 일부 실시예들에서, 상기 산소-함유 가스는 일부 양의 수증기를 포함할 수 있다. 산소-함유 가스로의 상기 노출은 금속성 물질을 퇴적하는데 사용되는 퇴적 챔버 내에서 인-시튜(in-situ)로 수행될 수 있다. 선택적으로, 상기 기판은 반응 챔버로부터 상기 기판을 언로딩(unloading) 시키고 상기 기판을 클린 룸 에어에 노출시킴으로써(소위 "에어 브레이크(air break) 단계"로 지칭됨) 산소-함유 가스에 노출될 수 있다.

- [0026] 금속성 물질의 상기 제1 층은 물리 기상 증착(physical vapor deposition, PVD), 화학 기상 증착(chemical vapor deposition, CVD), 펄스 CVD(pulsed CVD), 또는 원자층 증착(atomic layer deposition, ALD)에 의해 퇴적될 수 있다. 금속성 물질의 상기 제2 층은 플라즈마-인핸스드(plasma-enhanced) CVD 또는 플라즈마-인핸스드 ALD를 포함하는 PVD, CVD, 펄스 CVD 또는 ALD에 의해 퇴적될 수 있다. 일부 실시예들에서, 상기 금속성 층들은 높은 스텝 커버리지(high step coverage)를 달성하기 위해 ALD를 사용하여 퇴적될 수 있다. 전구체들은 시간적으로 분리된 펄스들(temporally separated pulses)에 따라 교번하여 또는 순차적으로 반응 챔버 내로 유동될 수 있다. 일부 실시예들에서, 한 사이클을 구성하는 각각의 전구체의 일 펄스(예를 들어, 티타늄 전구체의 일 펄스 및 질소 전구체의 일 펄스)의 시퀀스와 함께, 퇴적 사이클 당 화합물의 단일층 정도 또는 그 미만이 형성된다. 예를 들어, TiN은 시간적으로 분리된 펄스들에 따라  $TiCl_4$  및  $NH_3$ 를 전구체들로 사용하여 형성될 수 있다. 여기에 설명된 바와 같이, 일부 실시예들에서, 상기 금속성 물질은 탄탈륨 나이트라이드, 탄탈륨 카바이드, 탄

탈륨 니트로카바이드, 티타늄 카바이드, 티타늄 카보나이트라이드, 나오븀 나이트라이드, 나오븀 카바이드, 나오븀 니트로카바이드, 몰리브데늄 나이트라이드, 몰리브데늄 카바이드, 몰리브데늄 니트로카바이드, 하프늄 나이트라이드, 지르코늄 나이트라이드, 텉스텐, 및 텉스텐 나이트라이드를 포함할 수 있다. 일부 실시예들에서, 상기 제1 및 제2 층들은 단일 물질로 형성될 수 있다. 일부 다른 실시예들에서, 상기 제1 및 제2 층들 중 적어도 하나는 복수의 서브층들로 형성된 박층들(laminate layers)일 수 있다.

[0027] 예로서, 다양한 금속성 층들의 퇴적이 조사되었고 이를 층들을 형성하기 위한 퇴적 시퀀스들이 도 2 및 도 4에 구체적으로 나타난다. 도 2 및 도 4에 나타난 처리들 이후, 모든 표본들은 형성 가스( $N_2$  내 4%  $H_2$ ) 내 420°C에서 30분간의 어닐을 받았다. 환원 분위기(reducing ambient)에서의 퇴적물 및 처리들이 원자층 증착(ALD)을 위한 ASM 인터네셔널의 EmrtALD® 단일 웨이퍼 반응기 시스템에서 수행되었고, 이는 플라즈마가 상기 반응 챔버 내에서 생성되는 것을 허용하는 플라즈마 옵션도 제공한다. 상기 EmrtALD® 단일 웨이퍼 반응기 시스템은, 네덜란드 알메르(Almere)의 ASM 인터네셔널 N.V.로부터 입수될 수 있다. 도 2, 도 4, 및 도 6은 TiN 퇴적물에 관한 다양한 구체적인 사항들을 제공한다. 다른 일부 실시예들에서, 탄탈륨 나이트라이드, 탄탈륨 카바이드, 탄탈륨 카보나이트라이드, 티타늄 카바이드, 티타늄 카보나이트라이드, 나오븀 나이트라이드, 나오븀 카바이드, 나오븀 카보나이트라이드, 몰리브데늄 나이트라이드, 몰리브데늄 카바이드, 몰리브데늄 카보나이트라이드, 하프늄 나이트라이드, 지르코늄 나이트라이드, 텉스텐, 및 텉스텐 나이트라이드와 같은 금속성 물질들은, 유사한 결과들을 달성하기 위해, 유사한 공정 단계들 및 조건들을 사용하여 TiN과 함께 또는 TiN 대신에 형성될 수 있다.

[0028] 여기에 개시된 실시예들에 따른 퇴적이 유효 일함수(EWF)의 증가를 제공하는 것으로 밝혀졌다. 유효 일함수(EWF) 값들 및 등가 산화막 두께(equivalent oxide thickness, EOT) 값들이 금속-질연체-반도체(MIS) 구조물들 상의 C-V 측정들로부터 추출되었다. 상기 금속 전극들은 실리콘 기판들 상의 1nm 계면  $SiO_2$  및 2nm  $HfO_2$  층들의 상부에 퇴적되었다. 도 2를 참조하면, 모든 TiN 퇴적물은 390°C에서 수행되었고, 에어 브레이크들이 제1 TiN 층 퇴적과 막 처리 단계 사이 및 상기 처리 단계와 제2 TiN 층 퇴적 단계 사이 모두에 적용되었다. 단일 10 nm 두께의 ALD TiN 층은 전형적으로 약 4.7 - 4.75 eV (1A 참조)의 일함수를 제공한다. 그러나, 여기에 개시된 실시예들에 따른 퇴적은 더욱 높은 유효 일함수(EWF)를 나타냈다. 예를 들어, 2 nm ALD TiN 층, 이후 에어 브레이크,  $H_2/Ar$  플라즈마 처리(각각 2초의 32 펄스들), 제2 에어 브레이크, 및 10nm ALD TiN 층은 4.96 eV (1F 참조)의 이례적으로 높은 유효 일함수를 보여주었다.

[0029] 상기 유효 일함수의 증가는 여기된 수소 종들로의 노출에 기인한 것일 수 있다. 도 3을 참조하면, 32 사이클의 플라즈마-인핸스드 ALD(PEALD)를 통해 하부 및 상부 ALD TiN 층들 사이로 TaCN 박층을 성장시킴으로써, 심지어 더욱 높은 4.98 eV (1C 참조) 또는 5.04 eV (1B 참조)의 일함수 값들이 달성되었다. 상기 PEALD TaCN 층을 열적(thermal) ALD TaCN 층으로 교체한 결과(1D 및 1E 참조), 단일 10 nm ALD TiN 층의 그것과 가까운 더욱 낮은 일함수가 나타났다. 이러한 결과들은, PEALD TaCN으로 얻어진 더욱 높은 유효 일함수(EWF)가 PEALD TaCN 퇴적 동안 개시된 하부 (제1) TiN 층의  $Ar/H_2$ -함유 플라즈마로의 노출에 기인한 것일 수 있다는 것을 보여준다. 또한, 2초에서 3초 또는 4초로 증가된 플라즈마 펄스들의 지속기간은 유효 산화막 두께(effective oxide thickness, EOT)에서 증가된 유효 일함수(EWF)로 귀결된다는 사실이 발견되었다. 마지막으로, 플라즈마 처리 단계를 적용하지 않고 2nm 제1 TiN 층과 더 두꺼운 제2 TiN 층 사이에 에어 브레이크들만을 적용하는 것(1G 참조)은 유효 일함수(EWF) 증가를 일으키지 않음이 발견되었다.

[0030] 또한, TiN 층들에 대해 전술한 것과 유사한 공정들을 사용함으로써, TiN/TaCN 이중층들 및 TaC 층들의 일함수가 증가될 수 있다는 것이 밝혀졌다. 상기 TiN/TaCN 이중층들 및 상기 TaC 층들은 플라즈마에 의해 생성된 래디컬들 없이 열적으로 활성화된 공정에 의해 퇴적되었고, 이후 수소-함유 가스 내에서 상기 층들의 처리가 이루어졌으며, 상기 처리는 수소 래디컬들에 또는 수소-함유 플라즈마에 상기 층들을 노출시키는 단계를 포함하였다. 열적으로 활성화된 수소-함유 가스에 상기 층들을 노출시킴으로써 일함수가 또한 증가될 수 있다.

[0031] 다른 실험들에서, 도 4에 나타난 결과를 또한 조사되었으며, 도 4는 이하의 파라미터들의 영향을 나타낸다.

[0032] - 에어 브레이크들의 횟수 및 이들의 순서들(positions)의 영향:

[0033]  $Ar/H_2$  플라즈마 처리 이전 및 이후;

[0034]  $Ar/H_2$  플라즈마 처리 이전;

[0035]  $Ar/H_2$  플라즈마 처리 이후; 및

[0036] 에어 브레이크 없음;

[0037] - TiN 퇴적 온도의 영향(325°C vs. 390°C); 및

[0038] - Ar/H<sub>2</sub> 플라즈마 처리 동안의 웨이퍼 온도의 영향(325°C vs. 390°C).

[0039] 상기 Ar/H<sub>2</sub> 플라즈마는, 펄스-방식(pulse-wise)으로, 각각 2초의 32 펄스들로 인가되었다.

[0040] 도 5에서 관찰될 수 있듯이, TiN 막들에 대한 325°C 퇴적 온도는 규칙적으로 더욱 높은 등가/유효 산화막 두께(EOT) 값을 나타낸다. 바람직한 EWF/EOT 트레이드-오프가 다음 시퀀스로 달성될 수 있음이 밝혀졌다.

[0041] - 모두가 390°C에서 성장된 제1 및 제2 TiN 층들

[0042] - 390°C에서 수행된 Ar/H<sub>2</sub> 플라즈마 처리

[0043] - 2개의 에어 브레이크들(Ar/H<sub>2</sub> 플라즈마 처리 이전 및 이후).

[0044] 유사한 조건들에서 처리된 표본들의 경우 도 2 및 도 4의 일부 결과들(도 2의 1F vs. 도 4의 2B) 사이에 차이들이 존재함이 이해될 것이다. 이러한 변동들은 도 1 및 도 4의 실험들 사이의 시간 경과(time lapse)에 기인한 것일 수 있다. 나아가, 도 4의 실험들에서의 에어 브레이크는 도 2의 실험들에서의 에어 브레이크(1-2 주들(weeks))보다 더 짧았다(1-2 일들(days)). 그럼에도 불구하고, 실험들 각각의 세트들에서, Ar/H<sub>2</sub> 플라즈마로의 노출을 갖는 모든 시퀀스들은 그러한 노출을 갖지 않는 세트들의 기준들(도 2: 1A, 1G, 도 4: 2A, 2E)과 대비하여 유효 일함수(EWF)의 증가를 제공하였다.

[0045] 도 2 및 도 4에 구체화된 실험들에서 사용된 다양한 추가적인 공정 조건들이 도 6에 요약된다. TBTDET는 TertiaryButylimido Tris(DiEthylamino)Tantalum, Ta[N(C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>]<sub>3</sub>[=NC(CH<sub>3</sub>)<sub>3</sub>]임이 이해될 것이다. 다른 온도들에서 및 더욱 적은(또는 생략된) 에어 브레이크들에서, 다양한 처리 파라미터들을 조절함으로써 원하는 높은 유효 일함수(EWF)가 달성될 수 있다고 여겨진다. 공정 파라미터들의 일부 예들은, 1) 하부 TiN 층 두께를 변화시키는 것; 2) 플라즈마 전력 및 시간을 변화시키는 것, (플라즈마 없는) 열적 처리들만을 포함함; 및 3) 반응기 내 O<sub>2</sub>, N<sub>2</sub>, 및 H<sub>2</sub> 함유량을 변화시키는 것을 포함하도록 변화될 수 있지만, 이러한 공정 파라미터들은 전술한 예에 제한되지 않는다. 전술한 실험들에서, EWF/EOT 추세선이 관측되었다: 더욱 높은 등가/유효 산화막 두께(EOT)에서 더욱 높은 유효 일함수(EWF)가 관측된다. 반면에, 일부 응용들에서는, 낮은 등가/유효 산화막 두께(EOT) 값들에서 높은 유효 일함수(EWF)를 달성하는 것이 바람직하다. 전술한 파라미터들의 변화가 높은 유효 일함수(EWF)와 낮은 등가/유효 산화막 두께(EOT) 사이의 바람직한 트레이드-오프를 허용할 수 있다고 여겨진다.

[0046] 이론적으로 제한됨이 없이, 수소-함유 가스로의 노출과 조합된 에어 브레이크도 유효 일함수(EWF)에 영향을 미칠 수 있다고 여겨진다. 예를 들어, 에어 브레이크 이후 Ar/H<sub>2</sub> 플라즈마 처리, 이후 다른 에어 브레이크는 금속성 물질-함유 스택의 O 및 N 함유량 및/또는 결정 입도/형태(grain size/morphology)를 변화시키는 것으로 여겨지고, 결과적으로, 상기 스택(예를 들어, TiN 스택)의 유효 일함수(EWF)가 증가될 수 있다. 나아가, 상기 에어 브레이크는, 상기 제1 금속성 층을 수소-함유 가스 또는 수소-함유 플라즈마에 노출시키는 단계 동안, 산소 또는 수소-함유 불순물들(예를 들어, O<sub>2</sub> or H<sub>2</sub>O)의 출현을 야기할 수 있다. 이러한 불순물들은 원하는 스택 특성을 달성하는 데에 있어 역할을 할 수 있다.

[0047] 예를 들어, 이론적으로 제한하려는 의도 없이, 유효 일함수의 일부 증가들은 제1 금속층과 추가 금속 층 사이의 계면 상의 H-O 쌍극자들(dipoles)의 형성의 결과일 수 있다. 낮은 산소 농도가 제공될 수 있고, 이는 상기 제1 금속층 및/또는 반응기에 존재하는 잔여의 산소로부터 생기거나, 또는 수소 래디컬 또는 플라즈마 처리 동안, 이전, 또는 이후 상기 제1 금속층의 산소로의 의도적인 노출로부터 생길 수 있다. 상기 산소는 수소 처리 이전 및/또는 이후의 에어 브레이크들로부터 생길 수 있다. 바람직하게는, 상기 산소 농도는, 비바람직하게 등가/유효 산화막 두께(EOT)의 증가를 초래할 수 있는 금속 층들의 산화를 제한하기에 충분히 낮은 레벨로 유지될 수 있다.

[0048] 플라즈마 처리 동안의 Vpp(피크-투-피크 전압)가 더욱 결정적인 요소이고 플라즈마 전력보다 더 나은 유효 일함수(EWF)와의 상호관계를 나타낸다는 것이 도 7에 나타난다: 더 높은 Vpp에서 더 높은 유효 일함수(EWF)가 얻어진다. 390 °C에서 퇴적된 TiN 막들에 대한 추가적인 결과들이 도 8에 나타난다. 2nm 두께의 제1 TiN 막이 퇴적되고, 이후 플라즈마 노출의 32 펄스들이 도 8에 나타난 펄스 지속기간 및 Vpp로 인가되고, 이후 10nm 두께의

제2 TiN 필름이 퇴적된다. 에어 브레이크들이 수소 플라즈마 처리 이전 및 이후에 적용된다. 0.5 Torr에서 수소/Ar 혼합물로 수소 플라즈마 처리가 적용된다. 도 8로부터, 더욱 높은 V<sub>pp</sub> 및/또는 더욱 긴 펄스 지속기간이 더욱 높은 유효 일함수(EWF)를 나타냄이 관찰될 수 있다. 일부 실시예들에서, V<sub>pp</sub>는 약 110 V 이상, 약 130 V 이상, 약 160 V 이상, 또는 약 200 V 이상일 수 있다. 일부 실시예들에서, 여기된 수소 종으로의 노출 지속 기간은 약 2초 이상, 약 4초 이상, 또는 약 2~4초일 수 있다. 참고로, 플라즈마로의 노출 없이 형성된 TiN은, 전술한 바와 같이, 약 4.7 또는 4.73의 낮은 유효 일함수(EWF)를 갖는다.

[0049] 도 1b 및 도 1c를 다시 참조하면, 일부 실시예들에서, 제1 및 제2 층들의 퇴적에 의해 형성된 금속성 물질이 전극(54)으로서 활용될 수 있음이 이해될 것이다. 따라서, 일부 실시예들에서, 상기 제1 및 제2 층들의 퇴적이 유전 물질로 형성된 스페이서들에 의해 한정된 더욱 좁은 트렌치에서 수행될 수 있고, 금속 필(metal fill)이 게이트 전극(54)에 의해 정의된 오프닝 내로 퇴적될 수 있다.

[0050] CMOS 공정 플로우에서 금속 전극 스택들의 퇴적의 일부 예들이 도 9a 내지 도 12를 참조하여 이하에서 설명된다. 유사한 선영(hatching) 및 음영(shading)은 유사한 층들을 지칭한다. 공정 플로우들은 높은 일함수를 갖는 PMOS 금속 전극 및 낮은 일함수를 갖는 NMOS 금속 전극의 퇴적을 포함한다. 이하에서 논의된 물질들은 예들이고 다른 물질들도 또한 사용될 수 있음이 이해될 것이다. 예를 들어, 여기에 논의된 바와 같이, 다양한 다른 금속성 물질들이 TiN 대신에 사용될 수 있다.

[0051] <예 1>

예 1이 도 9a 내지 도 9d를 참조하여 논의될 것이다. 게이트 유전체는 HfO<sub>2</sub>를 포함할 수 있다. PMOS 금속 전극은, 하부에서 상부로, 2nm TiN 층, 1nm TaCN 층, 4nm TiN 층, 5nm TiAl 층, 및 필 금속층의 퇴적에 의해 형성된다. NMOS 금속 전극은, 하부에서 상부로, 2nm TiN 층, 1nm TaCN 층, 5nm TiAl 층, 및 필 금속층의 퇴적에 의해 형성된다. TiAl은 NMOS에 대한 낮은 일함수를 제공한다. 그러나, PMOS 스택에서, 상기 TiAl 층은 HfO<sub>2</sub>/금속 전극 계면으로부터 이격되어 있고 상기 HfO<sub>2</sub>/금속 전극 계면에서의 PMOS 스택 일함수에 대해 제한된 영향을 미친다. PMOS 스택에서 Ar/H\*(여기서 H\*은 플라즈마 내 수소 래디컬들과 같은 여기된-수소 함유 종들을 나타난다)로의 처리는, TaCN 층 퇴적 전에(도 9a 및 도 9b), 플라즈마 인핸스드 퇴적 공정이 TaCN 층을 형성하는데 사용되는 경우 TaCN 퇴적 동안(도 9c), 또는 TaCN 층 퇴적 후에(도 9d) 적용될 수 있다.

[0053] 도 9a의 스택들은 이하의 공정 플로우들을 사용하여 제조될 수 있다.

[0054] 1. 제1 TiN 층의 퇴적;

[0055] 2. 상기 제1 TiN 층의 수소-함유 가스에서의 처리;

[0056] 3. 열 공정에 의한 TaCN 층의 퇴적 및 제2 TiN 층의 퇴적;

[0057] 4. NMOS 소자들에서 상기 제2 TiN 층의 제거를 위한 리소그래피 및 에치(etch), TaCN 층에서 에치 스텝(etch stop) 됨; 및

[0058] 5. TiAl 층 및 필 금속(fill metal)의 퇴적.

[0059] 도 9b의 스택들은 이하의 공정 플로우들을 사용하여 제조될 수 있다.

[0060] 1. TiN 층의 퇴적;

[0061] 2. NMOS 소자들 상에 보호 층(예를 들어, 포토레지스트 또는 SiO<sub>2</sub> 층)을 형성하기 위한 리소그래피 및 에치;

[0062] 3. 상기 TiN 층의 수소-함유 가스에서의 처리;

[0063] 4. 상기 보호 층의 제거;

[0064] 5. 열 공정에 의한 TaCN 층의 퇴적 및 제2 TiN 층의 퇴적;

[0065] 6. NMOS 소자들에서 상기 제2 TiN 층의 제거를 위한 리소그래피 및 에치, TaCN 층에서 에치 스텝 됨; 및

[0066] 7. TiAl 층 및 필 금속의 퇴적.

[0067] 도 9c의 스택들은 이하의 공정 플로우들을 사용하여 제조될 수 있다.

[0068] 1. 제1 TiN 층의 퇴적;

[0069] 2. 수소-함유 플라즈마 인핸스드 공정에 의한 TaCN 층의 퇴적;

[0070] 3. 제2 TiN 층의 퇴적;

[0071] 4. NMOS 소자들에서 상기 제2 TiN 층의 제거를 위한 리소그래피 및 에치, TaCN 층에서 에치 스탑 됨; 및

[0072] 5. TiAl 층 및 필 금속의 퇴적.

[0073] 도 9d의 스택들은 이하의 공정 플로우들을 사용하여 제조될 수 있다.

[0074] 1. 제1 TiN 층 및 TaCN 층의 퇴적

[0075] 2. NMOS 소자들 상에 보호 층(예를 들어, 포토레지스트 또는 SiO<sub>2</sub> 층)을 형성하기 위한 리소그래피 및 에치;

[0076] 3. 수소-함유 가스에서의 처리;

[0077] 4. 상기 보호 층의 제거;

[0078] 5. 제2 TiN 층의 퇴적;

[0079] 6. NMOS 소자들에서 상기 제2 TiN 층의 제거를 위한 리소그래피 및 에치, TaCN에서 에치 스탑 됨;

[0080] 7. (남은 TaCN 층의 두께를 줄이기 위한 선택적 에치);

[0081] 8. TiAl 층(nEWF) 및 필 금속의 퇴적, 선택적으로 필 금속 전에 박막 배리어 금속층(예를 들어, TiN 층)이 퇴적될 수 있음.

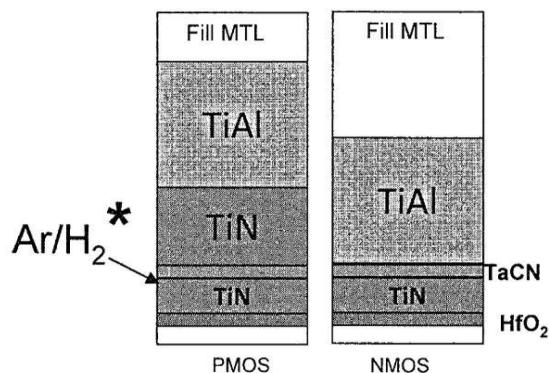

[0082] <예 2>

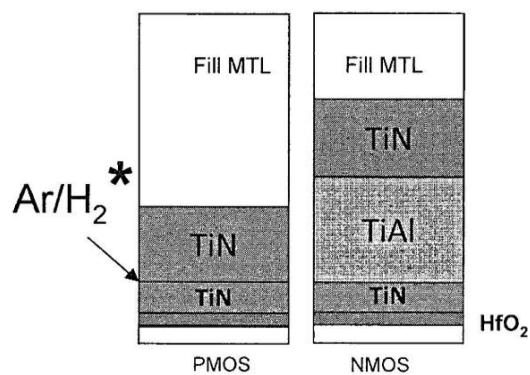

[0083] 예 2는 도 10을 참조하여 논의될 것이다. 게이트 유전층은 HfO<sub>2</sub>를 포함할 수 있다. PMOS 금속 전극은 2 nm TiN 층, 수소 함유 가스에 의한 상기 TiN 층의 처리, 4 nm TiN 층의 퇴적, 및 필 금속의 퇴적에 의해 형성된다. NMOS 금속 전극은 2 nm 제1 TiN 층, 5nm TiAl 층, 4nm 제2 TiN 층 및 필 금속층의 퇴적에 의해 형성된다. 도 10의 스택들은 이하의 공정 플로우를 사용하여 제조될 수 있다.

[0084] 1. 제1 TiN 층 및 TiAl 층의 퇴적;

[0085] 2. NMOS 소자들 상에 보호 층(예를 들어, 포토레지스트 층 또는 SiO<sub>2</sub> 층)을 형성하기 위한 리소그래피 및 에치;

[0086] 3. PMOS 소자들에서 상기 TiAl 층을 제거, 상기 TiN 층에서 에치 스탑 됨;

[0087] 4. 수소-함유 가스에서의 처리;

[0088] 5. 상기 보호 층의 제거; 및

[0089] 6. 제2 TiN 층 및 필 금속의 퇴적.

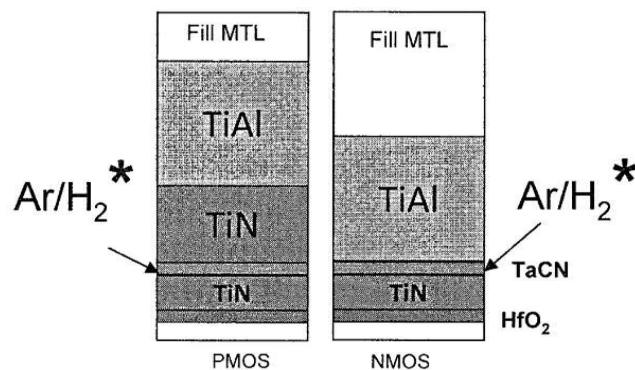

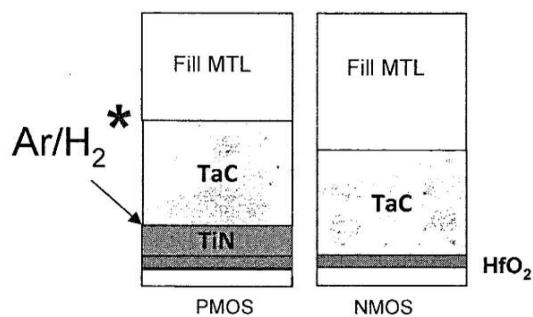

[0090] <예 3>

[0091] 예 3은 도 11을 참조하여 논의될 것이다. PMOS 전극은 2nm TiN 층, 상기 TiN 층의 수소-함유 가스에서의 처리, 5nm TaC 층의 퇴적 및 필 금속층의 퇴적에 의해 형성된다. NMOS 스택은 5nm TaC 층, 및 필 금속층을 포함할 수 있다. TaC도 또한 낮은 일함수를 제공하고, NMOS 소자들에 적합하며, TiAl과 유사하다. 그러나, TiAl이 전형적으로 PVD 공정에 의해 형성되는 반면에, TaC는 ALD에 의해 퇴적될 수 있다는 장점을 갖는다. 도 11의 스택들

은 이하의 공정 시퀀스에 의해 제조될 수 있다.

[0092] 1. 제1 TiN 층의 퇴적;

[0093] 2. 수소-함유 가스에서의 처리;

[0094] 3. NMOS 소자들에서 TiN의 제거를 위한 리소그래피 및 에치(선택적으로,  $\text{SiO}_2$  하드마스크와 함께),  $\text{HfO}_2$ 에서 에치 스탑 됨;

[0095] 4. (적절한 경우, 선택적으로 하드마스크 제거);

[0096] 5. NMOS 소자들의 유효 일함수(EWF) 설정을 위한 TaC 층의 퇴적; 및

[0097] 6. 필 금속의 퇴적.

[0098] <예 4>

[0099] 예 4는 도 12를 참조하여 논의될 것이다. PMOS 금속 전극은 5nm TaC 층의 퇴적, 수소-함유 가스에서의 처리, 및 금속 필 층의 퇴적에 의해 형성된다. NMOS 금속 전극은 5nm TaC 층 및 필 금속을 포함하고, NMOS 금속 전극의 경우에 있어서 유일한 차이점은, 수소-함유 가스에서의 처리가 생략되었다는 것이다. 눈여겨볼 점은, 수소-함유 가스에서의 처리만을 가지고도 TaC 층의 일함수가 PMOS 및 NMOS 소자들의 적절한 일함수들을 달성하기에 충분하도록 변화될 수 있다는 것이다. 도 12의 스택들은 이하의 공정 플로우를 사용하여 제조될 수 있다.

[0100] 1. TaC 층(nEWF)의 퇴적;

[0101] 2. NMOS 소자들을 보호 층(예를 들어, 포토레지스트 층 또는  $\text{SiO}_2$  층)으로 마스크(mask) 시키기 위한 리소그래피 및 에치;

[0102] 3. PMOS 소자들에 대한 유효 일함수(EWF)를 조절하기 위한 수소-함유 가스에서의 처리;

[0103] 4. NMOS 소자들에서 상기 보호 층의 제거; 및

[0104] 5. 필 금속의 퇴적.

[0105] 도 9a 내지 도 12에 나타난 예들 1 내지 4 모두에 있어서, 박막 배리어층, 예를 들어, 2nm TiN 층이 필 금속층의 퇴적 전에 추가적으로 퇴적될 수 있다. 이론적으로 제한됨이 없이, 그러한 배리어 층이 불순물들의 내부-확산(in-diffusion)으로부터 일함수 민감성 층들(work function sensitive layers)을 보호할 수 있는 것으로 여겨진다.

[0106] 여기에 설명된 공정들은 PMOS 및 NMOS 소자들의 유효 일함수를 동시에 조절하는데 사용될 수 있다. 또한, 다른 일함수들을 갖는 다른 그룹의 소자들이 형성될 수 있다. 다른 일함수들이 트랜지스터 소자의 다른 임계 전압들을 제공할 수 있음이 이해될 것이다. 결과적으로, 일부 실시예들에서, 고속 및 고전력 소모를 야기하는 낮은  $V_t$ ( $V_t$ =임계 전압)를 갖는 그룹, 중간 속도 및 중간 전력 소모를 여기하는 중간  $V_t$ 를 갖는 그룹, 및 저속 및 저전력 소모를 야기하는 높은  $V_t$ 를 갖는 그룹의 소자들을 형성하는 것이 가능하고, 그룹들 모드는 공정 플로우에 의해 동일한 기관 상에 형성된다. 다른 그룹들은 여기에 논의된 공정들에 따라 다른 수소 처리들에 노출될 수 있고, 또는 여기에 논의된 공정들에 따른 다른 스택들이 각각의 그룹에서 형성될 수 있다. 예를 들어, 다양한 그룹들에서의 전극 층들은 동시에 퇴적될 수 있고, 1개 이상의 그룹들이 보호 층들로 보호될 수 있는 반면, 1개 이상의 다른 그룹들은, 여기에 논의 된 바와 같이, 수소-함유 가스로의 처리에 노출된다. 이후, 노출된 그룹들은 보호되며, 상기 보호 층은 1개 이상의 다른 그룹들로부터 제거되어 이러한 다른 그룹들이 수소-함유 가스로 처리되는 것을 허용하도록 할 수 있다. 이 공정은 모든 그룹들이 수소-함유 가스에 노출될 때까지 원하는 바에 따라 반복될 수 있다. 각각의 그룹에 대한 상기 노출 파라미터는 다를 수 있고, 그에 따라 다른 그룹들에 대해 다른 임계 전압들이 설정될 수 있는 것이 허용된다.

[0107] 일부 다른 구현들에서, 다른 그룹들을 위한 전극 스택들이 따로 형성된다. 각각의 스택의 형성 동안 수소-함유 가스로의 노출에 대한 다른 조건을 제공함으로써, 다른 임계 전압들이 제공된다.

[0108] 전술한 공정들에 대해 본 발명의 범위에 벗어남이 다양한 생략들, 추가들 및 수정들이 이루어질 수 있고, 그러

한 수정들 및 변화들이, 첨부의 청구항들에 기재된 바와 같이, 본 발명의 범위 내에 해당하도록 의도된 것임이 당해 기술분야의 통상의 지식을 가진 자들에게 이해될 것이다.

## 도면

### 도면1a

선 HiK+MG 플로우

### 도면1b

선 HiK, 후 MG 플로우

### 도면1c

후 HiK+MG 플로우

## 도면2

| 제 1 TiN 층 | 예어<br>브레이크        | 후면 분위기에서의 처리 | 예어<br>브레이크                                                                 | 제 2 TiN 층          | EOT, nm            | EFM, eV |      |

|-----------|-------------------|--------------|----------------------------------------------------------------------------|--------------------|--------------------|---------|------|

| 1A        | -                 | -            | -                                                                          | 10 nm ALD TiN 390C | 0.92               | 4.74    |      |

| 1B        | 2 nm ALD TiN 390C | Y            | 1 nm PEALD TaCN<br>(325C, 3.5s, 32 cycles)                                 | Y                  | 10 nm ALD TiN 390C | 1.28    | 5.04 |

| 1C        | 2 nm ALD TiN 390C | Y            | 1 nm PEALD TaCN<br>(325C, 2s, 32 cycles)                                   | Y                  | 10 nm ALD TiN 390C | 1.18    | 4.98 |

| 1D        | 2 nm ALD TiN 390C | Y            | 1 nm ALD TaCN 325C                                                         | Y                  | 10 nm ALD TiN 390C | 0.94    | 4.76 |

| 1E        | 2 nm ALD TiN 390C | Y            | 1 nm ALD TaCN 325C+<br>Ar/H <sub>2</sub> -plasma<br>(325C, 2 s, 32 cycles) | Y                  | 10 nm ALD TiN 390C | 1.08    | 4.88 |

| 1F        | 2 nm ALD TiN 390C | Y            | Ar/H <sub>2</sub> -plasma<br>(325C, 2 s, 32 cycles)                        | Y                  | 10 nm ALD TiN 390C | 1.11    | 4.96 |

| 1G        | 2 nm ALD TiN 390C | Y            | -                                                                          | Y                  | 10 nm ALD TiN 390C | 1.03    | 4.75 |

도면3

## EWF/EOT summary

## 도면4

| 제 1 TiN 층 | 예어<br>브레이크        | 환원<br>처리 | 제 2 TiN 층                      | EOT, nm            | EFM, eV   |

|-----------|-------------------|----------|--------------------------------|--------------------|-----------|

| 2A        | -                 | -        | -                              | 10 nm ALD TiN 390C | 0.95 4.70 |

| 2B        | 2 nm ALD TiN 390C | Y        | Ar/H <sub>2</sub> -plasma 325C | 10 nm ALD TiN 390C | 1.09 4.85 |

| 2C        | 2 nm ALD TiN 390C | Y        | Ar/H <sub>2</sub> -plasma 390C | 10 nm ALD TiN 390C | 1.06 4.86 |

| 2D        | 2 nm ALD TiN 390C | N        | Ar/H <sub>2</sub> -plasma 390C | 10 nm ALD TiN 390C | 1.02 4.80 |

| 2E        | -                 | -        | -                              | 10 nm ALD TiN 325C | 0.99 4.66 |

| 2F        | 2 nm ALD TiN 325C | Y        | Ar/H <sub>2</sub> -plasma 325C | 10 nm ALD TiN 325C | 1.15 4.84 |

| 2G        | 2 nm ALD TiN 325C | Y        | Ar/H <sub>2</sub> -plasma 325C | 10 nm ALD TiN 325C | 1.14 4.78 |

| 2H        | 2 nm ALD TiN 325C | N        | Ar/H <sub>2</sub> -plasma 325C | 10 nm ALD TiN 325C | 1.13 4.77 |

| 2I        | 2 nm ALD TiN 325C | N        | Ar/H <sub>2</sub> -plasma 325C | 10 nm ALD TiN 325C | 1.14 4.76 |

도면5

## EWF/EOT summary

## 도면6

|                                       | 서CEPTION(Susceptor)<br>온도, C | 반응기 압력,<br>Torr | 전구체들                                | 펄싱 시퀀스                                                                       | 플라즈마<br>전력, W | 플라즈마 온<br>시간, s |

|---------------------------------------|------------------------------|-----------------|-------------------------------------|------------------------------------------------------------------------------|---------------|-----------------|

| ALD TiN                               | 325 or 390                   | 0.5             | TiCl <sub>4</sub> , NH <sub>3</sub> | 1.TiCl <sub>4</sub> pulse<br>2. Purge<br>3. NH <sub>3</sub> pulse<br>4.Purge | -             | -               |

| PEALD TaCN                            | 325                          | 1.5             | TBTDET,<br>Ar/H <sub>2</sub> plasma | 1.TBTDET pulse<br>2.Purge<br>3.Ar/H <sub>2</sub> plasma                      | 175           | 2 or 3.5        |

| ALD TaCN                              | 325                          | 4.0             | TBTDET, NH <sub>3</sub>             | 1.TBTDET pulse<br>2.Purge<br>3.NH <sub>3</sub> pulse<br>4.Purge              | -             | -               |

| Ar/H <sub>2</sub> plasma<br>treatment | 325 or 390                   | 1.5             | Ar/H <sub>2</sub> plasma            | 1.Ar/H <sub>2</sub> plasma<br>2.Purge                                        | 175           | 2               |

도면7

도면8

도면9a

도면9b

도면9c

도면9d

도면10

도면11

도면12