(12)发明专利申请

(10)申请公布号 CN 111684585 A

(43)申请公布日 2020.09.18

(21)申请号 201980011621.0

(74)专利代理机构 北京银龙知识产权代理有限

(22)申请日 2019.01.30

公司 11243

(30)优先权数据

2018-019434 2018.02.06 JP

代理人 丁文蕴 杜嘉璐

(85)PCT国际申请进入国家阶段日

(51)Int.Cl.

2020.08.04

H01L 23/12(2006.01)

H05K 3/00(2006.01)

(86)PCT国际申请的申请数据

PCT/JP2019/003169 2019.01.30

(87)PCT国际申请的公布数据

W02019/155959 JA 2019.08.15

(71)申请人 青井电子株式会社

地址 日本香川县

(72)发明人 河野一郎

权利要求书2页 说明书10页 附图8页

(54)发明名称

半导体装置的制造方法

(57)摘要

本发明提供半导体装置的制造方法，包括以下各步骤：准备在正面侧形成有剥离层的支撑基板；在支撑基板上的比剥离层更靠上的位置，局部地形成布线层；以使半导体芯片的垫与布线层电连接的方式将半导体芯片配置在支撑基板上；形成包括布线层及半导体芯片并且与支撑基板上的剥离层或者比该剥离层更靠上的层接触的密封层，且在支撑基板上形成包括半导体芯片、布线层以及密封层在内的中间层叠体；在形成中间层叠体后，切断支撑基板的周边部；以及以剥离层为边界，从切断周边部后的支撑基板机械式地剥离中间层叠体。

1.一种半导体装置的制造方法,其特征在于,包括以下各步骤:

准备在主面侧形成有剥离层的支撑基板;

在上述支撑基板上的比上述剥离层更靠上的位置,局部地形成布线层;

以使半导体芯片的垫的至少一部分与上述布线层的至少一部分电连接的方式将上述半导体芯片配置在上述支撑基板上;

形成包括上述布线层的至少一部分以及上述半导体芯片并且与上述支撑基板上的上述剥离层或者比上述剥离层更靠上的层接触的密封层,在上述支撑基板上,形成包括上述半导体芯片、上述布线层及上述密封层的中间层叠体;

在形成上述中间层叠体后,切断上述支撑基板的周边部;以及

以上述剥离层为边界,从切断上述周边部后的上述支撑基板机械式地剥离上述中间层叠体。

2.根据权利要求1所述的半导体装置的制造方法,其特征在于,

上述支撑基板的上述周边部的上述切断包括以下各步骤:

在上述支撑基板的周边部形成割断预定线;

在与上述割断预定线对应的位置处,从上述支撑基板的主面侧切断形成在上述支撑基板上的上述剥离层及上述密封层;以及

沿上述割断预定线割断上述支撑基板的周边部。

3.根据权利要求2所述的半导体装置的制造方法,其特征在于,

上述割断预定线的形成通过在上述支撑基板的背面形成切割线来进行。

4.根据权利要求3所述的半导体装置的制造方法,其特征在于,

上述切割线的形成在上述支撑基板上形成上述中间层叠体之后进行。

5.根据权利要求3所述的半导体装置的制造方法,其特征在于,

上述切割线的形成在上述支撑基板上形成上述布线层之前进行。

6.根据权利要求2所述的半导体装置的制造方法,其特征在于,

上述割断预定线的形成通过在形成上述剥离层之前在上述支撑基板的主面形成切割线来进行。

7.根据权利要求2所述的半导体装置的制造方法,其特征在于,

上述割断预定线的形成通过在上述支撑基板的内部形成与其它部分相比强度较弱的部分来进行。

8.根据权利要求1至7任一项中所述的半导体装置的制造方法,其特征在于,

作为上述支撑基板,使用在上述主面从基板侧依次形成有金属层、上述剥离层、薄铜层的支撑基板。

9.根据权利要求1至7任一项中所述的半导体装置的制造方法,其特征在于,

进行多次上述布线层的形成,来形成多层布线型的布线层。

10.根据权利要求1至7任一项中所述的半导体装置的制造方法,其特征在于,

在上述支撑基板上,多个并列地形成上述中间层叠体,而且一体地从上述支撑基板剥离上述多个并列地形成的上述中间层叠体,并且在上述剥离后,分别切断上述中间层叠体。

11.根据权利要求1至7任一项中所述的半导体装置的制造方法,其特征在于,

在上述中间层叠体中配置多个上述半导体芯片。

12. 根据权利要求1至7任一项中所述的半导体装置的制造方法，其特征在于，在上述中间层叠体中，与上述半导体芯片一起配置被动零件。

## 半导体装置的制造方法

### 技术领域

[0001] 本发明涉及一种半导体装置的制造方法。

### 背景技术

[0002] 对于所谓的后芯片型(chip-last) (RDL-first型)的半导体装置而言,在暂时使用的临时支撑基板上形成布线层及绝缘层,配置半导体芯片并进行模制,之后经由除去临时支撑基板的工序来制造上述半导体装置。临时支撑基板的除去通过从模制出的半导体芯片、布线层以及绝缘层(以下将它们统称为中间层叠体)机械式地剥下并分离临时支撑基板来进行。

[0003] 专利文献1中公开一种印刷布线板(半导体装置)的制造方法,该方法使用在表面上具备紧贴金属层、剥离层、防反射层以及极薄铜层并由玻璃构成的载体(支撑基板)。

[0004] 现有技术文献

[0005] 专利文献

[0006] 专利文献1:日本专利第6203988号公报

### 发明内容

[0007] 发明所要解决的课题

[0008] 专利文献1中公开以下方法:遍及支撑基板的整个面,一并从支撑基板剥离形成在支撑基板(载体)上的中间层叠体。

[0009] 但是,对于支撑基板的周边部而言,由于成膜条件不稳定,所以难以以稳定的膜厚对布线层、绝缘层进行成膜,并且在用于在周边部形成布线层的电镀工序中,需要使供电机机构(供电用电极)接触,由此容易产生伤痕等。

[0010] 因此,当也包括支撑基板上的周边部在内地进行剥离时,因布线层及绝缘层的不均匀性、伤痕的原因,有在周边部产生剥离不均的担忧。而且,周边部的剥离不均也对形成有模制出半导体芯片和布线层的中间层叠体的基板的中央部分的剥离产生负面影响,从而有使中间层叠体以及包括该中间层叠体的半导体装置的成品率降低的担忧。

[0011] 用于解决课题的方案

[0012] (1) 本发明的第1方案的半导体装置的制造方法包括以下各步骤:准备在正面侧形成有剥离层的支撑基板;在上述支撑基板上的比上述剥离层更靠上的位置,局部地形成布线层;以使半导体芯片的垫的至少一部分与上述布线层的至少一部分电连接的方式将上述半导体芯片配置在上述支撑基板上;形成包括上述布线层的至少一部分以及上述半导体芯片并且与上述支撑基板上的上述剥离层或者比上述剥离层更靠上的层接触的密封层,在上述支撑基板上,形成包括上述半导体芯片、上述布线层及上述密封层的中间层叠体;在形成上述中间层叠体后,切断上述支撑基板的周边部;以及以上述剥离层为边界,从切断上述周边部后的上述支撑基板机械式地剥离上述中间层叠体。

[0013] (2) 本发明的第2方案的半导体装置的制造方法根据第1方案所述的半导体装置的

制造方法,优选为,上述支撑基板的上述周边部的上述切断包括以下各步骤:在上述支撑基板的周边部形成割断预定线;在与上述割断预定线对应的位置处,从上述支撑基板的主面侧切断形成在上述支撑基板上的上述剥离层及上述密封层;以及沿上述割断预定线割断上述支撑基板的周边部。

[0014] (3) 本发明的第3方案的半导体装置的制造方法根据第2方案所述的半导体装置的制造方法,优选为,上述割断预定线的形成通过在上述支撑基板的背面形成切割线来进行。

[0015] (4) 本发明的第4方案的半导体装置的制造方法根据第3方案所述的半导体装置的制造方法,优选为,上述切割线的形成在上述支撑基板上形成上述中间层叠体之后进行。

[0016] (5) 本发明的第5方案的半导体装置的制造方法根据第3方案所述的半导体装置的制造方法,优选为,上述切割线的形成在上述支撑基板上形成上述布线层之前进行。

[0017] (6) 本发明的第6方案的半导体装置的制造方法根据第2方案所述的半导体装置的制造方法,优选为,上述割断预定线的形成通过在形成上述剥离层之前在上述支撑基板的主面形成切割线来进行。

[0018] (7) 本发明的第7方案的半导体装置的制造方法根据第2方案所述的半导体装置的制造方法,优选为,上述割断预定线的形成通过在上述支撑基板的内部形成与其它部分相比强度较弱的部分来进行。

[0019] (8) 本发明的第8方案的半导体装置的制造方法根据第1方案至第7方案中任一方案所述的半导体装置的制造方法,优选为,作为上述支撑基板,使用在上述主面从基板侧依次形成有金属层、上述剥离层、薄铜层的支撑基板。

[0020] (9) 本发明的第9方案的半导体装置的制造方法根据第1方案至第7方案中任一方案所述的半导体装置的制造方法,优选为,进行多次上述布线层的形成,来形成多层布线型的布线层。

[0021] (10) 本发明的第10方案的半导体装置的制造方法根据第1方案至第7方案中任一方案所述的半导体装置的制造方法,优选为,在上述支撑基板上,多个并列地形成上述中间层叠体,而且一体地从上述支撑基板剥离上述多个并列地形成的上述中间层叠体,并且在上述剥离后,分别切断上述中间层叠体。

[0022] (11) 本发明的第11方案的半导体装置的制造方法根据第1方案至第7方案中任一方案所述的半导体装置的制造方法,优选为,在上述中间层叠体中配置多个上述半导体芯片。

[0023] (12) 本发明的第12方案的半导体装置的制造方法根据第1方案至第7方案中任一方案所述的半导体装置的制造方法,优选为,在上述中间层叠体中,与上述半导体芯片一起配置被动零件。

[0024] 发明的效果如下。

[0025] 根据本发明,无论形成于支撑基板的周边部的膜的不均匀性、伤痕如何,都能够稳定地剥离中间层叠体。

## 附图说明

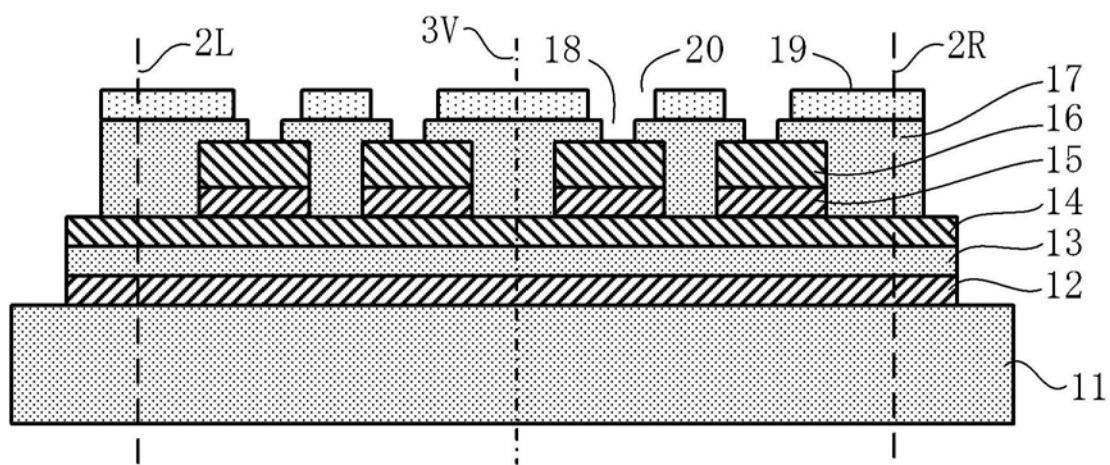

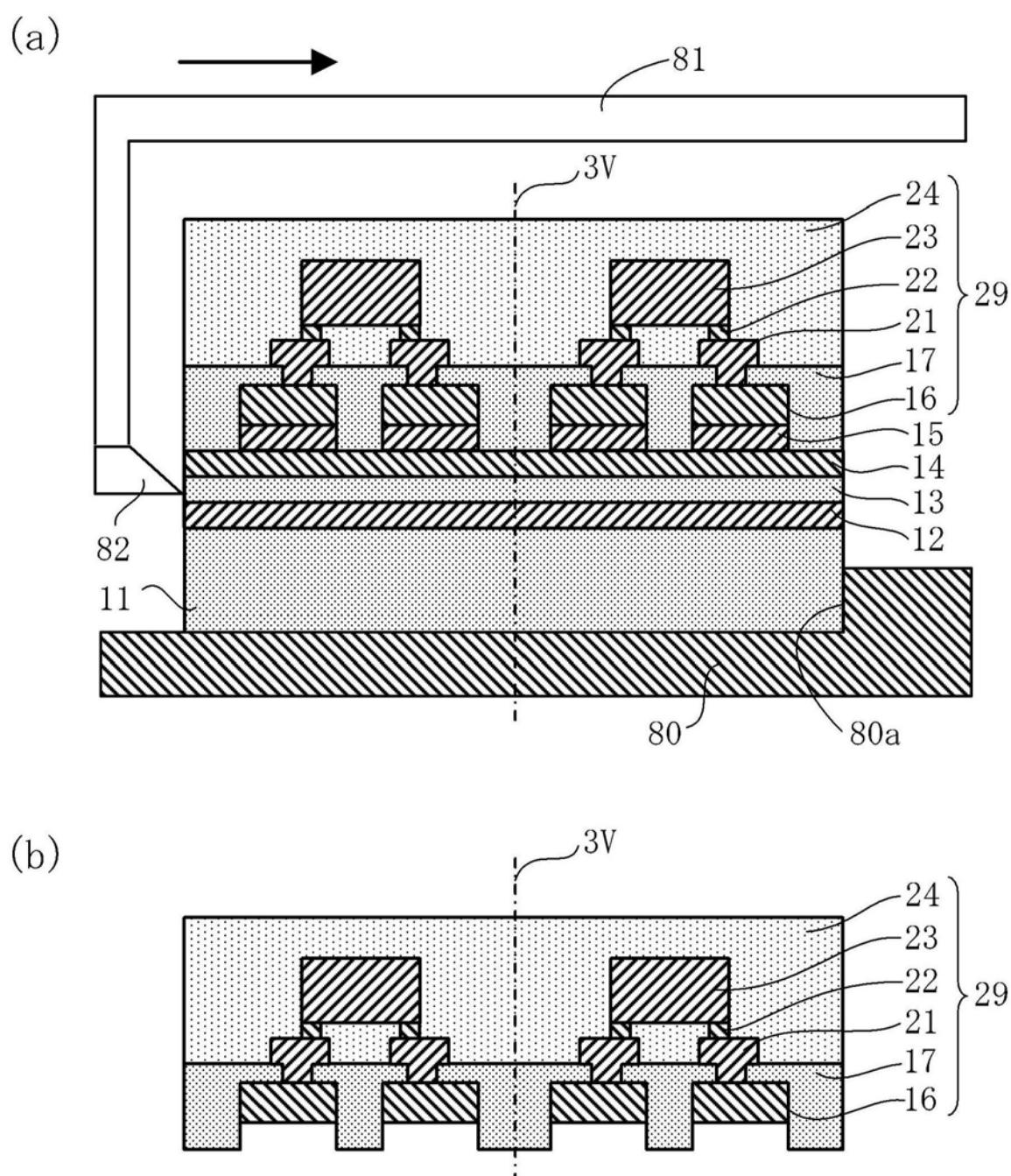

[0026] 图1是说明本发明的第1实施方式的半导体装置的制造方法的图,且是示出前半工序的图。

[0027] 图2是说明本发明的第1实施方式的半导体装置的制造方法的图，且是示出接续图1的工序的图。

[0028] 图3是说明本发明的第1实施方式的半导体装置的制造方法的图，且是示出接续图2的工序的图。

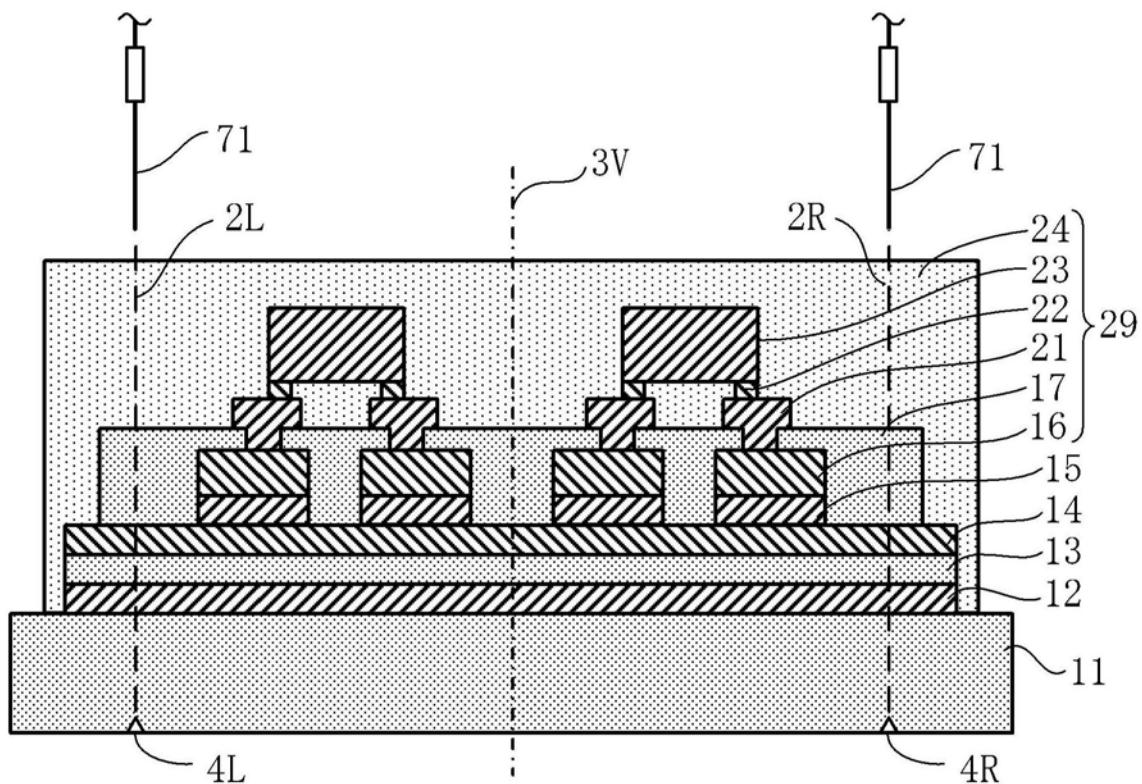

[0029] 图4是说明本发明的第1实施方式的半导体装置的制造方法的图，且是示出接续图3的工序的图。

[0030] 图5是说明本发明的第1实施方式的半导体装置的制造方法的图，且是示出接续图4的工序的图。

[0031] 图6是说明本发明的第1实施方式的半导体装置的制造方法的图，且是示出在支撑基板上并列地形成有多个中间层叠体的状态的图。

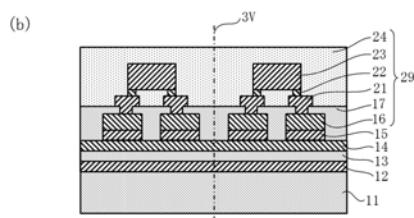

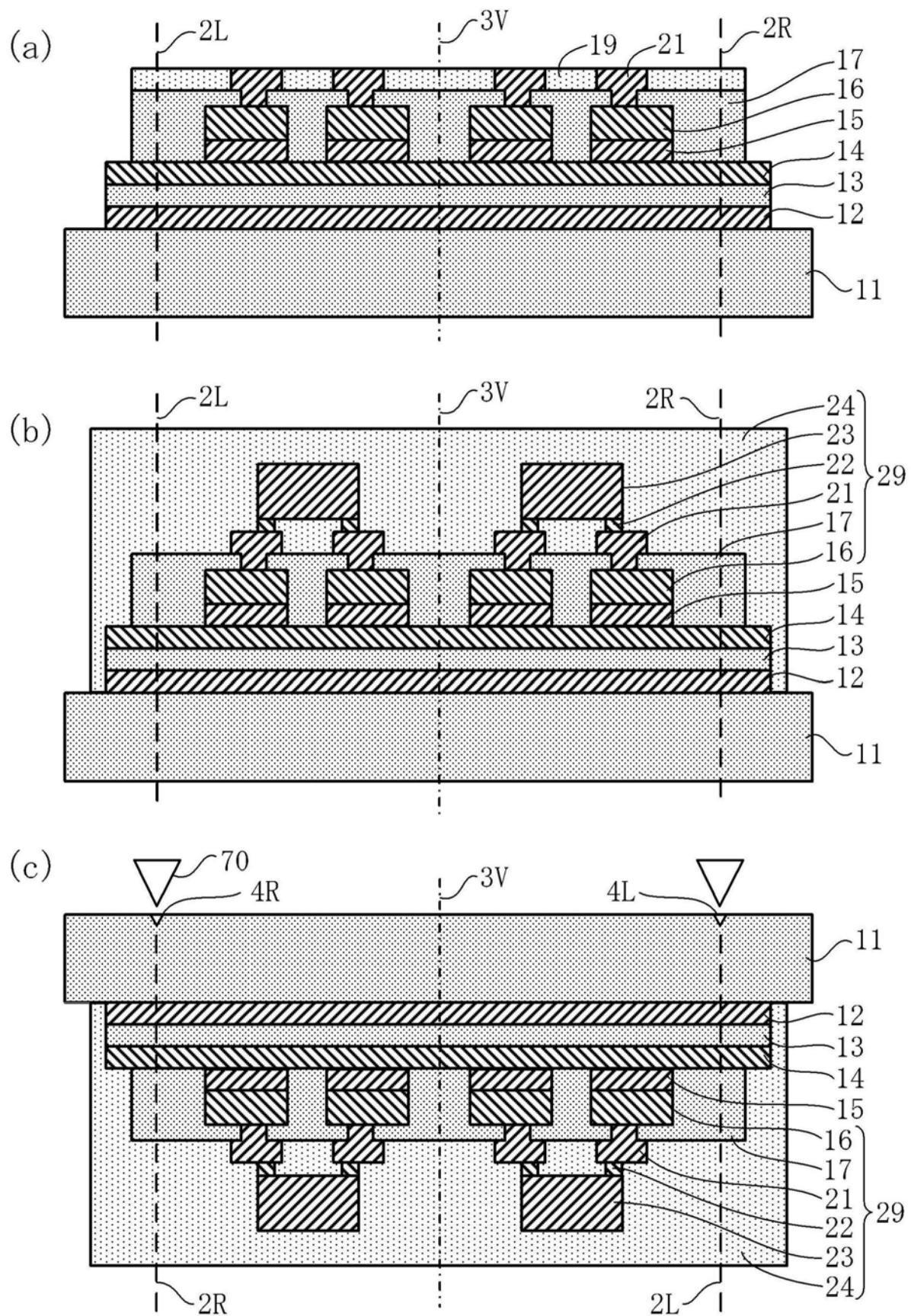

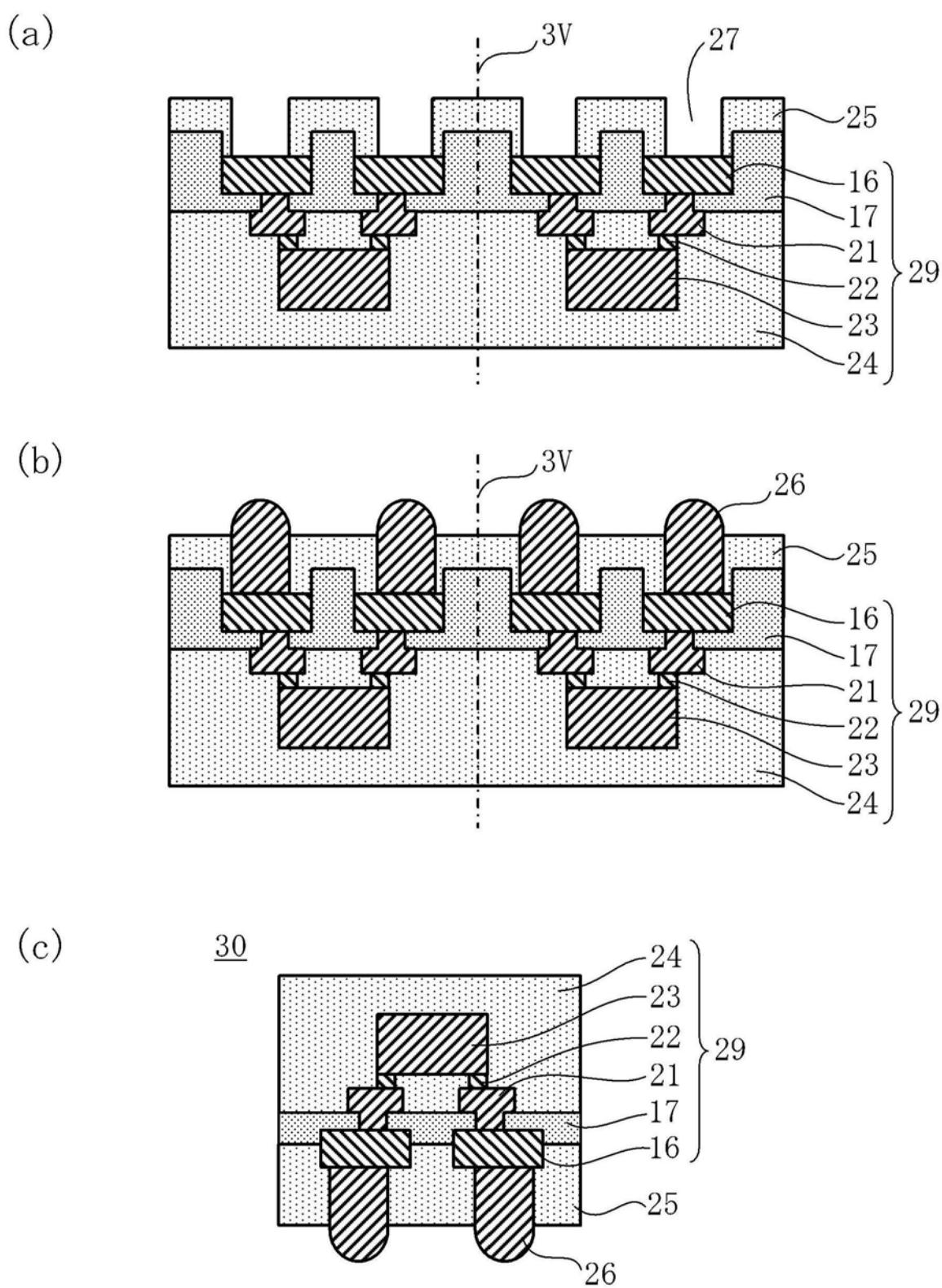

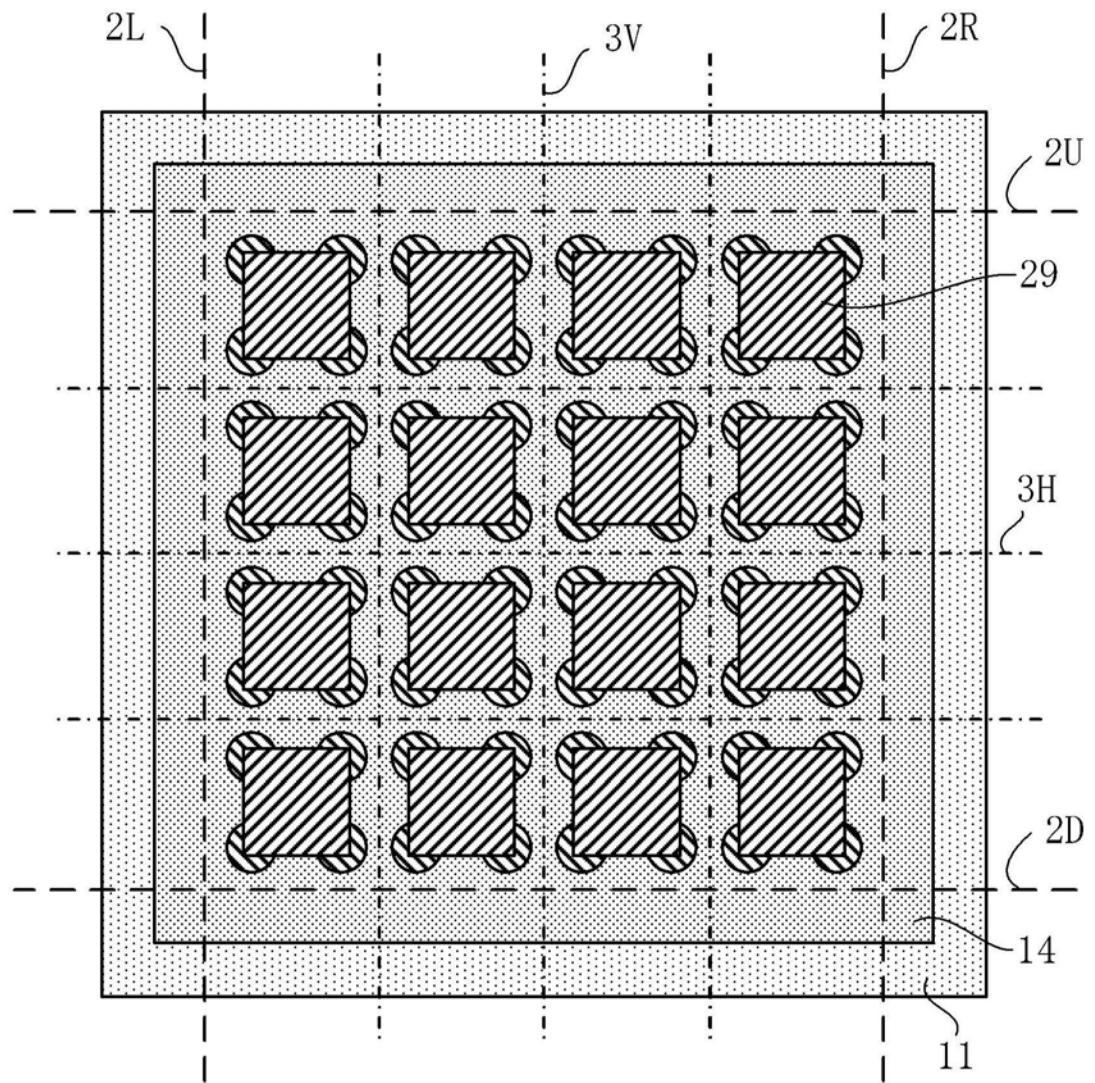

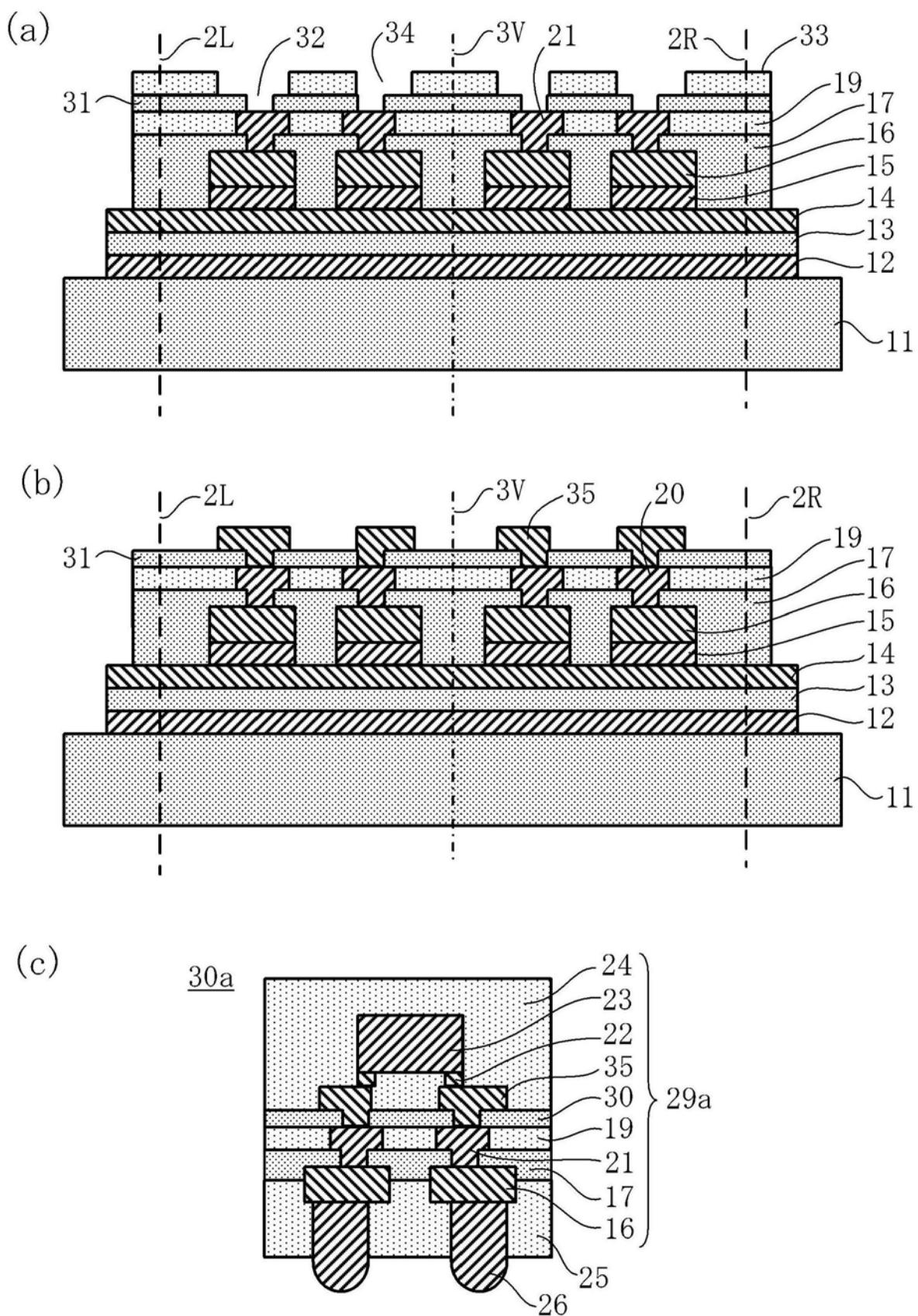

[0032] 图7是说明变形例1至3的半导体装置的制造方法的图。图7的(a)是说明变形例1的图。图7的(b)是说明变形例2的图。图7的(c)是说明变形例3的图。

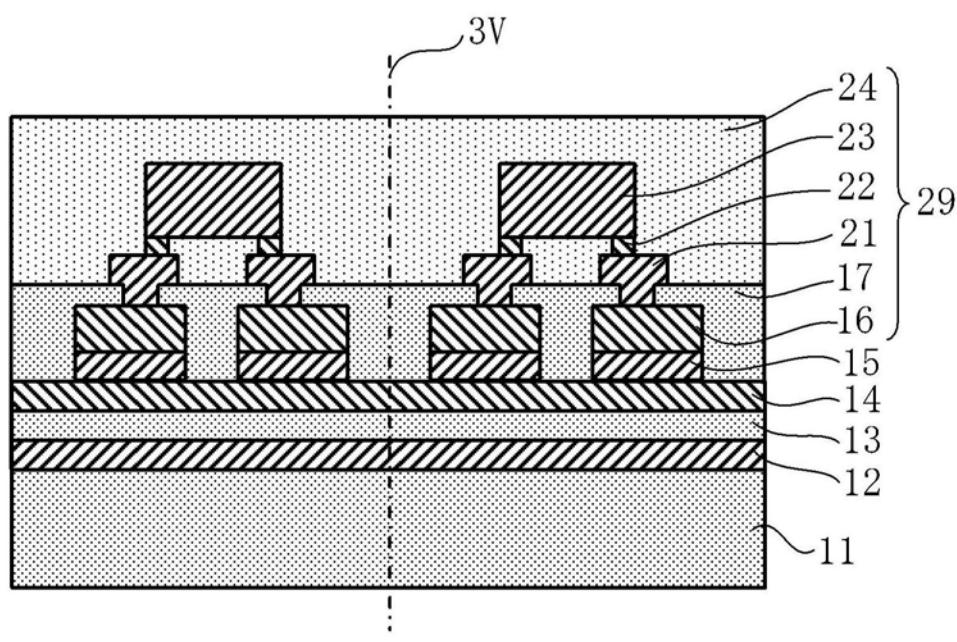

[0033] 图8是说明本发明的第2实施方式的半导体装置的制造方法的图。

## 具体实施方式

[0034] (第1实施方式)

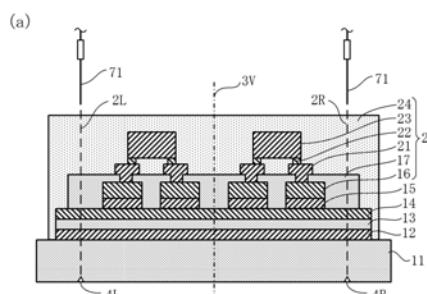

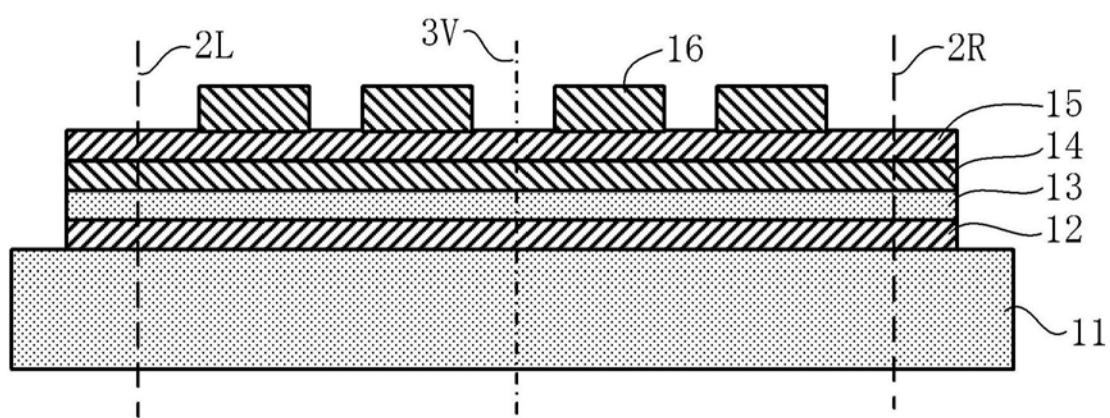

[0035] 图1至图6是用于说明本发明的第1实施方式的半导体装置30的制造方法的图。图1至图5是说明在支撑基板11上形成由布线层16、半导体芯片23、密封层24等构成的中间层叠体29的工序等的剖视图，图6是示出在支撑基板11上并列地形成有多个中间层叠体29的状态的俯视图。但是，图6中省略了下述的密封层24等一部分部件的图示。

[0036] (制造工序的概要)

[0037] 参照图6，说明本例的制造工序的概要。

[0038] 如图6所示，本例中，支撑基板11大致呈正方形，一边为100～300mm左右。而且，本例中，如图6所示，在该支撑基板11上，并列地形成多个包括下述的密封层、半导体芯片以及布线层的中间层叠体29。

[0039] 之后，在图6中虚线所示的左端切断线2L、右端切断线2R、上端切断线2U、下端切断线2D的位置处，切断支撑基板11的周边部。将左端切断线2L、右端切断线2R、上端切断线2U以及下端切断线2D统称为切断线2。

[0040] 在切断周边部后，从支撑基板11一并地剥离并列地形成的多个中间层叠体29。之后，将并列的多个中间层叠体29分别在图6中虚线所示的多个纵向分离线3V、多个横向分离线3H的位置处分离(切割)。将纵向分离线3V及横向分离线3H统称为分离线3。

[0041] 中间层叠体29经由下述的后续工序而完成为半导体装置30。切断线2的位置以及分离线3的间隔根据半导体装置30的大小(面积)来设定。

[0042] 以下，参照图1至图5，说明在支撑基板11上形成由布线层16、半导体芯片23、密封层24等构成的中间层叠体29的工序、以及形成半导体装置30的工序。

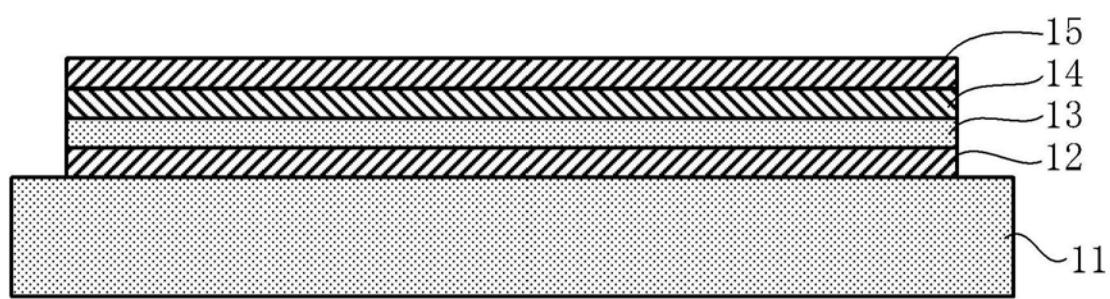

[0043] (支撑基板)

[0044] 图1的(a)是示出制造工序初期时的支撑基板11的截面构造的图。支撑基板11的结构与日本专利第6203988号公报所公开的带载体的铜箔的结构相同。支撑基板11本身由玻璃构成，在其正面(表侧的而且图中上方的面)，从基板侧依次形成有紧贴金属层12、剥离层

13、防反射层14、以及薄铜层15。构成上述的各层的材料、厚度可以与日本专利第6203988号公报所公开的带载体的铜箔的结构相同。

[0045] 即,支撑基板11本身由玻璃构成,其厚度优选为100~2000μm。

[0046] 从确保与支撑基板11的紧贴性的点看,紧贴金属层12优选是由从Ti、Cr以及Ni所构成的组中选择的至少一种金属构成的层,可以是纯金属,也可以是合金。紧贴金属层12的厚度优选为10~300nm左右。

[0047] 从易剥离性、膜形成性等观点看,剥离层13优选为主要包含碳来构成的层,更优选为主要由碳或烃构成的层,进一步优选为由作为硬质碳膜的非晶碳构成。剥离层13的厚度优选为1~20nm左右。

[0048] 防反射层14由从Cr、W、Ta、Ti、Ni以及Mo所构成的组中选择的至少一种金属构成。防反射层14的厚度优选为10~300nm左右。此外,由于防反射层14是为了提高制造工序中的布线层的图像检查的精度而设置的层,所以在不需要利用图像进行的检查工序的情况下等下也可以省略。

[0049] 薄铜层15是以厚度为50~2000nm左右的铜为主成分的层。薄铜层15优选通过真空蒸镀、溅射或者电镀来形成。

[0050] 并且,紧贴金属层12、剥离层13、防反射层14也优选利用溅射等来形成。

[0051] 再者,若形成有适于上述条件的剥离层13等的支撑基板11在市面上贩卖,则也可以购入即准备该支撑基板11来使用。

[0052] (下层垫的形成)

[0053] 图1的(b)示出以下状态:在作为支撑基板11上的最上层的薄铜层15之上形成有成为半导体装置30的一部分的下层垫16。当形成下层垫16时,首先在薄铜层15上的整个面形成未图示的光致抗蚀剂层,并在该光致抗蚀剂层形成与下层垫16的形状对应的所希望的图案。

[0054] 之后,在比切断线2更靠外侧的支撑基板11上的薄铜层15安装供电用电极,将支撑基板11浸渍在电镀液中并进行镀铜等电镀,从而在薄铜层15所露出的部分(即未由光致抗蚀剂覆盖的部分)形成下层垫16。之后,除去光致抗蚀剂。

[0055] 图1的(b)示出在形成下层垫16后除去光致抗蚀剂后状态。

[0056] 下层垫16的厚度优选为5~200μm左右,下层垫16的直径优选为30~200μm左右。下层垫16的上表面形状可以呈圆形也可以呈多边形。

[0057] 为了提高下层垫16与下述的层间绝缘膜17的紧贴性,也可以对下层垫16的表面及侧面进行粗糙化处理,或者也可以形成耦合剂来提高两者的紧贴性。

[0058] 并且,基于上述的工序,也能够利用形成于光致抗蚀剂的图案的形状,在形成下层垫16的同时,形成用于使支撑基板11上的不同的两处电导通的布线。

[0059] (层间绝缘膜的形成)

[0060] 图1的(c)示出以下状态:以覆盖下层垫16的方式在支撑基板11上形成有层间绝缘膜17,并在其上形成有干膜抗蚀剂19。作为层间绝缘膜17的材料,使用含80%以上硅填料的环氧树脂等。层间绝缘膜17利用打印法、压缩成型法、或者对片状的树脂膜进行真空层压的方法来形成,并在形成后进行某程度的固化处理。

[0061] 在以覆盖下层垫16的方式形成层间绝缘膜17后,在层间绝缘膜17的预定部位,利

用基于激光照射的消融等来形成用于形成通路的贯通孔18，另外进行将伴随贯通孔的形成而产生的残渣去除的去渣处理。而且，通过化学镀或者溅射，在形成有贯通孔18的层间绝缘膜17之上形成由铜等金属构成的未图示的电镀种子层。

[0062] 而且，在其上形成干膜抗蚀剂19，并利用基于激光照射的消融等，在干膜抗蚀剂19内的预定部位且与贯通孔18局部重叠的部位形成开口20。

[0063] 图1的(c)示出形成有开口20的状态。

[0064] (上层垫的形成)

[0065] 在比切断线2更靠外侧的支撑基板11上的层间绝缘膜17之上形成的上述的未图示的电镀种子层安装供电用电极。而且，通过将支撑基板11浸渍在电镀液中并进行镀铜等电镀，来使铜等金属堆积在贯通孔18及开口20的内部，从而形成通路及上层垫21(以下，一并地称作上层垫21)。

[0066] 图2的(a)示出在贯通孔18及开口20的内部形成有上层垫21的状态。

[0067] 此外，下层垫16和上层垫21均是导电性的部件，从而也能够将它们称作布线层。

[0068] (蚀刻)

[0069] 之后，除去干膜抗蚀剂19，进行层间绝缘膜17的固化处理。并且，进行形成在层间绝缘膜17上的上述的未图示的电镀种子层的除去(蚀刻)。它们的除去用公知的一般方法来进行即可。

[0070] (半导体芯片的接合及密封)

[0071] 图2的(b)表示以下状态：在上述形成的支撑基板11上的层叠物(下层垫16、上层垫21以及层间绝缘膜17)之上，接合半导体芯片23，并用密封层24密封了半导体芯片23。

[0072] 在接合半导体芯片23时，预先形成有带焊锡的铜柱22作为半导体芯片23的电极端子，并以使各铜柱22重叠在预定的上层垫21上的方式配置半导体芯片23。而且，使用助焊剂来临时固定铜柱22和上层垫21，之后接合C4(Controlled Collapse Chip Connection)。

[0073] 铜柱22与上层垫21的接合也可以通过超声波接合来进行。并且，也可以在半导体芯片23预先形成有焊球凸块、微焊凸块来代替带焊锡的铜柱22。

[0074] 之后，以覆盖半导体芯片23及支撑基板11的正面(图2的(b)中的上侧的面)的方式，利用压缩成型法等来形成基于树脂的密封层24。密封层24也覆盖下层垫16、上层垫21以及层间绝缘膜17的上表面、侧面，也覆盖形成在支撑基板11上的剥离层13或者位于比剥离层13更靠上层的防反射层14。

[0075] 通过以上工序，在支撑基板11上形成由密封层24、半导体芯片23、铜柱22、布线层(上层垫21及下层垫16)、层间绝缘膜17构成的中间层叠体29。

[0076] (支撑基板的周边部的切断)

[0077] 在形成中间层叠体29后，切断支撑基板11的周边部。即，切断支撑基板11中比图6所示的上述的切断线2更靠外侧的部分。

[0078] 图2的(c)示出为了切断周边部而将形成有中间层叠体29的正面朝向下侧配置的支撑基板11。此外，图2的(b)和图2的(c)中，由于支撑基板11以垂直于纸面的线为旋转中心旋转180度，所以替换右端切断线2R与左端切断线2L的位置关系。

[0079] 当切断周边部时，首先，利用划线轮70，在支撑基板11的背面(与上述正面相反的一侧的面)的相当于右端切断线2R和左端切断线2L的部分，形成作为微小的伤痕的切割线

4R、4L。

[0080] 同样,在支撑基板11的背面的相当于上端切断线2U和下端切断线2D的部分,也形成切割线。

[0081] 图3的(a)表示在切断周边部后使上下正转来配置的支撑基板11。在切断周边部后,使用切割机71在相当于左端切断线2L及右端切断线2R的部分处切断支撑基板11的主面侧的密封层24等层叠物。

[0082] 同样,也在相当于上端切断线2U和下端切断线2D的部分处,切断支撑基板11的主面侧的密封层24等层叠物。

[0083] 切割机71所进行的切断以密封层24、层间绝缘膜17、防反射层14、剥离层13、紧贴金属层12为对象,但当然也可以局部地切入到支撑基板11的主面附近。由于切断后的层叠物紧贴于支撑基板11的周边部(比切断线2更靠外侧)的主面,所以支撑基板11的周边部与支撑基板11相连,在此基础上,即使切断,也不会立即从支撑基板11离开。

[0084] 通过对该状态下的支撑基板11在周边部(比切断线2更靠外周部)施加击力,来在切断线2的位置处割断(割裂)支撑基板11。

[0085] 图3的(b)示出割断周边部后的状态下的支撑基板11及中间层叠体29。如图3的(b)所示,剥离层13的端部明确地露出于中间层叠体29的切截面。

[0086] 此外,由于切割线4R、4L是为了进行该割断(割裂)而形成的裂缝,所以也能够被视为割断预定线。

[0087] (中间层叠体从支撑基板的剥离)

[0088] 图4的(a)示出将割断周边部后的支撑基板11及中间层叠体29安装于剥离装置(80、81)来从支撑基板11剥离中间层叠体29的状态。

[0089] 作为一例,剥离装置是具备载置支撑基板11的载置台80、以及设有针状件等裂纹引发器82的剥离臂81的装置。

[0090] 在中间层叠体29的剥离中,首先,将支撑基板11的一方端(图4的(b)中为右端)固定于载置台80上的卡定部80a。而且,使裂纹引发器82的前端与形成在支撑基板11上的剥离层13的附近接触,并将其压入到支撑基板11上,从而形成剥离开始点。而且,通过使剥离臂81相对于载置台80向图中右方向相对移动,来从支撑基板11剥离中间层叠体29。

[0091] 本例中,由于在支撑基板11与中间层叠体29之间形成有剥离层13,所以能够以剥离层13为边界面,从支撑基板11均匀地剥离中间层叠体29。

[0092] 接着,从自支撑基板11剥离出的中间层叠体29,除去残存于剥离面的剥离层13的残骸、防反射层14、以及薄铜层15。

[0093] 图4的(b)示出从支撑基板11剥离并除去剥离层13的残骸、防反射层14、薄铜层15后的中间层叠体29。剥离层13的残骸、防反射层14、以及薄铜层15的除去也能够使用蚀刻等公知的一般除去方法。

[0094] (焊锡球的形成)

[0095] 图5的(a)示出以下状态:为了在中间层叠体29的下层垫16形成焊锡球,而在层间绝缘膜17之上形成阻焊剂25,并在下层垫16上的阻焊剂25形成有开口27。图5的(a)中,中间层叠体29从图4的(b)所示的状态旋转(上下反转)来表示。

[0096] 之后,将助焊剂涂覆在阻焊剂25的开口27上,将焊锡球26临时固定在下层垫16上,

之后进行回流来固定焊锡球26。

[0097] 图5的(b)示出固定有焊锡球26的状态的中间层叠体29。

[0098] (切割)

[0099] 之后,用电路测试器等测定多个并列、即多个连续的状态下的各个中间层叠体29,并使用切割机来进行切割(形成单片)。

[0100] 图5的(c)示出切割完成后的状态的半导体装置30。

[0101] 此外,图1至图5的各图中,为了容易说明,相对于支撑基板11的面内方向的长度而放大地示出厚度方向的长度。

[0102] 并且,在上述的第1实施方式中,设为在支撑基板11上左右形成两个中间层叠体29,但形成在支撑基板11上的中间层叠体29的排列个数不限定于此,能够形成更多个中间层叠体29。

[0103] 此外,根据制造的半导体装置30的用途,也可以省略上述的焊锡球的形成工序。

[0104] (变形例)

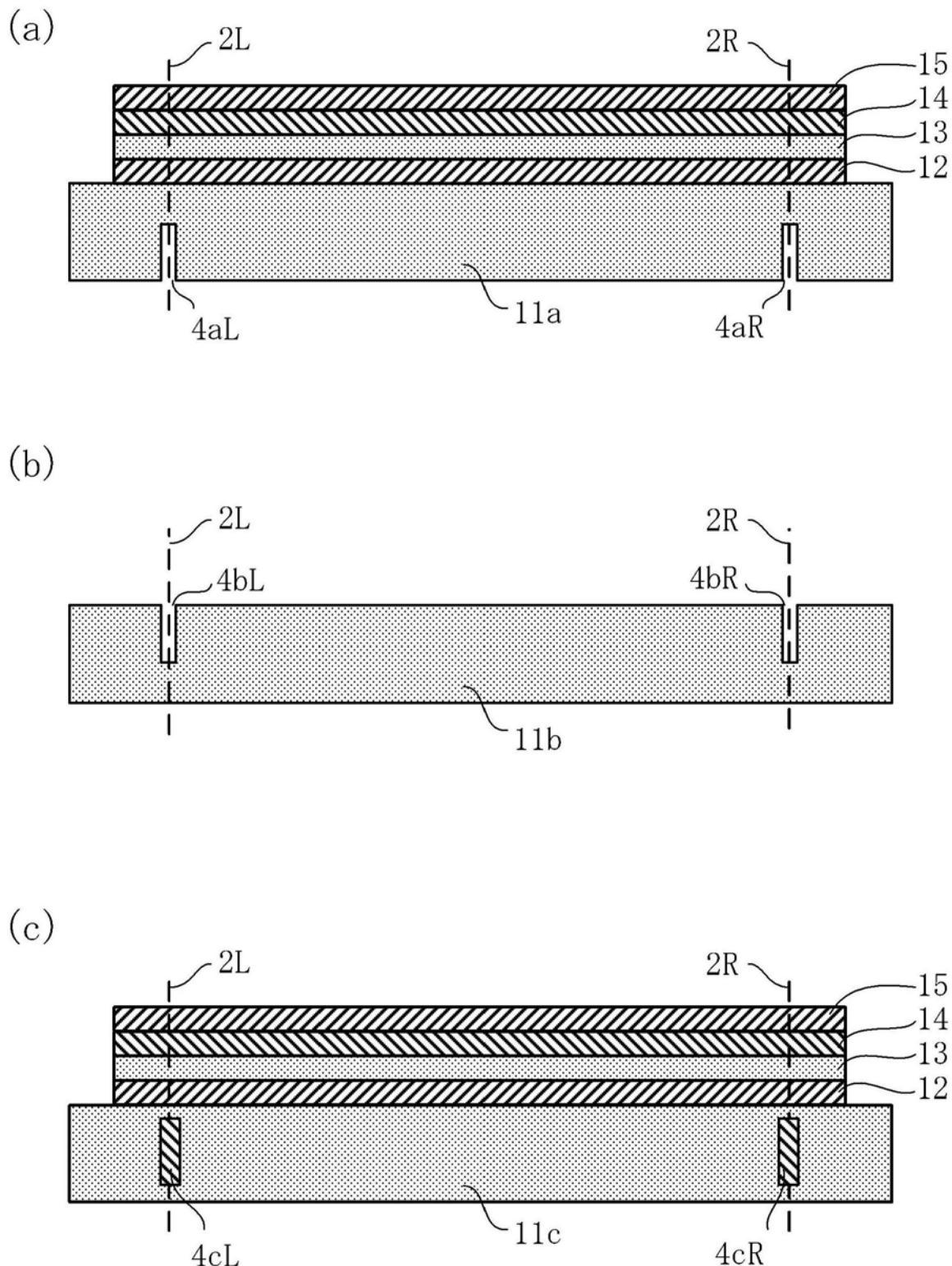

[0105] 以下,参照图7,说明变形例1至4。

[0106] 以下的变形例是与支撑基板11的切断方法相关的变形例。因而,除支撑基板11的切断方法以外,与上述的第1实施方式相同,从而省略说明。

[0107] (变形例1)

[0108] 图7的(a)示出在变形例1中使用的支撑基板11a。

[0109] 与在上述的第1实施方式中使用的支撑基板11相同,在支撑基板11a的正面,从基板侧依次形成有紧贴金属层12、剥离层13、防反射层14、以及薄铜层15。但是,在其背面(与上述的正面相反的一侧的面)且在相当于左端切断线2L及右端切断线2R等切断线2的位置,预先形成有切割线4aL及4aR。

[0110] 因此,本变形例1中,能够减少在半导体装置的制造工序中在支撑基板11a的背面形成切割线的工序(例如参照图(c))。

[0111] 切割线4aL及4aR、紧贴金属层12、剥离层13、防反射层14以及薄铜层15可以任一个先形成。但是,切割线4aL及4aR优选在于支撑基板11a上形成布线层(下层垫16)之前进行。

[0112] 此外,与上述的第1实施方式中的切割线4L及4R相同,变形例1的切割线4aL及4aR也能够被视为割断预定线。

[0113] (变形例2)

[0114] 图7的(b)示出在变形例2中使用的支撑基板11b。

[0115] 变形例2中,在支撑基板11b的正面的相当于左端切断线2L及右端切断线2R等切断线2的位置,预先形成有切割线4bL及4bR。而且,之后,在其正面,从基板侧依次预先形成有紧贴金属层12、剥离层13、防反射层14、以及薄铜层15,但对此未图示。

[0116] 即使是形成于支撑基板11b的正面的切割线,也与形成于背面的切割线相同地作为割断(割裂)的开始点发挥功能,从而本变形例2中,也能够减少在半导体装置的制造工序中在支撑基板11b的背面形成切割线的工序。

[0117] 此外,与上述的第1实施方式中的切割线4L及4R相同,变形例2的切割线4bL及4bR也能够被视为割断预定线。

[0118] (变形例3)

[0119] 图7的(c)示出在变形例3中使用的支撑基板11c。

[0120] 与在上述的第1实施方式中使用的支撑基板11相同，在支撑基板11c的正面，从基板侧依次形成有紧贴金属层12、剥离层13、防反射层14、以及薄铜层15。而且，在支撑基板11c的内部的相当于左端切断线2L及右端切断线2R等切断线2的位置，预先形成有与其它部分相比强度较弱的劣化部分4cL及4cR。

[0121] 该劣化部分4cL及4cR能够通过例如相对于玻璃制的支撑基板11c向劣化部分聚光地照射激光来形成。

[0122] 由于劣化部分4cL及4cR作为割断(割裂)的开始点发挥功能，所以在本变形例3中，也能够减少在半导体装置的制造工序中在支撑基板11c的背面形成切割线的工序。

[0123] 此外，与上述的第1实施方式中的切割线4L及4R相同，变形例3的劣化部分4cL及4cR也能够被视为割断预定线。

[0124] (变形例4)

[0125] 变形例4中，当切断支撑基板11的周边部时，并非在支撑基板11设置切割线来进行割断，而是使用切割机来切断支撑基板11整体。

[0126] 因而，与上述的第1实施方式、各变形例相比，在变形例4中，能够减少形成切割线的工序(例如参照图2的(c))、割断的工序，从而简化切断工序。

[0127] (第1实施方式以及变形例1至4的效果)

[0128] 根据以上的第1实施方式以及变形例1至4，得到以下的效果。

[0129] (1) 本实施方式的半导体装置30的制造方法包括以下各步骤：准备在正面侧形成有剥离层13的支撑基板11；在支撑基板11上的比剥离层13更靠上的位置，局部地形成布线层(下层垫16、上层垫21)；将半导体芯片23配置在支撑基板11上；形成包括布线层(下层垫16、上层垫21)的至少一部分以及半导体芯片23并且与支撑基板11上的剥离层13或者比该剥离层13更靠上的层接触的密封层24，并在支撑基板11上形成包括半导体芯片23、布线层16、21及密封层24在内的中间层叠体29；在形成中间层叠体29后，切断支撑基板11的周边部；以及以剥离层13为边界，从切断周边部后的支撑基板11机械式地剥离中间层叠体29。

[0130] 由于设为这样的制造方法，即使在支撑基板11的周边部产生膜不均、电镀电极的接触所引起的伤痕，上述负面影响也不会波及支撑基板11的中央部，能够稳定地从支撑基板11剥离中间层叠体29。其结果，能够提高中间层叠体29以及包括该中间层叠体的半导体装置的成品率。

[0131] (2) 另外，经由以下各步骤来进行支撑基板11的周边部的切断：在支撑基板11的周边部形成割断预定线；在与割断预定线对应的位置处，从支撑基板11的正面侧切断形成在支撑基板11上的剥离层13及密封层24；以及沿割断预定线割断支撑基板11的周边部，由此能够更稳定地进行支撑基板11的周边部的切断，进一步提高成品率。

[0132] (3) 另外，作为支撑基板11，使用在其正面从基板侧依次形成有金属层12、剥离层13、薄铜层14的支撑基板，从而能够更稳定地实现从剥离层13的剥离。

[0133] (4) 另外，构成为在支撑基板11上，多个并列地形成中间层叠体29，而且一体地从支撑基板11剥离多个并列地形成的中间层叠体29，并且在剥离后，分别切断中间层叠体29，从而能够实现生产效率较高的制造方法。

[0134] (第2实施方式)

[0135] 参照图8,说明半导体装置30a的制造方法的第2实施方式。

[0136] 在第2实施方式中,形成的布线层的层数为三层。此外,除以下说明的位置之外,第2实施方式的制造工序也与上述的第1实施方式相同。

[0137] 本变形例中,当在上述的第1实施方式中形成上层垫21并除去干膜抗蚀剂19后(即在从图2的(a)所示的状态除去干膜抗蚀剂19后),在上层垫21及层间绝缘膜17之上形成第2层间绝缘膜31,并在第2层间绝缘膜31的预定部分形成贯通孔32。

[0138] 在形成贯通孔32后的第2层间绝缘膜31上,通过化学镀或溅射,形成由铜等金属构成的未图示的电镀种子层。

[0139] 而且,在其上形成干膜抗蚀剂33,并在干膜抗蚀剂33内的预定部位形成开口34。图7的(a)示出形成有开口34的状态。

[0140] 之后,通过进行镀铜等电镀,来使铜等金属堆积在贯通孔32及开口34的内部,从而形成最上层垫35。此外,由于最上层垫35也是导电性的部件,所以也能够被视为上述的布线层的一部分。

[0141] 而且,除去干膜抗蚀剂33,进行第2层间绝缘膜31的固化处理。并且,进行形成在第2层间绝缘膜31上的上述的未图示的电镀种子层的除去(蚀刻)。

[0142] 图7的(b)示出形成有最上层垫35并除去干膜抗蚀剂33后的状态。

[0143] 之后,通过进行与在上述的实施方式中示出的(半导体芯片的接合及密封)的工序之后相同的工序,能够制造图7的(c)所示的布线层的层数为三层(下层垫16、上层垫21、最上层垫35)的半导体装置30a。

[0144] 此外,通过将与相对于上述的第1实施方式在第2实施方式中增加的工序相同的工序进一步追加到第2实施方式,能够制造布线层的层数为四层以上的半导体装置。

[0145] (第2实施方式的效果)

[0146] 根据以上的第2实施方式的制造方法,除了上述的第1实施方式及变形例1至4的效果之外,还有能够以较高的成品率来制造具有三层布线层的半导体装置的效果。

[0147] 在以上的各实施方式及变形例中,支撑基板11本身设为由玻璃制成,但支撑基板11本身也可以使用由陶瓷、树脂、或者金属中任一种构成的基板。并且,支撑基板11的形状也不限于正方形,也可以呈长方形、圆形等其它形状。

[0148] 并且,下层垫16、上层垫21、最上层垫35不限定于铜,也可以由其它金属形成。各种光致抗蚀剂也可以是感光性的干膜,并且也可以通过激光消融来形成图案。

[0149] 并且,在各中间层叠体29中配置的半导体芯片23不限定于一个,也可以将多个半导体芯片23配置于一个中间层叠体29中。由此能够实现更高性能的中间层叠体29及半导体装置30。

[0150] 再者,在各中间层叠体29中配置的电子器件不限定于半导体芯片23,也可以与半导体芯片23一起配置电容器、线圈、天线等被动零件。由此能够实现具有在仅半导体芯片23的情况下无法实现的功能的高功能的中间层叠体29及半导体装置30。

[0151] 本发明不限定于以上的内容。在本发明的技术思想的范围内能想到的其它方式也包括在本发明的范围内。

[0152] 以下优先权基础申请的公开内容作为引用文而录入本说明书中。

[0153] 日本专利申请2018年第019434号(2018年2月6日申请)

[0154] 符号的说明

[0155] 30、30a—半导体装置,11、11a、11b、11c—支撑基板,12—金属层,13—剥离层,14—防反射层,15—薄铜层,16—下层垫(布线层),17—层间绝缘膜,19—抗蚀剂,21—上层垫(布线层),23—半导体芯片,24—密封层,2—切断线,3—分离线,29—中间层叠体。

(a)

(b)

(c)

图1

图2

(a)

(b)

图3

图4

图5

图6

图7

图8