(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 103 10 779 B4 2007.04.05

(12)

## Patentschrift

(21) Aktenzeichen: **103 10 779.7**

(22) Anmelddatum: **12.03.2003**

(43) Offenlegungstag: **20.11.2003**

(45) Veröffentlichungstag

der Patenterteilung: **05.04.2007**

(51) Int Cl.<sup>8</sup>: **G11C 11/22 (2006.01)**

**G11C 16/02 (2006.01)**

**G11C 7/02 (2006.01)**

**G11C 5/14 (2006.01)**

**G11C 7/22 (2006.01)**

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 2 Patentkostengesetz).

(30) Unionspriorität:

**10/103,360**      **21.03.2002**      **US**

(73) Patentinhaber:

**Infineon Technologies AG, 81669 München, DE;**

**Kabushiki Kaisha Toshiba, Tokio/Tokyo, JP**

(74) Vertreter:

**Epping Hermann Fischer,**

**Patentanwaltsgeellschaft mbH, 80339 München**

(72) Erfinder:

**Takashima, Daisaburo, Kawasaki, Kanagawa, JP;**

**Shiratake, Shinichiro, Yokohama, JP; Joachim,**

**Hans-Oliver, Dr., Zushi, Kanagawa, JP; Roehr,**

**Thomas, Dr., Yokohama, Kanagawa, JP**

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

**DE 197 24 449 A1**

**US 62 75 425 B1**

**US 61 15 319**

**US 59 40 333**

**US 58 35 438**

**TAKASHIMA, D.; KUNISHIMA, I.: "High-density chain ferroelectric random access memory (chain FRAM)"**

**IEEE Journal of Solid-State Circuits, Bd. 33,**

**Nr. 5, Mai 1998, 787-792;**

### (54) Bezeichnung: **Integrierte Speicherschaltung mit erhöhter Zuverlässigkeit**

(57) Hauptanspruch: Integrierte Speicherschaltung, in der Speicherzellen in Ketten gruppiert sind, wobei eine Speicherkette mehrere Speicherzellen enthält, die zur Bildung der Kette in Reihe gekoppelt sind, und wobei jede der Speicherzellen der Kette einen Transistor enthält, der parallel an einen ferroelektrischen Kondensator gekoppelt ist, umfassend:

Wortleitungen der integrierten Speicherschaltung, die während eines Standby-Modus auf einem ersten Spannungspegel von logisch 1 gehalten werden;

von denen Wortleitungen, die nicht-ausgewählten Speicherzellen zugeordnet sind, als Vorbereitung auf einen Speicherzugriff auf einen zweiten Spannungspegel von logisch 1 angehoben werden, wobei der zweite Spannungspegel von logisch 1 oberhalb des ersten Spannungspegels von logisch 1 liegt;

von denen Wortleitungen, die einer ausgewählten Speicherzelle zugeordnet ist, von dem ersten Spannungspegel von logisch 1 auf eine logische 0 abgesenkt werden;

wobei die ausgewählte Speicherzelle der Speicherkette an eine Bitleitung gekoppelt wird und ein einer in der ausgewählten Speicherzelle gespeicherten Information repräsentierendes Signal auf die Bitleitung ausgegeben wird;...

**Beschreibung****GEBIET DER ERFINDUNG**

**[0001]** Die vorliegende Erfindung betrifft ferroelektrische integrierte Speicherschaltungen (ICs). Insbesondere betrifft die Erfindung die Erhöhung der Zuverlässigkeit von in einer verketteten Architektur konfigurierten ferroelektrischen Speicher-ICs.

**Stand der Technik****HINTERGRUND DER ERFINDUNG**

**[0002]** Ferroelektrische Metallocid-Keramikmaterialien wie etwa Bleizirkonattitanat (PZT) sind im Hinblick auf ihre Verwendung für ferroelektrische Kondensatoren von Halbleiterspeicherbauelementen untersucht worden. Es können auch andere ferroelektrische Materialien verwendet werden, beispielsweise unter anderem Strontiumbismuttantalat (SBT) oder Bismutlanthanattitanat (BLT). Das ferroelektrische Material wird zwischen zwei Elektroden angeordnet, so daß ein ferroelektrischer Kondensator zur Speicherung von Informationen gebildet wird. Der ferroelektrische Kondensator verwendet die Hysteresepolarisations-eigenschaft des ferroelektrischen Materials zum Speichern von Informationen. Der in der Speicherzelle gespeicherte Logikwert hängt von der Polarisation des ferroelektrischen Kondensators ab. Um die Polarisation des Kondensators zu ändern, ist an seine Elektroden eine Spannung anzulegen, die größer ist als die Schaltspannung (Koerzitivspannung). Die Polarisation des Kondensators hängt von der Polarität der angelegten Spannung ab. Ein Vorteil des ferroelektrischen Kondensators besteht darin, daß er selbst nach dem Entfernen des Stroms seinen Polarisationszustand beibehält, so daß er eine nichtflüchtige Speicherzelle darstellt.

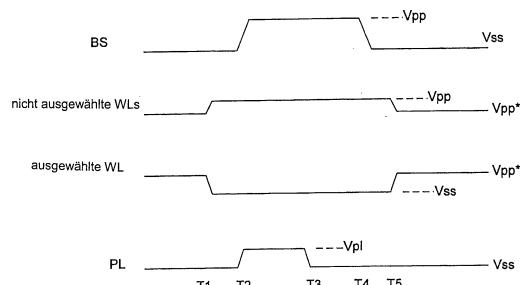

**[0003]** Fig. 1 zeigt mehrere Speicherzellen **105**. Die Speicherzellen umfassen jeweils einen Transistor **130**, der parallel an einen ferroelektrischen Kondensator **140** gekoppelt ist. Die Speicherzellen sind in Reihe gekoppelt, um eine Kette **103** zu bilden. Verkettete Speicherarchitekturen werden beispielsweise in Takashima et al., "High Density Chain ferroelectric random access Memory (chain FRAM)", IEEE Journal of Solid State Circuits, Band 33, Seiten 787-792, 5/1998, beschrieben, was durch Bezugnahme für alle Zwecke hier aufgenommen ist. Ein Ende einer Kette ist über einen Auswahltransistor **108** an eine Bitleitung **160** gekoppelt, während das andere Ende an eine Plattenleitung **170** gekoppelt ist. Die Gates der Transistoren sind an jeweilige Wortleitungen **150** gekoppelt. Die Bitleitung ist an eine Leseverstärkerschaltung gekoppelt, um Speicherzugriffe zu erleichtern (z.B. Lese- und Schreibvorgänge).

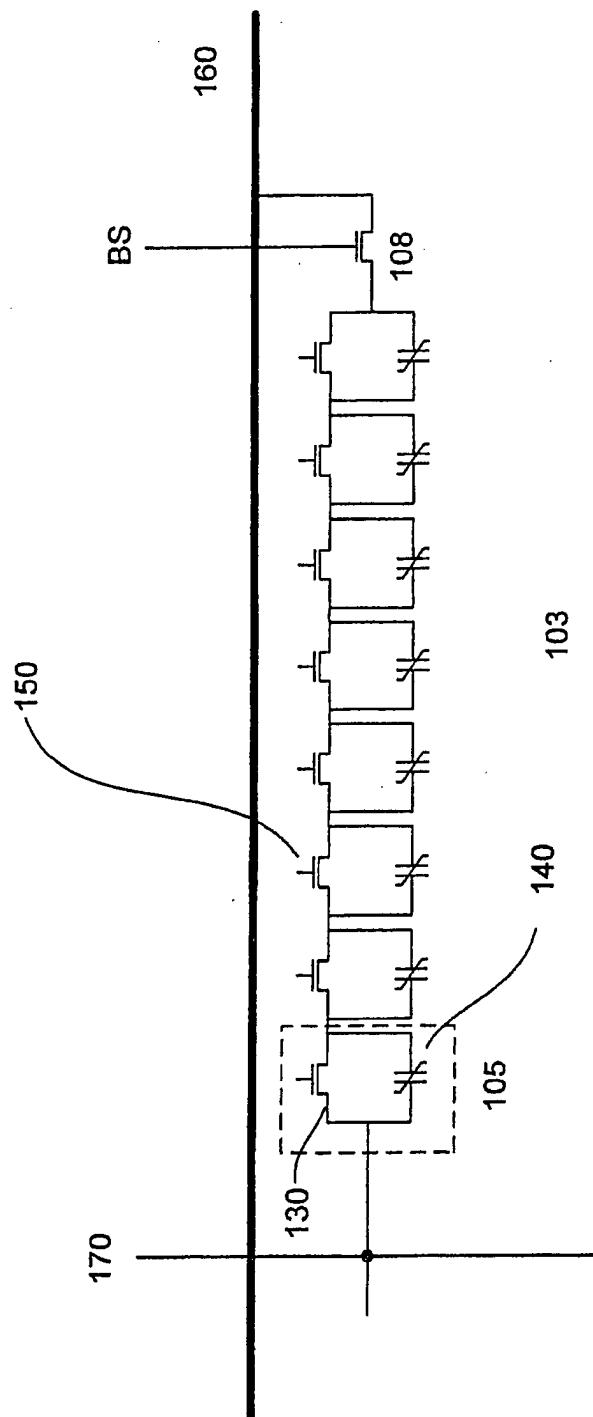

**[0004]** Fig. 2 zeigt ein Zeitablaufdiagramm einer Le-

seoperation zum Zugreifen auf eine Speicherzelle der Kette. Vor T1 sind die Speicherzellen in einem Standby-Modus. Während des Standby-Modus befindet sich das Signal BS auf einer logischen 0 (Maschine oder Vss), wodurch der Auswahltransistor nichtleitend wird und die Kette von der Bitleitung abkoppelt. Die an die Gates der Speicherzellen gekoppelten Wortleitungen liegen auf einem geboosteten oder erhöhten hohen Spannungsspeigel (Vpp), wodurch die Kondensatoren kurzgeschlossen werden. Die geboostete Spannung ist größer als die interne Spannung (Vint) des IC. Insbesondere muß Vpp ausreichend hoch sein, um während Lese- oder Schreiboperationen eine ausreichende Übersteuerung sicherzustellen. Beispielsweise beträgt Vpp etwa 3,8 V, während Vint etwa 2,5 V beträgt.

**[0005]** Bei etwa T1 wird die der ausgewählten Zelle zugeordnete Wortleitung auf eine logische 0 getrieben, während die Wortleitungen der nicht ausgewählten Zellen auf Vpp bleiben. Bei etwa T2 wird das Signal BS auf Vpp getrieben, um die Kette an die Bitleitung zu koppeln. Dann wird bis etwa T3 ein Impuls (Vpl, der beispielsweise etwa 2,5 V beträgt) an der Plattenleitung bereitgestellt. Der Impuls erzeugt am Kondensator der ausgewählten Zelle ein elektrisches Feld. Dann wird auf die Bitleitung ein Signal gelegt, das der im Kondensator gespeicherten Information entspricht, und von einem Leseverstärker erfaßt. Nach dem Ende des Zugriffs wird bei T4 die Kette durch Ansteuern von BS auf eine logische 0 von der Bitleitung abgekoppelt. Dann wird bei T5 die ausgewählte Wortleitung zurück auf Vpp getrieben, wodurch in den Standby-Modus zurückgekehrt wird.

**[0006]** Wie durch das Zeitablaufdiagramm gezeigt, werden die Wortleitungen während des Standby-Modus auf Vpp gehalten. Selbst während eines Speicherzugriffs wird nur die der ausgewählten Zelle zugeordnete Wortleitung auf eine logische 0 getrieben. Das fast konstante Anlegen einer geboosteten Spannung an die Gates kann die Zuverlässigkeit des Gateoxids beeinträchtigen, wodurch die Lebensdauer des Speicherbauelements reduziert wird.

**Aufgabenstellung**

**[0007]** Aufgrund der obigen Erörterung ist es wünschenswert, eine verkettete Architektur mit verbesserten Zuverlässigkeit bereitzustellen.

**[0008]** In der US 6 275 425 B1 ist eine Boost-Schaltung für einen ferroelektrischen Speicher beschrieben. Die Schaltungsknoten des ferroelektrischen Speichers, die eine geboostete Spannung benötigen, werden normalerweise bei der Versorgungsspannung gehalten, bis eine Spannungserhöhung erforderlich ist. Dies wird dem Spannungsgenerator durch ein entsprechendes Steuersignal mitgeteilt. Daraufhin erzeugt der Spannungsgenerator die erhöhte

Spannung. Die Boost-Schaltung kann auch zum Boosten einer Wortleitung in ferroelektrischen Speicherschaltung verwendet werden. Die Schaltung dient unter anderem dem Zweck, Verlustleistung zu sparen und nur dann die geboostete Spannung bereitzustellen, wenn diese tatsächlich benötigt wird.

#### KURZE DARSTELLUNG DER ERFINDUNG

**[0009]** Die Erfindung betrifft das Verbessern der Zuverlässigkeit von Speicher-ICs mit verketteten Architekturen.

**[0010]** Gemäß der Erfindung wird eine integrierte Speicherschaltung nach den Merkmalen des Patentspruchs 1 vorgeschlagen.

**[0011]** Bei einer Ausführungsform werden zum Ansteuern der Wortleitungen mehrere Spannungspegel verwendet. Während des Standby-Modus werden die Wortleitungen auf einem ersten oder reduzierten Spannungspegel von logisch 1 gehalten. Wenn ein Speicherzugriff vorgenommen werden soll, werden die nicht ausgewählten Wortleitungen auf einen geboosteten Spannungspegel getrieben, während die ausgewählte Wortleitung auf Vss oder logisch 0 getrieben wird. Der geboostete Spannungspegel ist größer als der erste Spannungspegel, damit eine ausreichende Übersteuerung der Transistoren der Speicherzelle sichergestellt wird. Indem zum Betreiben der Wortleitungen ein Verfahren mit mehreren Spannungspegeln bereitgestellt wird, werden die Gates der Transistoren nur wenn nötig der hohen Spannung ausgesetzt. Dies reduziert die Beanspruchung des Gateoxids, wodurch die Zuverlässigkeit verbessert wird.

#### KURZE BESCHREIBUNG DER ZEICHNUNGEN

**[0012]** [Fig. 1](#) zeigt eine herkömmliche Speicherkette;

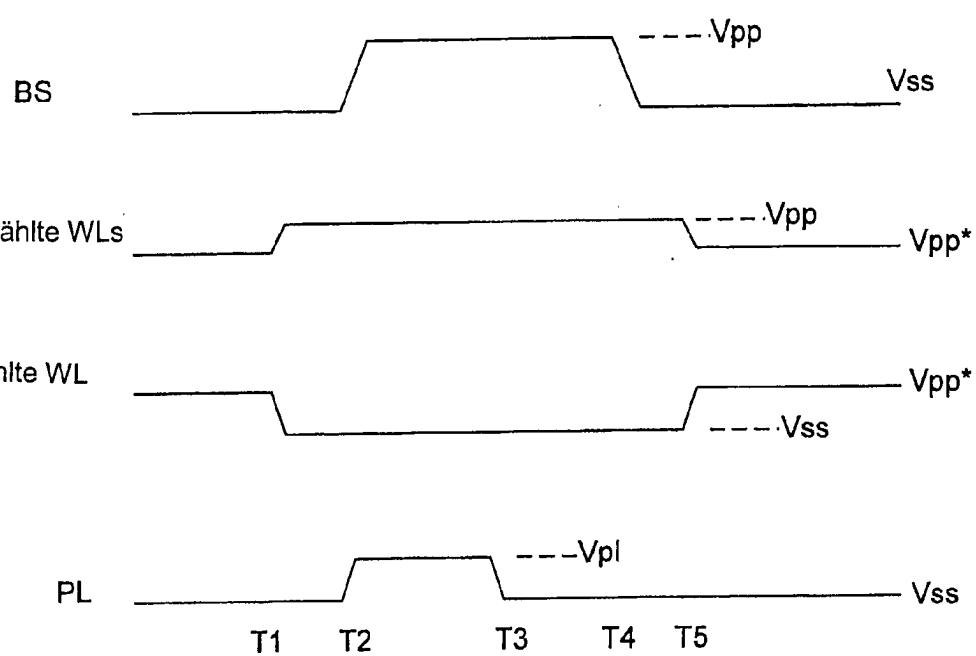

**[0013]** [Fig. 2](#) zeigt ein Zeitablaufdiagramm eines Speicherzugriffs in einer verketteten Architektur;

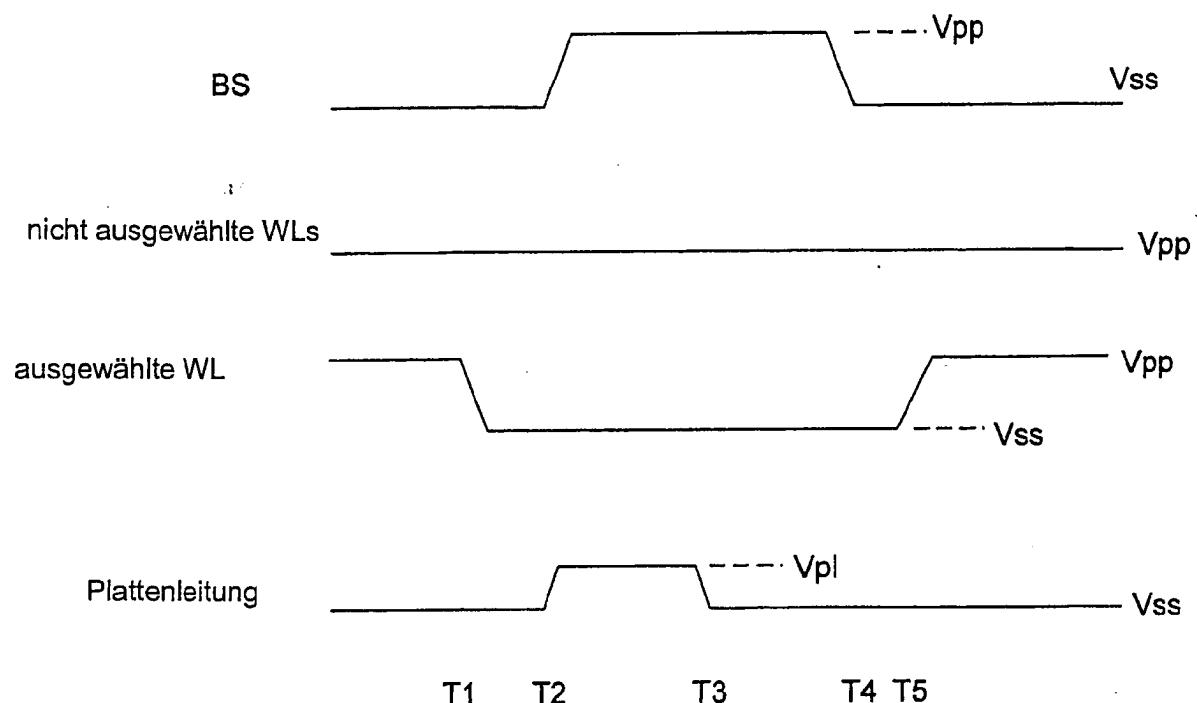

**[0014]** [Fig. 3](#) zeigt einen Teil eines Speicher-ICs gemäß einer Ausführungsform der Erfindung; und

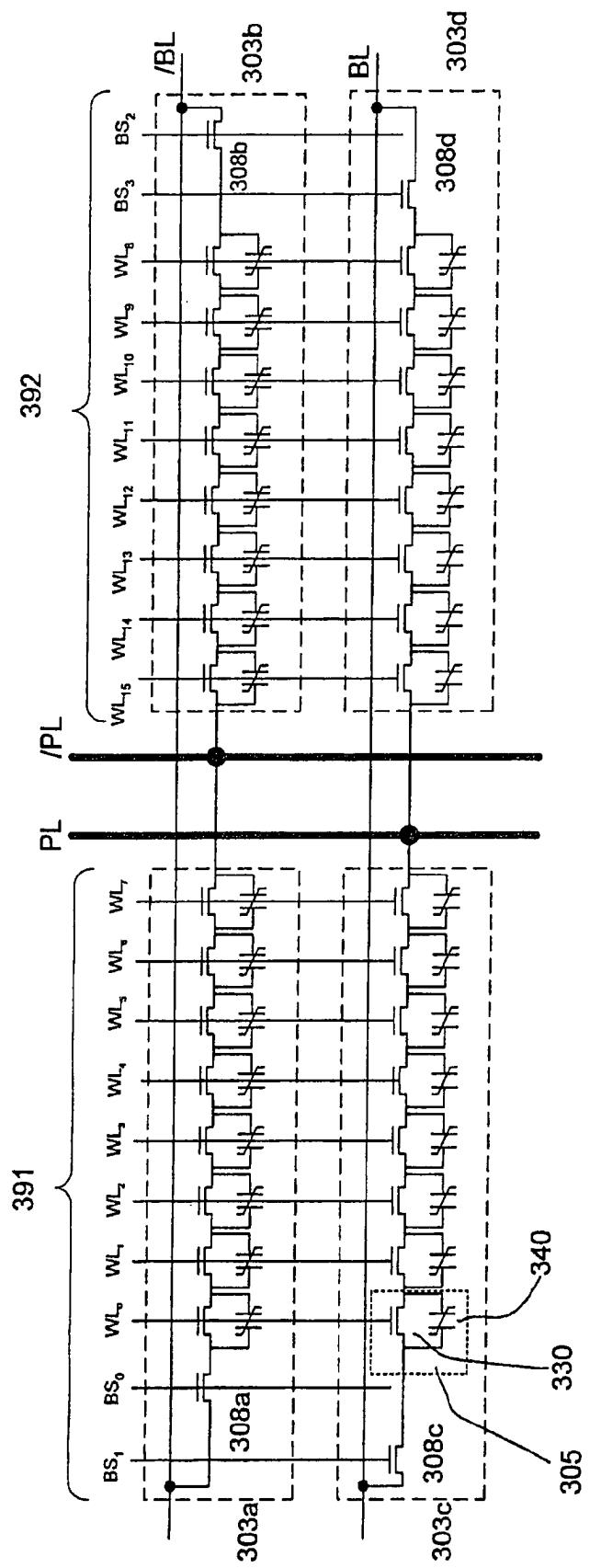

**[0015]** [Fig. 4](#) zeigt ein Zeitablaufdiagramm für die Durchführung eines Speicherzugriffs gemäß einer Ausführungsform der Erfindung.

#### Ausführungsbeispiel

#### AUSFÜHRLICHE BESCHREIBUNG DER ERFINDUNG

**[0016]** [Fig. 3](#) zeigt einen Teil 302 eines Speicher-ICs gemäß einer Ausführungsform der Erfindung. Der Teil enthält wie gezeigt ein Paar von Bitlei-

tungen (Bitleitung BL und Bitleitungskomplement/BL). Jede Bitleitung enthält eine erste und zweite Reihe oder Kette aus Speicherzellen 303a-b oder 303c-d. Auch das Vorsehen einer Bitleitung mit nur einer Kette oder einer anderen Anzahl von Ketten kann brauchbar sein. Die Speicherzellen einer Kette, jeweils mit einem parallel an einen Kondensator 340 gekoppelten Transistor 330, sind in Reihe gekoppelt. Bei einer Ausführungsform sind die Speicherzellen ferroelektrische Speicherzellen mit ferroelektrischen Kondensatoren. Die Gates der Zellentransistoren sind beispielsweise Gateleiter, die als Wortleitungen dienen oder an Wortleitungen gekoppelt sind. Ein Auswahltransistor 308 ist vorgesehen, um selektiv ein Ende einer Speicherkette an eine Bitleitung zu koppeln, während das andere Ende üblicherweise an die andere Speicherkette der Bitleitung und an eine Plattenleitung (PL oder/PL) gekoppelt ist.

**[0017]** Bei einer Ausführungsform werden zum Betreiben der verschiedenen Auswahltransistoren verschiedene Steuersignale verwendet. Beispielsweise wird BS0 oder BS1 verwendet, um wahlweise entweder Speicherkette 303a oder 303c an/BL beziehungsweise BL zu koppeln, wenn der linke Abschnitt 391 des Blocks ausgewählt ist. Falls der rechte Abschnitt 392 des Blocks ausgewählt ist, wird BS2 oder BS3 verwendet, um wahlweise entweder Speicherkette 303c oder 303d an/BL beziehungsweise BL zu koppeln. Die Signale BS werden mit der Kettenadresse codiert, um eine Zelle entweder in der rechten oder in der linken Kette auszuwählen. PL wird an die Speicherketten von BL gekoppelt, während PL an die Speicherketten von/BL gekoppelt wird.

**[0018]** Zahlreiche Bitleitungspaare sind über Wortleitungen miteinander verbunden und bilden einen Speicherblock. Der Speicherblock ist in einen ersten (linken) und zweiten (rechten) Abschnitt 391 und 392 unterteilt, die jeweils eine Kette einer Bitleitung umfassen. Bei einem Speicherzugriff wird eine Speicherzelle aus einem Bitleitungspaar ausgewählt, indem die entsprechende Wortleitung und das entsprechende BS-Signal ausgewählt wird.

**[0019]** Zum Betreiben der Wortleitungen wird ein Verfahren mit mehreren Vpp-Pegeln verwendet. Bei einer Ausführungsform wird während des Standby-Modus ein reduzierter Vpp-Spannungspegel ( $V_{pp}^*$ ) verwendet. Die reduzierte Spannung reicht aus, damit die Zellentransistoren leitend werden, so daß man einen niedrohmigen Kanal zum Kurzschließen des Kondensators erhält. Bei einem Speicherzugriff wird der reduzierte  $V_{pp}^*$ -Pegel auf den Vpp-Pegel geboostet oder erhöht. Bei einer Ausführungsform beträgt Vpp etwa 3,8 V und  $V_{pp}^*$  etwa 2,5 V.  $V_{pp}^*$  beispielsweise kann gleich Vint oder einer anderen verfügbaren Spannungsquelle mit einem Spannungspegel unter Vpp sein, wie etwa einer Blindzellen-Spannungsquelle (z.B. 1,8 V). Durch die

Bereitstellung eines Verfahrens mit zwei Vpp-Pegeln zum Ansteuern der Wortleitungen kann die mit Vpp verbundene Beanspruchung mit hoher Spannung reduziert werden, wodurch die Zuverlässigkeit verbessert wird.

**[0020]** [Fig. 4](#) zeigt ein Zeitablaufdiagramm eines Speicherzugriffs gemäß einer Ausführungsform der integrierten Speicherschaltung gemäß der Erfindung. Während des Standby-Modus ist BS eine logische 0, die Wortleitungen befinden sich auf einer reduzierten Spannung Vpp\* und die Plattenleitung PL befindet sich auf logisch 0. Bei T1 werden nicht ausgewählte Wortleitungen als Vorbereitung auf einen Speicherzugriff auf Vpp getrieben, während die ausgewählte Wortleitung auf Vss getrieben wird. Bei T2 wird das Signal BS auf eine logische 1 getrieben, um die gewählte Kette an die Bitleitung zu koppeln. Zur Sicherstellung der Übersteuerung des Auswahltransistors wird das Signal BS auf Vpp getrieben. Dann wird zwischen etwa T2 und T3 auf der Plattenleitung PL ein Impuls bereitgestellt. Der Impuls beträgt beispielsweise etwa 2,5 V. Der Impuls erzeugt am Kondensator der ausgewählten Zelle ein elektrisches Feld. Dann wird ein der im Kondensator gespeicherten Information entsprechendes Signal auf die Bitleitung gelegt und von einem Leseverstärker erfaßt. Nach dem Ende des Zugriffs wird die Kette von der Bitleitung abgekoppelt, indem bei T4 das Signal BS auf eine logische 0 gesteuert wird. Dann kehren bei T5 die Wortleitungen zu Vpp\* zurück (z.B. kehren sie in den Standby-Modus zurück).

### Patentansprüche

1. Integrierte Speicherschaltung, in der Speicherzellen in Ketten gruppiert sind, wobei eine Speicherkette mehrere Speicherzellen enthält, die zur Bildung der Kette in Reihe gekoppelt sind, und wobei jede der Speicherzellen der Kette einen Transistor enthält, der parallel an einen ferroelektrischen Kondensator gekoppelt ist, umfassend:

Wortleitungen der integrierten Speicherschaltung, die während eines Standby-Modus auf einem ersten Spannungspegel von logisch 1 gehalten werden; von denen Wortleitungen, die nicht-ausgewählten Speicherzellen zugeordnet sind, als Vorbereitung auf einen Speicherzugriff auf einen zweiten Spannungspegel von logisch 1 angehoben werden, wobei der zweite Spannungspegel von logisch 1 oberhalb des ersten Spannungspegels von logisch 1 liegt; von denen Wortleitungen, die einer ausgewählten Speicherzelle zugeordnet ist, von dem ersten Spannungspegel von logisch 1 auf eine logische 0 abgesenkt werden; wobei die ausgewählte Speicherzelle der Speicherkette an eine Bitleitung gekoppelt wird und ein in der ausgewählten Speicherzelle gespeicherten Information repräsentierendes Signal auf die Bitleitung ausgegeben wird;

wobei die Wortleitungen, die den nicht-ausgewählten Speicherzellen zugeordnet sind, auf den ersten Spannungspegel von logisch 1 abgesenkt werden; und wobei die Wortleitung, die der ausgewählten Speicherzelle zugeordnet ist, auf den ersten Spannungspegel von logisch 1 angehoben wird.

2. Integrierte Speicherschaltung nach Anspruch 1, weiterhin umfassend eine Plattenleitung, die an ein Ende der Speicherketten gekoppelt ist, auf der ein Impuls bereitgestellt wird.

3. Integrierte Speicherschaltung nach einem der Ansprüche 1 oder 2, wobei der erste Spannungspegel von logisch 1 gleich etwa 2,5 V und der zweite Spannungspegel von logisch 1 gleich etwa 3,8 V ist.

4. Integrierte Speicherschaltung nach einem der Ansprüche 1 bis 3, wobei der erste Spannungspegel von logisch 1 gleich etwa Vint ist, welche die interne Spannung der integrierten Speicherschaltung ist.

Es folgen 4 Blatt Zeichnungen

Fig. 1

STAND DER TECHNIK

Fig. 2

STAND DER TECHNIK

FIG. 3

Fig. 4