US 20010014522A1

## (19) United States (12) Patent Application Publication (10) Pub. No.: US 2001/0014522 A1 WEIMER et al. (43) Pub. Date:

## (54) FORMING A CONDUCTIVE STRUCTURE IN A SEMICONDUCTOR DEVICE

(76) Inventors: RONALD A. WEIMER, BOISE, ID (US); YONGJUN JEFF HU, BOISE, ID (US); PAI HUNG PAN, BOISE, ID (US); DEEPA RATAKONDA, BOISE, ID (US); JAMES BECK, BOISE, ID (US); RANDHIR P.S. THAKUR, CAPERTINO, CA (US)

> Correspondence Address: DAN C HU **TROP PRUNER HU & MILES PC** 8554 KATY FREEWAY **SUITE 100** HOUSTON, TX 77024

- (\*) This is a publication of a continued pros-Notice: ecution application (CPA) filed under 37 CFR 1.53(d).

- 09/397,763 Appl. No.: (21)

- Sep. 15, 1999 (22)Filed:

# **Related U.S. Application Data**

Division of application No. 09/031,407, filed on Feb. (62) 26, 1998.

## **Publication Classification**

- (51) Int. Cl.<sup>7</sup> ...... H01L 21/3205; H01L 21/4763; H01L 21/44

- U.S. Cl. ..... 438/591; 438/653; 438/655; (52)

118/724

Aug. 16, 2001

#### ABSTRACT (57)

A conductive structure for use in a semiconductor device includes a multilayer structure. A first layer includes a material containing silicon, e.g., polysilicon and silicon germanide. A barrier layer is formed over the first layer, with the barrier layer including metal silicide or metal silicide nitride. A top conductive layer is formed over the barrier layer. The top conductive layer can include metal or metal silicide. Selective oxidation can be performed to reduce the amount of oxidation of selected materials in a structure containing multiple layers, such as the multilayer conductive structure. The selective oxidation is performed in a singlewafer rapid thermal processing system, in which a selected ambient, including hydrogen, is used to ensure low oxidation of a selected material, such as tungsten or a metal nitride.

FIGURE 1

# FORMING A CONDUCTIVE STRUCTURE IN A SEMICONDUCTOR DEVICE

**[0001]** This is a divisional of co-pending and commonly assigned U.S. patent application Ser. No. 09/031,407, entitled "Forming a Conductive Structure in a Semiconductor Device," filed Feb. 26, 1998.

## BACKGROUND

**[0002]** The invention relates to forming a conductive structure in a semiconductor device.

**[0003]** Advanced integrated circuits in a semiconductor device require high speed interconnecting lines between circuits for improved device speed. Interconnecting lines are typically made of metal, e.g., aluminum, titanium. However, in some parts of a semiconductor device, particularly in regions where components are densely packed (such as the array of a memory device), or in regions where further heat steps are needed after formation of the interconnecting line during the manufacturing process, other materials are also widely used to form interconnecting lines, e.g., doped polysilicon or N+ or P+ diffused regions.

**[0004]** The different types of interconnecting lines exhibit different resistivities, with metal generally having the lowest resistivity. Polysilicon, which is also typically used as the conductive electrode at the gate of an N-channel or P-channel metal-oxide-silicon field effect transistor (MOSFET), exhibits a higher resistivity than metal.

**[0005]** As the speed requirements of semiconductors increase, the resistance of interconnecting lines, especially those formed of a higher resistivity material (such as polysilicon) reduces switching speeds of circuits in the device. The resistance of a line increases proportionately with its length. Thus, a polysilicon line running over a long length and connected to a large capacitive load, such as a wordline in a memory array connected to multiple transistors in the array, would cause a high RC delay during circuit switching.

**[0006]** One approach to reduce the resistivity of a polysilicon interconnect line is to use a polycide structure, in which a low resistance silicide (e.g., WSix) is formed on top of a doped polysilicon layer. This effectively forms a two-layer interconnect line in which the silicide layer provides a low resistivity conductive path.

**[0007]** Three-layer interconnecting lines have also been proposed, including a polymetal composite structure having tungsten (W) as the top layer, tungsten silicide nitride (WSiN) as the intermediate layer, and polysilicon as the bottom layer. The polymetal structure has a resistivity lower than the polycide structure that includes tungsten silicide on polysilicon.

### SUMMARY

**[0008]** In general, according to one embodiment, a method of forming a conductive structure in a semiconductor device includes forming a lower electrically conductive layer on a support surface and forming an electrically conductive barrier over the lower layer. Further, an upper conductive layer is formed over the barrier layer, the upper conductive layer including metal silicide.

**[0009]** Other features and embodiments will become apparent from the following description and from the claims.

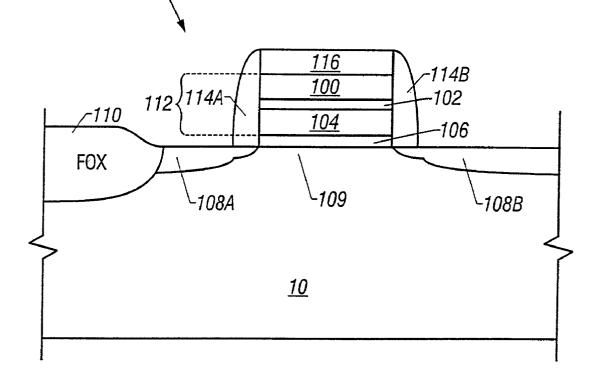

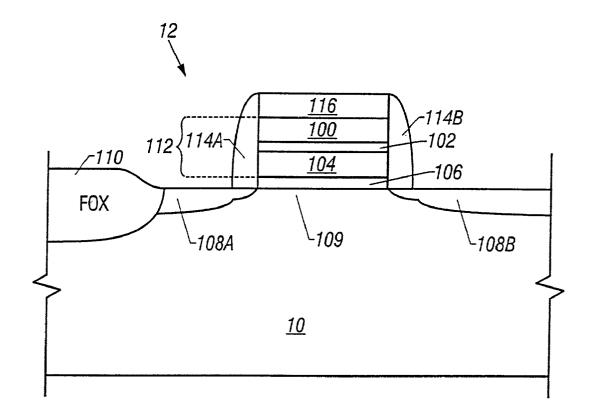

**[0010]** FIG. 1 is an enlarged, cross-sectional view of a transistor in a semiconductor device.

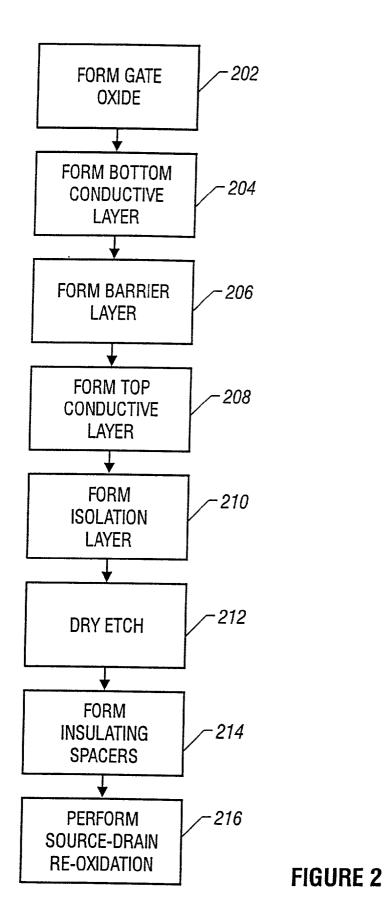

**[0011] FIG. 2** is a flow diagram of the fabrication steps for forming portions of the transistor structure of **FIG. 1**.

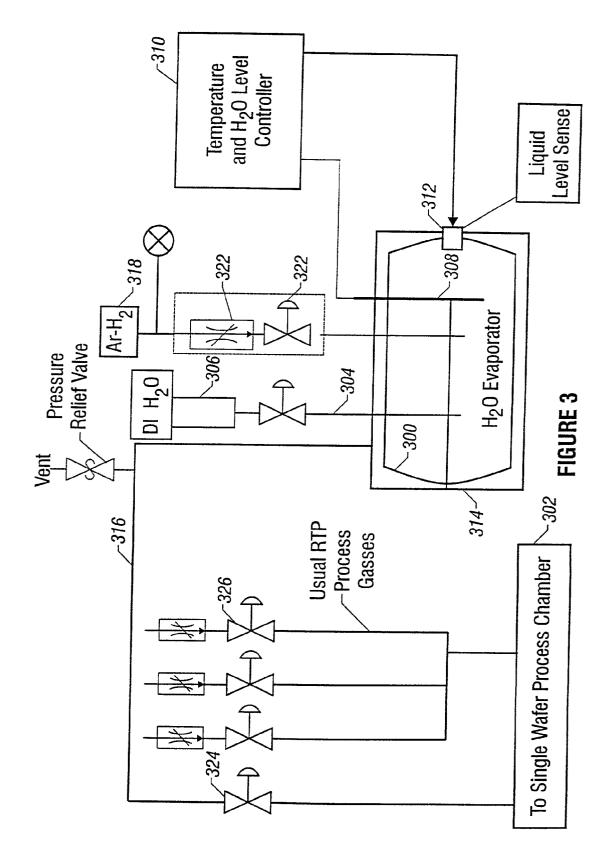

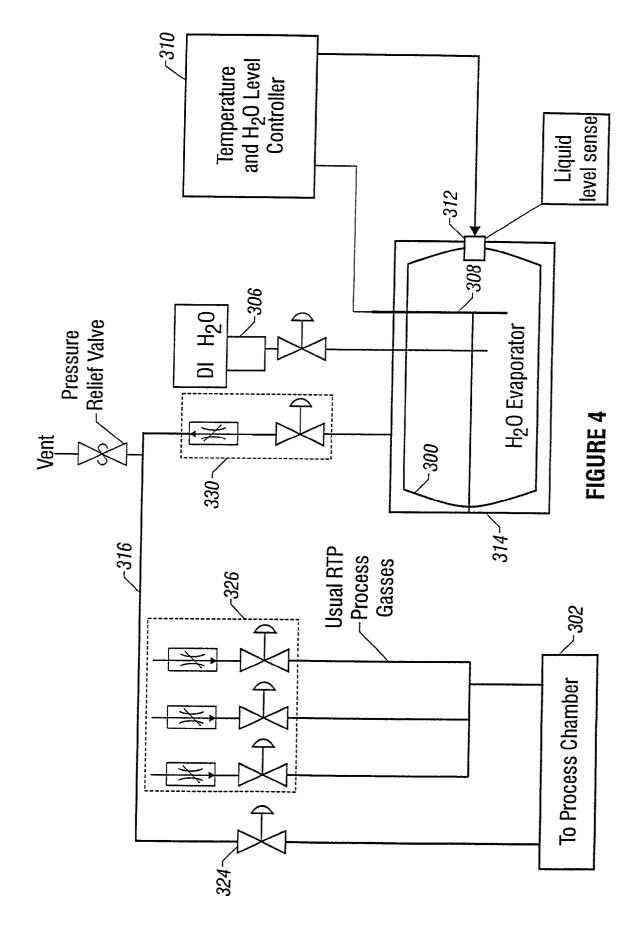

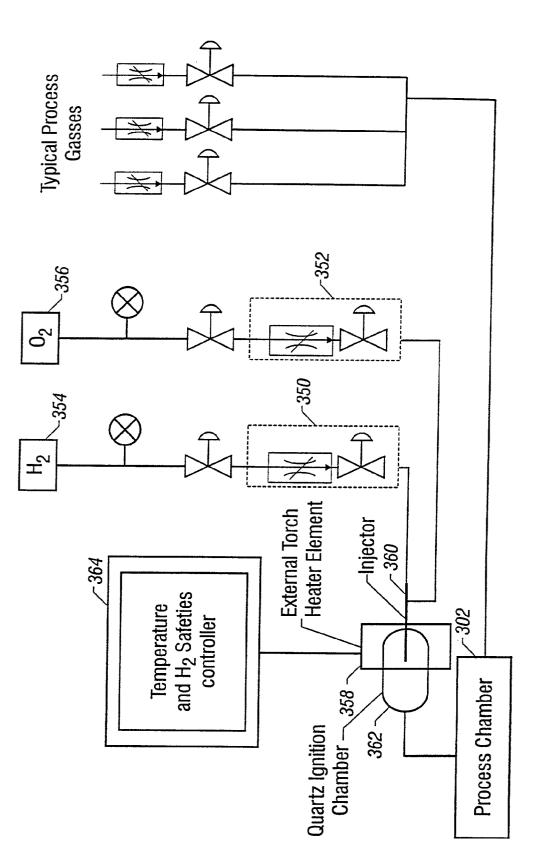

**[0012]** FIGS. 3, 4, and 5 are block diagrams of singlewafer rapid thermal processing systems for performing selective oxidation.

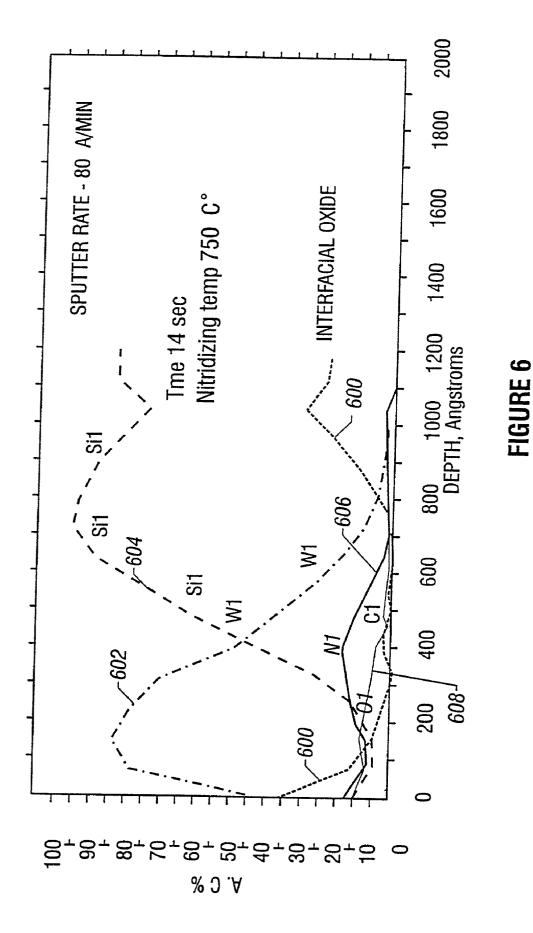

**[0013]** FIG. 6 is graph of an X-ray photoelectron spectrometer (XPS) surface analysis showing the selective oxidation region for a multilayer conductive structure.

## DETAILED DESCRIPTION

**[0014]** Referring to **FIG. 1, a** multilayer, low resistivity conductive structure is described. The conductive structure can be used as part of the gate structure of a MOS transistor (as shown) or as an interconnecting line to connect circuits, such as a wordline used to connect transistors connected to memory cells in a memory array.

[0015] In FIG. 1, a transistor 12 is formed on a base 10, which includes a semiconductor (e.g., silicon) substrate or multilayer substrate (e.g., silicon-on-insulator or SOI substrate). The transistor 12 is adjacent a field oxide layer 110. The transistor includes source and drain regions 108A and 108B and a channel region 109. If the transistor 12 is used in a memory array, the source would be connected to a memory cell capacitor structure (not shown), while the drain would be connected to a digit line (not shown). The transistor 12 can also have many other uses in a semiconductor device.

[0016] A gate oxide layer 106 is formed above the channel region 109. A gate stack 112 is then formed over the gate oxide layer 106. In one embodiment, the gate structure 112 includes three electrically conductive layers (100, 102, 104) to reduce the resistivity of the gate. The three-layer structure can also be used to form an interconnecting line separate from the transistor 12, in which case the gate oxide layer 106 beneath the stack 112 would be replaced with other insulating layers.

[0017] The bottom conductive layer 104 is formed of a material that includes silicon, e.g., doped or undoped polysilicon, silicon germanium (SiGex), or amorphous silicon. The top conductive layer 100 includes a low resistivity material, which can be metal or metal silicide. Sandwiched between the top layer 100 and the bottom layer 104 is a conductive diffusion barrier layer 102 that is resistant to oxidation, agglomeration, and silicidation.

**[0018]** The barrier layer **102** acts to prevent agglomeration of silicon from the bottom layer **104** into the top conductive layer **100**. For example, titanium silicide (TiSix) formed on polysilicon may result in agglomeration of silicon into the TiSix grains, which can increase resistivity. Silicidation can also occur between certain top layer and bottom layer materials, such as tungsten (W) formed on polysilicon, in which formation of higher resistivity Wsix can occur.

**[0019]** The barrier layer **102** is formed of a material that includes metal silicide, metal nitride, or metal silicide nitride, such as tungsten silicide (Wsix), tungsten silicide nitride (WSixNy), titanium silicide nitride (TiSixNy), tan-

talum silicide (TaSix), tantalum silicide nitride (TaSixNy), molybdenum silicide (MoSix), and molybdenum silicide nitride (MoSixNy), hafnium silicide (HfSix), hafnium silicide nitride (HfSixNy), zirconium silicide nitride (ZrSixNy), niobium silicide (NbSix), niobium silicide nitride (NbSixNy), and titanium nitride (TiNy).

**[0020]** Generally, a silicide, nitride, or silicide nitride composition is resistant to oxidation and is stable at high temperatures. The ability to withstand high temperatures is particularly important since the gate structure or interconnecting line is put through various subsequent high temperature process steps, including source-drain implant anneal, oxidation, and glass flow/reflow.

**[0021]** Metal silicides, nitrides, or silicide nitrides also have other desirable properties, including low resistivity, ease of formation, controlled oxidation properties, and stability in an oxidizing ambient. These materials also have excellent adhesion characteristics and exhibit low stress contacts.

**[0022]** The resistivity of a metal silicide, metal nitride, or metal silicide nitride barrier layer **102** is dependent on several factors, including the method of formation, annealing times and temperatures, and chemical purity. The stoichiometry of the refractory metal silicide, metal nitride, or metal silicide nitride composition can also affect resistivity; e.g., the x value of an MSix composition can affect the resistivity.

[0023] In the barrier layer 102 containing an MSixNy composition, the value of x for silicon can be set at a value greater than 2, while the value of y for nitrogen is set in the range between about 0.1 and 0.9, preferably between about 0.5-0.6. With higher y values, the MSixNy compositions are more stable at higher temperatures, but the compositions also have higher resistivities.

**[0024]** The top conductive layer **100** can be made from low resistivity materials, e.g., metal or metal suicides, such as tungsten (W), cobalt (Co), titanium silicide (TiSix), cobalt silicide (CoSix), nickel silicide (NiSix), or other metal or metal silicide layers. Typically, the value of x may be greater than or equal to 2, with the exception of NiSix, where x can be equal to one. Generally, the metal silicide compositions are more stable at high temperatures than tungsten or cobalt, which tend to have relatively high oxidation rates.

[0025] The gate stack 112 and the gate oxide 106 are electrically insulated by side insulating spacers 114A and 114B and a top insulating layer 116. The insulating materials can be formed using silicon nitride  $(Si_3N_4)$  or silicon dioxide  $(SiO_2)$ .

[0026] Referring to FIG. 2, the fabrication flow of portions of the transistor 12 shown in FIG. 1 is illustrated. After the field oxide 110 and source-drain regions 108A and 108B are formed in the base 10, the gate oxide 106 is formed on the surface of the base 10 (step 202) by thermal growth or deposition such as chemical vapor deposition (CVD). The thickness of the gate oxide 106, for current generation technologies, can typically range from about 30 angstroms (A) to 150 A.

**[0027]** Next, the bottom conductive layer **104** (which can include polysilicon, SiGex, or amorphous silicon) is formed, such as by deposition using a low pressure chemical vapor

deposition (LPCVD) process. The bottom conductive layer **104** can have an exemplary thickness ranging from about 100 A to 3,000 A. The polysilicon, SiGex, or amorphous silicon layer **104** can also be doped with a dopant such as phosphorous or boron to improve electrical conductivity.

[0028] Next, the barrier layer 102 is formed (step 206) to a thickness between about 50 A to 500 A, for example. Various methods can be used to form the diffusion barrier layer 102, including using chemical vapor deposition (CVD), physical vapor deposition (PVD), or deposition followed by a high temperature anneal of a metal (e.g., tungsten or titanium) in an ambient containing nitrogen, ammonia (NH<sub>3</sub>), or hydrazine (N<sub>2</sub>H<sub>4</sub>) in a rapid thermal processing (RTP) system.

**[0029]** Formation of metal silicide barrier layers using CVD may involve deposition of the metal onto the bottom conductive layer **104** followed by subsequent heating, which causes the metal and silicon containing material in the layer **104** to react to form a silicide. This type of silicide formation can yield low resistivity silicide layers.

[0030] To form a barrier layer 102 having metal silicide nitride (MSixNy) or metal nitride (MNy), the metal deposition onto the bottom conductive layer step is followed by a high temperature (e.g., 600-1000° C.) anneal in an ambient including  $NH_3$  or  $N_2H_4$ . The  $NH_3$  or  $N_2H_4$  anneal can be performed in a rapid thermal processing (RTP) system for a predetermined amount of time, e.g., between about 1-60 seconds. If the metal deposited is tungsten on a polysilicon, SiGex, or amorphous silicon layer, the anneal step forms a barrier layer that contains Wsix and SiN, with no formation (or very little formation) of tungsten nitride (WN), as illustrated by the X-ray photoelectron spectrometer (XPS) profile graph shown in FIG. 6. Wsix and SiN are more oxidation resistant than WN or tungsten. The high temperature anneal can also be performed with a titanium on a silicon-containing material structure. The anneal in the NH<sub>3</sub> or N<sub>2</sub>H<sub>4</sub> ambient forms a TiNy barrier layer.

[0031] FIG. 6 shows the percentage of materials present in a Wsix-polysilicon stack after anneal of a W/poly-Si structure in an  $NH_3$  ambient at 750° C. The depth (as defined by an axis generally projecting perpendicularly from the surface of the base 10) begins at the top surface (0 Å) of the stack 112 (without the top conductive layer 100) and continues downwardly into the stack. A layer of tungsten is initially deposited on polysilicon. After anneal in the  $NH_3$ , the layers formed include a tungsten layer 100 at the top and a Wsixny barrier layer 102 between the top tungsten layer and the bottom conductive layer 104.

**[0032]** PVD by sputtering or evaporation can also be used to form metal silicides and metal silicide nitrides. The evaporation method utilizes simultaneous deposition of the metal and silicon (or metal, silicon and nitrogen) under high vacuum or sputtering of a metal silicide composite target. Sputtering of the metal and silicon (or metal, Si, and N) can be performed using RF or magnetron sputtering.

[0033] After formation of the barrier layer 102, the metal or metal silicide conductive layer 100 is formed over the barrier layer 102 (step 208), using either CVD or PVD techniques, for example. The conductive layer 100 can be formed to a thickness between about 200 A to 2000 A. Following formation of the top conductive layer 100, the electrically insulating cap layer 116 is formed over the conductive layer 100 as an etch stop and oxidation barrier (step 210). The insulating layer 116 can be formed using vapor deposited  $SiO_2$  or  $Si_3N_4$ . A dry etch process (such as reactive ion etching) is then used to form the gate stack (step 212).

[0034] After the gate stack is formed, nitride insulating spacers 114A and 114B can optionally be formed using known methods, such as by LPCVD or PECVD nitride (step 214). Oxide spacers can also be used, such as those formed using CVD with tetraethylorthosilicate (TEOS). Whether this step is performed depends on the type of materials used in forming the stack 112.

**[0035]** For example, if a stack having a tungsten conductor on a titanium nitride barrier is used, then the spacers are useful as etch barriers as well as oxidation barriers in subsequent processing steps. The spacers **116A** and **116B** may also be used with other stacks that contain a metal conductor on a metal silicide or nitride barrier.

[0036] The spacer forming step 214 may not be needed when a stack having a metal silicide conductor on a metal silicide or metal silicide nitride barrier (e.g., TiSix conductor on Wsix barrier) is used. With such stacks, the spacer formation is performed after the source-drain re-oxidation step (216).

[0037] The source-drain re-oxidation step (216) is performed to remove damage caused by reactive ion etching and patterning of the gate electrode. The re-oxidation step causes oxide to be thermally grown on the sidewall of the etched polysilicon, SiGex, or amorphous silicon electrode, which also serves to thicken the gate oxide 106 at the gate edge to improve the gate oxide dielectric strength. The source-drain re-oxidation can be performed in the following environment:  $O_2$ ;  $O_2/H_2$ ;  $N_2O$ ; NO; or a selective ambient, such as an  $H_2O/H_2$  ambient in which the ratio of  $H_2O$  to  $H_2$ is controlled to predetermined ranges.

[0038] If the top conductive layer 100 is formed of a metal silicide material, and the barrier layer 102 is formed of a metal silicide or metal silicide nitride material, then the two layers are relatively resistant to oxidation and any of the source-drain re-oxidation techniques listed above can be used. However, certain materials that can be used in the top conduction layer 100, such as tungsten (W) or titanium (Ti), and certain materials in the barrier layer 102, such as a metal nitride (e.g., TiN), have relatively high oxidation rates.

**[0039]** For example, tungsten oxidation rate is much faster than that of silicon, and typical oxidation processes can cause the volume of tungsten oxide ( $WO_3$ ) to be much larger than that of W. If  $WO_3$  formation occurs, peeling or morphological degradation of the tungsten film may occur. Thus, in cases where the top conduction layer **100** has a relatively high oxidation rate, a selective oxidation process is preferred over conventional oxidation or wet oxidation. Similar issues exist when titanium is used as the top conduction layer **100**.

**[0040]** Possible metal nitride materials (in addition to the materials discussed above) for the barrier layer **102** include tungsten nitride (WN) or titanium nitride (TiN), which are susceptible to relatively fast oxidation. If such barrier layers are used, then selective oxidation may be particularly advantageous. However, even if metal silicide top conductive layers **100** or metal silicide or metal silicide nitride barrier

layers **102** are used, the selective oxidation process may also help to reduce the rate of oxidation of those materials.

[0041] Selective source drain re-oxidation can be performed in a water vapor ambient with controlled amounts of hydrogen added in a single-wafer rapid thermal processing (RTP) system (e.g., an AG8108 Heat Pulse RTP system) for selective oxidation of silicon over the metal, metal silicide, metal silicide nitride, or metal nitride top conducting layer 100 or barrier layer 102. In addition, use of a single-wafer system, such as the three types shown in FIGS. 3-5, provide several advantages over use of a furnace that can receive multiple wafers. In a single-wafer RTP system, better control of process conditions can be achieved. For example, better uniformity of temperature can be achieved over the entire surface of the wafer, which is particularly advantageous when large wafers (e.g., 300 mm wafers) are used. In addition, better ambient control and uniformity of oxidation over the entire processed surface of a wafer can be achieved.

[0042] The described selective oxidation processes (shown in FIGS. 3, 4, and 5) can also be applied to multi-wafer furnace systems.

[0043] Referring to FIG. 3, an RTP single-wafer system uses an ambient of argon-hydrogen  $(Ar-H_2)$  and water vapor. Other inert gases besides Ar can also be used. By controlling the ratio of H<sub>2</sub>O to O<sub>2</sub>, use of this ambient can reduce oxidation of a metal (e.g., tungsten) top conductive layer 100 and WN, Wsixny, TiN, and other metal nitride conductive diffusion barrier layers 102.

[0044] A quartz vessel 300 (which can contain 20 liters of liquid) is filled approximately half full of deionized water through a liquid flow controller 304 from a source 306. The vessel 300 is then heated and maintained at an elevated temperature, e.g., between about 95-98° C., through use of an external heating blanket 314 affixed to the outside of the quartz vessel 300. The elevated temperature evaporates portions of the deionized water.

[0045] The temperature of the deionized water in the vessel 300 is monitored by a thermocouple 308 inserted into a sheath in the quartz vessel 300. The over temperature trip level of the thermocouple 308 can be set at about 120° C. The thermocouple 308 is connected to a temperature and water level controller 310 for monitoring. The controller 310 adjusts the temperature of the blanket 314 as the liquid temperature in the vessel 300 varies. Over temperature thermocouples (not shown) can also monitor the heater blanket 314 temperature to prevent heater blanket temperature runaway.

[0046] The level of the deionized water in the vessel 300 is monitored by a liquid level sensor 312, also connected to the controller 310. The controller 310 adjusts the flow rate through the flow controller 304 to maintain the level of the liquid in the vessel 300. The autofill feature for the deionized water is disabled during a process run (to perform the source drain re-oxidation) so as not to disturb the water vapor delivery.

[0047] Delivery of the deionized water vapor is achieved by injecting an Ar— $H_2$  mixture into the vessel 300 through a mass flow controller 322 at a predetermined rate. The Ar— $H_2$  comes from a source 318. The  $H_2$  can originate from a pure hydrogen source or from a breakdown of a hydrogen containing compound such as  $NH_3$  or  $N_2H_4$ . The resulting water and argon vapor is transported through a line 316 (which can be a  $\frac{1}{2}$  inch heat taped stainless steel line) maintained at a predetermined temperature, e.g., about  $110^{\circ}$  C., to prevent recondensation of the vapor.

[0048] The vapor in the line 316 flows through a vapor flow controller 324 to a single-wafer process chamber 302. Other conventional RTP process gases are also provided through flow controllers 326 to the processor chamber 302. The flow of H<sub>2</sub>O can be selected to be in the range between about 1 SCCM (standard cubic centimeters per minute) and 50 SLM (standard liters per minute), with a preferred range of about 1 SCCM to 10 SLM. The flow rate of H<sub>2</sub> can be selected to a value in the range between about 1 SCCM and 50 SLM, with a preferred range of about 1 SCCM to 20 SLM. In the AG8108 system, the  $H_2O/H_2$  partial pressure ratio can be maintained between about 2.3 and 2.8. However, the ratios vary according to the specific types of RTP systems used. The processing temperature in the singlewafer processing chamber can be maintained between about 950° Ĉ. and 1100° C. Selective oxidation of silicon over tungsten of about 2:1 can be achieved using the system of FIG. 3.

[0049] Referring to FIG. 4, an alternative single-wafer RTP system performs source-drain selective re-oxidation using a different transport system. Elements that are the same as in the RTP system of FIG. 1 have common reference numerals. As in the RTP system of FIG. 1, a predetermined amount of deionized water is kept in the vessel 300 (e.g., half full in a 20-liter vessel). However, delivery of the deionized water vapor is achieved through the use of a vapor flow controller 330, rather than through use of the mass flow controller 322 to pump argon 318 into the vessel 300 to move vapor through the line 316. The pressure in the water vessel 300 can be approximately 960 Torr, which is sufficient to generate ample flow through the vapor flow controller 330. The vapor is then transported through the line 316 to the process chamber 302, with the line temperature maintained at about 110° C. to prevent recondensation of the vapor. Hydrogen is passed through one of the vapor flow controllers 326 to the process chamber 302 to perform selective oxidation of silicon over other materials.

[0050] Referring to FIG. 5, an RTP system with an external torch assembly is used to create the water vapor flow for selective oxidation. Hydrogen (H<sub>2</sub>) and oxygen (O<sub>2</sub>) are delivered through vapor flow controllers 350 and 352, respectively, from sources 354 and 356, respectively. The H<sub>2</sub> and O<sub>2</sub> are delivered to an injector 360 inserted into the external torch assembly 358. The torch assembly 358 is maintained at a temperature of about 900° C. to provide ignition energy. The resulting water vapor and H<sub>2</sub> mixture is delivered to the single-wafer process chamber 302 via a quartz tube interface 362.

[0051] As is the case with the RTP system of FIG. 3, the RTP systems of FIGS. 4 and 5 also maintain a predetermined  $H_2O/H_2$  partial pressure ratio and temperature.

[0052] In the RTP system of FIG. 5, safety measures are provided by an external controller 364, which monitors and maintains the external torch element temperature and provides over temperature and runaway safeties. The controller 364 can also implement steps to ensure safety associated with using  $H_2$  as a process gas. The safety mechanisms

implemented include maintaining a particular  $H_2/O_2$  ratio. Thus,  $H_2$  flow is disabled if no  $O_2$  is present;  $H_2$  is disabled if the torch temperature is below 700° C.; an initial nitrogen ( $N_2$ ) purge is performed of the injector **360** before the flow of  $H_2$  is turned on; and  $H_2$  leak detectors are used to determine when to turn off and purge the  $H_2$  line if an  $H_2$ leak is detected. The controller **364** also monitors the temperature of the process chamber **302** to prevent water vapor from being formed if the process chamber **302** is below 700° C. to prevent recondensation of the water vapor.

**[0053]** Other embodiments are also within the scope of the following claims. Although the layers in the multilayer conductive structure have been described with certain thicknesses for each layer, it is contemplated that the layer thicknesses can be varied and still achieve desirable results. The conductive structure described can be formed with a stack having more than three layers. Further, various systems and processes have been described with particular parameters; these parameters can also be varied. The systems described have components associated with certain, specific parameters and values, which can be varied.

What is claimed is:

**1**. A method of forming a multi-layer conductive structure in a semiconductor device, the method comprising:

forming a first layer containing silicon;

- depositing a metal layer over the first layer; and

- annealing the metal layer in an ambient having a composition selected from a group consisting of nitrogen, NH<sub>3</sub>, and hydrazine,

- wherein a second layer containing silicide is formed over the first layer after annealing.

- **2**. The method of claim 1, wherein the second layer contains a metal silicide nitride composition.

**3**. The method of claim 1, further comprising forming a top conductive layer over the second layer.

4. The method of claim 3, wherein the first layer, second layer, and top conductive layer form the multi-layer conductive structure.

5. A method of forming a conductive structure in a semiconductor device, the method comprising:

- forming a lower electrically conductive layer on a support surface;

- forming an electrically conductive barrier layer over the lower layer; and

forming an upper conductive layer over the barrier layer, the upper conductive layer including metal silicide.

6. The method of claim 5, wherein the lower layer includes silicon.

7. The method of claim 5, wherein the lower layer includes a material selected from the group consisting of polysilicon, SiGex, and amorphous silicon.

8. The method of claim 5, wherein the barrier layer includes a metal silicide composition.

9. The method of claim 5, wherein the barrier layer includes a metal silicide nitride composition.

**10**. The method of claim 5, wherein the upper conductive layer includes a material selected from the group consisting of TiSix, CoSix, NiSix, and PdSix.

**11**. A method of forming a conductive structure in a semiconductor device, comprising:

forming a first electrically conductive layer on a base;

forming a barrier layer over the first layer, the barrier layer including a metal silicide; and

forming a second electrically conductive layer over the barrier layer.

12. The method of claim 11, wherein the barrier layer includes tungsten silicide.

**13**. The method of claim 11, wherein forming the barrier layer includes using chemical vapor deposition.

**14**. The method of claim 11, wherein forming the barrier layer includes using physical vapor deposition.

15. The method of claim 11, wherein forming the barrier layer includes depositing a metal on a layer containing silicon and controlling the metal-silicon structure in a preselected ambient.

16. The method of claim 15, wherein the preselected ambient includes  $NH_{3}$ .

17. The method of claim 15, wherein the preselected ambient includes hydrazine.

18. The method of claim 15, wherein the preselected ambient includes nitrogen.

**19**. A method of oxidizing layers formed on a base of a semiconductor device, the layers including a first layer containing silicon, the method comprising:

generating a predetermined mixture of  $H_2$  and  $H_2O$ ;

providing the mixture to a single-wafer thermal processing chamber; and

heating the chamber to selectively oxidize the first layer over one or more other layers.

**20**. The method of claim 19, further comprising:

generating a flow of a mixture containing  $H_2O$  vapor and  $H_2$  by injecting an inert gas.

**21**. The method of claim 20, wherein the inert gas includes Argon.

22. The method of claim 19, further comprising:

filling a vessel with deionized water; and

heating the vessel to evaporate a portion of the water.

**23**. The method of claim 22, wherein injecting the inert gas includes injecting the inert gas into the vessel.

**24**. The method of claim 19, wherein heating the processing chamber includes heating the processing chamber to a temperature between about 950° C. and 1100° C.

25. The method of claim 19, wherein generating the mixture of  $H_2$  and  $H_2O$  includes injecting  $H_2$  and  $O_2$  vapor into a heating element.

**26**. The method of claim 25, wherein the heating element includes a torch heater assembly.

27. The method of claim 26, further comprising maintaining the torch heater assembly at a temperature above about  $900^{\circ}$  C. to provide ignition energy.

**28**. The method of claim 19, wherein the one or more other layers include tungsten.

**29**. The method of claim 19, wherein the one or more other layers include a metal nitride.

**30**. The method of claim 34, wherein the one or more other layers include a stack containing second and third layers formed over the first layer, the second and third layers both being electrically conductive.

**31**. An oxidation system for oxidizing layers formed on a base of a semiconductor device, a first layer containing silicon, the oxidation system comprising:

a source of H<sub>2</sub> vapor;

- a source of H<sub>2</sub>O vapor;

- a flow controller connected to deliver a mixture of  $H_2O$  and  $H_2$ ; and

- a process chamber in which the semiconductor device is placed, the process chamber connected to receive the mixture of  $H_2O$  and  $H_2$  to perform selective oxidation of the first layer over the other layers.

**32**. The system of claim 31, wherein the source of  $H_2O$  vapor includes a vessel containing water heated to evaporate a portion of the water.

**33**. The system of claim 32, wherein the inert gas is injected into the vessel.

34. The system of claim 32, wherein the  $H_2$  vapor is injected with the inert gas.

**35**. The system of claim 31, wherein the  $H_2O/H_2$  mixture has a partial pressure ratio of between about 2.3 and 2.8.

**36**. The system of claim 35, wherein the process chamber is heated to a temperature between about  $950^{\circ}$  C. and  $1100^{\circ}$  C.

**37**. The system of claim 31, wherein the process chamber is a single-wafer process chamber.

**38**. The method of claim 31, wherein the other layers include tungsten.

**39**. The method of claim 31, wherein the other layers include a metal nitride.

**40**. A selective oxidation system for oxidizing layers formed on a base of a semiconductor device, a first layer containing silicon, the system comprising:

a source of H<sub>2</sub> vapor;

a source of  $O_2$  vapor;

- a heating element connected to receive  $H_2$  vapor and  $O_2$ vapor, the heating element being heated to generate a mixture of  $H_2O$  and  $H_2$  having a predetermined partial pressure ratio; and

- a process chamber in which the semiconductor device is place, the process chamber connected to receive the mixture of  $H_2O$  and  $H_2$  to perform selective oxidation of the first layer over the other layers.

**41**. The system of claim 40, wherein the heating element is heated to above a predetermined temperature to generate  $H_2O$  vapor.

**42**. The system of claim 40, wherein the heating element includes a torch heater assembly.

43. The system of claim 42, wherein the torch heater assembly is maintained at a temperature above about  $700^{\circ}$  C. to provide ignition energy.

\* \* \* \* \*