(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5349775号

(P5349775)

(45) 発行日 平成25年11月20日(2013.11.20)

(24) 登録日 平成25年8月30日(2013.8.30)

(51) Int.Cl.

G06F 12/00 (2006.01)

F 1

G06F 12/00 564D

G06F 12/00 564B

請求項の数 2 (全 11 頁)

(21) 出願番号 特願2007-233377 (P2007-233377)

(22) 出願日 平成19年9月7日 (2007.9.7)

(65) 公開番号 特開2009-64360 (P2009-64360A)

(43) 公開日 平成21年3月26日 (2009.3.26)

審査請求日 平成22年7月9日 (2010.7.9)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】メモリコントローラ及びその制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

アクセスサイクルの異なる複数のメモリデバイスにデータの読み書きを行うメモリコントローラにおいて、

前記複数のメモリデバイスに対するメモリアクセス要求を保持する保持手段と、

前記複数のメモリデバイス毎のレイテンシを示すレイテンシ情報を格納する第1レジスタと、

前記複数のメモリデバイス毎の配線遅延を示す配線遅延情報を格納する第2レジスタと、

前記保持手段に保持されたメモリアクセス要求をメモリデバイスに発行する際に、前記第1レジスタに格納しているレイテンシ情報と前記第2レジスタに格納している配線遅延情報とに基づいて、前記メモリアクセス要求を発行する順序を変更するように制御する制御手段とを有し、

前記制御手段は、前記保持手段に保持した先頭のメモリアクセス要求に対する配線遅延情報をと、前記保持手段に保持した2番目のメモリアクセス要求に対する配線遅延情報をとにより、前記先頭のメモリアクセス要求が前記2番目のメモリアクセス要求よりもアクセス待ち時間が多い場合、前記2番目のメモリアクセス要求を発行する順番を変更することを特徴とするメモリコントローラ。

## 【請求項 2】

複数のメモリデバイスに対するメモリアクセス要求を保持する保持手段と、前記複数の

10

20

メモリデバイス毎のレイテンシを示すレイテンシ情報を格納する第1レジスタと、前記複数のメモリデバイス毎の配線遅延を示す配線遅延情報を格納する第2レジスタと、を備え、アクセスサイクルの異なる複数のメモリデバイスにデータの読み書きを行うメモリコントローラの制御方法であって、

前記保持手段に保持されたメモリアクセス要求をメモリデバイスに発行する際に、前記第1レジスタに格納しているレイテンシ情報を前記第2レジスタに格納している配線遅延情報とに基づいて、前記メモリアクセス要求を発行する順序を変更するように制御する制御工程を有し、

前記制御工程では、前記保持手段に保持した先頭のメモリアクセス要求に対する配線遅延情報と、前記保持手段に保持した2番目のメモリアクセス要求に対する配線遅延情報とにより、前記先頭のメモリアクセス要求が前記2番目のメモリアクセス要求よりもアクセス待ち時間が多い場合、前記2番目のメモリアクセス要求を発行するように順番を変更することを特徴とするメモリコントローラの制御方法。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、アクセスサイクルの異なる複数のメモリデバイスにデータの読み書きを行うメモリコントローラ及びその制御方法に関する。

【背景技術】

【0002】

20

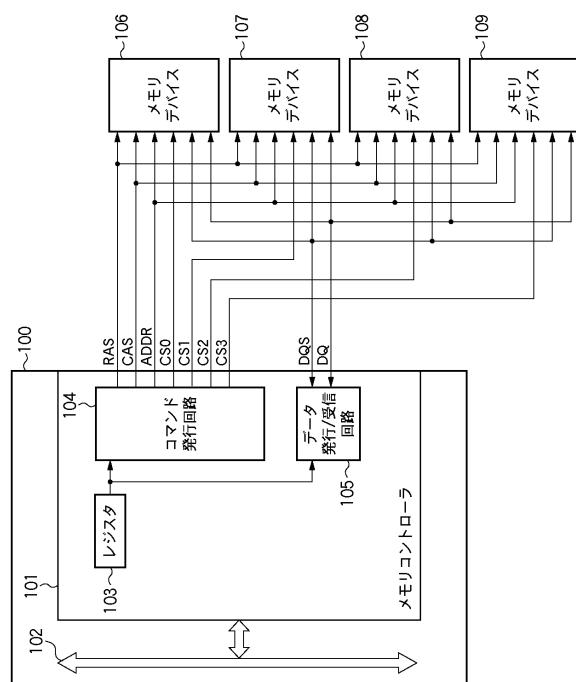

図1は、従来のメモリシステムにおける構成の一例を示す図である。図1に示す100はメモリコントローラを含むASIC(Application Specific Integrated Circuit)である。101はASIC100に含まれるメモリコントローラである。102はASIC100内でメモリコントローラ101と不図示の機能モジュールとを接続するチップ内部バスである。103はメモリコントローラ101と接続されるデバイスの条件を保存するレジスタである。

【0003】

104はメモリコントローラ101に接続されるメモリデバイスへアクセスコマンドを発行するコマンド発行回路である。105はメモリコントローラ101に接続されるメモリデバイスとの間でデータの送受信を行うデータ発行/受信回路である。106~109はメモリコントローラ101に接続されるメモリデバイスである。

30

【0004】

次に、図1を用いて、従来のASIC100内部のメモリコントローラ101の動作を説明する。まず、ASIC100内の不図示の機能モジュールからメモリデバイス106~109へのアクセス要求はチップ内部バス102を経由してメモリコントローラ101に伝えられる。一方、メモリコントローラ101は、受け取ったアクセス要求を解析し、該当する何れかのメモリデバイス106~109に対して、要求されたアクセスを満たすためのコマンドをコマンド発行回路104にて生成する。そして、そのコマンドをチップ外部への接続信号(RAS、CAS、ADDR、CS0~CS3)を用いて該当するメモリデバイスに発行し、データの送受信をデータ発行/受信回路105にて行う。

40

【0005】

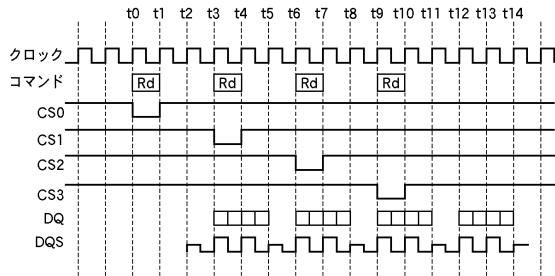

このときのチップ外部における信号の様子を図2に示す。図2では、RAS、CAS、ADDRは1つのコマンドに纏められている。また、メモリコントローラ101は、チップ内部バス102経由でメモリデバイス106~109への読み出し要求を順番に受け取り、メモリデバイス106~109に順に読み出しコマンドを発行する。

【0006】

通常、メモリデバイス106~109はバンクと呼ばれる複数の領域に分割され、各々の領域内的一部分をアクセス可能とし、それ以外の部分に対しては所定の手続きを行った後にアクセスが可能となる。この所定の手続きには、多くのクロックサイクルを必要とするが、各デバイスのバンク毎にアクセスできる部分は独立に設定できる。そこで、メモリ

50

コントローラ 101 内では要求されたコマンドを分析し、アクセスに際して所定の手続きが必要か否かを判断し、アクセスの順番を変更するといった操作が行われる場合が多い。これらの操作が行われている場合でも、図 2 に示すように、読み出しこマンドが連續し、該当するデバイスが異なれば、読み出しデータ (DQ 及び DQS) が衝突しないように読み出しこマンドの発行タイミングを制御する必要がある。

【特許文献 1】特開 2003-271445 号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

しかしながら、昨今のメモリデバイスにおける動作周波数の向上に伴い、従来のメモリコントローラでは無視されていた基板上の配線遅延が無視できない状況となりつつある。この状況を図 3 及び図 4 を用いて説明する。

【0008】

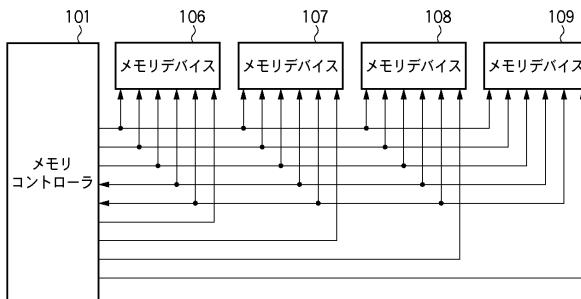

図 3 は、メモリコントローラとメモリデバイスとの関係を基板上のレイアウトイメージ的に書き直した図である。尚、図 3 に示す番号は、図 1 と同じものを用いている。図 3 に示すように、複数のメモリデバイス 106 ~ 109 を接続した場合、各メモリデバイスのメモリコントローラ 101 からの距離はそれぞれ異なり、メモリデバイス 106 から順にメモリデバイス 109 まで徐々に遠くに置かれることとなる。

【0009】

このような配置において、メモリコントローラ 101 が各メモリデバイスに読み出しを行った場合、各メモリデバイスとの距離の違いにより、読み出しデータの受け取りタイミングがメモリデバイスによって異なってくる。特に、クロック周期が短くなった場合には、クロックサイクルを超えたタイミングで読み出しデータがメモリコントローラ 101 に戻ってくる場合が考えられる。

【0010】

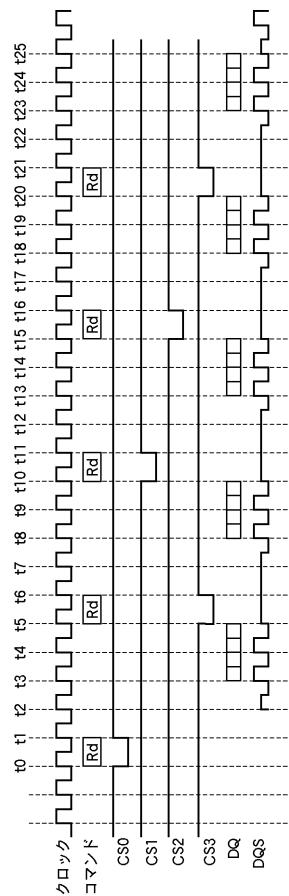

図 4 は、メモリデバイスがメモリコントローラから遠くなるに従って読み出しデータが 1 サイクルずつ遅く取り込まれるレイアウトになった場合のメモリデバイス間の待ちサイクル数を示す図である。ここで、メモリデバイスが異なる場合には最大待ちサイクル数分の待ちサイクルを与えなければデータの衝突が起こるため、メモリコントローラ 101 のデータバス上の動作タイミングは図 5 に示すように効率の悪い状況となる。

【0011】

本発明は、メモリデータバス上の効率を改善することを目的とする。

【課題を解決するための手段】

【0012】

本発明は、アクセスサイクルの異なる複数のメモリデバイスにデータの読み書きを行うメモリコントローラにおいて、前記複数のメモリデバイスに対するメモリアクセス要求を保持する保持手段と、前記複数のメモリデバイス毎のレイテンシを示すレイテンシ情報を格納する第 1 レジスタと、前記複数のメモリデバイス毎の配線遅延を示す配線遅延情報を格納する第 2 レジスタと、前記保持手段に保持されたメモリアクセス要求をメモリデバイスに発行する際に、前記第 1 レジスタに格納しているレイテンシ情報と前記第 2 レジスタに格納している配線遅延情報とに基づいて、前記メモリアクセス要求を発行する順序を変更するように制御する制御手段とを有し、前記制御手段は、前記保持手段に保持した先頭のメモリアクセス要求に対する配線遅延情報を、前記保持手段に保持した 2 番目のメモリアクセス要求に対する配線遅延情報をとにより、前記先頭のメモリアクセス要求が前記 2 番目のメモリアクセス要求よりもアクセス待ち時間が多い場合、前記 2 番目のメモリアクセス要求を発行するように順番を変更することを特徴とする。

【発明の効果】

【0014】

本発明によれば、複数のメモリデバイスとの間の配線遅延を示す情報と複数のメモリデバイスの各々のレイテンシ情報を基づき、各メモリデバイスに対するメモリアクセス要

10

20

30

40

50

求を発行する順序を変更するように制御することで、メモリデータバス上の効率を改善することが可能となる。

#### 【発明を実施するための最良の形態】

##### 【0015】

以下、図面を参照しながら発明を実施するための最良の形態について詳細に説明する。

##### 【0016】

###### 【第1の実施形態】

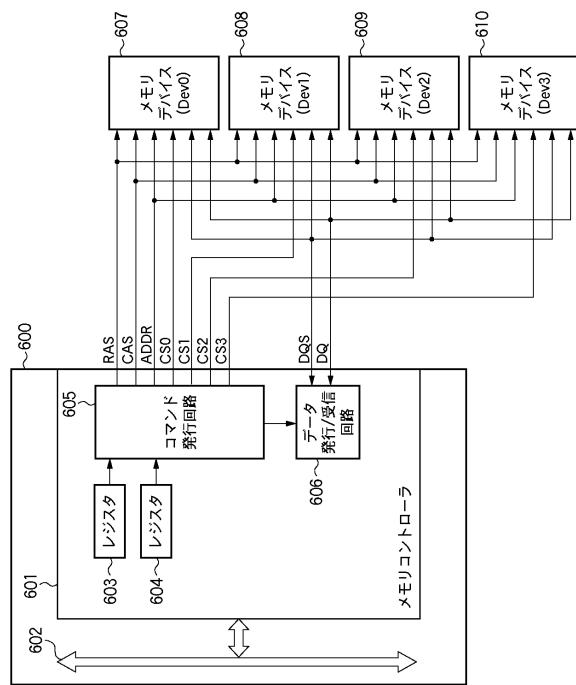

メモリコントローラがメモリデバイスへコマンドを発行する際に、デバイスレイテンシ情報と基板上の配線遅延情報に基づき、メモリデバイスへコマンドを発行する順序を制御する処理を、図6～図9を用いて説明する。

10

##### 【0017】

まず、第1の実施形態におけるメモリコントローラの構成及び動作を、図6及び図7を用いて説明する。

##### 【0018】

図6は、第1の実施形態におけるメモリシステムの構成の一例を示す図である。図6に示す600はメモリコントローラを含むASICである。601は第1の実施形態におけるメモリコントローラである。602はASIC600内でメモリコントローラ601と不図示の機能モジュールとを接続するチップ内部バスである。不図示の機能モジュールとメモリコントローラの間のトランザクションはチップ内部バスを介して送受信される。

20

##### 【0019】

603はメモリコントローラ601と接続されるデバイスのレイテンシ条件を保持するレジスタである。604はメモリコントローラ601と接続されるデバイスの配線遅延情報を保持するレジスタである。

##### 【0020】

605はメモリコントローラ601に接続されるメモリデバイスへアクセスコマンドを発行するコマンド発行回路である。606はメモリコントローラ601に接続されるメモリデバイスとの間でデータの送受信を行うデータ発行/受信回路である。607～610はメモリコントローラ601に接続されるメモリデバイスである。これ以降、メモリデバイスを単に「デバイス」と称す。

30

##### 【0021】

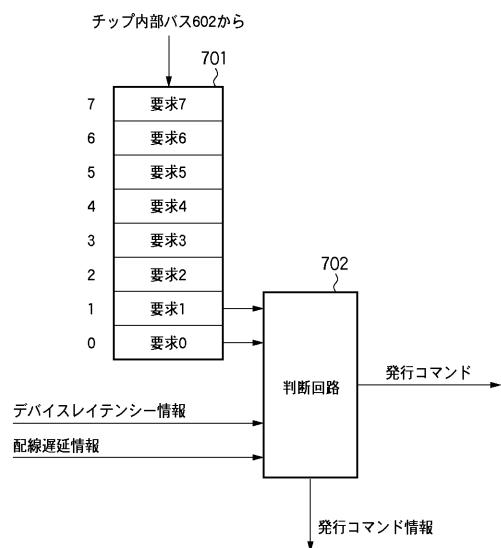

図7は、図6に示すコマンド発行回路605の構成の一例を示す図である。図7に示す701はバッファであり、チップ内部バス602から受け取ったメモリアクセスの要求を一時的に溜め込む。702は判断回路であり、バッファ701に溜められた複数の要求をデバイスに発行する際に、レイテンシ情報及び配線遅延情報に基づき、効率の良い順序に変更するように制御する。

##### 【0022】

まず、不図示の機能モジュールからチップ内部バス602を介してメモリアクセス要求がメモリコントローラ601へ伝達されると、その要求はコマンド発行回路605に伝えられる。これにより、コマンド発行回路605の内部では図7に示すように、伝えられたメモリアクセス要求は一旦バッファ701に蓄えられる。そして、判断回路702が、バッファ701が空でない場合に、バッファ701からその要求を取り出し、デバイスにコマンドとして発行し、かつ図6に示すデータ発行/受信回路606へ発行コマンドの情報を伝達する。

40

##### 【0023】

一方、データ発行/受信回路606は判断回路702から受け取った発行コマンド情報に基づき、デバイスへのデータの発行、メモリデバイスから受け取るデータのタイミング、チップ内部の受け取り機能モジュールの選択信号の生成を行う。

##### 【0024】

ここで、判断回路702が要求0を取り出した場合には、バッファ701は全ての要求を1つシフトする。つまり、現時点(シフト前)の要求1は判断回路702から要求0が

50

取り出された場合には、新たに要求 0 の位置へと移動し、現時点での要求 2 は新たに要求 1 の位置へ移動する。また、判断回路 702 が要求 1 を取り出した場合には、要求 0 は変更無く、現時点での要求 2 は新たに要求 1 の位置へ移動する。

#### 【 0 0 2 5 】

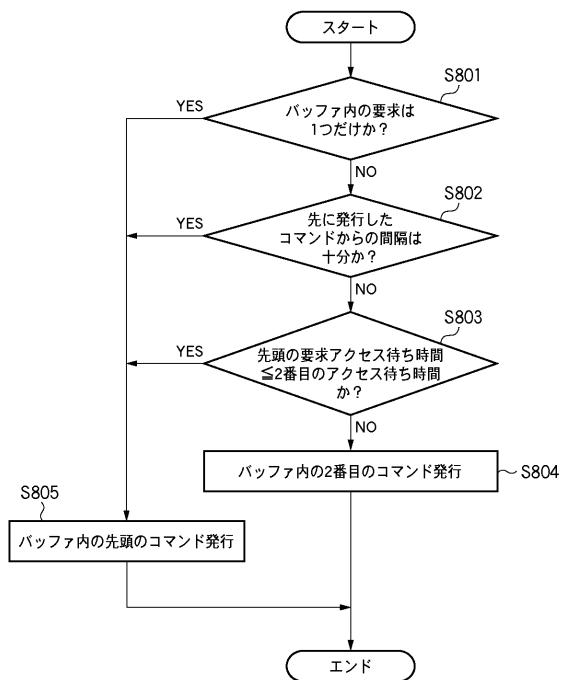

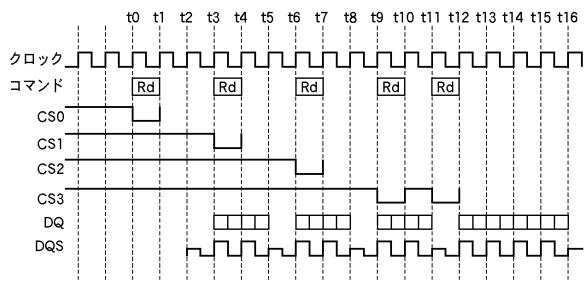

図 8 は、判断回路 702 で実行される判断処理を示すフローチャートである。図 9 は、バッファ 701 から取り出す要求を決定するときのタイミングを示す図である。尚、ここでは説明を簡単にするため、全ての要求は読み出し要求であるとし、各要求対象の領域は全てアクセス可能な状態になっているものとする。

#### 【 0 0 2 6 】

また、要求は、要求 0 (デバイス 607) 要求 1 (デバイス 610) 要求 2 (デバイス 608) 要求 3 (デバイス 609) 要求 4 (デバイス 610) の順番にバッファ 701 に格納されているものとする。そして、デバイス 607 への要求より先に発行したコマンドからは十分に間隔が取れているものとする。

#### 【 0 0 2 7 】

まず、ステップ S801 で、判断回路 702 は、バッファ 701 内の要求が 1 つだけか否かを判定し、1 つだけであればステップ S805 で、その要求のコマンド発行を行う。しかし、ステップ S801 で、前提のように、バッファ 701 内の要求が 1 つだけでなければステップ S802 で、先に発行したコマンドからの間隔が十分か否かを判断する。

#### 【 0 0 2 8 】

ここでは、上述の前提からコマンド間隔が十分であるので、図 9 に示す  $t_0$  でバッファ 701 内の先頭のコマンド発行 (デバイス 607 への読み出し) を行う。また、バッファ 701 では、上述したシフトが全ての要求に対して行われる。このシフトにより、要求は、要求 0 (デバイス 610)、要求 1 (デバイス 608)、要求 2 (デバイス 609)、要求 3 (デバイス 610) の順番となる。

#### 【 0 0 2 9 】

次に、バッファ 701 の内部が空でないことから、判断回路 702 は、次の要求の判断を開始する。そして、ステップ S803 で、判断回路 702 は、バッファ 701 の要求 0 (デバイス 610) と要求 1 (デバイス 608) のアクセス待ち時間を判定する。ここで、要求アクセス待ち時間は、レイテンシ情報を保持するレジスタ 603 と、配線遅延情報を保持するレジスタ 604 から得られるそれぞれのデバイス毎の読み出し要求発行後に、次のコマンド発行まで待たなければならない時間を示すものである。

#### 【 0 0 3 0 】

いま、デバイスのレイテンシが全て同一であるとすると、要求アクセス待ち時間の差は配線遅延情報に依存する。このように、メモリコントローラ 601 は、アクセスサイクルの異なる複数のメモリデバイスにデータの読み書きを行う。しかし、デバイス間の必要待ち時間が図 4 に示したテーブルで与えられるとすると、要求 0 のデバイス 610 へのアクセスには 3 サイクルの待ち時間を必要とする。一方、要求 1 のデバイス 608 へのアクセスには待ち時間が 1 サイクルしか必要とされない。従って、先頭の要求アクセス待ち時間は 2 番目のアクセス待ち時間より多いため、判断回路 702 はステップ S803 で、No と判定し、図 9 に示す  $t_3$  でバッファ 701 内の 2 番目 (要求 1) のコマンド発行を行う。

#### 【 0 0 3 1 】

また、バッファ 701 では、上述したシフトが全ての要求に対して行われる。その結果、要求は、要求 0 (デバイス 610) はそのままで、要求 2 (デバイス 609) が新たに要求 1 の位置に移動され、要求 3 (デバイス 610) が新たに要求 2 の位置に移動される。

#### 【 0 0 3 2 】

次に、バッファ 701 の内部が空でないことから、判断回路 702 は、次の要求の判断を開始する。そして、ステップ S803 で、判断回路 702 は、バッファ 701 の要求 0 (デバイス 610) と要求 1 (デバイス 609) のアクセス待ち時間を判定する。上述の

10

20

30

40

50

結果と同様に、判断回路702は、Noと判定し、図9に示すt6でバッファ701内の2番目(要求1)のコマンド発行を行う。

#### 【0033】

また、バッファ701では、上述したシフトが全ての要求に対して行われる。その結果、要求は、要求0(デバイス610)はそのままで、要求2(デバイス610)が新たに要求1の位置に移動される。

#### 【0034】

次に、バッファ701の内部が空でないことから、判断回路702は、次の要求の判断を開始する。そして、ステップS803で、判断回路702は、バッファ701の要求0(デバイス610)と要求1(デバイス610)のアクセス待ち時間を判定する。ここで、アクセス対象が同一のデバイスであるため、判断回路702は、Yesと判定し、図9に示すt9でバッファ701内の先頭の要求を実行する。

10

#### 【0035】

また、バッファ701では、上述したシフトが全ての要求に対して行われ、その結果、要求は、要求1(デバイス610)が新たに要求0の位置に移動される。

#### 【0036】

次に、バッファ701の内部が空でないことから、判断回路702は、次の要求の判断を開始する。この場合、バッファ701の内部の要求は要求0にあるデバイス610への要求のみであるので、判断回路702は、ステップS801でYesと判定し、ステップS805で、図9に示すt11でバッファ701の先頭の要求を実行する。この際、直前のコマンド発行対象デバイスと今回のコマンド発行対象デバイスが同一であることから、メモリデータバス上の空きサイクル無しとなるようにコマンドが発行されることは従来と同様である。

20

#### 【0037】

以上、基板における配線遅延情報に基づく動作について説明を行ってきたが、本発明は接続される各メモリデバイスに読み出しレイテンシが異なるデバイスを接続した場合にも上記説明と同様な効果を有する。その場合、上述した配線遅延情報をメモリデバイス間のレイテンシの差分情報と読み替えれば良い。

#### 【0038】

##### 【第2の実施形態】

30

次に、図面を参照しながら本発明に係る第2の実施形態を詳細に説明する。第1の実施形態では、各メモリデバイスの配線遅延情報をメモリコントローラ内の保持手段にて保持していた。しかし、各メモリデバイスの配線遅延情報をメモリコントローラ外部から端子にて供給するように構成しても良い。

#### 【0039】

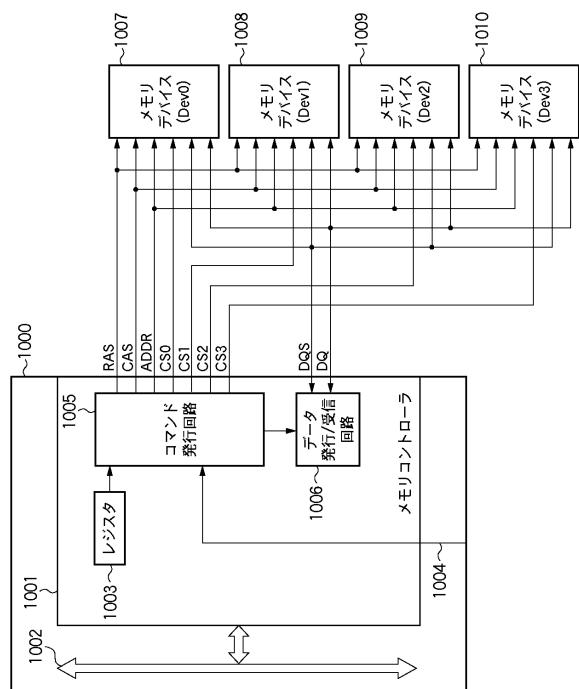

図10は、第2の実施形態におけるメモリシステムの構成の一例を示す図である。尚、図10に示す1000～1010は、第1の実施形態の図6に示す600～610に相当するものである。しかし、第1の実施形態では、各メモリデバイスの配線遅延情報を図6に示すレジスタ604に保持していたが、第2の実施形態では、外部から供給されるよう外部端子を備えるものである。

40

#### 【0040】

また、上述した各メモリデバイスの配線遅延情報を各メモリデバイスの読み出しレイテンシの差分情報に変えた場合にも第1の実施形態と同様な効果を得ることができる。

#### 【0041】

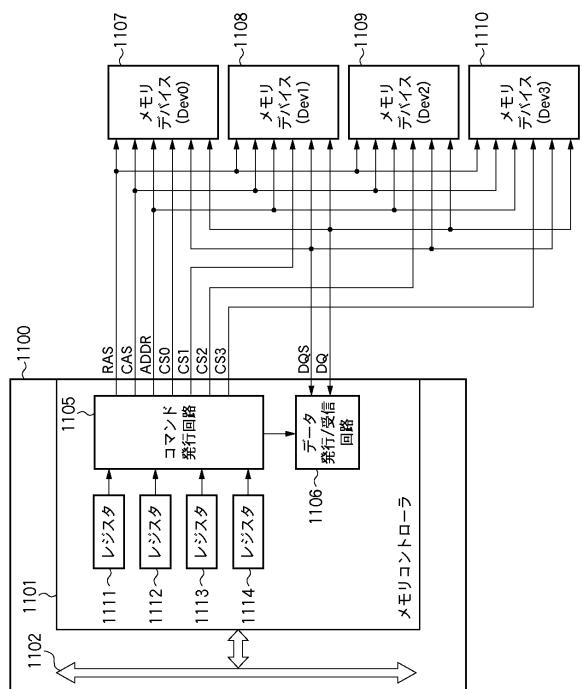

##### 【第3の実施形態】

次に、図面を参照しながら本発明に係る第3の実施形態を詳細に説明する。第1の実施形態では、各メモリデバイスの共通なレイテンシ情報と、個別のデバイスの配線遅延情報とをそれぞれレジスタに保持する構成としていた。しかし、第2の実施形態では、共通なレイテンシ情報を含めた個別のデバイス毎の遅延情報を格納する格納手段を備えるものである。

50

## 【0042】

図11は、第3の実施形態におけるメモリシステムの構成の一例を示す図である。尚、図11に示す1000～1002、1005～1010は、第1の実施形態の図6に示す600～602、605～610に相当するものである。

## 【0043】

図11に示す1111～1114は、デバイスのレイテンシ情報とデバイスの配線遅延情報とをそれぞれ保持するレジスタである。

## 【0044】

第3の実施形態によれば、第1の実施形態と同様な効果を得ることができる。

## 【0045】

尚、本発明は複数の機器（例えば、ホストコンピュータ、インターフェース機器、リーダ、プリンタなど）から構成されるシステムに適用しても、1つの機器からなる装置（例えば、複写機、ファクシミリ装置など）に適用しても良い。

## 【0046】

また、前述した実施形態の機能を実現するソフトウェアのプログラムコードを記録した記録媒体を、システム或いは装置に供給し、そのシステム或いは装置のコンピュータ（CPU若しくはMPU）が記録媒体に格納されたプログラムコードを読み出し実行する。これによっても、本発明の目的が達成されることは言うまでもない。

## 【0047】

この場合、コンピュータ読み取り可能な記録媒体から読み出されたプログラムコード自体が前述した実施形態の機能を実現することになり、そのプログラムコードを記憶した記録媒体は本発明を構成することになる。

## 【0048】

このプログラムコードを供給するための記録媒体として、例えばフレキシブルディスク、ハードディスク、光ディスク、光磁気ディスク、CD-ROM、CD-R、磁気テープ、不揮発性のメモリカード、ROMなどを用いることができる。

## 【0049】

また、コンピュータが読み出したプログラムコードを実行することにより、前述した実施形態の機能が実現されるだけでなく、次の場合も含まれることは言うまでもない。即ち、プログラムコードの指示に基づき、コンピュータ上で稼働しているOS（オペレーティングシステム）などが実際の処理の一部又は全部を行い、その処理により前述した実施形態の機能が実現される場合である。

## 【0050】

更に、記録媒体から読み出されたプログラムコードがコンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書込む。その後、そのプログラムコードの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるCPUなどが実際の処理の一部又は全部を行い、その処理により前述した実施形態の機能が実現される場合も含まれることは言うまでもない。

## 【図面の簡単な説明】

## 【0051】

【図1】従来のメモリシステムにおける構成の一例を示す図である。

【図2】チップ外部における信号の様子を示す図である。

【図3】メモリコントローラとメモリデバイスとの関係を基板上のレイアウトイメージ的に書き直した図である。

【図4】メモリデバイスがメモリコントローラから遠くなるに従って読み出しデータが1サイクルずつ遅く取り込まれるレイアウトになった場合のメモリデバイス間の待ちサイクル数を示す図である。

【図5】メモリコントローラ101のデータバス上の動作タイミングを示す図である。

【図6】第1の実施形態におけるメモリシステムの構成の一例を示す図である。

【図7】図6に示すコマンド発行回路605の構成の一例を示す図である。

10

20

30

40

50

【図8】判断回路702で実行される判断処理を示すフローチャートである。

【図9】バッファ701から取り出す要求を決定するときのタイミングを示す図である。

【図10】第2の実施形態におけるメモリシステムの構成の一例を示す図である。

【図11】第3の実施形態におけるメモリシステムの構成の一例を示す図である。

【符号の説明】

【0052】

600 メモリコントローラを含むASIC

601 メモリコントローラ

602 チップ内部バス

603 デバイスのレイテンシ条件を保持するレジスタ

10

604 デバイスの配線遅延情報を保持するレジスタ

605 コマンド発行回路

606 データ発行/受信回路

607 メモリデバイス(Dev 0)

608 メモリデバイス(Dev 1)

609 メモリデバイス(Dev 2)

610 メモリデバイス(Dev 3)

701 バッファ

702 判断回路

【図1】

【図2】

【図3】

【図4】

|      | Dev0 | Dev1 | Dev2 | Dev3 |

|------|------|------|------|------|

| Dev0 | 0    | 1    | 2    | 3    |

| Dev1 | 1    | 0    | 1    | 2    |

| Dev2 | 2    | 1    | 0    | 1    |

| Dev3 | 3    | 2    | 1    | 0    |

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(72)発明者 上田 浩市

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 桜井 茂行

(56)参考文献 特開2005-242500(JP, A)

国際公開第2005/114669(WO, A1)

特表2008-500668(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12/00 - 12/06

G 06 F 13/16 - 13/18