(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5581519号

(P5581519)

(45) 発行日 平成26年9月3日(2014.9.3)

(24) 登録日 平成26年7月25日(2014.7.25)

(51) Int.Cl.

H01L 23/12 (2006.01)

H05K 3/46 (2006.01)

F 1

H01L 23/12 501B

H01L 23/12 N

H05K 3/46 B

H05K 3/46 Q

請求項の数 11 (全 11 頁)

(21) 出願番号

特願2009-276270 (P2009-276270)

(22) 出願日

平成21年12月4日 (2009.12.4)

(65) 公開番号

特開2011-119502 (P2011-119502A)

(43) 公開日

平成23年6月16日 (2011.6.16)

審査請求日

平成24年10月9日 (2012.10.9)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100077621

弁理士 綿貫 隆夫

(74) 代理人 100092819

弁理士 堀米 和春

(74) 代理人 100146075

弁理士 岡村 隆志

(72) 発明者 清水 規良

長野県長野市小島田町80番地 新光電気

工業株式会社内

(72) 発明者 六川 昭雄

長野県長野市小島田町80番地 新光電気

工業株式会社内

最終頁に続く

(54) 【発明の名称】半導体パッケージとその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体チップが埋設された封止樹脂層を有する半導体パッケージの製造方法であって、支持基板上に、パッド形成面を上向きにして半導体チップを配置する工程と、前記半導体チップの前記パッド形成面および側面を直接被覆することによって該半導体チップが覆われるよう、前記支持基板上に封止樹脂層を形成する工程と、前記半導体チップのパッドの上面が表出して該パッドの上面と前記封止樹脂層の一方の面とが面一になるまで、前記封止樹脂層の上部を研磨する工程と、前記封止樹脂層の上部を研磨する工程の後に、前記封止樹脂層上に絶縁層を形成する工程と、

前記絶縁層に、前記パッドの上面を底面に露出する開口部を形成する工程と、前記絶縁層上に、前記開口部内に設けたビアにより前記パッドに接続される配線層を形成する工程と、

前記絶縁層上に、前記配線層において外部接続用パッドとなる部分を露出するソルダーレジスト膜を形成する工程と、

前記配線層を形成する工程の後の前記ソルダーレジスト膜を形成する工程の後に、前記支持基板を除去する工程と、

前記半導体チップの背面を、前記封止樹脂層の他方の面から露出させる工程と、を備えること

を特徴とする半導体パッケージの製造方法。

10

20

**【請求項 2】**

前記絶縁層と前記配線層とを複数積層して、最上層の配線層に、前記外部接続用パッドおよび前記ソルダーレジスト膜を形成する工程を備えること

を特徴とする請求項 1 記載の半導体パッケージの製造方法。

**【請求項 3】**

前記絶縁層、前記配線層、および前記ソルダーレジスト膜を合わせた厚さが、前記封止樹脂層の厚さより薄いこと

を特徴とする請求項 1 または請求項 2 記載の半導体パッケージの製造方法。

**【請求項 4】**

前記封止樹脂層は、モールド樹脂を用いて形成されること

を特徴とする請求項 1 ~ 3 のいずれか一項記載の半導体パッケージの製造方法。 10

**【請求項 5】**

前記支持基板は金属を用いて形成され、前記支持基板を除去する工程はエッチングによつて行われること

を特徴とする請求項 1 ~ 4 のいずれか一項記載の半導体パッケージの製造方法。

**【請求項 6】**

前記支持基板上に、固定用材料を介して半導体チップが配置され、

前記支持基板を除去する工程の後に、前記固定用材料を除去する工程を備えること

を特徴とする請求項 1 ~ 5 のいずれか一項記載の半導体パッケージの製造方法。 20

**【請求項 7】**

前記固定用材料は樹脂を用いて形成され、前記固定用材料を除去する工程は研磨によつて行われること

を特徴とする請求項 6 記載の半導体パッケージの製造方法。

**【請求項 8】**

パッドを有する半導体チップと、

前記半導体チップのパッド形成面と側面周囲を直接被覆し、且つ、前記パッドの上面を露出する一方の面を有する封止樹脂層と、

前記封止樹脂層の一方の面上に設けられた絶縁層と、

前記絶縁層に設けられ、前記パッドの上面を底面に露出する開口部と、

前記絶縁層上に設けられ、前記開口部内に設けられたビアにより前記パッドに接続された配線層と、

前記配線層上に設けられ、前記配線層において外部接続用パッドとなる部分を露出するソルダーレジスト膜と、を備え、

前記パッドの上面と前記封止樹脂層の一方の面とが同一の平坦面に形成されており、

前記半導体チップの背面が、前記封止樹脂層の他方の面側に露出していること

を特徴とする半導体パッケージ。 30

**【請求項 9】**

前記封止樹脂層が基板状に形成され、該封止樹脂層上に前記絶縁層と前記配線層とが複数積層され、最上層の配線層に、前記外部接続用パッドおよび前記ソルダーレジスト膜が設けられていること

を特徴とする請求項 8 記載の半導体パッケージ。 40

**【請求項 10】**

前記絶縁層、前記配線層、および前記ソルダーレジスト膜を合わせた厚さが、前記封止樹脂層の厚さより薄いこと

を特徴とする請求項 8 または請求項 9 記載の半導体パッケージ。

**【請求項 11】**

前記封止樹脂層は、モールド樹脂を用いて形成されていること

を特徴とする請求項 8 ~ 10 のいずれか一項記載の半導体パッケージ。

**【発明の詳細な説明】****【技術分野】**

50

**【0001】**

本発明は、半導体パッケージとその製造方法に関し、さらに詳細には、半導体チップを内蔵する半導体パッケージとその製造方法に関する。

**【背景技術】****【0002】**

現在、半導体チップ等の半導体装置を用いた電子機器の高性能化が進められており、基板へ半導体チップを実装する場合の高密度化や、また半導体チップを搭載した基板の小型化、省スペース化等が求められている。

**【0003】**

このため、半導体チップが埋め込まれたいわゆるチップ内蔵型の半導体パッケージとして、様々な構造が提案されている。また、このようなチップ内蔵型の半導体パッケージの製造方法に関しても、様々な技術が提案されている（特許文献1、特許文献2参照）。

**【先行技術文献】****【特許文献】****【0004】**

【特許文献1】国際公開第02/15266号パンフレット

【特許文献2】国際公開第02/33751号パンフレット

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

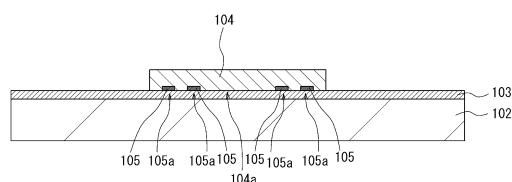

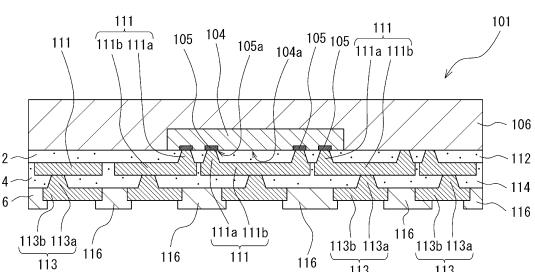

ここで、本願出願人において試作・検討を行った半導体パッケージ101の製造方法について説明する。

当該半導体パッケージの製造方法は、先ず、図11に示すように、厚さ0.2～0.5[m]程度の銅(Cu)板を用いて形成された支持基板102上に、ロールラミネート法等により樹脂材料(例えば、エポキシ樹脂等)からなるシート状の固定用材料103を設ける工程を実施する。

**【0006】**

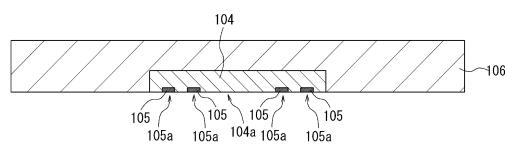

次いで、図12に示すように、支持基板102上に固定用材料103を介して、アクティブ面104aを下向きにして半導体チップ104を配置する工程を実施する。通常、マウンターを用いて配置を行う。

**【0007】**

次いで、図13に示すように、半導体チップ104が覆われるように、支持基板102上にモールド樹脂を用いて絶縁層106を形成する工程を実施する。

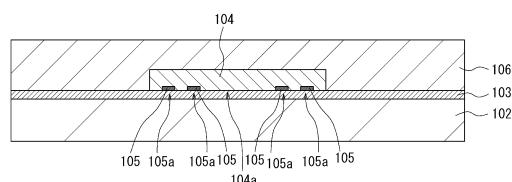

**【0008】**

次いで、図14に示すように、塩化第二銅水溶液を用いるエッチング法等によって支持基板102を除去する工程を実施する。その後、固定用材料103を除去する工程を実施する。

**【0009】**

次いで、図15に示すように、半導体チップ104のアクティブ面104a側に配線層および絶縁層を多層に積層する工程(ビルトアップ工程)を実施する。

**【0010】**

しかし、上記の製造方法の場合、図13により説明する工程において、加熱環境下で圧力が加えられることに起因して、固定用材料(ボンディングシート)103と仮搭載している半導体チップ104のパッド105との間にモールド樹脂が染み込む課題が生じていた。すなわち、当該部位にモールド樹脂が染み込むと、パッド105の表面105a上の残渣となってしまうため、ビルトアップ工程を実施するときにパッド105と配線層111(ここではビア111a)とを接続する妨げとなって、当該接続箇所における導通不良を発生させる原因となっていた。しかし、染み込む量や面積をコントロールすることは困難であった。

**【0011】**

10

20

30

40

50

また、図15により説明するビルトアップ工程を実施する際に、半導体チップ104を支持する層が絶縁層106のみとなってしまうため、同工程中（特に搬送時等）において反りが生じ易い課題があった。

#### 【0012】

また、モールド樹脂によって半導体チップ104を埋め込む構造であるため、絶縁層106の厚さを薄く形成することができなかった（図15参照）。

#### 【0013】

上記事情に鑑み、本発明は、パッドと配線層との接続不良の発生防止と、製造過程における半導体パッケージの反りの発生防止と、最終的に形成される半導体パッケージの薄型化とを同時に達成することが可能な半導体パッケージとその製造方法を提供することを目的とする。

10

#### 【課題を解決するための手段】

#### 【0014】

一実施形態として、以下に開示するような解決手段により、前記課題を解決する。

#### 【0015】

開示の半導体パッケージの製造方法は、半導体チップが埋設された封止樹脂層を有する半導体パッケージの製造方法であって、支持基板上に、パッド形成面を上向きにして半導体チップを配置する工程と、前記半導体チップの前記パッド形成面および側面を直接被覆することによって該半導体チップが覆われるように、前記支持基板上に封止樹脂層を形成する工程と、前記半導体チップのパッドの上面が表出して該パッドの上面と前記封止樹脂層の一方の面とが面一になるまで、前記封止樹脂層の上部を研磨する工程と、前記封止樹脂層の上部を研磨する工程の後に、前記封止樹脂層上に絶縁層を形成する工程と、前記絶縁層に、前記パッドの上面を底面に露出する開口部を形成する工程と、前記絶縁層上に、前記開口部内に設けたビアにより前記パッドに接続される配線層を形成する工程と、前記絶縁層上に、前記配線層において外部接続用パッドとなる部分を露出するソルダーレジスト膜を形成する工程と、前記配線層を形成する工程の後の前記ソルダーレジスト膜を形成する工程の後に、前記支持基板を除去する工程と、前記半導体チップの背面を、前記封止樹脂層の他方の面から露出させる工程と、を備えることを要件とする。

20

#### 【発明の効果】

#### 【0016】

開示の半導体パッケージの製造方法によれば、半導体チップのパッドの表面上に残渣が発生することを防止でき、当該残渣に起因して半導体パッケージに発生する導通不良を防止することができる。

また、配線層および絶縁層の形成工程後まで支持基板が除去されないため、製造過程における半導体パッケージに反り、うねりが発生することを防止もしくは低減できる。

また、非常に薄い半導体パッケージの製造が可能となる。

#### 【図面の簡単な説明】

#### 【0017】

【図1】本発明の実施形態に係る半導体パッケージの製造方法を説明するための説明図である。

40

【図2】本発明の実施形態に係る半導体パッケージの製造方法を説明するための説明図である。

【図3】本発明の実施形態に係る半導体パッケージの製造方法を説明するための説明図である。

【図4】本発明の実施形態に係る半導体パッケージの製造方法を説明するための説明図である。

【図5】本発明の実施形態に係る半導体パッケージの製造方法を説明するための説明図である。

【図6】本発明の実施形態に係る半導体パッケージの製造方法を説明するための説明図である。

50

【図7】本発明の実施形態に係る半導体パッケージの製造方法を説明するための説明図である。

【図8】本発明の実施形態に係る半導体パッケージの製造方法を説明するための説明図である。

【図9】本発明の実施形態に係る半導体パッケージの製造方法を説明するための説明図である。

【図10】本発明の実施形態に係る半導体パッケージの製造方法を説明するための説明図である。

【図11】本願出願人が試作・検討を行った半導体パッケージの製造方法を説明するための説明図である。10

【図12】本願出願人が試作・検討を行った半導体パッケージの製造方法を説明するための説明図である。

【図13】本願出願人が試作・検討を行った半導体パッケージの製造方法を説明するための説明図である。

【図14】本願出願人が試作・検討を行った半導体パッケージの製造方法を説明するための説明図である。

【図15】本願出願人が試作・検討を行った半導体パッケージの製造方法を説明するための説明図である。

#### 【発明を実施するための形態】

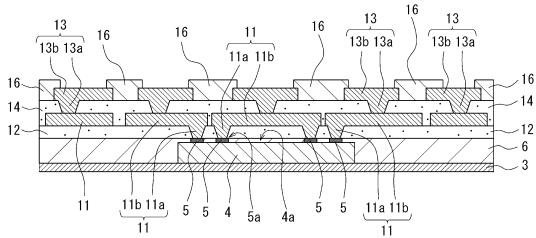

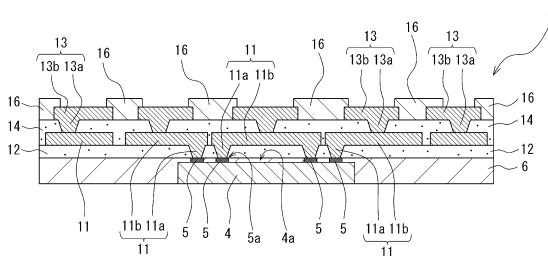

##### 【0018】

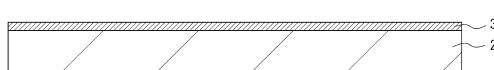

本発明の実施形態に係る半導体パッケージ1の製造方法について説明する。ここで、図1～図10は、半導体パッケージ1の製造工程を説明するための概略図(断面図)である。なお、後述のように、本発明では、電子部品4および絶縁層6と比較して、配線層11および絶縁層12が非常に薄い形状を有しているが、説明の便宜上、配線層11および絶縁層12を合わせた厚さを、絶縁層6よりも厚く図示している(配線層13および絶縁層14等についても同様)。その他にも、各図面において、説明の便宜上、実際の寸法・縮尺とは異なって図示されている部分がある。

##### 【0019】

先ず、図1に示すように、支持基板2を用意し、当該支持基板2の上面に固定用材料3を配設する工程を実施する。一例として、支持基板2は厚さ0.2～0.4[m]程度の銅(Cu)板を用いて形成される。その他にも、支持基板2として、エッチング法によって除去を行うことが可能なアルミニウム、ニッケル、鉄等からなる金属板や金属箔を用いることができる。30

##### 【0020】

また、固定用材料3は、樹脂材料(例えば、エポキシ樹脂等)からなるポンディングシートであって、ロールラミネート法、真空ラミネート法等のラミネート工法によって、支持基板2上に貼付される。なお、固定用材料3として、エポキシやポリイミド等を用いた接着剤を使用することができる。

その他にも、固定用材料3として、熱剥離性接着剤(例えば、接着剤中に所定温度の加熱により膨張する発泡剤が含有されたもの)を使用しても良い(効果については後述)。40

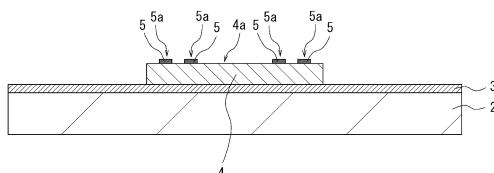

##### 【0021】

次いで、図2に示すように、支持基板2上に固定用材料3を介して、アクティブ面4aを上向きにして電子部品4を配置する工程を実施する。一例として、電子部品4を配置した後、キュアを行うことで、固定用材料3が硬化して電子部品4が支持基板2に対して固定されるため、以降の製造工程中において電子部品4の位置ズレが発生することを防止できる。なお、キュアを行う際の例として、大気中において、温度170～190[°]程度、時間30～60[分]程度の条件下で行われる。

##### 【0022】

ここで、電子部品4が半導体チップの場合を例に挙げて説明する。なお、電子部品4として、半導体チップ以外のものも当然に使用可能である。50

電子部品（半導体チップ）4は、アクティブ面（パッド形成面）4aに、ビア等（詳細は後述）と電気的な接続を行うためのパッド5が設けられている。また、一例として、パッド5は、半導体チップ4の回路に接続された平坦なアルミパッド上に、銅（Cu）を用いて形成される。

一例として、半導体チップ4の形状は、例えば、厚さ75～500[μm]程度（本実施形態では、375[μm]程度）、外形12[mm]×12[mm]程度である。また、パッド5の形状は、直径110[μm]程度、高さ10～30[μm]程度（本実施形態では、25[μm]程度）の円柱形状である。

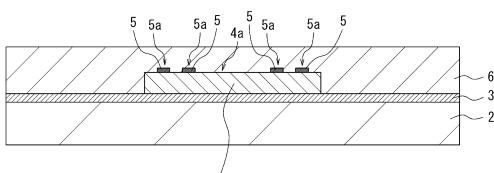

#### 【0023】

次いで、図3に示すように、半導体チップ4が覆われるように、支持基板2上にモールド樹脂を用いて絶縁層（封止樹脂層）6を形成する工程を実施する。10その後、キュアを行うことによって、モールド樹脂を硬化させる。これにより、半導体チップ4の側面が絶縁層（封止樹脂層）6で被覆されると共に、半導体チップ4のアクティブ面（パッド形成面）4a上にも絶縁層（封止樹脂層）6が設けられる。一例として、半導体パッケージ1として完成したときに、半導体チップ4側面周囲部分の絶縁層（封止樹脂層）6の幅が、0.2～6[mm]程度（本実施形態では、1.5[mm]程度）となる。これにより、半導体チップ4側面周囲の絶縁層（封止樹脂層）6上に配線層や外部接続用のパッドを設けることができ、半導体パッケージの多端子化に対応可能である。

また、本実施形態においては、モールド樹脂には、フィラー（例えば、二酸化ケイ素）20が含有された樹脂材料（本実施形態では、エポキシ樹脂）が用いられる。例えば、フィラー含有率は、50～80[w t %]程度である。また、キュアを行う際の例として、大気中において、温度200[ ]程度、時間60[分]程度の条件下で行われる。

なお、絶縁層（封止樹脂層）6を形成する方法としては、トランスファーモールドや、インジェクションモールド、ポッティング等の各種方法を用いることができる。

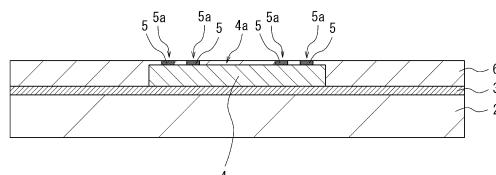

#### 【0024】

次いで、図4に示すように、半導体チップ4のパッド5の上面5aが表出（露出）するまで、絶縁層6の上部を研磨する工程を実施する。当該研磨工程は、一例として、研削あるいは研磨の機械的な処理方法によって行われる。ここで、絶縁層6の厚さは、半導体チップ4の厚さに応じて変化するが、例えば、厚さ85～530[μm]程度（本実施形態では、400[μm]程度）であり、半導体チップ4のアクティブ面（パッド形成面）4a上には、厚さ10～30[μm]程度（本実施形態では、25[μm]程度）の絶縁層（封止樹脂層）6が形成される。半導体チップ4のアクティブ面4aを絶縁層（封止樹脂層）6により確実に保護することができるため好適である。30

このとき、絶縁層6の上面（研磨面）とパッド5の上面5aとが、略同一の平坦面（面一）に形成されると、後工程において、精度良く配線層11および絶縁層12を積層できるため好適である。

なお、上記研磨工程の後に、さらに、CMP（Chemical Mechanical Polishing：化学的機械的研磨）法もしくはエッチング法によって、パッド5の上面5aを平滑にする工程を追加しても良い。

#### 【0025】

次いで、絶縁層6の上に、層間接続を行うビア11aと配線パターン11bにより構成される配線層11と絶縁層12とを形成する工程を実施する。本発明では、絶縁層6を基体として、その上に薄い膜状に配線層11と絶縁層12とが積層される構造を有する。例えば、配線パターン11bは、厚さ3[μm]程度であり、絶縁層12は、厚さ6～7[μm]程度である。

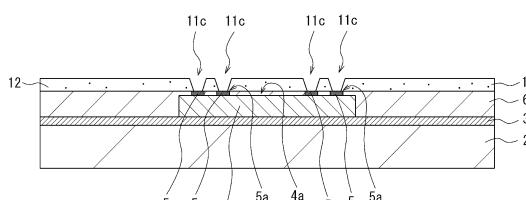

先ず、図5に示すように、絶縁層6の上に、スクリーン印刷法、樹脂フィルムのラミネート、もしくは塗布法等により、エポキシやポリイミド等の感光性樹脂材料よりなる絶縁層12を形成する。次に、この絶縁層12に対してマスクパターン（不図示）を介して光線を照射し露光・現像させることでパターニングを行い、当該絶縁層12におけるビア11aの形成予定位置（ここでは、図5に示すように、パッド5の上方位置等）に、パッド4050

5の上面5aが底面に露出するように開口部11cを形成する。次に、キュアを行い、絶縁層12を硬化させる。

なお、他の方法として、非感光性のエポキシやポリイミド等の絶縁樹脂により絶縁層12を形成し、レーザ加工によりビア11a用の開口部11cを形成しても良い(後述の絶縁層14およびビア13aに関しても同様)。

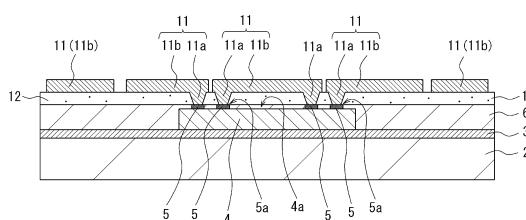

#### 【0026】

次に、絶縁層12上にスパッタ法によりシード層を形成する(不図示)。このとき、開口部11cの内壁面を含めてシード層を形成する。一例として、シード層はチタン(Ti)/銅(Cu)の二層で、厚さ50[nm]/500[nm]程度に形成する(銅(Cu)が表面となるように形成する)。なお、無電解銅めっき法によりシード層を形成してもよい。

#### 【0027】

次に、シード層上に、めっきレジストを形成し、露光・現像により配線パターン11bの形成位置のシード層を露出させるめっきレジストパターンを形成する。

次いで、シード層からの給電により電解銅めっきを施し、めっきレジストパターンから露出するシード層上に銅めっきを析出させる。この際、ビア用の開口部内を銅めっきで充填する。

次いで、めっきレジストの除去と、めっきレジスト除去により露出した部分のシード層の除去を行い、ビア11aと配線パターン11bからなる配線層11を形成する。

なお、上記の方法(セミアディティブ法)に代えて、サブトラクティブ法等、他の方法で配線層11を形成しても良い。

#### 【0028】

このように、図5、図6により説明した工程を備えて、配線層11および絶縁層12が形成され、当該配線層11と半導体チップ4のパッド5(ここでは上面5a)とが接続される。

#### 【0029】

上記の通り、絶縁層(封止樹脂層)6は、封止性の向上等を目的としてフィラー等が含有されているため、その上に直接、配線層を形成した場合、絶縁層(封止樹脂層)6との密着性が必ずしも良好ではなく、配線パターンの剥離等の問題が生じ得る。しかし、本発明では、絶縁層(封止樹脂層)6上に絶縁層12を形成し、この絶縁層12上に配線層11を形成するため、絶縁層12上に密着性良く配線層11を形成することができる。

#### 【0030】

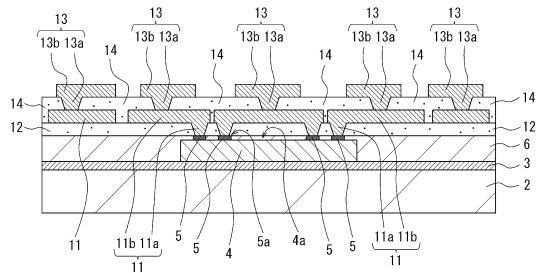

次いで、図7に示すように、前述の図5、図6により説明した工程と同様の形成工程を所定回数繰り返して、所定の多層構造となるように、順次、配線層13、・・・と絶縁層14、・・・とを積層する工程(ビルトアップ工程)を実施する。

ここで、一例として、配線層13以降を形成する工程は、配線層11を形成する工程と同様であり、絶縁層14以降を形成する工程は、絶縁層12を形成する工程と同様である。なお、本実施形態では、配線パターン13bは、厚さ10[μm]程度であり、絶縁層14は、厚さ10[μm]程度である。

#### 【0031】

次いで、図8に示すように、印刷等の方法を用いて最上層にソルダーレジスト膜16を形成する工程を実施する。このとき、配線層13の一部分を露出する開口部を有するように形成する。当該開口部から露出する配線層13の一部分が、外部接続用のパッドとなる。一例として、当該パッドの直径は300[μm]程度であり、ソルダーレジスト膜16の厚さは20[μm]程度である。なお、当該パッド部分に、表面保護層として、無電解めっきによりニッケル(Ni)めっき層と金(Au)めっき層を、この順に設けても良い。

ここで、配線層13に設けた外部接続用のパッドは、当該パッドにはんだボールやリードピンを接続して外部接続端子としても良く、あるいは、当該パッド自体を外部接続端子としても良い。

10

20

30

40

50

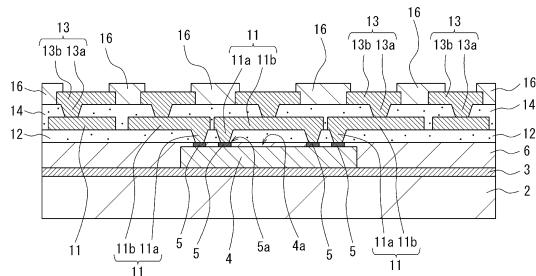

**【0032】**

次いで、図9に示すように、多層構造の最下層を構成している支持基板2を除去する工程を実施する。一例として、本実施形態においては、支持基板2は銅を用いて形成されているため、例えば塩化第二銅水溶液を用いるエッティング法によって除去を行う。

**【0033】**

次いで、図10に示すように、支持基板2が除去されたことによって最下面に露出した固定用材料3を除去する工程を実施する。これにより、絶縁層(封止樹脂層)6が基板状(平板状)に形成される。また、半導体チップ4の背面が絶縁層(封止樹脂層)6の裏面側に露出するように形成される。さらに、半導体チップ4の背面と絶縁層(封止樹脂層)6の裏面とが面一の平坦面に形成される。よって、半導体パッケージ1の薄型化および放熱性向上が図られる。10

一例として、エポキシ樹脂を用いて形成された固定用材料3を除去する工程は研磨(研削、研磨、CMP等)によって行われる。ちなみに、固定用材料3は、モールド樹脂と比較すれば、極めて研磨が容易である。

**【0034】**

なお、別 の方法として、固定用材料3に熱剥離性接着剤が使用されている場合には、図8に示す工程後に、所定温度に加熱することによって固定用材料3の接着性が消失し、半導体チップ4および絶縁層6と固定用材料3との界面から、半導体パッケージ1と固定用材料3および支持基板2とが分離し、容易に半導体パッケージ1を得ることができる。

**【0035】**

以上説明した工程を備えて、本発明に係る半導体パッケージ1の製造が行われる。

なお、本実施形態においては、実際は、支持基板2上に複数の半導体チップ4を搭載して、上記工程を実施し、支持基板2および固定用材料3を除去後、少なくとも一つの半導体チップ4を含むように絶縁層6、12、14、・・・、およびソルダーレジスト膜16を切断して、一度に複数個の半導体パッケージ1を得ている。

一例として、半導体パッケージ1は、平面形状が矩形の基板状(平板状)であり、その寸法は、幅15[m]×奥行き15[m]×厚さ0.44[m]程度である。

また、半導体パッケージ1は、全ての配線層11、13、・・・、絶縁層12、14、・・・、およびソルダーレジスト膜16を合わせた厚さが、絶縁層(封止樹脂層)6と比較して、非常に薄い形状を有している。30

**【0036】**

以上の通り、開示の半導体パッケージとその製造方法によれば、パッド上面が表出するまで研磨する工程により、あるいは当該工程と共にパッド上面を研磨する工程が追加されて、パッド上面に残渣が無い状態を生じさせることができる。したがって、その後、配線層の形成工程を実施するに際し、パッドと配線層との接続を良好に行うことができ、導通不良の発生を防止することができる。

**【0037】**

また、パッド上面が表出するまで研磨する工程によって、パッド上面とモールド樹脂からなる絶縁層の上面とが高精度の平坦面として得られる。したがって、当該平坦面を基礎として、ビルトアップ工程によって形成される多層構造を有する半導体パッケージの各層を高精度に積層することが可能となる。40

**【0038】**

剛性の高い金属材料からなる支持基板を有した状態で、製造工程(特に、ビルトアップ工程)を実施することが可能となるため、製造工程中に半導体パッケージにおいて反り、うねりの発生を防止することができる。このことは、半導体パッケージにおけるクラック発生防止の観点からも有効である。その一方で、銅を用いた支持基板は、除去工程も容易である。

**【0039】**

また、最終的に、半導体パッケージから支持基板を除去することが可能であり、除去された支持基板と半導体チップとの間にはモールド樹脂からなる絶縁層が形成されないため50

、半導体パッケージの薄型化が可能である。一例として、これまでの製造方法に対して、200 [μm] 程度の薄型化が可能という顕著な効果が得られる。

さらに、固定用材料の除去も可能であるため、半導体パッケージのより一層の薄型化が可能となる。

#### 【0040】

また、アクティブ面に設けられるパッドの周囲がモールド樹脂のみで覆われているため、従来、パッドとピアとの接続部において課題とされたクラック発生を解決することが可能となる。

#### 【0041】

なお、本発明は、以上説明した実施例に限定されることなく、本発明を逸脱しない範囲において種々変更可能であることは言うまでもない。特に、電子部品として半導体チップを例に挙げて説明したが、これに限定されるものではない。

#### 【符号の説明】

#### 【0042】

1、101 半導体パッケージ

2、102 支持基板

3、103 固定用材料

4、104 電子部品(半導体チップ)

5、105 パッド

6、12、14、106、112、114 絶縁層

11、13、111、113 配線層

11a、13a、111a、113a ピア

11b、13b、111b、113b 配線パターン

16、116 ソルダーレジスト膜

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図15】

【図14】

---

フロントページの続き

審査官 宮本 靖史

(56)参考文献 特開2008-288481(JP,A)

特開2001-217381(JP,A)

特開2004-327724(JP,A)

特開2004-047931(JP,A)

特開2006-222164(JP,A)

特開2004-241660(JP,A)

特開2000-124354(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12 - 23/15

H05K 3/46