【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第6部門第4区分

【発行日】平成22年5月13日(2010.5.13)

【公表番号】特表2009-531798(P2009-531798A)

【公表日】平成21年9月3日(2009.9.3)

【年通号数】公開・登録公報2009-035

【出願番号】特願2009-501796(P2009-501796)

【国際特許分類】

G 11 C 16/06 (2006.01)

G 11 C 16/02 (2006.01)

G 11 C 16/04 (2006.01)

【F I】

G 11 C 17/00 6 3 3 E

G 11 C 17/00 6 1 2 F

G 11 C 17/00 6 1 2 E

G 11 C 17/00 6 2 2 E

【手続補正書】

【提出日】平成22年3月23日(2010.3.23)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

基板上にメモリセルを有する複数のストリングを含むメモリアレイであって、当該メモリアレイは、複数のブロックを含み、各ブロックは、複数のページを含み、複数のワードラインがストリングを横切りメモリセルの各ページとなる、前記メモリアレイと、

アドレス命令に応答し、かつ前記アドレス命令に従いブロックを選択しさらに前記アドレス命令に従い選択されたブロックの中の少なくとも1つのページを選択するように構成された選択器と、

選択されたブロックの選択されたページが消去されるように基板にバイアス電圧を印加する基板バイアスを印加するものと、

を有する不揮発性メモリ。

【請求項2】

前記選択器は、

前記アドレス命令に含まれるブロックアドレス情報をデコードし、デコードされたブロックアドレスを提供する第1のデコーダと、

前記アドレス命令に含まれるページアドレス情報をデコードし、デコードされたページアドレスを提供する第2のデコーダとを有する、請求項1に記載の不揮発性メモリ。

【請求項3】

前記第2のデコーダは、

デコードされたページアドレスに応答して複数のページ選択信号を提供する出力回路を含む、請求項2に記載の不揮発性メモリ。

【請求項4】

前記選択器はさらに、デコードされたブロックアドレスに応答して複数のブロック選択信号を提供するブロック/ページ選択器を含む、請求項3に記載の不揮発性メモリ。

【請求項5】

前記ブロック / ページ選択器は、複数のグループの信号バス回路を含み、各グループは、複数のイネーブル / ディスエイブルのエレメントを有し、各々のイネーブル / ディスエイブルのエレメントは、各ブロックの複数のワードラインの各々つに結合される、請求項 4 に記載の不揮発性メモリ。

【請求項 6】

前記ブロック / ページ選択器はさらに、複数のドライバを含み、各ドライバは、デコードされたブロックアドレスに応答して各ブロック選択信号を提供してブロック選択を実行し、各ブロック選択信号は、各グループのイネーブル / ディスエイブルのエレメントに共通に提供される、請求項 5 に記載の不揮発性メモリ。

【請求項 7】

イネーブル / ディスエイブルのエレメントの各々は、

ブロック選択信号を受け取る第 1 の接続と、

ページ選択信号を受け取る第 2 の接続と、

各ワードラインに結合され、各メモリセルへゲートバイアスを提供してページ選択を実行する第 3 の接続と、を含む請求項 6 に記載の不揮発性メモリ。

【請求項 8】

イネーブル / ディスエイブルのエレメントの各々は、

ブロック選択信号を受け取るゲートと、

ページ選択信号を受け取る入力接続と、

ゲートバイアスとしての受け取られたページ選択信号を各メモリセルへの各ワードラインへ転送する出力接続と、を有するトランジスタを含み、

ゲートへのブロック選択信号に応答して、トランジスタは、入力接続から出力接続へページ選択信号を転送するようにイネーブルされる、請求項 7 に記載の不揮発性メモリ。

【請求項 9】

前記第 2 のデコーダの出力回路は、デコードされたページアドレスに応答してページ選択信号として第 2 の電圧を提供するよう構成され、

第 2 の電圧のページ選択信号は、デコードされたページアドレスによって選択されたページのワードラインに対するイネーブルトランジスタに提供され、

第 1 の電圧と第 2 の電圧との電圧差は、ページ消去動作を実行する、請求項 8 に記載の不揮発性メモリ。

【請求項 10】

前記第 2 のデコーダの出力回路はさらに、デコードされたページアドレスに応答してページ選択信号として第 3 の電圧を提供するよう構成され、

第 3 の電圧のページ選択信号は、デコードされたページアドレスにより非選択のページのワードラインに対するイネーブルトランジスタに提供される、請求項 9 に記載の不揮発性メモリ。

【請求項 11】

ワードラインデコーダは、基板電圧よりも低い第 2 の電圧と、基板電圧に近い第 3 の電圧とを提供し、第 1 の電圧と基板電圧との電圧差は、選択されたワードラインのメモリセルのページが消去されるようにする、請求項 10 に記載の不揮発性メモリ。

【請求項 12】

電圧供給は、0 ボルトの第 1 の電圧を提供する第 1 の供給と、第 3 の電圧と同じ第 2 の電圧を提供する第 2 の供給とを含む請求項 11 に記載の不揮発性メモリ。

【請求項 13】

複数のブロックの不揮発性メモリアレイのページを消去する方法であって、各ブロックが複数のページを有し、メモリアレイが基板上にメモリセルを有する複数のストリングを含み、複数のワードラインがストリングを横切りメモリセルの各ページとなる、前記方法は、

アドレス命令に従いブロックを選択すること、

アドレス命令に従い選択されたブロックの中の少なくとも 1 つのワードラインを選択す

ること、および

選択されたブロックの選択されたページが消去されるように基板に第1の電圧を印加することを含む方法。

【請求項14】

前記ブロックを選択するステップは、

選択されたブロックのワードラインに対しイネーブル／ディスエイブルのエレメントをイネーブルすることを含む、請求項13に記載の方法。

【請求項15】

前記少なくとも1つのワードラインを選択するステップは、

選択されたワードラインに対応するイネーブルされたイネーブル／ディスエイブルのエレメントを介して、選択されたブロックの少なくとも1つの選択されたワードラインに第2の電圧を印加すること、

非選択のワードラインに対応するイネーブルされたイネーブル／ディスエイブルのエレメントを介して、選択されたブロックの非選択ワードラインに第3の電圧を印加すること、を含む請求項14に記載の方法。

【請求項16】

前記第1の電圧を印加するステップは、

基板電圧と異なる第1の電圧を印加することを含み、第1の電圧と基板電圧との電圧差は、選択されたワードラインのメモリセルのページを消去させるものであり、

前記第2の電圧を印加するステップは、

第1の電圧と異なる第2の電圧を印加することを含み、第2の電圧と基板電圧との電圧差は、非選択のワードラインのメモリセルのページを消去させない、請求項15に記載の方法。

【請求項17】

前記第1の電圧を印加するステップは、基板電圧よりも低い電圧を印加することを含み、

前記第2の電圧を印加するステップは、基板電圧に近い電圧を印加することを含む、請求項16に記載の方法。

【請求項18】

前記第1の電圧を印加するステップは、約0ボルトを印加することを含む、請求項17に記載の方法。

【請求項19】

前記第1の電圧を印加するステップは、第2の電圧よりも低い電圧を印加することを含み、

前記第2の電圧を印加するステップは、基板電圧よりも低い電圧を印加することを含み、第1の電圧と基板電圧との電圧差は、選択されたワードラインのメモリセルのページを消去させる、請求項18に記載の方法。

【請求項20】

前記ブロックを選択するステップは、ブロックアドレスに従いブロック選択信号を提供することを含み、

前記各イネーブル／ディスエイブルのエレメントをイネーブルするステップは、選択されたブロックのイネーブル／ディスエイブルのエレメントにブロック選択信号を印加することを含む、請求項19に記載の方法。

【請求項21】

前記少なくとも1つのワードラインを選択するステップは、ページアドレスに従いページ選択信号を提供することを含み、

選択電圧を印加するステップは、ページ選択信号を選択されたブロックの選択されたワードラインに印加すること、および

イネーブルされたイネーブル／ディスエイブルのエレメントを介して、選択されたワードラインに前記選択電圧を印加することを含む、請求項20に記載の方法。

【手続補正2】

- 【補正対象書類名】図面

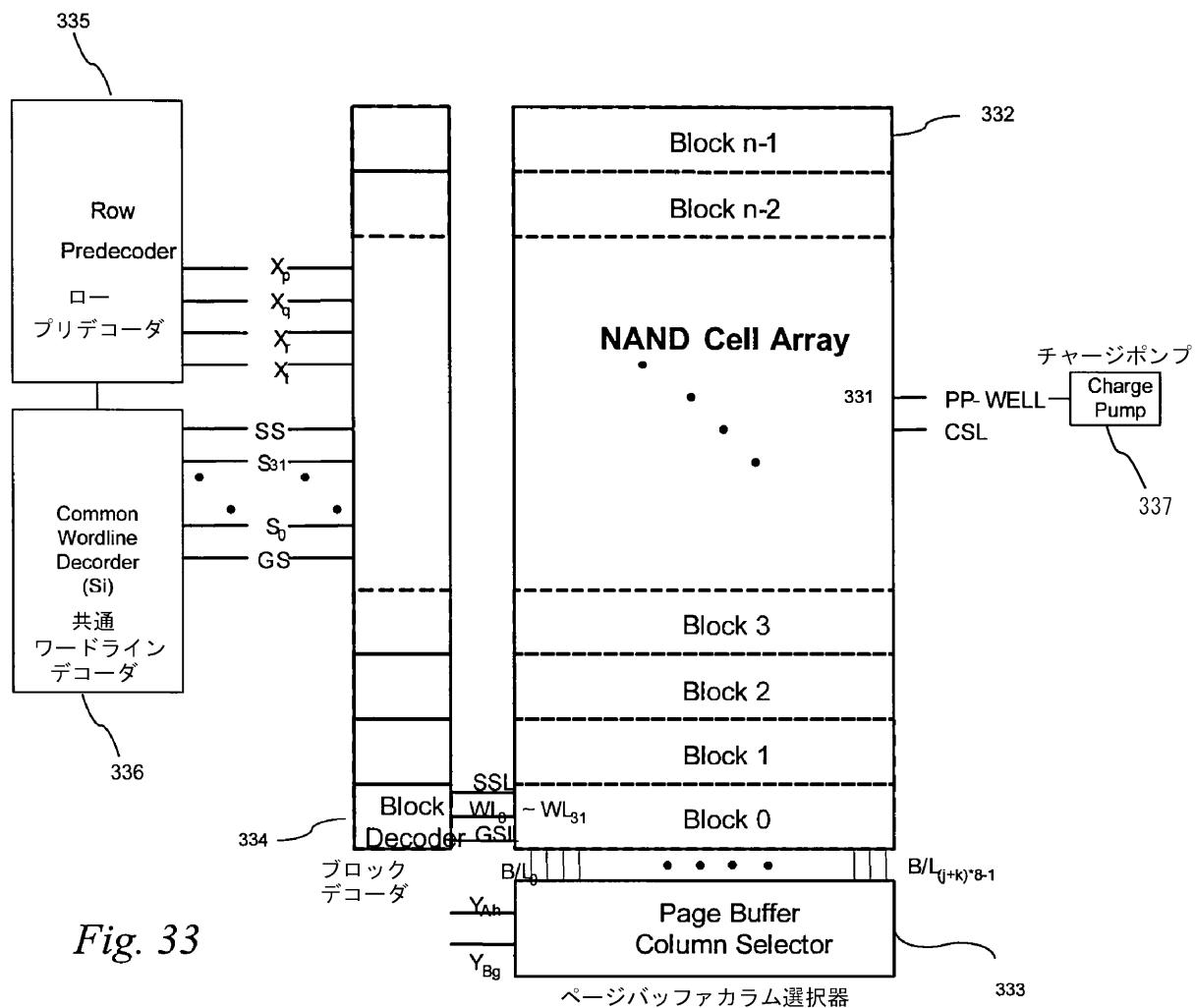

【補正対象項目名】図 3 3

【補正方法】変更

【補正の内容】

【図 3 3】

- 【手続補正 3】

【補正対象書類名】図面

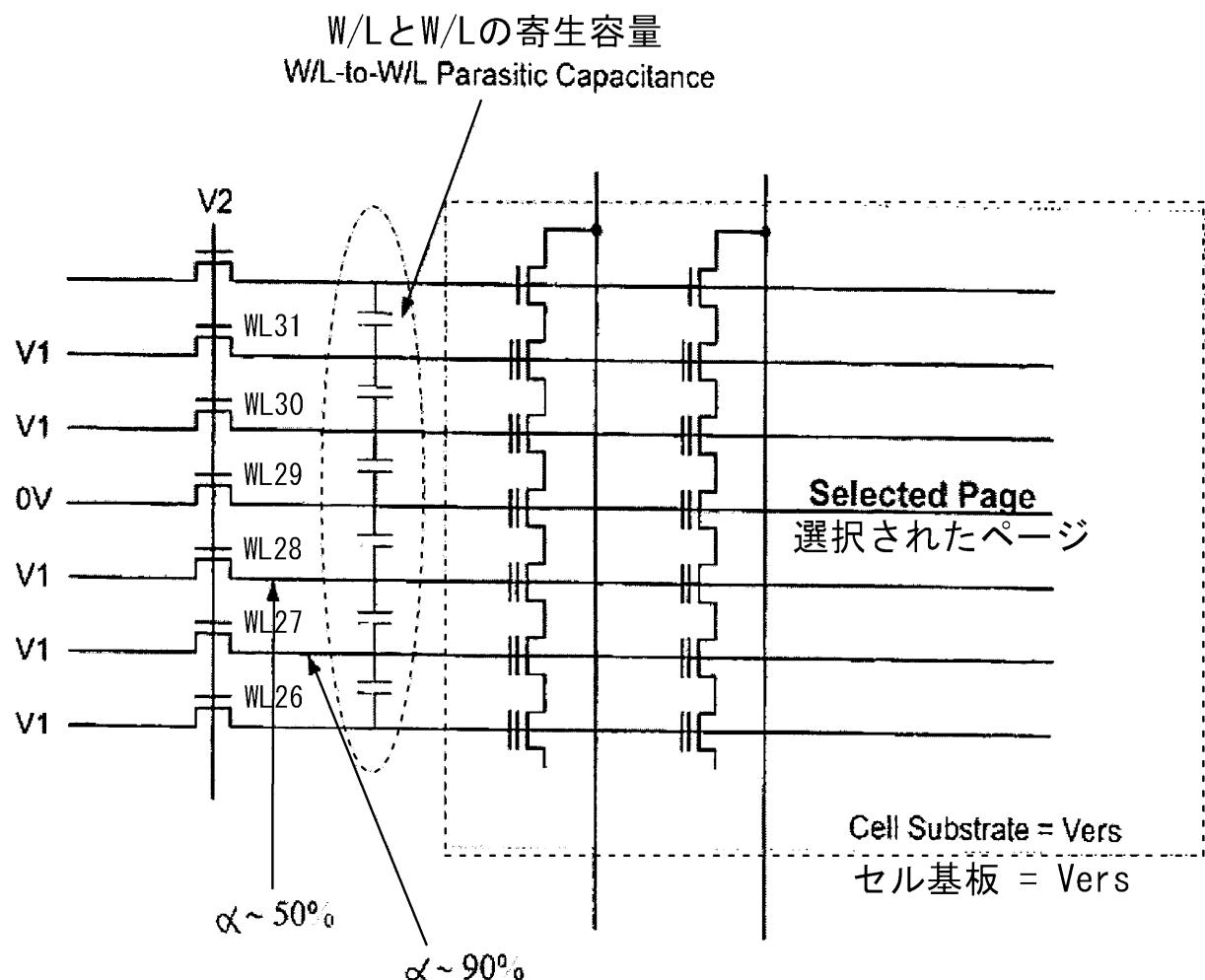

【補正対象項目名】図 5 0

【補正方法】変更

【補正の内容】

【図 50】

Fig. 50