(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6574549号

(P6574549)

(45) 発行日 令和1年9月11日(2019.9.11)

(24) 登録日 令和1年8月23日(2019.8.23)

(51) Int.Cl.

H03K 17/687 (2006.01)

F 1

H03K 17/687

G

請求項の数 25 外国語出願 (全 15 頁)

(21) 出願番号 特願2014-3422 (P2014-3422)

(22) 出願日 平成26年1月10日 (2014.1.10)

(65) 公開番号 特開2014-138423 (P2014-138423A)

(43) 公開日 平成26年7月28日 (2014.7.28)

審査請求日 平成29年1月6日 (2017.1.6)

(31) 優先権主張番号 13/742,086

(32) 優先日 平成25年1月15日 (2013.1.15)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 599034594

コーポ ユーエス、インコーポレイテッド

アメリカ合衆国オレゴン州97124・ヒ

ルスボロ・ノースイーストブルックウッド

パークウェイ 2300

2300 NE Brookwood P

arkway, Hillsboro, Or

egon 94124, U. S. A.

(74) 代理人 100105924

弁理士 森下 賢樹

(72) 発明者 プラブハカー、ラビシャンカー

アメリカ合衆国オレゴン州97124・ヒ

ルスボロ・ノースイーストブルックウッド

パークウェイ 2300

最終頁に続く

(54) 【発明の名称】抵抗分圧器を有するスイッチ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ソース端子、ゲート端子、ドレイン端子およびボディ端子を含む、金属酸化膜半導体電界効果トランジスタ(MOSFET)と、

第1抵抗および第2抵抗を有する抵抗分圧器であって、前記第2抵抗が前記ゲート端子および前記ボディ端子の間に接続され、前記第1抵抗がグランド源および前記ボディ端子の間に接続される抵抗分圧器と、を備え、

直流電源が前記ゲート端子に接続され、前記ゲート端子および前記抵抗分圧器に一定の直流電圧を供給するよう構成され、

前記ゲート端子の電圧および前記ボディ端子の電圧は、前記一定の直流電圧および前記グランド源のグランド電圧に依存する一方、前記ソース端子の電圧および前記ドレイン端子の電圧に非依存であり、

前記ソース端子および前記ドレイン端子の少なくとも一方は、無線周波数(RF)信号に接続される回路。

## 【請求項 2】

前記MOSFETは、n型MOSFETである請求項1に記載の回路。

## 【請求項 3】

前記MOSFETは、p型MOSFETである請求項1に記載の回路。

## 【請求項 4】

前記第1抵抗は、前記グランド源に接続される第1接続部と、前記ボディ端子に接続さ

れる第2接続部と、を備える請求項1から3のいずれか一項に記載の回路。

**【請求項5】**

前記第2抵抗は、前記ボディ端子に接続される第1接続部と、前記ゲート端子に接続される第2接続部と、を備える請求項1から4のいずれか一項に記載の回路。

**【請求項6】**

前記抵抗分圧器は、前記ゲート端子の電圧がグランド電圧と等しくないときに、前記ボディ端子の電圧を、前記ゲート端子の電圧と前記グランド電圧の間にバイアスするように構成される請求項1から5のいずれか一項に記載の回路。

**【請求項7】**

前記ボディ端子の電圧は、前記第1抵抗の抵抗値および前記第2抵抗の抵抗値に少なくとも部分的に基づく、既定の電圧である請求項6に記載の回路。 10

**【請求項8】**

前記ゲート端子の電圧は、前記グランド電圧に対して正である請求項6または7に記載の回路。

**【請求項9】**

前記ゲート端子の電圧は、前記グランド電圧に対して負である請求項6または7に記載の回路。

**【請求項10】**

前記MOSFETおよび前記抵抗分圧器を含むスイッチと、

前記スイッチを含む、無線周波数(RF)フロントエンド、RF送信器またはパワーコンバータと、をさらに備える請求項1から9のいずれか一項に記載の回路。 20

**【請求項11】**

一定の直流電圧を供給するように構成される直流電源と、

グランド電圧を供給するように構成されるグランド源と、

前記直流電源および前記グランド源に接続される一以上の単位セルと、を備え、

前記一以上の単位セルを構成する単位セルは、

ボディ端子と、前記直流電源に接続されるゲート端子と、ソース端子と、ドレイン端子とを有し、前記直流電源が前記ゲート端子に前記一定の直流電圧を供給するよう構成される金属酸化膜半導体電界効果トランジスタ(MOSFET)と、

コンデンサを含まない抵抗分圧器であって、前記グランド源および前記ボディ端子の間に接続される第1抵抗と、前記ゲート端子および前記ボディ端子の間に接続される第2抵抗とを備える抵抗分圧器と、を含み、 30

前記抵抗分圧器は、前記一定の直流電圧が前記グランド電圧に等しくないときに、前記ボディ端子の電圧および前記ゲート端子の電圧が前記一定の直流電圧および前記グランド電圧に依存する一方、前記ソース端子の電圧および前記ドレイン端子の電圧に非依存となるように、前記ボディ端子の電圧を前記直流電圧と前記グランド電圧の間にバイアスするように構成され、

前記ソース端子および前記ドレイン端子の少なくとも一方は、無線周波数(RF)信号に接続され、

前記MOSFETがオン状態の場合、前記ボディ端子の電圧が前記第1抵抗と前記第2抵抗の抵抗比に基づき、前記ソース端子と前記ドレイン端子の間での信号源からの信号伝達を増強する回路。 40

**【請求項12】**

前記MOSFETは、p型MOSFETである請求項11に記載の回路。

**【請求項13】**

前記MOSFETは、n型MOSFETである請求項11に記載の回路。

**【請求項14】**

前記第1抵抗は、前記グランド源に接続される第1接続部と、前記ボディ端子に接続される第2接続部と、を備える請求項11から13のいずれか一項に記載の回路。

**【請求項15】**

前記第2抵抗は、前記ボディ端子に接続される第1接続部と、前記ゲート端子に接続される第2接続部と、を備える請求項11から14のいずれか一項に記載の回路。

**【請求項16】**

前記直流電圧は、前記グランド電圧に対して正である請求項11から15のいずれか一項に記載の回路。

**【請求項17】**

前記直流電圧は、前記グランド電圧に対して負である請求項11から15のいずれか一項に記載の回路。

**【請求項18】**

ドレイン端子、ボディ端子、ソース端子およびゲート端子を備える金属酸化膜半導体電界効果トランジスタ(MOSFET)を、直流電源およびグランド源に接続し、10

第1抵抗を第2抵抗に直接接続して抵抗分圧器を形成し、

前記グランド源および前記ボディ端子の間に前記第1抵抗が位置し、前記ボディ端子および前記ゲート端子の間に前記第2抵抗が位置し、前記ボディ端子および前記ゲート端子の電圧が前記直流電源により供給される一定の直流電圧および前記グランド源のグランド電圧に依存する一方、前記ソース端子および前記ドレイン端子の電圧に非依存となるよう前記MOSFETの前記ボディ端子および前記ゲート端子を前記抵抗分圧器に接続し、

前記ソース端子および前記ドレイン端子の少なくとも一方を無線周波数(RF)信号に接続し、20

前記抵抗分圧器内の前記第1抵抗の抵抗値および前記第2抵抗の抵抗値は、前記ゲート端子が前記直流電源により供給される前記一定の直流電圧であるときに、前記ソース端子と前記ドレイン端子の間での信号源からの信号伝達を増強するために前記ボディ端子に必要とされる電圧に少なくとも部分的に基づき、

前記一定の直流電圧は、前記グランド源の前記グランド電圧と等しくない方法。

**【請求項19】**

前記MOSFETは、n型MOSFETである請求項18に記載の方法。

**【請求項20】**

前記MOSFETは、p型MOSFETである請求項18に記載の方法。

**【請求項21】**

さらに、前記第1抵抗の第1接続部を前記グランド源に接続し、前記第1抵抗の第2接続部を前記ボディ端子に接続する請求項18から20のいずれか一項に記載の方法。30

**【請求項22】**

さらに、前記第2抵抗の第1接続部を前記ゲート端子に接続し、前記第2抵抗の第2接続部を前記ボディ端子に接続する請求項18から21のいずれか一項に記載の方法。

**【請求項23】**

前記ボディ端子に必要とされる電圧は、前記直流電圧と前記グランド電圧の間である請求項18から22のいずれか一項に記載の方法。

**【請求項24】**

前記直流電圧は、前記グランド電圧に対して正である請求項18から23のいずれか一項に記載の方法。40

**【請求項25】**

前記直流電圧は、前記グランド電圧に対して負である請求項18から23のいずれか一項に記載の方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本開示の実施の形態は、一般に回路分野に関し、特に、電界効果トランジスタ(FET)を用いたスイッチ装置に関する。

**【背景技術】**

10

20

30

40

50

**【0002】**

無線周波数（RF）スイッチ装置は、多用途に用いられており、例えば、RF信号を選択的に通過させるための無線周波数システムに用いられる。FETを含むスイッチ装置において、FETをオン状態にバイアスするために、ゲート端子へのバイアス電圧の印加が必要とされうる。いくつかのケースにおいて、この印加電圧は、FETのボディを不定の電圧に浮遊（float）させることとなりうる。

**【図面の簡単な説明】****【0003】**

実施の形態は、例示を目的とし、添付の図面の記載に限定されないことを目的として例示される。添付の図面において同種の要素には同種の符号が付される。

10

**【0004】**

【図1】種々の実施の形態に係るスイッチ装置の構成を示す回路図である。

**【0005】**

【図2】n型FETの例を示す図である。

**【0006】**

【図3】種々の実施の形態に係るスイッチ装置のボディ電圧を制御する方法を示すフローチャートである。

**【0007】**

【図4】種々の実施の形態に係るスイッチ装置の構成を示す回路図である。

**【0008】**

【図5】種々の実施の形態に係る例示的な無線通信装置の構成を示すブロック図である。

20

**【発明を実施するための形態】****【0009】**

例示される実施の形態に係る様々な態様は、当業者にとって一般的に採用される用語を用いて他の当業者に本発明の本質を伝えるために示される。しかしながら、以下に示されるいくつかの要素のみを用いて代替的な実施の形態を実施しうることは、当業者にとって明らかであろう。説明のために、特定の装置または構成は、例示される実施の形態の詳細な理解を与えるために示される。しかし、当業者にとって、代替的な実施の形態を具体的な細部を省いて実施しうることは明らかであろう。他の例では、例示される実施の形態を不明確としないために、周知な特徴は除外され、もしくは単純化される。

30

**【0010】**

さらに、様々な動作は、複数の個別の動作として本開示の理解を最も助ける形で順に示される。しかしながら、記載の順序は、これらの動作が必ずしも順序依存であることを示すものであるとして解釈されるべきはない。特に、これらの動作は、説明される順序で実行される必要はない。

**【0011】**

「一つの実施の形態において」の語は、繰り返し用いられる。この語は、ほとんどの場合において、同じ実施の形態を参照するものではないが、同じ実施の形態を参照するかもしれない。「備える」、「有する」および「含む」の語は、文脈において別に規定されない限り、同義語である。

40

**【0012】**

種々の実施の形態の結合に用いうる用語に対し、文脈上の明確性を与えるため、「A / B」および「Aおよび/またはB」の語は、(A)、(B)または(AおよびB)を意味することとする。また、「A、Bおよび/またはC」の語は、(A)、(B)、(C)、(AおよびB)、(AおよびC)、(BおよびC)または(A、BおよびC)を意味する。

**【0013】**

「～と接続される」の語は、ここでは、派生的に用いられうる。「接続される」は、以下に示す一以上の意味で用いられうる。「接続される」は、二以上の要素が物理的または電気的に直接接触することを意味しうる。しかしながら、「接続される」は、二以上の要

50

素が互いに間接的に接触しつつ互いに協働または相互作用することも意味し、また、一つ以上の他の要素が、上述の意味で互いに接続された要素間において結合または接続されることを意味しうる。

#### 【0014】

実施の形態は、スイッチ装置またはFETを含むスイッチ回路を含んでもよい。FETは、ボディ、ソース、ドレインおよびゲートを備えててもよい。回路は、FETに接続される抵抗分圧器を含んでもよい。実施の形態において、抵抗分圧器は、電気的にFETのボディとグランドの間に位置し、FETに電気的に接続される第1抵抗を備えててもよい。抵抗分圧器は、電気的にFETのボディとゲートの間に位置し、FETに電気的に接続される第2抵抗をさらに備えててもよい。いくつかの実施の形態において、複数のFETおよび複数の抵抗分圧器は、スイッチ装置またはスイッチ回路に用いられてもよい。

10

#### 【0015】

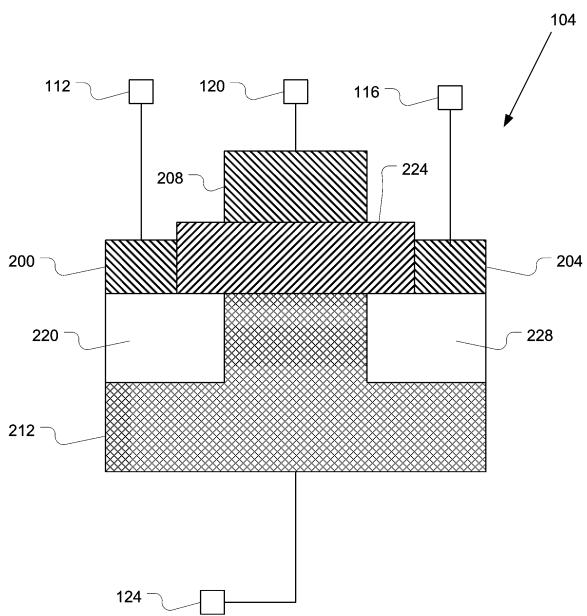

図1は、種々の実施の形態に係るスイッチ回路100を示す。スイッチ回路100（以下、回路100ともいう）は、電界効果トランジスタ（FET）を含んでもよい。FET104は、後述する図2に示されるFETのドレイン、ソース、ゲートおよびボディのそれぞれに接続される、ドレン端子112、ソース端子116、ゲート端子120およびボディ端子124を含んでもよい。いくつかの実施の形態において、ドレン端子112およびソース端子116は、図1に示されるように、電気的に互いに接続されてもよい。いくつかの実施の形態において、ドレン端子112およびソース端子116の間の電気的な接続には、抵抗128が含まれてもよい。いくつかの実施の形態において、FET104は、エンハンスマードのFETであってもよい。追加的または代替的に、FET104は、シリコン-オン-インシュレータ（SOI）および／またはパルク相補的金属酸化膜半導体（CMOS）装置であってもよい。いくつかの実施の形態において、FET104は、金属酸化膜半導体（MOSFET）であってもよいが、他の実施の形態において、FET104は、絶縁ゲートFET（IGFET）や金属絶縁体半導体（MISFET）としてもよい。

20

#### 【0016】

種々の実施の形態は、FET104のボディの電圧にバイアスをかけるために用いられるバイアス構造を提供する。このバイアス構造は、ここでは、n型のエンハンスマントモードFETに関して説明する。しかしながら、他の実施の形態において、このバイアス構造は、p型FETのような他の種類のFET向けの用途として、使用および／または変更(modify)されうる。

30

#### 【0017】

種々の実施の形態において、FET104は、後に無線周波数（RF）信号として示される伝送信号の切り替えを実現するため、「オフ」状態と「オン」状態の間で選択的に遷移しうる。例えば、FET104は、FET104が「オン」状態の場合、RF信号をソース端子116で受信し、FET104を通じてドレン端子112へRF信号を通過させてもよい。FET104は、FET104が「オフ」状態の場合、ドレン端子112とソース端子116の間のRF信号の通過を妨げてもよい。

40

#### 【0018】

FET104は、FET104を「オフ」状態と「オン」状態との間で遷移させるため、ゲート端子120において制御信号を受信してもよい。例えば、ドレン端子112およびソース端子116の電圧に対応する、+2.5Vの直流電圧がゲート端子120に印加されてもよい。いくつかの実施の形態において、この電圧は、デコーダ（図1に不図示）により印加されてもよい。この+2.5Vの電圧は、ドレン端子112とソース端子116の間の抵抗を極めて小さくし、その結果、RF信号がドレン端子112およびソース端子116の間を通過できるようにすることで、FET104を「オン」にする効果を有してもよい。

#### 【0019】

正の電圧をゲート端子120に印加することで、RF信号がFET104を通過できる

50

ようにしる。FET104は、図2にNMOS-FETとして示されるように、4つの要素を一般に備えててもためである。FET104は、ドレイン端子112に接続されるドレイン200と、ソース端子116に接続されるソース204と、ゲート端子120に接続されるゲート208により構成されてもよい。実施の形態において、ドレイン200、ソース204およびゲート208は、例えば、アルミニウムまたは銅などの金属または導電性材料で構成されてもよい。実施の形態において、ドレイン200、ソース204およびゲート208は、同じ材料または異なる材料で構成されてもよい。

#### 【0020】

FET104は、さらに、ボディ端子124に接続されるボディ212を備えてよい。

10 FET104は、詳細を後述するように、ドレイン200およびボディ212の間に位置するn型のドレイン部220と、ソース204およびボディ212の間に位置するn型のソース部228をさらに備えてもよい。

#### 【0021】

ここで、「端子」は、一般に、FET104を構成する要素であって、FET104が回路内の別の要素と接続する接続箇所として示される。いくつかの実施の形態において、ドレイン200およびドレイン端子112は、同じ要素であると考えてもよく、例えば、FET104は、ドレイン200と回路内の要素との直接接続を通じて、回路内の別の要素と接続してもよい。他の実施の形態においては、ドレイン端子112は、例えば、導電性のリード線など、電気的にドレイン200に接続される端子であってもよい。例えば、これらの他の実施の形態において、FET104は、ドレイン端子112を通じて回路内の別の要素と接続してもよく、このときのドレイン端子112は、ドレイン200に接続される、銅などの金属のリード線や他の導電性のリード線であってもよい。同様に、ソース204およびソース端子116は、ドレイン200およびドレイン端子112に関して上述したように、互いに同一であってもよいし、または、互いに電気的に接続されてもよい。同様に、ゲート208およびゲート端子120は、互いに同一であってもよいし、または、互いに電気的に接続されてもよい。最後に、ボディ212およびボディ端子124は、互いに同一であってもよいし、または、互いに接続されていてもよい。いくつかの実施の形態において、ボディ端子124は、ソース端子116に直接接続されてもよい。ここで、各要素に与えられる名称は、FET104の一つの要素を別の要素から識別するためのものであり、異なる実施の形態では異なる名称を用いるかもしれない。例えば、FET104において、n型のドレイン部220を「ドレイン」と呼び、n型のソース部228を「ソース」と呼ぶかもしれない。

20

30

#### 【0022】

FET104を用いる例として、直流電圧は、ゲート端子120に印加されるものとして説明され、同時に、ゲート端子120によりゲート208が特定の電圧を得ることとなりうるであろう。しかしながら、いくつかの実施の形態において、この直流電圧は、ゲート208に直接印加されてもよい。他の例として、RF信号は、FET104が「オン」のときに、ソース204またはソース端子116のいずれかにおいて受信され、FET104を通って、ドレイン200またはドレイン端子112へ通過してもよい。

#### 【0023】

ボディ212は、p型材料、例えば、シリコンやゲルマニウムなどのIV族元素に、ホウ素やアルミニウムなどのII族元素をドープしたもので構成されてもよい。n型のドレイン部220およびソース部228は、シリコンやゲルマニウムなどのIV族元素に、ヒ素やリンなどのV族元素をドープしたもので構成されてもよい。n型のドレイン部220およびソース部228は、ボディ212により互いに分離されてもよい。一般に、p型材料は、電子が欠乏し、「電子ホール」を有すると言われる。n型材料は、n型材料の内外にて電流として移動することのできる余分な電子を有し、その結果、「可動電子」を有するといわれる。

40

#### 【0024】

上述したように、FET104のゲート208は、銅やアルミニウムなどの導電性の金

50

属で構成されてもよい。他の実施の形態において、ゲート208は、タンタル、タングステン、窒化タンタルより構成されてもよい。他の実施の形態において、FET104のゲート208は、ポリシリコン材料で構成されてもよい。ドレイン200、ソース204、ゲート208およびボディ212は全て、誘電体224により互いに分離されてもよい。誘電体224は、例えば、二酸化シリコン、酸化窒化シリコン、または、ドレイン200とソース204の間の電子の流れを妨げる、その他の高誘電率(High-k)の誘電材料などである。

#### 【0025】

ゲート端子120に正電圧が印加されることによりゲート208が正の電圧を得るととき、ゲート208とFET104の他の部分との間に静電界が形成されてもよい。この正電圧は、ボディ212を構成するp型材料中の電子ホールを遠ざける一方で、ボディ212を構成するp型材料中の自由電子を引きつけうる。同時に、この正のゲート電圧は、n型のドレイン部220およびソース部228中の可動電子を引きつけうる。「閾値電圧」として知られる、ドレイン200およびソース204の直流電圧と比べてゲート208の正電圧が十分に高くなると、ボディ212を構成するp型材料における反発作用、および、ボディ212中の自由電子とn型のドレイン部220およびソース部228中の可動電子への誘引作用により、電子チャネルが形成されうる。この電子チャネルは、しばしば、「反転層」と呼ばれ、n型のドレイン部220およびソース部228の間であって誘電体224の直下に存在しうる。言い換えれば、n型のドレイン部220およびソース部228の間の電子チャネルは、ボディ212および誘電体214のちょうど間に存在しうる。いくつかの実施の形態において、ゲート端子120への印加電圧を増加させると、ゲート208の電圧が増加し、静電界の大きさが増大しうる。静電界が増大すると、電子チャネルの大きさが増え、その結果、ドレイン200およびソース204の間を通過できる電流量が増加しうる。

#### 【0026】

同様に、ゲート端子120にはデコーダにより-2.5Vの電圧が印加されうる。この-2.5Vの電圧は、ドレイン端子112とソース端子116の間の抵抗を極めて高くし、その結果、ドレイン端子112およびソース端子116の間を信号が通過できないようにならう。この抵抗は、ゲート端子120における負の電圧によりゲート208が負の電圧を得ることとなって、負の静電界が形成されるために高くなる。この負の静電界は、同時に、p型のボディ212中の電子ホールを引きつけるとともに、n型のドレイン部220およびソース部228中の可動電子を遠ざけて、ソース204およびドレイン200の間における電子の輸送可能性を無効とする。他の実施の形態においては、PMOS-FETがNMOS-FETの代わりに用いられてもよく、ボディ212はn型材料であってもよく、ドレイン部220およびソース部228は、p型材料であってもよい。

#### 【0027】

いくつかの実施の形態において、ボディ212の電圧は、ゲート208の電圧に追随(follow)する電圧、もしくは、ゲート208の電圧と同様の電圧であることが望ましいかもしれない。このような電圧が望まれうる理由は、例えば、ゲート208またはゲート端子120に正電圧が印加されるときにボディ212が正の電圧を得たとすると、ドレイン200およびソース204の間の電子チャネルが強化(enhanced)され、その結果、FET104の性能が高まるためである。同様に、ゲート208またはゲート端子120に負の電圧が印加されるときにボディ212が負の電圧を得たとすると、n型のドレイン部220およびソース部228における反発作用が高まり、FET104の抵抗が増大し、信号のいかなる漏れも減少しうる。

#### 【0028】

いくつかのケースにおいて、PMOS-FETのような能動素子がダイオードとして用いられており、ボディ端子124とゲート端子120の間においてFET104と接続されている。ゲート端子120における電圧が負になり、例えば、-2.5Vとなると、ダイオードは、ボディ212の電圧が負になるようにするかもしれないし、多くの実施の形

10

20

30

40

50

態において、ボディ 212 の電圧は、ゲート端子 120 における電圧に極めて近くなるかもしだい。例えば、ゲート端子 120 における電圧が -2.5V であるとすると、ボディ 212 の電圧は -2.3V であるかもしだい。この作用は、「ブートストラップ (bootstrapping)」と呼ばれる。いくつかの実施の形態において、ボディ 212 の電圧がゲート端子 120 の電圧の近くに維持されることが望ましいかもしだい。他の実施の形態においては、例えば、ゲート端子 120 に印加される電圧が +2.5V または -2.5V のときに、0.数V (1 / 10V の数倍) となる、小さな値だけボディ 212 の電圧が異なることが望ましいかもしだい。

#### 【0029】

しかしながら、ダイオードとして PMOS - FET を用いる場合、ゲート 208 の電圧が正になると、ボディ 212 の電圧は、勝手な値となるかもしだい。この場合において、ボディ 212 の電圧は「浮遊 (floating)」していると言われるかもしだい。このボディ 212 の浮遊電圧は、ボディ 212 における正確な電圧および電流がわからないと回路設計が難しくなるかもしだいため、問題となりうる。

10

#### 【0030】

具体的には、上述したように、ボディ 212 の電圧の増加または減少のそれぞれにより、ソース 204 およびドレイン 200 の間の RF 信号の伝送は、強化または縮小されるかもしだい。上述したように、ゲート 208 の電圧が正のときにボディ 212 の電圧が増加すると、n 型のドレイン部 220 およびソース部 228 の間のチャネルはより大きくなり、より大きな電流が FET 104 を通って流れることができるようになるかもしだい。

20

しかしながら、ボディ 212 の電圧が何であるかがわからず、FET 104 を通る RF 信号の電流の流れが何になりうるかを予測することが困難となるかもしだい。さらに、ボディ 212 の電圧が浮遊し制御されておらず、ボディ 212 の電圧が大きくなりすぎると、RF 信号の電流が非常に大きくなるかもしだい。この大電流は、FET 104 を発熱させるかもしだいし、この発熱により FET 104 に損傷を与えるかもしだい。また、FET 104 を用いる回路や、FET 104 を用いる装置にさえも損傷を与えるかもしだい。

20

#### 【0031】

いくつかの実施の形態において、抵抗分圧器 132 は、PMOS - FET の代わりに用いられる。抵抗分圧器 132 は、第 1 抵抗 136 および第 2 抵抗 140 を含んでもよい。第 1 抵抗 136 は、ボディ端子 124 とグランド 144 の間に位置してもよい。第 2 抵抗 140 は、ボディ端子 124 とゲート端子 120 の間に位置してもよい。

30

#### 【0032】

図 1 に示すように、抵抗分圧器 132 を用いることで、上述したダイオードの使用、例えば、能動的な PMOS - FET の使用に比べて、顕著な利益を提供しうる。具体的には、抵抗分圧器 132 は、デコーダによってゲート 208 に正の電圧または負の電圧が印加されるかに関わらず、既知の電圧となるゲート 208 の電圧に、ボディ 212 の電圧が追随できるようにしうる。言い換えれば、抵抗分圧器 132 は、ゲート 208 が正の電圧であれば、ボディ 212 の「浮遊」電圧を取り除いてもよく、代わりに、ボディ 212 の電圧を予測された値としてもよい。

40

#### 【0033】

さらに、PMOS - FET ダイオードは、PMOS - FET を「オン」または「オフ」とするために追加的な電力の入力を必要としうる。抵抗分圧器 132 を用いる回路は、PMOS - FET が存在しないため、受動的となり、その結果、追加的な電力の入力を必要としないかもしだい。この電力入力の減少は、回路設計を単純化し、FET 104 を用いる回路のコストを低減させるかもしだい。

#### 【0034】

第 1 抵抗 136 および第 2 抵抗 140 の抵抗値は、一以上の FET 104、ゲート端子 120 における電圧、ドレイン端子 112 における電圧、ソース端子 116 における電圧および / またはボディ 212 の電圧がゲート 208 の電圧にどの程度近接して追随するこ

50

とが望ましいかに関連して、具体的に選択されるかもしれない。例えば、ゲート208の電圧が+2.5Vのときにボディ212の電圧が+1.0Vとなることが望ましい場合、第1抵抗136および第2抵抗140の一方または双方の抵抗値は、ゲート208の電圧が+2.5Vのときにボディ212の電圧が+2.3Vとなることが望ましい場合と、異なるかもしれない。いくつかの実施の形態において、ゲート208が所定電圧にあるときのボディ212の電圧は、少なくとも、第2抵抗140に対する第1抵抗136の抵抗値の比率に部分的に基づくかもしれない。

#### 【0035】

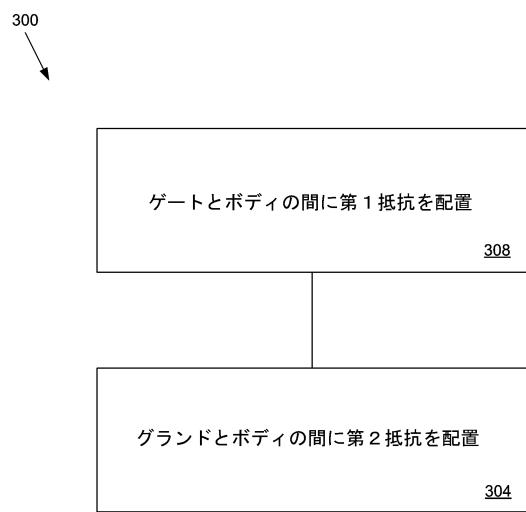

図3は、種々の実施の形態に係るゲート端子（例えば、ゲート端子120）に電圧を印加するときのFETのボディ（例えば、FET104のボディ212）をバイアスする方法300を示すフロー・チャートである。具体的には、ブロック308において、第1抵抗、例えば、第1抵抗136は、ボディ端子124とグランド144の間ににおいて、FETに接続されるかもしれない。次に、ブロック304において、第2抵抗、例えば、第2抵抗140は、ゲート端子120とボディ端子124の間ににおいて、FET104に電気的に接続されるかもしれない。

10

#### 【0036】

第1抵抗136および第2抵抗140の抵抗値を適切に選択することで、ボディ212の電圧はバイアスされ、その結果、ゲート208またはゲート端子120の電圧に追随するかもしれない。言い換えれば、ボディ212は、ゲート端子120に正の電圧が印加されたときに、既知の正の電圧を有するかもしれない。逆に、ボディ212は、ゲート端子120に負の電圧が印加されたときに、既知の負の電圧を有するかもしれない。いくつかの実施の形態において、ボディ212の電圧は、ゲート208に照らして、少なくとも第1抵抗136および第2抵抗140の抵抗値の比率に部分的に基づくかもしれない。

20

#### 【0037】

いくつかの実施の形態において、FET104および抵抗分圧器132は、単位セルと呼ばれるようにして組み合わされてもよい。いくつかの実施の形態において、この単位セルは、FET104のゲート端子120に接続されるデコーダをさらに含んでもよい。いくつかの実施の形態において、スイッチは、複数のFETおよび抵抗分圧器を含んでもよく、言い換えれば、複数の単位セルを含んでもよい。これらの実施の形態において、複数の単位セルは、互いに直列接続されてもよい。単位セルが直列接続されることが望ましい理由は、上述したように、FET104が「オフ」となったときに、ソース端子116とドレイン端子112の間に大きな抵抗が生成されるためである。RF信号の電流が非常に大きいと、FET104は損傷するかもしれない。複数のFETを直列接続することで、大きなRF信号により生成される負荷が分散され、その結果、それぞれのFETは、負荷の一部のみを担うこととなる。このようにして、FETの寿命は延長されるかもしれない。

30

#### 【0038】

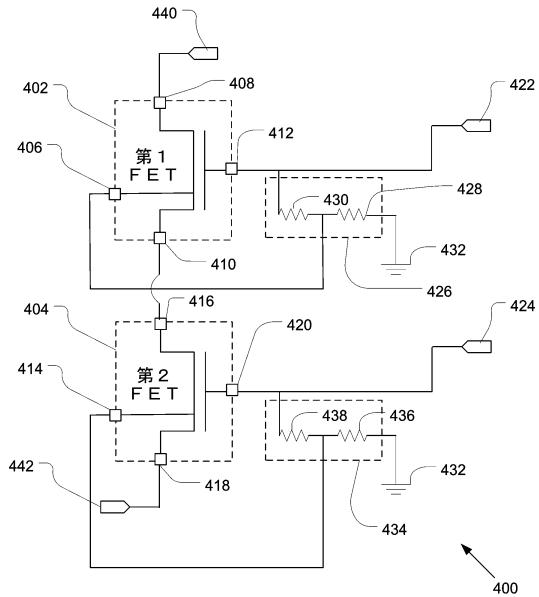

図4は、互いに直列接続される複数の単位セルを有するスイッチ回路400の例を示す。他の実施の形態は、追加の単位セルを有してもよい。いくつかの実施の形態において、スイッチ回路400は、信号バスが直列であっても分岐していてもよい。図4は、具体的に、二つのFETである第1FET402および第2FET404を有するスイッチ回路400の実施の形態を示す。第1FET402は、第1FET402のボディ、ドレイン、ソースおよびゲート（不図示）のそれぞれに接続される、ボディ端子406、ドレイン端子408、ソース端子410およびゲート端子412を含んでもよい。第2FET404は、同様に、第2FET404のボディ、ドレイン、ソースおよびゲート（不図示）のそれぞれに接続される、ボディ端子414、ドレイン端子416、ソース端子418およびゲート端子420を含んでもよい。第1FET402のゲート端子412は、ゲート端子412に直流電圧を供給するように構成される、第1直流電源422に電気的に接続されてもよい。また、第2FET404のゲート端子420は、ゲート端子420に直流電圧を供給するように構成される、第2直流電源424に電気的に接続されてもよい。いく

40

50

つかの実施の形態において、第1直流電源422および第2直流電源424は、同じ直流電源であってもよい。実施の形態において、第1直流電源422および第2直流電源424を「デコーダ」と呼んでもよい。

#### 【0039】

図1を参照して上述したように、第1FET402は、ボディ端子406およびグランド432の間に電気的に接続される第1抵抗428と、ボディ端子406およびゲート端子412の間に電気的に接続される第2抵抗430とを備える、抵抗分圧器426と接続されてもよい。同様に、第2FET404は、ボディ端子414およびグランド432の間に電気的に接続される第1抵抗436と、ボディ端子414およびゲート端子420の間に電気的に接続される第2抵抗438とを備える、抵抗分圧器434と接続されてもよい。10

#### 【0040】

スイッチ回路400に係るいくつかの実施の形態において、二つの単位セルは、互いに直列に接続されてもよい。これらの実施の形態において、第2FET404のドレイン端子416は、第1FET402のソース端子410に接続されてもよい。さらに、第1FET402のドレイン端子408は、RF入力端子440に接続されてもよく、第2FET404のソース端子418は、RF出力端子442に接続されてもよい。この実施の形態において、RF入力端子440は、スイッチ回路400を構成する第1FET402および第2FET404を「オン」にしたときに、スイッチ回路400を通過するRF信号のソースであってもよい。RF出力端子442は、このスイッチからRF信号が出て行く端子であってもよい。RF入力端子440、RF出力端子442および信号の流れは、後述する図5を参照しながら、より詳細に説明する。20

#### 【0041】

いくつかの実施の形態において、RF出力端子442はグランドに接続されてもよく、一方で、RF入力端子440は、電源に接続されてもよい。上述したように、これまで説明した構成は、n型もしくはNMOSのFETに関する。しかしながら、スイッチ回路400の構成に対して多少の変更を施したスイッチ回路400において、p型もしくはPMOSのFETもまた用いることができるかもしれない。他の実施の形態において、RF入力端子440およびRF出力端子442は、回路の他の要素と接続されてもよい。RF入力端子440およびRF出力端子442の接続は、スイッチ回路が用いられる用途に依存してもよい。30

#### 【0042】

いくつかの実施の形態において、第1FET402の第1抵抗428の抵抗値は、第2FET404の第1抵抗428の抵抗値と同じであってもよい。他の実施の形態において、二つの第1抵抗428、426の抵抗値は、異なっていてもよい。同様に、第2抵抗430、438の抵抗値は、スイッチ回路400またはFET402、404の種類、用途または使用に応じて、同じであってもよいし、異なってもいてもよい。

#### 【0043】

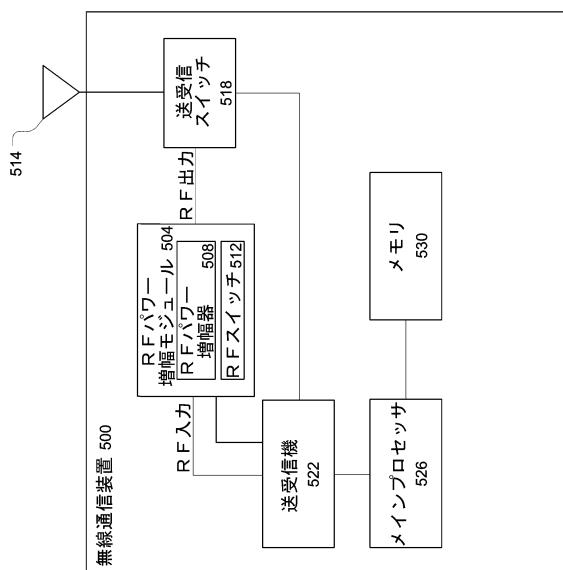

図5は、いくつかの実施の形態に係る例示的な無線通信装置500を示すブロック図である。無線通信装置500は、一以上のRF増幅器508を含む、RFパワー増幅(PA)モジュール504を有してもよい。RFパワー増幅モジュール504は、さらに、一以上のRF増幅器508に接続される、一以上のRFスイッチ512を含んでもよい。RFスイッチ512は、スイッチ回路100および/または400と同様であってもよいし、および/または、スイッチ回路100および/または400を含んでもよい。40

#### 【0044】

RFパワー増幅モジュール504に加えて、無線通信装置500は、少なくとも図示されるように互いに接続される、アンテナ構造514、送受信スイッチ518、送受信機522、メインプロセッサ526およびメモリ530を有してもよい。無線通信装置500は、送信および受信の機能を有するように図示される一方で、他の実施の形態において、送信機能のみ又は受信機能のみを有する装置を含んでもよい。RFスイッチ512は、R50

Fパワー増幅モジュール504に含まれるように図示される一方で、他の実施の形態においては、RFスイッチ512は、RFパワー増幅モジュール504に加えて又は代えて、送受信スイッチ518および／または送受信機522のような、無線通信装置500の他の構成要素に含まれていてもよい。他の実施の形態において、RFスイッチ512は、RFフロントエンド、RF送信器またはパワーコンバータの構成要素であってもよい。

#### 【0045】

種々の実施の形態において、無線通信装置500は、携帯電話、ページング装置、パソコンデジタルアシスタント、テキストメッセンジャー装置、ポータブルコンピュータ、デスクトップコンピュータ、基地局、加入者局、アクセスポイント、レーダー、衛星通信装置、その他無線によりRF信号を送受信可能なかなる装置であってもよいが、これらに限定されるものではない。10

#### 【0046】

メインプロセッサ526は、無線通信装置500の全体的な動作を制御するために、メモリ530に記憶される基本的なOS(operating system)プログラムを実行してもよい。例えば、メインプロセッサ526は、送受信機522による信号の受信および送信を制御してもよい。メインプロセッサ526は、メモリ530に常駐する他のプロセスやプログラムを実行する能力を有してもよく、実行するプロセスの要求に応じて、データをメモリ530に移動したり、メモリ530から取り出したりしてもよい。

#### 【0047】

送受信機522は、送信用データ(例えば、音声データ、ウェブデータ、Eメール、通信用データなど)をメインプロセッサ526から取得し、出力用データを意味するRF信号を生成し、RF入力信号をRFパワー増幅モジュール504に供給してもよい。送受信機522はまた、選択された帯域においてRFパワー増幅モジュール504がフルパワー モードもしくはバックオフパワー モードのいずれか一方で動作するように、RFパワー増幅モジュール504を制御してもよい。いくつかの実施の形態において、送受信機522は、OFDM変調を用いるRF入力信号を生成してもよい。20

#### 【0048】

RFパワー増幅モジュール504は、ここに記載するように、RF入力信号を増幅してRF出力信号を供給してもよい。RF出力信号は、送受信スイッチ518に転送され、その後、無線(OTA; over-the-air)伝送のためにアンテナ構造514に転送されてもよい。いくつかの実施の形態において、送受信スイッチ518は、デュプレクサを含んでもよい。同様に、送受信機522は、アンテナ構造514から入力される無線(OTA)信号を、送受信スイッチ518を通じて受信してもよい。送受信機522は、入力信号を処理し、さらなる処理のためにメインプロセッサ526へ送信してもよい。30

#### 【0049】

一以上のRFスイッチ512は、無線通信装置500の構成要素の間、および／または、これらの構成要素に対して、RF信号(例えば、RF入力信号および／またはRF出力信号)を選択的に通過するために用いてもよい。

#### 【0050】

種々の実施の形態のいて、アンテナ構造514は、例えば、ダイポールアンテナ、モノポールアンテナ、パッチアンテナ、ループアンテナ、マイクロストリップアンテナまたはRF信号の無線(OTA)送信／受信に適した、いかなる種類のアンテナを含む、一以上の指向性および／または無指向性アンテナを含んでもよい。40

#### 【0051】

当業者であれば、無線通信装置500が例示として示されており、簡潔性および明確性のため、無線通信装置500の大半の構成および動作が、実施の形態の理解のために必要とされる程度に示され、記載されていることが認識されるであろう。種々の実施の形態は、無線通信装置500に関連し、具体的なニーズに従う適切な目的を実行する、いかなる適切な要素または要素の結合を考慮する。さらに言えば、無線通信装置500は、具体的に実施されうる種類の装置に限定されるように解釈すべきではないことが理解されよう。50

## 【0052】

ここに、方法および装置が提供される。ある実施の形態において、回路は、ソース端子、ゲート端子、ドレイン端子およびボディ端子を含むMOSFETを備えてよい。回路は、第1抵抗および第2抵抗を有し、ゲート端子とボディ端子の間に接続される抵抗分圧器をさらに備えてよい。一実施の形態において、MOSFETは、n型MOSFETであってよい。一実施の形態において、MOSFETは、p型MOSFETであってよい。いくつかの実施の形態において、第1抵抗は、グランドと接続される第1接続部と、ボディ端子と接続される第2接続部とを備えてよい。いくつかの実施の形態において、第2抵抗は、ボディ端子と接続される第1接続部と、ゲート端子と接続される第2接続部とを備えてよい。いくつかの実施の形態において、抵抗分圧器は、ゲート端子の電圧がグランド電圧と等しくないとき、ボディ端子の電圧を、ゲート端子の電圧およびグランド電圧の間にバイアスするように構成されてもよい。他の実施の形態において、ボディ端子の電圧は、第1抵抗の抵抗値および第2抵抗の抵抗値に少なくとも部分的に基づく、既定の電圧であってよい。一実施の形態において、ゲート端子の電圧は、グランド電圧に対して正であってよい。一実施の形態において、ゲート端子の電圧は、グランド電圧に対して負であってよい。一実施の形態において、回路は、MOSFETおよび抵抗分圧器を含むスイッチおよび、このスイッチを含むRFフロントエンド、RF送受信機、またはパワーコンバータをさらに備えてよい。

## 【0053】

一実施の形態において、回路は、電源電圧を供給するように構成される電源と、グランド電圧を供給するように構成されるグランド源と、電源およびグランド源に接続される一以上の単位セルとを備えてよい。一以上の単位セルを構成する単位セルは、ボディ端子、ゲート端子、ソース端子およびドレイン端子を有するMOSFETと、第1抵抗および第2抵抗を備える抵抗分圧器を含み、抵抗分圧器は、ゲート端子の電圧がグランド端子と等しくないとき、ボディ端子の電圧を、ゲート端子の電圧およびグランド電圧の間にバイアスするように構成されてもよい。いくつかの実施の形態において、MOSFETは、p型MOSFETであってよい。いくつかの実施の形態において、MOSFETは、n型MOSFETであってよい。いくつかの実施の形態において、第1抵抗は、グランド源と接続される第1接続部と、ボディ端子と接続される第2接続部とを備えてよい。いくつかの実施の形態において、第2抵抗は、ボディ端子と接続される第1接続部と、ゲート端子と接続される第2接続部とを備えてよい。いくつかの実施の形態において、抵抗分圧器は、ゲート端子とボディ端子の間に接続されてもよい。いくつかの実施の形態において、ボディ端子の電圧は、抵抗分圧器の抵抗値に少なくとも部分的に基づく、既定の電圧であってよい。いくつかの実施の形態において、ゲート端子の電圧は、グランド電圧に対して正であってよい。いくつかの実施の形態において、ゲート端子の電圧は、グランド電圧に対して負であってよい。

## 【0054】

いくつかの実施の形態は、電源およびグランド源にMOSFETを接続する方法を提供してもよい。MOSFETは、ドレイン端子、ボディ端子、ソース端子およびゲート端子を備えてよい。この方法は、さらに、抵抗分圧器がボディ端子とゲート端子の間に位置するように、MOSFETのボディ端子およびゲート端子を抵抗分圧器に接続してもよい。第1抵抗の抵抗値および第2抵抗の抵抗値は、ゲート端子がグランド源におけるグランド電圧と等しくないゲート電圧であるときに、ボディ端子に必要とされる電圧に少なくとも部分的に基づいてもよい。いくつかの実施の形態において、MOSFETは、n型MOSFETまたはp型MOSFETであってよい。いくつかの実施の形態において、この方法は、さらに、第1抵抗の第1接続部をグランド源に接続し、第1抵抗の第2接続部をボディ端子に接続してもよい。いくつかの実施の形態において、この方法は、さらに、第2抵抗の第1端子をゲート端子に接続し、第2抵抗の第2端子をボディ端子に接続してもよい。いくつかの実施の形態において、ボディ端子に必要とされる電圧は、ゲート電圧とグランド電圧の間であってよい。いくつかの実施の形態において、ゲート電圧は、グラ

10

20

30

40

50

ンド電圧に対して正であってもよい。いくつかの実施の形態において、ゲート電圧は、グランド電圧に対して負であってもよい。

**【 0 0 5 5 】**

本開示は、上述の実施の形態の観点から示されたが、本開示の範囲を逸脱しない限りにおいて、同様の目的を実現すると考えられるさまざまな代替的および／または等価な実施の形態により、上述した特定の実施の形態が置換されてもよいことは、当業者によって理解されるであろう。当業者であれば、本開示によって示された内容が、様々な実施の形態として実施されてもよいことは、すぐに理解されるであろう。本記載は、制限的であるとみなされる代わりに、例示的であるとみなされることを意図する。

**【 図 1 】**

**【 図 2 】**

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 フリノ、ジュニア ジェイムズ ピー.

アメリカ合衆国オレゴン州97124・ヒルスボロ・ノースイーストブルックウッドパークウェイ

2300

審査官 及川 尚人

(56)参考文献 特開2006-041232(JP,A)

特開2004-296795(JP,A)

米国特許出願公開第2010/0156511(US,A1)

米国特許第5959488(US,A)

国際公開第2006/011364(WO,A1)

特開2009-065304(JP,A)

特開2010-028352(JP,A)

特開2004-007212(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K 17/00 - 17/70

H03K 19/094