(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2015년05월15일

(11) 등록번호 10-1520440

(24) 등록일자 2015년05월08일

(51) 국제특허분류(Int. Cl.)

H01L 21/02 (2006.01) G03F 7/00 (2006.01)

(21) 출원번호 10-2010-7002932

(22) 출원일자(국제) 2008년07월10일

심사청구일자 2013년04월19일

(85) 번역문제출일자 2010년02월09일

(65) 공개번호 10-2010-0057799

(43) 공개일자 2010년06월01일

(86) 국제출원번호 PCT/US2008/008470

(87) 국제공개번호 WO 2009/009095

국제공개일자 2009년01월15일

(30) 우선권주장

11/775,727 2007년07월10일 미국(US)

(56) 선행기술조사문헌

KR1020040036476 A\*

US06383952 B1\*

KR1020030095462 A\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

어드밴스드 마이크로 디바이시즈, 인코포레이티드

미국 캘리포니아 94088-3453 서니베일 피.오.박스

3453 원 에이엠디 플레이스

(72) 발명자

김령한

미국 캘리포니아 95138 산 호세 니구엘 레인 1055

동 윤페이

미국 캘리포니아 94089 서니베일 레이크버드 드라

이브 822

(뒷면에 계속)

(74) 대리인

박장원

전체 청구항 수 : 총 10 항

심사관 : 오순영

(54) 발명의 명칭 스페이서 리쏘그래피

**(57) 요약**

제1 마스크 패턴(10)을 형성하는 단계와, 상기 제1 마스크 패턴(10) 위에 교차 결합가능 층(20)을 형성하는 단계 와; 상기 제1 마스크 패턴(20)과 교차 결합가능 층(20) 사이에 교차 결합된 스페이서(30, 31)를 형성하는 단계 와; 상기 교차 결합가능 층(20), 상기 제1 마스크 패턴(10)의 상부 면으로부터의 교차 결합된 스페이서(30),

(뒷면에 계속)

**대 표 도 - 도4**

그리고 상기 제1 마스크 패턴(10)을 제거하여 상기 교차 결합된 스페이서(31)의 나머지 부분들을 포함하는 제2 마스크 패턴을 형성하는 단계와; 그리고 하부 타겟 층(11) 내에 초정밀 패턴을 형성하기 위해 상기 제2 마스크 패턴(31)을 사용하여 식각하는 단계를 포함하는 스페이서 리쏘그래피 기법을 사용하여, 타겟 층(11) 내에 초정밀 치수들이 정밀하고 효율적으로 형성된다. 실시예들은, 산을 생성할 수 있는 포토레지스트 물질로부터 제1 마스크 패턴(10)을 형성하는 단계와; 산이 존재할 때 교차 결합 반응을 일으킬 수 있는 물질을 포함하는 교차 결합가능 물질(20)을 증착하는 단계와; 그리고 상기 제1 마스크 패턴(10)의 나머지 부분들 및 남아있는 비교차 결합된 층(20)을 제거하기 전에, 상기 제1 마스크 패턴(10)의 상부 면으로부터 비교차 결합된 층(20) 및 교차 결합된 스페이서(30)의 부분들을 제거하는 단계를 포함한다.

(72) 발명자

**월로우 토마스 아이.**

미국 캘리포니아 94070 산 카를로스 헐 드라이브

1361

**라 폰타인 브루노**

미국 캘리포니아 94566 플리샌튼 트렌顿 서클 356

## 명세서

### 청구범위

#### 청구항 1

반도체 디바이스를 제조하는 방법으로서,

타겟 층(11) 위에 제1 마스크 패턴(10)을 형성하는 단계;

상기 제1 마스크 패턴(10) 위에 교차 결합 가능 층(20)을 형성하는 단계;

상기 제1 마스크 패턴(10)과 상기 교차 결합 가능 층(20) 사이에 교차 결합 된 스페이서(30,31)를 형성하는 단계;

상기 타겟 층(11)을 피복하고, 상기 교차 결합 가능 층(20)의 부분을 남긴 채 상기 제1 마스크 패턴(10)을 노출시키기 위해 상기 교차 결합 가능 층(20)의 일부 및 상기 교차 결합된 스페이서(30)의 일부를 제거하고, 그 후에 상기 교차 결합 가능 층(20)의 상기 타겟 층(11)을 피복하는 부분과 상기 제1 마스크 패턴(10)을 제거하여 상기 교차 결합된 스페이서(31)의 나머지 부분으로 이루어지는 제2 마스크 패턴을 형성하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스 제조 방법.

#### 청구항 2

제1 항에 있어서,

상기 교차 결합 가능 층(20)은 산이 존재할 때 교차 결합 반응을 일으킬 수 있는 물질을 포함하는 것을 특징으로 하는 반도체 디바이스 제조 방법.

#### 청구항 3

제2 항에 있어서,

상기 제1 마스크 패턴(10)은 산을 생성할 수 있는 물질을 포함하는 것을 특징으로 하는 반도체 디바이스 제조 방법.

#### 청구항 4

제3 항에 있어서,

상기 제1 마스크 패턴(10)과 상기 교차 결합 가능 층(20) 사이에 교차 결합 된 스페이서(30,31)를 형성하는 단계는 조사(irradiation) 또는 가열에 의해 상기 제1 마스크 패턴(10) 내에 산을 생성하는 단계와, 그리고 상기 교차-결합된 스페이서(30,31)를 형성하기 위하여 상기 산이 상기 교차 결합 가능 물질(20) 쪽으로 확산되도록 가열하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스 제조 방법.

#### 청구항 5

제1 항에 있어서,

상기 제1 마스크 패턴(10)이 충분히 노출되도록, 상기 교차 결합 가능 층(20)의 일부와 상기 교차 결합된 스페이서(30)를 제거하고, 그 후에 상기 교차 결합 가능 층(20)의 나머지 부분 및 상기 제1 마스크 패턴(10)을 제거함으로써 상기 제2 마스크 패턴을 형성하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스 제조 방법.

#### 청구항 6

반도체 디바이스를 제조하는 방법으로서,

타겟 층(11) 위에 제1 유기 물질로 이루어진 제1 마스크 패턴(10)을 형성하는 단계와;

산이 존재할 때 교차 결합 반응을 일으킬 수 있는 제2 유기 물질로 이루어진 층(20)을 형성하는 단계와;

상기 제1 마스크 패턴(10) 위에 교차 결합된 스페이서(30, 31)를 형성하기 위하여, 산을 생성하고 상기 제2 유

기 물질의 일부와 교차 결합되도록 상기 산을 상기 제2 유기 물질(20)에 확산시키는 단계와;

상기 타겟 층(11)을 피복하고, 상기 교차 결합 가능 층(20)의 부분을 남긴 채 상기 제1 마스크 패턴(10)을 노출시키기 위해 상기 제2 유기 물질(20)의 일부 및 상기 교차 결합된 스페이서(30)의 일부를 제거하는 식각을 행하고, 그 후에 상기 제2 유기 물질(20)의 상기 타겟 층(11)을 피복하는 부분과 상기 제1 마스크 패턴(10)을 제거하는 식각을 행하여, 상기 교차 결합된 스페이서(31)의 나머지 부분으로 이루어지는 제 2 마스크 패턴을 형성하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스 제조 방법.

### 청구항 7

제6 항에 있어서,

상기 제1 유기 물질(10)은 산을 생성할 수 있으며,

상기 제1 유기 물질(10)을 가열(heating) 또는 조사(irradiation)함으로써 상기 산을 생성하는 단계와;

상기 산이 확산되도록 가열하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스 제조 방법.

### 청구항 8

제7 항에 있어서,

상기 제1 유기 물질은 노보락 수지(novolac resin), 나프트카논디아지드계(naphthoquinonediazde-based) 감광제(photo sensitive agent) 및 콜로-메틸-트리아진 산 발생제(cholo-methyl-triazine acid generator), 또는 폴리하이드록시-스타이렌 유도체(polyhydroxy-styrene derivative) 및 오늄염(onium salt)을 포함하는 것을 특징으로 하는 반도체 디바이스 제조 방법.

### 청구항 9

제8 항에 있어서,

상기 제2 유기 물질(20)은 수용성 수지(water-soluble resins)인 것을 특징으로 하는 반도체 디바이스 제조 방법.

### 청구항 10

제6 항에 있어서,

상기 제1 마스크 패턴(10)을 산 용액(acid solution)으로 처리하여 산을 생성하는 단계를 포함하는 것을 특징으로 하는 반도체 디바이스 제조 방법.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 정밀하게 형성된 초정밀(ultrafine) 디자인 피쳐들을 가지는 반도체 디바이스들의 제조에 관한 것이다. 본 발명은 특히 제조 산출량이 증대된 효율적인 방식으로 아주 작은 서브-마이크론(deep sub-micron) 범위의 디자인 피쳐들을 가진 고속 집적 회로들을 가지는 반도체 디바이스들을 제조하는 것에 적용될 수 있다.

### 배경 기술

[0002] 반도체 디바이스 피쳐들의 치수는 종래의 제조 기술에 도전하는 매우 낮은 서브-마이크론 범위의 치수로 끊임없이 축소되고 있다. 임계 치수가 축소됨에 따라, 높은 제조 산출량과 함께 효과적인 방식으로 높은 치수 정밀성을 달성하는 것은 더욱 어려운 일이 되었다. 최소의 피쳐 사이즈는, 특정 리쏘그래피 시스템의 화학적 제약조건 및 광학적 제약조건 그리고 왜곡에 대한 공차(tolerance for distortion)에 의존한다. 종래의 리쏘그래피의 제약조건들에 부가하여, 초정밀 설계 피쳐들을 정밀하게 형성하는 것에 수반되는 제조 비용이 증가하며, 따라서 설비의 효율적인 사용과 높은 제조 산출량을 위한 제조에서의 진보가 요구된다.

[0003] 스페이서 리쏘그래피 공정들을 수반하는 이중 노출 기법들(double exposure techniques)이 발전되어왔다. 그러나, 이 기법들은 완전히 성공적이지는 않았으며 제조 산출량이 낮고, 일부 기법들은 다양한 툴 및 빈번한 화학 기계적 연마(CMP: chemical mechanical polishing)의 사용이 요구된다. 웨이퍼를 한 툴에서 또 다른 툴로 이동

시키는 것 및 CMP를 빈번하게 사용하는 것은 시간을 소비할 뿐만 아니라, 불가피하게 수율을 감소시키는 결과를 초래하여, 칩 생산자를 불리한 입장이 되게 한다. 오늘날의 경쟁적인 시장에서, 수익성을 위해서는 적어도 70%의 수율이 요구된다.

[0004] 따라서, 20nm 미만, 예를 들어 10nm 미만의 디자인 피쳐들을 포함하는 35nm 미만의 디자인 피쳐들과 같은 아주 작은 서브마이크론 범위로 정밀하게 형성되는 피쳐들을 갖는 디바이스들을 포함하는 반도체 칩의 제조를 가능하게 해주는 방법론이 필요하다. 특히, 높은 효율성 및 높은 제조 산출량을 가진 미세한 디자인 피쳐들의 정밀한 형성을 가능하게 해주는 방법론이 필요하다.

## 발명의 내용

### 발명의 효과

[0005] 본 발명의 이점은 아주 작은 서브마이크론 범위의 치수로 정밀하게 형성된 피쳐들을 갖는 반도체 디바이스들을 제조하는 방법을 제공하는 것이다.

[0006] 본 발명의 또 다른 이점은 높은 제조 산출량에서 정밀하게 형성된 서브마이크론 피쳐들을 갖는 반도체 디바이스들을 제조하는 효율적인 방법을 제공하는 것이다.

[0007] 본 발명의 또 다른 이점들 및 다른 피쳐들은 하기의 기술에서 설명될 것이며, 부분적으로 하기의 설명을 검토함으로서 당업자에게 명백해질 것이고, 본 발명을 실시함으로써 습득될 수 있을 것이다. 본 발명의 이점들은 첨부의 청구항들에서 구체적으로 지시된 대로 실시 및 획득될 수 있다.

[0008] 본 발명에 따르면, 상술된 이점들 및 다른 이점들이 반도체 디바이스를 제조하는 방법에 의해 부분적으로 달성되며, 상기 방법은, 타겟 층 위에 제1 마스크 패턴을 형성하는 단계와; 상기 제1 마스크 패턴 위에 교차 결합 가능한 층(cross-linkable layer)을 형성하는 단계와; 상기 제1 마스크 패턴과 상기 교차 결합 가능한 층 사이에 교차 결합된(cross-linked) 스페이서를 형성하는 단계와; 그리고 상기 교차 결합 가능한 층, 상기 제1 마스크 층을 노출시키기에 충분한 상기 교차 결합된 스페이서 부분들, 그리고 상기 제1 마스크 층을 제거하여 상기 교차 결합된 스페이서의 나머지 부분들을 포함하는 제2 마스크 패턴을 형성하는 단계를 포함한다.

[0009] 본 발명의 또 다른 이점은, 반도체 디바이스를 제조하는 방법을 제공하는 것이며, 상기 방법은 타겟 층 위에 제1 포토레지스트 마스크 패턴을 형성하는 단계와, 상기 제1 마스크 패턴은 상부면과 측면을 가지며 산을 생성할 수 있는 물질을 포함하고; 산이 존재할 때 교차 결합 반응을 일으킬 수 있는 물질을 포함하는 교차 결합 가능한 층을 상기 제1 포토레지스트 마스크 패턴 위에 형성하는 단계와; 가열 또는 조사(irradiation)에 의해 상기 제1 포토레지스트 마스크 패턴 내에 산을 생성하는 단계와; 상기 산이 상기 교차 결합 가능한 층으로 확산되어 상기 제1 포토레지스트 마스크 패턴의 상부면 및 측면에 교차 결합된 스페이서를 형성하게 하도록 가열하는 단계와; 상기 제1 포토레지스트 마스크 패턴의 상면 위의 상기 교차 결합된 스페이서를 노출시키기 위하여 상기 교차 결합 가능한 층의 부분들을 제거하고, 상기 제1 포토레지스트 마스크 패턴의 측면 위의 교차 결합 스페이서를 남겨둔채 상기 제1 포토레지스트 마스크 패턴의 상면으로부터 상기 노출된 교차 결합된 스페이서를 제거하는 단계와; 상기 교차 결합 가능한 층의 나머지 부분들을 제거하고 상기 포토레지스트 마스크 패턴을 제거하여, 상기 제1 포토레지스트 마스크 패턴의 측면 위에 이전에 형성된 상기 교차 결합된 스페이서를 포함하는 제2 마스크 패턴을 형성하는 단계; 그리고 상기 제2 마스크 패턴을 사용하여 상기 타겟 층을 식각하는 단계를 포함한다.

[0010] 본 발명의 또 다른 이점은 반도체 디바이스의 제조 방법을 제공하는 것이며, 상기 방법은, 타겟 층 위에 제1 마스크 패턴을 형성하는 단계와, 상기 제1 마스크 패턴은 제1 유기 물질을 포함하며; 산이 존재할 때 교차 결합 반응을 일으킬 수 있는 제2 유기 물질을 포함하는 층을 형성하는 단계와; 상기 제1 마스크 패턴 위에 교차 결합된 스페이서를 형성하기 위하여, 산을 형성하고 상기 제2 유기 물질로 확산시켜 상기 제2 유기 물질의 일부를 교차 결합시키는 단계와; 상기 제1 마스크 패턴을 노출시키기에 충분한 정도로 교차 결합된 스페이서 및 상기 제2 유기 물질의 일부를 제거하기 위하여 식각하는 단계와; 그리고 상기 제2 유기 물질의 나머지 부분들 및 제1 마스크 패턴을 제거하여 상기 교차 결합된 스페이서의 나머지 부분들을 포함하는 제2 마스크 패턴을 형성하기 위하여 식각하는 단계를 포함한다.

[0011] 본 발명의 실시예들은 35nm 미만의 두께에서 스페이서 층을 형성하는 단계와, 제2 유기 물질의 일부 및 교차 결합된 스페이서 층의 일부를 제1 마스크 패턴을 노출하기에 충분한 정도로 제거하기 위하여 적시의 식각 기법에 의해 식각하는 단계와, 후속하여, 상기 제2 유기 물질 및 제1 마스크 패턴의 나머지 부분들 모두를 제거하기 위하여 식각하는 단계를 포함한다. 본 발명의 실시예들은 노보락 수지(novolac resin), 나프트카논디아지드계

(napthoquinonediazde-based) 감광성 제제(photo sensitive agent) 및 콜로-메틸-트리아진 산 발생제(cholo-methyl-triazine acid generator)를 포함하는 포토레지스트 물질로부터 제1 마스크 패턴을 형성하는 단계, 또는 포토어시스트 산 발생제(photo-assisted acid generator)로서 기능하는 오늄염(onium salt) 및 폴리하이드록시-스타이렌 유도체(polyhydroxy-styrene derivative)로부터 제1 유기 물질을 형성하는 단계를 포함한다. 본 발명의 실시예들은 또한 교차 결합가능 층으로서 수용성 수지를 포함하는 유기 물질을 증착하는 단계를 포함한다.

[0012] 본 발명의 또 다른 이점들은 다음의 상세한 설명으로부터 당업자에게 쉽게 이해될 것인바, 다음의 상세한 설명에서는 본 발명의 실시예들이 본 발명을 실행하기 위한 가장 적합한 방식의 예에 의해 간단하게 설명된다. 이해될 바와 같이, 본 발명은 다른 그리고 상이한 실시예들을 적용할 수 있으며, 그것의 몇몇 세부사항들은 본 발명에서 벗어남 없이 다양하고 명백한 관점에서 수정될 수 있다. 따라서, 도면들 및 상세한 설명은 그 특성상 제한적인 것이 아닌 예시적인 것으로서 고려되어야 한다.

### 발명을 실시하기 위한 구체적인 내용

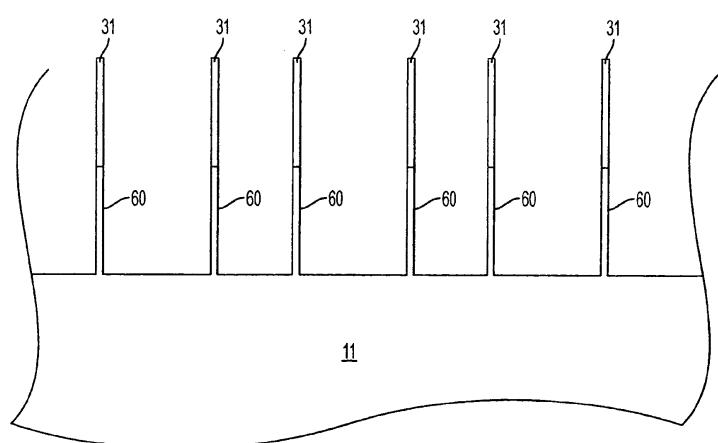

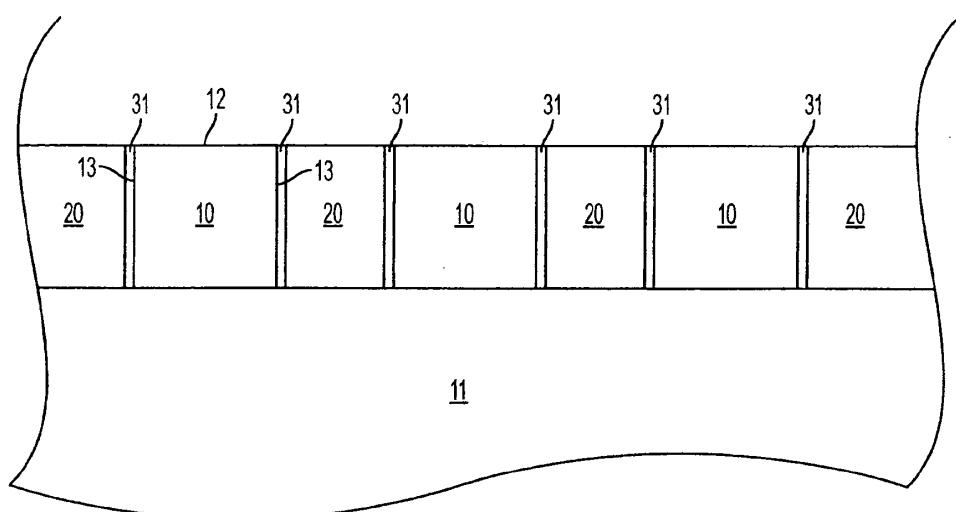

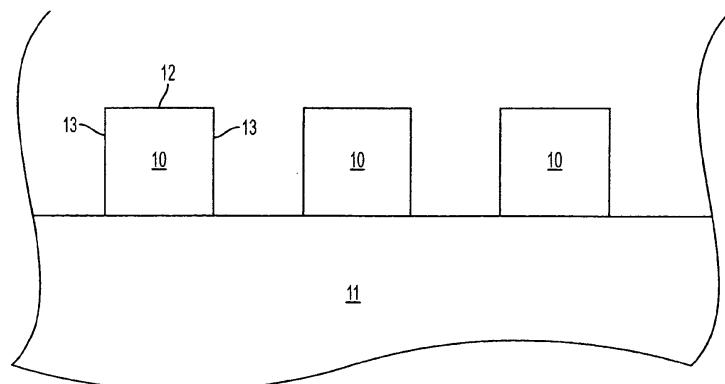

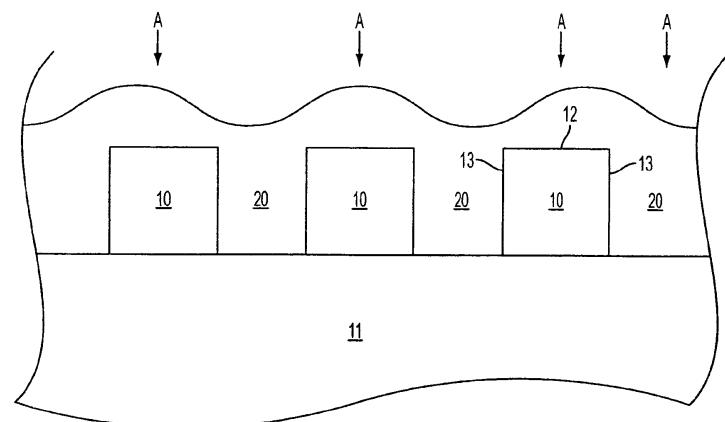

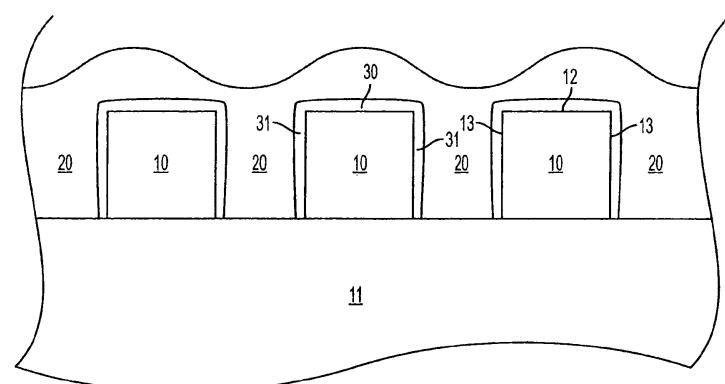

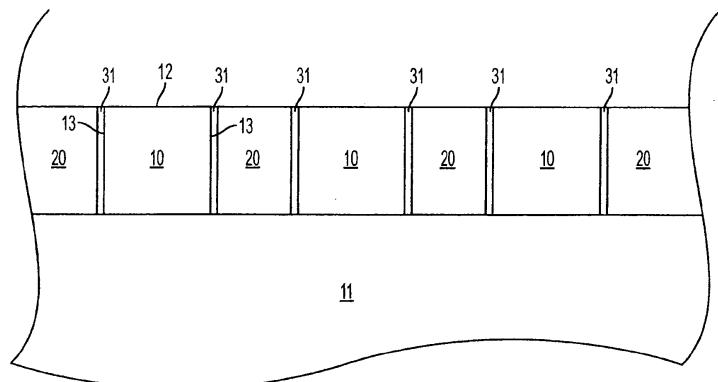

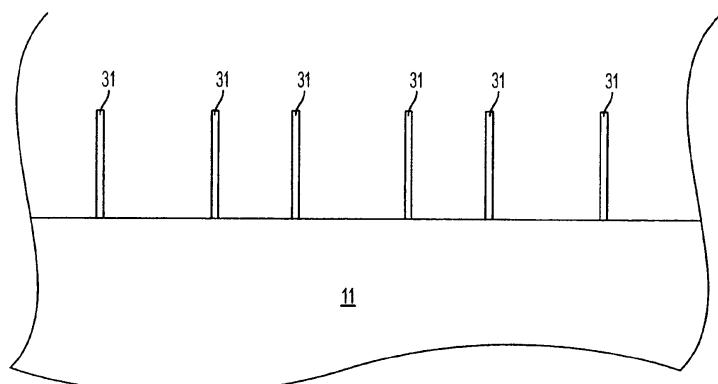

[0013] 도 1 내지 6은 본 발명의 실시예에 따른 방법의 순차적 단계들을 개략적으로 도시하는 단면도이다. 도 1 내지 6에서, 유사한 피쳐들은 유사한 도면부호로 표시된다.

[0014] 본 발명은 20nm 미만, 예를 들어 10nm 미만과 같은, 35nm 미만의 정밀하게 형성된 초정밀 디자인 피쳐들을 가진 반도체 디바이스들을 제조하는 것과 관련된 문제점을 해결하기 위한 것이다. 이 문제점들은 종래의 리쏘그래피 시스템의 화학적 및 광학적 제약조건에 의해 부과되는 치수적 제한, 간접 공정(intervening processing)의 다중 노출 단계들에서 기인된 정렬불량(misalignment), 그리고 피쳐 형상의 왜곡(distortion)으로부터 기인된다. 종래의 제조 기법들은 특히, 경쟁력을 유지하기 위한 높은 제조 산출량을 가능하게 해주는 효율적인 방식으로 정밀하게 형성된 초정밀 디자인 피쳐들에 대한 수요를 따라가기 위해 도전받고 있다. 다중 노출, 상이한 툴들 간의 웨이퍼의 이동, 그리고 특히, 화학 기계적 공정(CMP) 작업과 같은 작업들은 제조 산출량을 감소시키며, 따라서 수익성에 불리한 영향을 준다.

[0015] 종래의 리쏘그래피 실시는 특히 증가된 제조 산출량을 가진 효율적인 방식으로 정밀하게 형성된 아주 미세한 디바이스 피쳐들에 대한 끊임없는 수요를 만족시키지 못해왔다. 예를 들어, 종래의 실시는 종종 부수적인 정렬불량 문제들을 가진 다중 노출을 포함한 리쏘그래피 단계들 동안 몇개의 서로 다른 툴들을 사용하는 것을 수반하며, 종종 CMP 공정을 필요로 한다. 상이한 툴들 및 CMP의 사용, 특히 유전체 표면상에서 상이한 툴들 및 CMP를 사용하는 것은, 시간을 소비할 뿐만 아니라, 칩 불량 증가를 야기하고, 따라서 제조산출량 및 수익성을 저하시킨다.

[0016] 본 발명은 증가된 제조 산출량을 갖는 효율적인 방식으로 정밀하게 형성된 초정밀 디자인 피쳐들을 가진 다양한 타입의 반도체 디바이스들을 포함한 칩의 형성을 가능하게 해주는 방법론을 제공한다. 본 발명의 실시예들에 따라, 제1 마스크 패턴이 초정밀 패턴이 형성될 타겟 층 위에 형성된다. 제1 마스크 패턴 위에 교차 결합된 스페이서가 형성된다. 제2 마스크 패턴이 후속적으로 형성되며, 상기 제2 마스크 패턴은 상기 교차 결합된 스페이서의 부분들을 포함한다. 스페이서의 두께는 35nm 미만과 같은 정밀한 초정밀 자기정렬 피쳐들을 달성하도록 제어된다.

[0017] 본 발명의 실시예의 순차적인 단계들이 도 1 내지 6에 개략적으로 도시되며, 여기서 유사한 피쳐들은 유사한 참조 부호들로 표시된다. 도 1을 참조하면, 이격된 부분들(10)을 포함하는 제1 마스크 패턴이 타겟층(11) 위에 형성된다. 타겟 층(11)은 게이트 전극이 형성된 전도성층 또는 반도체층과 같은, 종래의 반도체 제조 기법 중에 형성된 식각될 임의의 다양한 층들일 수 있다. 제1 마스크 패턴은 일반적으로 포토레지스트 물질과 같은 유기물질(organic material)을 포함하며, 후속적으로 도포된 층에서, 교차 결합 반응과 같은 반응을 야기할 수 있는 요소를 포함할 수 있다. 본 발명의 일부 실시예들에 따르면, 제1 마스크 패턴(10)은 산을 생성할 수 있는 포토레지스트 물질을 포함한다. 적절한 물질들은 노보락 수지(novolac resin), 나프트카논디아지드계의 감광제, 그리고 산 발생제로서 기능하는 콜로-메틸-트리아진(cholo-methyl-triazine)의 혼합물을 포함한다. 본 발명의 몇몇 실시예들은 또한 포토 어시스트 산 발생제(photo-assisted acid generator)로서 기능하는 오늄 염(onium salt) 및 폴리-하이드록시-스타이렌 유도체(poly-hydroxy-styrene derivative)를 포함하는 혼합물로부터 제1 마스크 패턴을 형성하는 것을 포함한다. 제1 마스크층은 자외선(UV ray), 전자 빔, 또는 X-레이와 같은 특정 타입의 방사선에 노출될 때 혹은 가열될 때 산을 생성하는 메커니즘을 사용하는 화학 증폭형 레지스트(chemically amplified resist)로 형성될 수 있다.

[0018] 도 2를 참조하면, 층(20)이 증착되어 제1 마스크 패턴(10)을 덮는다. 본 발명의 일부 실시예들에서, 층(20)은

교차 결합 반응을 일으킬 수 있는 물질(예를 들어, 산이 존재할 때 교차 결합 반응을 일으킬 수 있는 물질)을 포함한다. 층(20)에 적합한 물질은 수용성(water-soluble) 및 비수용성(water-insoluble) 수지, 산이 존재할 때 교차 결합 반응을 일으키는 수용성 및 비수용성 수지, 수용성 및 비수용성 교차 결합제(cross linking agent), 그리고 그것들의 혼합물을 포함한다. 본 발명의 일부 실시예들에서, 수용성 수지은 폴리아크릴 산(polyacrylic acid), 폴리비닐 아세탈(polyvinyl acetal), 폴리비닐피로리돈(polyvinylpyrrolidone), 폴리비닐 알콜, 폴리에틸렌이민(polyethyleneimine), 스티렌-말레이 앤이드 코폴리머(styren-maleic anhydride copolymer), 폴리비닐아민(polyvinylamine), 폴리알릴아민(polyallylamine), 옥사졸린 군-함유 수용성 수지(oxazoline group-containing water-soluble resins), 수용성 우레탄, 수용성 폐놀, 수용성 에폭시, 수용성 멜라민 수지, 수용성 우레 수지(urea resins), 알카이드 수지(alkyd resins), 설포나마이드(sulfonamide), 이것들의 염(salt), 그리고 이것들 중 두개 이상의 혼합물을 포함하는 그룹으로부터 선택된다. 수용성 교차 결합제는 멜라민계 교차 결합 제(melamine-based cross-linking agents)(예를 들어, 멜라민 유도체(melamine derivatives) 또는 메틸-롤멜라민 유도체(methyl-lolmelamine derivatives)), 우레계(urea-based) 교차 결합제(예를 들어, 우레 유도체(urea derivatives), 메틸로이 우레 유도체(methyloy urea derivatives), 에틸렌 우레 카복시레이트(ethylene urea carboxylates), 또는 메틸올-에틸렌-우레 유도체(methylol-ethylene-urea derivatives)), 그리고 아미노계(amino-based) 교차 결합제(예를 들어, 벤조구아나민(benzoguanamine), 글리콜루릴(glycoluril), 이소시아네이트(isocyanate))로 구성된 그룹에서 선택된 한가지 타입의 물질 또는 두개 이상의 타입의 물질일 수 있다.

[0019] 본 발명의 실시예에서, 제2 층(20)은 폴리비닐 아세탈 수지으로 형성되며, 그것의 양은 폴리비닐 아세탈 수지의 아세탈화의 정도를 제어함으로써 제어된다. 본 발명의 다른 실시예들에서, 층(20)은 폴리비닐 아세탈과 메톡시-메틸올-우레의 혼합물, 폴리비닐 아세탈과 메톡시-메틸올-멜라민의 혼합물, 또는 메톡시-메틸올-멜라민과 폴리아릴-아민(polyallyl-amine)의 혼합물의 그룹에서 선택된 물질을 포함할 수 있다. 본 발명의 또 다른 실시예에서는 JSR Micro Inc.(Sunnyvale, CA.)에 의해 유통되는 JSR CSX0004와 같은 교차 결합제(cross-linker)를 사용하는 것이 특별히 적합한 것이 발견되었다. JSR CSX0004는 미량만이 물에 용해된다.

[0020] 일반적으로, 제2 층(20)은 제1 레지스트 폐턴(10)을 용해할 수 없는 용매(solvent)를 사용하여 증착된다. 층(20)을 증착하는데에 적합한 용매는 순수한 물(pre water) 또는 순수한 물과 알콜의 혼합물을 포함한다.

[0021] 일부 실시예들에 따르면, 층(20)과 반응하거나 교차 결합 반응을 야기할 수 있는 종(species)이 제1 마스크 패턴 위에 형성되거나 제1 마스크 패턴 내에 생성된다. 적절한 처리는 도 2에 화살표 A로 표시된것과 같이 노출된 전체 기판 위로 적합한 파장을 가진 빛을 조사하는 것을 포함한다. 본 발명의 또 다른 실시예에서, 제1 마스크 패턴의 선택된 부분들(10) 내에 산을 생성하기 위하여, 다른 부분들을 차폐함으로써 제1 마스크의 부분들이 선택적으로 조사될 수 있다. 본 발명의 다른 실시예들에서, 제1 마스크 패턴의 선택된 부분들(10)을 가열하여 산을 생성하기 위해 레이저 열 어닐링이 수행될 수 있다. 제1 마스크 패턴의 특정 부분들(10)만이 선택적으로 가열되거나 처리되는 경우, 교차 결합된 스페이서층은 상기 선택적으로 가열되거나 처리된 부분들 위에만 형성될 것이다.

[0022] 도 3을 참조하면, 층(20)의 부분들이 제1 마스크 패턴 위에 스페이서를 형성하는 반응을 일으키게 된다. 예를 들어, 약 60° 내지 약 130°의 온도로 가열함으로써 웨이퍼가 베이크될 수 있으며, 따라서 제1 마스크 패턴 내에 생성된 산이 제2 층(20)으로 확산되어 상기 제1 마스크 패턴 위에 교차 결합된 스페이서를 형성하는 교차 결합 반응을 일으키게 할 수 있다. 도 3에 도시된 바와 같이, 교차 결합된 스페이서는 제1 마스크 패턴(10)의 상부면(12)에 형성된 상부(30)와 제1 마스크 패턴(10)의 측면(13)에 형성된 측부(30)를 포함한다. 가열의 정도는 관련된 특정 물질 및 교차 결합된 스페이서의 요구 두께에 따라 가열 지속시간을 60초 내지 120초와 같이 제어함으로서 제어될 수 있다.

[0023] 후속적으로, 도 4에 개략적으로 도시된 것과 같이, 층(20)의 상부와 교차 결합된 스페이서의 상부(30)가 제거된다. 그러한 제거는 화학적 제거 또는 CMP에 의해 수행될 수 있다. 그러나, 본 발명의 실시예들에 따르면, CMP는 바람직하게는 생략될 수 있으며, 층(20)의 상부와 교차 결합된 스페이서의 상부(30)는 층(20)의 상부를 선택적으로 식각하고 뒤이어 교차 결합된 스페이서의 상부(30)를 제거하기 위해 선택적적으로 식각하는 것과 같은 식각에 의해 제거된다. 대안적으로, 적절한(timed) 식각 기법이, 도 4에 도시된 것과 같이 제1 마스크 패턴 부분들(10)의 상부면(12)을 노출하기 위해 층(20)의 상부 및 교차 결합된 스페이서의 상부(30)를 개별적으로 또는 동시에(in one step) 제거하는데에 사용될 수 있다. (비교차 결합된) 교차 결합가능 층(20)의 상부 및 교차 결합된 스페이서의 상부(30)를 제거하기 위한 적합한 식각제(etchants)는 O<sub>2</sub>, N<sub>2</sub>, 그리고 C<sub>x</sub>H<sub>y</sub>F<sub>z</sub>를 포함하는 가스

식각제 성분을 포함한다.

[0024] 도 5를 참조하면, (비교차 결합된) 교차 결합가능 층(20)의 나머지 부분이 제1 마스크 패턴의 부분들(10)과 함께 식각 등에 의해 제거되어, 전에 제1 마스크 패턴 부분들(10)의 측면(13)에 있었던 교차 결합된 부분들(31)을 포함하는 제2 마스크 패턴 또는 최종 마스크 패턴을 형성한다. 나머지 비교차 결합 층(20) 및 부분들(10)을 제거하기 위한 적합한 식각제는  $O_2$ ,  $N_2$ , 그리고  $C_xH_yF_z$ 를 포함하는 가스 식각제 성분을 포함한다. 후속적으로, 타겟 층(11) 내에 게이트 전극과 같은 피쳐들(60)을 형성하기 위하여, 제2 마스크 패턴을 사용하여 식각이 수행된다. 피쳐들(60)은 교차 결합된 스페이서 부분들(31)과 자기 정렬되며, 스페이서층(31)의 두께와 유사한 너비를 가진다.

[0025] 본 발명은 다양한 타입의 물질 및 기법을 사용하여 실시될 수 있다. 예를 들어, 미국 특허 6,319,853 및 미국 특허 5,858,620에 개시된 방법 및 물질들을 사용함으로써 산이 생성될 수 있으며, 상기 미국 특허는 그 전체가 본 명세서에 참조로서 포함된다. 예를 들어, 제1 마스크 패턴을 형성한 후와 층(20)을 증착한 후 사전베이킹 (prebaking)이 수행될 수 있다. 산은 조사(irradiation) 이외의 다른 방법, 즉 층(20)을 증착하기 전에 제1 마스크 패턴을 산성 용액으로 처리하고, 뒤이어, 산이 확산되어 층(20)의 부분을 교차결합할 수 있도록 가열하는 것과 같은 방법에 의해 형성될 수 있다.

[0026] 본 발명의 실시예들은 바람직하게는 제1 마스크 패턴과 층(20)에 대해 유기 물질을 사용함으로써, 상이한 툴들 간의 이동을 최소화해준다. 또한, 본 발명의 실시예들에서, 절연층의 CMP 문제는, 시기 적절한(timed) 식각 기법을 사용하는 것에 의해서와 같이 식각에 의해 방지될 수 있다. 본 발명의 실시예들은 제1 마스크 패턴을 형성하는 것에 있어서 단일 노출 단계를 사용하여 실시될 수 있으며, 그럼으로써 간접 공정에서의 다중 노출에 수반되는 불량정렬 문제들을 방지할 수 있다.

[0027] 본 발명은 EPROM(소거가능하고 프로그램가능한 판독전용 메모리), EEPROM(전기적으로 소거가능하고 프로그램가능한 판독전용 메모리), EEPROM(플래시 소거가능하며 프로그램가능한 판독전용 메모리)와 같은 반도체 메모리 디바이스들을 포함하는 다양한 타입의 임의의 반도체 디바이스들을 포함하는 반도체 칩의 제조에서 사용될 수 있다. 본 발명의 실시예들에 따라 제조된 반도체 칩은 컴퓨터, 셀룰러 전화기, 디지털 카메라와 같은 다양한 상용 전자 디바이스들에서 사용될 수 있으며, 종래 방식의 인쇄 회로 보드와 쉽게 통합될 수 있다.

[0028] 본 발명은 높은 제조 산출량으로 정밀한 초정밀 디자인 피쳐들을 가진 디바이스들 포함하는 반도체 칩의 효율적인 제조를 가능하게 해준다. 본 발명은, 증가된 회로 속도를 보여주는 플래시 메모리 반도체 디바이스를 포함하는 고도로 집적된 반도체 디바이스를 갖는 칩을 포함하여, 임의의 다양한 타입의 산업적 응용에 유용한 반도체 칩들을 제조하는 산업적 적용성을 가진다.

[0029] 상기에서, 본 발명은 본 발명을 구체적으로 설명하는 실시예들을 참조로 기술되었다. 그러나, 청구항들에서 설명되는 바와 같은 본 발명의 광의의 정신 및 범주에서 벗어남 없이 본 발명에 대한 다양한 수정 및 변경이 이루어질 수 있음을 자명한 것이다. 따라서, 상세한 설명 및 도면은 예시적인 것으로 이해되어야 하며 제한적인 것으로 이해되어서는 안된다. 본 발명은 다양한 조합 및 실시예들을 사용할 수 있으며, 본 명세서에서 설명된 것과 같은 본 발명의 개념의 범주 내에서 임의의 수정 및 변형이 이루어질 수 있다.

도면

도면1

도면2

도면3

도면4

도면5

도면6