(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7023791号**

**(P7023791)**

(45)発行日 令和4年2月22日(2022.2.22)

(24)登録日 令和4年2月14日(2022.2.14)

(51)国際特許分類

|         |                 |     |         |       |         |

|---------|-----------------|-----|---------|-------|---------|

| G 0 6 F | 12/00 (2006.01) | F I | G 0 6 F | 12/00 | 5 5 0 K |

| G 1 1 C | 7/10 (2006.01)  |     | G 0 6 F | 12/00 | 5 6 4 D |

|         |                 |     | G 1 1 C | 7/10  | 4 0 0   |

|         |                 |     | G 1 1 C | 7/10  | 5 0 0   |

請求項の数 20 (全30頁)

|                   |                                  |          |                                                                                                                                                                             |

|-------------------|----------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21)出願番号          | 特願2018-102557(P2018-102557)      | (73)特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路12<br>9<br>129, Samsung-ro, Yeo<br>ngtong-gu, Suwon-si<br>, Gyeonggi-do, Repub<br>lic of Korea |

| (22)出願日           | 平成30年5月29日(2018.5.29)            | (74)代理人  | 110000051<br>特許業務法人共生国際特許事務所                                                                                                                                                |

| (65)公開番号          | 特開2018-200739(P2018-200739<br>A) | (72)発明者  | 孫 永 訓<br>大韓民国 京畿道 水原市 灵通区 179<br>ボンギル ワールドカップ路 34 1F<br>最終頁に続く                                                                                                              |

| (43)公開日           | 平成30年12月20日(2018.12.20)          |          |                                                                                                                                                                             |

| 審査請求日             | 令和3年5月18日(2021.5.18)             |          |                                                                                                                                                                             |

| (31)優先権主張番号       | 10-2017-0066377                  |          |                                                                                                                                                                             |

| (32)優先日           | 平成29年5月29日(2017.5.29)            |          |                                                                                                                                                                             |

| (33)優先権主張国・地域又は機関 | 韓国(KR)                           |          |                                                                                                                                                                             |

| (31)優先権主張番号       | 10-2017-0089692                  |          |                                                                                                                                                                             |

| (32)優先日           | 平成29年7月14日(2017.7.14)            |          |                                                                                                                                                                             |

| (33)優先権主張国・地域又は機関 | 韓国(KR)                           |          |                                                                                                                                                                             |

| 早期審査対象出願          |                                  |          |                                                                                                                                                                             |

(54)【発明の名称】 オン - ダイターミネーションの制御方法及びこれを遂行するシステム

**(57)【特許請求の範囲】****【請求項 1】**

第1メモリランク及び第2メモリランクを含み、前記第1メモリランクは第1ランク選択信号によって活性化され、前記第2メモリランクは第2ランク選択信号によって活性化されるマルチ - ランクシステムの動的ランダムアクセスメモリ (DRAM) を動作させる方法であって、

第1オン - ダイターミネーション (ODT) 動作モードと第2オン - ダイターミネーション (ODT) 動作モードのうちの1つを活性化するようにモードレジスタ設定 (MRES T) を設定するステップと、

前記第1ランク選択信号が活性化され、前記第2ランク選択信号が不活性化されている間中、前記第1及び第2メモリランクで共有されるコマンドバスを介して、外部装置から動作クロック信号対に同期して第1CASコマンドと書き込みコマンドを連続して受信するステップと、

前記第1CASコマンドと前記書き込みコマンドを受信した後、前記第1及び第2メモリランクで共有されるデータバスを介して、外部装置から書き込みデータを受信するステップであって、前記第1ODT動作モードが活性化された場合、前記書き込みデータの受信中に前記第1メモリランクの第1ODT回路及び前記第2メモリランクの第2ODT回路がそれぞれ第1活性化状態として活性化され、前記第2ODT動作モードが活性化された場合、前記書き込みデータの受信中に前記第1メモリランクの前記第1ODT回路が第2活性化状態として活性化され、前記第2メモリランクの前記第2ODT回路が第1活性化状態とし

て活性化されるステップと、

前記書込みデータの受信中に、前記動作クロック信号対に同期してトグルするデータストローブ信号対を受信するステップであって、前記データストローブ信号対のトグル周波数は前記動作クロック信号対の周波数よりも高いステップと、

前記第1ランク選択信号が活性化され、前記第2ランク選択信号が不活性化されている間中、前記コマンドバスを介して、第2CASコマンドと読み出しコマンドを連続して受信するステップと、

前記第2CASコマンド及び前記読み出しコマンドに応答して、前記データバスを介して読み出しデータを出力するステップであって、前記第1ODT動作モードが活性化された場合又は前記第2ODT動作モードが活性化された場合、前記読み出しデータを出力している間中、前記第1メモリランクの前記第1ODT回路は不活性され、前記第2メモリランクの前記第2ODT回路は第1活性化状態として活性化されるステップと、

を含むことを特徴とする、マルチ-ランクシステムの動的ランダムアクセスメモリを動作させる方法。

#### 【請求項2】

前記データストローブ信号対の前記トグル周波数は、前記動作クロック信号対の周波数の2倍であることを特徴とする、請求項1に記載のマルチ-ランクシステムの動的ランダムアクセスメモリを動作させる方法。

#### 【請求項3】

前記データストローブ信号対の前記トグル周波数は、前記動作クロック信号対の周波数の4倍であることを特徴とする、請求項1に記載のマルチ-ランクシステムの動的ランダムアクセスメモリを動作させる方法。

#### 【請求項4】

前記第1CASコマンドは、前記書込みコマンドが直後に続くことを示す第1フィールドを含み、前記第1フィールドの論理レベルはハイ(High)であることを特徴とする、請求項1に記載のマルチ-ランクシステムの動的ランダムアクセスメモリを動作させる方法。

#### 【請求項5】

前記第2CASコマンドは、前記読み出しコマンドが直後に続くことを示す第2フィールドを含み、前記第2フィールドの論理レベルはハイであることを特徴とする、請求項1に記載のマルチ-ランクシステムの動的ランダムアクセスメモリを動作させる方法。

#### 【請求項6】

前記第1ODT回路の第1抵抗値を設定し、前記第2ODT回路の第2抵抗値を設定するために第2モードレジスタを設定するステップをさらに含むことを特徴とする、請求項1に記載のマルチ-ランクシステムの動的ランダムアクセスメモリを動作させる方法。

#### 【請求項7】

前記第1メモリランクはターゲットメモリランクであり、前記第2メモリランクはノン-ターゲットメモリランクであり、前記ターゲットメモリランクのDRAMは、前記書込みコマンドと前記読み出しコマンドに応答して書き込み動作と読み出し動作を実行することを特徴とする、請求項1に記載のマルチ-ランクシステムの動的ランダムアクセスメモリを動作させる方法。

#### 【請求項8】

前記DRAMのパワーオン時、前記モードレジスタ設定のデフォルト設定は前記第1ODT動作モードであることを特徴とする、請求項1に記載のマルチ-ランクシステムの動的ランダムアクセスメモリを動作させる方法。

#### 【請求項9】

第1ODT動作モードから第2ODT動作モードへのODT動作モード変更は、手順をプログラミングするモードレジスタ設定によって行われることを特徴とする、請求項8に記載のマルチ-ランクシステムの動的ランダムアクセスメモリを動作させる方法。

#### 【請求項10】

10

20

30

40

50

前記第 1 O D T 回路の O D T 抵抗は、前記第 1 O D T 動作モード中は第 1 値を、前記第 2 O D T 動作モード中は第 2 値を有するようにそれぞれ設定され、前記第 1 値は前記第 2 値とは異なることを特徴とする、請求項 1 に記載のマルチ - ランクシステムの動的ランダムアクセスメモリを動作させる方法。

【請求項 1 1】

前記第 1 値及び前記第 2 値は、第 2 モードレジスタ設定に格納された複数の異なる抵抗値から選択されることを特徴とする、請求項 1 0 に記載のマルチ - ランクシステムの動的ランダムアクセスメモリを動作させる方法。

【請求項 1 2】

マルチ - ランクシステムであって、

10

前記マルチ - ランクシステムは、

第 1 オン - ダイターミネーション ( O D T ) 動作モードと第 2 オン - ダイターミネーション ( O D T ) 動作モードのうちの 1 つを活性化にするように構成されたモードレジスタ設定 ( M R S E T ) と、

第 1 ランク選択信号によって活性化される第 1 動的ランダムアクセスメモリ ( D R A M ) を含む第 1 メモリランクと、

第 2 ランク選択信号によって活性化される第 2 動的ランダムアクセスメモリ ( D R A M ) を含む第 2 メモリランクと、

前記第 1 メモリランク及び前記第 2 メモリランクに動作クロック信号対を提供する動作クロックバスと、

20

前記第 1 メモリランク及び前記第 2 メモリランクで共有され、外部装置に接続されたコマンドバスと、

前記第 1 メモリランク及び前記第 2 メモリランクで共有され、前記外部装置に接続されたデータバスと、

前記第 1 メモリランク及び前記第 2 メモリランクで共有され、前記外部装置に接続されたデータストローブバスと、を含み、

前記第 1 D R A M は、

前記第 1 ランク選択信号が活性化され、前記第 2 ランク選択信号が不活性化されている間中、前記コマンドバスを介して前記動作クロック信号対に同期して第 1 C A S コマンドと書込みコマンドを連続して受信し、

30

前記第 1 C A S コマンドと前記書込みコマンドを受信した後、前記データバスを介して書込みデータを受信し、前記第 1 O D T 動作モードが活性化された場合、前記書込みデータを受信中に前記第 1 メモリランクの第 1 O D T 回路及び前記第 2 メモリランクの第 2 O D T 回路がそれぞれ第 1 活性化状態として活性化され、前記第 2 O D T 動作モードが活性化された場合、前記書込みデータの受信中に前記第 1 メモリランクの前記第 1 O D T 回路が第 2 活性化状態として活性化され、前記第 2 メモリランクの前記第 2 O D T 回路が第 1 活性化状態として活性化され、

前記書込みデータの受信中に、前記動作クロック信号対に同期してトグルするデータストローブ信号対を受信し、前記データストローブ信号対のトグル周波数は前記動作クロック信号対の周波数よりも高く、

40

前記第 1 ランク選択信号が活性化され、前記第 2 ランク選択信号が不活性化されている間中、前記コマンドバスを介して第 2 C A S コマンドと読み出しコマンドを連続して受信し、前記第 2 C A S コマンドと前記読み出しコマンドに応答して、前記データバスを介して読み出しデータを出力し、前記第 1 O D T 動作モードが活性化された場合又は前記第 2 O D T 動作モードが活性化された場合、前記読み出しデータを出力している間中、前記第 1 メモリランクの前記第 1 O D T 回路を不活性化し、前記第 2 メモリランクの前記第 2 O D T 回路を第 1 活性化状態として活性化することを特徴とするマルチ - ランクシステム。

【請求項 1 3】

前記データストローブ信号対の前記トグル周波数は、前記動作クロック信号対の周波数の 2 倍であることを特徴とする、請求項 1 2 に記載のマルチ - ランクシステム。

50

**【請求項 14】**

前記第1C A Sコマンドは、前記書込みコマンドが直後に続くことを示す第1フィールドを含み、前記第1フィールドの論理レベルはハイ(H i g h)であることを特徴とする、請求項12に記載のマルチ-ランクシステム。

**【請求項 15】**

前記第2C A Sコマンドは、前記読み出しコマンドが直後に続くことを示す第2フィールドを含み、前記第2フィールドの論理レベルはハイであることを特徴とする、請求項12に記載のマルチ-ランクシステム。

**【請求項 16】**

前記第1O D T回路の第1抵抗値を設定し、前記第2O D T回路の第2抵抗値を設定するために第2モードレジスタを設定することを特徴とする、請求項12に記載のマルチ-ランクシステム。

10

**【請求項 17】**

前記第1メモリランクはターゲットメモリランクであり、前記第2メモリランクはノン-ターゲットメモリランクであり、前記ターゲットメモリランクのD R A Mは、前記書込みコマンド及び前記読み出しコマンドに応答して、書き込み及び読み出し動作を行うことを特徴とする、請求項12に記載のマルチ-ランクシステム。

**【請求項 18】**

前記D R A Mのパワーオン時、モードレジスタ設定のデフォルト設定は前記第1O D T動作モードであることを特徴とする、請求項12に記載のマルチ-ランクシステム。

20

**【請求項 19】**

第1O D T動作モードから第2O D T動作モードへのO D T動作モード変更は、手順をプログラミングするモードレジスタ設定によって行われることを特徴とする、請求項18に記載のマルチ-ランクシステム。

**【請求項 20】**

前記第1O D T回路のO D T抵抗は、前記第1O D T動作モード中は第1値、前記第2O D T動作モード中には第2値を有するようにそれぞれ設定され、前記第1値は前記第2値とは異なることを特徴とする、請求項12に記載のマルチ-ランクシステム。

**【発明の詳細な説明】****【技術分野】**

30

**【0 0 0 1】**

本発明は半導体集積回路に関し、より詳しくは、オン-ダイターミネーションの制御方法、これを遂行する装置及びシステムに関する。

**【背景技術】****【0 0 0 2】**

オン-ダイターミネーション(on-die\_termination: O D T)は、送信装置と受信装置との間のインターフェースにおける信号反射(signal\_reflection)を最小化することによって、信号品位(signal\_integrity)を向上するために導入された。O D T回路は、転送線のインピーダンスとマッチングされたターミネーション抵抗(termination\_resistor)を提供することによって、信号反射を抑制できる。しかし、信号品位の向上のためにO D Tを具現する場合、消耗電力が増加する。

40

**【発明の概要】****【発明が解決しようとする課題】****【0 0 0 3】**

前記の問題点を解決するためになされた本発明の一目的は、消耗電力を減少し、信号品位を向上するできるオン-ダイターミネーションの制御方法を提供することにある。

**【0 0 0 4】**

また本発明の一目的は、消耗電力を減少し、信号品位を向上するできるオン-ダイターミネーションの制御方法を遂行するシステムを提供することにある。

50

**【課題を解決するための手段】**

**【0005】**

前記の一目的を達成するために、本発明の実施形態に従う複数のメモリランクを含むマルチ - ランクシステムのオン - ダイターミネーションの制御方法は、パワーオン時、前記複数のメモリランクのオン - ダイターミネーション回路を初期状態にイネーブルするステップ、前記複数のメモリランクのうち、書き込みターゲットメモリランクに対する書き込み動作を遂行する間中、前記複数のメモリランクのオン - ダイターミネーション回路をイネーブルするステップ、及び前記複数のメモリランクのうち、読み出しターゲットメモリランクに対する読み出し動作を遂行する間中、前記読み出しターゲットメモリランクのオン - ダイターミネーション回路をディスエーブルするステップを含む。

10

**【0006】**

前記の一目的を達成するために、本発明の実施形態に係るメモリ装置のオン - ダイターミネーションの制御方法は、パワーオン時、前記メモリ装置のオン - ダイターミネーション回路を、第1抵抗値を有する初期状態にイネーブルするステップ、前記メモリ装置に対する書き込み動作を遂行する間中、前記メモリ装置のオン - ダイターミネーション回路をイネーブルするステップ、及び前記メモリ装置に対する読み出し動作を遂行する間中、前記メモリ装置のオン - ダイターミネーション回路をディスエーブルするステップを含む。

**【0007】**

前記の一目的を達成するために、本発明の実施形態に係るマルチ - ランクシステムは、複数のメモリランク及び前記複数のメモリランクを制御するメモリコントローラを含む。パワーオン時、前記複数のメモリランクのオン - ダイターミネーション回路は初期状態にイネーブルされ、前記複数のメモリランクのうち、書き込みターゲットメモリランクに対する書き込み動作を遂行する間中、前記複数のメモリランクのオン - ダイターミネーション回路はイネーブルされ、前記複数のメモリランクのうち、読み出しターゲットメモリランクに対する読み出し動作を遂行する間中、前記読み出しターゲットメモリランクのオン - ダイターミネーション回路はディスエーブルされる。

20

**【発明の効果】**

**【0008】**

本発明の実施形態に係るマルチオン - ダイターミネーションの制御方法、これを遂行する装置及びシステムは、ターゲットメモリランク及びノン - ターゲットメモリランクのオン - ダイターミネーション回路のイネーブルされた初期状態を維持し、かつ読み出し動作の対象となる読み出しターゲットメモリランクのオン - ダイターミネーション回路のみをディスエーブルする静的制御を通じて消耗電力を減少し、信号品位を向上できる。

30

**【図面の簡単な説明】**

**【0009】**

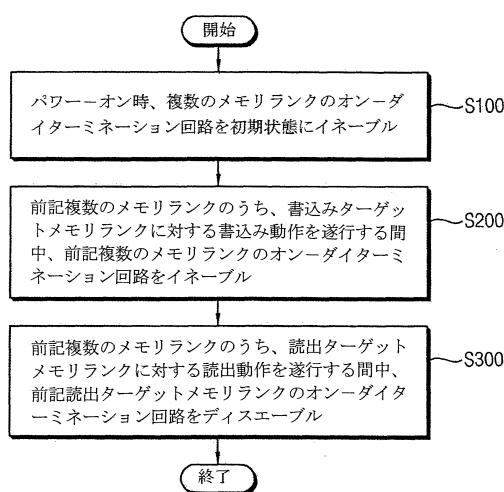

**【図1】**本発明の実施形態に係るオン - ダイターミネーションの制御方法を示すフローチャートである。

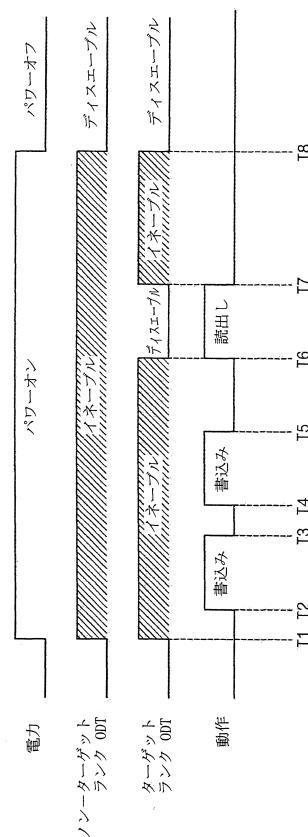

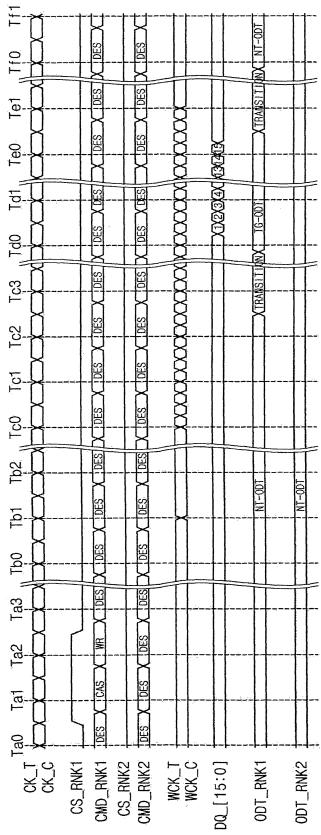

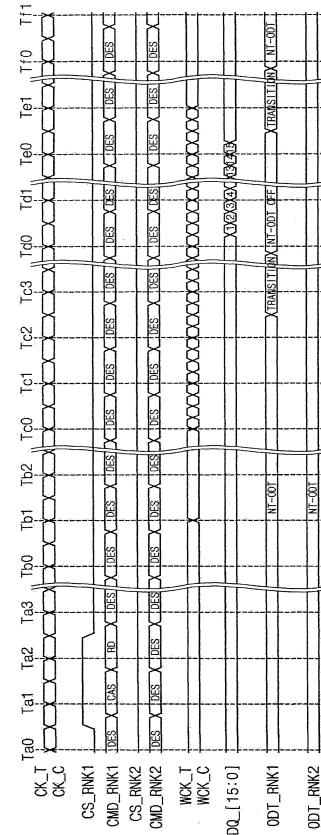

**【図2】**本発明の実施形態に係るオン - ダイターミネーションの制御方法を示すタイミング図である。

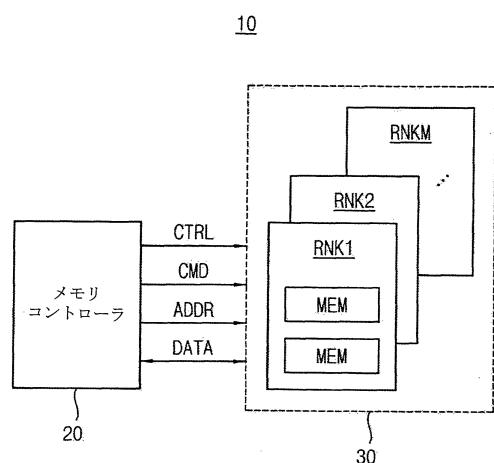

**【図3】**本発明の実施形態に係るマルチ - ランクシステムを示すブロック図である。

40

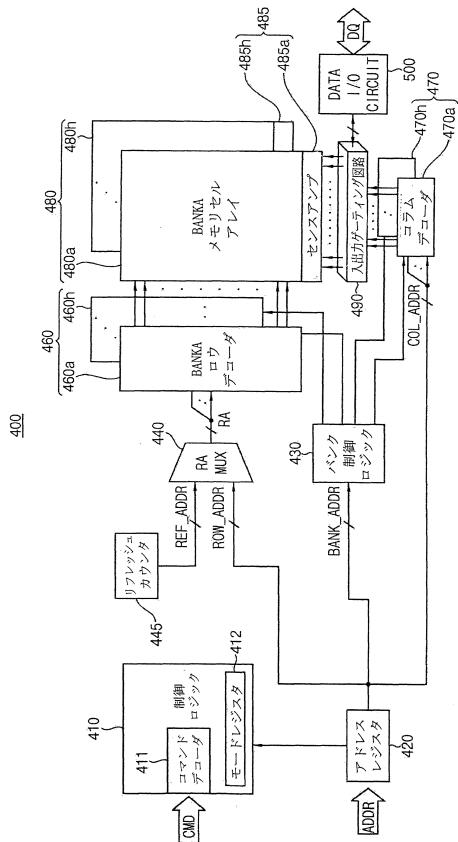

**【図4】**図3のマルチ - ランクシステムに含まれるメモリ装置の一実施形態を示すブロック図である。

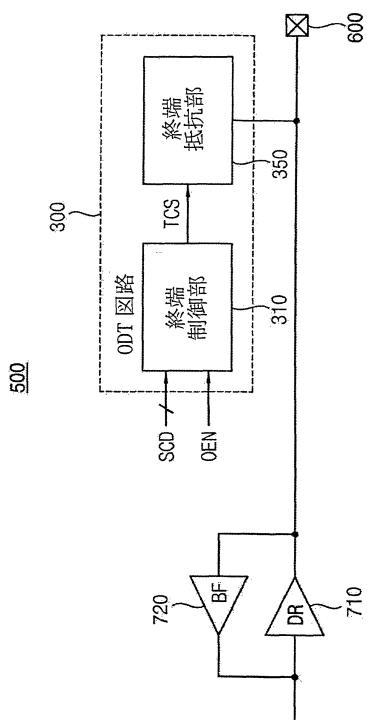

**【図5】**図4のメモリ装置に含まれるデータ入出力回路の一実施形態を示すブロック図である。

**【図6】**図5のデータ入出力回路に含まれるオン - ダイターミネーション回路の一実施形態を示す回路図である。

**【図7】**本発明の実施形態に係る書き込み動作でのオン - ダイターミネーションの制御方法を示す図である。

**【図8】**本発明の実施形態に係る読み出し動作でのオン - ダイターミネーションの制御方法を示す図である。

50

【図 9】本発明の実施形態に係る書き込み動作でのオン - ダイターミネーションの制御方法を示す図である。

【図 10】本発明の実施形態に係る読み出し動作でのオン - ダイターミネーションの制御方法を示す図である。

【図 11】本発明の実施形態に係る読み出し動作でのオン - ダイターミネーションの制御方法を示す図である。

【図 12】本発明の実施形態に係るオン - ダイターミネーションの制御方法に適用される抵抗設定の一実施形態を示す図である。

【図 13】図 12 の抵抗設定に相応する書き込み動作でのオン - ダイターミネーション回路の等価抵抗を説明するための図である。 10

【図 14】図 12 の抵抗設定に相応する読み出し動作でのオン - ダイターミネーション回路の等価抵抗を説明するための図である。

【図 15】センター - タップターミネーション ( CTT : center - tapped termination ) を説明するための図である。

【図 16】センター - タップターミネーション ( CTT : center - tapped termination ) を説明するための図である。

【図 17】第 1 シュード - オープン ( 擬似オープン ) ドレイン ( POD : pseudo - open \_ drain ) ターミネーションを説明するための図である。

【図 18】第 1 シュード - オープンドレイン ( POD : pseudo - open \_ drain ) ターミネーションを説明するための図である。 20

【図 19】第 2 シュード - オープンドレインターミネーションを説明するための図である。

【図 20】第 2 シュード - オープンドレインターミネーションを説明するための図である。

【図 21】本発明の実施形態に係るオン - ダイターミネーションの制御方法に適用される抵抗設定の一実施形態を示す図である。

【図 22】本発明の一実施形態に係る CAS コマンドを示す図である。

【図 23】本発明の実施形態に係るオン - ダイターミネーションのためのモードレジスタを説明するための図である。

【図 24】本発明の実施形態に係るオン - ダイターミネーションのためのモードレジスタを説明するための図である。

【図 25】本発明の一実施形態に係る積層型メモリ装置の構造を示す図である。 30

【図 26】本発明の実施形態に係るメモリ装置をモバイルシステムに応用した例を示すブロック図である。

#### 【発明を実施するための形態】

##### 【0010】

以下、添付した図面を参照して、本発明の好ましい実施形態をより詳細に説明する。図面上の同一の構成要素に対しては同一の参照符号を使用し、同一の構成要素に対して重複した説明は省略する。

##### 【0011】

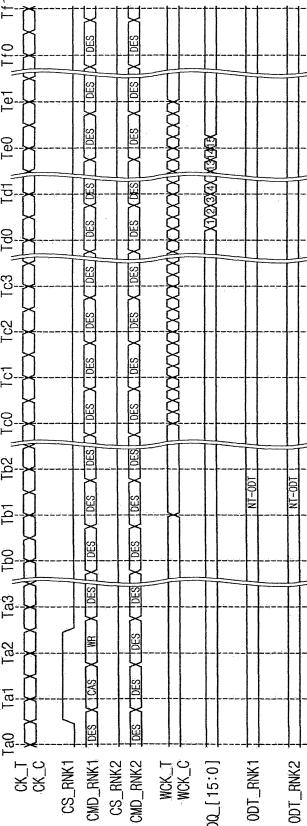

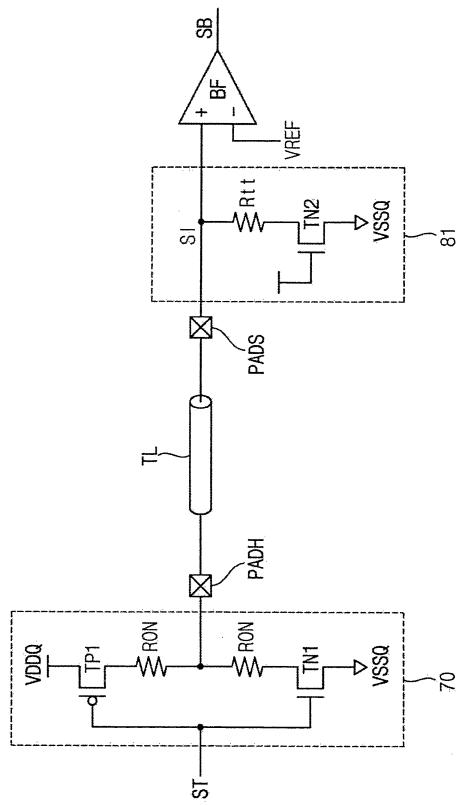

図 1 は本発明の実施形態に係るオン - ダイターミネーションの制御方法を示すフローチャートであり、図 2 は本発明の実施形態に係るオン - ダイターミネーションの制御方法を示すタイミング図である。 40

##### 【0012】

図 1 及び図 2 には複数のメモリランクを含むマルチ - ランクシステムのオン - ダイターミネーションの制御方法が図示されている。マルチ - ランクシステムに対しては図 3 を参照して後述する。

##### 【0013】

図 1 を参照すると、パワーオン時、前記複数のメモリランクのオン - ダイターミネーション回路を初期状態にイネーブルする ( S100 )。前記複数のメモリランクのうち、書き込みターゲットメモリランクに対する書き込み動作を遂行する間中、前記複数のメモリランクのオン - ダイターミネーション回路をイネーブルする ( S200 )。前記複数のメモリラ 50

ンクのうち、読み出しターゲットメモリランクに対する読み出し動作を遂行する間中、前記読み出しターゲットメモリランクのオン・ダイターミネーション回路をディスエーブルする(S300)。

#### 【0014】

メモリアクセス動作は書き込み動作(write\_operation)及び読み出し動作(read\_operation)を含み、前記メモリアクセス動作はその他のモードレジスタ書き込み動作、モードレジスタ読み出し動作、リフレッシュ動作などとは区別される。書き込み動作の場合には複数のメモリランクは、書き込み動作の対象となる書き込みターゲットメモリランク及びそれ以外のノン・ターゲットメモリランクに区分される。読み出し動作の場合には複数のメモリランクは、読み出し動作の対象となる読み出しターゲットメモリランク及びそれ以外のノン・ターゲットメモリランクに区分される。以下、前記書き込みターゲットメモリランク又は読み出しターゲットメモリランクは何れも単にターゲットメモリランクと称される。

10

#### 【0015】

図2を参照すると、マルチ・ランクシステムがパワーオンされる時点T1で、全てのメモリランクのオン・ダイターミネーション回路を初期状態にイネーブルする。一実施形態で、前記複数のメモリランクのオン・ダイターミネーション回路は前記初期状態で全て同一の第1抵抗値を有する。図2にはオン・ダイターミネーション回路の初期状態へのイネーブル時点がパワーオン時点と一致するものとして図示されているが、パワーオン過程が完了した後、一定の時差をあいてオン・ダイターミネーション回路が初期状態にイネーブルされ得る。

20

#### 【0016】

書き込み動作が遂行される時間区間(time\_interval)T2～T3及びT4～T5で、書き込みターゲットメモリランク及びノン・ターゲットメモリランクを含む全てのメモリランクのオン・ダイターミネーション回路はイネーブルされた状態を維持する。一実施形態で、書き込み動作が遂行される間中、書き込みターゲットメモリランク及びノン・ターゲットメモリランクを含む全てのメモリランクのオン・ダイターミネーション回路は、前記第1抵抗値を有する前記初期状態をそのまま維持する。他の実施形態で、書き込み動作が遂行される間中、書き込みターゲットメモリランクは、前記第1抵抗値から第2抵抗値へ変更され、ノン・ターゲットメモリランクのオン・ダイターミネーション回路は前記第1抵抗値を有する前記初期状態をそのまま維持する。

30

#### 【0017】

読み出し動作が遂行される時間区間T6～T7で、読み出しターゲットメモリランクのオン・ダイターミネーション回路はディスエーブルされ、ノン・ターゲットメモリランクのオン・ダイターミネーションはイネーブルされる。一実施形態で、読み出し動作が遂行される間中、ノン・ターゲットメモリランクのオン・ダイターミネーション回路は、前記第1抵抗値を有する前記初期状態をそのまま維持する。

図2には読み出しターゲットメモリランクのオン・ダイターミネーション回路がディスエーブルされる時間区間と読み出し動作が遂行される時間区間とが一致するものとして図示されているが、読み出しターゲットメモリランクのオン・ダイターミネーション回路がディスエーブルされる時間区間は読み出し動作が遂行される時間区間に含まれ得る。即ち、少なくともデータ入出力ピンを通じてデータが実際に出入力される間のみ、読み出しターゲットメモリランクのオン・ダイターミネーション回路がディスエーブルされれば充分であり得る。

40

#### 【0018】

マルチ・ランクシステムがパワー・オフされる時点T8で、電力供給が中断され、全てのメモリランクのオン・ダイターミネーション回路がディスエーブルされる。

#### 【0019】

ターゲットメモリランクのオン・ダイターミネーション回路のみをイネーブルし、ノン・ターゲットメモリランクのオン・ダイターミネーション回路をディスエーブルする場合には、ノン・ターゲットメモリランクにインジェクション(注入)された信号の伝搬波動(

50

wave) が終端されないのでジッター(jitter)を発生させ、信号品位が低下することがある。一方、本発明の実施形態に係るオン・ダイターミネーションの制御方法では、書込みターゲットメモリランクの場合を除いては、オン・ダイターミネーションを常にイネーブルすることによって、信号品位を向上できる。ノン・ターゲットメモリランクのオン・ダイターミネーション回路を常にイネーブルしても後述するシード・オープンドレインターミネーションの場合にはスタンバイ電力消耗が発生しない。

#### 【0020】

一方、ノン・ターゲットメモリランクのオン・ダイターミネーション回路を書込み動作ではイネーブルし、読み出し動作ではディスエーブルする場合には、全てのメモリランクが書込みコマンド及び読み出しコマンドを受信してデコーディングするように待機しなければならないので、パワーダウンモードへの進入が困難になり、スタンバイ電力が増加する。一方、本発明の実施形態に係るオン・ダイターミネーションの制御方法では、ノン・ターゲットメモリランクに対する書込み動作及び読み出し動作全てに対してオン・ダイターミネーション回路のイネーブル状態を維持するので、パワーダウンモードへの进入が容易であり、従って、スタンバイ電力を減少できる。一実施形態で、複数のメモリランクはメモリコントローラから提供されるランク選択信号の各々に基づいて自身がターゲットメモリランクに該当するか否かが分かる。この場合、スタンバイ状態では全てのメモリランクがパワーダウンモードに進入し、活性化(イネーブル)されたランク選択信号に相応するターゲットメモリランクのみパワーダウンモードからノーマル動作モードにウェークリアップできる。残りのノン・ターゲットメモリランクは、オン・ダイターミネーションのイネーブル状態を変更する必要がないので、パワーダウンモードをそのまま維持できる。

10

20

#### 【0021】

このように、本発明の実施形態に係るマルチオン・ダイターミネーションの制御方法、これを遂行する装置、及びシステムは、ターゲットメモリランク及びノン・ターゲットメモリランクのオン・ダイターミネーション回路のイネーブルされた初期状態を維持し、かつ読み出し動作の対象となる読み出しターゲットメモリランクのオン・ダイターミネーション回路のみをディスエーブルする静的制御を通じて消費電力を減少し、信号品位を向上できる。

#### 【0022】

図1及び2を参照して、マルチ・ランクシステムのオン・ダイターミネーションの制御方法を説明したが、本発明の実施形態は単一ランクシステム又は1つのメモリ装置を含むシステムにも適用できる。

30

#### 【0023】

单一ランクシステムの場合には1つのメモリランク又は1つのメモリ装置が書込み動作又は読み出し動作時、常にターゲットメモリランクに該当する。本発明の実施形態に従って、パワーオン時、前記メモリ装置のオン・ダイターミネーション回路を初期状態にイネーブルすることができる。メモリ装置のオン・ダイターミネーションの制御方法として、前記メモリ装置に対する書込み動作を遂行する間中、前記メモリ装置のオン・ダイターミネーション回路をイネーブルする。前記メモリ装置に対する読み出し動作を遂行する間中、前記メモリ装置のオン・ダイターミネーション回路をディスエーブルする。

#### 【0024】

40

図3は、本発明の実施形態に係るマルチ・ランクシステムを示すブロック図である。

#### 【0025】

図3を参照すると、マルチ・ランクシステム10は、メモリコントローラ20及びメモリサブシステム30を含む。メモリサブシステム30は複数のメモリランク(MRK1～MRKM)を含み、メモリランク(MRK1～MRKM)の各々は少なくとも1つのメモリ装置(MEM)を含む。メモリコントローラ20とメモリサブシステム30は相互間の通信のためのインターフェースを各々含む。前記インターフェースは、コマンド(CMD)、アドレス(ADDR)、制御信号(CTRL)などを転送するためのコントロールバス及びデータ(DATA)を転送するためのデータバスを通じて連結される。

一実施形態で、コマンド(CMD)はアドレス(ADDR)を含むと見做される。メモリ

50

コントローラ 20 は、メモリサブシステム 30 を制御するためのコマンド信号 (CMD) 及び制御信号 (CTRL) を発生し、メモリコントローラ 20 の制御に従ってメモリサブシステム 30 にデータ (DATA) が書込まれるか、又はメモリサブシステム 30 からデータ (DATA) が読出される。

本発明の実施形態に従って、パワーオン時、メモリランク (RNK1 ~ RNKM) のオン - ダイターミネーション回路は初期状態にイネーブルされ、メモリランク (MRK1 ~ MRKM) のうち、書き込みターゲットメモリランクに対する書き込み動作を遂行する間中、メモリランク (MRK1 ~ MRKM) のオン - ダイターミネーション回路はイネーブルされ、メモリランク (MRK1 ~ MRKM) のうち、読み出しターゲットメモリランクに対する読み出し動作を遂行する間中、前記読み出しターゲットメモリランクのオン - ダイターミネーション回路はディスエーブルされる。 10

#### 【0026】

図4は、図3のマルチ - ランクシステムに含まれるメモリ装置の一実施形態を示すプロック図である。

#### 【0027】

図4を参照すると、メモリ装置400は、制御ロジック410、アドレスレジスタ420、バンク制御ロジック430、ロウアドレスマルチプレクサ (RA\_MUX) 440、リフレッシュカウンター445、ロウデコーダ460、カラムデコーダ470、メモリセルアレイ480、センスアンプ部485、入出力ゲーティング回路490、及びデータ入出力回路500を含む。 20

#### 【0028】

メモリセルアレイ480は、複数のバンクアレイ480a ~ 480hを含む。ロウデコーダ460は複数のバンクアレイ480a ~ 480hに各々連結された複数のバンクロウデコーダ460a ~ 460hを含み、カラムデコーダ470は複数のバンクアレイ480a ~ 480hに各々連結された複数のカラムデコーダ470a ~ 470hを含み、センスアンプ部485は複数のバンクアレイ480a ~ 480hに各々連結された複数のセンスアンプ485a ~ 485hを含む。

#### 【0029】

アドレスレジスタ420は、メモリコントローラからバンクアドレス (BANK\_ADDR)、ロウアドレス (ROW\_ADDR)、及びカラムアドレス (COL\_ADDR) を含むアドレス (ADD) を受信する。アドレスレジスタ420は、受信されたバンクアドレス (BANK\_ADDR) をバンク制御ロジック430に提供し、受信されたロウアドレス (ROW\_ADDR) をロウアドレスマルチプレクサ (RA\_MUX) 440に提供し、受信されたカラムアドレス (COL\_ADDR) をカラムデコーダ470に提供する。 30

#### 【0030】

バンク制御ロジック430は、バンクアドレス (BANK\_ADDR) に応答してバンク制御信号を生成する。前記バンク制御信号に応答して、複数のバンクロウデコーダ460a ~ 460hのうち、バンクアドレス (BANK\_ADDR) に相応するバンクロウデコーダが活性化され、複数のバンクカラムデコーダ470a ~ 470hのうち、バンクアドレス (BANK\_ADDR) に相応するバンクカラムデコーダが活性化される。 40

#### 【0031】

ロウアドレスマルチプレクサ440は、アドレスレジスタ220からロウアドレス (ROW\_ADDR) を受信し、リフレッシュカウンター445からリフレッシュロウアドレス (REF\_ADDR) を受信する。ロウアドレスマルチプレクサ440は、ロウアドレス (ROW\_ADDR) 又はリフレッシュロウアドレス (REF\_ADDR) をロウアドレス (RA) として選択的に出力することができる。ロウアドレスマルチプレクサ440から出力されたロウアドレス (RA) はバンクロウデコーダ460a ~ 460hに各々印加される。

#### 【0032】

バンクロウデコーダ460a ~ 460hのうち、バンク制御ロジック430により活性化

10

20

30

40

50

されたバンクロウデコーダは、ロウアドレスマルチプレクサ 440 から出力されたロウアドレス (R A) をデコーディングして前記ロウアドレスに相応するワードラインを活性化する。例えば、前記活性化されたバンクロウデコーダはロウアドレスに相応するワードラインにワードライン駆動電圧を印加する。

#### 【 0033】

カラムデコーダ 470 は、カラムアドレスラッチ (図示せず) を含む。カラムアドレスラッチは、アドレスレジスタ 420 からカラムアドレス (C O L \_ A D D R ) を受信し、受信されたカラムアドレス (C O L \_ A D D R ) を一時的に格納する。また、カラムアドレスラッチは、バストモード (burst mode) で、受信されたカラムアドレス (C O L \_ A D D R ) を徐々に増加する。カラムアドレスラッチは一時的に格納された又は徐々に増加したカラムアドレス (C O L \_ A D D R ) をバンクカラムデコーダ 470 a ~ 470 h に各々印加する。

10

#### 【 0034】

バンクカラムデコーダ 470 a ~ 470 h のうち、バンク制御ロジック 430 により活性化されたバンクカラムデコーダは、入出力ゲーティング回路 490 を通じてバンクアドレス (B A N K \_ A D D R ) 及びカラムアドレス (C O L \_ A D D R ) に相応するセンスアンプを活性化する。

20

#### 【 0035】

入出力ゲーティング回路 490 は、入出力データをゲーティングする回路と共に、入力データマスクロジック、バンクアレイ 480 a ~ 480 h から出力されたデータを格納するための読み出しデータラッチ、及びバンクアレイ 480 a ~ 480 h にデータを書込むための書き込みドライバを含む。

20

#### 【 0036】

バンクアレイ 480 a ~ 480 h のうち、1つのバンクアレイから読み出されるデータ (D Q) は前記1つのバンクアレイに相応するセンスアンプにより感知され、前記読み出しデータラッチに格納される。前記読み出しデータラッチに格納されたデータ (D Q) は、データ入出力回路 500 を通じてメモリコントローラ 20 に提供される。バンクアレイ 480 a ~ 480 h のうち、1つのバンクアレイに書き込まれるデータ (D Q) は、前記メモリコントローラ 20 からデータ入出力回路 500 に提供される。データ入出力回路 500 に提供されたデータ (D Q) は、前記書き込みドライバを通じて前記1つのバンクアレイに書き込まれる。

30

#### 【 0037】

制御ロジック 410 は、メモリ装置 400 の動作を制御する。例えば、制御ロジック 410 はメモリ装置 400 が書き込み動作又は読み出し動作を遂行するように制御信号を生成する。制御ロジック 410 は、メモリコントローラから受信されるコマンド (C M D) をデコーディングするコマンドデコーダ 411 及びメモリ装置 400 の動作条件を設定するためのモードレジスタ (mode register) 412 を含む。

40

#### 【 0038】

図 5 は、図 4 のメモリ装置に含まれるデータ入出力回路 500 の一実施形態を示すブロック図である。

#### 【 0039】

図 5 を参照すると、データ入出力回路 500 は、オン - ダイターミネーション (O D T) 回路 300 、データ入出力ピン 600 、送信ドライバ (D R) 710 、及び受信バッファ (B F) 720 を含む。送信ドライバ 710 は読み出しだ基づいてデータ入出力ピン 600 を駆動し、受信バッファ 720 はデータ入出力ピン 600 を通じて提供される書き込みデータを受信する。

#### 【 0040】

O D T 回路 300 は、終端制御部 310 及び終端抵抗部 350 を含む。

終端抵抗部 350 はデータ入出力ピン 600 に連結され、データ入出力ピン 600 に連結された転送線に終端抵抗を提供する。本発明の実施形態に係るオン - ダイターミネーショ

50

ンの制御方法は、メモリコントローラ 20 とメモリ装置 30 との間の双方向 (bi-directional) 通信を遂行する入出力ピンのオン - ダイターミネーションを制御する場合に適用できる。従って、本発明の実施形態に係るオン - ダイターミネーションの制御方法は、データ入出力ピン 600 だけでなくデータストローブ (data\_strobe) ピン、データマスク (data\_mask) ピン、終端データストローブ (termination\_data\_strobe) ピンのオン - ダイターミネーションにも適用できる。メモリコントローラ 20 からメモリ装置 30 への単方向通信を遂行するアドレス及びコマンドピンに対するオン - ダイターミネーションは、本発明の範疇から除外される。ここで、“ピン”という用語は、集積回路に対する電気的相互接続を幅広く示すものであって、例えばパッド又は集積回路上の他の電気的接触点を含む。

10

#### 【0041】

終端抵抗部 350 は、電源電圧とデータ入出力ピン 600 との間に終端抵抗を提供するプル - アップターミネーション動作及び / 又は接地電圧と入出力ピン 600 との間に終端抵抗を提供するプル - ダウンターミネーション動作を遂行する。プル - アップターミネーション動作及びプル - ダウンターミネーション動作の双方を遂行するセンター - タップターミネーション (CTT : center-tapped termination) は図 15 及び図 16 を参照して後述し、プル - ダウンターミネーション動作のみを遂行する第 1 シュード - オープンドレイン (POD : pseudo-open-drain) ターミネーションは図 17 及び図 18 を参照して後述し、プル - アップターミネーション動作のみを遂行する第 2 シュード - オープンドレインターミネーションは図 19 及び図 20 を参照して後述する。

20

#### 【0042】

一方、図 5 には終端抵抗部 350 が別途に備えられた実施形態を図示したが、別の実施形態に従っては、送信ドライバ (DR) 710 内の信号ドライバ (図示せず) 自体が終端抵抗の役割を遂行する。例えば、データ書込み動作時、受信バッファ 720 はイネーブルされてデータを受信し、送信ドライバ (DR) 710 はデータを転送せず、終端抵抗部の役割を遂行する。

30

#### 【0043】

終端抵抗部 350 が前記プル - アップターミネーション動作を遂行する場合、データ入出力ピン 600 に連結された前記転送線の電圧は電源電圧に維持される。これによって、前記転送線にローレベルを有するデータが転送される時のみに終端抵抗部 350 及び前記転送線に電流が流れる。一方、終端抵抗部 350 が前記プル - ダウンターミネーション動作を遂行する場合、データ入出力ピン 600 に連結された前記転送線の電圧は接地電圧に維持される。これによって、前記転送線にハイレベルを有するデータが転送される時のみに終端抵抗部 350 及び前記転送線に電流が流れる。

#### 【0044】

終端制御部 310 は、ストレンジス (strength) コード (SCD) 及び出力イネーブル信号 (OEN) に基づいて終端抵抗部 350 を制御する終端制御信号 (TCS) を生成することができる。

40

#### 【0045】

一実施形態で、ストレンジスコード (SCD) はデータレート (data\_rate) に関連する複数ビットである。ここで、データレートはメモリ装置の動作周波数 (operating\_frequency)、即ちデータ入出力ピン 600 を通じて送受信されるデータのトグルレートを意味する。図 23 及び図 24 を参照して後述するように、複数ビットのストレンジスコード (SCD) は図 4 のモードレジスタ 412 に格納された値に基づいて提供される。

#### 【0046】

出力イネーブル信号 (OEN) は、データ入出力ピン 600 に連結された転送線を通じてデータが出力される読出しモード (read\_mode) において活性化される。出力イネーブル信号 (OEN) が活性化された場合、終端制御部 310 は前記終端抵抗を提供し

50

ないように終端抵抗部 350 を制御する終端制御信号 (TCS) を生成する。例えば、終端制御部 310 は活性化された出力イネーブル信号 (OEN) に応答して所定のロジックレベルを有する終端制御信号 (TCS) を生成し、終端抵抗部 350 は前記所定のロジックレベルを有する終端制御信号 (TCS) に応答して終端抵抗部 350 とデータ入出力ピン 600 の電気的な連結を切断する。このように、終端抵抗部 350 とデータ入出力ピン 600 との電気的な連結が切断された時、オン・ダイターミネーション回路 300 又は終端抵抗部 350 が「ディスエーブルされた」と言われる。

#### 【0047】

書込みモードにおいて出力イネーブル信号 (OEN) が不活性化 (ディスエーブル) された場合、終端制御部 310 は前記終端抵抗を提供するように終端抵抗部 350 を制御する終端制御信号 (TCS) を生成する。終端制御部 310 はストレングスコード (SCD) に応答して前記終端抵抗の抵抗値を可変するように終端制御信号 (TCS) のロジックレベルを変更する。

10

#### 【0048】

図 6 は、図 5 のデータ入出力回路に含まれるオン・ダイターミネーション回路の一実施形態を示す回路図である。

#### 【0049】

図 6 を参照すると、オン・ダイターミネーション回路 300 はプルアップ終端制御部 330、プルダウン終端制御部 340、プルアップ終端抵抗部 360、及びプルダウン終端抵抗部 370 を含むことができる。

20

#### 【0050】

プルアップ終端制御部 330 は第 1 ~ 第 3 選択器 334 ~ 336 を含み、プルダウン終端制御部 340 は第 4 ~ 第 6 選択器 344 ~ 346 を含む。プルアップ終端抵抗部 360 は、第 1 ~ 第 3 の PMOS ドラッグスター 361 ~ 363 及び第 1 ~ 第 3 抵抗 (R1, R2, R3) を含む。第 1 ~ 第 3 の PMOS ドラッグスター 361 ~ 363 は電源電圧 (VDDQ) に連結され、第 1 ~ 第 3 抵抗 (R1, R2, R3) は各々第 1 ~ 第 3 の PMOS ドラッグスター 361 ~ 363 の各々とデータ入出力ピン 600 との間に連結される。プルダウン終端抵抗部 370 は、第 1 ~ 第 3 の NMOS ドラッグスター 371 ~ 373 及び第 4 ~ 第 6 抵抗 (R4, R5, R6) を含む。第 1 ~ 第 3 の NMOS ドラッグスター 371 ~ 373 は各々接地電圧 (VSSQ) に連結され、第 4 ~ 第 6 抵抗 (R4, R5, R6) は第 1 ~ 第 3 の NMOS ドラッグスター 371 ~ 373 の各々とデータ入出力ピン 600 との間に連結される。

30

#### 【0051】

第 1 ~ 第 3 選択器 334 ~ 336 の各々は選択信号として出力イネーブル信号 (OEN) を受信し、電源電圧 (VDDQ) を第 1 入力信号として受信し、第 1 ~ 第 3 ストレングスコードビット (SCD1, SCD2, SCD3) を第 2 入力信号として受信することができる。第 4 ~ 第 6 選択器 344 ~ 346 の各々は選択信号として出力イネーブル信号 (OEN) を受信し、接地電圧 (VSSQ) を第 1 入力信号として受信し、第 4 ~ 第 6 ストレングスコードビット (SCD4, SCD5, SCD6) を第 2 入力信号として受信することができる。

40

#### 【0052】

読み出しモードで出力イネーブル信号 (OEN) が活性化されれば、第 1 ~ 第 3 選択器 334 ~ 336 の各々はハイレベルの第 1 ~ 第 3 終端制御信号 (TCS1, TCS2, TCS3) を出力し、第 4 ~ 第 6 選択器 344 ~ 346 の各々はローレベルの第 4 ~ 第 6 終端制御信号 (TCS4, TCS5, TCS6) を出力する。従って、ハイレベルの第 1 ~ 第 3 終端制御信号 (TCS1, TCS2, TCS3) により第 1 ~ 第 3 の PMOS ドラッグスター 361 ~ 363 がターン・オフされ、ローレベルの第 4 ~ 第 6 終端制御信号 (TCS4, TCS5, TCS6) により第 1 ~ 第 3 の NMOS ドラッグスター 371 ~ 373 がターン・オフされる。これによって、データ入出力ピン 600 は電源電圧 (VDDQ) 及び接地電圧 (VSSQ) から電気的に遮断される。結果的に、読み出しモードでオン・ダイター

50

ミネーション回路 300 はディスエーブルされる。

【0053】

書込みモードで出力イネーブル信号 (OEN) が不活性化されれば、第 1 ~ 第 3 選択器 334 ~ 336 の各々は第 1 ~ 第 3 ストレングスコードビット (SCD1、SCD2、SCD3) を第 1 ~ 第 3 終端制御信号 (TCS1、TCS2、TCS3) としてプルアップ終端抵抗部 360 に出力し、第 4 ~ 第 6 選択器 344 ~ 346 の各々は第 4 ~ 第 6 ストレングスコードビット (SCD4、SCD5、SCD6) を第 4 ~ 第 6 終端制御信号 (TCS4、TCS5、TCS6) としてプルダウン終端抵抗部 370 に出力する。

【0054】

前述したように、複数ビットのストレングスコード (SCD)、即ちストレングスコードビット (SCD1 ~ SCD6) はデータレート (data\_rate)、即ち動作周波数 (FOP、データのトグルレート) を反映する。データレートが高い場合には終端抵抗を減少して速い時間にチャンネルを充放電する。また、データレートが低い場合には終端抵抗を増加してチャンネルに沿って流れるDC電流を減少させて電流消耗を減少する。

10

【0055】

図 6 で、第 1 ~ 第 6 抵抗 (R1 ~ R6) は各々 1 つの抵抗として図示されているが、実施形態によっては第 1 ~ 第 6 抵抗 (R1 ~ R6) の各々は、並列連結された複数の抵抗及び前記抵抗の連結を制御するためのトランジスタの組み合わせにより具現される。

【0056】

図 6 を参照して図 15 及び図 16 のセンター - タップターミネーション (CTT : center-tapped\_termination) に該当する構成を説明したが、これからシュード - オープンドレイン (POD : pseudo-open\_drain) ターミネーション構成が理解できよう。即ち、図 6 でプルアップ終端制御部 330 及びプルアップ終端抵抗部 360 を省略した構成は、図 17 及び図 18 の第 1 の POD ターミネーションに対応し、図 6 でプルダウン終端制御部 340 及びプルダウン終端抵抗部 370 を省略した構成は図 19 及び図 20 の第 2 の POD ターミネーションに対応する。

20

【0057】

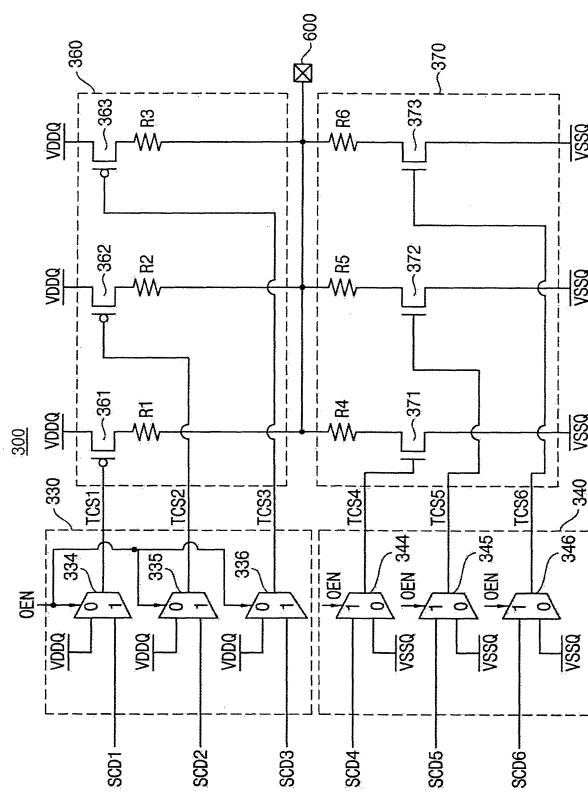

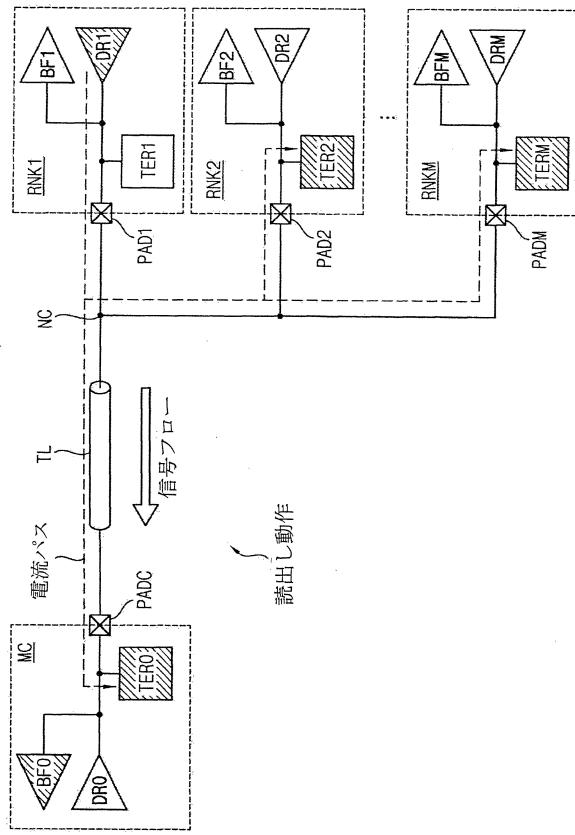

図 7、図 8、及び図 9 は、本発明の実施形態に係る書込み動作におけるオン - ダイターミネーションの制御方法を示す図である。

【0058】

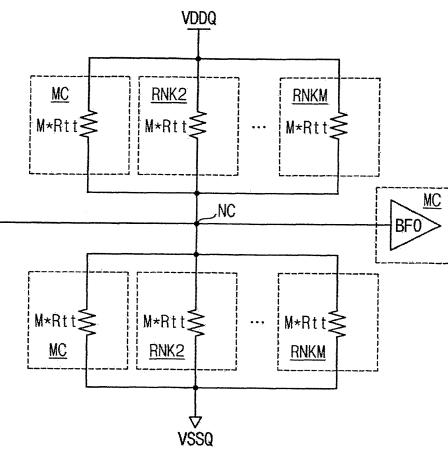

図 7 に図示したように、メモリコントローラ (MC) はデータ入出力ピン (PADC、PAD1 ~ PADM) と転送ライン TL を通じて複数のメモリランク (RNK1 ~ RNKM) に並列連結される。転送ライン TL は共通ノード (NC) において複数のメモリランク (RNK1 ~ RNKM) のデータ入出力ピン (PAD1 ~ PADM) に分岐する。

30

【0059】

図 7 には第 1 メモリランク (RNK1) が書込みターゲットメモリランクに該当し、第 2 ~ 第 M メモリランク (RNK2 ~ RNKM) がノン - ターゲットメモリランクに該当する例が図示されており、イネーブルされる構成要素が斜線で表示 (ハッチ) されている。

【0060】

書込み動作では、データ送信装置に相当するメモリコントローラ (MC) の送信ドライバ (DR0) がイネーブルされ、受信バッファ (BF0) がディスエーブルされる。また、データ受信装置に相当するターゲットメモリランク (RNK1) の受信バッファ (BF1) がイネーブルされ、ターゲットメモリランク (RNK1) の送信ドライバ (DR1)、ノン - ターゲットメモリランク (RNK2 ~ RNKM) の受信バッファ (BF2 ~ BFM)、及び送信ドライバ (DR2 ~ DRM) はディスエーブルされる。

40

【0061】

本発明の実施形態に従って書込み動作を遂行する間中、書込みターゲットメモリランク (RNK1) のオン - ダイターミネーション回路 (TER1) 及びノン - ターゲットメモリランク (RNK2 ~ RNKM) のオン - ダイターミネーション回路 (TER2 ~ TERM) が全てイネーブルされる。一方、メモリコントローラ (MC) のオン - ダイターミネー

50

ション回路 (T E R 0) はディスエーブルされる。メモリコントローラ (M C) の送信ドライバ (D R 0) から全てのオン - ダイターミネーション回路 (T E R 1 ~ T E R M) まで電流経路 (c u r r e n t \_ p a t h) が形成され、結果的に、信号反射を抑制して信号品位を向上できる。

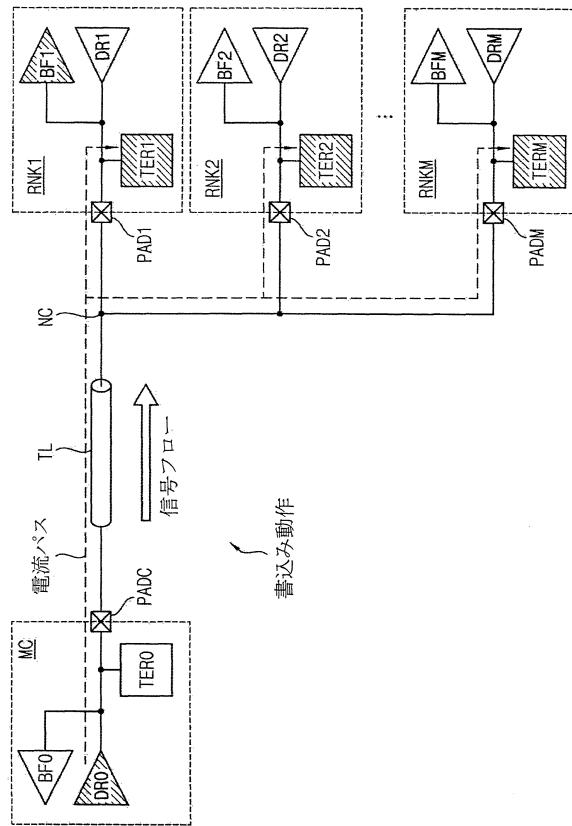

#### 【 0 0 6 2 】

図 8 及び図 9 を参照すると、時点 (T a 0 ~ T f 1) は動作クロック信号対 (C K \_ T、C K \_ C) のエッジに対応する。第 1 ランク選択信号 (C S \_ R N K 1) 及び第 1 コマンド信号 (C M D \_ R N K 1) は第 1 メモリランク (R N K 1) に専属し (d e d i c a t e d)、第 2 ランク選択信号 (C S \_ R N K 2) 及び第 2 コマンド信号 (C M D \_ R N K 2) は第 2 メモリランク (R N K 2) に専属する。データストローブ信号対 (W C K \_ T、W C K \_ C) とデータ信号 (D Q [1 5 : 0]) はメモリコントローラ (M C) からターゲットメモリランク (R N K 1) に提供される。

10

O D T \_ R N K 1 は第 1 メモリランク (R N K 1) のオン - ダイターミネーション状態を示し、O D T \_ R N K 2 は第 2 メモリランク (R N K 2) のオン - ダイターミネーション状態を示す。D E S は非選択 (d e s e l e c t) を示す。T R A N S I T I O N はオン - ダイターミネーション状態の変更時、過渡期区間を示す。

#### 【 0 0 6 3 】

図 8 及び図 9 は、第 1 メモリランク (R N K 1) がターゲットメモリランクに該当し、第 2 メモリランク (R N K 2) がノン - ターゲットメモリランクに該当する場合の書き込み動作を示す。従って、第 1 ランク選択信号 (C S \_ R N K 1) が活性化される間中、第 1 コマンド信号 (C M D \_ R N K 1) を通じて C A S コマンド (C A S) 及び書き込みコマンド (W R) が転送され、第 2 ランク選択信号 (C S \_ R N K 2) 及び第 2 コマンド信号 (C M D \_ R N K 2) は不活性化された状態を維持する。

20

#### 【 0 0 6 4 】

本発明の実施形態に従って、書き込み動作を遂行する間中、ターゲットメモリランク (R N K 1) 及びノン - ターゲットメモリランク (R N K 2) のオン - ダイターミネーション回路はイネーブルされる。

一実施形態において、図 8 に図示したように、書き込み動作のためのデータ信号 (D Q [1 5 : 0]) がトグリングする間中、ノン - ターゲット (N T) メモリランク (R N K 2) 及びターゲット (T G) メモリランク (R N K 1) のオン - ダイターミネーション回路は、全て前述した初期状態、即ち、ノン - ターゲット O D T 状態 (N T - O D T) をそのまま維持する。

30

他の実施形態において、図 9 に図示したように、書き込み動作のためのデータ信号 (D Q [1 5 : 0]) がトグリングする間中、ノン - ターゲットメモリランク (R N K 2) のオン - ダイターミネーション回路は、前述した初期状態 (N T - O D T) をそのまま維持し、ターゲットメモリランク (R N K 1) は初期状態 (N T - O D T) と相異する抵抗値を有する他の状態、即ち、ターゲット O D T (T G - O D T) に変更される。

#### 【 0 0 6 5 】

図 10 及び図 11 は、本発明の実施形態に係る読み出し動作でのオン - ダイターミネーションの制御方法を示す図である。

40

#### 【 0 0 6 6 】

図 10 に図示したように、メモリコントローラ (M C) はデータ入出力ピン (P A D C、P A D 1 ~ P A D M) と転送ライン (T L) を通じて複数のメモリランク (R N K 1 ~ R N K M) に並列連結できる。転送ライン (T L) は、共通ノード (N C) で複数のメモリランク (R N K 1 ~ R N K M) のデータ入出力ピン (P A D 1 ~ P A D M) に分岐する。

#### 【 0 0 6 7 】

図 10 には第 1 メモリランク (R N K 1) が読み出しターゲットメモリランクに該当し、第 2 ~ 第 M メモリランク (R N K 2 ~ R N K M) がノン - ターゲットメモリランクに該当する例が図示されており、イネーブルされる構成要素が斜線で表示されている。

#### 【 0 0 6 8 】

読み出し動作では、データ受信装置に相応するメモリコントローラ（M C）の送信ドライバ（D R 0）がディスエーブルされ、受信バッファ（B F 0）がイネーブルされる。また、データ送信装置に相応するターゲットメモリランク（R N K 1）の送信ドライバ（D R 1）がイネーブルされ、ターゲットメモリランク（R N K 1）の受信バッファ（B F 1）、ノン・ターゲットメモリランク（R N K 2～R N K M）の受信バッファ（B F 2～B F M）、及び送信ドライバ（D R 2～D R M）はディスエーブルされる。

#### 【0069】

本発明の実施形態に従って読み出し動作を遂行する間中、書き込みターゲットメモリランク（R N K 1）のオン・ダイターミネーション回路（T E R 1）はディスエーブルされ、ノン・ターゲットメモリランク（R N K 2～R N K M）のオン・ダイターミネーション回路（T E R 2～T E R M）はイネーブルされる。一方、メモリコントローラ（M C）のオン・ダイターミネーション回路（T E R 0）はイネーブルされる。ターゲットメモリランク（R N K 1）の送信ドライバ（D R 1）からメモリコントローラ（M C）のオン・ダイターミネーション回路（T E R 0）及びノン・ターゲットメモリランクのオン・ダイターミネーション回路（T E R 2～T E R M）まで電流経路（current\_path）が形成され、結果的に信号反射を抑制して信号品位を向上できる。10

#### 【0070】

図11で、時点（T a 0～T f 1）は動作クロック信号対（C K\_T、C K\_C）のエッジに該当する。第1ランク選択信号（C S\_R N K 1）及び第1コマンド信号（C M D\_R N K 1）は第1メモリランク（R N K 1）に専属し（dedicated）、第2ランク選択信号（C S\_R N K 2）及び第2コマンド信号（C M D\_R N K 2）は第2メモリランク（R N K 2）に専属される。データストローブ信号対（W C K\_T、W C K\_C）とデータ信号（D Q [15:0]）はターゲットメモリランク（R N K 12）からメモリコントローラ（M C）に提供される。O D T\_R N K 1は第1メモリランク（R N K 1）のオン・ダイターミネーション状態を示し、O D T\_R N K 2は第2メモリランク（R N K 2）のオン・ダイターミネーション状態を示す。D E Sは非選択（deselect）を示す。TRANSITIONは、オン・ダイターミネーション状態の変更時、過渡期区間を示す。20

#### 【0071】

図11は、第1メモリランク（R N K 1）がターゲットメモリランクに該当し、第2メモリランク（R N K 2）がノン・ターゲットメモリランクに該当する場合の読み出し動作を示す。従って、第1ランク選択信号（C S\_R N K 1）が活性化される間中、第1コマンド信号（C M D\_R N K 1）を通じてC A Sコマンド（C A S）及び読み出しこみ（R D）が転送され、第2ランク選択信号（C S\_R N K 2）及び第2コマンド信号（C M D\_R N K 2）は不活性化された状態を維持する。30

#### 【0072】

本発明の実施形態に従って、読み出し動作を遂行する間中、ターゲットメモリランク（R N K 1）のオン・ダイターミネーション回路はディスエーブルされ、ノン・ターゲットメモリランク（R N K 2）のオン・ダイターミネーション回路はイネーブルされる。

一実施形態において、図11に図示したように、書き込み動作のためのデータ信号（D Q [15:0]）がトグリングする間中、ノン・ターゲットメモリランク（R N K 2）のオン・ダイターミネーション回路は前述した初期状態（N T - O D T）をそのまま維持し、ターゲットメモリランク（R N K 1）はディスエーブルされた状態（N T - O D T - O F F）に変更される。40

#### 【0073】

図12は、本発明の実施形態に係るオン・ダイターミネーションの制御方法に適用される抵抗設定の一実施形態を示す図である。

#### 【0074】

図12を参照すると、読み出し動作でターゲットメモリランク（R N K\_T G）のオン・ダイターミネーション回路はディスエーブルされ、ノン・ターゲットメモリランク（R N K

10

20

30

40

50

$_N T$ ) 及びメモリコントローラ (MC) のオン - ダイターミネーション回路は第 1 抵抗値 ( $M * R_{t t}$ ) を有する。書き込み動作でターゲットメモリランク (RNK\_TG) 及びノン - ターゲットメモリランク (RNK\_NT) のオン - ダイターミネーション回路は、第 1 抵抗値 ( $M * R_{t t}$ ) を有する。第 1 抵抗値 ( $M * R_{t t}$ ) は、前述した初期状態の抵抗値に該当する。結果的に、図 8 を参照して説明したように、書き込み動作を遂行する間中、ターゲットメモリランク (RNK\_TG) 及びノン - ターゲットメモリランク (RNK\_NT) のオン - ダイターミネーション回路は、第 1 抵抗値 ( $M * R_{t t}$ ) を有する前記初期状態をそのまま維持する。

【 0 0 7 5 】

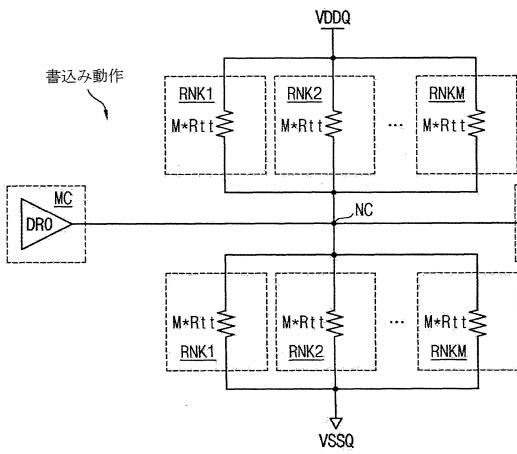

図13は、図12の抵抗設定に相応する、書き込み動作におけるターミネーション回路の等価抵抗を説明するための図である。

【 0 0 7 6 】

図13を参照すると、メモリコントローラ(MC)からターゲットメモリランク(RNK1)にデータが転送される書き込み動作が遂行される間中、ターゲットメモリランク(RNK1)及びノン-ターゲットメモリランク(RNK2～RNKM)のオン-ダイターミネーション回路が全て第1抵抗値( $M * R_{t\ t}$ )を有することができる。複数のメモリランク(RNK1～RNKM)の個数がMの場合、共通ノード(NC)と電源電圧(VDDQ)との間には第1抵抗値( $M * R_{t\ t}$ )を有するM個の抵抗が並列連結され、結果的に共通ノード(NC)と電源電圧(VDDQ)との間の等価抵抗は $R_{t\ t}$ に相応する。同様に、共通ノード(NC)と接地電圧(VSSQ)との間の等価抵抗は $R_{t\ t}$ に相応する。このような等価抵抗( $R_{t\ t}$ )に該当する多様なターミネーション方式については図15から図20を参照して後述する。

【 0 0 7 7 】

図14は、図12の抵抗設定に相応する読み出し動作でのターミネーション回路の等価抵抗を説明するための図である。

【 0 0 7 8 】

図14を参照すると、ターゲットメモリランク (RNK1) からメモリコントローラ (MC) にデータが転送される読出し動作が遂行される間中、ターゲットメモリランク (RNK1) のオン - ダイターミネーション回路はディスエーブルされ、メモリコントローラ (MC) 及びノン - ターゲットメモリランク (RNK2 ~ RNKM) のオン - ダイターミネーション回路は全て第1抵抗値 ( $M * R_{t\ t}$ ) を有する。複数のメモリランク (RNK1 ~ RNKM) の個数がMの場合、共通ノード (NC) と電源電圧 (VDDQ)との間には第1抵抗値 ( $M * R_{t\ t}$ ) を有するM個の抵抗が並列連結され、結果的に共通ノード (NC) と電源電圧 (VDDQ)との間の等価抵抗は  $R_{t\ t}$  に相応する。同様に、共通ノード (NC) と接地電圧 (VSSQ)との間の等価抵抗は  $R_{t\ t}$  に相応する。このような等価抵抗 ( $R_{t\ t}$ ) に該当する多様なターミネーション方式に対して図15から図20を参照して後述する。図15から図20の構成はターミネーション方式を説明するためのものであり、送信ドライバ - ミネーション回路などを図示した構成に限定されない。例えば、トランジスタのN - タイプ及びP - タイプを変更でき、送信ドライバにパワーゲーティングのためのトランジスタを追加できる。

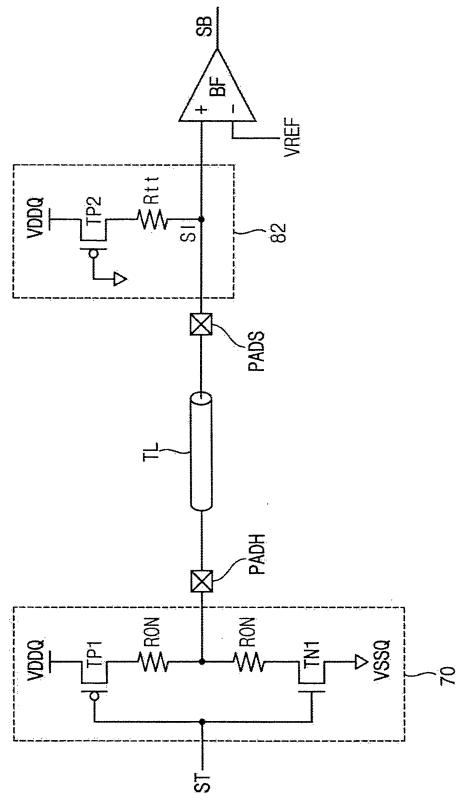

〔 0 0 7 9 〕

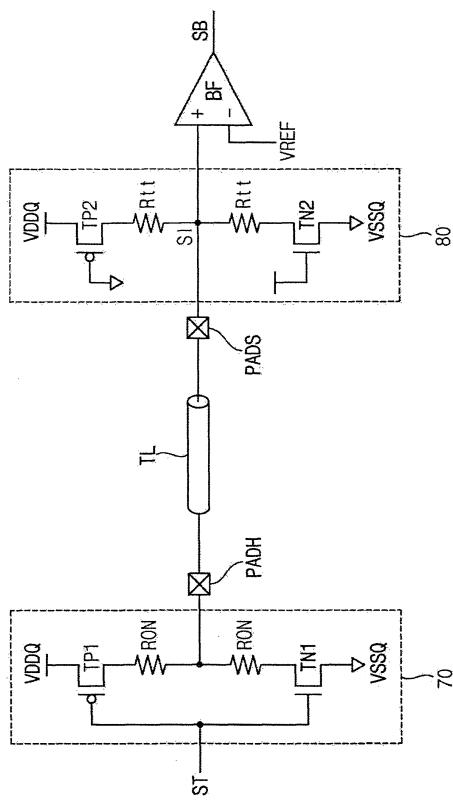

図15及び図16は、センター・タップターミネーション(CTT:center-tapped termination)を説明するための図である。

[ 0 0 8 0 ]

図15を参照すると、送信装置の送信ドライバ70は内部回路からの送信信号(ST)に基づいて入出力パッド(PADH)を駆動する。送信装置の入出力パッド(PADH)は、転送ライン(TL)を通じて受信装置の入出力パッド(PADS)に連結される。受信装置の入出力パッド(PADS)にはインピーダンスマッチングのために、CTT方式のターミネーション回路(80)が連結される。受信装置の受信バッファ(BF)は、入出力パッド(PADS)を通じて入力される入力信号(SI)を基準電圧(VREF)と比

較してバッファ信号 (S B) を内部回路に提供する。

#### 【0081】

送信ドライバ70は、電源電圧 (VDDQ) 及び入出力パッド (PADH) の間に連結されたプルアップ部と入出力パッド (PADH) 及び接地電圧 (VSSQ) の間に連結されたプルダウン部を含む。プルアップ部は、送信信号 (ST) に応答してスイッチングされるPMOSトランジスタ (TP1) 及びターンオン抵抗 (RON) を含む。プルダウン部は、送信信号 (ST) に応答してスイッチングされるNMOSトランジスタ (TN1) 及びターンオン抵抗 (RON) を含む。ターンオン抵抗 (RON) は省略可能であり、その場合、ターンオン抵抗 (RON) はトランジスタ (TP1、TN1) の各々がターンオンされる場合の電圧ノード及び入出力ノード (PADH) の間の抵抗で以って代表され得る。

10

#### 【0082】

CTT方式のターミネーション回路80は、第1電源電圧 (VDDQ) 及び入出力パッド (PADS) の間に連結された第1サブターミネーション回路と入出力パッド (PADH) 及び第2電源電圧 (VSSQ) の間に連結された第2サブターミネーション回路を含む。第1サブターミネーション回路は、ロー電圧によりターンオンされるPMOSトランジスタ (TP2) 及び終端抵抗 (Rtt) を含む。第2サブターミネーション回路は、ハイ電圧によりターンオンされるNMOSトランジスタ (TN2) 及び終端抵抗 (Rtt) を含む。終端抵抗 (Rtt) は省略可能であり、その場合、終端抵抗 (Rtt) はトランジスタ (TP2、TN2) の各々がターンオンされる場合の電圧ノード及び入出力ノード (PADS) の間の抵抗で以って代表され得る。

20

#### 【0083】

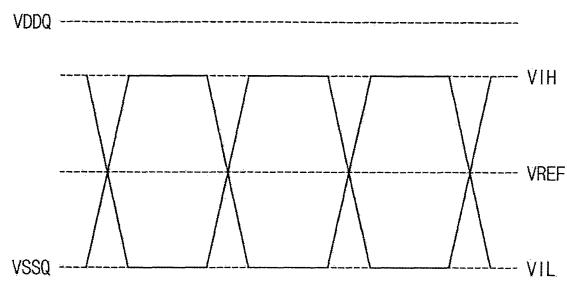

図15のCTT方式のターミネーション回路80を含む場合、入力信号 (SI) のハイ電圧レベル (VIH) とロー電圧レベル (VIL) は図16に図示した通りである。電源電圧 (VSSQ) を0と仮定し、転送ライン (TL) での電圧降下などを無視すれば、入力信号 (SI) のハイ電圧レベル (VIH) とロー電圧レベル (VIL) 及び最適の基準電圧 (VREF) は<数式1>の通り計算できる。

#### 【0084】

<数式1>

$$VIH = VDDQ * (RON + Rtt) / (2 * RON + Rtt)$$

$$VIL = VDDQ * RON / (2 * RON + Rtt)$$

$$VREF = (VIH + VIL) / 2 = VDDQ / 2$$

30

#### 【0085】

図17及び図18は、第1シュード-オーブンドレイン (POD : p s e u d o - o p e n\_d r a i n) ターミネーションを説明するための図である。

#### 【0086】

図17を参照すると、送信装置の送信ドライバ70は内部回路からの送信信号 (ST) に基づいて入出力パッド (PADH) を駆動する。送信装置の入出力パッド (PADH) は転送ライン (TL) を通じて受信装置の入出力パッド (PADS) に連結される。受信装置の入出力パッド (PADS) にはインピーダンスマッチングのために第1のPODターミネーション方式のターミネーション回路81が連結される。受信装置の受信バッファ (BF) は入出力パッド (PADS) を通じて入力される入力信号 (SI) を基準電圧 (VREF) と比較してバッファ信号 (SB) を内部回路に提供する。

40

#### 【0087】

送信ドライバ70は、電源電圧 (VDDQ) 及び入出力パッド (PADH) の間に連結されたプルアップ部と入出力パッド (PADH) 及び接地電圧 (VSSQ) の間に連結されたプルダウン部を含む。プルアップ部は、送信信号 (ST) に応答してスイッチングされるPMOSトランジスタ (TP1) 及びターンオン抵抗 (RON) を含む。プルダウン部は、送信信号 (ST) に応答してスイッチングされるNMOSトランジスタ (TN1) 及びターンオン抵抗 (RON) を含む。ターンオン抵抗 (RON) は省略可能であり、その場合、ターンオン抵抗 (RON) はトランジスタ (TP1、TN1) の各々がターンオン

50

される場合の電圧ノード及び入出力ノード( P A D H )の間の抵抗で以って代表され得る。

【 0 0 8 8 】

第1のP O Dターミネーション方式のターミネーション回路8 1は、ハイ電圧によりターンオンされるN M O Sトランジスタ( T N 2 )及び終端抵抗( R t t )を含む。終端抵抗( R t t )は省略可能であり、その場合、終端抵抗( R t t )はトランジスタ( T N 2 )がターンオンされる場合の電圧ノード及び入出力ノード( P A D S )の間の抵抗で以って代表され得る。

【 0 0 8 9 】

図1 7 の第1のP O Dターミネーション方式のターミネーション回路8 1を含む場合、入力信号( S I )のハイ電圧レベル( V I H )とロー電圧レベル( V I L )は、図1 8 に図示した通りである。接地電圧( V S S Q )を0と仮定し、転送ライン( T L )での電圧降下などを無視すれば、入力信号( S I )のハイ電圧レベル( V I H )とロー電圧レベル( V I L )及び最適の基準電圧( V R E F )は<数式2>の通り計算できる。

10

【 0 0 9 0 】

<数式2>

$$V I H = V D D Q * R t t / ( R O N + R t t )$$

$$V I L = V S S Q = 0$$

$$V R E F = ( V I H + V I L ) / 2 = V D D Q * R t t / ( 2 * ( R O N + R t t ) )$$

【 0 0 9 1 】

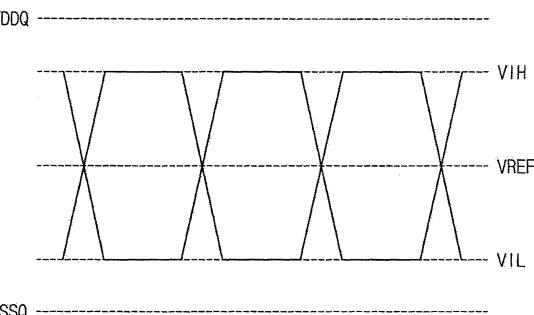

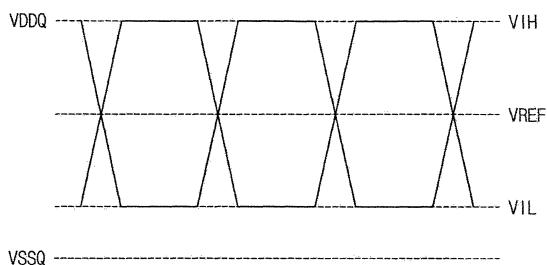

図1 9 及び図2 0 は、第2 P O D ( シュード( 擬似 ) - オープンドレインターミネーション )を説明するための図である。

20

【 0 0 9 2 】

図1 9 を参照すると、送信装置の送信ドライバ7 0は内部回路からの送信信号( S T )に基づいて入出力パッド( P A D H )を駆動する。送信装置の入出力パッド( P A D H )は、転送ライン( T L )を通じて受信装置の入出力パッド( P A D S )に連結される。受信装置の入出力パッド( P A D S )にはインピーダンスマッチングのために第2のP O Dターミネーション方式のターミネーション回路8 2が連結される。受信装置の受信バッファ( B F )は入出力パッド( P A D S )を通じて入力される入力信号( S I )を基準電圧( V R E F )と比較してバッファ信号( S B )を内部回路に提供する。

30

【 0 0 9 3 】

送信ドライバ7 0は電源電圧( V D D Q )及び入出力パッド( P A D H )の間に連結されたプルアップ部と入出力パッド( P A D H )及び接地電圧( V S S Q )の間に連結されたプルダウン部を含む。プルアップ部は、送信信号( S T )に応答してスイッチングされるP M O Sトランジスタ( T P 1 )及びターンオン抵抗( R O N )を含む。プルダウン部は、送信信号( S T )に応答してスイッチングされるN M O Sトランジスタ( T N 1 )及びターンオン抵抗( R O N )を含む。ターンオン抵抗( R O N )は省略可能であり、その場合、ターンオン抵抗( R O N )はトランジスタ( T P 1 、 T N 1 )の各々がターンオンなる場合の電圧ノード及び入出力ノード( P A D H )の間の抵抗で以って代表され得る。

【 0 0 9 4 】

第2のP O Dターミネーション方式のターミネーション回路8 2は、ロー電圧によりターンオンされるP M O Sトランジスタ( T P 2 )及び終端抵抗( R t t )を含む。終端抵抗( R t t )は省略可能であり、その場合、終端抵抗( R t t )はトランジスタ( T P 2 )がターンオンされる場合の電圧ノード及び入出力ノード( P A D S )の間の抵抗で以って代表され得る。

40

【 0 0 9 5 】

図1 9 の第2のP O Dターミネーション方式のターミネーション回路8 2を含む場合、入力信号( S I )のハイ電圧レベル( V I H )とロー電圧レベル( V I L )は、図2 0 に図示した通りである。接地電圧( V S S Q )を0と仮定し、転送ライン( T L )での電圧降下などを無視すれば、入力信号( S I )のハイ電圧レベル( V I H )とロー電圧レベル( V I L )及び最適の基準電圧( V R E F )は<数式3>の通り計算できる。

50

## 【 0 0 9 6 】

&lt; 数式 3 &gt;

$$V_{IH} = V_{DDQ}$$

$$V_{IL} = V_{DDQ} * R_{ON} / (R_{ON} + R_{tt})$$

$$V_{REF} = (V_{IH} + V_{IL}) / 2 = V_{DDQ} * (2R_{ON} + R_{tt}) / (2 * (R_{ON} + R_{tt}))$$

## 【 0 0 9 7 】

このように、本発明のオン・ダイターミネーション回路は多様なターミネーション方式を採用できる。一実施形態において、<数式1>から<数式3>に従う最適の基準電圧( $V_{REF}$ )を求めるためのトレーニング過程が遂行できる。他の実施形態において、メモリコントローラは連続的にイネーブルされているノン・ターゲットメモリランクのオン・ダイターミネーション抵抗を考慮してメモリコントローラのオン・ダイターミネーション抵抗値を調節するか、又はメモリコントローラの転送ドライバのターンオン抵抗値を調節できる。

10

## 【 0 0 9 8 】

図21は、本発明の実施形態に係るオン・ダイターミネーションの制御方法に適用される抵抗設定の一実施形態を示す図である。

## 【 0 0 9 9 】

図21を参照すると、読み出し動作の間中、ターゲットメモリランク( $R_{NK\_TG}$ )のオン・ダイターミネーション回路はディスエーブルされ、ノン・ターゲットメモリランク( $R_{NK\_NT}$ )及びメモリコントローラ( $MC$ )のオン・ダイターミネーション回路は第1抵抗値( $M * R_{tt}$ )を有する。書き込み動作の間中、ターゲットメモリランク( $R_{NK\_TG}$ )は第1抵抗値( $M * R_{tt}$ )と相異する第2抵抗値( $M * R_{tt} + R_{tg}$ )を有し、ノン・ターゲットメモリランク( $R_{NK\_NT}$ )のオン・ダイターミネーション回路は、第1抵抗値( $M * R_{tt}$ )を有し、メモリコントローラ( $MC$ )のオン・ダイターミネーション回路はディスエーブルされる。

20

第1抵抗値( $M * R_{tt}$ )は、前述した初期状態の抵抗値に該当する。例えば、第1抵抗値( $M * R_{tt}$ )は約70であり、第2抵抗値( $M * R_{tt} + R_{tg}$ )は約150である。結果的に、図9を参照して説明したように、書き込み動作を遂行する間中、ターゲットメモリランク( $R_{NK\_TG}$ )のオン・ダイターミネーション回路の抵抗値は第1抵抗値( $M * R_{tt}$ )から第2抵抗値( $M * R_{tt} + R_{tg}$ )に変更できる。

30

## 【 0 1 0 0 】

図22は、本発明の一実施形態に係るCASコマンドを示す図である。

## 【 0 1 0 1 】

図22にはLPDDR5(低パワーダブルデータレート5)標準で予定されたCASコマンドが例示的に図示されている。

## 【 0 1 0 2 】

図22を参照すると、CASコマンドはコマンドアドレス信号(CA0~CA5)の組合せで表現できる。Hは論理ハイレベルを示し、Lは論理ローレベルを示し、EDC\_EN、WS\_WR、WS\_RD、WS\_FAST、DC0~DC3、NT0、NT1、BLはCASコマンドを形成するフィールド値を示す。特に、NT0及びNT1はターミネーションの動的制御のためのフィールド値を示す。

40

## 【 0 1 0 3 】

図22に図示したように、本発明の実施形態に係るオン・ダイターミネーションの静的制御を適用する場合にNT0及びNT1のフィールドは省略され、将来の他の用途に割り当て(RFU、reserved\_for\_future\_use)られる。

## 【 0 1 0 4 】

図23及び図24は、本発明の実施形態に係るオン・ダイターミネーションのためのモードレジスタを説明するための図である。

## 【 0 1 0 5 】

50

オン・ダイターミネーションを制御するための情報は、図4のモードレジスタ412の対応した部分に格納される。例えば、モードレジスタ412の前記対応した部分は図23及び図24に図示したようなモードレジスタ設定(MRSET)を有する。オペランド(OPO~OP7)の一部の値はオン・ダイターミネーション回路の抵抗値に関する情報などを表示できる。

#### 【0106】

図23には図8を参照して説明したように、ターゲットメモリランク及びノン・ターゲットメモリランクのオン・ダイターミネーション回路の抵抗値を共通に制御するための値(ODT)が図示されている。一方、図24には図9を参照して説明したように、ターゲットメモリランクのオン・ダイターミネーション回路の抵抗値を制御するための第1値(TG-ODT)及びノン・ターゲットメモリランクのオン・ダイターミネーション回路の抵抗値を制御するための第2値(NT-ODT)が図示されている。

モードレジスタ412に格納された値(ODT、TG-ODT、NT-ODT)は、モードレジスタ書き込み動作を通じてメモリコントローラから提供される。このようなモードレジスタ412に格納された値(ODT、TG-ODT、NT-ODT)に基づいて前述したストレングス(strength)コード(SCD)が提供される。

#### 【0107】

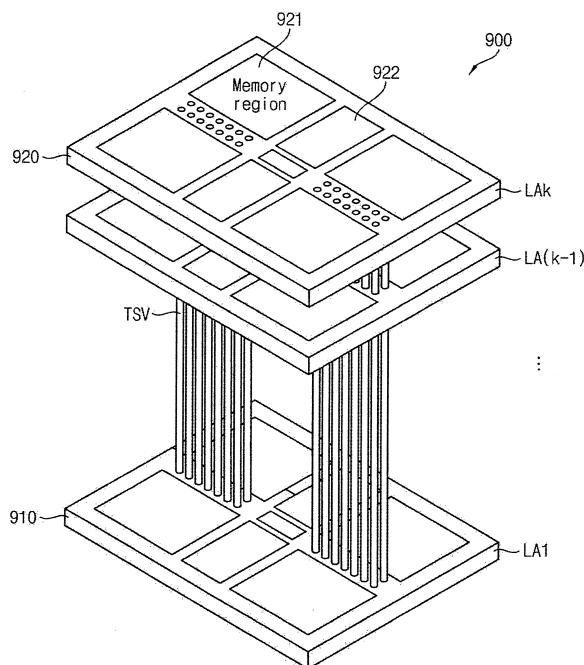

図25は、本発明の一実施形態に係る積層型メモリ装置の構造を示す図である。

#### 【0108】

図25に図示したように、半導体メモリ装置900は多数の半導体ダイ又は半導体レイヤ(LA1~LAk、kは3以上の自然数)を備える。最も下に位置する半導体レイヤ(LA1)はマスタレイヤであり、残りの半導体レイヤ(LA2~LAk)はスレーブレイヤであると想定される。スレーブレイヤは前述したような複数のメモリランクを形成する。

#### 【0109】

半導体レイヤ(LA1~LAk)は貫通ピア(TSV)を通じて信号を互いに送受信し、マスターレイヤ(LA1)はチップ入出力パッド部を通じて外部のメモリコントローラ(図示せず)と通信する。前記チップ入出力パッド部はマスタレイヤ(LA1)の下面に形成されるか、又はベース基板(図示せず)に形成される。

#### 【0110】

第1半導体レイヤ(LA1)910乃至第k半導体レイヤ920は、各々メモリセルアレイ領域921を駆動するための各種の周辺回路922を備える。例えば、周辺回路922は各メモリセルアレイ領域921のワードラインを駆動するためのロードライバ(X-Driver)と、各メモリ領域のビットラインを駆動するためのカラムドライバ(Y-Driver)と、データの入出力を制御するためのデータ入出力部、外部からコマンド(CMD)の入力を受けてバッファリングするコマンドバッファと、外部からアドレスの入力を受けてバッファリングするアドレスバッファなどを備える。

#### 【0111】

第1半導体レイヤ910は、制御ロジックをさらに含む。制御ロジックはメモリコントローラ(図示せず)から提供されるコマンド及びアドレス信号に基づいてメモリ領域921に対するアクセスを制御し、メモリ領域921をアクセスするための制御信号を生成する。

#### 【0112】

図26は、本発明の実施形態に係るメモリ装置をモバイルシステムに応用した例を示すブロック図である。

#### 【0113】

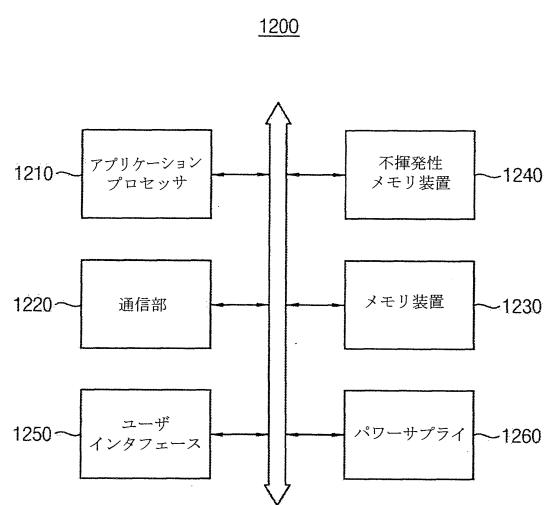

図26を参照すると、モバイルシステム1200は、アプリケーションプロセッサ1210、通信(Connectivity)部1220、メモリ装置1230、不揮発性メモリ装置1240、ユーザインターフェース1250、及びパワーサプライ1260を含む。

#### 【0114】

アプリケーションプロセッサ1210は、インターネットブラウザ、ゲーム、動映像などを提供するアプリケーションを実行する。通信部1220は、外部装置との無線通信又は

10

20

30

40

50

有線通信を遂行する。メモリ装置 1230 は、アプリケーションプロセッサ 1210 により処理されるデータを格納するか、又は動作メモリ (Working\_Memory) として作動する。

例えば、メモリ装置 1230 は DDR\_SDRAM、LPDDR\_SDRAM、GDDR\_SDRAM、RDRAMなどの動的ランダムアクセスメモリである。

不揮発性メモリ装置 1240 は、モバイルシステム 1200 をブーティングするためのポートイメージを格納する。ユーザインターフェース 1250 は、キーパッド、タッチスクリーンのような 1 つ以上の入力装置、及び / 又はスピーカー、ディスプレイ装置のような 1 つ以上の出力装置を含む。パワーサプライ 1260 は、モバイルシステム 1200 の動作電圧を供給する。また、実施形態によって、モバイルシステム 1200 はカメライメージプロセッサ (Camera\_Image\_Processor; CIS) をさらに含み、メモリカード (Memory\_Card)、ソリッドステートドライブ (Solid\_State\_Drive; SSD)、ハードディスクドライブ (Hard\_Disk\_Drive; HDD)、CD-ROMなどの格納装置をさらに含む。10

#### 【0115】

メモリ装置 1230 及び / 又は不揮発性メモリ装置 1240 は、図 1 から図 24 を参照して前述したような本発明の実施形態に係るオン - ダイターミネーションの制御方法を遂行するための構成を有することができる。

#### 【0116】

以上、説明したように、本発明の実施形態に係るマルチ - ランクシステムのオン - ダイターミネーションの制御方法、これを遂行する装置及びシステムは、ターゲットメモリランク及びノン - ターゲットメモリランクのオン - ダイターミネーション回路のイネーブルされた初期状態を維持し、かつ読み出し動作の対象となる読み出しターゲットメモリランクのオン - ダイターミネーション回路のみをディスエーブルする静的制御を通じて消費電力を減少し、信号品位を向上することができる。20

#### 【産業上の利用可能性】

#### 【0117】

本発明の実施形態は、メモリ装置及びこれを含むシステムに有效地に適用できる。

特に、本発明の実施形態は、メモリカード、ソリッドステートドライブ (Solid\_State\_Drive; SSD)、コンピュータ (computer)、ノートブック (laptop)、携帯電話 (cellular)、スマートフォン (smartphone)、MP3プレーヤ、PDA (Personal\_Digital\_Assistants)、PMP (Portable\_Multimedia\_Player)、デジタルTV、デジタルカメラ、ポータブルゲームコンソール (portable\_game\_console)などの電子機器にさらに有效地に適用できる。30

#### 【0118】

以上、本発明を好ましい実施形態を参考して説明したが、該当技術分野の熟練した当業者は以下の特許請求範囲に記載された本発明の思想及び領域から外れない範囲内で本発明を多様に修正及び変更できると理解されよう。

#### 【0119】

10 マルチ - ランクシステム

20 メモリコントローラ

30 メモリサブシステム

70 送信ドライバ

80 CTT 方式のターミネーション回路

81 第 1 の POD ターミネーション方式のターミネーション回路

82 第 2 の POD ターミネーション方式のターミネーション回路

300 オン - ダイターミネーション (ODT) 回路

310 終端制御部

330 ブラップ終端制御部

10

20

30

40

50

|                          |                                  |    |

|--------------------------|----------------------------------|----|

| 3 3 4、 3 3 5、 3 3 6      | 第 1、 第 2、 第 3 選択器                |    |

| 3 4 0                    | プルダウン終端制御部                       |    |

| 3 4 4、 3 4 5、 3 4 6      | 第 4、 第 5、 第 6 選択器                |    |

| 3 5 0                    | 終端抵抗部                            |    |

| 3 6 0                    | プルアップ終端抵抗部                       |    |

| 3 6 1、 3 6 2、 3 6 3      | 第 1、 第 2、 第 3 P M O S ドラッグ       |    |

| 3 7 0                    | プルダウン終端抵抗部                       |    |

| 3 7 1、 3 7 2、 3 7 3      | 第 1、 第 2、 第 3 N M O S ドラッグ       |    |

| 4 0 0                    | メモリ装置                            |    |

| 4 1 0                    | 制御ロジック                           | 10 |

| 4 1 1                    | コマンドデコーダ                         |    |

| 4 1 2                    | モードレジスタ                          |    |

| 4 2 0                    | アドレスレジスタ                         |    |

| 4 3 0                    | バンク制御ロジック                        |    |

| 4 4 0                    | ロウアドレスマルチプレクサ ( R A _ M U X )    |    |

| 4 4 5                    | リフレッシュカウンター                      |    |

| 4 6 0                    | ロウデコーダ                           |    |

| 4 6 0 a ~ 4 6 0 h        | バンクロウデコーダ                        |    |

| 4 7 0、 4 7 0 a ~ 4 7 0 h | カラムデコーダ                          |    |

| 4 8 0                    | メモリセルアレイ                         | 20 |

| 4 8 0 a ~ 4 8 0 h        | バンクアレイ                           |    |

| 4 8 5                    | センスアンプ部                          |    |

| 4 8 5 a ~ 4 8 5 h        | センスアンプ                           |    |

| 4 9 0                    | 入出力ゲーティング回路                      |    |

| 5 0 0                    | データ入出力回路                         |    |

| 6 0 0                    | データ入出力ピン                         |    |

| 7 1 0                    | 送信ドライバ ( D R )                   |    |

| 7 2 0                    | 受信バッファ ( B F )                   |    |

| 9 0 0                    | 半導体メモリ装置                         |    |

| 9 1 0                    | 第 1 半導体レイヤ、マスタレイヤ ( L A 1 )      | 30 |

| 9 2 0                    | 第 k 半導体レイヤ ( L A k )             |    |

| 9 2 1                    | メモリセルアレイ領域                       |    |

| 9 2 2                    | 周辺回路                             |    |

| 1 2 0 0                  | モバイルシステム                         |    |

| 1 2 1 0                  | アプリケーションプロセッサ                    |    |

| 1 2 2 0                  | 通信 ( C o n n e c t i v i t y ) 部 |    |

| 1 2 3 0                  | メモリ装置                            |    |

| 1 2 4 0                  | 不揮発性メモリ装置                        |    |

| 1 2 5 0                  | ユーザインターフェース                      |    |

| 1 2 6 0                  | パワーサプライ                          | 40 |

【図面】

【図 1】

【図 2】

10

20

【図 3】

10

【図 4】

30

40

50

【図5】

【 四 6 】

【 四 7 】

【 四 8 】

10

20

30

40

50

【図 9】

【図 10】

10

20

30

40

【図 11】

【図 12】

|      | ターゲットメモリランク RNK_TG | ノンターゲットメモリランク RNK_NT | メモリコントローラ MC |

|------|--------------------|----------------------|--------------|

| 読み出し | 不活性化               | M*Rtt                | M*Rtt        |

| 書き込み | M*Rtt              | M*Rtt                | 不活性化         |

50

【図 1 3】

【図 1 4】

10

【図 1 5】

【図 1 6】

20

30

40

50

【図 17】

【図 18】

10

【図 19】

【図 20】

30

40

50

【図 2 1】

|      |                           |                             |                 |

|------|---------------------------|-----------------------------|-----------------|

|      | ターゲット<br>メモリランク<br>RNK_TG | ノンターゲット<br>メモリランク<br>RNK_NT | メモリコントローラ<br>MC |

| 読み出し | 不活性化                      | M*Rtt                       | M*Rtt           |

| 書き込み | M*Rtt+Rtg                 | M*Rtt                       | 不活性化            |

【図 2 2】

|     |     |     |     |          |          |       |         |

|-----|-----|-----|-----|----------|----------|-------|---------|

| CMD | CA0 | CA1 | CA2 | CA3      | CA4      | CA5   | CA6     |

| CAS | L   | L   | H   | EDC_EN   | WS_MR    | WS_RD | WS_FAST |

| DC0 | DC1 | DC2 | DC3 | NT0->RFU | NT1->RFU | BL    |         |

10

20

30

【図 2 3】

| MRSET | OP7 | OP6 | OP5 | OP4 | OP3 | OP2 | OP1 | OP0 |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

|       | RFU |     |     |     | ODT |     |     |     |

【図 2 4】

| MRSET | OP7 | OP6 | OP5 | OP4 | OP3    | OP2 | OP1 | OP0 |

|-------|-----|-----|-----|-----|--------|-----|-----|-----|

|       | RFU |     |     |     | TG-ODT |     |     |     |

40

50

【図25】

【図26】

10

20

30

40

50

---

フロントページの続き

(72)発明者 金 始 弘

大韓民国 京畿道 華城市 東灘大路 示範ギル 19 1408 - 2404

(72)発明者 李 起 ギヨ

大韓民国 ソウル 松坡区 オリンピック路 99 113 - 2701

(72)発明者 崔 ジョン 煥

大韓民国 京畿道 華城市 東灘文化センタ路 39 - 1 320 - 202

(72)発明者 河 慶 淑

大韓民国 京畿道 華城市 東灘スプソク路 68 873 - 202

審査官 後藤 彰

(56)参考文献 特開2013 - 069399 (JP, A)

特表2013 - 534014 (JP, A)

特開2010 - 170296 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

G 11 C 7 / 10

G 06 F 12 / 00