RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 465 358**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21) **N° 80 18856**

-

- (54) Dispositif de commande de deux moteurs pas à pas dans une pièce d'horlogerie électronique.

- (51) Classification internationale (Int. Cl. 3). H 02 P 8/00; G 04 C 3/14.

- (22) Date de dépôt..... 29 août 1980.

- (33) (32) (31) Priorité revendiquée : *Suisse, 7 septembre 1979, n° 8 099/79-8.*

- (41) Date de la mise à la disposition du

public de la demande ..... B.O.P.I. — « Listes » n° 12 du 20-3-1981.

-

- (71) Déposant : EBAUCHES, société anonyme, résidant en Suisse.

- (72) Invention de : Fridolin Wiget.

- (73) Titulaire : *Idem* (71)

- (74) Mandataire : SEFEA Département Propriété Industrielle ASUAG,

15, rue de Valeury, boîte postale 57, 74103 Annemasse.

-

- 1 -

La présente invention concerne un dispositif de commande non simultanée, par impulsions électriques polarisées, de deux bobines de moteur pas à pas dans une pièce d'horlogerie électronique.

5 Dans le secteur horloger, il est connu d'utiliser des moteurs pas à pas pour actionner par l'intermédiaire de trains d'engrenages les aiguilles ou d'autres éléments d'affichage, tels que ceux indiquant la date. Un moteur pas à pas de ce type est généralement alimenté par

10 des impulsions électriques polarisées ayant une fréquence déterminée. Cette fréquence est obtenue à partir d'un oscillateur à quartz suivi de plusieurs diviseurs de fréquences.

Le brevet US 3 742 697 décrit un dispositif délivrant des impulsions électriques polarisées, comportant deux branches connectées en parallèle aux bornes + et - de la pile et formées chacune de deux transistors qui travaillent en mode saturé - bloqué. Le moteur est connecté entre les points de liaison des transistors de chaque branche.

20

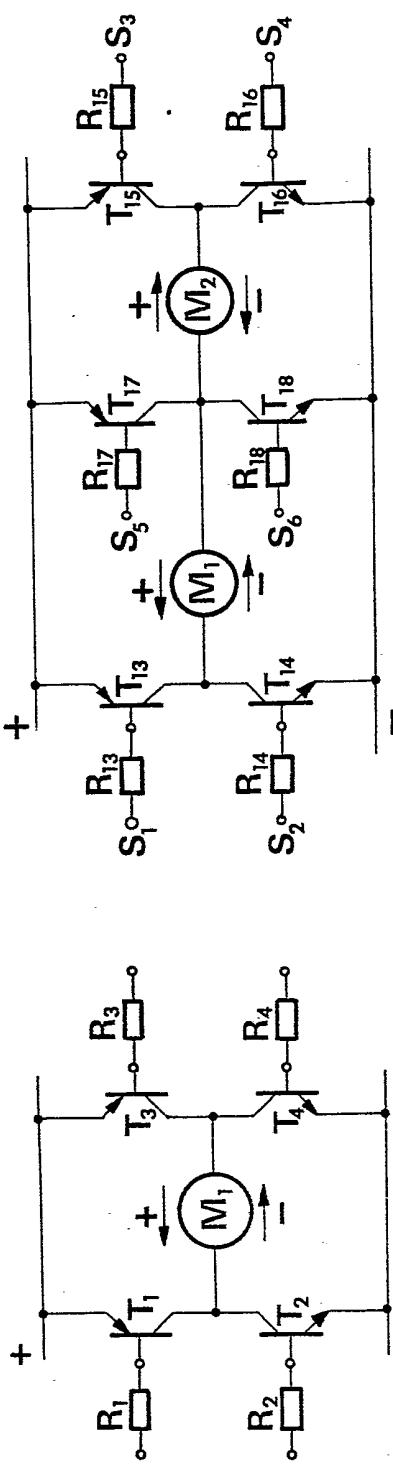

La figure 1 illustre un tel montage en pont. Les transistors  $T_1$  à  $T_4$  sont saturés alternativement deux par deux ( $T_1-T_4$  et  $T_3-T_2$ ) par des impulsions successives à une fréquence déterminée au moyen d'un circuit logique (non représenté) commandant les bases des transistors  $T_1$  à  $T_4$  à travers les résistances de limitation de courant  $R_1$  à  $R_4$ . Ainsi, le moteur  $M_1$  est soumis successivement et alternativement à des impulsions positives et négatives. Sur cette figure, comme pour les autres figures, les flèches + et - indiquent schématiquement le sens du courant dans l'enroulement du moteur, ou autrement dit, si une impulsion polarisée positivement ou négativement lui est appliquée.

25

30

Il est également connu d'utiliser deux moteurs pas à pas dans une même montre. Dans un tel cas, un des moteurs peut actionner, par exemple, l'aiguille des secondes et l'aiguille des minutes, tandis que l'autre actionne l'aiguille des heures et l'indicateur de date. Cet

35

- 2 -

agencement permet de munir la montre de moyens simples à la fois dans leur construction et dans leur utilisation pour permettre la correction des données qu'elle affiche et un changement aisément des fuseaux horaires, ou encore, par 5 exemple, l'incorporation à la montre de la fonction chronographe. Le brevet français 2 394 840 décrit un exemple d'une telle montre comportant deux moteurs pas à pas.

Si, comme représenté à la figure 2, le circuit de la figure 1 est utilisé dans une montre à deux moteurs 10  $M_1$  et  $M_2$ , huit transistors  $T_5$  à  $T_{12}$  et huit résistances  $R_5$  à  $R_{12}$  sont alors nécessaires et quatre bornes doivent être prévues sur le circuit intégré pour sa liaison avec ces moteurs.

Or, ces transistors sont des transistors de 15 puissance qui, contrairement aux circuits logiques qui les commandent, utilisent une grande place sur la plaquette du circuit intégré. Une telle solution va donc à l'encontre d'une miniaturisation croissante et d'une diminution du coût de fabrication dans ce domaine. Une réduction du nombre 20 des bornes du circuit intégré est en outre souhaitable pour améliorer sa fiabilité, et également pour diminuer son prix de revient.

Le but de cette invention est de fournir un dispositif de commande de deux moteurs pas à pas utilisant un 25 nombre réduit de transistors et permettant de diminuer le nombre de bornes et le prix de revient du circuit dans lequel ces transistors sont intégrés.

L'invention a donc pour objet un dispositif de commande tel que défini dans la revendication 1.

30 Les figures suivantes illustrent, à titre d'exemple, certaines formes d'exécution de l'invention.

La figure 1 illustre un circuit de commande d'un moteur pas à pas selon l'état de la technique.

35 La figure 2 illustre une application du circuit de la figure 1 à un dispositif comportant deux moteurs pas à pas.

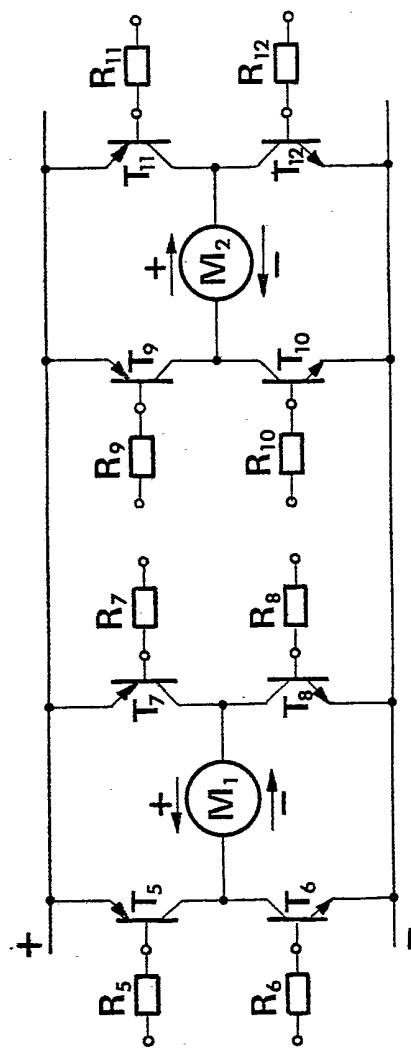

La figure 3 représente une première forme d'exé-

- 3 -

cution du dispositif selon l'invention.

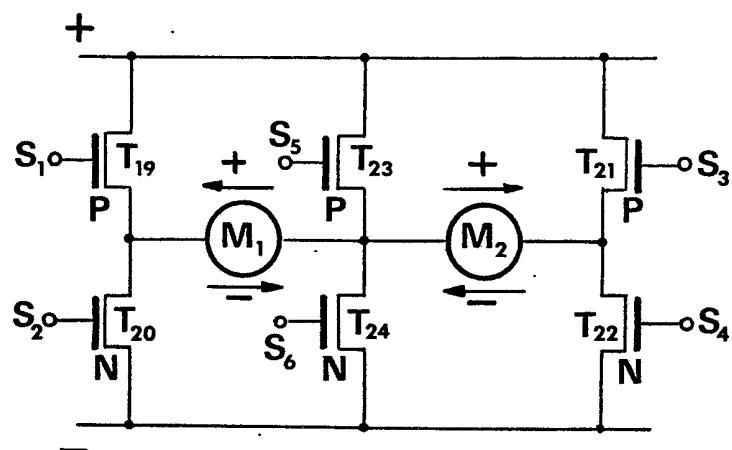

La figure 4 représente une deuxième forme d'exécution du dispositif selon l'invention.

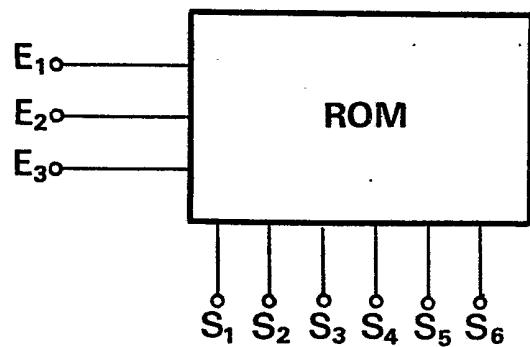

La figure 5 représente schématiquement une mémoire ROM utilisable avec le dispositif selon l'invention.

Les figures 1 et 2 ont déjà été décrites dans l'introduction.

Le dispositif de la figure 3 comporte trois branches connectées en parallèle aux bornes + et - d'une source d'énergie électrique non représentée. Chaque branche est formée d'un transistor PNP et d'un transistor NPN dont les émetteurs sont reliés, respectivement, aux bornes + et - de la source, et dont les collecteurs sont réunis. Ces transistors PNP sont désignés par les références  $T_{13}$ ,  $T_{15}$  et  $T_{17}$  et ces transistors NPN par  $T_{14}$ ,  $T_{16}$  et  $T_{18}$ . La bobine du moteur  $M_1$  est branchée entre les collecteurs des transistors  $T_{13}$  et  $T_{14}$  d'une part et les collecteurs des transistors  $T_{17}$  et  $T_{18}$  d'autre part. De même, la bobine du moteur  $M_2$  est branchée entre les collecteurs des transistors  $T_{15}$  et  $T_{16}$  d'une part, et également les collecteurs des transistors  $T_{17}$  et  $T_{18}$  d'autre part.

La figure 4 illustre une variante de réalisation qui ne diffère de celle de la figure 3 que par le fait que les transistors PNP ont été remplacés par des transistors à effet de champ MOS à canal P désignés par  $T_{19}$ ,  $T_{21}$  et  $T_{23}$ , et les transistors NPN par des transistors à effet de champ MOS à canal N, désignés par  $T_{20}$ ,  $T_{22}$  et  $T_{24}$ .

Dans les deux variantes décrites, comme les deux moteurs  $M_1$  et  $M_2$  ne doivent pas fonctionner simultanément, les transistors  $T_{17}$  et  $T_{18}$ , respectivement  $T_{23}$  et  $T_{24}$ , qui sont communs aux deux moteurs, peuvent avoir les mêmes dimensions, dans le circuit intégré, que les autres transistors  $T_{13}$  à  $T_{16}$ , respectivement  $T_{19}$  à  $T_{22}$ . En outre, une seule borne est nécessaire pour relier le point commun des transistors  $T_{17}$  et  $T_{18}$ , respectivement  $T_{23}$  et  $T_{24}$ , avec l'extérieur du circuit intégré.

Les bases des transistors  $T_{13}$  à  $T_{18}$  ou les élec-

- 4 -

trodes de commande des transistors  $T_{19}$  à  $T_{24}$  reçoivent, d'un circuit de commande dont un exemple sera décrit plus loin, des signaux de durée et de polarité définies de manière à bloquer ou à rendre conducteurs les transistors 5 voulus pour faire tourner l'un ou l'autre des moteurs dans un sens ou dans l'autre.

Ainsi, par exemple un signal logique "0" appliquée aux transistors  $T_{13}$ ,  $T_{15}$ ,  $T_{17}$ ,  $T_{19}$ ,  $T_{21}$  ou  $T_{23}$  provoque leur conduction, alors qu'un signal logique "1" provoque leur blocage. Les transistors  $T_{14}$ ,  $T_{16}$ ,  $T_{18}$ ,  $T_{20}$ ,  $T_{22}$  et  $T_{24}$ , par contre, sont rendus conducteurs par un signal logique "1" et sont bloqués par un signal logique "0". 10 Comme c'est le cas en général dans les circuits logiques, on entend ici par signal logique "0", respectivement "1", 15 un signal ayant la même tension que le pôle négatif, respectivement positif, de la source d'alimentation.

Pour faire passer dans le moteur  $M_1$  un courant positif, dans le sens de la flèche désignée par +, il faut rendre conducteurs les transistors  $T_{14}$  et  $T_{17}$ , respectivement  $T_{20}$  et  $T_{23}$ . Pour faire passer un courant négatif dans 20 le même moteur, il faut rendre conducteur les transistors  $T_{13}$  et  $T_{18}$ , respectivement  $T_{19}$  et  $T_{24}$ .

De même, pour faire passer un courant positif dans le moteur  $M_2$ , il faut rendre conducteur les transistors  $T_{16}$  et  $T_{17}$ , respectivement  $T_{22}$  et  $T_{23}$  et pour faire passer dans le même moteur un courant négatif, il faut rendre conducteurs les transistors  $T_{15}$  et  $T_{18}$ , respectivement  $T_{21}$  et  $T_{24}$ . 25

Les signaux nécessaires peuvent être fournis, par 30 exemple, par une mémoire morte (ROM) telle que celle qui est représentée à la figure 5.

Cette mémoire morte comporte six sorties,  $S_1$  à  $S_6$ , qui sont les sorties de données, et qui sont destinées à être reliées, à travers les résistances  $R_{13}$  à  $R_{18}$ , aux bases des transistors  $T_{13}$  à  $T_{18}$  ou, directement, aux électrodes de commande des transistors  $T_{19}$  à  $T_{24}$ . Elle comporte trois entrées désignées par  $E_1$ ,  $E_2$  et  $E_3$ , qui sont les 35

- 5 -

entrées d'adresse, et qui reçoivent d'un circuit de commande non représenté des signaux logiques dont chaque combinaison correspond à un état de blocage, de court-circuit, ou de passage d'un courant positif ou négatif dans l'un 5 ou dans l'autre moteur.

Ce circuit de commande n'est pas représenté car son schéma dépend de la fonction qui est assignée à chacun des moteurs et des moyens automatiques ou manuels qui sont prévus pour les commander. Il comprend en tout cas une 10 base de temps et des circuits logiques qui élaborent, en fonction des signaux délivrés par la base de temps et par les moyens de commande, les signaux logiques qui doivent être appliqués à chaque instant, aux entrées de E1 à E3 de la mémoire morte.

15 Le tableau ci-dessous résume le fonctionnement du circuit :

|    | ETATS          |                | ENTREES        |                |                | SORTIES        |                |                |                |                |                |   |

|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---|

|    | M <sub>1</sub> | M <sub>2</sub> | E <sub>1</sub> | E <sub>2</sub> | E <sub>3</sub> | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | S <sub>5</sub> | S <sub>6</sub> |   |

| 20 | 1              | OFF            | OFF            | 0              | 0              | 0              | 1              | 0              | 1              | 0              | 1              | 0 |

|    | 2              | +              | OFF            | 0              | 1              | 0              | 1              | 1              | 1              | 0              | 0              | 0 |

|    | 3              | -              | OFF            | 0              | 0              | 1              | 0              | 0              | 1              | 0              | 1              | 1 |

|    | 4              | CC             | OFF            | 0              | 1              | 1              | 1              | 1              | 1              | 0              | 1              | 1 |

|    | 5              | OFF            | +              | 1              | 1              | 0              | 1              | 0              | 1              | 1              | 0              | 0 |

|    | 6              | OFF            | -              | 1              | 0              | 1              | 1              | 0              | 0              | 0              | 1              | 1 |

|    | 7              | OFF            | CC             | 1              | 1              | 1              | 1              | 0              | 1              | 1              | 1              | 1 |

|    | 8              | CC             | CC             | 1              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 1 |

Dans ce tableau, les deux premières colonnes intitulées, ensemble, "Etats", indiquent les différentes combinaisons d'état possibles des deux moteurs M<sub>1</sub> et M<sub>2</sub>. Dans ces colonnes, "OFF" signifie que le moteur désigné en tête est hors service, "CC" que sa bobine est en court-circuit (la bobine d'un moteur pas à pas est généralement court-circuitée à la fin de chaque impulsion motrice pour diminuer la durée des oscillations du rotor autour de sa position d'équilibre), "+" et "-" qu'un courant positif, res-

- 6 -

pectivement négatif, le traverse.

Les trois colonnes intitulées "Entrées" donnent un exemple des combinaisons de trois signaux logiques délivrés par le circuit de commande pour chacun des huit 5 états possibles répertoriés dans les deux première colonnes, signaux logiques qui sont appliqués aux entrées  $E_1$  à  $E_3$  de la mémoire morte ROM.

Les six dernières colonnes intitulées "Sorties" indiquent les états logiques que prennent les sorties  $S_1$  10 à  $S_6$  de la mémoire morte pour chacune de ces combinaisons des états logiques d'entrée. On peut noter que les combinaisons des états logiques des sorties  $S_1$  à  $S_6$ , qui sont les seules qui peuvent se présenter, sont telles que les transistors  $T_{13}$  à  $T_{18}$ , respectivement  $T_{19}$  à  $T_{24}$ , ne conduisent que dans les conditions voulues. Les moteurs  $M_1$  15 et  $M_2$  ne reçoivent ainsi jamais de courant simultanément, et les deux transistors d'une même branche ( $T_{13}$  et  $T_{14}$ ,  $T_{15}$  et  $T_{16}$ , etc) ne conduisent jamais en même temps.

Il est évident que le présent dispositif pour- 20 rait également être utilisé pour commander un moteur unique muni de deux enroulements, tel que le moteur pas à pas à deux sens décrit dans le brevet US No 4 144 467.

- 7 -

REVENDICATIONS

1. Dispositif de commande non simultanée, par impulsions électriques polarisées, de deux bobines de moteur pas à pas dans une pièce d'horlogerie électronique, caractérisé en ce qu'il comporte trois branches connectées en parallèle aux bornes d'une source d'énergie électrique et respectivement formées de deux transistors en série qui peuvent être commandés indépendamment pour déterminer le fonctionnement sélectif des bobines et la polarité desdites impulsions, lesdites bobines étant connectées, d'une part, toutes les deux au point de liaison des transistors de l'une des branches et, d'autre part, respectivement aux points de liaison des transistors des deux autres branches.

2. Dispositif selon la revendication 1, caractérisé en ce que les transistors sont à effet de champ, chaque branche comportant un transistor à effet de champ à canal P et un transistor à effet de champ à canal N.

FIG. 1

FIG. 2

FIG. 3

2/2

**FIG.4****FIG.5**