(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6677613号

(P6677613)

(45) 発行日 令和2年4月8日(2020.4.8)

(24) 登録日 令和2年3月17日(2020.3.17)

(51) Int.Cl.

F 1

|                   |                  |            |      |

|-------------------|------------------|------------|------|

| <b>H01L 29/78</b> | <b>(2006.01)</b> | H01L 29/78 | 652Q |

| <b>H01L 29/06</b> | <b>(2006.01)</b> | H01L 29/06 | 301F |

| <b>H01L 29/12</b> | <b>(2006.01)</b> | H01L 29/78 | 652P |

|                   |                  | H01L 29/78 | 652D |

|                   |                  | H01L 29/78 | 652K |

請求項の数 5 (全 19 頁) 最終頁に続く

(21) 出願番号

特願2016-180766 (P2016-180766)

(22) 出願日

平成28年9月15日(2016.9.15)

(65) 公開番号

特開2018-46201 (P2018-46201A)

(43) 公開日

平成30年3月22日(2018.3.22)

審査請求日

平成30年8月30日(2018.8.30)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(73) 特許権者 317011920

東芝デバイス&amp;ストレージ株式会社

東京都港区芝浦一丁目1番1号

(74) 代理人 100108062

弁理士 日向寺 雅彦

(72) 発明者 下村 紗矢

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 加藤 浩朗

東京都港区芝浦一丁目1番1号 株式会社

東芝内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1導電形の第1半導体領域と、

前記第1半導体領域の上に選択的に設けられた第2導電形の第2半導体領域と、

前記第2半導体領域の上に選択的に設けられた第1導電形の第3半導体領域と、

前記第1半導体領域中および前記第2半導体領域中に第1絶縁部を介して設けられ、第1方向に延び、前記第1方向と交差する第2方向において複数設けられたゲート電極と、

前記第3半導体領域の上に設けられ、前記第3半導体領域と電気的に接続された第1電極と、

前記第1半導体領域中において前記複数のゲート電極と離間し、前記第2方向に延び、前記第1方向において複数設けられた第2絶縁部と、

前記第1方向に延びる第1絶縁部分を有し、前記第1絶縁部分が前記第2方向において前記複数のゲート電極と前記複数の第2絶縁部との間に位置し、前記第1半導体領域中において前記複数のゲート電極および前記複数の第2絶縁部と離間した第3絶縁部と、

前記複数の第2絶縁部および前記第3絶縁部の上に設けられ、前記複数のゲート電極と電気的に接続された第2電極と、

を備えた半導体装置。

## 【請求項 2】

第1導電形の第1半導体領域と、

前記第1半導体領域の上に選択的に設けられた第2導電形の第2半導体領域と、

10

20

前記第2半導体領域の上に選択的に設けられた第1導電形の第3半導体領域と、

前記第1半導体領域中および前記第2半導体領域中に第1絶縁部を介して設けられ、第

1方向に延び、前記第1方向と交差する第2方向において複数設けられたゲート電極と、

前記第3半導体領域の上に設けられ、前記第3半導体領域と電気的に接続された第1電

極と、

前記第1半導体領域中において前記複数のゲート電極と離間し、前記第2方向に延び、

前記第1方向において複数設けられた第2絶縁部と、

前記第1方向に延びる第1絶縁部分および前記第2方向に延びる第2絶縁部分を有し、

前記第1絶縁部分が前記第2方向において前記複数のゲート電極の一部と前記複数の第2

絶縁部との間に位置し、前記第2絶縁部分が前記第1方向において前記複数のゲート電極

の他の一部と前記複数の第2絶縁部との間に位置し、前記第1半導体領域中において前記

複数のゲート電極および前記複数の第2絶縁部と離間した第3絶縁部と、 10

前記複数の第2絶縁部および前記第3絶縁部の上に設けられ、前記複数のゲート電極と

電気的に接続された第2電極と、

を備えた半導体装置。

#### 【請求項3】

第1導電形の第1半導体領域と、

前記第1半導体領域の上に選択的に設けられた第2導電形の第2半導体領域と、

前記第2半導体領域の上に選択的に設けられた第1導電形の第3半導体領域と、

前記第1半導体領域中および前記第2半導体領域中に第1絶縁部を介して設けられ、第

1方向に延びるゲート電極と、 20

前記第3半導体領域の上に設けられ、前記第3半導体領域と電気的に接続された第1電

極と、

前記第1半導体領域中において前記ゲート電極と離間し、前記第1方向と交差する第2

方向に延びる第2絶縁部と、

前記第1方向に延びる第1絶縁部分を有し、前記第1絶縁部分が前記第2方向において

前記ゲート電極と前記第2絶縁部との間に位置し、前記第1半導体領域中において前記ゲ

ート電極および前記第2絶縁部と離間した第3絶縁部と、

前記第2絶縁部および前記第3絶縁部の上に設けられ、前記ゲート電極と電気的に接続

された第2電極と、 30

前記第2絶縁部中に設けられ、前記第2方向に延び、前記第1電極および前記第2電極

と電気的に分離された第1導電部と、

前記第1絶縁部分中を前記第1方向に延びる第1導電部分を有し、前記第3絶縁部中に

設けられ、前記第1電極および前記第2電極と電気的に分離された第2導電部と、

を備えた半導体装置。

#### 【請求項4】

第1導電形の第1半導体領域と、

前記第1半導体領域の上に選択的に設けられた第2導電形の第2半導体領域と、

前記第2半導体領域の上に選択的に設けられた第1導電形の第3半導体領域と、

前記第1半導体領域中および前記第2半導体領域中に第1絶縁部を介して設けられ、第

1方向に延び、前記第1方向と交差する第2方向において複数設けられたゲート電極と、 40

前記第3半導体領域の上に設けられ、前記第3半導体領域と電気的に接続された第1電

極と、

前記第1半導体領域中において前記複数のゲート電極と離間し、前記第1方向に延び、

前記第2方向において複数設けられた第2絶縁部と、

前記第1方向に延びる第1絶縁部分と前記第2方向に延びる第2絶縁部分を有し、前記

第1絶縁部分が前記第2方向において前記複数のゲート電極の一部と前記複数の第2絶縁

部との間に位置し、前記第2絶縁部分が前記第1方向において前記複数のゲート電極の他

の一部と前記複数の第2絶縁部との間に位置し、前記第1半導体領域中において前記複数

のゲート電極および前記複数の第2絶縁部と離間した第3絶縁部と、 50

前記複数の第2絶縁部および前記第3絶縁部の上に設けられ、前記複数のゲート電極と電気的に接続された第2電極と、

を備えた半導体装置。

【請求項5】

第1導電形の第1半導体領域と、

前記第1半導体領域の上に選択的に設けられた第2導電形の第2半導体領域と、

前記第2半導体領域の上に選択的に設けられた第1導電形の第3半導体領域と、

前記第1半導体領域中および前記第2半導体領域中に第1絶縁部を介して設けられたゲート電極と、

前記第3半導体領域の上に設けられ、前記第3半導体領域と電気的に接続された第1電極と、

前記第1半導体領域中において前記ゲート電極と離間し、前記第1半導体領域の一部を囲む環状の第2絶縁部と、

前記第2絶縁部の上に設けられ、前記ゲート電極と電気的に接続された第2電極と、

前記第2絶縁部と離間して前記第1半導体領域中に設けられ、前記第2絶縁部の内側に位置し、前記第1半導体領域の一部を囲む環状の第3絶縁部と、

前記第2絶縁部中に設けられ、前記第1電極および前記第2電極と電気的に分離された環状の第1導電部と、

前記第3絶縁部中に設けられ、前記第1電極および前記第2電極と電気的に分離された環状の第2導電部と、

を備えた半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置に関する。

【背景技術】

【0002】

MOSFET (Metal Oxide Semiconductor Field Effect Transistor)などの半導体装置は、寄生トランジスタを有する。この寄生トランジスタは、動作し難いことが望ましい。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特許第5701913号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明が解決しようとする課題は、寄生トランジスタの動作を抑制できる半導体装置を提供することである。

【課題を解決するための手段】

【0005】

実施形態に係る半導体装置は、第1導電形の第1半導体領域と、第2導電形の第2半導体領域と、第1導電形の第3半導体領域と、ゲート電極と、第1電極と、第2絶縁部と、第3絶縁部と、第2電極と、を有する。前記第2半導体領域は、前記第1半導体領域の上に選択的に設けられている。前記第3半導体領域は、前記第2半導体領域の上に選択的に設けられている。前記ゲート電極は、前記第1半導体領域中および前記第2半導体領域中に第1絶縁部を介して設けられている。前記ゲート電極は、第1方向に延びている。前記ゲート電極は、前記第1方向と交差する第2方向において複数設けられている。前記第1電極は、前記第3半導体領域の上に設けられている。前記第1電極は、前記第3半導体領域と電気的に接続されている。前記第2絶縁部は、前記第1半導体領域中において前記複数設けられたゲート電極と離間して設けられる。

10

20

30

40

50

数のゲート電極と離間している。前記第2絶縁部は、前記第2方向に延びている。前記第2絶縁部は、前記第2方向に延び、前記第1方向において複数設けられている。前記第3絶縁部は、前記第1方向に延びる第1絶縁部分を有する。前記第3絶縁部の前記第1絶縁部分は、前記第2方向において前記複数のゲート電極と前記複数の第2絶縁部との間に位置している。前記第3絶縁部は、前記第1半導体領域中において前記複数のゲート電極および前記複数の第2絶縁部と離間している。前記第2電極は、前記複数の第2絶縁部および前記第3絶縁部の上に設けられている。前記第2電極は、前記複数のゲート電極と電気的に接続されている。

【図面の簡単な説明】

【0006】

10

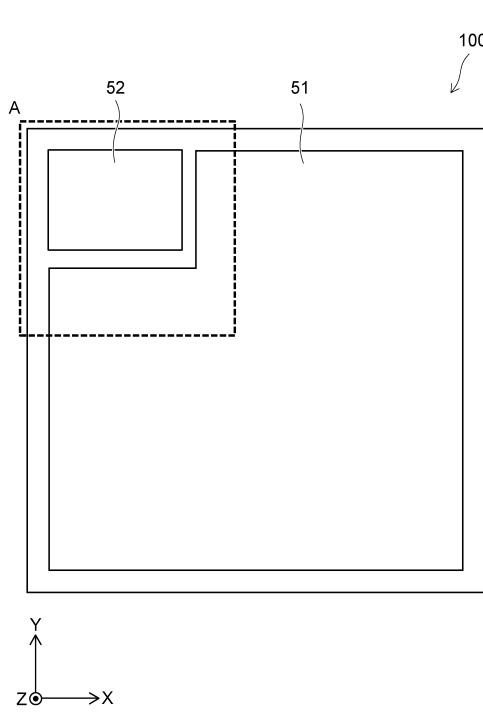

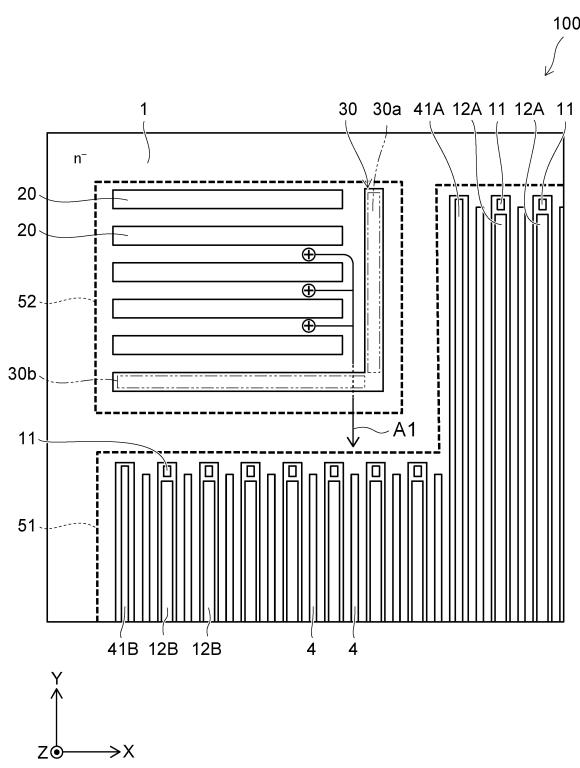

【図1】第1実施形態に係る半導体装置の平面図である。

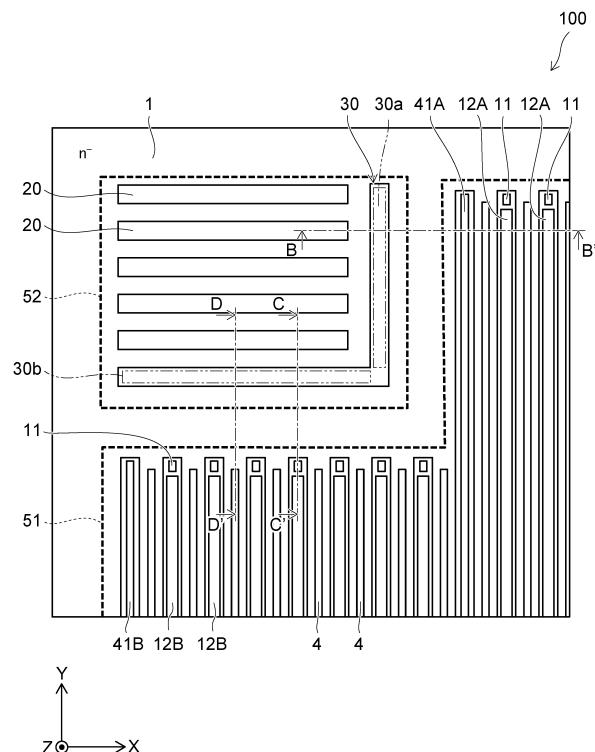

【図2】図1の部分Aを拡大した平面図である。

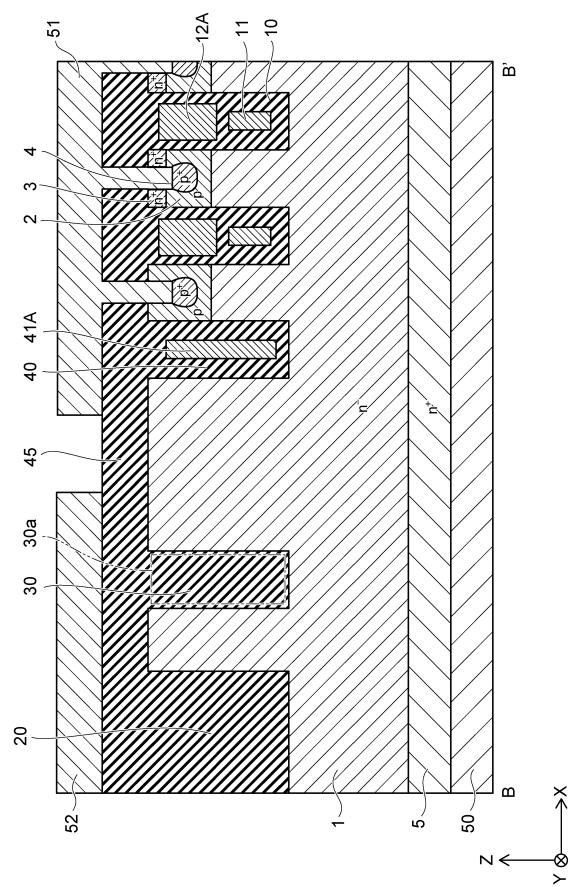

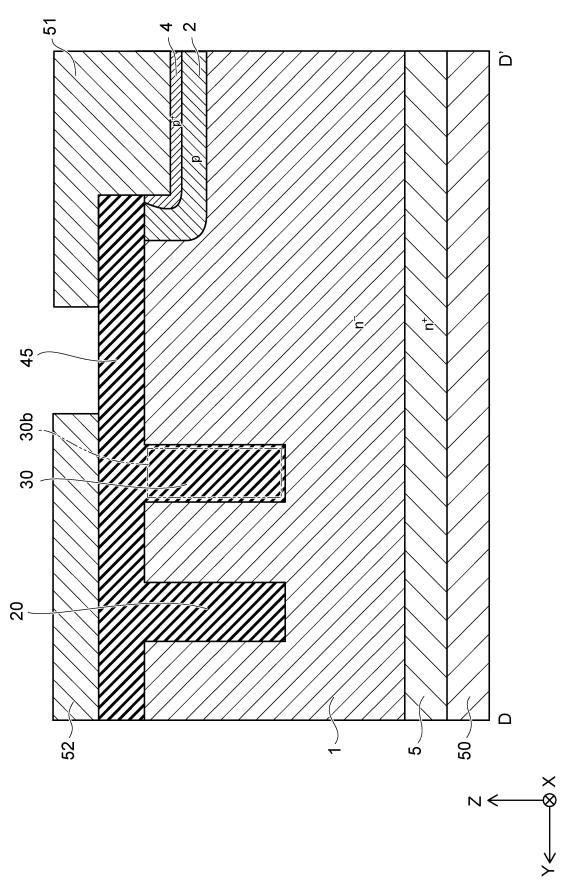

【図3】図2のB-B'断面図である。

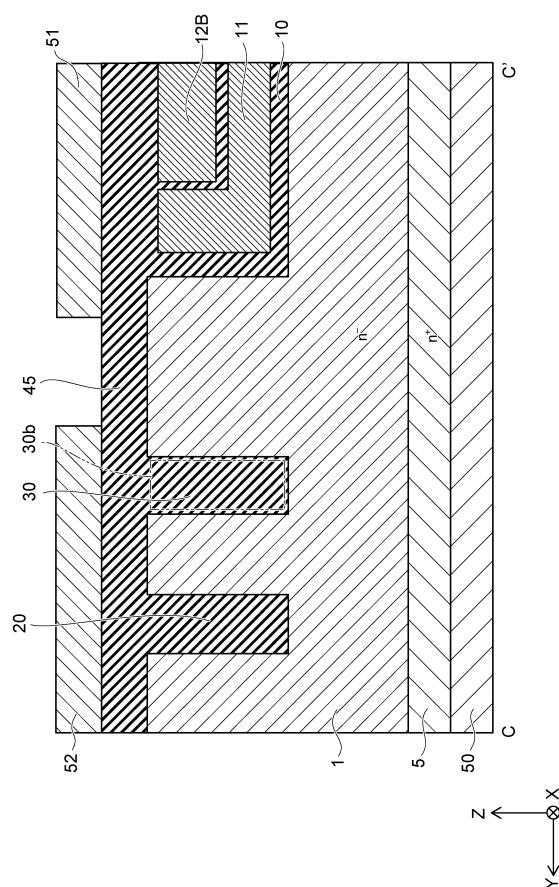

【図4】図2のC-C'断面図である。

【図5】図2のD-D'断面図である。

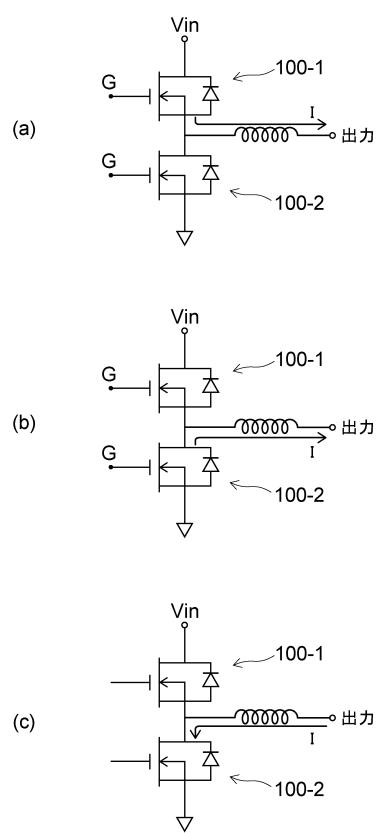

【図6】第1実施形態に係る半導体装置が接続された電気回路の一例を表す回路図である。

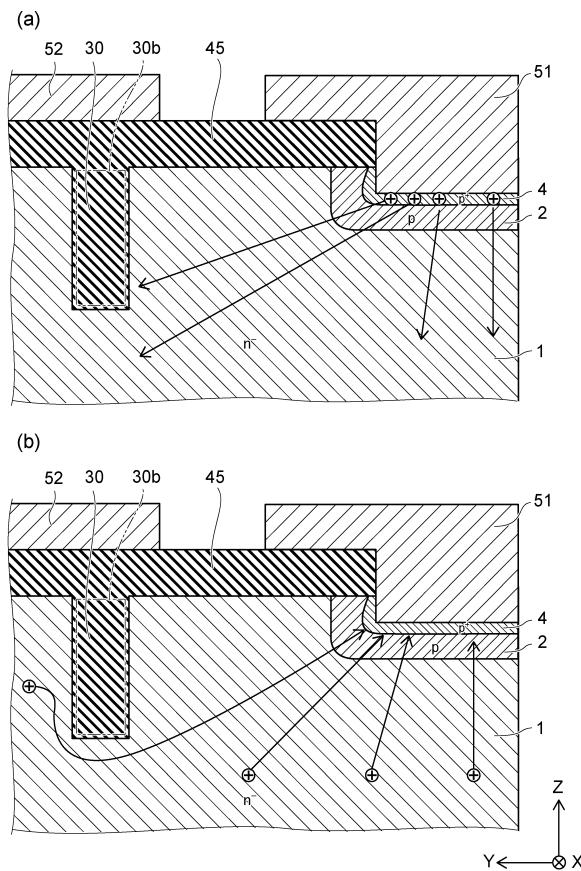

【図7】第1実施形態に係る半導体装置におけるキャリアの流れを表す断面図である。

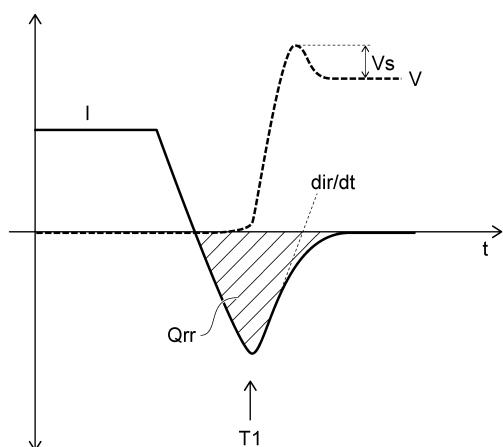

【図8】図6に表す電気回路中の半導体装置における電流および電圧の波形を表すグラフである。

20

【図9】第1実施形態に係る半導体装置100の平面図である。

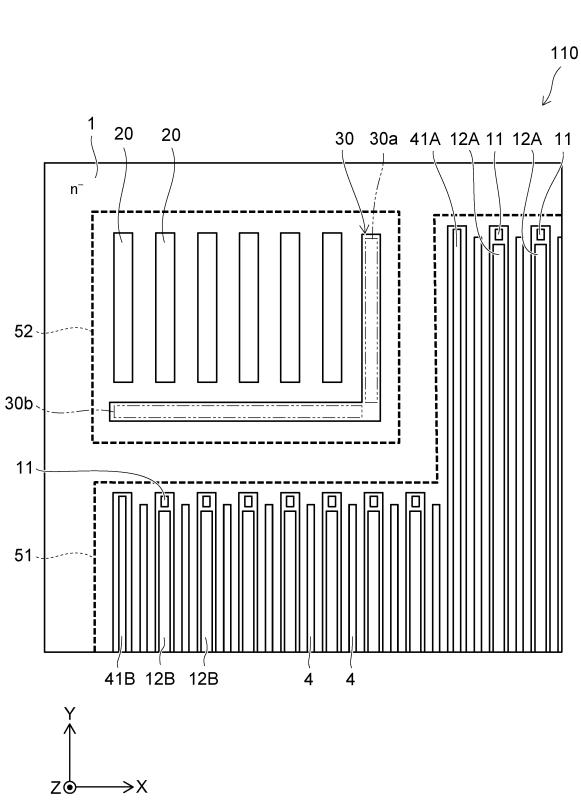

【図10】第1実施形態の第1変形例に係る半導体装置の一部を表す平面図である。

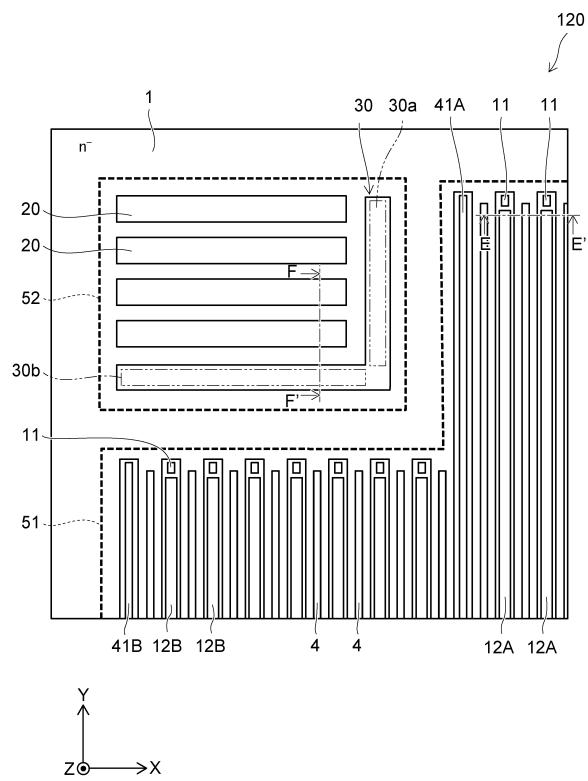

【図11】第1実施形態の第2変形例に係る半導体装置の一部を表す平面図である。

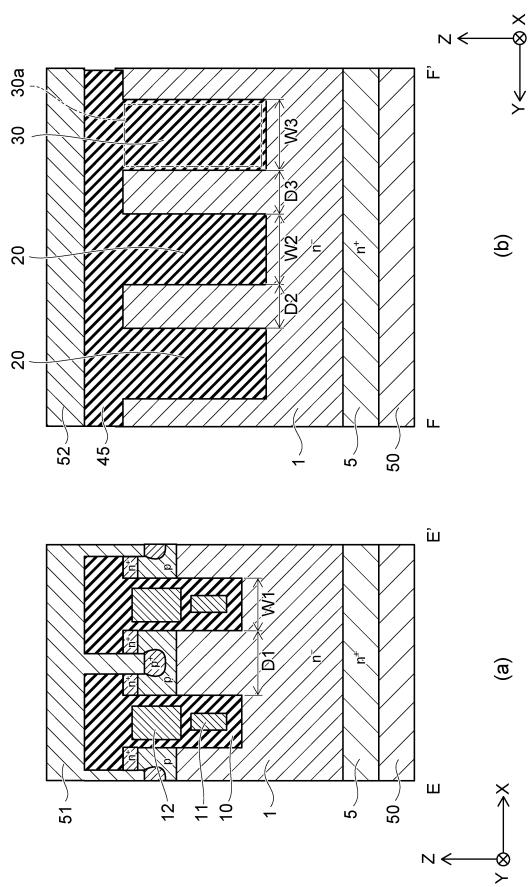

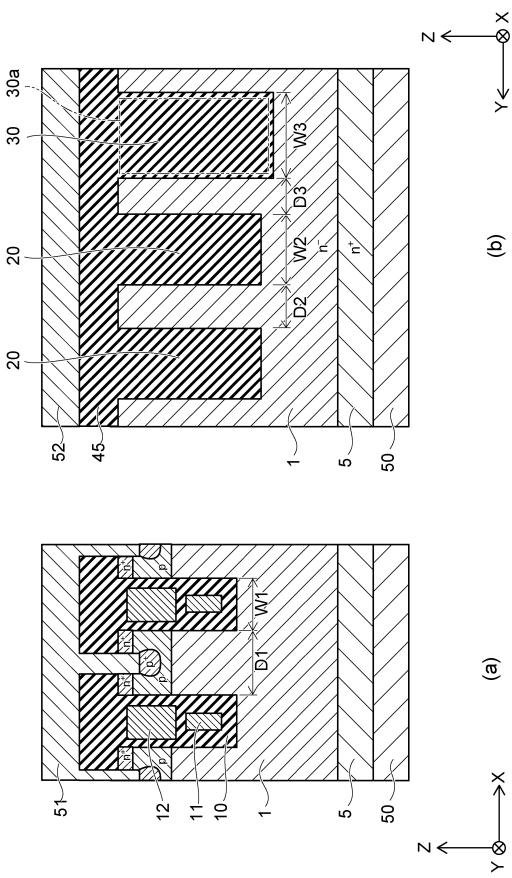

【図12】(a)図11のE-E'断面図である。(b)図11のF-F'断面図である。

【図13】第1実施形態の第2変形例に係る半導体装置の他の一例を表す部分拡大断面図である。

【図14】第1実施形態の第3変形例に係る半導体装置の一部を表す平面図である。

【図15】図14のG-G'断面図である。

【図16】第2実施形態に係る半導体装置の一部を表す平面図である。

30

【図17】図16のH-H'断面図である。

【図18】第2実施形態の第1変形例に係る半導体装置の一部を表す断面図である。

【図19】第2実施形態の第2変形例に係る半導体装置の一部を表す断面図である。

【発明を実施するための形態】

【0007】

以下に、本発明の各実施形態について図面を参照しつつ説明する。

なお、図面は模式的または概念的なものであり、各部分の厚みと幅との関係、部分間の大きさの比率などは、必ずしも現実のものと同一とは限らない。また、同じ部分を表す場合であっても、図面により互いの寸法や比率が異なって表される場合もある。

また、本願明細書と各図において、既に説明したものと同様の要素には同一の符号を付して詳細な説明は適宜省略する。

40

各実施形態の説明には、XYZ直交座標系を用いる。ドレン電極50からソース電極51に向かう方向をZ方向とする。また、Z方向に対して垂直であり、相互に直交する2方向をX方向(第2方向)およびY方向(第1方向)とする。

以下の説明において、 $n^+$ 、 $n^-$ 及び $p^+$ 、 $p$ の表記は、各導電形における不純物濃度の相対的な高低を表す。すなわち、「+」が付されている表記は、「+」および「-」のいずれも付されていない表記よりも不純物濃度が相対的に高く、「-」が付されている表記は、いずれも付されていない表記よりも不純物濃度が相対的に低いことを示す。

以下で説明する各実施形態について、各半導体領域のp形とn形を反転させて各実施形態を実施してもよい。

50

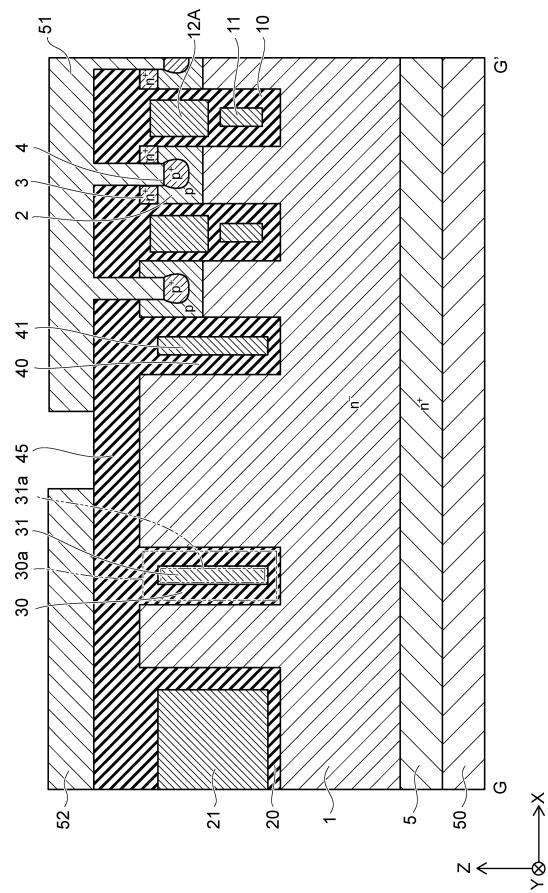

## 【0008】

(第1実施形態)

図1～図5を用いて、第1実施形態に係る半導体装置の一例について説明する。

図1は、第1実施形態に係る半導体装置100の平面図である。

図2は、図1の部分Aを拡大した平面図である。

図3は、図2のB-B'断面図である。

図4は、図2のC-C'断面図である。

図5は、図2のD-D'断面図である。

なお、図2では、ソース電極51およびゲートパッド52が破線で表され、絶縁層45、p形ベース領域2、およびn<sup>+</sup>形ソース領域3が省略されている。

10

## 【0009】

半導体装置100は、例えば、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)である。

図1～図4に表すように、半導体装置100は、n<sup>-</sup>形(第1導電形)半導体領域1(第1半導体領域)と、p形(第2導電形)ベース領域2(第2半導体領域)と、n<sup>+</sup>形ソース領域3(第3半導体領域)と、p<sup>+</sup>形コンタクト領域4と、n<sup>+</sup>形ドレイン領域5と、絶縁部10(第1絶縁部)と、フィールドプレート電極(以下、FP電極という)11と、ゲート電極12Aおよび12Bと、絶縁部20(第2絶縁部)と、絶縁部30(第3絶縁部)と、絶縁部40と、FP電極41Aおよび41Bと、絶縁層45と、ドレイン電極50と、ソース電極51(第1電極)と、ゲートパッド52(第2電極)と、を有する。

20

## 【0010】

図1に表すように、半導体装置100の上面には、ソース電極51およびゲートパッド52が設けられている。ソース電極51とゲートパッド52とは、互いに離隔され、電気的に分離されている。

## 【0011】

図2に表すように、ソース電極51の下には、ゲートパッド52と電気的に接続された複数のゲート電極12Aおよび複数のゲート電極12Bが設けられている。複数のゲート電極12Aおよび複数のゲート電極12Bは、X方向に並べられ、各々がY方向に延びている。Z方向から見た場合に、ゲートパッド52は、Y方向において、ゲート電極12Bと並び、ゲート電極12Aとは並んでいない。このため、ゲート電極12BのY方向における長さは、ゲート電極12AのY方向における長さよりも短い。

30

以降では、ゲート電極12Aおよび12Bに共通する性質については、これらのゲート電極をまとめて「ゲート電極12」と称して説明する。

## 【0012】

ゲートパッド52の下には、複数の絶縁部20がY方向に並べられている。各絶縁部20は、X方向に延びている。ゲート電極12Aの一部は、X方向において絶縁部20と並んでいる。また、ゲート電極12Bは、Y方向において、絶縁部20の一部と並んでいる。

## 【0013】

40

絶縁部30は、Y方向に延びる第1絶縁部分30aと、X方向に延びる第2絶縁部分30bと、を有する。第1絶縁部分30aは、X方向において、複数の絶縁部20と複数のゲート電極12Aとの間に位置している。第2絶縁部分30bは、Y方向において、複数の絶縁部20と複数のゲート電極12Bとの間に位置している。

## 【0014】

FP電極41Aおよび41Bは、ソース電極51の下に設けられている。Z方向から見た場合に、ゲートパッド52は、Y方向において、FP電極41Bと並び、FP電極41Aと並んでいない。このため、FP電極41BのY方向における長さは、FP電極41AのY方向における長さよりも短い。

FP電極41Aの一部は、X方向において、ゲート電極12Aの一部と絶縁部30との

50

間に位置している。FP電極41Bは、複数のゲート電極12Bの半導体装置外周側に位置している。ゲート電極12Bは、X方向において、FP電極41Aの一部とFP電極41Bとの間に設けられている。

以降では、FP電極41Aおよび41Bに共通する性質については、これらのFP電極をまとめて「FP電極41」と称して説明する。

#### 【0015】

図3～図5に表すように、半導体装置100の下面には、ドレイン電極50が設けられている。

<sup>10</sup>n<sup>+</sup>形ドレイン領域5は、ドレイン電極50の上に設けられ、ドレイン電極50と電気的に接続されている。

n<sup>-</sup>形半導体領域1は、n<sup>+</sup>形ドレイン領域5の上に設けられている。

p形ベース領域2は、n<sup>-</sup>形半導体領域1の上に選択的に設けられている。

n<sup>+</sup>形ソース領域3およびp<sup>+</sup>形コンタクト領域4は、p形ベース領域2の上に選択的に設けられている。

#### 【0016】

FP電極11は、絶縁部10を介してn<sup>-</sup>形半導体領域1中に設けられている。

ゲート電極12は、絶縁部10を介してn<sup>-</sup>形半導体領域1中およびp形ベース領域2中に設けられている。ゲート電極12は、FP電極11の上に位置し、FP電極11と離間している。図4に表すように、FP電極11のY方向における端部は、Z方向に向けて屈曲しており、ゲート電極12とY方向において並んでいる。

#### 【0017】

ソース電極51の一部は、p形ベース領域2中に設けられ、n<sup>+</sup>形ソース領域3およびp<sup>+</sup>形コンタクト領域4と電気的に接続されている。ゲート電極12とソース電極51との間には、絶縁層45が設けられ、これらの電極は電気的に分離されている。

#### 【0018】

FP電極41は、絶縁部40を介してn<sup>-</sup>形半導体領域1中およびp形ベース領域2中に設けられている。FP電極41は、ゲート電極12とX方向において離間している。

FP電極11および41は、ソース電極51またはゲートパッド52と電気的に接続されている。

#### 【0019】

<sup>30</sup>絶縁部20および30は、p形ベース領域2、絶縁部10、およびゲート電極12と離間してn<sup>-</sup>形半導体領域1中に設けられている。また、絶縁部20と30は、n<sup>-</sup>形半導体領域1中で、X方向およびY方向において離間している。

絶縁部20および絶縁部30の周りのn<sup>-</sup>形半導体領域1は、絶縁層45に覆われており、ゲートパッド52は、絶縁層45の上に、ソース電極51と離間して設けられている。絶縁部10、20、および30は、絶縁層45によってつながっている。絶縁部10、20、および30と、絶縁層45とは、例えば、一体に形成された絶縁膜である。

#### 【0020】

ここで、半導体装置100の動作について説明する。

ソース電極51に対して正の電圧がドレイン電極50に印加された状態で、ゲート電極12に閾値以上の電圧が印加されると、半導体装置がオン状態となる。このとき、絶縁部10近傍のp形ベース領域2にチャネル（反転層）が形成される。電子は、このチャネルを通ってn<sup>+</sup>形ソース領域3からn<sup>-</sup>形半導体領域1に流れ、n<sup>+</sup>形ドレイン領域5を通って排出される。

その後、ゲート電極12に印加される電圧が閾値よりも低くなると、p形ベース領域2におけるチャネルが消滅し、半導体装置がオフ状態になる。

#### 【0021】

半導体装置100がオフ状態になると、FP電極11とドレイン電極50との間の電位差により、絶縁部10とn<sup>-</sup>形半導体領域1との界面からn<sup>-</sup>形半導体領域1に向けて空乏層が広がる。絶縁部10とn<sup>-</sup>形半導体領域1との界面から広がるこの空乏層により、

10

20

30

40

50

半導体装置の耐圧を高めることができる。あるいは、半導体装置の耐圧が向上した分、n<sup>-</sup>形半導体領域1におけるn形不純物濃度を高め、半導体装置のオン抵抗を低減することができる。

#### 【0022】

また、半導体装置100は、p形ベース領域2をアノード、n<sup>-</sup>形半導体領域1をカソードとするダイオードを内蔵している。このため、ドレイン電極50に対してソース電極51に正の電圧が印加された際には、ドレイン電極50からソース電極51へ順方向の電流が流れる。

#### 【0023】

次に、各構成要素の材料の一例を説明する。

n<sup>-</sup>形半導体領域1、p形ベース領域2、n<sup>+</sup>形ソース領域3、p<sup>+</sup>形コンタクト領域4、およびn<sup>+</sup>形ドレイン領域5は、半導体材料として、シリコン、炭化シリコン、窒化ガリウム、またはガリウムヒ素を含む。半導体材料としてシリコンが用いられる場合、n形不純物として、ヒ素、リン、またはアンチモンを用いることができる。p形不純物として、ボロンを用いることができる。

F P電極11、ゲート電極12、およびF P電極41は、ポリシリコンなどの導電材料を含む。

絶縁部10、20、30、および40は、酸化シリコンなどの絶縁材料を含む。

ドレイン電極50、ソース電極51、およびゲートパッド52は、アルミニウムなどの金属を含む。

#### 【0024】

ここで、本実施形態による効果を、図6～図8を用いて説明する。

図6は、第1実施形態に係る半導体装置100が接続された電気回路の一例を表す回路図である。

図7は、第1実施形態に係る半導体装置におけるキャリアの流れを表す断面図である。

図8は、図6に表す電気回路中の半導体装置100-2における電流および電圧の波形を表すグラフである。

なお、図8において、実線は、ダイオードを流れる電流を表し、破線は、ソース電極51に対するドレイン電極50の電圧を表している。横軸は時間を表し、ダイオードの電流は順方向に流れる場合を正として表している。

#### 【0025】

図6に表す例では、本実施形態に係る2つの半導体装置100-1と100-2が用いられ、ハーフブリッジ回路が構成されている。図6(a)は、半導体装置100-1がオン状態、半導体装置100-2がオフ状態であり、半導体装置100-1に電流Iが流れている様子を表している。

#### 【0026】

図6(a)に表す状態で、半導体装置100-1がターンオフされると、インダクタンスLによる誘導起電力が生じる。これにより、図6(b)に表すように、半導体装置100-2のダイオードに順方向の電流Iが流れる。このとき、正孔が、図7(a)に表すように、p形ベース領域2を通してソース電極51からn<sup>-</sup>形半導体領域1に注入される。

#### 【0027】

半導体装置100-2のダイオードに順方向電流が流れると、半導体装置100-2の内部に蓄積されたキャリアが排出される。このとき、正孔は、図7(b)に表すように、p形ベース領域2を通してソース電極51へ排出される。半導体装置100-2からキャリアが排出されることで、図6(c)に表すように、半導体装置100-2には、ドレイン電極50からソース電極51に向かって逆回復電流が流れる。

#### 【0028】

図8に表すように、タイミングT1で逆回復電流が流れると、その後、半導体装置100-2のソース電極51に対するドレイン電極50の電圧Vが上昇していく。このとき、逆回復電流の減少の傾きd i r / d tに応じて、電圧Vにサージ電圧V<sub>s</sub>が発生する。

10

20

30

40

50

$d_{ir}/dt$  が大きいと、サージ電圧  $V_s$  も大きくなる。サージ電圧  $V_s$  が大きいと、 $n^+$  形ソース領域 3、 $p$  形ベース領域 2、および  $n^-$  形半導体領域 1 から構成される寄生 NPN トランジスタが動作し易くなる。寄生 NPN トランジスタが動作すると、半導体装置内を大電流が流れ、半導体装置が破壊される可能性があるため、 $d_{ir}/dt$  は、小さいことが望ましい。

#### 【0029】

また、図 8 に表す蓄積電荷  $Q_{rr}$  が大きく、一部の  $p$  形ベース領域 2 および  $p^+$  形コンタクト領域 4 に正孔が集中して流れると、寄生トランジスタのベース電位が上昇し、寄生トランジスタが動作する可能性がある。従って、 $d_{ir}/dt$  と同様に、蓄積電荷  $Q_{rr}$  も少ないことが望ましい。10

#### 【0030】

ダイオード動作時に注入された正孔の一部は、ゲートパッド 52 の下の  $n^-$  形半導体領域 1 にも蓄積される。ゲートパッド 52 の下の  $n^-$  形半導体領域 1 に蓄積された正孔は、逆回復動作時には、近くの  $p$  形ベース領域 2 に移動してソース電極 51 へ排出される。従って、ゲートパッド 52 下の  $n^-$  形半導体領域 1 に近い  $p$  形ベース領域 2 には、他の部分に比べて多くの正孔が流れるため、より寄生 NPN トランジスタが動作し易い。

このため、ゲートパッド 52 の下に蓄積される電荷  $Q_{rr}$  の減少、およびゲートパッド 52 の下に蓄積されたキャリアによる逆回復時の  $d_{ir}/dt$  の減少が、寄生 NPN トランジスタの動作の抑制に特に効果的である。20

#### 【0031】

この点について、本実施形態に係る半導体装置 100 のように、ゲートパッド 52 下の  $n^-$  形半導体領域 1 中に絶縁部 20 を設けることで、ゲートパッド 52 の下の  $n^-$  形半導体領域 1 の体積を減少させることができる。このため、ゲートパッド 52 の下に蓄積される電荷  $Q_{rr}$  を減少させることができる。20

#### 【0032】

また、絶縁部 20 が複数設けられていることで、 $n^-$  形半導体領域 1 に注入された正孔の一部が、絶縁部 20 同士の間に蓄積される。絶縁部 20 同士の間の  $n^-$  形半導体領域 1 に蓄積された正孔は、逆回復動作時に、絶縁部 20 によってその移動が妨げられ、ソース電極 51 に向けて移動し難くなるため、逆回復に要する時間を長くし、 $d_{ir}/dt$  を小さくすることができる。30

#### 【0033】

さらに、本実施形態に係る半導体装置 100 では、絶縁部 30 の第 1 絶縁部分 30a が、複数の絶縁部 20 と複数のゲート電極 12A との間を Y 方向に延びている。このような構造を採用することで、逆回復動作時に、絶縁部 20 同士の間の  $n^-$  形半導体領域 1 に蓄積された正孔がソース電極 51 に向けて移動する際に、その移動が第 1 絶縁部分 30a によって妨げられる。このため、逆回復に要する時間を長くし、 $d_{ir}/dt$  をさらに小さくすることができる。

#### 【0034】

すなわち、本実施形態によれば、絶縁部 20 および 30 が設けられることで、蓄積電荷  $Q_{rr}$  を減少させ、かつ  $d_{ir}/dt$  を小さくすることができ、これにより寄生 NPN トランジスタが動作する可能性を低減することができる。40

#### 【0035】

ここで、図 9 を参照しつつ、本実施形態に係る半導体装置のより望ましい形態について説明する。

図 9 は、第 1 実施形態に係る半導体装置の平面図である。

第 1 絶縁部分 30a は、X 方向において、複数の絶縁部 20 と離間している。絶縁部 30 が第 1 絶縁部分 30a のみを有する場合、絶縁部 20 同士の間に蓄積された正孔が、図 9 の矢印 A1 に表すように、絶縁部 20 と絶縁部 30 との隙間を流れ、 $p^+$  形コンタクト領域 4 に流れる可能性がある。従って、絶縁部 20 と 30 との隙間を流れた正孔が、一部の  $p^+$  形コンタクト領域 4 に集中して流れ、寄生 NPN トランジスタが動作してしまう可50

能性がある。

**【0036】**

絶縁部30が、第1絶縁部分30aに加えて、第2絶縁部分30bを有することで、矢印A1のように、絶縁部20と30との隙間を-Y方向に向けて流れる正孔を減少させることができる。このため、正孔が一部のp<sup>+</sup>形コンタクト領域4に集中して流れることを抑制し、寄生NPNトランジスタが動作する可能性をより一層低減させることが可能となる。

**【0037】**

また、逆回復動作時には、n<sup>-</sup>形半導体領域1の電位は、p形ベース領域2の電位よりも高く、ソース電極51に接続されたFP電極41Aの電位よりも高い。このため、絶縁部20および30とゲート電極12Aとの間に、FP電極41Aが設けられていることで、逆回復時にFP電極41A近傍を通った正孔が、FP電極41Aによってトラップすることができる。これにより、電荷Qrrを減少させ、寄生NPNトランジスタが動作する可能性をより一層低減させることが可能となる。

**【0038】**

(第1変形例)

図10は、第1実施形態の第1変形例に係る半導体装置110の一部を表す平面図である。

図10では、ソース電極51およびゲートパッド52が破線で表され、絶縁層45および各半導体領域が省略されている。

**【0039】**

図2～図4に表す半導体装置100では、ゲート電極12がY方向に延び、絶縁部20がX方向に延びている。これに対して、本変形例に係る半導体装置110では、ゲート電極12と絶縁部20とが、ともにY方向に延びている。

**【0040】**

半導体装置110では、半導体装置100と同様に、複数の絶縁部20が、ゲートパッド52の下に設けられている。また、絶縁部30の第2絶縁部分30bが、Y方向において、複数のゲート電極12Bと複数の絶縁部20との間に設けられている。

**【0041】**

このため、本変形例によれば、半導体装置100と同様に、ダイオード動作時における正孔の蓄積量および逆回復動作時における正孔の排出量を低減させることができる。

また、絶縁部30がY方向に延びる第1絶縁部分30aをさらに有することで、絶縁部20と第2絶縁部分30bの隙間を流れる正孔を減少させることができるとも同様である。

**【0042】**

ただし、ゲート電極12と絶縁部20が互いに異なる方向に延びている場合、絶縁部20同士の間に蓄積された正孔が、絶縁部20に沿ってソース電極51に向けて流れる際に、その流れがゲート電極12によって移動が妨げられる。従って、ゲート電極12と絶縁部20が互いに異なる方向に延びている場合、ゲート電極12と絶縁部20が同じ方向に延びている場合に比べて、電荷Qrrが減少し、寄生NPNトランジスタが動作する可能性をさらに低減することが可能である。

**【0043】**

(第2変形例)

図11は、第1実施形態の第2変形例に係る半導体装置120の一部を表す平面図である。

図12(a)は図11のE-E'断面図であり、図12(b)は図11のF-F'断面図である。

図13は、第1実施形態の第2変形例に係る半導体装置120の他の一例を表す部分拡大断面図である。

なお、図11では、ソース電極51およびゲートパッド52が破線で表され、絶縁層4

10

20

30

40

50

5 および各半導体領域が省略されている。

**【0044】**

本変形例に係る半導体装置120では、図11に表すように、ゲート電極12と絶縁部20が互いに異なる方向に延びている。また、図12に表すように、絶縁部20の幅W2および絶縁部30の幅W3は、絶縁部10の幅W1よりも広い。

なお、ここでは、幅とは、それぞれの絶縁部が延びている方向に対して垂直な方向における、各絶縁部の長さを意味している。

**【0045】**

絶縁部20同士の間の距離D2および絶縁部20と30との間の距離D3は、絶縁部10同士の間の距離D1よりも短い。また、絶縁部20の下端および絶縁部30の下端は、絶縁部10の下端よりも下方に設けられている。10

**【0046】**

幅W2および幅W3を、幅W1よりも広くし、距離D2および距離D3を、距離D1よりも短くすることで、半導体装置100に比べて、ゲートパッド52の下のn<sup>-</sup>形半導体領域1の体積を小さくし、ゲートパッド52の下に蓄積される正孔の量を減少させることができる。

**【0047】**

また、絶縁部20の下端および絶縁部30の下端は、絶縁部10の下端よりも下方に設けることで、ゲートパッド52の下のn<sup>-</sup>形半導体領域1の体積をさらに小さくし、図8に表す電荷Q<sub>r r</sub>を減少させることができる。加えて、絶縁部20同士の間に蓄積した正孔がソース電極51から排出されるまでの時間がより長くなるために、d<sub>i r</sub> / d<sub>t</sub>をさらに小さくすることができる。20

**【0048】**

すなわち、本変形例に係る半導体装置120によれば、半導体装置100に比べて、寄生NPNトランジスタが動作する可能性をさらに低減することが可能である。

**【0049】**

なお、図13に表すように、絶縁部30の幅W3を幅W2よりも広くし、距離D3を距離D2よりも短くしてもよい。また、絶縁部30の下端の位置を絶縁部20の下端の位置よりも深くしてもよい。こうすることで、より一層、ゲートパッド52下の正孔の蓄積量およびソース電極51への正孔の排出量を減少させ、寄生NPNトランジスタが動作する可能性を低減させることが可能となる。30

**【0050】**

(第3変形例)

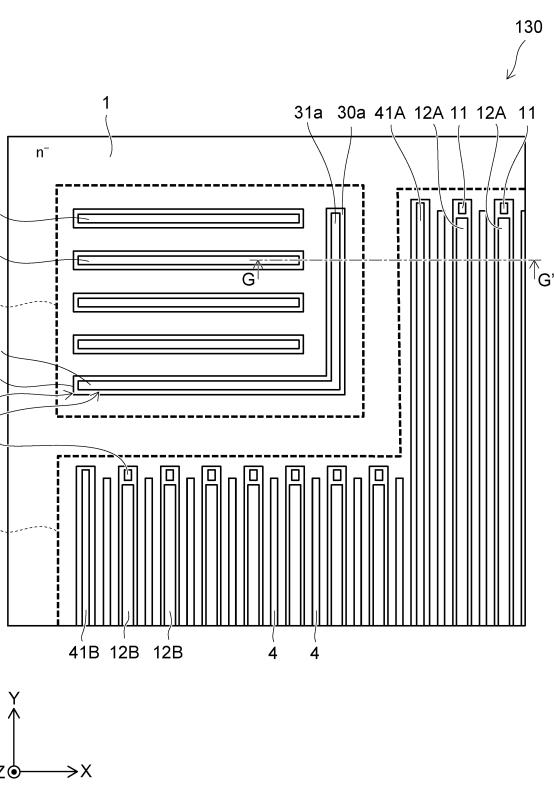

図14は、第1実施形態の第3変形例に係る半導体装置130の一部を表す平面図である。

図15は、図14のG-G'断面図である。

なお、図14では、ソース電極51およびゲートパッド52が破線で表され、絶縁層45および各半導体領域が省略されている。

**【0051】**

半導体装置130は、導電部21および導電部31をさらに備える点で、半導体装置100と異なる。導電部21は、絶縁部20中に設けられ、導電部31は、絶縁部30中に設けられている。40

**【0052】**

導電部21は、絶縁部20に沿ってX方向に延びている。

導電部31は、第1導電部分31aおよび第2導電部分31bを有する。第1導電部分31aは、第1絶縁部分30a中に設けられ、Y方向に延びている。第2導電部分31bは、第2絶縁部分30b中に設けられ、X方向に延びている。

**【0053】**

導電部21および31は、ソース電極51およびゲートパッド52と電気的に分離されており、これらの導電部の電位は、フローティングである。50

**【0054】**

本変形例に係る半導体装置130においても、半導体装置100と同様に、電荷Qrrおよびdir/dtを減少させ、寄生NPNトランジスタが動作する可能性を低減させることが可能となる。

**【0055】**

また、導電部21および31をソース電極51およびゲートパッド52と電気的に分離することで、ソース電極51の容量およびゲートパッド52の容量の増加を抑え、半導体装置のスイッチング速度の低下を抑制することができる。

**【0056】**

なお、ここでは、半導体装置100に対して導電部21および31を設けた場合について説明したが、本変形例はこれに限られない。例えば、半導体装置110または120の絶縁部20中および絶縁部30中に、導電部21および31が設けられていてもよい。

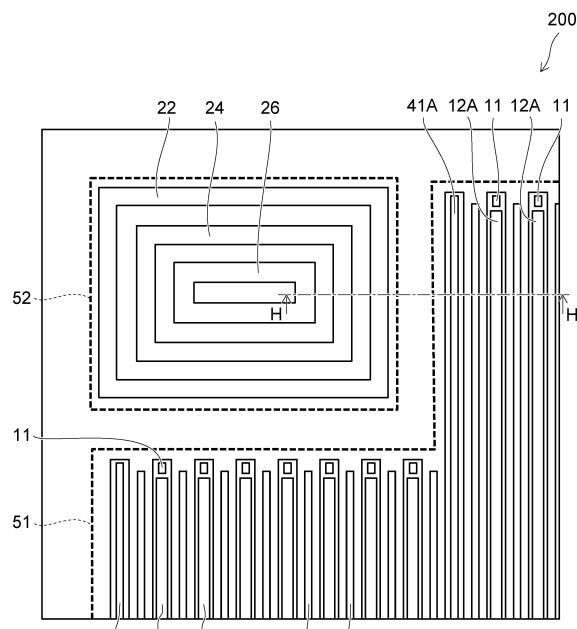

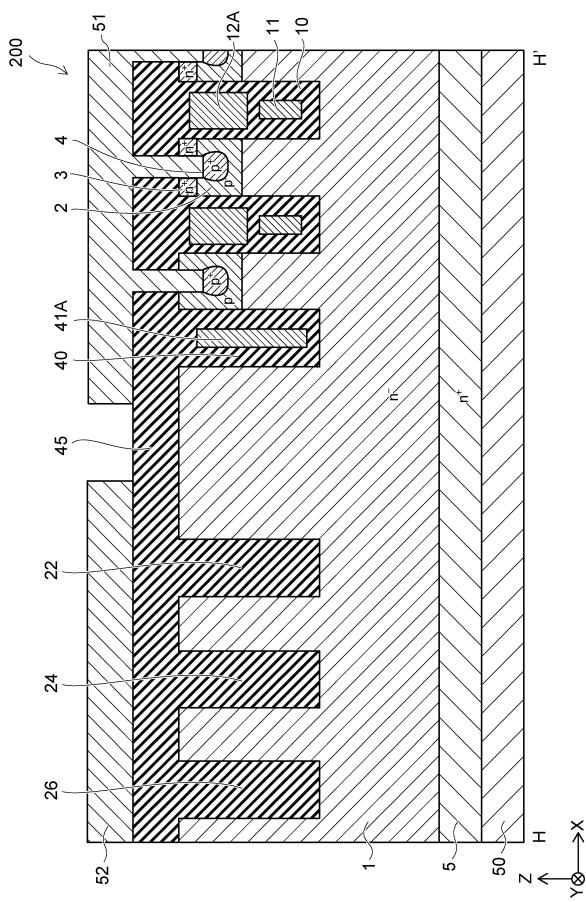

**【0057】****(第2実施形態)**

図16は、第2実施形態に係る半導体装置200の一部を表す平面図である。

図17は、図16のH-H'断面図である。

なお、図16では、ソース電極51およびゲートパッド52が破線で表され、絶縁層45および各半導体領域が省略されている。

**【0058】**

半導体装置200は、ゲートパッド52の下に設けられた絶縁部の構造が半導体装置100と異なる。

**【0059】**

図16および図17に表すように、半導体装置200では、ゲートパッド52の下に、絶縁部22(第2絶縁部)、24(第3絶縁部)、および26が設けられている。絶縁部22、24、および26は、それぞれ環状に設けられ、n-形半導体領域1の一部を囲んでいる。絶縁部24は、絶縁部22の内側に設けられ、絶縁部26は、絶縁部24の内側に設けられている。

**【0060】**

所定の方向に延びる複数の絶縁部をゲートパッド52の下に設けた場合、絶縁部同士の隙間を通して、ゲートパッド52下の領域とソース電極51との間を正孔が移動する可能性がある。

これに対して、本実施形態に係る半導体装置200のように、ゲートパッド52の下に環状の絶縁部を設けることで、ゲートパッド52下の領域とソース電極51との間の正孔の移動をより一層抑制することが可能となる。このため、本実施形態によれば、第1実施形態に係る半導体装置に比べて、図8に表したdir/dtをより小さくし、寄生NPNトランジスタが動作する可能性をさらに低減することが可能である。

**【0061】**

なお、ゲートパッド52の下に設けられる環状の絶縁部の数は、図16に表す例よりも少なくとも良いし、多くても良い。絶縁部の数は任意であり、適宜変更することが可能である。

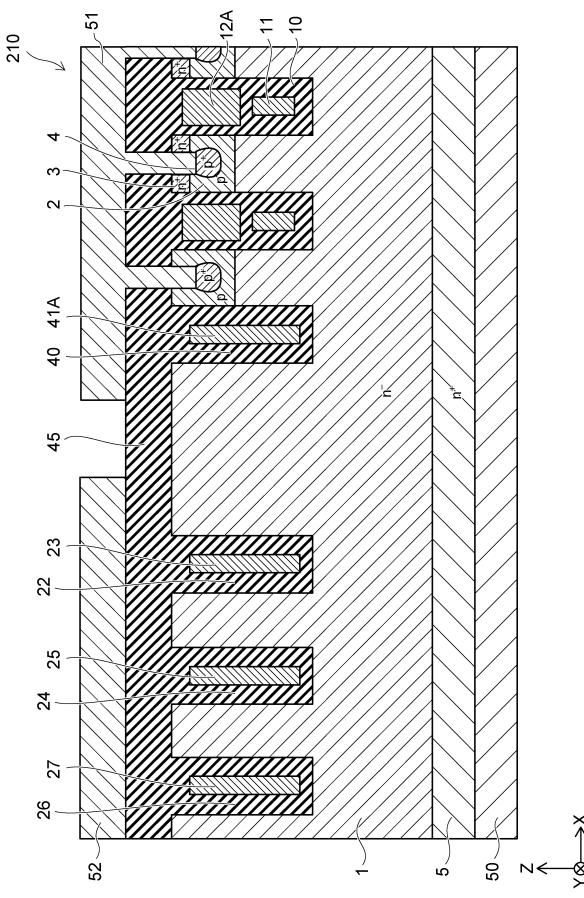

**【0062】****(第1変形例)**

図18は、第2実施形態の第1変形例に係る半導体装置210の一部を表す断面図である。

**【0063】**

半導体装置210は、導電部23、25、および27をさらに備える点で、半導体装置200と異なる。

図18に表すように、導電部23、25、および27は、それぞれ、絶縁部22、24、および26の中に設けられている。導電部23、25、および27は、それぞれ環状に設けられており、n-形半導体領域1の一部を囲んでいる。

10

20

30

40

50

**【0064】**

導電部23、25、および27は、ソース電極51およびゲートパッド52と電気的に分離されており、これらの導電部の電位は、フローティングである。

**【0065】**

本変形例においても、半導体装置200と同様に、電荷Qrrおよびdir/dtを減少させ、寄生NPNトランジスタが動作する可能性を低減することが可能である。

**【0066】**

また、導電部23、25、および27をソース電極51およびゲートパッド52と電気的に分離することで、ソース電極51の容量およびゲートパッド52の容量の増加を抑え、半導体装置のスイッチング速度の低下を抑制することができる。

10

**【0067】**

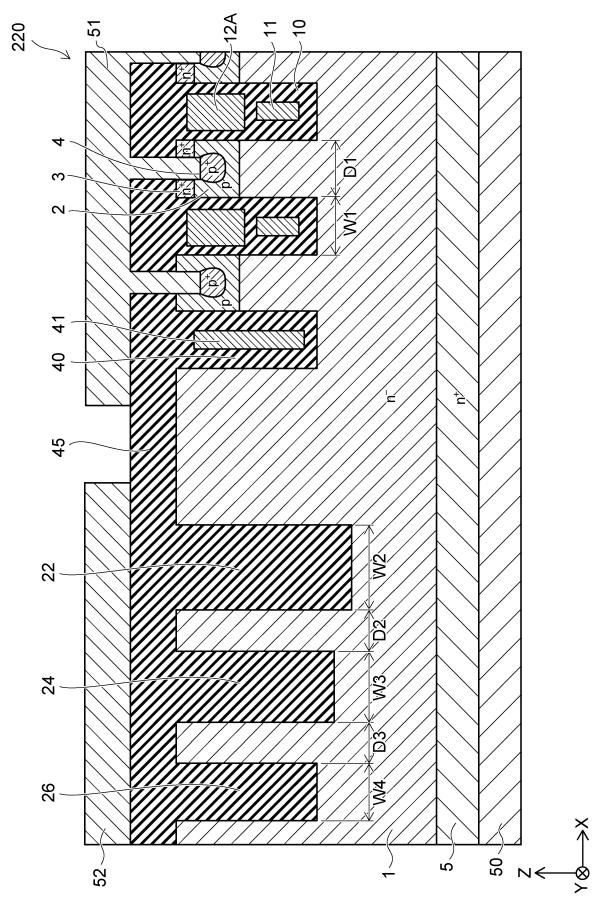

## (第2変形例)

図19は、第2実施形態の第2変形例に係る半導体装置220の一部を表す断面図である。

**【0068】**

半導体装置220は、絶縁部22、24、および26の構造が半導体装置200と異なる。

図19に表すように、絶縁部22の幅W2は、絶縁部24の幅W3よりも広く、幅W3は、絶縁部26の幅W4よりも広い。幅W2は、例えば、絶縁部10の幅と同じか、それよりも広い。

20

**【0069】**

絶縁部22と24との間の距離D2は、絶縁部24と26との間の距離D3よりも狭い。距離D3は、絶縁部10同士の間の距離D1よりも狭い。また、絶縁部22の下端の位置は、絶縁部24の下端の位置よりも深く、絶縁部24の下端の位置は、絶縁部26の下端の位置よりも深い。絶縁部26の下端の位置は、例えば、絶縁部10の下端の位置と同じか、それよりも深い。

**【0070】**

すなわち、絶縁部22、24、および26は、外側に向かうほど、幅が広く、下端の位置が深くなっている。外側の絶縁部の幅を広く、下端の位置を深くすることで、半導体装置200に比べて、ゲートパッド52下の領域とソース電極51との間の正孔の移動をより一層抑制し、dir/dtを小さくすることが可能となる。このため、本変形例によれば、寄生NPNトランジスタが動作する可能性をさらに低減させることができる。

30

**【0071】**

なお、半導体装置220においても半導体装置210と同様に、絶縁部22、24、および26中に、それぞれ、導電部23、25、および27が設けられていてよい。

**【0072】**

以上で説明した各実施形態における、各半導体領域の間の不純物濃度の相対的な高低については、例えば、SCM(走査型静電容量顕微鏡)を用いて確認することが可能である。なお、各半導体領域におけるキャリア濃度は、各半導体領域において活性化している不純物濃度と等しいものとみなすことができる。従って、各半導体領域の間のキャリア濃度の相対的な高低についても、SCMを用いて確認することができる。

40

また、各半導体領域における不純物濃度については、例えば、SIMS(二次イオン質量分析法)により測定することが可能である。

**【0073】**

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。実施形態に含まれる、例えば、n<sup>-</sup>形半導体領域1、p形ベース領域2、n<sup>+</sup>形ソース領域3、p<sup>+</sup>形コンタクト領域4、n<sup>+</sup>形ドレイン領域5、絶縁部10、フィールドプレート電極11、ゲート電極12、絶縁部

50

20、22、24、および26、導電部21、23、25、および27、絶縁部30、導電部31、絶縁部40、フィールドプレート電極41、絶縁層45、ドレイン電極50、ソース電極51、およびゲートパッド52などの各要素の具体的な構成に関しては、当業者が公知の技術から適宜選択することが可能である。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。また、前述の各実施形態は、相互に組み合わせて実施することができる。

【符号の説明】

【0074】

100、110、120、130、200、210、220 半導体装置、1 n<sup>-</sup> 形半導体領域、2 p 形ベース領域、3 n<sup>+</sup> 形ソース領域、4 p<sup>+</sup> 形コンタクト領域、5 n<sup>+</sup> 形ドレイン領域、10、20、22、24、26、30、40 絶縁部、11、41A、41B フィールドプレート電極、12A、12B ゲート電極、21、23、25、27、31 導電部、45 絶縁層、50 ドレイン電極、51 ソース電極、52 ゲートパッド

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

---

フロントページの続き

(51)Int.Cl.

F I

|        |       |         |

|--------|-------|---------|

| H 01 L | 29/78 | 6 5 2 F |

| H 01 L | 29/78 | 6 5 2 S |

| H 01 L | 29/78 | 6 5 3 C |

| H 01 L | 29/78 | 6 5 2 T |

| H 01 L | 29/06 | 3 0 1 V |

(72)発明者 小林 研也

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 恩田 和彦

(56)参考文献 特開2014-229705(JP,A)

特開2014-135367(JP,A)

特開2005-286042(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 78

H 01 L 29 / 06

H 01 L 29 / 12