(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2018-60179

(P2018-60179A)

(43) 公開日 平成30年4月12日(2018.4.12)

| (51) Int.Cl.               | F 1  |      |         |           | テーマコード (参考) |

|----------------------------|------|------|---------|-----------|-------------|

| <b>G09G 3/20</b> (2006.01) | G09G | 3/20 | 6 1 1 A | 2 H 1 8 9 |             |

| <b>G09F 9/30</b> (2006.01) | G09F | 9/30 | 3 0 8 A | 3 K 1 0 7 |             |

| <b>G09F 9/40</b> (2006.01) | G09F | 9/30 | 3 3 8   | 5 C 0 0 6 |             |

| <b>G09F 9/00</b> (2006.01) | G09F | 9/30 | 3 6 5   | 5 C 0 8 0 |             |

| <b>G09G 3/36</b> (2006.01) | G09F | 9/40 | 3 0 1   | 5 C 0 9 4 |             |

審査請求 未請求 請求項の数 8 O L (全 58 頁) 最終頁に続く

|              |                              |                                                                                         |                                                |

|--------------|------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------|

| (21) 出願番号    | 特願2017-180975 (P2017-180975) | (71) 出願人                                                                                | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成29年9月21日 (2017. 9. 21)     | (72) 発明者                                                                                | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (31) 優先権主張番号 | 特願2016-193264 (P2016-193264) | (72) 発明者                                                                                | 高橋 圭<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (32) 優先日     | 平成28年9月30日 (2016. 9. 30)     | F ターム (参考) 2H189 AA27 AA31 AA69 LA03 LA07<br>LA08 LA10 LA14 LA15 LA17<br>LA19 LA28 LA30 |                                                |

| (33) 優先権主張国  | 日本国 (JP)                     | 3K107 AA01 BB01 BB07 BB08 CC14<br>CC32 CC41 DD03 DD17 EE57<br>EE65 HH05                 |                                                |

| 申請有り         |                              | 最終頁に続く                                                                                  |                                                |

(54) 【発明の名称】表示装置および電子機器

## (57) 【要約】

【課題】新規な表示装置、および電子機器を提供すること。

【解決手段】表示装置は、信号生成回路と、第1のゲートドライバと、第2のゲートドライバと、画素を有する表示部と、を有する。画素は、液晶素子と、発光素子と、液晶素子の表示を制御する第1の画素回路と、発光素子の表示を制御する第2の画素回路と、を有する。表示部は、第1の表示部と、第2の表示部と、を有する。第1のゲートドライバは、第1の画素回路に第1の走査信号を出力する機能を有する。第2のゲートドライバは、第2の画素回路に第2の走査信号を出力する機能を有する。第1の表示部は、第1のゲートドライバおよび第2のゲートドライバから第1の走査信号および第2の走査信号がそれぞれ出力されて表示を行う機能を有する。第2の表示部は、第1のゲートドライバが出力する第1の走査信号、および第2のゲートドライバが出力する第2の走査信号を停止して表示を行う機能を有する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

信号生成回路と、第1のゲートドライバと、第2のゲートドライバと、画素を有する表示部と、を有し、

前記画素は、液晶素子と、発光素子と、前記液晶素子の表示を制御する第1の画素回路と、前記発光素子の表示を制御する第2の画素回路と、を有し、

前記表示部は、第1の表示部と、第2の表示部と、を有し、

前記第1のゲートドライバは、前記第1の画素回路に第1の走査信号を出力する機能を有し、

前記第2のゲートドライバは、前記第2の画素回路に第2の走査信号を出力する機能を有し、

前記第1の表示部は、前記第1のゲートドライバおよび前記第2のゲートドライバから前記第1の走査信号および前記第2の走査信号がそれぞれ出力されて表示を行う機能を有し、

前記第2の表示部は、前記第1のゲートドライバが出力する前記第1の走査信号、および前記第2のゲートドライバが出力する前記第2の走査信号を停止して表示を行う機能を有する表示装置。

**【請求項 2】**

請求項1において、

前記信号生成回路は、前記第1のゲートドライバから前記表示部への前記第1の走査信号の出力または停止を制御する信号を出力する機能と、前記第2のゲートドライバから任意の行の前記画素への前記第2の走査信号の出力または停止を制御する信号を出力する機能と、を有する表示装置。

**【請求項 3】**

請求項1または2において、

前記第1の画素回路および前記第2の画素回路は、トランジスタを有し、

前記トランジスタは、半導体層に金属酸化物を有する表示装置。

**【請求項 4】**

請求項3において、

前記第1の画素回路が有するトランジスタは、前記第2の画素回路が有するトランジスタと同層に設けられる表示装置。

**【請求項 5】**

請求項1乃至4のいずれか一項において、

前記液晶素子は、開口が設けられた反射電極を有し、前記反射電極で外光を反射して表示を行う機能を有し、

前記発光素子は、前記開口を通じて光を射出して表示を行う機能を有する表示装置。

**【請求項 6】**

信号生成回路と、第1のゲートドライバと、第2のゲートドライバと、画素を有する表示部と、を有する表示装置と、

筐体と、を有し、

前記画素は、液晶素子と、発光素子と、前記液晶素子の表示を制御する第1の画素回路と、前記発光素子の表示を制御する第2の画素回路と、を有し、

前記表示部は、第1の表示部と、第2の表示部と、第3の表示部と、を有し、

前記第1のゲートドライバは、前記第1の表示部乃至前記第3の表示部が有する前記画素の前記第1の画素回路に前記第1の走査信号を出力する機能を有し、

前記第2のゲートドライバは、前記第1の表示部乃至前記第3の表示部が有する前記画素の前記第2の画素回路に前記第2の走査信号を出力する機能を有し、

前記第1の表示部は、平面に画像を表示する領域であり、

前記第2の表示部は、前記第1の表示部に隣接し、且つ曲面に画像を表示する領域であり、

10

20

30

40

50

前記第3の表示部は、前記第2の表示部に隣接し、且つ平面に画像を表示する領域であり、

前記第1の表示部および前記第2の表示部は、前記第1のゲートドライバおよび前記第2のゲートドライバから前記第1の走査信号および前記第2の走査信号がそれぞれ出力されて表示を行う機能を有し、

前記第3の表示部は、前記第1のゲートドライバが出力する前記第1の走査信号、および前記第2のゲートドライバが出力する前記第2の走査信号を停止して表示を行う機能を有する電子機器。

#### 【請求項7】

請求項6において、

前記信号生成回路は、前記第1のゲートドライバから前記表示部への前記第1の走査信号の出力または停止を制御する信号を出力する機能と、前記第2のゲートドライバから任意の行の前記画素への前記第2の走査信号の出力または停止を制御する信号を出力する機能と、を有する電子機器。

#### 【請求項8】

請求項6または7において、

前記筐体は、第1の筐体と、第2の筐体と、第3の筐体と、を有し、

前記第1の表示部は、前記第1の筐体に設けられ、

前記第2の表示部は、前記第2の筐体に設けられ、

前記第3の表示部は、前記第3の筐体に設けられ、

前記第2の筐体は、前記第1の筐体および前記第3の筐体より薄い構造を有する電子機器。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明の一態様は、表示装置および電子機器に関する。

##### 【背景技術】

##### 【0002】

表示装置を備えた電子機器が普及している。このような電子機器は、持ち歩いて使用する場合、二次電池を電源に用いる。二次電池が電源を供給可能な期間を延ばすために、表示装置の低消費電力化が有効である。

##### 【0003】

表示装置の低消費電力化を図るために特許文献1では、反射型素子と発光型素子を組み合わせた、表示装置が提案されている（特許文献1）。明るい環境では反射型素子、暗い環境では発光型素子を用いることで、外光環境に依存しない良好な表示品質と、消費電力が少ない表示装置、を提供することができる。

##### 【0004】

酸化物半導体トランジスタ（oxide semiconductorトランジスタ、以下、OSトランジスタと呼称する）を、液晶表示装置や有機EL（エレクトロルミネッセンス）表示装置などの表示装置に用いる技術が提案されている。OSトランジスタはオフ電流が非常に小さいため、静止画を表示する際のリフレッシュ頻度を少なくし、液晶表示装置や有機EL表示装置の消費電力を低減する技術が開示されている（特許文献2、特許文献3）。なお、本明細書において、上述の表示装置の消費電力を減らす技術を、「アイドリング・ストップ」または「IDS駆動」と呼称する。

##### 【先行技術文献】

##### 【特許文献】

##### 【0005】

【特許文献1】特開2003-157026号公報

【特許文献2】特開2011-141522号公報

【特許文献3】特開2011-141524号公報

10

20

30

40

50

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

IDS駆動は、情報の更新を間欠的に行うため、低消費電力化に有効である。しかしながら、情報の更新の頻度が減るため、利便性に欠く虞がある。利便性を高めるためには、情報の更新が必要な部分の表示を更新する構成が重要となる。

**【0007】**

本発明の一態様は、低消費電力化と利便性に優れた表示装置および電子機器を提供することを課題の一とする。本発明の一態様は、屋外または屋内に限らず視認性に優れた表示装置および電子機器を提供することを課題の一とする。

10

**【0008】**

これらの課題の記載は、他の課題の存在を妨げるものではない。本発明の一態様は、これらの課題の全てを解決する必要はないものとする。これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

**【課題を解決するための手段】****【0009】**

本発明の一態様は、信号生成回路と、第1のゲートドライバと、第2のゲートドライバと、画素を有する表示部と、を有し、画素は、液晶素子と、発光素子と、液晶素子の表示を制御する第1の画素回路と、発光素子の表示を制御する第2の画素回路と、を有し、表示部は、第1の表示部と、第2の表示部と、を有し、第1のゲートドライバは、第1の画素回路に第1の走査信号を出力する機能を有し、第2のゲートドライバは、第2の画素回路に第2の走査信号を出力する機能を有し、第1の表示部は、第1のゲートドライバおよび第2のゲートドライバから第1の走査信号および第2の走査信号がそれぞれ出力されて表示を行う機能を有し、第2の表示部は、第1のゲートドライバが出力する第1の走査信号、および第2のゲートドライバが出力する第2の走査信号を停止して表示を行う機能を有する表示装置である。

20

**【0010】**

本発明の一態様において、信号生成回路は、第1のゲートドライバから表示部への第1の走査信号の出力または停止を制御する信号を出力する機能と、第2のゲートドライバから任意の行の画素への第2の走査信号の出力または停止を制御する信号を出力する機能と、を有する表示装置が好ましい。

30

**【0011】**

本発明の一態様において、第1の画素回路および第2の画素回路は、トランジスタを有し、トランジスタは、半導体層に金属酸化物を有する表示装置が好ましい。

**【0012】**

本発明の一態様において、第1の画素回路が有するトランジスタは、第2の画素回路が有するトランジスタと同層に設けられる表示装置が好ましい。

**【0013】**

本発明の一態様において、液晶素子は、開口が設けられた反射電極を有し、反射電極で外光を反射して表示を行う機能を有し、発光素子は、開口を通じて光を射出して表示を行う機能を有する表示装置が好ましい。

40

**【0014】**

本発明の一態様は、信号生成回路と、第1のゲートドライバと、第2のゲートドライバと、画素を有する表示部と、を有する表示装置と、筐体と、を有し、画素は、液晶素子と、発光素子と、液晶素子の表示を制御する第1の画素回路と、発光素子の表示を制御する第2の画素回路と、を有し、表示部は、第1の表示部と、第2の表示部と、第3の表示部と、を有し、第1のゲートドライバは、第1の表示部乃至第3の表示部が有する画素の第1の画素回路に第1の走査信号を出力する機能を有し、第2のゲートドライバは、第1の表示部乃至第3の表示部が有する画素の第2の画素回路に第2の走査信号を出力する機能

50

を有し、第1の表示部は、平面に画像を表示する領域であり、第2の表示部は、第1の表示部に隣接し、且つ曲面に画像を表示する領域であり、第3の表示部は、第2の表示部に隣接し、且つ平面に画像を表示する領域であり、第1の表示部および第2の表示部は、第1のゲートドライバおよび第2のゲートドライバから第1の走査信号および第2の走査信号がそれぞれ出力されて表示を行う機能を有し、第3の表示部は、第1のゲートドライバが出力する第1の走査信号、および第2のゲートドライバが出力する第2の走査信号を停止して表示を行う機能を有する電子機器である。

【0015】

本発明の一態様において、信号生成回路は、第1のゲートドライバから表示部への第1の走査信号の出力または停止を制御する信号を出力する機能と、第2のゲートドライバから任意の行の画素への第2の走査信号の出力または停止を制御する信号を出力する機能と、を有する電子機器が好ましい。10

【0016】

本発明の一態様において、筐体は、第1の筐体と、第2の筐体と、第3の筐体と、を有し、第1の表示部は、第1の筐体に設けられ、第2の表示部は、第2の筐体に設けられ、第3の表示部は、第3の筐体に設けられ、第2の筐体は、第1の筐体および第3の筐体より薄い構造を有する電子機器が好ましい。

【0017】

なおその他の本発明の一態様については、以下で述べる実施の形態における説明、および図面に記載されている。20

【発明の効果】

【0018】

本発明の一態様は、低消費電力化と利便性に優れた表示装置および電子機器を提供することができる。本発明の一態様は、屋外または屋内に限らず視認性に優れた表示装置および電子機器を提供することができる。

【図面の簡単な説明】

【0019】

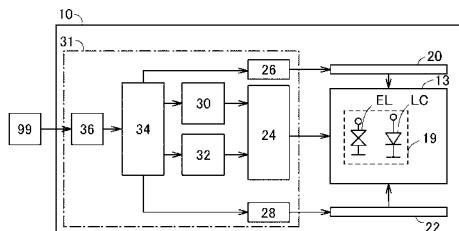

【図1】表示装置の構成例を示す図。

【図2】表示装置の構成例を示す図。

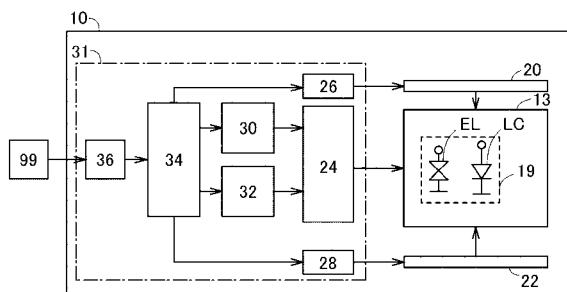

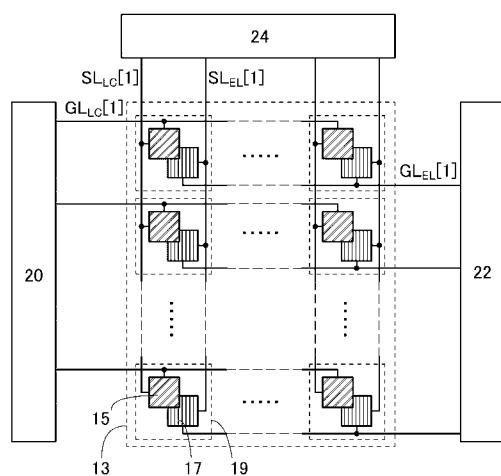

【図3】表示装置の画素の構成例を示す図。

30

【図4】表示装置の構成例を説明する図。

【図5】表示装置の動作例を説明する図。

【図6】表示装置の動作例を説明する図。

【図7】表示装置の動作例を説明する図。

【図8】表示装置の構成例を説明する、模式図及び状態遷移図。

【図9】表示装置の動作例を示す図。

【図10】表示装置の動作例を示す図。

【図11】表示装置の構成例を説明する、回路図。

【図12】表示装置の構成例を説明する、回路図。

40

【図13】表示装置の駆動回路の動作例を示す図。

【図14】表示装置の構成例を説明する図。

【図15】表示装置の回路図。

【図16】表示装置の構成例を説明する図。

【図17】表示装置の構成例を説明する図。

【図18】表示装置の構成例を説明する図。

【図19】入出力パネルの構成例を説明する図。

【図20】入出力パネルの構成例を説明する図。

【図21】試料のXRDスペクトルの測定結果を説明する図。

【図22】試料のTEM像、および電子線回折パターンを説明する図。

【図23】試料のEDXマッピングを説明する図。

50

【図24】表示モジュールの構成例を説明する図。

【図25】電子機器の構成例を説明する図。

【発明を実施するための形態】

【0020】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0021】

(実施の形態1)

10

<表示装置の構成>

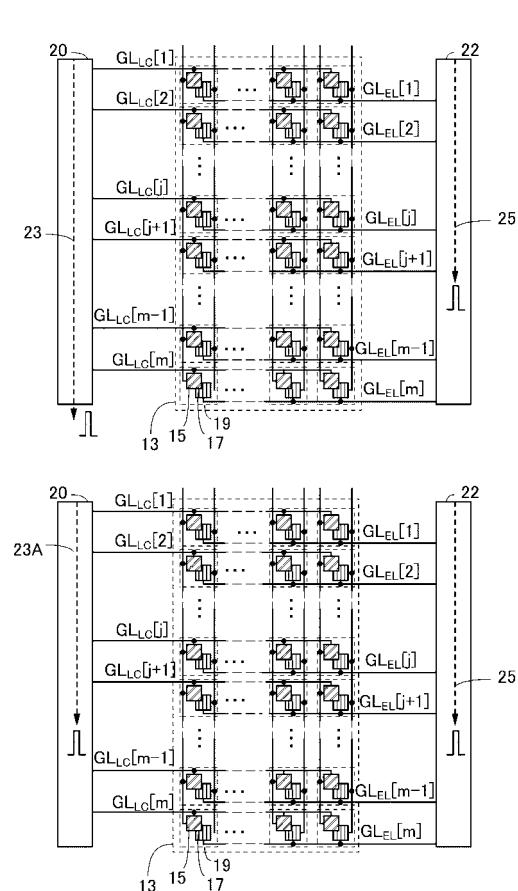

図1は、表示装置の構成を説明するためのブロック図である。表示装置10は、ソースドライバIC31、ゲートドライバ20、ゲートドライバ22、および表示部13を有する。

【0022】

表示部13は、画素19(または副画素)を有する。画素19は、反射型表示素子である液晶素子LC、および発光型表示素子である発光素子ELを有する。液晶素子LCは、発光素子ELと重なる領域を有する。上記重なる領域において、発光素子ELから発せられた光が、液晶素子LCを通過する構成を有している。発光素子ELおよび液晶素子LCは、画素19ごとに設けられる。

20

【0023】

本明細書等において、画素とは、例えば、明るさを制御できる要素一つ分を示すものとする。よって、一例としては、一画素とは、一つの色要素を示すものとし、その色要素一つで明るさを表現する。従って、そのときは、R(赤)G(緑)B(青)の色要素からなるカラー表示装置の場合には、画像の最小単位は、Rの画素とGの画素とBの画素との三画素から構成されるものとする。この場合、RGBのそれぞれの画素は副画素と呼び、RGBの副画素を併せて画素と呼ぶ。

【0024】

ソースドライバIC31は、ソースドライバ24、信号生成回路26、信号生成回路28、フレームメモリ30、フレームメモリ32、制御回路34およびインターフェース36を有する。

30

【0025】

ソースドライバIC31は、アプリケーションプロセッサ99から画像を表示するための信号(画像データ)等を受信する。アプリケーションプロセッサ99は、画像データを所定の形式の信号に変換してインターフェース36に出力する機能を有する。インターフェース36は、LVDS(Low Voltage Differential Signaling)、MIPI(Mobile Industry Processor Interface)などに即した信号に変換する回路が挙げられる。

【0026】

フレームメモリ30およびフレームメモリ32は、インターフェース36を経て制御回路34より入力される1フレーム分の画像データを一時的に記憶するための回路である。図1では複数のフレームメモリを図示しているが1つでもよい。またラインメモリを用いることも可能である。フレームメモリのメモリセルは、SRAM(Static RAM)またはDRAM(Dynamic RAM)を用いることができる。DRAMのトランジスタはオフ電流の小さいトランジスタを用いることで、リフレッシュ頻度を低減できるため低消費電力を図る上で好ましい。

40

【0027】

信号生成回路26は、ゲートドライバ20が出力する走査信号を制御するための信号を生成する回路である。信号生成回路28は、ゲートドライバ22が出力する走査信号を制御するための信号を生成する回路である。信号生成回路26および信号生成回路28は、

50

ゲートドライバ20およびゲートドライバ22にクロック信号CLK、パルス幅制御信号PWC、リセット信号RES、およびスタートパルス等の信号を出力し、走査信号の出力を制御する。

#### 【0028】

例えば信号生成回路26または信号生成回路28は、パルス幅制御信号PWCおよびクロック信号CLKをLレベルに固定することで、ゲートドライバ20またはゲートドライバ22より出力される走査信号をLレベルとする期間を設けることができ、画素に書き込む画像データのリフレッシュレートを小さくできる。なおゲートドライバ20またはゲートドライバ22において、走査信号として出力されるパルス信号をLレベルの信号とすることを、走査信号の出力を停止させるともいう。

10

#### 【0029】

また、信号生成回路26または信号生成回路28は、任意の行に対応するパルス幅制御信号PWCをLレベルに固定することで、ゲートドライバ20またはゲートドライバ22の任意の行より出力される走査信号をLレベルとする期間を設けることができ、走査信号を一部の行に出力する動作と、その他の行に出力する走査信号をLレベルの信号とすることができます。なおゲートドライバ20またはゲートドライバ22において、任意の行に出力される走査信号として出力されるパルス信号をLレベルの信号とすることを、任意の行の画素への走査信号の出力を停止させるともいう。

20

#### 【0030】

ソースドライバ24は、各列のソース線に画像データに基づく電圧（ビデオ電圧）を与えるための回路である。ゲートドライバ20は、選択した行にある画素において、液晶素子LCを駆動するための画素回路にソース線に与えたビデオ電圧を書き込むための走査信号を出力する回路である。ゲートドライバ22は、選択した行にある画素において、発光素子ELを駆動するための画素回路にソース線に与えたビデオ電圧を書き込むための走査信号を出力する回路である。液晶素子LCを駆動するための画素回路にビデオ電圧が書き込まれることで、表示部13は画像を表示することができる。また、発光素子ELを駆動するための画素回路にビデオ電圧が書き込まれることで、表示部13は画像を表示することができる。なお画素回路とは、画素において、ビデオ電圧が書き込まれることで液晶素子あるいは発光素子等の表示素子の階調を制御するための回路である。

30

#### 【0031】

図1に示す表示装置10では、表示部13の表示部ごとにゲート線への走査信号の出力と停止を選択的に切り替えて、画像を表示することができる。例えば表示部13がm行（mは2以上の自然数）のゲート線に接続された画素を有する場合、1行目からk行目（kはm未満の自然数）までのゲート線に接続される表示部（第1の表示部ともいう）にある画素に走査信号を出力し、（k+1）行目からm行目までのゲート線に接続される表示部（第2の表示部ともいう）にある画素への走査信号を停止する構成とするよう、信号生成回路26または信号生成回路28から出力される信号を制御する。このように走査信号の出力または停止は、ゲートドライバ20またはゲートドライバ22の任意の行のゲート線ごとに制御することができる。つまり表示素子の階調を制御する画素回路ごとに走査信号の出力または停止を制御して、表示をすることができる。

40

#### 【0032】

具体的に図1に示す表示装置10では、第1の表示部では発光素子ELおよび液晶素子LCとの双方による表示を行うようゲートドライバ20およびゲートドライバ22の双方より走査信号を出力し、第2の表示部では液晶素子LCのみによる表示を行うようゲートドライバ20より走査信号を出力し、発光素子ELによる表示を行わないようゲートドライバ22からの走査信号を停止させて、表示を行うことができる。つまり、ゲートドライバ20は全行のゲート線に走査信号を出力する一方で、ゲートドライバ22は第1の表示部にあるゲート線に走査信号を出力する一方で、第2の表示部にあるゲート線への走査信号を停止するよう、信号生成回路26および信号生成回路28から出力するパルス幅制御信号PWCおよびクロック信号CLKといった制御信号を切り替えて動作させる。

50

## 【0033】

上述した、反射型表示素子である液晶素子LCを用いて表示を行う第2の表示部は、情報の更新する頻度の小さい表示とすることが好適である。液晶素子LCで表示を行う場合、IDS駆動を用いて表示を行うことで情報の更新を間欠的に行い、情報の更新を行わない分の低消費電力化を図ることができる。または、反射型表示素子である液晶素子LCは画像を表示する際に光源として外光を利用することができるため、別途光源の必要がなく、さらなる消費電力の低減に有効である。

## 【0034】

なお上述の情報とは、画素が有する各表示部で表示される情報である。つまり各表示部に入力される画像データに相当する。また情報の更新とは、画素が有する各表示部で表示される情報を更新することである。つまり各表示部に入力される画像データの書き換え(リフレッシュ)頻度に相当する。

10

## 【0035】

また上述した、発光素子ELおよび/または液晶素子LCを用いて表示を行う第1の表示部は、情報の更新する頻度の高い表示とすることが好適である。発光素子ELおよび/または液晶素子LCで表示を行う場合、外光の強度が低い場合でも暗い環境下であっても視認性の高い表示状態に切り替えて情報の更新を行うため、低消費電力化と利便性に優れた表示装置とすることができます。

## 【0036】

20

## &lt;表示部の構成&gt;

図2は、表示装置10が有する表示部13の構成を説明するためのブロック図である。表示部13は、複数の画素19を有する。画素19は、画素回路15および画素回路17を有する。また図2は、図1で示すソースドライバ24、ゲートドライバ20およびゲートドライバ22を図示している。

## 【0037】

30

画素回路15は、ビデオ電圧が書き込まれることで液晶素子LC(図示せず)による階調を制御するための回路である。画素回路15は、トランジスタおよび容量素子を有する。画素回路15に書き込まれるビデオ電圧は、ソース線SLLCを介して与えられる。画素回路15にビデオ電圧を書き込むための走査信号は、ゲートドライバ20よりゲート線GLLCを介して与えられる。

## 【0038】

40

画素回路17は、ビデオ電圧が書き込まれることで発光素子EL(図示せず)による階調を制御するための回路である。画素回路17は、トランジスタおよび容量素子を有する。画素回路17に書き込まれるビデオ電圧は、ソース線SLELを介して与えられる。画素回路17にビデオ電圧を書き込むための走査信号は、ゲートドライバ22よりゲート線GLENを介して与えられる。

## 【0039】

なお図面等において、ソース線SLEL、ソース線SLLC、ゲート線GLLCおよびゲート線GLENは、ソース線SLEL[1]、ソース線SLLC[1]、ゲート線GLLC[1]およびゲート線GLEN[1]として図示しているが、これらは1行目または1列目を表している。なお画素19をm行n列(m、nは共に自然数)で表す場合、表示部13が有する画素は、ソース線SLEL[1]乃至[n]のいずれか一列、ソース線SLLC[1]乃至[n]のいずれか一列、ゲート線GLLC[1]乃至[m]のいずれか一行およびゲート線GLEN[1]乃至[m]のいずれか一行に接続される。

## 【0040】

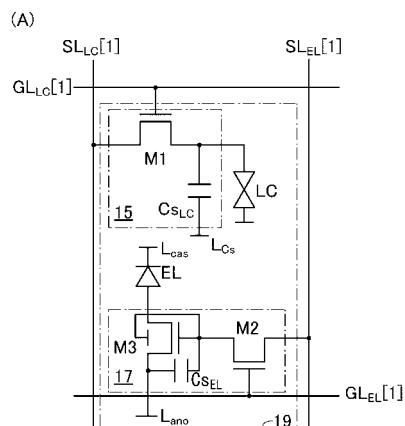

次いで画素19の回路について説明する。図3(A)は、画素19の回路図の一例である。画素19は、画素回路15、画素回路17、液晶素子LCおよび発光素子ELを有する。

## 【0041】

50

図3(A)において、画素回路15は、トランジスタM1および容量素子C<sub>SLLC</sub>を有

する。画素回路 17 は、トランジスタ M2、M3 および容量素子 CSEL を有する。画素 19 が有する各素子は、図 3 (A) に示すように、ゲート線 GLLC[1]、ゲート線 GLEL[1]、信号線 SLLC[1]、信号線 SEL[1]、容量線 LCS、電流供給線 Lano、および共通電位線 Lcas に接続される。

#### 【0042】

なお容量素子 CSEL は、発光素子 EL を駆動するための階調電圧をトランジスタ M3 のゲートに保持するために設けている。このような構成とすることで、発光素子 EL を駆動するための階調電圧の保持をより確実に行うことができる。

#### 【0043】

なおトランジスタ M3 は、バックゲートを有するトランジスタとしている。このような構成とすることで、トランジスタを流れる電流量を大きくすることができる。なおバックゲートに与える電圧は、別の配線から与える構成としてもよい。このような構成とすることで、トランジスタの閾値電圧のコントロールすることができる。

#### 【0044】

トランジスタ M1 は、導通状態を制御することで、液晶素子 LC を駆動するための階調電圧を容量素子 CSLC に与える。トランジスタ M2 は、導通状態を制御することで、発光素子 EL を駆動するための階調電圧をトランジスタ M3 のゲートに与える。トランジスタ M3 は、ゲートの電圧に応じて電流供給線 Lano と共に電位線 Lcas との間に電流を流して発光素子 EL を駆動する。

#### 【0045】

トランジスタ M1 乃至 M3 は、n チャネル型トランジスタを用いることができる。n チャネル型トランジスタは、各配線の電圧の大小関係を変えることで、p チャネル型トランジスタに置き換えることもできる。トランジスタ M1 乃至 M3 の半導体材料は、シリコンを用いることができる。シリコンは、単結晶シリコン、ポリシリコン、微結晶シリコンまたはアモルファスシリコンなどを適宜選択して用いることができる。

#### 【0046】

あるいはトランジスタ M1 乃至 M3 の半導体材料は、酸化物半導体を用いることができる。酸化物半導体は、インジウムを含む酸化物半導体またはインジウムとガリウムと亜鉛を含む酸化物半導体などを用いることができる。

#### 【0047】

また画素 19 が有するトランジスタ M1 乃至 M3 は、ボトムゲート型のトランジスタや、トップゲート型トランジスタなどの様々な形態のトランジスタを用いて作製することができる。

#### 【0048】

また画素 19 が有するトランジスタ M1 乃至 M3 を、バックゲートを有するトランジスタとしてもよい。バックゲートに与える電圧は、ゲート線 GLLC[j] やゲート線 GLEL[j] とは異なる、別の配線から与える構成としてもよい。また、バックゲートを有するトランジスタは、トランジスタ M3 だけというように限定してもよい。このような構成とすることで、トランジスタの閾値電圧のコントロール、あるいはトランジスタを流れる電流量を大きくすることができる。

#### 【0049】

液晶素子 LC は、IPS (In-Plane-Switching) モード、TN (Twisted Nematic) モード、FFS (Fringe Field Switching) モード、ASM (Axially Symmetric aligned Micro-cell) モード、OCB (Optically Compensated Birefringence) モード、FLC (Ferroelectric Liquid Crystal) モード、AFLC (AntiFerroelectric Liquid Crystal) モードなどを用いることができる。または、垂直配向 (VA) モード、ECB (Electrically Controlled Birefringence) モード、ゲストホストモード等を用いることができる。

10

20

30

40

50

## 【0050】

液晶素子が有する液晶材料には、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶等を用いることができる。または、コレステリック相、スマートチック相、キュービック相、カイラルネマチック相、等方相等を示す液晶材料を用いることができる。または、ブルー相を示す液晶材料を用いることができる。

## 【0051】

なお発光素子ELとしては、有機エレクトロルミネッセンス素子、無機エレクトロルミネッセンス素子等のEL素子の他、または発光ダイオードなどを用いることができる。

## 【0052】

EL素子は、白色の光を射出するように積層された積層体を用いることができる。具体的には、青色の光を射出する蛍光材料を含む発光性の有機化合物を含む層と、緑色および赤色の光を射出する蛍光材料以外の材料を含む層または黄色の光を射出する蛍光材料以外の材料を含む層と、を積層した積層体を、用いることができる。

10

## 【0053】

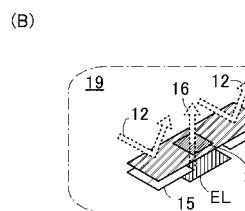

次いで画素19の層構造の模式図について説明する。図3(B)に示す画素19では、画素回路15、画素回路17、液晶素子LCおよび発光素子ELの配置を示している。図3(B)に示す液晶素子LCは開口21を有する。この開口21は、反射電極に設けられる開口を表している。図3(B)に示す発光素子ELは、液晶素子LCが有する開口21に重ねて設けられる。図3(B)に示す画素回路15および画素回路17は、液晶素子LCが設けられる層と発光素子ELが設けられる層の間に設けられる。なお図3(B)に示す画素回路15および画素回路17は、異なる層に設けられてもよい。

20

## 【0054】

図3(B)に示す構成とすることで画素19は、液晶素子LCによる反射光12の強度の制御と、開口21を透過する発光素子ELの発する光16の強度の制御と、によって階調を制御することができる。なお反射光12が射出される方向および発光素子ELが発する光16が射出される方向は、表示装置10の表示面となる。なお発光素子ELの発する光16を射出するために液晶素子LCの反射電極に設けられる開口21は、光16が射出される構成であればよく、開口に限らず反射電極に形成した切欠きあるいはスリット状の形状とすることもできる。

30

## 【0055】

図3(B)に示す構成では、液晶素子LCが有する反射電極の下に画素回路15および画素回路17といった画素を駆動するための回路を配置することができる。そのため、発光素子ELを駆動するための画素回路17が増える分の開口率の低下を抑制することができる。

## 【0056】

また図3(B)に示す構成では、画素19ごとに液晶素子LCを制御することができる画素回路15、及び発光素子ELを制御することができる画素回路17を有する。つまり、画素19ごとに液晶素子LCおよび発光素子ELの階調表示を別々に制御することができる。このような構成では、複数の画素で一様に点灯するバックライトの制御とは異なり、表示する画像に応じた発光素子ELの発光を画素レベルといった最小単位で制御することができるため、余分な発光を抑えることができる。そのため図3(B)の画素を有する表示装置は、低消費電力化を図ることができる。

40

## 【0057】

なお画素回路15および画素回路17は、階調表示を制御するためのトランジスタを有する。当該トランジスタとしてチャネル形成領域に金属酸化物を有するトランジスタを用いる構成とすることが好適である。金属酸化物は、酸化物半導体として機能し、当該酸化物半導体をチャネル形成領域に有するOSトランジスタは、オフ電流が極めて低い。そのため、表示装置で静止画表示を行う場合、画素回路でビデオ電圧に応じた電荷を長時間保持することができる。画素回路内にビデオ電圧に応じた電荷を長時間保持できる構成とす

50

ることで、画素の書き換え頻度（リフレッシュレート）を減らせる（例えばフレームレート30Hz以下）ため、低消費電力化を図ることができる。

#### 【0058】

##### <表示装置の動作例>

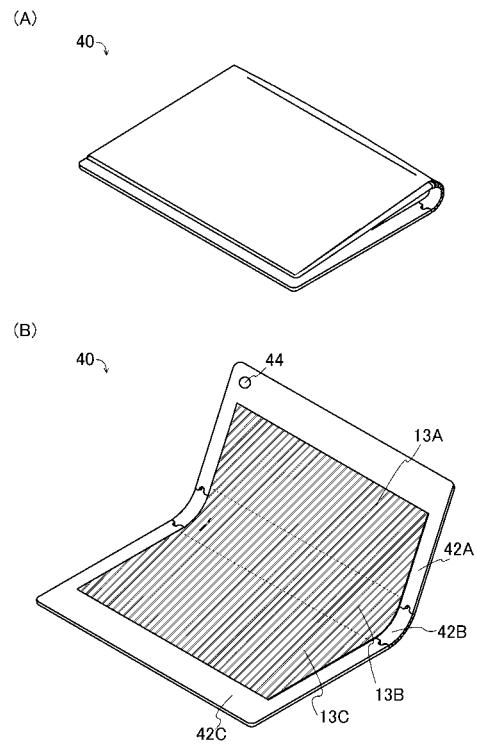

次いで図1に示す表示装置の動作について、当該表示装置を備えた電子機器を挙げて説明する。図4(A)、(B)には、図1の表示装置を備えた電子機器40を示す。図4(A)、(B)に示す電子機器は、図4(A)に示すように、クラムシェル型のノート型コンピュータのように、表示部が重なって折り畳む（フォーダブル：Foldable）ことが可能な構造を有する。

#### 【0059】

なお図4(A)に示す折り畳んだ状態では、折り曲げ部の曲率半径が0( $R=0$ )とするのではなく、折り畳んだ状態での折り曲げ部の形状が緩やかな曲面となるよう曲率半径が5mm以上30mm以下とすることが好ましい。当該構成とすることで、表示装置の折り曲げによる破断を抑制することができる。なお外力による折り曲げ部の想定を超えた変形を抑制するように、ロック機能を設けることが好ましい。

#### 【0060】

図4(B)に示す電子機器40は、筐体内に図1の表示装置10を具備し、表示部を視認することができる。なお図5(B)において表示部は、表示部13A、表示部13Bおよび表示部13Cに分けて図示している。なお図5(B)において電子機器40の筐体は、筐体42A、筐体42Bおよび筐体42Cに分けて図示している。その他の構成として電子機器40は、光センサ44を図示している。

#### 【0061】

筐体42Aと筐体42Cとは、筐体42Bで連結されている。筐体42A乃至42Cを組み合わせた際の長軸方向の両辺に図1のゲートドライバ20、22が配置される。筐体42Bは、電子機器40におけるヒンジとして機能し、表示部13Aとび表示部13Cとを重ねることで折り畳むことが可能な構造とすることができます。これにより、持ち運ぶ際には可搬性に優れ、使用するときには大きな表示部により、視認性に優れる電子機器とすることができます。

#### 【0062】

ヒンジとして機能する筐体42Bは、筐体42Aと筐体42Cとを開いたときに、これらの角度が所定の角度よりも大きい角度にならないように、ロック機構を有することが好ましい。例えば、ロックがかかる（それ以上に開かない）角度は、90度以上180度未満であることが好ましく、代表的には、90度、120度、135度、または150度などとすることができます。これにより、利便性、安全性、及び信頼性を高めることができる。筐体42A乃至42Cの構成例については、後述する。

#### 【0063】

表示部として機能する表示部13A、表示部13Bおよび表示部13Cは、タッチパネルとして機能し、指やスタイラスなどにより操作することができる。

#### 【0064】

表示部として機能する表示部13A、表示部13Bおよび表示部13Cは、一つのフレキシブルディスプレイとして組み込まれる。これにより、表示部13A、表示部13Bおよび表示部13Cは、途切れることのない連続した表示を行うことができる。また表示部13Bは、その少なくとも一部が湾曲し、曲面を有せしめることができる。

#### 【0065】

曲面を有する表示部13Bは、平面を有する表示部13Aおよび表示部13Cとの間に切れ目なく設けられる。当該構成により、表示する画像をより立体的に表示させることができる。

#### 【0066】

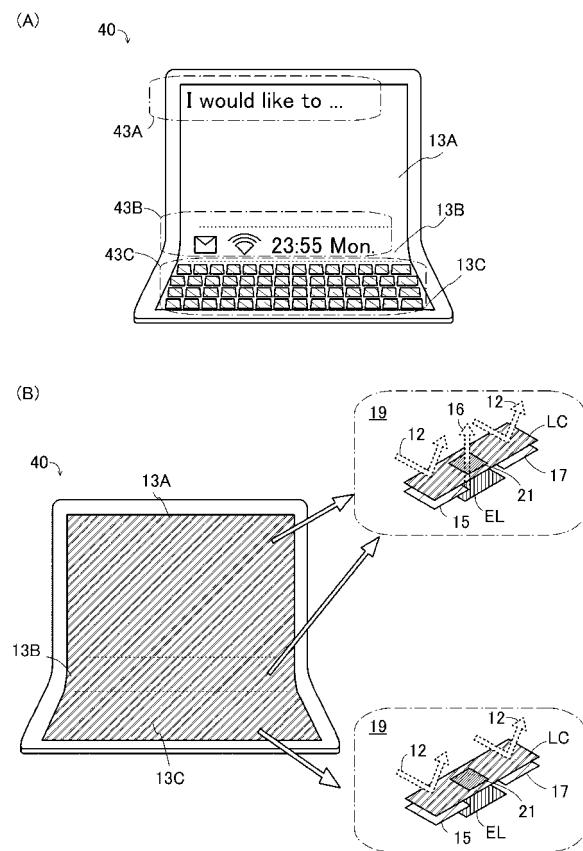

図5(A)は、図4(A)、(B)に示す電子機器40の使用例について説明するための図である。図5(A)では、表示部13A、表示部13Bおよび表示部13Cに分けて

10

20

30

40

50

図示する画像を異ならせた例を図示している。平面を有する表示部 13A では、テキスト 43A を表示した図を図示している。曲面を有する表示部 13B では、アイコン 43B 等を表示した図を図示している。平面を有する表示部 13C では、入力キー 43C を表示した図を図示している。

#### 【0067】

なお図 5(A) では一例として、表示部 13A にテキスト 43A を示したが、動画等の情報の更新が必要な表示を行う領域とすることが好ましい。また図 5(A) では一例として、表示部 13B にアイコン 43B を示したが、表示部 13A と同様に、動画等の情報の更新が必要な表示を行う領域としてもよい。また図 5(A) では一例として、表示部 13C に入力キー 43C を示したが、リフレッシュレートの小さい静止画等とすることが好ましい。なお表示部 13C を動画等の情報の更新が必要な表示を行う領域としてもよい。表示する画像および周辺環境における外光の有無に応じて、表示部 13A、表示部 13B および表示部 13C でリフレッシュレートおよび表示モードの切り替えを行うことが利便性および低消費電力の点で好ましい。

10

#### 【0068】

図 5(A) で図示する電子機器 40 について、図 5(B) に改めて図示する。図 5(A) で示す電子機器 40 における表示部 13A、表示部 13B および表示部 13C では、情報の更新が必要な領域と情報の更新が継続して必要な領域とに分けることができる。例えば、図 5(A) で図示するテキスト 43A およびアイコン 43B を図示する表示部 13A および表示部 13B では、図 5(B) に図示するように、液晶素子 LC の反射光 12 および発光素子 EL の光 16 を利用した表示を行う構成とする。また図 5(A) で図示する入力キー 43C を図示する表示部 13C では、図 5(B) に図示するように、情報の更新が継続して不要な領域とし、液晶素子 LC による表示の更新を間欠的、つまりリフレッシュレートを小さくして表示を行う。つまり図 5(B) に図示するように、液晶素子 LC による反射光 12 を利用した表示を行う構成とする。

20

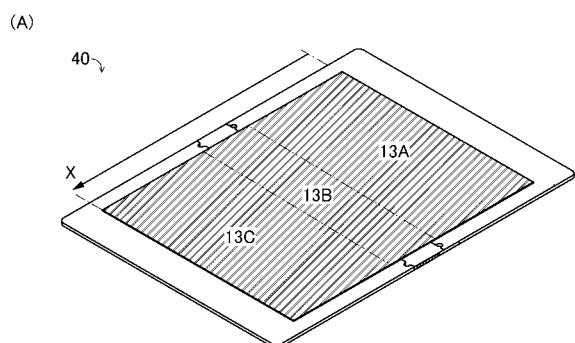

#### 【0069】

図 6(A) に図示する電子機器 40 は、表示部 13A、表示部 13B および表示部 13C を有する表示部を平面となるように変形したものである。なお図 6(A) に図示する電子機器 40 では、表示装置 10 が有するゲートドライバ 20 および 22 は、矢印 X に平行な方向に表示部の両辺に配置され、表示部 13A にある画素から順に、表示部 13B および表示部 13C にかけて走査信号を出力する構成とする。図 6(A) に図示するように、図 4(A)、(B) および図 5(A)、(B) に図示する電子機器 40 は、タブレット型の電子機器の形状に変形して用いることもできる。

30

#### 【0070】

図 6(B) には、表示部 13 および周辺の駆動回路のブロック図を図示する。図 6(B) に示す表示部 13 は、複数の画素 19 を有する。画素 19 は、画素回路 15 および画素回路 17 を有する。また図 6(B) は、ソースドライバ 24、ゲートドライバ 20 およびゲートドライバ 22 を図示している。

#### 【0071】

なお図 6(B) では、図 2 と同様に、1 列目のソース線 SLEL[1] およびソース線 SLLC[1]、並びに 1 行目のゲート線 GLLC[1] およびゲート線 GLEL[1] を図示している。加えて、図 6(B) では、2 行目のゲート線 GLLC[2] およびゲート線 GLEL[2]、j 行目 (j は 3 以上 (m - 1) 以下 (m は 5 以上の自然数) の自然数) のゲート線 GLLC[j] およびゲート線 GLEL[j]、j + 1 行目のゲート線 GLLC[j + 1] およびゲート線 GLEL[j + 1]、m - 1 行目のゲート線 GLLC[m - 1] およびゲート線 GLEL[m - 1]、m 行目のゲート線 GLLC[m] およびゲート線 GLEL[m] を図示している。

40

#### 【0072】

なお以下の説明において、図 6(B) に示す 1 行目のゲート線 GLLC[1] およびゲート線 GLEL[1]、ならびに 2 行目のゲート線 GLLC[2] およびゲート線 GLEL[2]

50

L [ 2 ] は、図 6 ( A ) の表示部 13 A の画素に走査信号を与えるゲート線とする。また図 6 ( B ) に示す j 行目のゲート線 GLLC [ j ] およびゲート線 GLEL [ j ] 、ならびに j + 1 行目のゲート線 GLLC [ j + 1 ] およびゲート線 GLEL [ j + 1 ] は、図 6 ( A ) の表示部 13 B の画素に走査信号を与えるゲート線とする。また図 6 ( B ) に示す m - 1 行目のゲート線 GLLC [ m - 1 ] およびゲート線 GLEL [ m - 1 ] 、ならびに m 行目のゲート線 GLLC [ m ] およびゲート線 GLEL [ m ] は、図 6 ( A ) の表示部 13 C の画素に走査信号を与えるゲート線とする。

#### 【 0 0 7 3 】

図 6 ( B ) に図示するブロック図を用いて、図 7 ( A ) 、 ( B ) では、図 6 の動作を行う場合の図 1 の表示装置の動作について説明する。

10

#### 【 0 0 7 4 】

図 7 ( A ) において破線矢印 23 は、ゲートドライバ 20 が走査信号を順次出力する走査方向を可視化したものである。また図 7 ( A ) において破線矢印 25 は、ゲートドライバ 22 が走査信号を順次出力する走査方向を可視化したものである。

20

#### 【 0 0 7 5 】

本発明の一態様の表示装置の動作は、図 7 ( A ) に示すように、図 6 の動作を行う場合において情報の更新が必要な領域において発光素子 EL に書き込んだビデオ電圧の更新を行うように走査信号を出力する構成とする。つまり、ゲートドライバ 20 が破線矢印 23 のように走査信号を全行に順次出力する際に、ゲートドライバ 22 では 1 行目のゲート線 GLEL [ 1 ] 、 2 行目のゲート線 GLEL [ 2 ] 、 j 行目のゲート線 GLEL [ j ] 、 j + 1 行目のゲート線 GLEL [ j + 1 ] から走査信号を出力し、 m - 1 行目のゲート線 GLEL [ m - 1 ] 、 m 行目のゲート線 GLEL [ m ] から走査信号を出力しないように動作させる。ゲートドライバ 22 から選択的に走査信号を出力するよう図 1 の信号生成回路 26 による各制御信号を切り替えて、当該走査信号の出力および停止の切り替えを実現する。

20

#### 【 0 0 7 6 】

また図 7 ( B ) では図 7 ( A ) とは異なる本発明の一態様の表示装置の動作を説明する図である。図 7 ( B ) での動作は、ゲートドライバ 22 と同様に、ゲートドライバ 20 による走査信号の出力を選択的に行わせることで表示部 13 C にある画素への走査信号を一定期間停止し、表示部 13 C の表示の更新を間欠的に行う構成とする。図 7 ( B ) では、図 7 ( A ) で示した破線矢印 23 の一部を図示しない ( 破線矢印 23A ) ことで表示部 13 C にある画素への走査信号の出力の定期的な停止を表している。つまり、ゲートドライバ 20 では 1 行目のゲート線 GLLC [ 1 ] 、 2 行目のゲート線 GLLC [ 2 ] 、 j 行目のゲート線 GLLC [ j ] 、 j + 1 行目のゲート線 GLLC [ j + 1 ] から走査信号を出力し、 m - 1 行目のゲート線 GLLC [ m - 1 ] 、 m 行目のゲート線 GLLC [ m ] から走査信号を出力しないように動作させるとともに、ゲートドライバ 22 では 1 行目のゲート線 GLEL [ 1 ] 、 2 行目のゲート線 GLEL [ 2 ] 、 j 行目のゲート線 GLEL [ j ] 、 j + 1 行目のゲート線 GLEL [ j + 1 ] から走査信号を出力し、 m - 1 行目のゲート線 GLEL [ m - 1 ] 、 m 行目のゲート線 GLEL [ m ] から走査信号を出力しないように動作させる。

30

#### 【 0 0 7 7 】

ゲートドライバ 20 からの上記した走査信号の出力または停止の制御は、図 1 の信号生成回路 26 による各制御信号を切り替えることで実現する。同様にゲートドライバ 22 からの上記した走査信号の出力および停止の制御は、図 1 の信号生成回路 28 による各制御信号を切り替えることで実現する。

40

#### 【 0 0 7 8 】

本発明の一態様に係る表示装置 10 では、情報の更新が必要な表示部において、外光の強度が低い場合でも暗い環境下であっても視認性の高い表示状態に切り替えて表示を行うことができるため、低消費電力化と利便性に優れた表示装置とすることができます。加えて情報の更新が不要な表示部において、発光素子 EL の発光を抑制するとともにビデオ電圧

50

の書き換え頻度を低減することができる。従って、低消費電力化と利便性に優れた表示装置とすることができる。

#### 【0079】

##### <筐体の構成例>

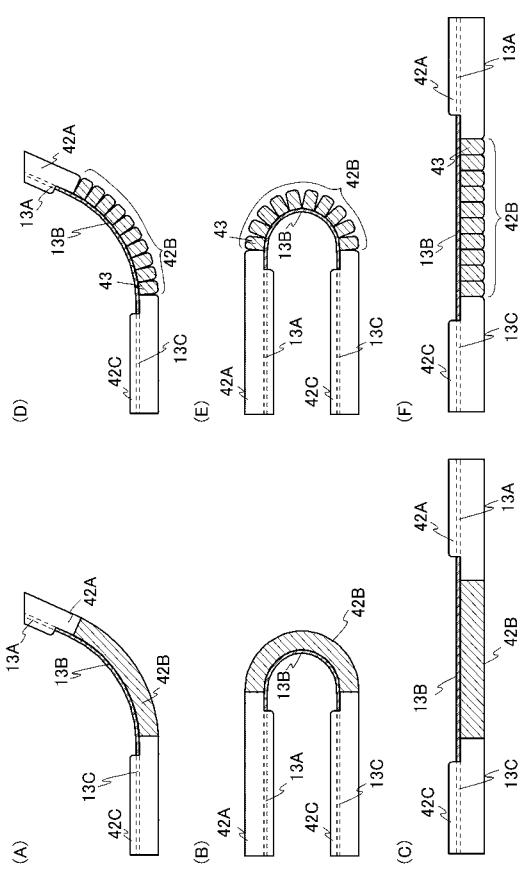

図4(B)等で図示したヒンジとして機能する筐体42Bの構成について、筐体42A乃至42Cの接続部における側面図を図8(A)乃至(C)、図8(D)乃至(F)に図示し、説明する。

#### 【0080】

筐体42Bは、例えば、ばね又はゴムといった弾性体を単体あるいは組み合わせて用いることができる。電子機器40を図4(B)あるいは図8(A)のように折り畳んだ状態では筐体42Bの大きさを自然長の長さとし、図4(A)あるいは図8(B)のように折り畳んだ際に筐体42Bが伸びて他の部分の形状を維持できるようにする。電子機器40を図4(B)あるいは図8(A)のように折り畳んだ状態では筐体42Bの大きさを自然長の長さとし、図6(A)あるいは図8(C)のように表示部を平坦にした際に筐体42Bが縮んで他の部分の形状を維持できるようにする。

10

#### 【0081】

あるいは、筐体42Bは、例えば、複数のスペーサを連結させた構造体を用いることができる。なお複数のスペーサを連結させた構造体は、上述した弾性体と組み合わせて用いることもできる。電子機器40を図4(B)あるいは図8(D)のように表示部の一部を湾曲させた状態では筐体42Bが有するスペーサ43の間隔の大きさを所定の間隔とし、図4(A)あるいは図8(E)のように折り畳む際に前述の間隔より広げてスペーサ43を配置する形状とする。電子機器40を図4(B)あるいは図8(D)のように表示部の一部を湾曲させた状態では筐体42Bが有するスペーサ43の間隔の大きさを所定の間隔とし、図6(A)あるいは図8(F)のように伸ばした際に前述の間隔を狭めてスペーサ43を配置する形状とする。

20

#### 【0082】

なお筐体42Bは、他の箇所、例えば筐体42Aおよび42Cよりも薄い構造とすることが好ましい。当該構成とすることで使用時において、表示部13Bを湾曲しやすくできるとともに、表示部13Aおよび13Cにおける表面の平坦性および耐衝撃性を高めることができる。筐体42Aおよび42Cは、人力などの外力によって変形しない程度の強度とすることが好ましい。当該構成とすることで、表示部13Aおよび13Cの平坦性が十分確保された電子機器とすることができます。

30

#### 【0083】

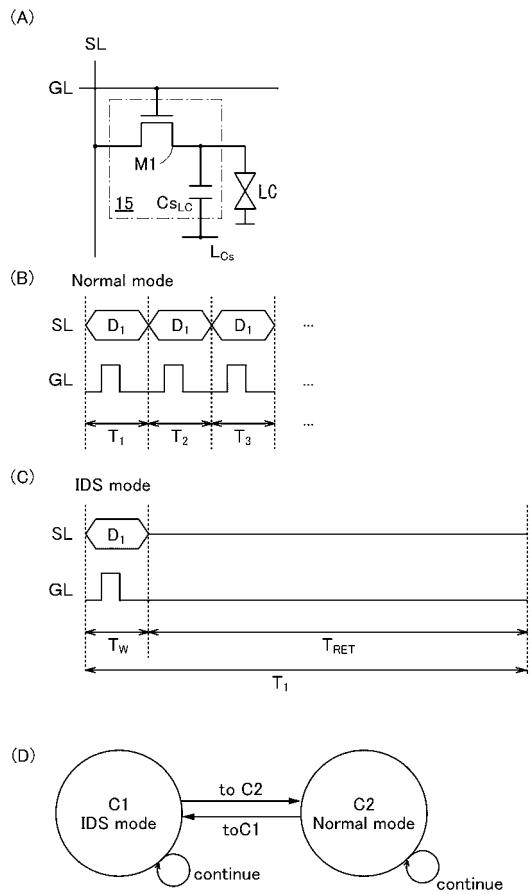

##### <表示装置の表示モード>

図9(A)乃至(D)を用いて、上記表示装置の動作例で説明したリフレッシュレートを小さくする表示モードについて説明する。また図10(A)乃至(E)を用いて、図4(B)で説明した光センサ44を利用した表示モードの切り替えについて説明する。

#### 【0084】

なお上記表示装置の動作例で説明したリフレッシュレートを小さくする表示モードをアイドリング・ストップ(IDS)駆動モードとして以下説明する。なお表示装置10が取り得る表示モードとして、通常のフレーム周波数で動作する通常駆動モード(Normal mode)と、アイドリング・ストップ(IDS)駆動モードと、を挙げて説明する。

40

#### 【0085】

なお、IDS駆動とは、画像データの書き込み処理を実行した後、画像データの書き換えを停止する駆動方法のことをいう。一旦画像データの書き込みをして、その後次の画像データの書き込みまでの間隔を延ばすことで、その間の画像データの書き込みに要する分の消費電力を削減することができる。

#### 【0086】

上述した通常駆動モードとIDS駆動について、図9(A)乃至(D)で一例を挙げて

50

説明する。なお図9(A)乃至(D)では、液晶素子LCおよび画素回路15に通常駆動モードとIDS駆動を適用する場合について説明するが、発光素子ELおよび画素回路17についても通常駆動モードとIDS駆動を適用することが可能である。

#### 【0087】

図9(A)は、液晶素子LCおよび画素回路15で構成される画素の回路図を図示している。図9(A)では、ソース線SLおよびゲート線GLに接続されたトランジスタM1、容量素子C<sub>SLC</sub>および液晶素子LCを図示している。ソース線SLおよびゲート線GLは、図3等で図示するソース線SLLCおよびゲート線GLLCに相当する。

#### 【0088】

図9(B)は、通常駆動モードでのソース線SLおよびゲート線GLにそれぞれ与える信号の波形を示すタイミングチャートである。通常駆動モードでは通常のフレーム周波数(例えば60Hz)で動作する。1フレーム期間を期間T1乃至T3で表すと、各フレーム期間でゲート線に走査信号を与え、ソース線のビデオ電圧D1を画素に書き込む動作を行う。この動作は、期間T1乃至T3で同じビデオ電圧D1を書き込む場合であっても、異なるビデオ電圧を書き込む場合であっても同じである。

10

#### 【0089】

一方図9(C)は、IDS駆動でのソース線SLおよびゲート線GLにそれぞれ与える信号の波形を示すタイミングチャートである。IDS駆動では低速のフレーム周波数(例えば1Hz)で動作する。1フレーム期間を期間T1で表し、その中にビデオ電圧の書き込み期間を期間TW、ビデオ電圧の保持期間を期間TRETで表す。IDS駆動は、期間TWでゲート線に走査信号を与え、ソース線のビデオ電圧D1を画素に書き込み、期間TRETでゲート線をLレベルの電圧に固定し、トランジスタM1を非導通状態として一旦書き込んだビデオ電圧D1を画素に保持させる動作を行う。なお、低速のフレーム周波数としては、例えば、0.1Hz以上60Hz未満とすればよい。

20

#### 【0090】

図9(D)には、上述した通常駆動モードとIDS駆動とを切り替える場合の状態遷移図を示す。状態C1はIDS駆動モードを表し、状態C2は通常駆動モードを表している。

#### 【0091】

状態C1およびC2は、表示するコンテンツに応じて異ならせる。例えば図5で説明した時計表示を行う場合には、液晶素子LCおよび発光素子ELの双方の表示においてIDS駆動が有効である。また例えば画面全体に液晶素子LCおよび発光素子ELを駆動させて動画を表示において通常駆動モードが有効である。

30

#### 【0092】

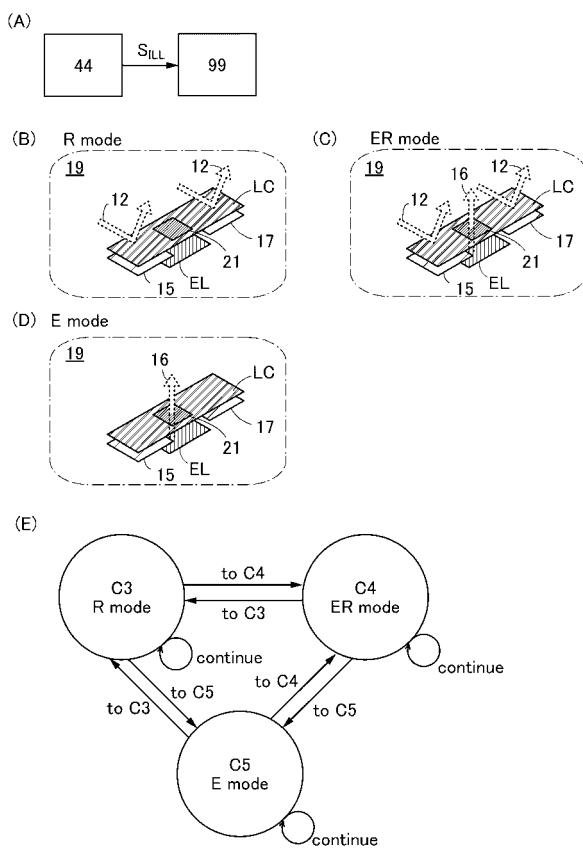

また図10を用いて、図4(B)で説明した光センサ44を利用した電子機器40での表示装置の表示モードの切り替えについて説明する。

#### 【0093】

電子機器40は、光センサ44で取得される照度の情報を含む信号によって、動作モードを切り替えることができる。図10(A)のブロック図では、光センサ44およびアプリケーションプロセッサ99を示している。

40

#### 【0094】

図10(A)において光センサ44は、例えば、照度に応じた信号SILLを生成する機能を有する。アプリケーションプロセッサ99は、信号SILLに応じて表示モードを切り替える機能を有する。

#### 【0095】

また図10(B)乃至(D)には、照度に応じて表示装置が取り得る表示モードを説明するための画素の模式図である。なお図10(B)乃至(D)においては、図3(B)と同様に、画素回路15、画素回路17、液晶素子LC、発光素子EL、開口21、液晶素子LCが有する反射電極が反射する反射光12、および開口21より射出される発光素子ELが発する光16を図示している。

50

## 【0096】

表示装置10が取り得る表示モードとしては、図10(B)乃至(D)に示す、反射表示モード(R mode)と、反射+発光表示モード(ER mode)と、発光表示モード(E mode)と、を挙げて説明する。

## 【0097】

反射表示モードは、画素が有する液晶素子を駆動して反射光の強度を調節して階調を制御する表示モードである。具体的には図10(B)に示す画素の模式図のように液晶素子LCが有する反射電極で反射光12の強度を調節して階調の制御を行う。

## 【0098】

反射+発光表示モード(ER mode)は、液晶素子の駆動と発光素子の駆動とによって反射光の強度と発光素子の光の強度の双方を調節して階調を制御する表示モードである。具体的には図10(C)に示す画素の模式図のように液晶素子LCが有する反射電極で反射光12の強度と、発光素子ELが開口21より射出する光16の強度と、を調節して階調の制御を行う。上記図7(A)、(B)で示した表示装置の動作は、図10(C)における反射+発光表示モード時において適用することで、表示品位の向上および消費電力の低減の双方を図ることができる。

10

## 【0099】

なお本明細書等において、上記した反射+発光表示モード(ER mode)のように、発光素子EL(第1の表示素子)と、液晶素子LC(第2の表示素子)とを組み合わせた表示をハイブリッド表示と呼称する。

20

## 【0100】

ハイブリッド表示とは、1つのパネルにおいて、反射光と、自発光とを併用して、色調または光強度を互いに補完して、文字または画像を表示する方法である。または、ハイブリッド表示とは、同一画素または同一副画素において複数の表示素子から、それぞれの光を用いて、文字及び/または画像を表示する方法である。ただし、ハイブリッド表示を行っているハイブリッドディスプレイを局所的にみると、複数の表示素子のいずれか一を用いて表示を行う画素または副画素と、複数の表示素子の二以上を用いて表示を行う画素または副画素と、を有する場合がある。

## 【0101】

なお、本明細書等において、上記構成のいずれか1つまたは複数の表現を満たすものを、ハイブリッド表示という。

30

## 【0102】

また、ハイブリッドディスプレイは、同一画素または同一副画素に複数の表示素子を有する。なお、複数の表示素子としては、例えば、光を反射する反射型素子と、光を射出する自発光素子とが挙げられる。なお、反射型素子と、自発光素子とは、それぞれ独立に制御することができる。ハイブリッドディスプレイは、表示部において、反射光、及び自発光のいずれか一方または双方を用いて、文字及び/または画像を表示する機能を有する。

## 【0103】

発光表示モード(E mode)は、発光素子を駆動して光の強度を調節して階調を制御する表示モードである。具体的には図10(D)に示す画素の模式図のように、発光素子ELが開口21より射出する光16の強度を調節して階調の制御を行う。上記図7(A)、(B)で示した表示装置の動作は、図10(D)における発光表示モード時において適用することで、消費電力の低減を図ることができる。

40

## 【0104】

図10(E)には、上述した3つのモード(反射表示モード、反射+発光表示モード、発光表示モード)の状態遷移図を示す。状態C3は反射表示モードを表し、状態C4は反射+発光表示モードを表し、状態C5は発光表示モードを表している。

## 【0105】

図10(E)に図示するように、状態C3乃至C5は照度に応じていずれかの状態の表示モードを取り得る。例えば屋外のように照度が大きい場合、状態C3を取り得る。また

50

屋外から屋内に移動するような照度が小さくなる場合、状態 C 3 から状態 C 5 に遷移する。また屋内であっても照度が大きく、反射光による階調表示が可能な場合、状態 C 5 から状態 C 4 に遷移する。

#### 【0106】

以上のように照度に応じて表示モードを切り替える構成とすることで、消費電力が比較的大きい発光素子の光の強度による階調表示の頻度を減らすことができる。そのため、表示装置の消費電力を低減することができる。

#### 【0107】

##### <ゲートドライバの構成例>

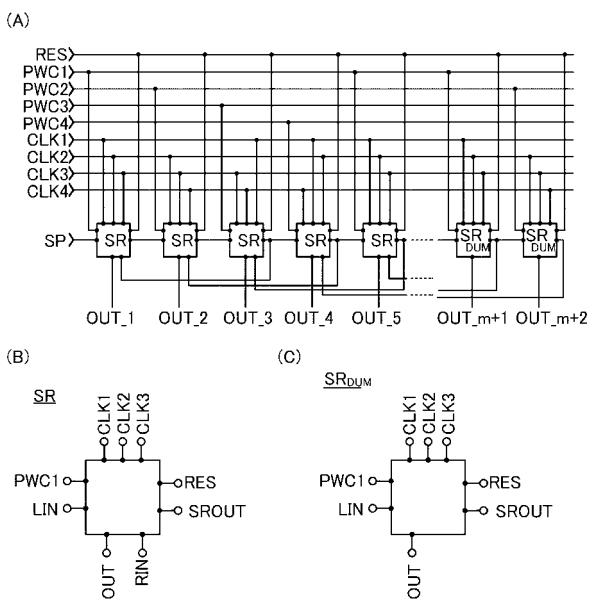

次いで上記図 1 等で説明したゲートドライバ 20、22 に適用可能なシフトレジスタの具体例について、説明する。 10

#### 【0108】

図 11 (A) には、 $m + 2$  段のパルスを出力できるシフトレジスタの回路構成の一例を示す。図 11 (A) のシフトレジスタは、外部よりスタートパルス SP、クロック信号 CLK1 乃至 CLK4、パルス幅制御信号 PWC1 乃至 PWC4、リセット信号 RES によって、出力端子 OUT\_1 乃至 OUT\_m+2 にパルスを出力することができる。なお図示では省略したが、リセット信号 RES、制御信号 A、B は、別々の配線に与えられる信号である。なお出力端子 OUT\_1 乃至 OUT\_m は、上記説明したゲート線 GLEL [1] 乃至 [m]、GLLC [1] 乃至 [m] に相当し、パルスは走査信号に相当する。 20

#### 【0109】

回路 SR には、図 11 (B) に示す各信号が与えられる。回路 SRDUM には、図 11 (C) に示す各信号が与えられる。回路 SR および回路 SRDUM において与えられる、クロック信号 CLK1 乃至 CLK4、パルス幅制御信号 PWC1 乃至 PWC4 は段ごとに異なる。なお LIN はシフトレジスタのシフト方向の上段側から与えられる信号である。また RIN は、シフトレジスタのシフト方向の下段側から与えられる信号である。また SROUT は、次段のシフトレジスタに与えられる信号である。 OUT は、負荷となるゲート線に与えられる信号である。 30

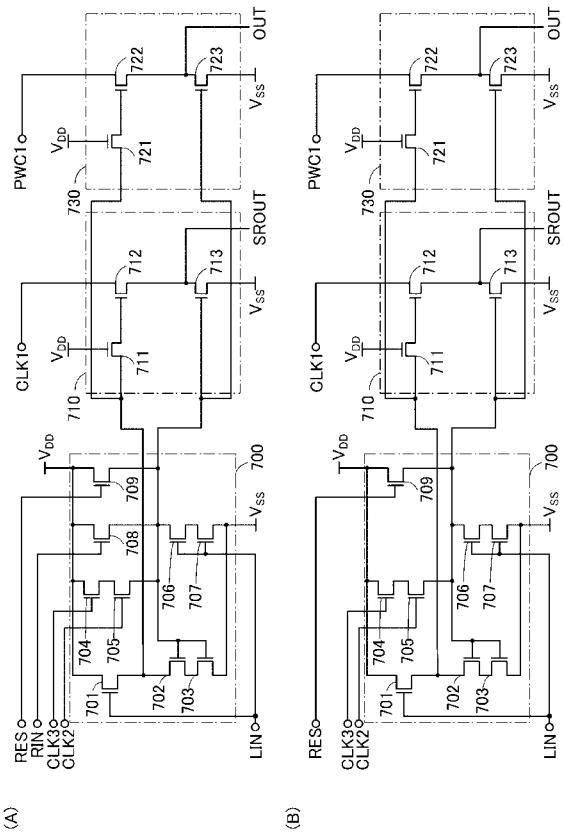

#### 【0110】

回路 SR の回路構成の一例を図 12 (A) に示す。図 12 (A) に示す回路 700 は、トランジスタ 701 乃至 709 を有する。図 12 (A) に示す回路 710 は、トランジスタ 711 乃至 713 を有する。図 12 (A) に示す回路 730 は、トランジスタ 721 乃至 723 を有する。トランジスタ 701 乃至 709、711 乃至 713、および 721 乃至 723 は、シングルゲートトランジスタとして図示したが、バックゲートを有するデュアルゲートトランジスタでもよい。同様に、回路 SRDUM の回路構成の一例を図 12 (B) に示す。 40

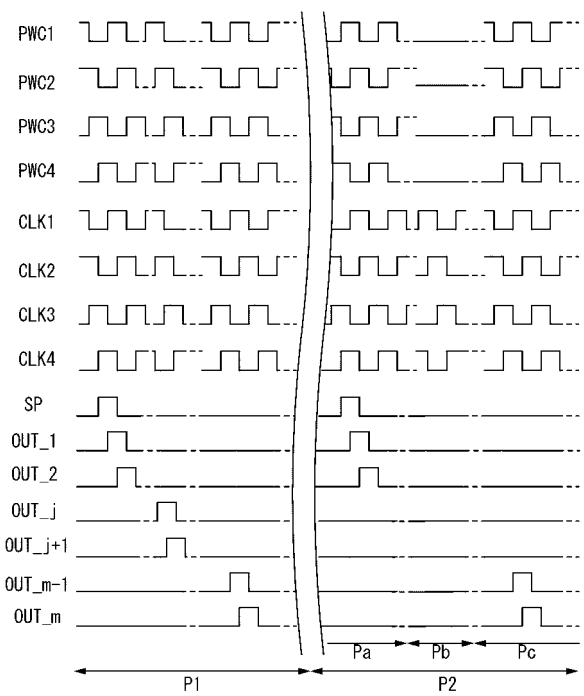

#### 【0111】

また図 13 には、パルス幅制御信号 PWC1 乃至 PWC4、クロック信号 CLK1 乃至 CLK4、スタートパルス SP、および出力端子 OUT\_1 乃至 OUT\_m の波形を表すタイミングチャートを示す。図 13 に示すタイミングチャートは、前半の期間が図 7 (A) で説明した破線矢印 23 で図示した各行に順に走査信号を出力する期間 P1 に相当する。また後半の期間が図 7 (A) で説明した破線矢印 25 で図示した所定の行にのみ走査信号を出力する期間 P2 に相当する。 50

#### 【0112】

期間 P1 では、スタートパルス SP、パルス幅制御信号 PWC1 乃至 PWC4、およびクロック信号 CLK1 乃至 CLK4 に応じて、順にパルスが出力される。

#### 【0113】

一方、第 2 の期間 P2 では、所定の行のみパルスが出力されるようにするため、パルス幅制御信号 PWC1 乃至 PWC4 を一定期間 L レベルに固定する。例えば図 13 では、出力端子 OUT\_1、OUT\_2、OUT\_m-1 および OUT\_m にパルスを出力し、出力端子 OUT\_j、OUT\_j+1 にパルスを出力されないようにする。この場合、期間

P a、期間 P c では、期間 P 1 と同様にパルス幅制御信号 P W C 1 乃至 P W C 4 によるトグル動作を行い、期間 P b では、パルス幅制御信号 P W C 1 乃至 P W C 4 を L レベルとする。パルス幅制御信号 P W C 1 乃至 P W C 4 を L レベルとすることで、出力端子 O U T \_ j 、O U T \_ j + 1 が L レベルとなるため、パルスが出力されない。

## 【0114】

このようにゲートドライバを領域ごとに分割することなく、所定の行に対応する走査信号の出力を停止させることができる。

## 【0115】

## (実施の形態 2 )

本実施の形態では、本発明の一態様である表示装置について、上記実施の形態 1 での説明を補完するための構成例、回路構成例について説明する。

10

## 【0116】

## [構成例]

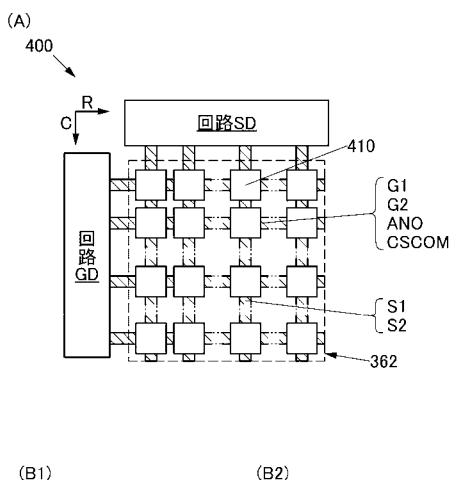

図 14 (A) は、表示装置 400 の構成の一例を示すブロック図である。表示装置 400 は、表示部 362 にマトリクス状に配列した複数の画素 410 を有する。また表示装置 400 は、回路 G D と、回路 S D を有する。また方向 R に配列した複数の画素 410 、及び回路 G D と電気的に接続する複数の配線 G 1 、複数の配線 G 2 、複数の配線 A N O 、及び複数の配線 C S C O M を有する。また方向 C に配列した複数の画素 410 、及び回路 S D と電気的に接続する複数の配線 S 1 及び複数の配線 S 2 を有する。

20

## 【0117】

なお、ここでは簡単のために回路 G D と回路 S D を 1 つずつ有する構成を示したが、液晶素子を駆動する回路 G D 及び回路 S D と、発光素子を駆動する回路 G D 及び回路 S D を、別々に設けてもよい。

## 【0118】

画素 410 は、反射型の液晶素子と、発光素子を有する。画素 410 において、液晶素子と発光素子とは、互いに重なる部分を有する。

## 【0119】

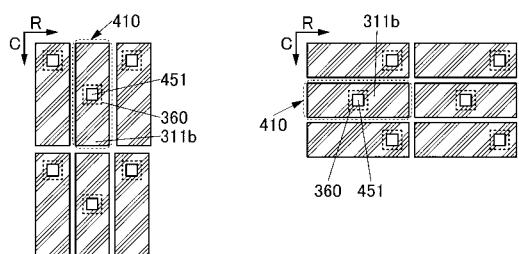

図 14 (B1) は、画素 410 が有する導電層 311b の構成例を示す。導電層 311b は、画素 410 における液晶素子の反射電極として機能する。また導電層 311b には、開口 451 が設けられている。

30

## 【0120】

図 14 (B1) には、導電層 311b と重なる領域に位置する発光素子 360 を破線で示している。発光素子 360 は、導電層 311b が有する開口 451 と重ねて配置されている。これにより、発光素子 360 が発する光は、開口 451 を介して表示面側に射出される。

## 【0121】

図 14 (B1) では、方向 R に隣接する画素 410 が異なる色に対応する画素である。このとき、図 14 (B1) に示すように、方向 R に配列する複数の画素において、開口 451 が一直線上に配列されないように、それぞれ導電層 311b の異なる位置に設けられていることが好ましい。これにより、隣接する 2 つの発光素子 360 を離すことが可能で、発光素子 360 が発する光が隣接する画素 410 が有する着色層に入射してしまう現象（クロストークともいう）を抑制することができる。また、隣接する 2 つの発光素子 360 を離して配置することができるため、発光素子 360 の E L 層をシャドウマスク等により作り分ける場合であっても、高い精細度の表示装置を実現できる。

40

## 【0122】

また、図 14 (B2) に示すような配列としてもよい。

## 【0123】

非開口部の総面積に対する開口 451 の総面積の比の値が大きすぎると、液晶素子を用いた表示が暗くなってしまう。また、非開口部の総面積に対する開口 451 の総面積の比の値が小さすぎると、発光素子 360 を用いた表示が暗くなってしまう。

50

## 【0124】

また、反射電極として機能する導電層311bに設ける開口451の面積が小さすぎると、発光素子360が射出する光から取り出せる光の効率が低下してしまう。

## 【0125】

開口451の形状は、例えば多角形、四角形、橢円形、円形または十字等の形状とすることができます。また、細長い筋状、スリット状、市松模様状の形状としてもよい。また、開口451を隣接する画素に寄せて配置してもよい。好ましくは、開口451を同じ色を表示する他の画素に寄せて配置する。これにより、クロストークを抑制できる。

## 【0126】

## [回路構成例]

10

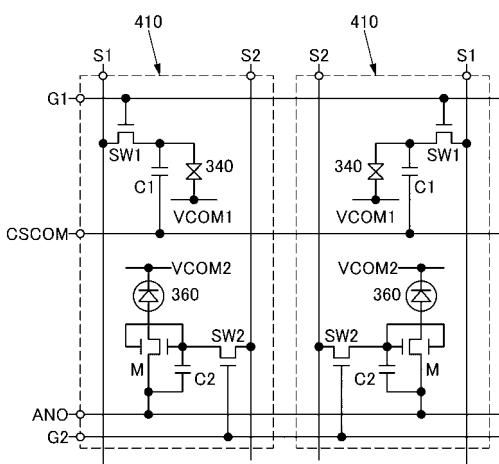

図15は、画素410の構成例を示す回路図である。図15では、隣接する2つの画素410を示している。

## 【0127】

画素410は、スイッチSW1、容量素子C1、液晶素子340、スイッチSW2、トランジスタM、容量素子C2、及び発光素子360等を有する。また、画素410には、配線G1、配線G2、配線ANO、配線CSCOM、配線S1、及び配線S2が電気的に接続されている。また、図15では、液晶素子340と電気的に接続する配線VCOM1、及び発光素子360と電気的に接続する配線VCOM2を示している。

## 【0128】

20

図15では、スイッチSW1及びスイッチSW2に、トランジスタを用いた場合の例を示している。

## 【0129】

スイッチSW1は、ゲートが配線G1と接続され、ソース又はドレインの一方が配線S1と接続され、ソース又はドレインの他方が容量素子C1の一方の電極、及び液晶素子340の一方の電極と接続されている。容量素子C1は、他方の電極が配線CSCOMと接続されている。液晶素子340は、他方の電極が配線VCOM1と接続されている。

## 【0130】

30

またスイッチSW2は、ゲートが配線G2と接続され、ソース又はドレインの一方が配線S2と接続され、ソース又はドレインの他方が、容量素子C2の一方の電極、トランジスタMのゲートと接続されている。容量素子C2は、他方の電極がトランジスタMのソース又はドレインの一方、及び配線ANOと接続されている。トランジスタMは、ソース又はドレインの他方が発光素子360の一方の電極と接続されている。発光素子360は、他方の電極が配線VCOM2と接続されている。

## 【0131】

図15では、トランジスタMが半導体を挟む2つのゲートを有し、これらが接続されている例を示している。これにより、トランジスタMが流すことのできる電流を増大させることができる。

## 【0132】

40

配線G1には、スイッチSW1を導通状態または非導通状態に制御する信号を与えることができる。配線VCOM1には、所定の電位を与えることができる。配線S1には、液晶素子340が有する液晶の配向状態を制御する信号を与えることができる。配線CSCOMには、所定の電位を与えることができる。

## 【0133】

配線G2には、スイッチSW2を導通状態または非導通状態に制御する信号を与えることができる。配線VCOM2及び配線ANOには、発光素子360が発光する電位差が生じる電位をそれぞれ与えることができる。配線S2には、トランジスタMの導通状態を制御する信号を与えることができる。

## 【0134】

50

図15に示す画素410は、例えば反射モードの表示を行う場合には、配線G1及び配線S1に与える信号により駆動し、液晶素子340による光学変調を利用して表示するこ

とができる。また、発光モードで表示を行う場合には、配線 G 2 及び配線 S 2 に与える信号により駆動し、発光素子 3 6 0 を発光させて表示することができる。また両方のモードで駆動する場合には、配線 G 1 、配線 G 2 、配線 S 1 及び配線 S 2 のそれぞれに与える信号により駆動することができる。

#### 【 0 1 3 5 】

##### ( 実施の形態 3 )

本実施の形態では、本発明の一態様の表示装置の断面構成の例について説明する。

#### 【 0 1 3 6 】

##### [ 断面構成例 1 ]

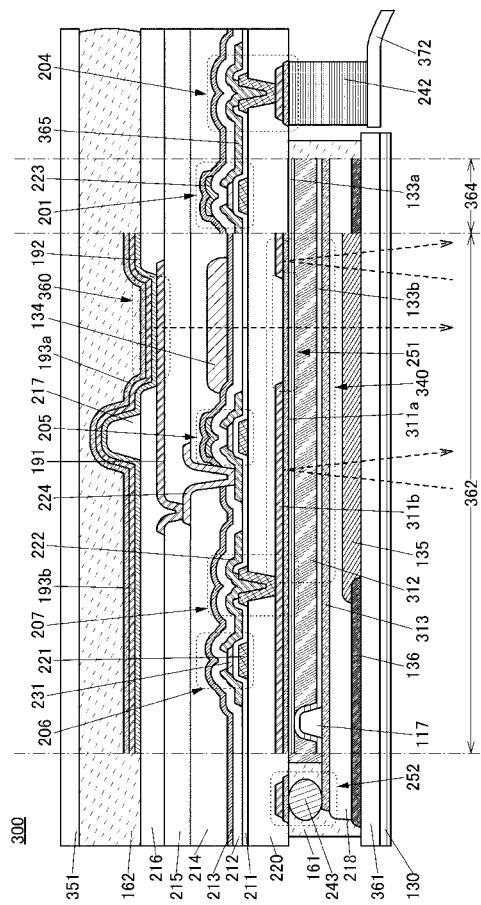

図 1 6 に、 F P C 3 7 2 を含む領域の一部、回路 3 6 4 を含む領域の一部、および表示部 3 6 2 を含む領域の一部をそれぞれ切断したときの断面の一例を示す。 10

#### 【 0 1 3 7 】

表示パネルは、基板 3 5 1 と基板 3 6 1 の間に、絶縁層 2 2 0 を有する。また基板 3 5 1 と絶縁層 2 2 0 の間に、発光素子 3 6 0 、トランジスタ 2 0 1 、トランジスタ 2 0 5 、トランジスタ 2 0 6 、着色層 1 3 4 等を有する。また絶縁層 2 2 0 と基板 3 6 1 の間に、液晶素子 3 4 0 、着色層 1 3 5 等を有する。また基板 3 6 1 と絶縁層 2 2 0 は接着層 1 6 1 を介して接着され、基板 3 5 1 と絶縁層 2 2 0 は接着層 1 6 2 を介して接着されている。

#### 【 0 1 3 8 】

着色層 1 3 4 には、赤色 ( R ) 、緑色 ( G ) 、または青色 ( B ) 等を透過する、原色系のカラーフィルタを用いることができる。一方、着色層 1 3 5 には、シアン ( C ) 、マゼンタ ( M ) 、イエロー ( Y ) 等を透過する、補色系のカラーフィルタを用いることができる。 20

#### 【 0 1 3 9 】

トランジスタ 2 0 6 は、液晶素子 3 4 0 と電気的に接続し、トランジスタ 2 0 5 は、発光素子 3 6 0 と電気的に接続する。トランジスタ 2 0 5 とトランジスタ 2 0 6 は、いずれも絶縁層 2 2 0 の基板 3 5 1 側の面上に形成されているため、これらを同一の工程を用いて作製することができる。

#### 【 0 1 4 0 】

基板 3 6 1 には、着色層 1 3 5 、遮光層 1 3 6 、絶縁層 2 1 8 、および液晶素子 3 4 0 の共通電極として機能する導電層 3 1 3 、配向膜 1 3 3 b 、絶縁層 1 1 7 等が設けられている。絶縁層 1 1 7 は、液晶素子 3 4 0 のセルギャップを保持するためのスペーサとして機能する。 30

#### 【 0 1 4 1 】

絶縁層 2 2 0 の基板 3 5 1 側には、絶縁層 2 1 1 、絶縁層 2 1 2 、絶縁層 2 1 3 、絶縁層 2 1 4 、絶縁層 2 1 5 等の絶縁層が設けられている。絶縁層 2 1 1 は、その一部が各トランジスタのゲート絶縁層として機能する。絶縁層 2 1 2 、絶縁層 2 1 3 、および絶縁層 2 1 4 は、各トランジスタを覆って設けられている。また絶縁層 2 1 4 を覆って絶縁層 2 1 5 が設けられている。絶縁層 2 1 4 および絶縁層 2 1 5 は、平坦化層としての機能を有する。なお、ここではトランジスタ等を覆う絶縁層として、絶縁層 2 1 2 、絶縁層 2 1 3 、絶縁層 2 1 4 の 3 層を有する場合について示しているが、これに限られず 4 層以上であってもよいし、单層、または 2 層であってもよい。また平坦化層として機能する絶縁層 2 1 4 は、不要であれば設けなくてもよい。 40

#### 【 0 1 4 2 】

また、トランジスタ 2 0 1 、トランジスタ 2 0 5 、およびトランジスタ 2 0 6 は、一部がゲートとして機能する導電層 2 2 1 、一部がソースまたはドレインとして機能する導電層 2 2 2 、半導体層 2 3 1 を有する。ここでは、同一の導電膜を加工して得られる複数の層に、同じハッチングパターンを付している。

#### 【 0 1 4 3 】

液晶素子 3 4 0 は反射型の液晶素子である。液晶素子 3 4 0 は、導電層 3 1 1 a 、液晶

312、導電層313が積層された積層構造を有する。また、導電層311aの基板351側に接して、可視光を反射する導電層311bが設けられている。導電層311bは開口251を有する。また、導電層311aおよび導電層313は可視光を透過する材料を含む。また、液晶312と導電層311aの間に配向膜133aが設けられ、液晶312と導電層313の間に配向膜133bが設けられている。また、基板361の外側の面には、偏光板130を有する。

#### 【0144】

液晶素子340において、導電層311bは可視光を反射する機能を有し、導電層313は可視光を透過する機能を有する。基板361側から入射した光は、偏光板130により偏光され、導電層313、液晶312を透過し、導電層311bで反射する。そして、液晶312および導電層313を再度透過して、偏光板130に達する。このとき、導電層311bと導電層313の間に与える電圧によって液晶の配向を制御し、光の光学変調を制御することができる。すなわち、偏光板130を介して射出される光の強度を制御することができる。また光は着色層135によって特定の波長領域以外の光が吸収されることにより、取り出される光は、例えば赤色を呈する光となる。

#### 【0145】

発光素子360は、ボトムエミッション型の発光素子である。発光素子360は、絶縁層220側から導電層191、EL層192、および導電層193bの順に積層された積層構造を有する。また導電層193bを覆って導電層193aが設けられている。導電層193bは可視光を反射する材料を含み、導電層191および導電層193aは可視光を透過する材料を含む。発光素子360が発する光は、着色層134、絶縁層220、開口251、導電層313等を介して、基板361側に射出される。

#### 【0146】

ここで、図16に示すように、開口251には可視光を透過する導電層311aが設けられていることが好ましい。これにより、開口251と重なる領域においてもそれ以外の領域と同様に液晶312が配向するため、これらの領域の境界部で液晶の配向不良が生じ、意図しない光が漏れてしまうことを抑制できる。

#### 【0147】

ここで、基板361の外側の面に配置する偏光板130として直線偏光板を用いてもよいが、円偏光板を用いることもできる。円偏光板としては、例えば直線偏光板と1/4波長位相差板を積層したものを用いることができる。これにより、外光反射を抑制することができる。また、外光反射を抑制するために光拡散板を設けてもよい。また、偏光板の種類に応じて、液晶素子340に用いる液晶素子のセルギャップ、配向、駆動電圧等を調整することで、所望のコントラストが実現されるようにすればよい。

#### 【0148】

導電層191の端部を覆う絶縁層216上には、絶縁層217が設けられている。絶縁層217は、絶縁層220と基板351が必要以上に接近することを抑制するスペーサとしての機能を有する。またEL層192や導電層193aを遮蔽マスク(メタルマスク)を用いて形成する場合には、当該遮蔽マスクが被形成面に接触することを抑制するための機能を有していてもよい。なお、絶縁層217は不要であれば設けなくてもよい。

#### 【0149】

トランジスタ205のソースまたはドレインの一方は、導電層224を介して発光素子360の導電層191と電気的に接続されている。

#### 【0150】

トランジスタ206のソースまたはドレインの一方は、接続部207を介して導電層311bと電気的に接続されている。導電層311bと導電層311aは接して設けられ、これらは電気的に接続されている。ここで、接続部207は、絶縁層220に設けられた開口を介して、絶縁層220の両面に設けられる導電層同士を接続する部分である。

#### 【0151】

基板351の基板361と重ならない領域には、接続部204が設けられている。接続

10

20

30

40

50

部204は、接続層242を介してFPC372と電気的に接続されている。接続部204は接続部207と同様の構成を有している。接続部204の上面は、導電層311aと同一の導電膜を加工して得られた導電層が露出している。これにより、接続部204とFPC372とを接続層242を介して電気的に接続することができる。

#### 【0152】

接着層161が設けられる一部の領域には、接続部252が設けられている。接続部252において、導電層311aと同一の導電膜を加工して得られた導電層と、導電層313の一部が、接続体243により電気的に接続されている。したがって、基板361側に形成された導電層313に、基板351側に接続されたFPC372から入力される信号または電位を、接続部252を介して供給することができる。

10

#### 【0153】

接続体243としては、例えば導電性の粒子を用いることができる。導電性の粒子としては、有機樹脂またはシリカなどの粒子の表面を金属材料で被覆したものを用いることができる。金属材料としてニッケルや金を用いると接触抵抗を低減できるため好ましい。またニッケルをさらに金で被覆するなど、2種類以上の金属材料を層状に被覆させた粒子を用いることが好ましい。また接続体243として、弾性変形、または塑性変形する材料を用いることが好ましい。このとき導電性の粒子である接続体243は、図16に示すように上下方向に潰れた形状となる場合がある。こうすることで、接続体243と、これと電気的に接続する導電層との接触面積が増大し、接触抵抗を低減できるほか、接続不良などの不具合の発生を抑制することができる。

20

#### 【0154】

接続体243は、接着層161に覆われるよう配置することが好ましい。例えば、硬化前の接着層161に接続体243を分散させておけばよい。

#### 【0155】

図16では、回路364の例としてトランジスタ201が設けられている例を示している。

#### 【0156】

図16では、トランジスタ201およびトランジスタ205の例として、チャネルが形成される半導体層231を2つのゲートで挟持する構成が適用されている。一方のゲートは導電層221により、他方のゲートは絶縁層212を介して半導体層231と重なる導電層223により構成されている。このような構成とすることで、トランジスタのしきい値電圧を制御することができる。このとき、2つのゲートを接続し、これらに同一の信号を供給することによりトランジスタを駆動してもよい。このようなトランジスタは他のトランジスタと比較して電界効果移動度を高めることができ、オン電流を増大させることができる。その結果、高速駆動が可能な回路を作製することができる。さらには、回路部の占有面積を縮小することが可能となる。オン電流の大きなトランジスタを適用することで、表示パネルを大型化、または高精細化したときに配線数が増大したとしても、各配線における信号遅延を低減することができる、表示ムラを抑制することができる。

30

#### 【0157】

なお、回路364が有するトランジスタと、表示部362が有するトランジスタは、同じ構造であってもよい。また回路364が有する複数のトランジスタは、全て同じ構造であってもよいし、異なる構造のトランジスタを組み合わせて用いてもよい。また、表示部362が有する複数のトランジスタは、全て同じ構造であってもよいし、異なる構造のトランジスタを組み合わせて用いてもよい。

40

#### 【0158】

各トランジスタを覆う絶縁層212、絶縁層213のうち少なくとも一方は、水や水素などの不純物が拡散しにくい材料を用いることが好ましい。すなわち、絶縁層212または絶縁層213はバリア膜として機能させることができる。このような構成とすることで、トランジスタに対して外部から不純物が拡散することを効果的に抑制することができなり、信頼性の高い表示パネルを実現できる。

50

## 【0159】

基板361側において、着色層135、遮光層136を覆って絶縁層218が設けられている。絶縁層218は、平坦化層としての機能を有していてもよい。絶縁層218により、導電層313の表面を概略平坦にできるため、液晶312の配向状態を均一にできる。

## 【0160】

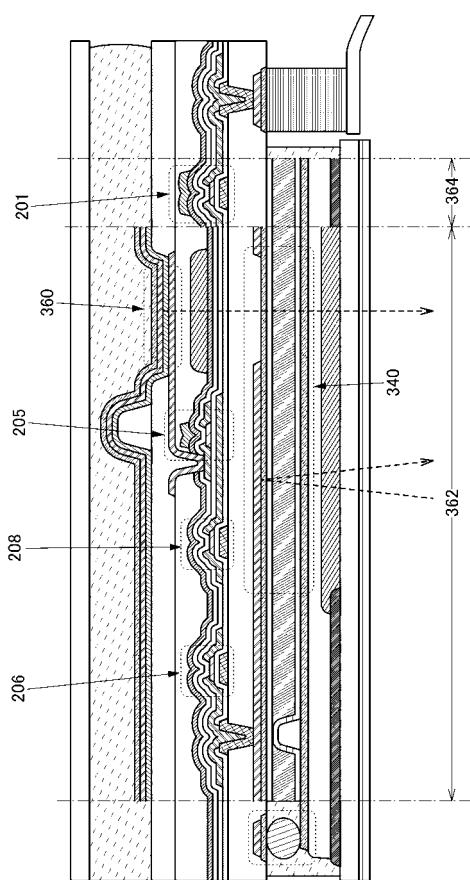

## [断面構成例2]

また、本発明の一態様の表示パネルは、図17に示すように、画素に設けられる第1のトランジスタと、第2のトランジスタが重なる領域を有する構成であってもよい。このような構成とすることで、一画素あたりの面積を小さくすることができ、高精細な画像が表示できる画素密度の高い表示パネルを形成することができる。10

## 【0161】

例えば、発光素子360を駆動するためのトランジスタであるトランジスタ205と、トランジスタ208が重なる領域を有するように構成とすることができます。または、液晶素子340を駆動するためのトランジスタ206と、トランジスタ205およびトランジスタ208の一方が重なる領域を有するように構成であってもよい。

## 【0162】

## [断面構成例3]

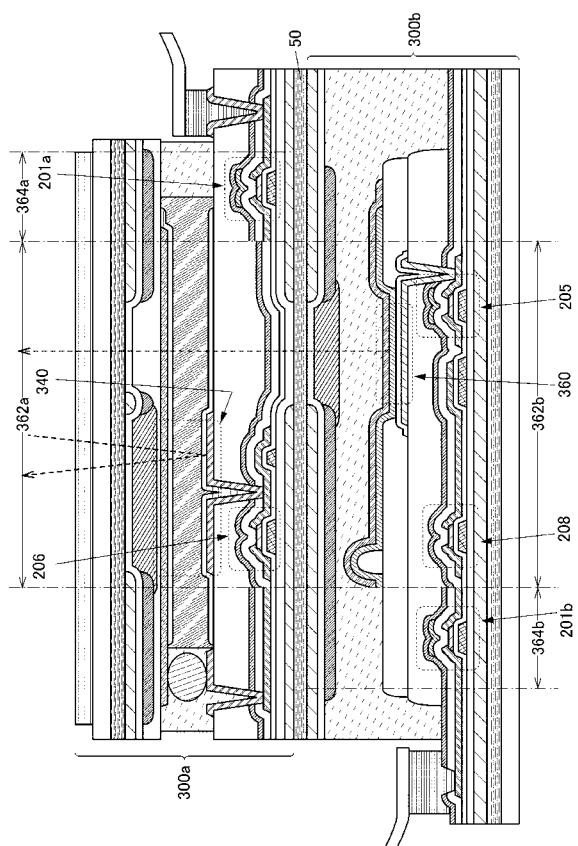

また、本発明の一態様の表示パネルは、図18に示すように、表示パネル300aと表示パネル300bが接着層50を介して貼り合わされた構成であってもよい。表示パネル300aは、表示部362aに液晶素子340およびトランジスタ206を有し、表示部362aを駆動する回路364aにトランジスタ201aを有する。表示パネル300bは、表示部362bに発光素子360およびトランジスタ205、208を有し、表示部362bを駆動する回路364bにトランジスタ201bを有する。20

## 【0163】

このような構成とすることで、表示パネル300aおよび表示パネル300bのそれぞれに適した作製工程を用いることができ、製品歩留りを向上させることができる。

## 【0164】

## [各構成要素について]

以下では、上記に示す各構成要素について説明する。

## 【0165】

## [基板]

表示パネルが有する基板には、平坦面を有する材料を用いることができる。表示素子からの光を取り出す側の基板には、該光を透過する材料を用いる。例えば、ガラス、石英、セラミック、サファイア、有機樹脂などの材料を用いることができる。

## 【0166】

厚さの薄い基板を用いることで、表示パネルの軽量化、薄型化を図ることができる。さらに、可撓性を有する程度の厚さの基板を用いることで、可撓性を有する表示パネルを実現できる。

## 【0167】

また、発光を取り出さない側の基板は、透光性を有していないために、上記に挙げた基板の他に、金属基板等を用いることもできる。金属基板は熱伝導性が高く、基板全体に熱を容易に伝導できるため、表示パネルの局所的な温度上昇を抑制することができ、好ましい。可撓性や曲げ性を得るためにには、金属基板の厚さは、 $10\text{ }\mu\text{m}$ 以上 $200\text{ }\mu\text{m}$ 以下が好ましく、 $20\text{ }\mu\text{m}$ 以上 $50\text{ }\mu\text{m}$ 以下であることがより好ましい。40

## 【0168】

金属基板を構成する材料としては、特に限定はないが、例えば、アルミニウム、銅、ニッケル等の金属、もしくはアルミニウム合金またはステンレス等の合金などを好適に用いることができる。

## 【0169】

10

20

30

40

50

また、金属基板の表面を酸化する、または表面に絶縁膜を形成するなどにより、絶縁処理が施された基板を用いてもよい。例えば、スピンドルコート法やディップ法などの塗布法、電着法、蒸着法、またはスパッタリング法などを用いて絶縁膜を形成してもよいし、酸素雰囲気で放置するまたは加熱するほか、陽極酸化法などによって、基板の表面に酸化膜を形成してもよい。

#### 【0170】

可撓性を有し、可視光に対する透過性を有する材料としては、例えば、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)等のポリエステル樹脂、ポリアクリロニトリル樹脂、ポリイミド樹脂、ポリメチルメタクリレート樹脂、ポリカーボネート(PC)樹脂、ポリエーテルスルホン(PES)樹脂、ポリアミド樹脂、シクロオレフィン樹脂、ポリスチレン樹脂、ポリアミドイミド樹脂、ポリ塩化ビニル樹脂、ポリテトラフルオロエチレン(PTFE)樹脂等が挙げられる。特に、熱膨張係数の低い材料を用いることが好ましく、例えば、熱膨張係数が $30 \times 10 - 6 / K$ 以下のポリアミドイミド樹脂、ポリイミド樹脂、PET等を好適に用いることができる。また、ガラス繊維に有機樹脂を含浸した基板や、無機フィラーを有機樹脂に混ぜて熱膨張係数を下げた基板を使用することもできる。このような材料を用いた基板は、重量が軽いため、該基板を用いた表示パネルも軽量にすることができる。

10

#### 【0171】

上記材料中に纖維体が含まれている場合、纖維体は有機化合物または無機化合物の高強度纖維を用いる。高強度纖維とは、具体的には引張弾性率またはヤング率の高い纖維のことを行い、代表例としては、ポリビニルアルコール系纖維、ポリエステル系纖維、ポリアミド系纖維、ポリエチレン系纖維、アラミド系纖維、ポリパラフェニレンベンゾピスオキサゾール纖維、ガラス纖維、または炭素纖維が挙げられる。ガラス纖維としては、Eガラス、Sガラス、Dガラス、Qガラス等を用いたガラス纖維が挙げられる。これらは、織布または不織布の状態で用い、この纖維体に樹脂を含浸させ樹脂を硬化させた構造物を、可撓性を有する基板として用いてもよい。可撓性を有する基板として、纖維体と樹脂からなる構造物を用いると、曲げや局所的押圧による破損に対する信頼性が向上するため、好ましい。

20

#### 【0172】

または、可撓性を有する程度に薄いガラス、金属などを基板に用いることもできる。または、ガラスと樹脂材料とが接着層により貼り合わされた複合材料を用いてもよい。

30

#### 【0173】

可撓性を有する基板に、表示パネルの表面を傷などから保護するハードコート層(例えば、窒化シリコン、酸化アルミニウムなど)や、押圧を分散可能な材質の層(例えば、アラミド樹脂など)等が積層されていてもよい。また、水分等による表示素子の寿命の低下等を抑制するために、可撓性を有する基板に透水性の低い絶縁膜が積層されていてもよい。例えば、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム等の無機絶縁材料を用いることができる。

#### 【0174】

基板は、複数の層を積層して用いることもできる。特に、ガラス層を有する構成とすると、水や酸素に対するバリア性を向上させ、信頼性の高い表示パネルとすることができる。

40

#### 【0175】

##### [トランジスタ]

トランジスタは、ゲート電極として機能する導電層と、半導体層と、ソース電極として機能する導電層と、ドレイン電極として機能する導電層と、ゲート絶縁層として機能する絶縁層と、を有する。上記では、ボトムゲート構造のトランジスタを適用した場合を示している。

#### 【0176】

なお、本発明の一態様の表示装置が有するトランジスタの構造は特に限定されない。例

50

えば、プレーナ型のトランジスタとしてもよいし、スタガ型のトランジスタとしてもよいし、逆スタガ型のトランジスタとしてもよい。また、トップゲート型またはボトムゲート型のいずれのトランジスタ構造としてもよい。または、チャネルの上下にゲート電極が設けられていてもよい。

#### 【0177】

トランジスタに用いる半導体材料の結晶性についても特に限定されず、非晶質半導体、結晶性を有する半導体（微結晶半導体、多結晶半導体、単結晶半導体、または一部に結晶領域を有する半導体）のいずれを用いてもよい。結晶性を有する半導体を用いると、トランジスタ特性の劣化を抑制できるため好ましい。

#### 【0178】

また、トランジスタに用いる半導体材料としては、エネルギーギャップが2 eV以上、好ましくは2.5 eV以上、より好ましくは3 eV以上である金属酸化物を用いることができる。代表的には、インジウムを含む金属酸化物などであり、例えば、後述するCAC-OSなどを用いることができる。

#### 【0179】

シリコンよりもバンドギャップが広く、且つキャリア密度の小さい金属酸化物を用いたトランジスタは、その低いオフ電流により、トランジスタと直列に接続された容量素子に蓄積した電荷を長期間に亘って保持することが可能である。

#### 【0180】

半導体層は、例えばインジウム、亜鉛およびM（アルミニウム、チタン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、セリウム、スズ、ネオジムまたはハフニウム等の金属）を含むIn-M-Zn系酸化物で表記される膜とすることができる。

#### 【0181】

半導体層を構成する金属酸化物がIn-M-Zn系酸化物の場合、In-M-Zn酸化物を成膜するために用いるスパッタリングターゲットの金属元素の原子数比は、In-M-Znを満たすことが好ましい。このようなスパッタリングターゲットの金属元素の原子数比として、In:M:Zn = 1:1:1、In:M:Zn = 1:1:1.2、In:M:Zn = 3:1:2、In:M:Zn = 4:2:3、In:M:Zn = 4:2:4.1、In:M:Zn = 5:1:6、In:M:Zn = 5:1:7、In:M:Zn = 5:1:8等が好ましい。なお、成膜される半導体層の原子数比はそれぞれ、上記のスパッタリングターゲットに含まれる金属元素の原子数比のプラスマイナス40%の変動を含む。

#### 【0182】

本実施の形態で例示したボトムゲート構造のトランジスタは、作製工程を削減できるため好ましい。またこのとき金属酸化物を用いることで、多結晶シリコンよりも低温で形成できる、半導体層よりも下層の配線や電極の材料、基板の材料として、耐熱性の低い材料を用いることが可能なため、材料の選択の幅を広げることができる。例えば、極めて大面積のガラス基板などを好適に用いることができる。

#### 【0183】

半導体層としては、キャリア密度の低い金属酸化物膜を用いる。例えば、半導体層は、キャリア密度が $1 \times 10^{17} / \text{cm}^3$ 以下、好ましくは $1 \times 10^{15} / \text{cm}^3$ 以下、さらに好ましくは $1 \times 10^{13} / \text{cm}^3$ 以下、より好ましくは $1 \times 10^{11} / \text{cm}^3$ 以下、さらに好ましくは $1 \times 10^{10} / \text{cm}^3$ 未満であり、 $1 \times 10^{-9} / \text{cm}^3$ 以上のキャリア密度の金属酸化物を用いることができる。そのような金属酸化物を、高純度真性または実質的に高純度真性な金属酸化物と呼ぶ。これにより不純物濃度が低く、欠陥準位密度が低いため、安定な特性を有する金属酸化物であるといえる。

#### 【0184】

なお、これらに限られず、必要とするトランジスタの半導体特性および電気特性（電界効果移動度、しきい値電圧等）に応じて適切な組成のものを用いればよい。また、必要とするトランジスタの半導体特性を得るために、半導体層のキャリア密度や不純物濃度、欠

10

20

30

40

50

陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

#### 【0185】

半導体層を構成する金属酸化物において、第14族元素の一つであるシリコンや炭素が含まれると、半導体層において酸素欠損が増加し、n型化してしまう。このため、半導体層におけるシリコンや炭素の濃度（二次イオン質量分析法により得られる濃度）を、 $2 \times 10^{18}$  atoms/cm<sup>3</sup>以下、好ましくは $2 \times 10^{17}$  atoms/cm<sup>3</sup>以下とする。

#### 【0186】

また、アルカリ金属およびアルカリ土類金属は、金属酸化物と結合するとキャリアを生成する場合があり、トランジスタのオフ電流が増大してしまうことがある。このため半導体層における二次イオン質量分析法により得られるアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、好ましくは $2 \times 10^{16}$  atoms/cm<sup>3</sup>以下にする。

#### 【0187】

また、半導体層を構成する金属酸化物に窒素が含まれていると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている金属酸化物を用いたトランジスタはノーマリーオン特性となりやすい。このため半導体層における二次イオン質量分析法により得られる窒素濃度は、 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下にすることが好ましい。

#### 【0188】

また、半導体層は、例えば非単結晶構造でもよい。非単結晶構造は、例えば、c軸に配向した結晶を有するCAAC-OS(C-Axis Aligned Crystalline Oxide Semiconductor、または、C-Axis Aligned and A-B-plane Anchored Crystalline Oxide Semiconductor)、多結晶構造、微結晶構造、または非晶質構造を含む。非単結晶構造において、非晶質構造は最も欠陥準位密度が高く、CAAC-OSは最も欠陥準位密度が低い。

#### 【0189】

非晶質構造の金属酸化物膜は、例えば、原子配列が無秩序であり、結晶成分を有さない。または、非晶質構造の酸化物膜は、例えば、完全な非晶質構造であり、結晶部を有さない。

#### 【0190】

なお、半導体層が、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、CAAC-OSの領域、単結晶構造の領域のうち、二種以上を有する混合膜であってもよい。混合膜は、例えば上述した領域のうち、いずれか二種以上の領域を含む単層構造、または積層構造を有する場合がある。

#### 【0191】

<CAAC-OSの構成>

以下では、本発明の一態様で開示されるトランジスタに用いることができるCAAC(Cloud-Aligned Composite)-OSの構成について説明する。

#### 【0192】

本明細書等において、金属酸化物(metal oxide)とは、広い表現での金属の酸化物である。金属酸化物は、酸化物絶縁体、酸化物導電体(透明酸化物導電体を含む)、酸化物半導体(Oxide Semiconductorまたは単にOSともいう)などに分類される。例えば、トランジスタの活性層に金属酸化物を用いた場合、当該金属酸化物を酸化物半導体と呼称する場合がある。つまり、OS FETと記載する場合においては、金属酸化物または酸化物半導体を有するトランジスタと換言することができる。

#### 【0193】

本明細書において、金属酸化物が、導電体の機能を有する領域と、誘電体の機能を有す

10

20

30

40

50

る領域とが混合し、金属酸化物全体では半導体として機能する場合、CAC(Cloud-Aligned Composite)-OS(Oxide Semiconductor)、またはCAC-metal oxideと定義する。

#### 【0194】

つまり、CAC-OSとは、例えば、酸化物半導体を構成する元素が、0.5nm以上10nm以下、好ましくは、0.5nm以上3nm以下、またはその近傍のサイズで偏在した材料の一構成である。なお、以下では、酸化物半導体において、一つあるいはそれ以上の元素が偏在し、該元素を有する領域が、0.5nm以上10nm以下、好ましくは、0.5nm以上3nm以下、またはその近傍のサイズで混合した状態をモザイク状、またはパッチ状ともいう。

10

#### 【0195】

特定の元素が偏在した領域は、該元素が有する性質により、物理特性が決定する。例えば、金属酸化物を構成する元素の中でも比較的、絶縁体となる傾向がある元素が偏在した領域は、誘電体領域となる。一方、金属酸化物を構成する元素の中でも比較的、導体となる傾向がある元素が偏在した領域は、導電体領域となる。また、導電体領域、および誘電体領域がモザイク状に混合することで、材料としては、半導体として機能する。

#### 【0196】

つまり、本発明の一態様における金属酸化物は、物理特性が異なる材料が混合した、マトリックス複合材(matrix composite)、または金属マトリックス複合材(metal matrix composite)の一種である。

20

#### 【0197】

なお、酸化物半導体は、少なくともインジウムを含むことが好ましい。特にインジウムおよび亜鉛を含むことが好ましい。また、それらに加えて、元素M(Mは、ガリウム、アルミニウム、シリコン、ホウ素、イットリウム、銅、バナジウム、ベリリウム、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種)が含まれていてもよい。

#### 【0198】

例えば、In-Ga-Zn酸化物におけるCAC-OS(CAC-OSの中でもIn-Ga-Zn酸化物を、特にCAC-IGZOと呼称してもよい。)とは、インジウム酸化物(以下、InOX1(X1は0よりも大きい実数)とする。)、またはインジウム亜鉛酸化物(以下、InX2ZnY2OZ2(X2、Y2、およびZ2は0よりも大きい実数)とする。)と、ガリウム酸化物(以下、GaOX3(X3は0よりも大きい実数)とする。)、またはガリウム亜鉛酸化物(以下、GaX4ZnY4OZ4(X4、Y4、およびZ4は0よりも大きい実数)とする。)などと、に材料が分離することでモザイク状となり、モザイク状のInOX1、またはInX2ZnY2OZ2が、膜中に均一に分布した構成(以下、クラウド状ともいう。)である。

30

#### 【0199】

つまり、CAC-OSは、GaOX3が主成分である領域と、InX2ZnY2OZ2、またはInOX1が主成分である領域とが、混合している構成を有する複合酸化物半導体である。なお、本明細書において、例えば、第1の領域の元素Mに対するInの原子数比が、第2の領域の元素Mに対するInの原子数比よりも大きいことを、第1の領域は、第2の領域と比較して、Inの濃度が高いとする。

40

#### 【0200】

なお、IGZOは通称であり、In、Ga、Zn、およびOによる1つの化合物をいう場合がある。代表例として、InGaO3(ZnO)m1(m1は自然数)、またはIn(1+x0)Ga(1-x0)O3(ZnO)m0(-1 x0 1、m0は任意数)で表される結晶性の化合物が挙げられる。

#### 【0201】

上記結晶性の化合物は、単結晶構造、多結晶構造、またはCAC構造を有する。なお

50

、 C A A C 構造とは、複数の I G Z O のナノ結晶が c 軸配向を有し、かつ a - b 面においては配向せずに連結した結晶構造である。

#### 【 0 2 0 2 】

一方、 C A C - O S は、酸化物半導体の材料構成に関する。 C A C - O S とは、 I n 、 G a 、 Z n 、および O を含む材料構成において、一部に G a を主成分とするナノ粒子状領域が観察され、一部に I n を主成分とするナノ粒子状領域が観察され、それぞれモザイク状にランダムに分散している構成をいう。従って、 C A C - O S において、結晶構造は副次的な要素である。

#### 【 0 2 0 3 】

なお、 C A C - O S は、組成の異なる二種類以上の膜の積層構造は含まないものとする。例えば、 I n を主成分とする膜と、 G a を主成分とする膜との 2 層からなる構造は、含まない。

#### 【 0 2 0 4 】

なお、 G a O X 3 が主成分である領域と、 I n X 2 Z n Y 2 O Z 2 、または I n O X 1 が主成分である領域とは、明確な境界が観察できない場合がある。

#### 【 0 2 0 5 】

なお、ガリウムの代わりに、アルミニウム、シリコン、ホウ素、イットリウム、銅、バナジウム、ベリリウム、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種が含まれている場合、 C A C - O S は、一部に該元素を主成分とするナノ粒子状領域が観察され、一部に I n を主成分とするナノ粒子状領域が観察され、それぞれモザイク状にランダムに分散している構成をいう。

#### 【 0 2 0 6 】

##### < C A C - O S の解析 >

続いて、各種測定方法を用い、基板上に成膜した酸化物半導体について測定を行った結果について説明する。

#### 【 0 2 0 7 】

##### 試料の構成と作製方法

以下では、本発明の一態様に係る 9 個の試料について説明する。各試料は、それぞれ、酸化物半導体を成膜する際の基板温度、および酸素ガス流量比を異なる条件で作製する。なお、試料は、基板と、基板上の酸化物半導体と、を有する構造である。

#### 【 0 2 0 8 】

各試料の作製方法について、説明する。

#### 【 0 2 0 9 】

まず、基板として、ガラス基板を用いる。続いて、スパッタリング装置を用いて、ガラス基板上に酸化物半導体として、厚さ 1 0 0 nm の I n - G a - Z n 酸化物を形成する。成膜条件は、チャンバー内の圧力を 0 . 6 P a とし、ターゲットには、酸化物ターゲット ( I n : G a : Z n = 4 : 2 : 4 . 1 [ 原子数比 ] ) を用いる。また、スパッタリング装置内に設置された酸化物ターゲットに 2 5 0 0 W の A C 電力を供給する。

#### 【 0 2 1 0 】

なお、酸化物を成膜する際の条件として、基板温度を、意図的に加熱しない温度（以下、室温または R . T . ともいう。）、 1 3 0 、または 1 7 0 とした。また、 A r と酸素の混合ガスに対する酸素ガスの流量比（以下、酸素ガス流量比ともいう。）を、 1 0 % 、 3 0 % 、または 1 0 0 % とすることで、 9 個の試料を作製する。

#### 【 0 2 1 1 】

##### X 線回折による解析

本項目では、 9 個の試料に対し、 X 線回折 ( X R D : X - r a y d i f f r a c t i o n ) 測定を行った結果について説明する。なお、 X R D 装置として、 Br u k e r 社製 D 8 A D V A N C E を用いた。また、条件は、 O u t - o f - p l a n e 法による / 2 スキャンにて、走査範囲を 1 5 d e g . 乃至 5 0 d e g . 、ステップ幅を 0 . 0 2 d

10

20

30

40

50

e g . 、走査速度を 3 . 0 deg . / 分とした。

#### 【 0 2 1 2 】

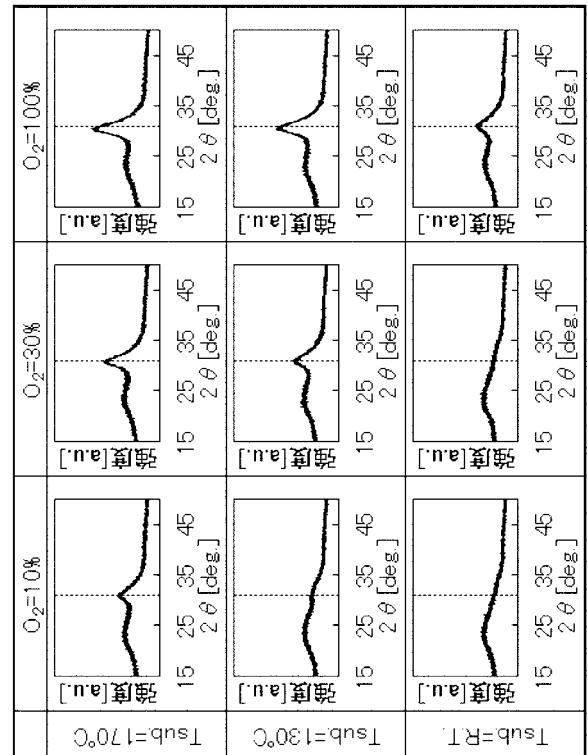

図 2 1 に Out - o f - plane 法を用いて XRD スペクトルを測定した結果を示す。なお、図 2 1 において、上段には成膜時の基板温度条件が 170 の試料における測定結果、中段には成膜時の基板温度条件が 130 の試料における測定結果、下段には成膜時の基板温度条件が R . T . の試料における測定結果を示す。また、左側の列には酸素ガス流量比の条件が 10 % の試料における測定結果、中央の列には酸素ガス流量比の条件が 30 % の試料における測定結果、右側の列には酸素ガス流量比の条件が 100 % の試料における測定結果、を示す。

#### 【 0 2 1 3 】

図 2 1 に示す XRD スペクトルは、成膜時の基板温度を高くする、または、成膜時の酸素ガス流量比の割合を大きくすることで、 $2 = 31^\circ$  付近のピーク強度が高くなる。なお、 $2 = 31^\circ$  付近のピークは、被形成面または上面に略垂直方向に対して c 軸に配向した結晶性 IGZO 化合物 ( CAAc ( c - axis aligned crystal line ) - IGZO ともいう。) であることに由来することが分かっている。

#### 【 0 2 1 4 】

また、図 2 1 に示す XRD スペクトルは、成膜時の基板温度が低い、または、酸素ガス流量比が小さいほど、明確なピークが現れなかった。従って、成膜時の基板温度が低い、または、酸素ガス流量比が小さい試料は、測定領域の a - b 面方向、および c 軸方向の配向は見られないことが分かる。

#### 【 0 2 1 5 】

##### 電子顕微鏡による解析

本項目では、成膜時の基板温度 R . T . 、および酸素ガス流量比 10 % で作製した試料を、 HAADF ( High - Angle Annular Dark Field ) - STEM ( Scanning Transmission Electron Microscope ) によって観察、および解析した結果について説明する ( 以下、 HAADF - STEM によって取得した像は、 TEM 像ともいう。 ) 。

#### 【 0 2 1 6 】

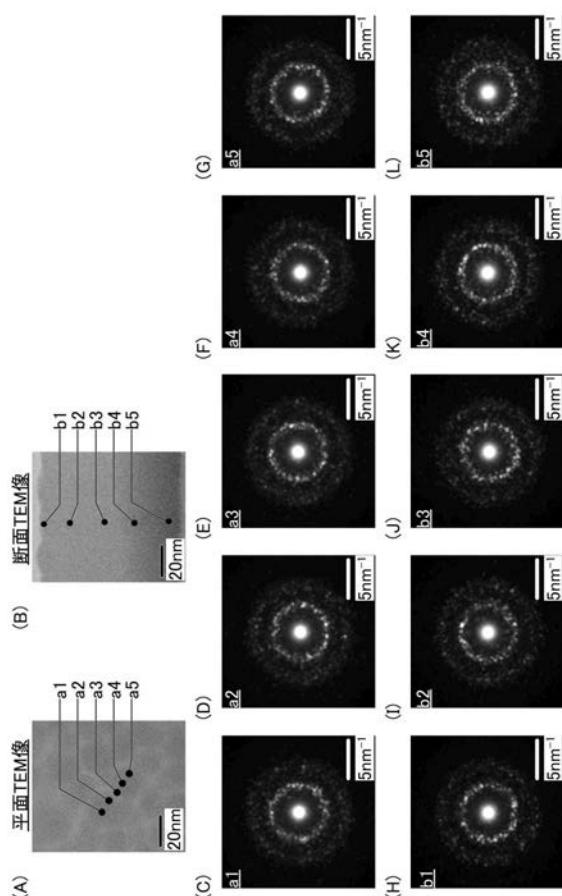

HAADF - STEM によって取得した平面像 ( 以下、平面 TEM 像ともいう。 ) 、および断面像 ( 以下、断面 TEM 像ともいう。 ) の画像解析を行った結果について説明する。なお、 TEM 像は、球面収差補正機能を用いて観察した。なお、 HAADF - STEM 像の撮影には、日本電子株式会社製原子分解能分析電子顕微鏡 JEM - ARM 200 F を用いて、加速電圧 200 kV 、ビーム径約 0 . 1 nm の電子線を照射して行った。

#### 【 0 2 1 7 】

図 2 2 ( A ) は、成膜時の基板温度 R . T . 、および酸素ガス流量比 10 % で作製した試料の平面 TEM 像である。図 2 2 ( B ) は、成膜時の基板温度 R . T . 、および酸素ガス流量比 10 % で作製した試料の断面 TEM 像である。

#### 【 0 2 1 8 】

##### 電子線回折パターンの解析

本項目では、成膜時の基板温度 R . T . 、および酸素ガス流量比 10 % で作製した試料に、プローブ径が 1 nm の電子線 ( ナノビーム電子線ともいう。 ) を照射することで、電子線回折パターンを取得した結果について説明する。

#### 【 0 2 1 9 】

図 2 2 ( A ) に示す、成膜時の基板温度 R . T . 、および酸素ガス流量比 10 % で作製した試料の平面 TEM 像において、黒点 a 1 、黒点 a 2 、黒点 a 3 、黒点 a 4 、および黒点 a 5 で示す電子線回折パターンを観察する。なお、電子線回折パターンの観察は、電子線を照射しながら 0 秒の位置から 35 秒の位置まで一定の速度で移動させながら行う。黒点 a 1 の結果を図 2 2 ( C ) 、黒点 a 2 の結果を図 2 2 ( D ) 、黒点 a 3 の結果を図 2 2 ( E ) 、黒点 a 4 の結果を図 2 2 ( F ) 、および黒点 a 5 の結果を図 2 2 ( G ) に示す。

#### 【 0 2 2 0 】

10

20

30

40

50

図22(C)、図22(D)、図22(E)、図22(F)、および図22(G)より、円を描くように(リング状に)輝度の高い領域が観測できる。また、リング状の領域に複数のスポットが観測できる。

#### 【0221】

また、図22(B)に示す、成膜時の基板温度R.T.、および酸素ガス流量比10%で作製した試料の断面TEM像において、黒点b1、黒点b2、黒点b3、黒点b4、および黒点b5で示す電子線回折パターンを観察する。黒点b1の結果を図22(H)、黒点b2の結果を図22(I)、黒点b3の結果を図22(J)、黒点b4の結果を図22(K)、および黒点b5の結果を図22(L)に示す。

10

#### 【0222】

図22(H)、図22(I)、図22(J)、図22(K)、および図22(L)より、リング状に輝度の高い領域が観測できる。また、リング状の領域に複数のスポットが観測できる。

#### 【0223】

ここで、例えば、InGaZnO<sub>4</sub>の結晶を有するCAAC-OSに対し、試料面に平行にプローブ径が300nmの電子線を入射させると、InGaZnO<sub>4</sub>の結晶の(009)面に起因するスポットが含まれる回折パターンが見られる。つまり、CAAC-OSは、c軸配向性を有し、c軸が被形成面または上面に略垂直な方向を向いていることがわかる。一方、同じ試料に対し、試料面に垂直にプローブ径が300nmの電子線を入射させると、リング状の回折パターンが確認される。つまり、CAAC-OSは、a軸およびb軸は配向性を有さないことがわかる。

20

#### 【0224】

また、微結晶を有する酸化物半導体(nano crystalline oxide semiconductor。以下、nc-OSという。)に対し、大きいプローブ径(例えば50nm以上)の電子線を用いる電子線回折を行うと、ハローパターンのような回折パターンが観測される。また、nc-OSに対し、小さいプローブ径の電子線(例えば50nm未満)を用いるナノビーム電子線回折を行うと、輝点(スポット)が観測される。また、nc-OSに対しナノビーム電子線回折を行うと、円を描くように(リング状に)輝度の高い領域が観測される場合がある。さらに、リング状の領域に複数の輝点が観測される場合がある。

30

#### 【0225】

成膜時の基板温度R.T.、および酸素ガス流量比10%で作製した試料の電子線回折パターンは、リング状に輝度の高い領域と、該リング領域に複数の輝点を有する。従って、成膜時の基板温度R.T.、および酸素ガス流量比10%で作製した試料は、電子線回折パターンが、nc-OSになり、平面方向、および断面方向において、配向性は有さない。

40

#### 【0226】

以上より、成膜時の基板温度が低い、または、酸素ガス流量比が小さい酸化物半導体は、アモルファス構造の酸化物半導体膜とも、単結晶構造の酸化物半導体膜とも明確に異なる性質を有すると推定できる。

40

#### 【0227】

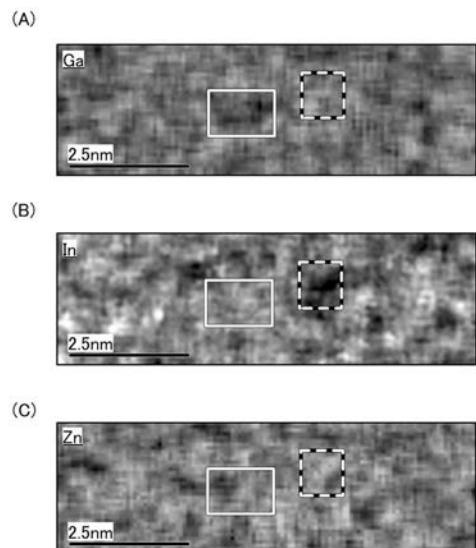

##### 元素分析

本項目では、エネルギー分散型X線分光法(EDX: Energy Dispersive X-ray spectroscopy)を用い、EDXマッピングを取得し、評価することによって、成膜時の基板温度R.T.、および酸素ガス流量比10%で作製した試料の元素分析を行った結果について説明する。なお、EDX測定には、元素分析装置として日本電子株式会社製エネルギー分散型X線分析装置JED-2300Tを用いる。なお、試料から放出されたX線の検出にはSiドリフト検出器を用いる。

#### 【0228】

EDX測定では、試料の分析対象領域の各点に電子線照射を行い、これにより発生する

50

試料の特性 X 線のエネルギーと発生回数を測定し、各点に対応する E D X スペクトルを得る。本実施の形態では、各点の E D X スペクトルのピークを、 I n 原子の L 裂への電子遷移、 G a 原子の K 裂への電子遷移、 Z n 原子の K 裂への電子遷移及び O 原子の K 裂への電子遷移に帰属させ、各点におけるそれぞれの原子の比率を算出する。これを試料の分析対象領域について行うことにより、各原子の比率の分布が示された E D X マッピングを得ることができる。

#### 【 0 2 2 9 】

図 2 3 には、成膜時の基板温度 R . T . 、および酸素ガス流量比 1 0 % で作製した試料の断面における E D X マッピングを示す。図 2 3 ( A ) は、 G a 原子の E D X マッピング ( 全原子に対する G a 原子の比率は 1 . 1 8 乃至 1 8 . 6 4 [ a t o m i c % ] の範囲とする。 ) である。図 2 3 ( B ) は、 I n 原子の E D X マッピング ( 全原子に対する I n 原子の比率は 9 . 2 8 乃至 3 3 . 7 4 [ a t o m i c % ] の範囲とする。 ) である。図 2 3 ( C ) は、 Z n 原子の E D X マッピング ( 全原子に対する Z n 原子の比率は 6 . 6 9 乃至 2 4 . 9 9 [ a t o m i c % ] の範囲とする。 ) である。また、図 2 3 ( A ) 、図 2 3 ( B ) 、および図 2 3 ( C ) は、成膜時の基板温度 R . T . 、および酸素ガス流量比 1 0 % で作製した試料の断面において、同範囲の領域を示している。なお、 E D X マッピングは、範囲における、測定元素が多いほど明るくなり、測定元素が少ないほど暗くなるように、明暗で元素の割合を示している。また、図 2 3 に示す E D X マッピングの倍率は 7 2 0 万倍である。

10

#### 【 0 2 3 0 】

図 2 3 ( A ) 、図 2 3 ( B ) 、および図 2 3 ( C ) に示す E D X マッピングでは、画像に相対的な明暗の分布が見られ、成膜時の基板温度 R . T . 、および酸素ガス流量比 1 0 % で作製した試料において、各原子が分布を持って存在している様子が確認できる。ここで、図 2 3 ( A ) 、図 2 3 ( B ) 、および図 2 3 ( C ) に示す実線で囲む範囲と破線で囲む範囲に注目する。

20

#### 【 0 2 3 1 】

図 2 3 ( A ) では、実線で囲む範囲は、相対的に暗い領域を多く含み、破線で囲む範囲は、相対的に明るい領域を多く含む。また、図 2 3 ( B ) では実線で囲む範囲は、相対的に明るい領域を多く含み、破線で囲む範囲は、相対的に暗い領域を多く含む。

30

#### 【 0 2 3 2 】

つまり、実線で囲む範囲は I n 原子が相対的に多い領域であり、破線で囲む範囲は I n 原子が相対的に少ない領域である。ここで、図 2 3 ( C ) では、実線で囲む範囲において、右側は相対的に明るい領域であり、左側は相対的に暗い領域である。従って、実線で囲む範囲は、 I n X 2 Z n Y 2 O Z 2 、または I n O X 1 などが主成分である領域である。

40

#### 【 0 2 3 3 】

また、実線で囲む範囲は G a 原子が相対的に少ない領域であり、破線で囲む範囲は G a 原子が相対的に多い領域である。図 2 3 ( C ) では、破線で囲む範囲において、左上の領域は、相対的に明るい領域であり、右下側の領域は、相対的に暗い領域である。従って、破線で囲む範囲は、 G a O X 3 、または G a X 4 Z n Y 4 O Z 4 などが主成分である領域である。

40

#### 【 0 2 3 4 】

また、図 2 3 ( A ) 、図 2 3 ( B ) 、および図 2 3 ( C ) より、 I n 原子の分布は、 G a 原子よりも、比較的、均一に分布しており、 I n O X 1 が主成分である領域は、 I n X 2 Z n Y 2 O Z 2 が主成分となる領域を介して、互いに繋がって形成されているよう見える。このように、 I n X 2 Z n Y 2 O Z 2 、または I n O X 1 が主成分である領域は、クラウド状に広がって形成されている。

#### 【 0 2 3 5 】

このように、 G a O X 3 などが主成分である領域と、 I n X 2 Z n Y 2 O Z 2 、または I n O X 1 が主成分である領域とが、偏在し、混合している構造を有する I n - G a - Z n 酸化物を、 C A C - O S と呼称することができる。

50

## 【0236】

また、CAC-O<sub>S</sub>における結晶構造は、n<sub>C</sub>構造を有する。CAC-O<sub>S</sub>が有するn<sub>C</sub>構造は、電子線回折像において、単結晶、多結晶、またはCAC構造を含むIGZOに起因する輝点（スポット）以外にも、数か所以上の輝点（スポット）を有する。または、数か所以上の輝点（スポット）に加え、リング状に輝度の高い領域が現れるとして結晶構造が定義される。

## 【0237】

また、図23(A)、図23(B)、および図23(C)より、GaOX<sub>3</sub>などが主成分である領域、及びInX<sub>2</sub>Z<sub>n</sub>Y<sub>2</sub>OZ<sub>2</sub>、またはInOX<sub>1</sub>が主成分である領域のサイズは、0.5nm以上10nm以下、または1nm以上3nm以下で観察される。なお、好ましくは、EDXマッピングにおいて、各元素が主成分である領域の径は、1nm以上2nm以下とする。

10

## 【0238】

以上より、CAC-O<sub>S</sub>は、金属元素が均一に分布したIGZO化合物とは異なる構造であり、IGZO化合物と異なる性質を有する。つまり、CAC-O<sub>S</sub>は、GaOX<sub>3</sub>などが主成分である領域と、InX<sub>2</sub>Z<sub>n</sub>Y<sub>2</sub>OZ<sub>2</sub>、またはInOX<sub>1</sub>が主成分である領域と、に互いに相分離し、各元素を主成分とする領域がモザイク状である構造を有する。

## 【0239】

ここで、InX<sub>2</sub>Z<sub>n</sub>Y<sub>2</sub>OZ<sub>2</sub>、またはInOX<sub>1</sub>が主成分である領域は、GaOX<sub>3</sub>などが主成分である領域と比較して、導電性が高い領域である。つまり、InX<sub>2</sub>Z<sub>n</sub>Y<sub>2</sub>OZ<sub>2</sub>、またはInOX<sub>1</sub>が主成分である領域を、キャリアが流れることにより、酸化物半導体としての導電性が発現する。従って、InX<sub>2</sub>Z<sub>n</sub>Y<sub>2</sub>OZ<sub>2</sub>、またはInOX<sub>1</sub>が主成分である領域が、酸化物半導体中にクラウド状に分布することで、高い電界効果移動度（μ）が実現できる。

20

## 【0240】

一方、GaOX<sub>3</sub>などが主成分である領域は、InX<sub>2</sub>Z<sub>n</sub>Y<sub>2</sub>OZ<sub>2</sub>、またはInOX<sub>1</sub>が主成分である領域と比較して、絶縁性が高い領域である。つまり、GaOX<sub>3</sub>などが主成分である領域が、酸化物半導体中に分布することで、リーク電流を抑制し、良好なスイッチング動作を実現できる。

30

## 【0241】

従って、CAC-O<sub>S</sub>を半導体素子に用いた場合、GaOX<sub>3</sub>などに起因する絶縁性と、InX<sub>2</sub>Z<sub>n</sub>Y<sub>2</sub>OZ<sub>2</sub>、またはInOX<sub>1</sub>に起因する導電性とが、相補的に作用することにより、高いオン電流（I<sub>on</sub>）、および高い電界効果移動度（μ）を実現することができる。

## 【0242】

また、CAC-O<sub>S</sub>を用いた半導体素子は、信頼性が高い。従って、CAC-O<sub>S</sub>は、ディスプレイをはじめとするさまざまな半導体装置に最適である。

## 【0243】

また、半導体層にCAC-O<sub>S</sub>を有するトランジスタは電界効果移動度が高く、且つ駆動能力が高いので、該トランジスタを、駆動回路、代表的にはゲート信号を生成するゲート線駆動回路に用いることで、額縁幅の狭い（狭額縁ともいう）表示装置を提供することができる。また、該トランジスタを、表示装置が有する信号線からの信号の供給を行う信号線駆動回路（とくに、信号線駆動回路が有するシフトレジスタの出力端子に接続されるデマルチブレクサ）に用いることで、表示装置に接続される配線数が少ない表示装置を提供することができる。

40

## 【0244】

また、半導体層にCAC-O<sub>S</sub>を有するトランジスタは低温ポリシコンを用いたトランジスタのように、レーザ結晶化工程が不要である。これのため、大面積基板を用いた表示装置であっても、製造コストを低減することが可能である。さらに、ウルトラハイビジョン（「4K解像度」、「4K2K」、「4K」）、スーパーハイビジョン（「8K解像度

50

」、「8K4K」、「8K」)のように高解像度であり、且つ大型の表示装置において、半導体層にC A C - O Sを有するトランジスタを駆動回路及び表示部に用いることで、短時間での書き込みが可能であり、表示不良を低減することが可能であり好ましい。

#### 【0245】

または、トランジスタのチャネルが形成される半導体にシリコンを用いてもよい。シリコンとしてアモルファスシリコンを用いてもよいが、特に結晶性を有するシリコンを用いることが好ましい。例えば、微結晶シリコン、多結晶シリコン、単結晶シリコンなどを用いることが好ましい。特に、多結晶シリコンは、単結晶シリコンに比べて低温で形成でき、且つアモルファスシリコンに比べて高い電界効果移動度と高い信頼性を備える。

#### 【0246】

本実施の形態で例示したボトムゲート構造のトランジスタは、作製工程を削減できるため好ましい。またこのときアモルファスシリコンを用いることで、多結晶シリコンよりも低温で形成できるため、半導体層よりも下層の配線や電極の材料、基板の材料として、耐熱性の低い材料を用いることが可能なため、材料の選択の幅を広げることができる。例えば、極めて大面積のガラス基板などを好適に用いることができる。一方、トップゲート型のトランジスタは、自己整合的に不純物領域を形成しやすいため、特性のばらつきなどを低減することができるため好ましい。このとき特に、多結晶シリコンや単結晶シリコンなどを用いる場合に適している。

#### 【0247】

##### 〔導電層〕

トランジスタのゲート、ソースおよびドレインのほか、表示装置を構成する各種配線および電極などの導電層に用いることのできる材料としては、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニアム、モリブデン、銀、タンタル、またはタングステンなどの金属、またはこれを主成分とする合金などが挙げられる。またこれらの材料を含む膜を単層で、または積層構造として用いることができる。例えば、シリコンを含むアルミニウム膜の単層構造、チタン膜上にアルミニウム膜を積層する二層構造、タングステン膜上にアルミニウム膜を積層する二層構造、銅 - マグネシウム - アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜上に銅膜を積層する二層構造、タングステン膜上に銅膜を積層する二層構造、チタン膜または窒化チタン膜と、その上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にチタン膜または窒化チタン膜を形成する三層構造、モリブデン膜または窒化モリブデン膜と、その上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造等がある。なお、酸化インジウム、酸化錫または酸化亜鉛等の酸化物を用いてもよい。また、マンガンを含む銅を用いると、エッチングによる形状の制御性が高まるため好ましい。

#### 【0248】

また、透光性を有する導電性材料としては、酸化インジウム、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛、ガリウムを添加した酸化亜鉛などの導電性酸化物またはグラフェンを用いることができる。または、金、銀、白金、マグネシウム、ニッケル、タングステン、クロム、モリブデン、鉄、コバルト、銅、パラジウム、またはチタンなどの金属材料や、該金属材料を含む合金材料を用いることができる。または、該金属材料の窒化物(例えば、窒化チタン)などを用いてもよい。なお、金属材料、合金材料(またはそれらの窒化物)を用いる場合には、透光性を有する程度に薄くすればよい。また、上記材料の積層膜を導電層として用いることができる。例えば、銀とマグネシウムの合金とインジウムスズ酸化物の積層膜などを用いると、導電性を高めることができるため好ましい。これらは、表示装置を構成する各種配線および電極などの導電層や、表示素子が有する導電層(画素電極や共通電極として機能する導電層)にも用いることができる。

#### 【0249】

##### 〔絶縁層〕

各絶縁層に用いることのできる絶縁材料としては、例えば、アクリル、エポキシなどの

10

20

30

40

50

樹脂、シロキサン結合を有する樹脂の他、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウムなどの無機絶縁材料を用いることもできる。

#### 【0250】

また、発光素子は、一対の透水性の低い絶縁膜の間に設けられていることが好ましい。これにより、発光素子に水等の不純物が侵入することを抑制でき、装置の信頼性の低下を抑制できる。

#### 【0251】

透水性の低い絶縁膜としては、窒化シリコン膜、窒化酸化シリコン膜等の窒素と珪素を含む膜や、窒化アルミニウム膜等の窒素とアルミニウムを含む膜等が挙げられる。また、酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜等を用いてもよい。

10

#### 【0252】

例えば、透水性の低い絶縁膜の水蒸気透過量は、 $1 \times 10 - 5 [ g / (m^2 \cdot day) ]$  以下、好ましくは $1 \times 10 - 6 [ g / (m^2 \cdot day) ]$  以下、より好ましくは $1 \times 10 - 7 [ g / (m^2 \cdot day) ]$  以下、さらに好ましくは $1 \times 10 - 8 [ g / (m^2 \cdot day) ]$  以下とする。

#### 【0253】

##### 〔液晶素子〕

液晶素子としては、例えば垂直配向（V A : Vertical Alignment）モードが適用された液晶素子を用いることができる。垂直配向モードとしては、M V A (Multi-Domain Vertical Alignment) モード、P V A (Patterned Vertical Alignment) モード、A S V (Advanced Super View) モードなどを用いることができる。

20

#### 【0254】

また、液晶素子には、様々なモードが適用された液晶素子を用いることができる。例えばV A モードのほかに、T N (Twisted Nematic) モード、I P S (In-Plane-Switching) モード、F F S (Fringe Field Switching) モード、A S M (Axially Symmetric aligned Micro-cell) モード、O C B (Optically Compensated Birefringence) モード、F L C (Ferroelectric Liquid Crystal) モード、A F L C (AntiFerroelectric Liquid Crystal) モード、E C B (Electrically Controlled Birefringence) モード、ゲストホストモード等が適用された液晶素子を用いることができる。

30

#### 【0255】

なお、液晶素子は、液晶の光学的変調作用によって光の透過または非透過を制御する素子である。なお、液晶の光学的変調作用は、液晶にかかる電界（横方向の電界、縦方向の電界または斜め方向の電界を含む）によって制御される。なお、液晶素子に用いる液晶としては、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶（P D L C : Polymer Dispersed Liquid Crystal）、高分子ネットワーク型液晶（P N L C : Polymer Network Liquid Crystal）、強誘電性液晶、反強誘電性液晶等を用いることができる。これらの液晶材料は、条件により、コレステリック相、スメクチック相、キュービック相、カイラルネマチック相、等方相等を示す。

40

#### 【0256】

また、液晶材料としては、ポジ型の液晶、またはネガ型の液晶のいずれを用いてもよく、適用するモードや設計に応じて最適な液晶材料を用いればよい。

#### 【0257】

また、液晶の配向を制御するため、配向膜を設けることができる。なお、横電界方式を採用する場合、配向膜を用いないブルー相を示す液晶を用いてもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転

50

移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善するために数重量%以上のカイラル剤を混合させた液晶組成物を液晶層に用いる。ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、応答速度が短く、光学的等方性である。また、ブルー相を示す液晶とカイラル剤とを含む液晶組成物は、配向処理が不要であり、視野角依存性が小さい。また配向膜を設けなくてもよいのでラビング処理も不要となるため、ラビング処理によって引き起こされる静電破壊を防止することができ、作製工程中の液晶表示装置の不良や破損を軽減することができる。

#### 【0258】

また、液晶素子として、透過型の液晶素子、反射型の液晶素子、または半透過型の液晶素子などを用いることができる。

10

#### 【0259】

本発明の一態様では、特に反射型の液晶素子を用いることができる。

#### 【0260】

透過型または半透過型の液晶素子を用いる場合、一対の基板を挟むように、2つの偏光板を設ける。また偏光板よりも外側に、バックライトを設ける。バックライトとしては、直下型のバックライトであってもよいし、エッジライト型のバックライトであってもよい。LED (Light Emission Diode) を備える直下型のバックライトを用いると、ローカルディミングが容易となり、コントラストを高めることができるため好ましい。また、エッジライト型のバックライトを用いると、バックライトを含めたモジュールの厚さを低減できるため好ましい。

20

め好ましい。

#### 【0261】

反射型の液晶素子を用いる場合には、表示面側に偏光板を設ける。またこれとは別に、表示面側に光拡散板を配置すると、視認性を向上させられるため好ましい。

#### 【0262】

また、反射型、または半透過型の液晶素子を用いる場合、偏光板よりも外側に、フロントライトを設けてもよい。フロントライトとしては、エッジライト型のフロントライトを用いることが好ましい。LED (Light Emission Diode) を備えるフロントライトを用いると、消費電力を低減できるため好ましい。

30

#### 【0263】

##### 〔発光素子〕

発光素子としては、自発光が可能な素子を用いることができ、電流または電圧によって輝度が制御される素子をその範疇に含んでいる。例えば、LED、有機EL素子、無機EL素子等を用いることができる。

#### 【0264】

発光素子は、トップエミッション型、ボトムエミッション型、デュアルエミッション型などがある。光を取り出す側の電極には、可視光を透過する導電膜を用いる。また、光を取り出さない側の電極には、可視光を反射する導電膜を用いることが好ましい。

#### 【0265】

EL層は少なくとも発光層を有する。EL層は、発光層以外の層として、正孔注入性の高い物質、正孔輸送性の高い物質、正孔ブロック材料、電子輸送性の高い物質、電子注入性の高い物質、またはバイポーラ性の物質（電子輸送性および正孔輸送性が高い物質）等を含む層をさらに有していてもよい。

40

#### 【0266】

EL層には低分子系化合物および高分子系化合物のいずれを用いることもでき、無機化合物を含んでいてもよい。EL層を構成する層は、それぞれ、蒸着法（真空蒸着法を含む）、転写法、印刷法、インクジェット法、塗布法等の方法で形成することができる。

#### 【0267】

陰極と陽極の間に、発光素子の閾値電圧より高い電圧を印加すると、EL層に陽極側から正孔が注入され、陰極側から電子が注入される。注入された電子と正孔はEL層におい

50

て再結合し、EL層に含まれる発光物質が発光する。

#### 【0268】

発光素子として、白色発光の発光素子を適用する場合には、EL層に2種類以上の発光物質を含む構成とすることが好ましい。例えば2以上の発光物質の各々の発光が補色の関係となるように、発光物質を選択することにより白色発光を得ることができる。例えば、それぞれR(赤)、G(緑)、B(青)、Y(黄)、O(橙)等の発光を示す発光物質、またはR、G、Bのうち2以上の色のスペクトル成分を含む発光を示す発光物質のうち、2以上を含むことが好ましい。また、発光素子からの発光のスペクトルが、可視光領域の波長(例えば350nm乃至750nm)の範囲内に2以上のピークを有する発光素子を適用することが好ましい。また、黄色の波長領域にピークを有する材料の発光スペクトルは、緑色および赤色の波長領域にもスペクトル成分を有する材料であることが好ましい。10

#### 【0269】

EL層は、一の色を発光する発光材料を含む発光層と、他の色を発光する発光材料を含む発光層とが積層された構成とすることが好ましい。例えば、EL層における複数の発光層は、互いに接して積層されていてもよいし、いずれの発光材料も含まない領域を介して積層されていてもよい。例えば、蛍光発光層と燐光発光層との間に、当該蛍光発光層または燐光発光層と同一の材料(例えばホスト材料、アシスト材料)を含み、且ついずれの発光材料も含まない領域を設ける構成としてもよい。これにより、発光素子の作製が容易になり、また、駆動電圧が低減される。

#### 【0270】

また、発光素子は、EL層を1つ有するシングル素子であってもよいし、複数のEL層が電荷発生層を介して積層されたタンデム素子であってもよい。

#### 【0271】

可視光を透過する導電膜は、例えば、酸化インジウム、インジウム錫酸化物、インジウム亜鉛酸化物、酸化亜鉛、ガリウムを添加した酸化亜鉛などを用いて形成することができる。また、金、銀、白金、マグネシウム、ニッケル、タングステン、クロム、モリブデン、鉄、コバルト、銅、パラジウム、もしくはチタン等の金属材料、これら金属材料を含む合金、またはこれら金属材料の窒化物(例えば、窒化チタン)等も、透光性を有する程度に薄く形成することで用いることができる。また、上記材料の積層膜を導電層として用いることができる。例えば、銀とマグネシウムの合金とインジウム錫酸化物の積層膜などを用いると、導電性を高めることができるために好ましい。また、グラフェン等を用いてもよい。30

#### 【0272】

可視光を反射する導電膜は、例えば、アルミニウム、金、白金、銀、ニッケル、タングステン、クロム、モリブデン、鉄、コバルト、銅、もしくはパラジウム等の金属材料、またはこれら金属材料を含む合金を用いることができる。また、上記金属材料や合金に、ランタン、ネオジム、またはゲルマニウム等が添加されていてもよい。また、チタン、ニッケル、またはネオジムと、アルミニウムを含む合金(アルミニウム合金)を用いてもよい。また銅、パラジウム、マグネシウムと、銀を含む合金を用いてもよい。銀と銅を含む合金は、耐熱性が高いため好ましい。さらに、アルミニウム膜またはアルミニウム合金膜に接して金属膜または金属酸化物膜を積層することで、酸化を抑制することができる。このような金属膜、金属酸化物膜の材料としては、チタンや酸化チタンなどが挙げられる。また、上記可視光を透過する導電膜と金属材料からなる膜とを積層してもよい。例えば、銀とインジウム錫酸化物の積層膜、銀とマグネシウムの合金とインジウム錫酸化物の積層膜などを用いることができる。40

#### 【0273】

電極は、それぞれ、蒸着法やスパッタリング法を用いて形成すればよい。そのほか、インクジェット法などの吐出法、スクリーン印刷法などの印刷法、またはメッキ法を用いて形成することができる。

#### 【0274】

10

20

30

40

50

なお、上述した、発光層、ならびに正孔注入性の高い物質、正孔輸送性の高い物質、電子輸送性の高い物質、および電子注入性の高い物質、バイポーラ性の物質等を含む層は、それぞれ量子ドットなどの無機化合物や、高分子化合物（オリゴマー、デンドリマー、ポリマー等）を有していてもよい。例えば、量子ドットを発光層に用いることで、発光材料として機能させることもできる。

#### 【0275】

なお、量子ドット材料としては、コロイド状量子ドット材料、合金型量子ドット材料、コア・シェル型量子ドット材料、コア型量子ドット材料などを用いることができる。また、12族と16族、13族と15族、または14族と16族の元素グループを含む材料を用いてもよい。または、カドミウム、セレン、亜鉛、硫黄、リン、インジウム、テルル、鉛、ガリウム、ヒ素、アルミニウム等の元素を含む量子ドット材料を用いてもよい。

10

#### 【0276】

##### 〔接着層〕

接着層としては、紫外線硬化型等の光硬化型接着剤、反応硬化型接着剤、熱硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤を用いることができる。これら接着剤としてはエポキシ樹脂、アクリル樹脂、シリコーン樹脂、フェノール樹脂、ポリイミド樹脂、イミド樹脂、PVC（ポリビニルクロライド）樹脂、PVB（ポリビニルブチラル）樹脂、EVA（エチレンビニルアセート）樹脂等が挙げられる。特に、エポキシ樹脂等の透湿性が低い材料が好ましい。また、二液混合型の樹脂を用いてもよい。また、接着シート等を用いてもよい。

20

#### 【0277】

また、上記樹脂に乾燥剤を含んでいてもよい。例えば、アルカリ土類金属の酸化物（酸化カルシウムや酸化バリウム等）のように、化学吸着によって水分を吸着する物質を用いることができる。または、ゼオライトやシリカゲル等のように、物理吸着によって水分を吸着する物質を用いてもよい。乾燥剤が含まれていると、水分などの不純物が素子に侵入することを抑制でき、表示パネルの信頼性が向上するため好ましい。

#### 【0278】

また、上記樹脂に屈折率の高いフィラーや光散乱部材を混合することにより、光取り出し効率を向上させることができる。例えば、酸化チタン、酸化バリウム、ゼオライト、ジルコニア等を用いることができる。

30

#### 【0279】

##### 〔接続層〕

接続層としては、異方性導電フィルム（ACF：Anisotropic Conductive Film）や、異方性導電ペースト（ACP：Anisotropic Conductive Paste）などを用いることができる。

#### 【0280】

##### 〔着色層〕

着色層に用いることのできる材料としては、金属材料、樹脂材料、顔料または染料が含まれた樹脂材料などが挙げられる。

#### 【0281】

##### 〔遮光層〕

遮光層として用いることのできる材料としては、カーボンブラック、チタンブラック、金属、金属酸化物、複数の金属酸化物の固溶体を含む複合酸化物等が挙げられる。遮光層は、樹脂材料を含む膜であってもよいし、金属などの無機材料の薄膜であってもよい。また、遮光層に、着色層の材料を含む膜の積層膜を用いることもできる。例えば、ある色の光を透過する着色層に用いる材料を含む膜と、他の色の光を透過する着色層に用いる材料を含む膜との積層構造を用いることができる。着色層と遮光層の材料を共通化することで、装置を共通化できるほか工程を簡略化できるため好ましい。

40

#### 【0282】

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組

50

み合わせて実施することができる。

**【0283】**

(実施の形態4)

本発明の一態様の入出力パネルの構成について、図19および図20を参照しながら説明する。

**【0284】**

図19は、本発明の一態様の入出力パネルの構成を説明する図である。図19は入出力パネルが備える画素の断面図である。

**【0285】**

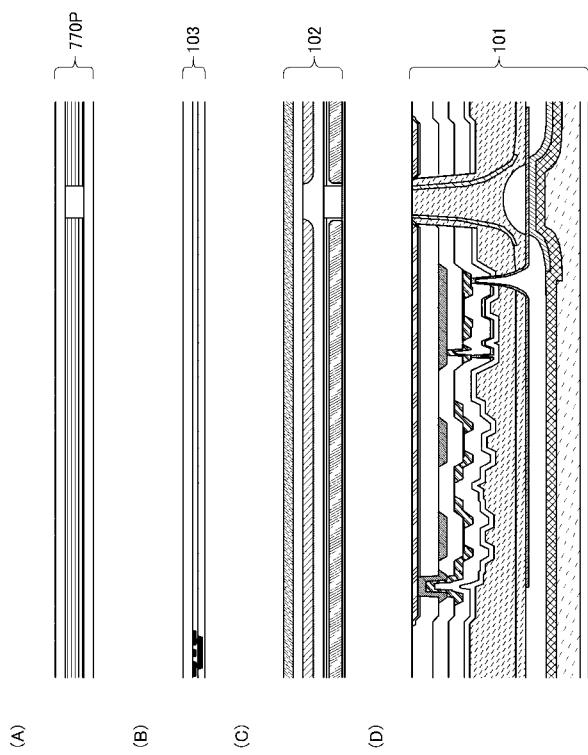

図20は、本発明の一態様の入出力パネルの構成を説明する図である。図20(A)は図19に示す入出力パネルの機能膜の構成を説明する断面図であり、図20(B)は入力ユニットの構成を説明する断面図であり、図20(C)は第2のユニットの構成を説明する断面図であり、図20(D)は第1のユニットの構成を説明する断面図である。

**【0286】**

なお、本明細書において、1以上の整数を値とする変数を符号に用いる場合がある。例えば、1以上の整数の値をとる変数pを含む(p)を、最大p個の構成要素のいずれかを特定する符号の一部に用いる場合がある。また、例えば、1以上の整数の値をとる変数mおよび変数nを含む(m, n)を、最大m×n個の構成要素のいずれかを特定する符号の一部に用いる場合がある。

**【0287】**

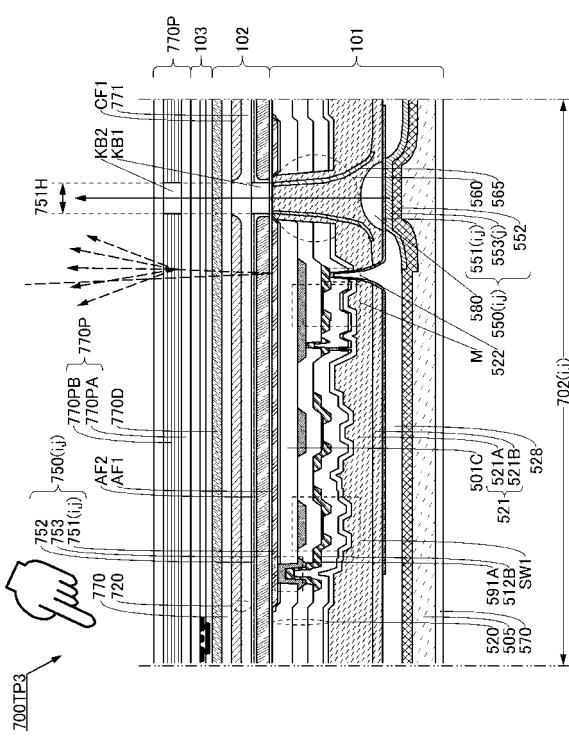

本構成例で説明する入出力パネル700TP3は、画素702(i, j)を有する(図19参照)。また、入出力パネル700TP3は、第1のユニット101と、第2のユニット102と、入力ユニット103と、機能膜770Pと、を有する(図20参照)。第1のユニット101は機能層520を含み、第2のユニット102は機能層720を含む。

**【0288】**

《画素702(i, j)》

画素702(i, j)は、機能層520の一部と、第1の表示素子750(i, j)と、第2の表示素子550(i, j)と、を有する(図19参照)。

**【0289】**

機能層520は、第1の導電膜、第2の導電膜、絶縁膜501Cおよび画素回路530(i, j)を含む。なお、図示しない画素回路530(i, j)は、例えば、トランジスタMを含む。また、機能層520は、光学素子560、被覆膜565およびレンズ580を含んでいてもよい。また、機能層520は、絶縁膜528および絶縁膜521を備えていてもよい。絶縁膜521Aおよび絶縁膜521Bを積層した材料を、絶縁膜521に用いることができる。

**【0290】**

例えば、屈折率1.55近傍の材料を絶縁膜521Aまたは絶縁膜521Bに用いることができる。または、屈折率1.6近傍の材料を絶縁膜521Aまたは絶縁膜521Bに用いることができる。または、アクリル樹脂またはポリイミドを絶縁膜521Aまたは絶縁膜521Bに用いることができる。

**【0291】**

絶縁膜501Cは、第1の導電膜および第2の導電膜の間に挟まれる領域を備え、絶縁膜501Cは開口部591Aを備える。

**【0292】**

第1の導電膜は、第1の表示素子750(i, j)と電気的に接続される。具体的には、第1の表示素子750(i, j)の電極751(i, j)と電気的に接続される。なお、電極751(i, j)を、第1の導電膜に用いることができる。

**【0293】**

第2の導電膜は、第1の導電膜と重なる領域を備える。第2の導電膜は、開口部591

10

20

30

40

50

Aにおいて、第1の導電膜と電気的に接続される。例えば、導電膜512Bを第2の導電膜に用いることができる。第2の導電膜は、画素回路530(i,j)と電気的に接続される。例えば、画素回路530(i,j)のスイッチSW1に用いるトランジスタのソース電極またはドレイン電極として機能する導電膜を第2の導電膜に用いることができる。ところで、絶縁膜501Cに設けられた開口部591Aにおいて第2の導電膜と電気的に接続される第1の導電膜を、貫通電極ということができる。

#### 【0294】

第2の表示素子550(i,j)は、画素回路530(i,j)と電気的に接続される。第2の表示素子550(i,j)は、機能層520に向けて光を射出する機能を備える。また、第2の表示素子550(i,j)は、例えば、レンズ580または光学素子560に向けて光を射出する機能を備える。10

#### 【0295】

第2の表示素子550(i,j)は、第1の表示素子750(i,j)を用いた表示を視認できる範囲の一部において、第2の表示素子を用いた表示を視認できるように、上記の第2の表示素子が配設される。例えば、第2の表示素子550(i,j)が射出する光を遮らない領域751Hを備える形状を第1の表示素子750(i,j)の電極751(i,j)に用いる。なお、外光を反射する強度を制御して画像情報を表示する第1の表示素子750(i,j)に外光が入射し反射する方向を、破線の矢印を用いて図中に示す。また、第1の表示素子750(i,j)を用いた表示を視認できる範囲の一部に第2の表示素子550(i,j)が光を射出する方向を、実線の矢印を用いて図中に示す。20

#### 【0296】

これにより、第1の表示素子を用いた表示を視認することができる領域の一部において、第2の表示素子を用いた表示を視認することができる。または、入出力パネルの姿勢等を変えることなく使用者は表示を視認することができる。または、第1の表示素子が反射する光が表現する物体色と、第2の表示素子が射出する光が表現する光源色とを掛け合わせることができる。その結果、利便性または信頼性に優れた新規な入出力パネルを提供することができる。

#### 【0297】

例えば、第1の表示素子750(i,j)は、電極751(i,j)と、電極752と、液晶材料を含む層753と、を備える。また、配向膜AF1と、配向膜AF2とを備える。具体的には、反射型の液晶素子を第1の表示素子750(i,j)に用いることができる。30

#### 【0298】

例えば、屈折率2.0近傍の透明導電膜を電極752または電極751(i,j)に用いることができる。具体的には、インジウムとスズとシリコンを含む酸化物を電極752または電極751(i,j)に用いることができる。または、屈折率1.6近傍の材料を配向膜に用いることができる。

#### 【0299】

例えば、第2の表示素子550(i,j)は、電極551(i,j)と、電極552と、発光性の材料を含む層553(j)と、を備える。電極552は、電極551(i,j)と重なる領域を備える。発光性の材料を含む層553(j)は、電極551(i,j)および電極552の間に挟まれる領域を備える。電極551(i,j)は、接続部522において、画素回路530(i,j)と電気的に接続される。具体的には、有機EL素子を第2の表示素子550(i,j)に用いることができる。40

#### 【0300】

例えば、屈折率2.0近傍の透明導電膜を電極551(i,j)に用いることができる。具体的には、インジウムとスズとシリコンを含む酸化物を電極551(i,j)に用いることができる。または、屈折率1.8近傍の材料を発光性の材料を含む層553(j)に用いることができる。

#### 【0301】

10

20

30

40

50

光学素子 560 は透光性を備え、光学素子 560 は第 1 の領域、第 2 の領域および第 3 の領域を備える。

【0302】

第 1 の領域は第 2 の表示素子 550 ( i , j ) から可視光を供給される領域を含み、第 2 の領域は被覆膜 565 と接する領域を含み、第 3 の領域は可視光の一部を射出する機能を備える。また、第 3 の領域は第 1 の領域の可視光を供給される領域の面積以下の面積を備える。

【0303】

被覆膜 565 は可視光に対する反射性を備え、被覆膜 565 は可視光の一部を反射して、第 3 の領域に供給する機能を備える。

10

【0304】

例えば、金属を被覆膜 565 に用いることができる。具体的には、銀を含む材料を被覆膜 565 に用いることができる。例えば、銀およびパラジウム等を含む材料または銀および銅等を含む材料を被覆膜 565 に用いることができる。

【0305】

《レンズ 580》

可視光を透過する材料をレンズ 580 に用いることができる。または、1.3 以上 2.5 以下の屈折率を備える材料をレンズ 580 に用いることができる。例えば、無機材料または有機材料をレンズ 580 に用いることができる。

20

【0306】

例えば、酸化物または硫化物を含む材料をレンズ 580 に用いることができる。

【0307】

具体的には、酸化セリウム、酸化ハフニウム、酸化ランタン、酸化マグネシウム、酸化ニオブ、酸化タンタル、酸化チタン、酸化イットリウム、酸化亜鉛、インジウムとスズを含む酸化物またはインジウムとガリウムと亜鉛を含む酸化物などを、レンズ 580 に用いることができる。または、硫化亜鉛などを、レンズ 580 に用いることができる。

30

【0308】

例えば、樹脂を含む材料をレンズ 580 に用いることができる。具体的には、塩素、臭素またはヨウ素が導入された樹脂、重金属原子が導入された樹脂、芳香環が導入された樹脂、硫黄が導入された樹脂などをレンズ 580 に用いることができる。または、樹脂と樹脂より屈折率の高い材料のナノ粒子を含む樹脂をレンズ 580 に用いることができる。酸化チタンまたは酸化ジルコニアなどをナノ粒子に用いることができる。

【0309】

《機能層 720》

機能層 720 は、基板 770 および絶縁膜 501C の間に挟まれる領域を備える。機能層 720 は、絶縁膜 771 と、着色膜 CF1 と、を有する。

30

【0310】

着色膜 CF1 は、基板 770 および第 1 の表示素子 750 ( i , j ) の間に挟まれる領域を備える。

40

【0311】

絶縁膜 771 は、着色膜 CF1 と液晶材料を含む層 753 の間に挟まれる領域を備える。これにより、着色膜 CF1 の厚さに基づく凹凸を平坦にすることができる。または、着色膜 CF1 等から液晶材料を含む層 753 への不純物の拡散を、抑制することができる。

【0312】

例えば、屈折率 1.55 近傍のアクリル樹脂を、絶縁膜 771 に用いることができる。

【0313】

《基板 570、基板 770》

また、本実施の形態で説明する入出力パネルは、基板 570 と、基板 770 と、を有する。

50

【0314】

基板 770 は、基板 570 と重なる領域を備える。基板 770 は、基板 570 との間に機能層 520 を挟む領域を備える。

【0315】

基板 770 は、第 1 の表示素子 750 (i, j) と重なる領域を備える。例えば、複屈折が抑制された材料を当該領域に用いることができる。また、基板 770 は、反射防止層が設けられることが好ましい。反射防止層として、多層構造の誘電体層を用いることで、光の干渉効果により光の反射を抑えることができる。

【0316】

例えば、屈折率 1.5 近傍の樹脂材料を基板 770 に用いることができる。

【0317】

《接合層 505》

また、本実施の形態で説明する入出力パネルは、接合層 505 を有する。

【0318】

接合層 505 は、機能層 520 および基板 570 の間に挟まれる領域を備え、機能層 520 および基板 570 を貼り合せる機能を備える。

【0319】

《構造体 KB1、構造体 KB2》

また、本実施の形態で説明する入出力パネルは、構造体 KB1 と、構造体 KB2 とを有する。

【0320】

構造体 KB1 は、機能層 520 および基板 770 の間に所定の間隙を設ける機能を備える。構造体 KB1 は領域 751H と重なる領域を備え、構造体 KB1 は透光性を備える。これにより、第 2 の表示素子 550 (i, j) によって射出される光を一方の面に供給され、他方の面から射出することができる。

【0321】

また、構造体 KB1 は光学素子 560 と重なる領域を備え、例えば、光学素子 560 に用いる材料の屈折率との差が 0.2 以下になるように選択された材料を構造体 KB1 に用いる。これにより、第 2 の表示素子 550 (i, j) が射出する光を効率よく利用することができる。または、第 2 の表示素子 550 (i, j) の面積を広くすることができる。または、有機 EL 素子に流す電流の密度を下げることができる。

【0322】

構造体 KB2 は、偏光層 770PB の厚さを所定の厚さに制御する機能を備える。構造体 KB2 は第 2 の表示素子 550 (i, j) と重なる領域を備え、構造体 KB2 は透光性を備える。

【0323】

または、所定の色の光を透過する材料を構造体 KB1 または構造体 KB2 に用いることができる。これにより、構造体 KB1 または構造体 KB2 を例えばカラーフィルターに用いることができる。例えば、青色、緑色または赤色の光を透過する材料を構造体 KB1 または構造体 KB2 に用いることができる。また、黄色の光または白色の光等を透過する材料を構造体 KB1 または構造体 KB2 に用いることができる。

【0324】

具体的には、ポリエスチル、ポリオレフィン、ポリアミド、ポリイミド、ポリカーボネート、ポリシロキサン若しくはアクリル樹脂等またはこれらから選択された複数の樹脂の複合材料などを構造体 KB1 または構造体 KB2 に用いることができる。また、感光性を有する材料を用いて形成してもよい。

【0325】

例えば、屈折率 1.5 近傍のアクリル樹脂を構造体 KB1 に用いることができる。また、屈折率 1.55 近傍のアクリル樹脂を構造体 KB2 に用いることができる。

【0326】

《入力ユニット 103》

10

20

30

40

50

入力ユニット 103 は検知素子を備える。検知素子は、画素 702 (i, j) と重なる領域に近接するものを検知する機能を備える。これにより、表示部に近接させる指などをポインタに用いて、位置情報を入力することができる。

#### 【0327】

例えば、静電容量型の近接センサ、電磁誘導型の近接センサ、光学方式の近接センサ、抵抗膜方式の近接センサまたは表面弹性波方式の近接センサなどを、入力ユニット 103 に用いることができる。具体的には、表面型静電容量方式、投影型静電容量方式または赤外線検知型の近接センサを用いることができる。

#### 【0328】

例えば、静電容量方式の近接センサを備える屈折率 1.6 近傍のタッチセンサを入力ユニット 103 に用いることができる。10

#### 【0329】

《機能膜 770D、機能膜 770P 等》

また、本実施の形態で説明する入出力パネル 700TP3 は、機能膜 770D と、機能膜 770P と、を有する。

#### 【0330】

機能膜 770D は第 1 の表示素子 750 (i, j) と重なる領域を備える。機能膜 770D は機能層 520 との間に第 1 の表示素子 750 (i, j) を挟む領域を備える。

#### 【0331】

例えば、光拡散フィルムを機能膜 770D に用いることができる。具体的には、基板の表面と交差する方向に沿った軸を備える柱状構造を有する材料を、機能膜 770D に用いることができる。これにより、光を軸に沿った方向に透過し易く、他の方向に散乱し易くすることができる。または、例えば、第 1 の表示素子 750 (i, j) が反射する光を拡散することができる。20

#### 【0332】

機能膜 770P は、偏光層 770PB、位相差フィルム 770PA または構造体 KB2 を備える。偏光層 770PB は開口部を備え、位相差フィルム 770PA は偏光層 770PB と重なる領域を備える。なお、構造体 KB2 は開口部に設けられる。

#### 【0333】

例えば、二色性色素、液晶材料および樹脂を偏光層 770PB に用いることができる。偏光層 770PB は、偏光性を備える。これにより、機能膜 770P を偏光板に用いることができる。30

#### 【0334】

偏光層 770PB は第 1 の表示素子 750 (i, j) と重なる領域を備え、構造体 KB2 は第 2 の表示素子 550 (i, j) と重なる領域を備える。これにより、液晶素子を第 1 の表示素子に用いることができる。例えば、反射型の液晶素子を第 1 の表示素子に用いることができる。または、第 2 の表示素子が射出する光を効率よく取り出すことができる。または、有機 EL 素子に流す電流の密度を下げることができる。または、有機 EL 素子の信頼性を高めることができる。

#### 【0335】

例えば、反射防止フィルム (A G (A n t i - G l a r e ) f i l m)、偏光フィルムまたは位相差フィルムを機能膜 770P に用いることができる。具体的には、2 色性色素を含む膜および位相差フィルムを機能膜 770P に用いることができる。40

#### 【0336】

また、ゴミの付着を抑制する帯電防止膜、汚れを付着しにくくする撥水性の膜、使用に伴う傷の発生を抑制するハードコート膜などを、機能膜 770P に用いることができる。

#### 【0337】

例えば、屈折率 1.6 近傍の材料を光拡散フィルムに用いることができる。また、屈折率 1.6 近傍の材料を位相差フィルム 770PA に用いることができる。

#### 【0338】

50

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0339】

(実施の形態5)

本実施の形態では、本発明の一態様を用いて作製することができる表示モジュールについて説明する。

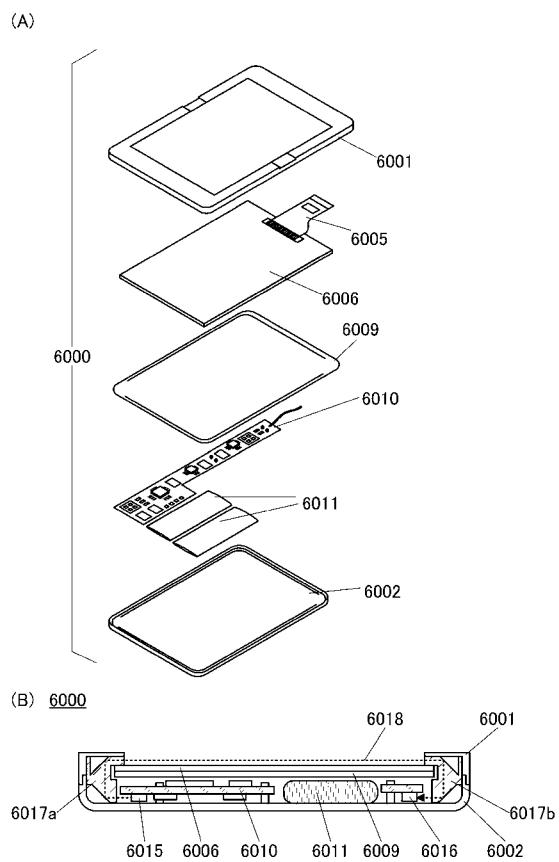

【0340】

図24(A)に示す表示モジュール6000は、上部カバー6001と下部カバー6002との間に、FPC6005に接続された表示パネル6006、フレーム6009、プリント基板6010、及びバッテリ6011を有する。

10

【0341】

例えば、本発明の一態様を用いて作製された表示装置を、表示パネル6006に用いることができる。これにより、高い歩留まりで表示モジュールを作製することができる。

【0342】

上部カバー6001及び下部カバー6002は、表示パネル6006のサイズに合わせて、形状や寸法を適宜変更することができる。

【0343】

また、表示パネル6006に重ねてタッチパネルを設けてもよい。タッチパネルとしては、抵抗膜方式または静電容量方式のタッチパネルを表示パネル6006に重畠して用いることができる。また、タッチパネルを設けず、表示パネル6006に、タッチパネル機能を持たせるようにすることも可能である。

20

【0344】

フレーム6009は、表示パネル6006の保護機能の他、プリント基板6010の動作により発生する電磁波を遮断するための電磁シールドとしての機能を有する。またフレーム6009は、放熱板としての機能を有していてもよい。

【0345】

プリント基板6010は、電源回路、ビデオ信号及びクロック信号を出力するための信号生成回路等の回路を有する。電源回路に電力を供給する電源としては、外部の商用電源であっても良いし、別途設けたバッテリ6011による電源であってもよい。バッテリ6011は、商用電源を用いる場合には、省略可能である。又バッテリ6011は、表示パネルを湾曲させる領域と重ならないように配置する構成とする。当該構成は、バッテリ6011の破線を防ぐ上で好適である。

30

【0346】

また、表示モジュール6000は、偏光板、位相差板、プリズムシートなどの部材を追加して設けてもよい。

【0347】

図24(B)は、光学式のタッチセンサを備える表示モジュール6000の断面概略図である。

【0348】

表示モジュール6000は、プリント基板6010に設けられた発光部6015及び受光部6016を有する。また、上部カバー6001と下部カバー6002により囲まれた領域に一対の導光部(導光部6017a、導光部6017b)を有する。

40

【0349】

表示パネル6006は、フレーム6009を間に介してプリント基板6010やバッテリ6011と重ねて設けられている。表示パネル6006とフレーム6009は、導光部6017a、導光部6017bに固定されている。

【0350】

発光部6015から発せられた光6018は、導光部6017aにより表示パネル6006の上部を経由し、導光部6017bを通って受光部6016に達する。例えば指やスティラスなどの被検知体により、光6018が遮られることにより、タッチ操作を検出す

50

ることができる。

【0351】

発光部6015は、例えば表示パネル6006の隣接する2辺に沿って複数設けられる。受光部6016は、発光部6015と対向する位置に複数設けられる。これにより、タッチ操作がなされた位置の情報を取得することができる。

【0352】

発光部6015は、例えばLED素子などの光源を用いることができる。特に、発光部6015として、使用者に視認されず、且つ使用者にとって無害である赤外線を発する光源を用いることが好ましい。

【0353】

受光部6016は、発光部6015が発する光を受光し、電気信号に変換する光電素子を用いることができる。好適には、赤外線を受光可能なフォトダイオードを用いることができる。

10

【0354】

導光部6017a、導光部6017bとしては、少なくとも光6018を透過する部材を用いることができる。導光部6017a及び導光部6017bを用いることで、発光部6015と受光部6016とを表示パネル6006の下側に配置することができ、外光が受光部6016に到達してタッチセンサが誤動作することを抑制できる。特に、可視光を吸収し、赤外線を透過する樹脂を用いることが好ましい。これにより、タッチセンサの誤動作をより効果的に抑制できる。

20

【0355】

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0356】

(実施の形態6)

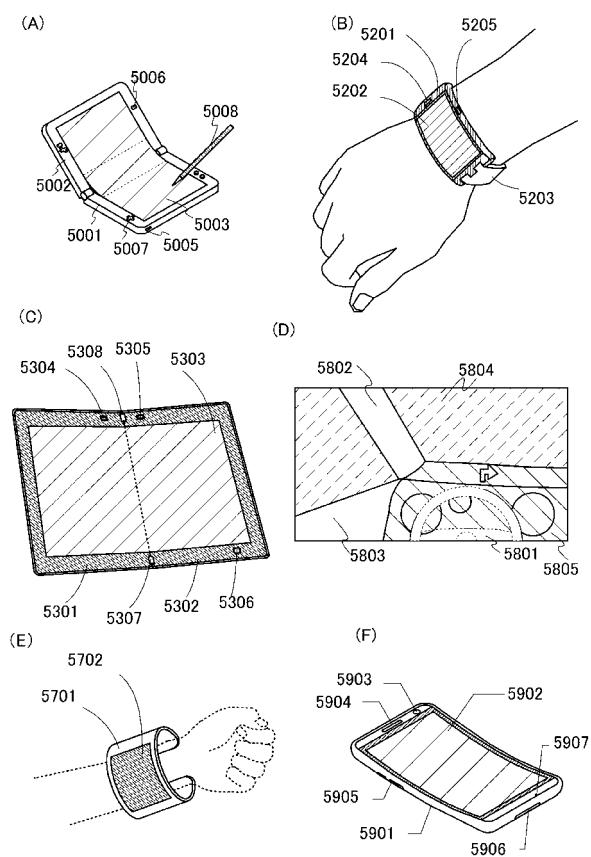

図25に、本発明の一態様に係る表示装置を有する携帯端末に適用可能な電子機器の具体例を示す。

【0357】

図25(A)は携帯型ゲーム機であり、筐体5001、筐体5002、本発明の一態様に係る表示装置5003、マイクロホン5005、スピーカ5006、操作キー5007、スタイルス5008等を有する。携帯型ゲーム機に本発明の一態様に係る表示装置5003を用いることで、使用環境における外光の強度に左右されずに、表示装置5003に表示品質の高い画像を表示することができ、消費電力も抑えることができる。

30

【0358】

図25(B)は腕時計型の携帯端末であり、筐体5201、本発明の一態様に係る表示装置5202、ベルト5203、光センサ5204、スイッチ5205等を有する。腕時計型の携帯端末に本発明の一態様に係る表示装置5202を用いることで、使用環境における外光の強度に左右されずに、表示装置5202に表示品質の高い画像を表示することができ、消費電力も抑えることができる。

40

【0359】

図25(C)はタブレット型のパーソナルコンピュータであり、筐体5301、筐体5302、本発明の一態様に係る表示装置5303、光センサ5304、光センサ5305、スイッチ5306等を有する。表示装置5303は、筐体5301及び筐体5302によって支持されている。そして、表示装置5303は可撓性を有する基板を用いて形成されているため形状をフレキシブルに曲げることができると機能を有する。筐体5301と筐体5302の間の角度をヒンジ5307及び5308において変更することで、筐体5301と筐体5302が重なるように、表示装置5303を折りたたむことができる。図示してはいないが、開閉センサを内蔵させ、上記角度の変化を表示装置5303において使用条件の情報として用いても良い。タブレット型のパーソナルコンピュータに本発明の一態様に係る表示装置5303を用いることで、使用環境における外光の強度に左右されず

50

に、表示装置 5303 に表示品質の高い画像を表示することができ、消費電力も抑えることができる。

#### 【0360】