(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2020-188267

(P2020-188267A)

(43) 公開日 令和2年11月19日(2020.11.19)

(51) Int.Cl.

**H01L 27/146 (2006.01)**

**H01L 21/76 (2006.01)**

**H04N 5/369 (2011.01)**

**G03B 13/36 (2006.01)**

**G02B 7/34 (2006.01)**

F 1

H01L 27/146

H01L 21/76

H04N 5/369

G03B 13/36

G02B 7/34

A

D

L

600

O L

テーマコード(参考)

2H011

2H151

4M118

5C024

5F032

審査請求 有 請求項の数 20 O L (全 28 頁) 最終頁に続く

(21) 出願番号

特願2020-120693 (P2020-120693)

(22) 出願日

令和2年7月14日(2020.7.14)

(62) 分割の表示

特願2016-104823 (P2016-104823)

の分割

原出願日

平成28年5月26日(2016.5.26)

(71) 出願人

000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人

100094112

弁理士 岡部 譲

(74) 代理人

100101498

弁理士 越智 隆夫

(74) 代理人

100106183

弁理士 吉澤 弘司

(74) 代理人

100128668

弁理士 斎藤 正巳

(72) 発明者

加藤 太朗

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

最終頁に続く

(54) 【発明の名称】撮像装置

## (57) 【要約】

【課題】複数の光電変換部を有する画素を有する撮像装置において、受光光量に応じた適切な画像の取得と焦点検出精度の向上とを実現しうる撮像装置を提供する。

【解決手段】2次元状に配された複数の画素を有する撮像装置であって、複数の画素のうちの少なくとも一部の画素は、半導体基板に設けられ、光電変換により生じた信号電荷を蓄積する第1導電型の第1の半導体領域をそれぞれが含む第1及び第2の光電変換部と、第1の光電変換部と前記第2の光電変換部との間の半導体基板に設けられ、第1の半導体領域の信号電荷に対して第1のポテンシャル障壁を形成する第2の半導体領域からなる第1の分離部と、第1の光電変換部と第2の光電変換部との間の半導体基板に設けられ、第1の半導体領域の信号電荷に対して第1のポテンシャル障壁よりも高い第2のポテンシャル障壁を形成するトレンチ分離からなる第2の分離部と、を有する。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

2次元状に配された複数の画素を有する撮像装置であって、

前記複数の画素のうちの少なくとも一部の画素は、

半導体基板に設けられ、光電変換により生じた信号電荷を蓄積する第1導電型の第1

の半導体領域をそれぞれが含む第1及び第2の光電変換部と、

前記第1の光電変換部と前記第2の光電変換部との間の前記半導体基板に設けられ、

前記第1の半導体領域の信号電荷に対して第1のポテンシャル障壁を形成する第2の半導

体領域からなる第1の分離部と、

前記第1の光電変換部と前記第2の光電変換部との間の前記半導体基板に設けられ、

前記第1の半導体領域の信号電荷に対して前記第1のポテンシャル障壁よりも高い第2の

ポテンシャル障壁を形成するトレンチ分離からなる第2の分離部と、を有する

ことを特徴とする撮像装置。

**【請求項 2】**

前記第1の光電変換部と前記第2の光電変換部とは、平面視において、第1の方向に隣

接して配置されており、

前記第1の分離部と前記第2の分離部とは、平面視において、前記第1の方向と交差す

る第2の方向に隣接して配置されている

ことを特徴とする請求項1記載の撮像装置。

**【請求項 3】**

前記少なくとも一部の画素は、2つの前記第2の分離部を含み、

2つの前記第2の分離部は、前記第2の方向に沿って前記第1の分離部を挟むように配

置されている

ことを特徴とする請求項2記載の撮像装置。

**【請求項 4】**

前記第1の分離部は、平面視において、前記画素の中心部に配置されている

ことを特徴とする請求項2又は3記載の撮像装置。

**【請求項 5】**

前記第1の分離部は、画素領域における前記画素の場所に応じて、前記画素内における

場所が定められている

ことを特徴とする請求項2又は3記載の撮像装置。

**【請求項 6】**

平面視における前記第1の分離部の長さは、平面視における前記第2の分離部の長さ以

下である

ことを特徴とする請求項1乃至5のいずれか1項に記載の撮像装置。

**【請求項 7】**

平面視における前記第2の分離部の幅は、平面視における前記第1の分離部の幅よりも

狭い

ことを特徴とする請求項1乃至6のいずれか1項に記載の撮像装置。

**【請求項 8】**

前記少なくとも一部の画素は、隣接する他の画素と前記第1の光電変換部及び前記第2

の光電変換部との間に設けられた第3の分離部を更に有し、

前記第3の分離部の、前記第1の半導体領域の信号電荷に対するポテンシャル障壁は、

前記第1のポテンシャル障壁よりも高い

ことを特徴とする請求項1乃至7のいずれか1項に記載の撮像装置。

**【請求項 9】**

平面視における前記第3の分離部の幅は、平面視における前記第1の分離部の幅よりも

広い

ことを特徴とする請求項8記載の撮像装置。

**【請求項 10】**

10

20

30

40

50

前記第3の分離部の少なくとも一部は、トレンチ分離により構成されていることを特徴とする請求項8又は9記載の撮像装置。

**【請求項11】**

前記第3の分離部は、前記半導体基板の第1の表面から、前記第1の半導体領域、前記第1の分離部及び前記第2の分離部が設けられた深さよりも深くに渡って設けられていることを特徴とする請求項8乃至10のいずれか1項に記載の撮像装置。

**【請求項12】**

前記第2の半導体領域は、第2導電型であり、

前記第3の分離部は、前記第2の半導体領域よりもキャリア濃度の高い前記第2導電型の第3の半導体領域を有する

ことを特徴とする請求項8乃至10のいずれか1項に記載の撮像装置。

10

**【請求項13】**

前記第2の半導体領域は、前記第1導電型であり、

前記第2の半導体領域のキャリア濃度は、前記第1の半導体領域のキャリア濃度よりも低い

ことを特徴とする請求項1乃至11のいずれか1項に記載の撮像装置。

**【請求項14】**

前記第2の分離部の周囲に、前記第2の半導体領域よりもキャリア濃度の高い第2導電型の第4の半導体領域を更に有する

ことを特徴とする請求項1乃至13のいずれか1項に記載の撮像装置。

20

**【請求項15】**

前記第2の分離部は、前記半導体基板に設けられたトレンチに、前記半導体基板とは屈折率の異なる材料又は金属材料が埋め込まれてなる

ことを特徴とする請求項1乃至14のいずれか1項に記載の撮像装置。

**【請求項16】**

前記第1の分離部及び前記第2の分離部は、前記半導体基板の第1の表面から、前記第1の半導体領域が設けられた深さよりも深くに渡って設けられている

ことを特徴とする請求項1乃至15のいずれか1項に記載の撮像装置。

**【請求項17】**

前記半導体基板は、第1の表面及び第2の表面を含み、

前記第1の分離部は、前記半導体基板の前記第1の表面から前記第2の表面に渡って設けられており、

前記第2の分離部は、前記半導体基板の前記第1の表面から前記第2の表面に渡る領域のうちの前記第1の表面側の一部分に設けられている

ことを特徴とする請求項1乃至15のいずれか1項に記載の撮像装置。

30

**【請求項18】**

前記少なくとも一部の画素は、前記半導体基板の前記第1の表面側に、前記第1の光電変換部及び前記第2の光電変換部に光を集光する1つのマイクロレンズを更に有する

ことを特徴とする請求項16又は17記載の撮像装置。

**【請求項19】**

請求項1乃至18のいずれか1項に記載の撮像装置と、

前記撮像装置から出力された信号を処理する信号処理部と、を有し、

前記信号処理部は、前記第1の光電変換部で生成された信号電荷に基づく第1の信号と、前記第2の光電変換部で生成された信号電荷に基づく第2の信号とに基づき、デフォーカス量を算出する

ことを特徴とする撮像システム。

40

**【請求項20】**

前記信号処理部は、前記第1の光電変換部及び前記第2の光電変換部で生成された信号電荷に基づく第3の信号に基づき、画像を生成する

ことを特徴とする請求項19記載の撮像システム。

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、複数の光電変換部を有する画素を含む撮像装置に関する。

**【背景技術】****【0002】**

ビデオカメラや電子スチルカメラなどの撮像システムにおいて、撮影時のフォーカス(ピント、焦点)調整を自動的に行うオートフォーカス(AF)機能が広く普及している。AF機能を備えた撮像装置としては、各画素が複数の光電変換部を有するものが知られている。1つの画素が2つの光電変換部を有する撮像装置では、1つの画素の2つの光電変換部からの1対の出力信号を用いて位相差方式による焦点検出を行うことができ、これら2つの光電変換部からの出力信号を加算することで画像用信号を取得することも可能である。

10

**【0003】**

特許文献1には、光電変換部間の分離構造を工夫することにより、複数の光電変換部の信号を1つの信号として取り扱う場合に、複数の光電変換部に感度や入射光量の差があるときにも適切な信号が得られるようにした光電変換装置が記載されている。

**【先行技術文献】****【特許文献】****【0004】**

20

【特許文献1】特開2013-084742号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

複数の光電変換部を有する画素を用いて撮像及び焦点検出を行う場合、焦点検出精度を高めること、複数の光電変換部に感度や入射光量の差があるときにも適切な信号が得られること、光電変換部の飽和電荷量を増やすこと、が求められる。

**【0006】**

しかしながら、これらにはトレードオフの関係があり、例えば特許文献1に記載の技術を用いて複数の光電変換部に感度や入射光量の差がある場合にも適切な信号を得られる構成とした場合、焦点検出精度や光電変換部の飽和電荷量が低下することがあった。特に、画素サイズが数ミクロン以下の撮像装置や裏面照射型の撮像装置の場合において、その影響は顕著であった。

30

**【0007】**

本発明の目的は、複数の光電変換部を有する画素を有する撮像装置において、受光光量に応じた適切な画像の取得と焦点検出精度の向上とを実現しうる撮像装置を提供することにある。

**【課題を解決するための手段】****【0008】**

40

本発明の一観点によれば、2次元状に配された複数の画素を有する撮像装置であって、前記複数の画素のうちの少なくとも一部の画素は、半導体基板に設けられ、光電変換により生じた信号電荷を蓄積する第1導電型の第1の半導体領域をそれぞれが含む第1及び第2の光電変換部と、前記第1の光電変換部と前記第2の光電変換部との間の前記半導体基板に設けられ、前記第1の半導体領域の信号電荷に対して第1のポテンシャル障壁を形成する第2の半導体領域からなる第1の分離部と、前記第1の光電変換部と前記第2の光電変換部との間の前記半導体基板に設けられ、前記第1の半導体領域の信号電荷に対して前記第1のポテンシャル障壁よりも高い第2のポテンシャル障壁を形成するトレンチ分離からなる第2の分離部と、を有する撮像装置が提供される。

**【発明の効果】****【0009】**

50

本発明によれば、複数の光電変換部を含む画素を有する撮像装置において、受光光量に応じた適切な画像の取得と焦点検出精度の向上とを実現することができる。

【図面の簡単な説明】

【0010】

【図1】本発明の第1実施形態による撮像装置の概略構成を示すブロック図である。

【図2】本発明の第1実施形態による撮像装置の画素回路の一例を示す図である。

【図3】本発明の第1実施形態による撮像装置の画素の構成例を示す図である。

【図4】撮像光学系の射出瞳と画素に入射する光との関係を説明する図である。

【図5】画素への入射光に対する光電変換部の感度の入射角特性を示すグラフである。

【図6】画素への入射光量と光電変換部からの出力との関係を示すグラフである。

10

【図7】本発明の第2実施形態による撮像装置の画素の構成例を示す図である。

【図8】本発明の第3実施形態による撮像装置の画素の構成例を示す図である。

【図9】本発明の第4実施形態による撮像装置の画素の構成例を示す図である。

【図10】本発明の第5実施形態による撮像装置の画素の構成例を示す図である。

【図11】本発明の第6実施形態による撮像装置の画素の構成例を示す図である。

【図12】本発明の第7実施形態による撮像装置の画素の構成例を示す図である。

【図13】本発明の第8実施形態による撮像システムの概略構成を示すブロック図である

。

【発明を実施するための形態】

【0011】

以下、本発明に係る撮像装置の実施形態について図面を参照して説明する。なお、本明細書で特に図示又は記載されない部分に関しては、当該技術分野の周知又は公知技術を適用することができる。また、以下に説明する各実施形態は、本発明の一つの実施形態であって、これに限定されるものではない。

【0012】

[第1実施形態]

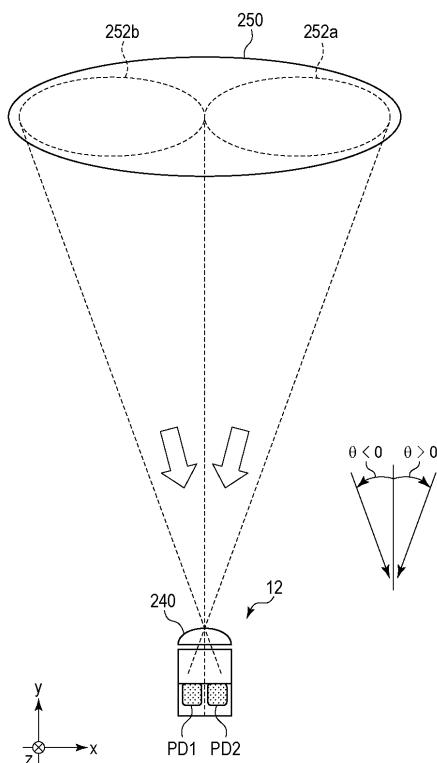

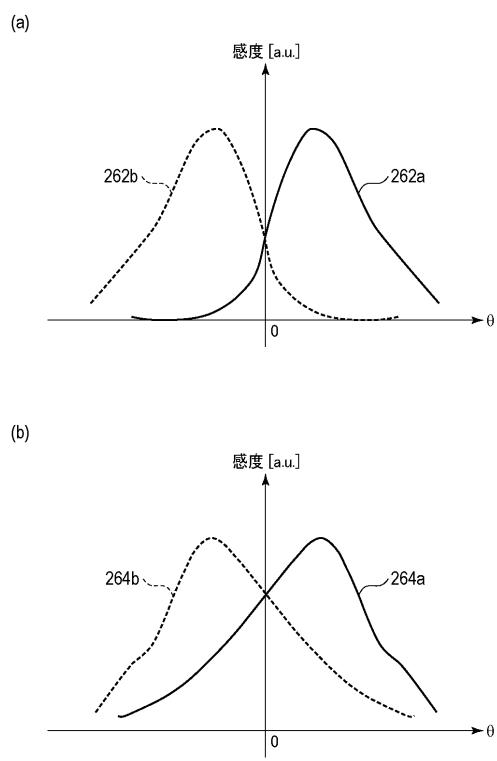

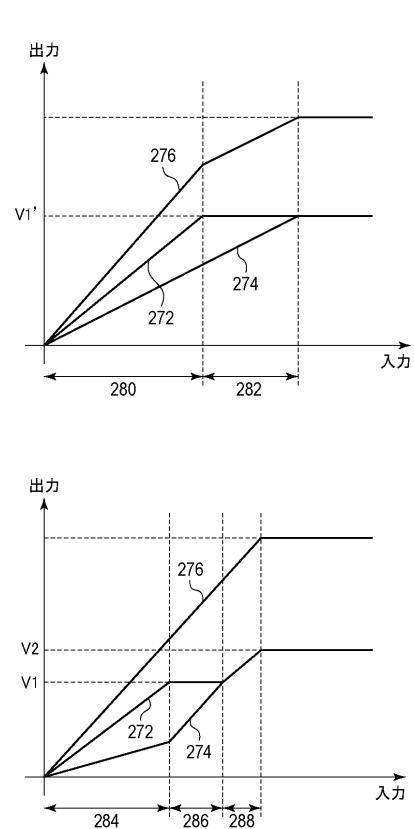

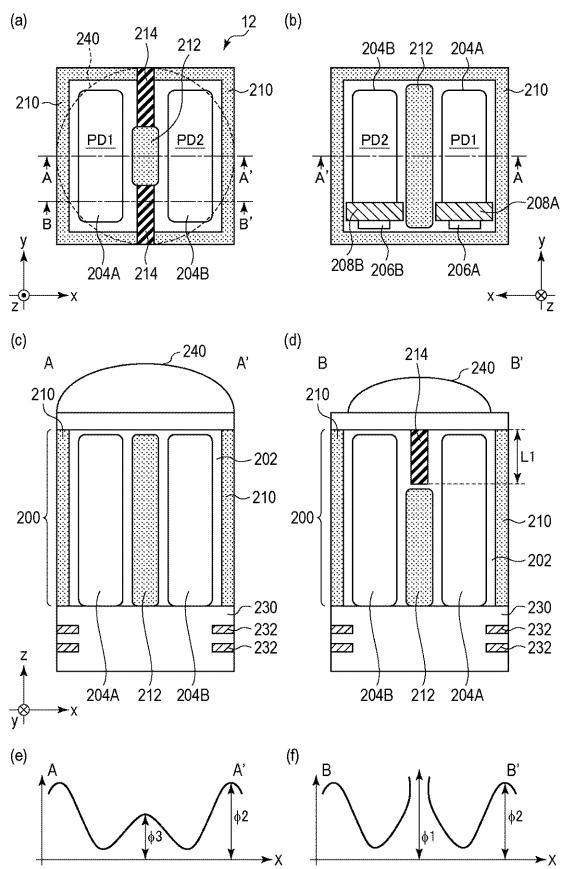

本発明の第1実施形態による撮像装置について、図1乃至図6を用いて説明する。図1は、本実施形態による撮像装置の構成例を示すブロック図である。図2は、本実施形態による撮像装置の画素回路の一例を示す図である。図3は、本実施形態による撮像装置の画素の構成例を示す図である。図4は、撮像光学系の射出瞳と画素に入射する光との関係を説明する図である。図5は、画素への入射光に対する光電変換部の感度の入射角特性を示すグラフである。図6は、画素への入射光量と光電変換部からの出力との関係を示すグラフである。

30

【0013】

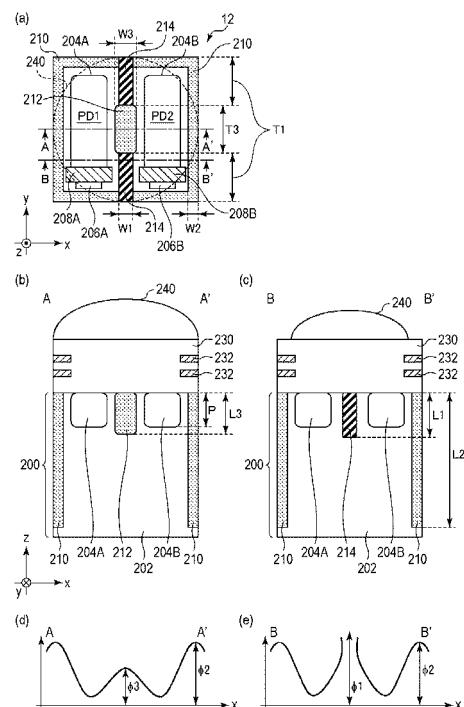

本実施形態による撮像装置100は、図1に示すように、画素領域10と、垂直走査回路20と、読み出し回路30A, 30Bと、水平走査回路40A, 40Bと、出力アンプ50A, 50Bと、制御回路60とを備えている。

【0014】

画素領域10には、複数の画素12が複数行及び複数列に渡って2次元状(マトリクス状)に配されている。複数の画素12は、撮像画素と、焦点検出画素とを含む。撮像画素は、画像を形成するための画像用信号を出力する画素である。焦点検出画素は、位相差方式による焦点検出を行うための焦点検出用信号を出力する画素である。焦点検出画素は、画素領域10内に分散して配されてもよいし、1次元状又は2次元状に並べて配されてもよい。焦点検出画素は、焦点検出を行うためだけに用いてもよいし、焦点検出用としてだけでなく、画像の生成用、すなわち撮像画素として用いてもよい。

40

【0015】

垂直走査回路20は、画素12から信号を読み出す際に画素12内の読み出し回路を駆動するための制御信号を、画素アレイの行毎に設けられた制御信号線14を介して画素12に供給する回路部である。画素12から読み出された信号は、画素アレイの列毎に設けられた垂直出力線16を介して読み出し回路30に入力される。図1には一例として、画

50

素領域 10 の対向する周辺部に読み出し回路 30A, 30B をそれぞれ設け、垂直出力線 16A を介して読み出し回路 30A に接続される列と、垂直出力線 16B を介して読み出し回路 30B に接続される列とに分けた場合を示している。読み出し回路 30 は、必ずしも複数に分ける必要はなく、総ての列に接続される 1 つの読み出し回路 30 を設けてよい。

#### 【0016】

読み出し回路 30A, 30B は、画素 12 から読み出された信号に対して所定の処理、例えば、増幅処理や加算処理等の信号処理を実施する回路部である。読み出し回路 30A, 30B は、例えば、列アンプ、相関二重サンプリング (CDS) 回路、加算回路等を含み得る。読み出し回路 30A, 30B は、A/D 変換回路を更に含んでもよい。

10

#### 【0017】

水平走査回路 40A, 40B は、読み出し回路 30A, 30B において処理された信号を列毎に順番に出力アンプ 50A, 50B に転送するための制御信号を、読み出し回路 30A, 30B に供給する回路部である。出力アンプ 50A, 50B は、バッファアンプや差動増幅器などから構成され、水平走査回路 40A, 40B によって選択された列の信号を増幅して出力するための回路部である。

20

#### 【0018】

制御回路 60 は、垂直走査回路 20、読み出し回路 30A, 30B 及び水平走査回路 40A, 40B に、それらの動作やタイミングを制御する制御信号を供給するための回路部である。撮像装置 100 には制御回路 60 を設けずに、垂直走査回路 20、読み出し回路 30A, 30B 及び水平走査回路 40A, 40B に供給する制御信号を、撮像装置 100 の外部から供給するようにしてもよい。

20

#### 【0019】

なお、本明細書において、画素領域 10 以外の領域、すなわち、垂直走査回路 20、読み出し回路 30A, 30B、水平走査回路 40A, 40B、出力アンプ 50A, 50B 及び制御回路 60 が設けられた領域は、周辺回路領域と称することがある。

#### 【0020】

以上の構成は、本発明を適用しうる撮像装置 100 の 1 つの構成例に過ぎず、本発明を適用可能な撮像装置の構成は、これに限定されるものではない。

30

#### 【0021】

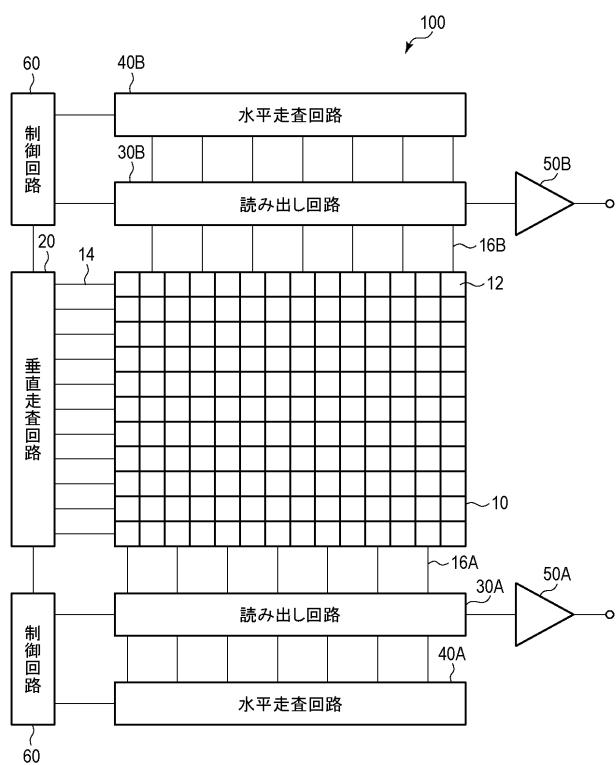

画素 12 は、例えば図 2 に示すように、光電変換部 PD1, PD2 と、転送トランジスタ M1, M2 と、リセットトランジスタ M3 と、増幅トランジスタ M4 と、選択トランジスタ M5 とを含む。光電変換部 PD1, PD2 は、例えばフォトダイオードである。光電変換部 PD1 のフォトダイオードは、アノードが接地電圧線に接続され、カソードが転送トランジスタ M1 のソースに接続されている。光電変換部 PD2 のフォトダイオードは、アノードが接地電圧線に接続され、カソードが転送トランジスタ M2 のソースに接続されている。転送トランジスタ M1, M2 のドレインは、リセットトランジスタ M3 のソース及び増幅トランジスタ M4 のゲートに接続されている。転送トランジスタ M1, M2 のソース、リセットトランジスタ M3 のソース及び増幅トランジスタ M4 のゲートの接続ノードは、いわゆる浮遊拡散 (フローティングディフュージョン: FD) 領域を構成する。リセットトランジスタ M3 のドレイン及び増幅トランジスタ M4 のドレインは、電源電圧線 (Vdd) に接続されている。増幅トランジスタ M4 のソースは、選択トランジスタ M5 のドレインに接続されている。選択トランジスタ M5 のソースは、垂直出力線 16 に接続されている。垂直出力線 16 の他端部には、増幅トランジスタ M4 にバイアス電流を供給してソースフォロワ回路を構成するための電流源 18 が接続されている。

40

#### 【0022】

光電変換部 PD1, PD2 は、光電変換によって入射光量に応じた電荷を生成する。転送トランジスタ M1 は、光電変換部 PD1 で生じた電荷を FD 領域へ転送する。転送トランジスタ M2 は、光電変換部 PD2 で生じた電荷を FD 領域へ転送する。FD 領域は、このノードに寄生する容量によって光電変換部 PD1, PD2 から転送された電荷を保持す

50

る電荷保持部として機能し、また、保持電荷量を増幅トランジスタM4のゲートに印加する電圧に変換する電荷電圧変換部としても機能する。リセットトランジスタM3は、FD領域及び光電変換部PD1, PD2の電位をリセットする機能を備える。増幅トランジスタM4は、ゲート電圧に応じた画素信号を、選択トランジスタM5を介して垂直出力線16に出力する。リセットトランジスタM3、増幅トランジスタM4及び選択トランジスタM5は、電荷保持部であるFD領域で保持されている電荷の量に基づく画素信号を出力する画素内読み出し回路を構成するトランジスタである。

【0023】

画素12から焦点検出信号を出力する場合は、光電変換部PD1で生成された信号電荷に基づく信号と、光電変換部PD2で生成された信号電荷に基づく信号とをそれぞれ出力する。外部の信号処理部は、光電変換部PD1で生成された信号電荷に基づく信号と、光電変換部PD2で生成された信号電荷に基づく信号とに基づき、デフォーカス量を算出する。画素12から画像信号を出力する場合は、光電変換部PD1で生成された信号電荷と光電変換部PD2で生成された信号電荷とをFD領域で足し合わせ、合計の信号電荷に基づく信号を出力する。

10

【0024】

図2に示す回路構成の場合、各行の制御信号線14は、転送ゲート信号線TX1, TX2、リセット信号線RES、選択信号線SELを含む。各行の転送ゲート信号線TX1は、当該行に属する複数の画素12の転送トランジスタM1のゲートに接続される。各行の転送ゲート信号線TX2は、当該行に属する複数の画素12の転送トランジスタM2のゲートに接続される。各行のリセット信号線RESは、当該行に属する複数の画素12のリセットトランジスタM3のゲートに接続される。各行の選択信号線SELは、当該行に属する複数の画素12の選択トランジスタM5のゲートに接続される。

20

【0025】

なお、撮像画素は、上述の焦点検出画素と同様の画素構成でもよいし、焦点検出画素とは異なる画素構成でもよい。撮像画素を焦点検出画素と同様の画素構成とする場合、2つの光電変換部PD1, PD2で生じた総電荷に基づき、画素信号を生成する。1つの画素12を構成する光電変換部の数は、必ずしも2つである必要はなく、3つ以上であってもよい。また、撮像画素にあっては、1つの画素12を構成する光電変換部の数は1つでもよい。

30

【0026】

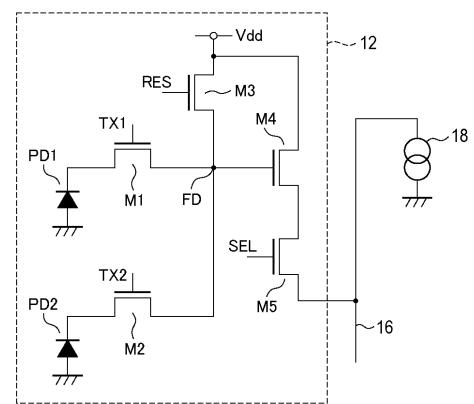

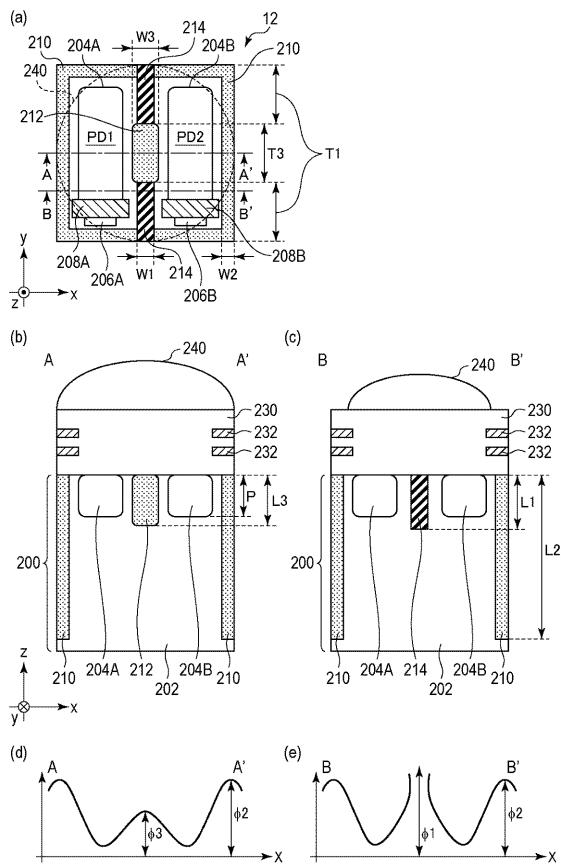

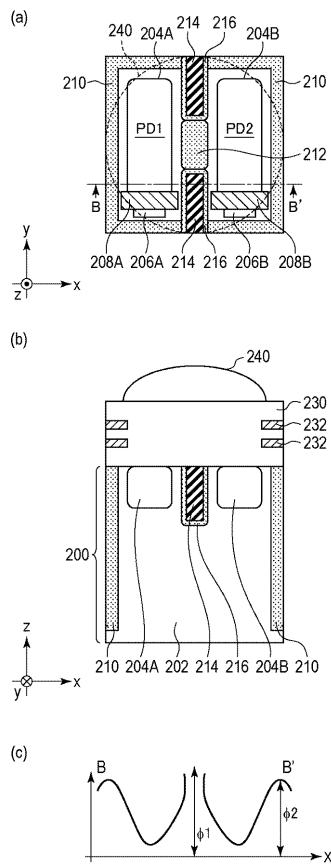

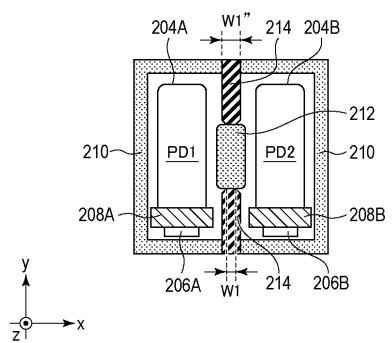

図3は、画素12の光電変換部PD1, PD2及び転送トランジスタM1, M2が設けられた部分の構造を示す図である。各画素12は、リセットトランジスタM3、増幅トランジスタM4、選択トランジスタM5をも更に含むが、ここでは説明を省略する。図3(a)は、光電変換部PD1, PD2を光の入射方向から見た平面図である。図3(b)は、図3(a)のA-A線断面図である。図3(c)は、図3(a)のB-B線断面図である。

30

【0027】

なお、以後の説明において、画素12は、焦点検出画素を表すものとする。ただし、撮像画素は、焦点検出画素と同様の構成とすることも可能である。本実施形態の撮像装置の画素構成は、後述するように、ニー特性のない合成出力や大きい飽和電荷量を得られるものであり、撮像画素に適用するうえでも有用である。

40

【0028】

半導体基板200の少なくとも主表面側には、p型半導体領域202が設けられている。半導体基板200は例えばn型シリコン基板であり、p型半導体領域202は例えばPウェルである。ここでは、説明の便宜上、半導体基板200の表面をx-y平面、半導体基板200の法線方向をz方向とする垂直座標系を定義するものとする。画素12への光の入射方向は、概ね-z方向である。また、x方向は、焦点検出画素の瞳分割方向に対応するものとする。

【0029】

50

光電変換部 P D 1 は、 p 型半導体領域 2 0 2 の表面部に設けられた n 型半導体領域 2 0 4 A を含む。 n 型半導体領域 2 0 4 A は、 p 型半導体領域 2 0 2 との間に P N 接合を形成し、光電変換部 P D 1 としてのフォトダイオードを構成している。 n 型半導体領域 2 0 4 A は、電子に対するポテンシャルが低くなっている、信号電荷である電子を蓄積する電荷蓄積部として機能する。ここでは、 n 型半導体領域 2 0 4 A の z 方向の深さを P とする。

【 0 0 3 0 】

同様に、光電変換部 P D 2 は、 p 型半導体領域 2 0 2 の表面部に、 n 型半導体領域 2 0 4 A から離して設けられた n 型半導体領域 2 0 4 B を含む。 n 型半導体領域 2 0 4 A , 2 0 4 B は、 x 方向に隣接して配置されている。 n 型半導体領域 2 0 4 B は、 p 型半導体領域 2 0 2 との間に P N 接合を形成し、光電変換部 P D 2 としてのフォトダイオードを構成している。 n 型半導体領域 2 0 4 B は、電子に対するポテンシャルが低くなっている、信号電荷である電子を蓄積する電荷蓄積部として機能する。ここでは、 n 型半導体領域 2 0 4 B の z 方向の深さを P とする。

10

【 0 0 3 1 】

このように、光電変換部 P D 1 と光電変換部 P D 2 とは、平面視において、 x 方向に隣接して配置されている。なお、本明細書では、半導体基板 2 0 0 の表面に平行な面に投影した各部の位置関係を説明する際に、「平面視」という表現を用いるものとする。平面視したレイアウトの一例は、半導体基板 2 0 0 を光の入射方向から見た平面図である。

【 0 0 3 2 】

光電変換部 P D 1 , P D 2 は、いわゆる埋め込みフォトダイオードとしてもよい。この場合、 n 型半導体領域 2 0 4 A , 2 0 4 B の表面部には、 n 型半導体領域 2 0 4 A , 2 0 4 B とは逆導電型の p 型半導体領域が設けられる。

20

【 0 0 3 3 】

p 型半導体領域 2 0 2 の表面部には、また、 n 型半導体領域 2 0 4 A から離して、 n 型半導体領域 2 0 6 A が設けられている。 n 型半導体領域 2 0 4 A , 2 0 6 A は、 y 方向に隣接して配置されている。 n 型半導体領域 2 0 4 A と n 型半導体領域 2 0 6 A との間の半導体基板 2 0 0 上には、図示しないゲート絶縁膜を介してゲート電極 2 0 8 A が設けられている。これにより、 n 型半導体領域 2 0 4 A をソース、 n 型半導体領域 2 0 6 A をドレイン、ゲート電極 2 0 8 A をゲートとする転送トランジスタ M 1 が構成されている。 n 型半導体領域 2 0 6 A は、 F D 領域である。

30

【 0 0 3 4 】

同様に、 p 型半導体領域 2 0 2 の表面部には、 n 型半導体領域 2 0 4 B から離して、 n 型半導体領域 2 0 6 B が設けられている。 n 型半導体領域 2 0 4 B , 2 0 6 B は、 y 方向に隣接して配置されている。 n 型半導体領域 2 0 4 B と n 型半導体領域 2 0 6 B との間の半導体基板 2 0 0 上には、図示しないゲート絶縁膜を介してゲート電極 2 0 8 B が設けられている。これにより、 n 型半導体領域 2 0 4 B をソース、 n 型半導体領域 2 0 6 B をドレイン、ゲート電極 2 0 8 B をゲートとする転送トランジスタ M 2 が構成されている。 n 型半導体領域 2 0 6 B は、 F D 領域である。

【 0 0 3 5 】

光電変換部 P D 1 , P D 2 及び転送トランジスタ M 1 , M 2 が設けられた領域の周囲には、この領域を囲うように分離部 2 1 0 が設けられている。分離部 2 1 0 は、光電変換部 P D 1 , P D 2 を、隣接する他の画素 1 2 から分離するためのものである。分離部 2 1 0 は、 p 型半導体領域 2 0 2 よりもキャリア濃度の高い p 型半導体領域を含む。分離部 2 1 0 の少なくとも一部は、 S T I (Shallow Trench Isolation) 法や L O C O S (Local Oxidation of Silicon) 法により形成した素子分離絶縁領域でもよい。ここでは、分離部 2 1 0 の z 方向の深さを L 2 とする。

40

【 0 0 3 6 】

また、分離部 2 1 0 で囲まれた領域内の、光電変換部 P D 1 及び転送トランジスタ M 1 が設けられた領域と、光電変換部 P D 2 及び転送トランジスタ M 2 が設けられた領域との間の領域には、分離部 2 1 2 及び 2 1 4 が設けられている。分離部 2 1 2 と分離部 2 1 4

50

とは、平面視において、 $x$  方向と交差する方向 ( $y$  方向) に隣接して配置されている。図 3 の例では、1 つの分離部 212 と 2 つの分離部 214 とが設けられており、2 つの分離部 214 は、平面視において、 $y$  方向に沿って分離部 212 を挟むように配置されている。つまり、光電変換部 PD1 が設けられた領域と光電変換部 PD2 が設けられた領域との間には、分離部 212 は設けられているが分離部 214 は設けられていない部分と、分離部 214 は設けられているが分離部 212 は設けられていない部分とがある。図 3 (a) には分離部 212 と分離部 214 とが接している状態を示しているが、分離部 212 と分離部 214 とは離間していてもよい。分離部 210, 212, 214 は、半導体基板 200 の表面から所定の深さに渡って設けられている。ここでは、分離部 212, 214 の  $z$  方向の深さを、それぞれ  $L_3, L_1$  とする。

10

#### 【0037】

分離部 212, 214 は、光電変換部 PD1 と光電変換部 PD2 との間を分離するためのものである。分離部 212 は、 $n$  型半導体領域 204A と  $n$  型半導体領域 204B との間に信号電荷に対してポテンシャル障壁を形成しうる半導体領域により構成されている。分離部 212 は、典型的には、光電変換部 PD1, PD2 の電荷蓄積部 ( $n$  型半導体領域 204A, 204B) と逆導電型の半導体領域 ( $p$  型半導体領域) からなり、 $n$  型半導体領域 204A と  $n$  型半導体領域 204B との間に PN 接合分離を形成する。分離部 212 は、 $n$  型半導体領域 204A と  $n$  型半導体領域 204B との間にポテンシャル障壁を形成しうる半導体領域であればよく、 $n$  型半導体領域 204A, 204B よりもキャリア濃度の低い  $n$  型半導体領域により構成されてもよい。分離部 214 は、半導体基板 200 に設けられたトレンチ内に充填材が埋め込まれてなる分離構造体、いわゆるトレンチ分離により構成されている。なお、分離部 212 は、光電変換部 PD1 と光電変換部 PD2 との間の、分離部 214 が設けられていない隙間の部分と考えることもできる。分離部 212 には、必ずしも別途の不純物を導入する必要はない。

20

#### 【0038】

半導体基板 200 の上には、絶縁層 230 が設けられている。絶縁層 230 は、1 種類の材料で形成された単層膜であってもよいし、異なる材料からなる複数の膜の積層膜であってもよい。絶縁層 230 を構成する材料は、特に限定されるものではないが、例えば、酸化シリコン ( $SiO_2$ )、窒化シリコン ( $Si_3N_4$ )、炭化シリコン ( $SiC$ ) などが挙げられる。例えば、絶縁層 230 は、酸化シリコンの単層膜であってもよいし、酸化シリコン、窒化シリコン及び炭化シリコンの積層膜であってもよい。絶縁層 230 は、その内部に、各部の接続配線や信号配線等を構成する配線層 232 を有する。配線層 232 は、1 層であってもよいし、2 層以上の多層構造であってもよい。図 3 は、配線層が 2 層構造の場合の例を示している。

30

#### 【0039】

絶縁層 230 の上には、マイクロレンズ 240 が設けられている。マイクロレンズ 240 は、2 つの光電変換部 PD1, PD2 を含む 1 つの画素 12 に対して 1 つずつ設けられており、入射した光を光電変換部 PD1, PD2 に集光する。マイクロレンズ 240 と半導体基板 200 との間には、カラーフィルタ (図示せず) を設けてもよい。

30

#### 【0040】

なお、上述した構成は、信号電荷として電子を用いる場合の一例である。信号電荷としてホールを用いる場合には、各半導体領域の導電型は逆になる。上記説明における各トランジスタのソース及びドレインの称呼は一例であり、トランジスタの導電型や着目する機能等によっては全部又は一部が逆の名称で呼ばれることがある。他の実施形態においても同様である。

40

#### 【0041】

図 3 (d) は、半導体基板 200 の表面から深さ  $L_1$  の間の領域における最小のポテンシャル障壁の高さを A-A 線断面に沿って繋ぐことにより描いたポテンシャル分布図である。図 3 (e) は、半導体基板 200 の表面から深さ  $L_1$  の間の領域における最小のポテンシャル障壁の高さを B-B 線断面に沿って繋ぐことにより描いたポテンシャル分布

50

図である。

【0042】

分離部214, 210, 212の信号電荷(ここでは電子)に対するポテンシャル障壁の高さをそれぞれ1, 2, 3とすると、ポテンシャル障壁の高さ1, 2, 3は、以下の関係を有している。

$$3 < 2 < 1$$

【0043】

なお、ポテンシャル障壁の高さ1は、n型半導体領域204Aとn型半導体領域204Bとの間に分離部214によって形成される、信号電荷に対するポテンシャル障壁の高さである。ポテンシャル障壁の高さ2は、隣接する画素とn型半導体領域204A, 204Bとの間に分離部210によって形成される、信号電荷に対するポテンシャル障壁の高さである。ポテンシャル障壁の高さ3は、n型半導体領域204Aとn型半導体領域204Bとの間に分離部212によって形成される、信号電荷に対するポテンシャル障壁の高さである。

10

【0044】

分離部214のy方向の長さの合計の長さをT1、x方向の幅をW1、分離部212のy方向の長さをT3、x方向の幅をW3、分離部210のx方向の幅をW2とすると、長さT1, T3、幅W1, W2, W3は、以下の関係を有していることが望ましい。

$$T_3 > T_1, W_3 > W_1, W_3 > W_2$$

20

【0045】

なお、本明細書において、分離部212, 214の長さとは、光電変換部PD1, PD2が隣接して配置される方向(x方向)と交差する方向(y方向)の分離部212, 214の長さである。分離部212, 214の幅とは、光電変換部PD1, PD2が隣接して配置される方向(x方向)の分離部212, 214の長さである。

20

【0046】

また、n型半導体領域204A, 204Bのz方向の深さをP、分離部214のz方向の深さをL1、分離部210のz方向の深さをL2、分離部212のz方向の深さをL3とすると、深さP, L1, L2, L3は、以下の関係を有していることが望ましい。

$$P < L_3 < L_2, P < L_1 < L_2$$

30

【0047】

次に、本実施形態による撮像装置において各パラメータを上記のように設定する理由やそれにより得られる具体的な効果を説明する前に、前提となる技術として、焦点検出画素を用いた焦点検出の原理について、簡単に説明する。なお、以下において画素12への光の入射角 $\theta$ を説明するときは、撮像光学系の光学軸、すなわちz軸に平行な方向(-z方向)から入射する光の入射角 $\theta$ を0度とする。そして、z軸からx-z平面の第一象限側に傾いた方向から入射する光の入射角 $\theta$ の符号を正( $\theta > 0$ )とし、z軸からx-z平面の第二象限側に傾いた方向から入射する光の入射角 $\theta$ の符号を負( $\theta < 0$ )とする(図4参照)。

30

【0048】

撮像光学系の射出瞳250を通過した光は、図4に示すように、マイクロレンズ240を介して、同じ画素12の光電変換部PD1, PD2に入射する。ここで、射出瞳250内に、x方向に隣接する瞳領域252aと瞳領域252bとを仮定する。射出瞳250を通過した光のうち瞳領域252aから画素12へと入射した光(すなわち、入射角 $\theta > 0$ の光)は、マイクロレンズ240を透過し、光電変換部PD1に入射する。一方、射出瞳250を通過した光のうち瞳領域252bから画素12へと入射した光(すなわち、入射角 $\theta < 0$ の光)は、マイクロレンズ240を透過し、光電変換部PD2に入射する。光電変換部PD1, PD2では、光電変換により、それぞれに入射した光の量に応じた信号電荷が生成される。

40

【0049】

位相差方式の焦点検出では、光電変換部PD1からの信号と光電変換部PD2からの信

50

号との位置関係を相対的にシフトさせて信号の一致度を表す相関量を計算し、相関（信号の一致度）が良くなるシフト量から像ずれ量を検出する。撮像信号のデフォーカス量の大きさが増加するのに伴い光電変換部 P D 1 からの信号と光電変換部 P D 2 からの信号との間の像ずれ量の大きさが増加する関係性から、像ずれ量をデフォーカス量に変換することで焦点検出を行うことができる。

#### 【0050】

このようにして、光電変換部 P D 1 から出力される信号と光電変換部 P D 2 から出力される信号との間の位相差を測定することにより、焦点検出を行うことができる。

#### 【0051】

図 5 は、光電変換部 P D 1, P D 2 の感度と入射光の入射角との関係（入射角特性）を示している。図 5 (a) は、焦点検出性能が良い画素 12 の入射角特性の一例である。比較のため、図 5 (b) には、焦点検出性能が悪い画素 12 の入射角特性を示している。図 5 (a) の特性 262a 及び図 5 (b) の特性 264a は、入射した光に対する光電変換部 P D 1 の感度を示している。図 5 (a) の特性 262b 及び図 5 (b) の特性 264b は、入射した光に対する光電変換部 P D 2 の感度を示している。感度の単位は任意である。

10

#### 【0052】

画素 12 内の光電変換部 P D 1 と光電変換部 P D 2 との間のポテンシャル障壁が十分に高い場合、光電変換部 P D 1 で生成される電荷と光電変換部 P D 2 で生成される電荷とは明確に分離され、図 5 (a) に示すような入射角特性となる。この場合、図 4 における瞳領域 252a から入射した光に基づく信号と瞳領域 252b から入射した光に基づく信号とが明確に分離されることとなり、焦点検出性能は良好である。

20

#### 【0053】

しかし、画素 12 内の光電変換部 P D 1 と光電変換部 P D 2 との間のポテンシャル障壁が低い場合、光電変換部 P D 1 と光電変換部 P D 2 との間での電荷の漏れ、すなわち電荷クロストークが多くなる。この場合、図 5 (b) に示すような入射角特性となり、光電変換部 P D 1 で生成される電荷に基づく信号と光電変換部 P D 2 で生成される電荷に基づく信号とは明確に分離されない。この結果、図 4 における瞳領域 252a から入射した光に基づく信号と瞳領域 252b から入射した光に基づく信号とが明確に分離されないこととなり、焦点検出性能は悪化する。

30

#### 【0054】

したがって、焦点検出性能を向上するためには、光電変換部 P D 1 と光電変換部 P D 2 との間のポテンシャル障壁は、できるだけ高くすることが望ましい。

#### 【0055】

しかしながら、光電変換部 P D 1 と光電変換部 P D 2 との間のポテンシャル障壁を高くしすぎると、以下のような課題が生じる。

#### 【0056】

図 6 は、画素 12 への入射光量（入力）と光電変換部 P D 1, P D 2 からの出力との関係を示すグラフである。図中、特性 272 が光電変換部 P D 1 からの出力を示し、特性 274 が光電変換部 P D 2 からの出力を示し、特性 276 が光電変換部 P D 1 の出力と光電変換部 P D 2 の出力を合成した出力（合成出力）を示している。合成出力は、光電変換部 P D 1 からの出力と光電変換部 P D 2 からの出力を加算することで得られる。合成出力を得るために、平均化、增幅等を行ってもよい。

40

#### 【0057】

なお、図 6 では、仮に、光電変換部 P D 1 の方が光電変換部 P D 2 よりも感度が高い場合、或いは、光電変換部 P D 1 に光電変換部 P D 2 よりも多くの光が入射している場合を想定している。

#### 【0058】

図 6 (a) は、光電変換部 P D 1 と光電変換部 P D 2 との間のポテンシャル障壁が高い場合の特性を示している。ここでいうポテンシャル障壁が高い場合とは、光電変換部 P D

50

1, P D 2 間のポテンシャル障壁の高さが、隣接する画素との間のポテンシャル障壁の高さ及び F D 領域 (n 型半導体領域 206A, 206B) との間のポテンシャル障壁の高さよりも高い場合である。すなわち、光電変換部 P D 1, P D 2 で飽和電荷量を超える電荷が生成された場合、この過剰な電荷は、光電変換部 P D 1, P D 2 間を移動することはなく、隣接する画素や F D 領域に流出することになる。

#### 【0059】

出力 V 1 は、光電変換部 P D 1, P D 2 の飽和電荷量に対応する出力である。画素 1 2 への入射光量が範囲 280 のとき、光電変換部 P D 1, P D 2 は飽和しておらず、光電変換部 P D 1 からの出力 (特性 272) 及び光電変換部 P D 2 からの出力 (特性 274) は、いずれも入射光量の増加に応じて増加する。範囲 280 では、光電変換部 P D 1 及び光電変換部 P D 2 の双方から適切な出力が得られるため、これらの合成出力 (特性 276) としても入射光量に応じた適切な出力が得られる。

10

#### 【0060】

画素 1 2 への入射光量が範囲 282 のとき、光電変換部 P D 2 は飽和していないが、光電変換部 P D 1 は飽和している。このため、光電変換部 P D 2 からの出力 (特性 274) は入射光量の増加に応じて増加するが、光電変換部 P D 1 からの出力は出力 V 1 で一定となる。すなわち、光電変換部 P D 1 において飽和電荷量を超えて生成された電荷は、光電変換部 P D 1 と光電変換部 P D 2 との間のポテンシャル障壁を越えて光電変換部 P D 2 に流入することはできず、隣接する画素などへ漏れ込むことになる。この結果、光電変換部 P D 1 において飽和電荷量を超えて生成された電荷は、光電変換部 P D 1 の出力と光電変換部 P D 2 の出力との合成出力には反映されず、範囲 282 における特性 276 の傾きは、範囲 280 における特性 276 の傾きよりも小さくなる。この結果、特性 276 は、直線が途中で折れ曲がった特性、いわゆる「ニー特性」をもってしまう。特性 276 がニー特性を持つてしまうと、入射光量に対する出力の線形性が悪化するため、入射光量に応じた適切な合成出力が得られなくなる。

20

#### 【0061】

つまり、光電変換部 P D 1 と光電変換部 P D 2 との間のポテンシャル障壁が高く、これらの間を電荷が移動できない場合、光電変換部 P D 1 及び光電変換部 P D 2 のうちの少なくとも一方が飽和すると、入射光量に応じた適切な合成出力が得られなくなる。

30

#### 【0062】

図 6 (b) は、光電変換部 P D 1 と光電変換部 P D 2 との間のポテンシャル障壁が低い場合の特性を示している。ここでいうポテンシャル障壁が低い場合とは、光電変換部 P D 1, P D 2 間のポテンシャル障壁の高さが、隣接する画素との間のポテンシャル障壁の高さ及び F D 領域 (n 型半導体領域 206A, 206B) との間のポテンシャル障壁の高さよりも低い場合である。すなわち、光電変換部 P D 1, P D 2 のうちの一方で飽和電荷量を超える電荷が生成された場合、この電荷は、まずは光電変換部 P D 1, P D 2 のうちの他方に流入することになる。

#### 【0063】

出力 V 1 は、光電変換部 P D 1, P D 2 のそれぞれの飽和電荷量に対応する出力である。画素 1 2 への入射光量が範囲 284 のとき、光電変換部 P D 1, P D 2 は飽和しておらず、光電変換部 P D 1 からの出力 (特性 272) 及び光電変換部 P D 2 からの出力 (特性 274) は、いずれも入射光量の増加に応じて増加する。範囲 284 では、光電変換部 P D 1 及び光電変換部 P D 2 の双方から適切な出力が得られるため、これらの合成出力 (特性 276) としても入射光量に応じた適切な出力が得られる。

40

#### 【0064】

画素 1 2 への入射光量が範囲 286 のとき、光電変換部 P D 2 は飽和していないが、光電変換部 P D 1 は飽和している。この場合、光電変換部 P D 1 において飽和電荷量を超えて生成された電荷は、光電変換部 P D 1 と光電変換部 P D 2 との間のポテンシャル障壁を乗り越えて光電変換部 P D 2 へと移動することができる。したがって、画素 1 2 の入射光量が範囲 286 のとき、光電変換部 P D 1 の出力と光電変換部 P D 2 の出力との合成出力

50

は、光電変換部 P D 1 で生成された電荷と光電変換部 P D 2 で生成された電荷とを合成した電荷量に基づくものとなる。つまり、範囲 286 においても、入射光量に応じた適切な合成出力を得ることができる。

#### 【0065】

画素 12 の入射光量が範囲 288 のとき、光電変換部 P D 1, P D 2 の両方が飽和するが、光電変換部 P D 1, P D 2 から隣接する画素などへの電荷の漏れ込みは生じていない。すなわち、光電変換部 P D 1 及び光電変換部 P D 2 の全体としては、飽和は生じていない。したがって、画素 12 の入射光量が範囲 288 のとき、光電変換部 P D 1 の出力と光電変換部 P D 2 の出力との合成出力は、光電変換部 P D 1 で生成された電荷と光電変換部 P D 2 で生成された電荷とを合成した電荷量に基づくものとなる。

10

#### 【0066】

出力 V2 は、光電変換部 P D 1, P D 2 の全体としての飽和電荷量に対応する出力である。入射光量に応じた適切な合成出力は、光電変換部 P D 1, P D 2 の全体としての飽和電荷量に対応する出力である出力 V2 に達するまで、得ることができる。

#### 【0067】

つまり、光電変換部 P D 1 と光電変換部 P D 2 との間のポテンシャル障壁が低い場合、光電変換部 P D 1, P D 2 の全体としての飽和電荷量に対応する入射光量まで、入射光量に応じた合成出力を得ることができる。

#### 【0068】

このように、光電変換部 P D 1 と光電変換部 P D 2 との間のポテンシャル障壁の高さを適切に設定することにより、広い入射光量範囲に渡ってニー特性のない良好な合成出力を得ることができる。しかしながら、光電変換部 P D 1 と光電変換部 P D 2 との間の分離を、特許文献 1 に記載されるような P N 接合分離だけで行った場合、「良好な焦点検出性能」、「ニー特性のない合成出力」、「十分な飽和電荷量」の 3 つを同時に実現することは困難であった。特に、画素サイズが数ミクロン程度と小さい場合や、裏面照射型センサの場合に、その影響は顕著であった。

20

#### 【0069】

光電変換部 P D 1 と光電変換部 P D 2 との間の分離を P N 接合分離で行う場合、光電変換部 P D 1 と光電変換部 P D 2 との間の分離部は、半導体基板 200 に不純物をイオン注入することにより形成される。半導体基板 200 に注入された不純物は、イオン注入時の原子散乱やその後の熱処理による拡散によって、深さ方向 (-z 方向) のみならず、横方向 (x, y 方向) にも広がりを持って分布する。このため、画素サイズが小さくなるほどに、画素サイズに対して光電変換部 P D 1 と光電変換部 P D 2 との間の分離部が占める割合は、相対的に大きくなる。

30

#### 【0070】

また、P N 接合分離では、光電変換部 P D 1, P D 2 間の領域のキャリア濃度を高くすることでポテンシャル障壁は高くなるが、分離部の横方向の広がりは更に大きくなり、ひいては光電変換部 P D 1, P D 2 の体積が小さくなつて飽和電荷量が小さくなる。また、光電変換部 P D 1 と光電変換部 P D 2 との間のポテンシャル障壁が高くなりすぎると、図 6 (a) を用いて説明したように、入射光量に応じた所望の合成出力を得られない可能性がある。

40

#### 【0071】

逆に、光電変換部 P D 1, P D 2 間の幅を狭めるために光電変換部 P D 1 と光電変換部 P D 2 との間の領域のキャリア濃度を低くしすぎると、ポテンシャル障壁が低くなつて光電変換部 P D 1 と光電変換部 P D 2 との間の電荷クロストークが多くなる。その結果、図 5 を用いて説明したように、焦点検出性能が悪化する。

#### 【0072】

つまり、光電変換部 P D 1, P D 2 間を P N 接合分離によって分離する場合、特に画素サイズが数ミクロン程度以下と小さいときには、「良好な焦点検出性能」、「ニー特性のない合成出力」、「十分な飽和電荷量」の 3 つを同時に実現することが困難となる。

50

## 【0073】

そこで、本実施形態による撮像装置では、1つのマイクロレンズ240を共有する1つの画素12の2つの光電変換部PD1, PD2を、ポテンシャル障壁高さの異なる2種類の分離部212, 214により分離している。

## 【0074】

分離部214は、いわゆるトレンチ分離により構成されている。分離部214による分離特性は、トレンチの幅及び深さ、トレンチに埋め込む充填材の種類等によって決定することができる。トレンチ分離からなる分離部214を設けることで、光電変換部PD1, PD2間のポテンシャル障壁の高さ1は、図3(e)に示すように非常に大きくすることができ、分離部214によって電荷の移動をほぼ完全にブロックすることが可能である。分離部214の幅は、半導体基板200に形成するトレンチの幅によって決定されるため、撮像装置の製造に用いられる露光装置の最小解像寸法程度にまで縮小することが可能である。このため、分離部214は、PN接合分離の場合と比較して、画素サイズに応じた微細化が容易である。

10

## 【0075】

分離部212は、光電変換部PD1, PD2の電荷蓄積部の信号電荷に対してポテンシャル障壁を形成する半導体領域からなる分離部であり、ポテンシャル障壁の高さ3は、分離部214のポテンシャル障壁の高さ1よりも十分に小さい。光電変換部PD1と光電変換部PD2との間の一部の領域に分離部212が設けられていることにより、電荷は、分離部214の部分は越えられないが、分離部212の部分を通って光電変換部PD1と光電変換部PD2との間を移動することができる。分離部212のポテンシャル障壁の高さ3は、分離部212の幅W3及びキャリア濃度により設計することができる。

20

## 【0076】

したがって、光電変換部PD1, PD2間に分離部212と分離部214とを設け、これらのパラメータを適宜設計することで、光電変換部PD1, PD2間の電荷の移動、すなわち電荷クロストークの度合いを制御することができる。これにより、図5(a)に示したような焦点検出に好適な入射角特性を得ることが可能となり、焦点検出性能を向上することができる。一例では、分離部212の長さT3を分離部214の長さT1以下(T3 < T1)にすることで、光電変換部PD1と光電変換部PD2との間を移動する電荷の量を適切に抑制することができる。

30

## 【0077】

分離部214は、前述の通り画素サイズに応じた微細化が可能であることから、光電変換部PD1, PD2間の領域の全体をPN接合分離で分離する場合と比較して、光電変換部PD1, PD2の体積の減少を抑制することができる。これにより、光電変換部PD1, PD2の十分な飽和電荷量を確保することができる。

## 【0078】

光電変換部PD1, PD2を囲う分離部210のポテンシャル障壁の高さ2は、分離部212のポテンシャル障壁の高さ3よりも大きくすることが望ましい。これにより、光電変換部PD1, PD2間の電荷移動を許容しつつ、隣接する画素やFD領域への電荷の漏れを防止することができる。例えば、光電変換部PD1が光電変換部PD2よりも先に飽和したとき、隣接する画素やFD領域などへ電荷が漏れる前に光電変換部PD2に電荷を移動させることができ、図6(b)に示すような入射光に対する出力特性を得ることができる。また、光電変換部PD1, PD2の全体としての飽和電荷量を増やすことも可能となる。

40

## 【0079】

以上をまとめると、分離部214のポテンシャル障壁の高さ1、分離部210のポテンシャル障壁の高さ2、分離部212のポテンシャル障壁の高さ3は、前述のように、以下の式(1)の関係となるように設定するとよい。

$$3 < 2 < 1 \quad \dots (1)$$

## 【0080】

50

本実施形態の上記構成とすることにより、「良好な焦点検出性能」、「ニー特性のない合成出力」、「十分な飽和電荷量」の3つを同時に実現することが可能となる。

【0081】

本実施形態では、 $x$   $y$  面において、 $y$  方向に沿って分離部214、分離部212、分離部214の順に並べ、分離部212を画素12の中心付近に配置している。これは、マイクロレンズ240から入射する光は、 $x$   $y$  面において、画素12の中心付近に最も集中するからである。分離部212を画素12の中心付近に配置することで、分離部214で損失する光を抑制することができ、感度を向上することができる。

【0082】

また、分離部214の幅 $W_1$ は、分離部212の幅 $W_3$ よりも小さく ( $W_1 < W_3$ ) することが望ましい。トレンチ分離からなる分離部214は分離部212と比較して微細化が容易であり、分離部214の幅 $W_1$ は分離部212の幅 $W_3$ よりも狭くすることが可能である。このようにすることで、画素サイズが小さい場合においても、分離部214の幅 $W_1$ を狭めた分、光電変換部PD1, PD2の体積を大きくすることができ、飽和電荷量を増やすことができる。

【0083】

また、分離部214の深さ $L_1$ 及び分離部212の深さ $L_3$ は、n型半導体領域204A, 204Bの深さ $P$ よりも大きく、分離部210の深さ $L_2$ よりも小さく ( $P < L_1 < L_2$ ,  $P < L_3 < L_2$ ) することが望ましい。

【0084】

このようにすることで、n型半導体領域204A, 204Bに蓄積した電子が半導体基板200の深さ方向 (- $z$  方向) のバスを介して光電変換部PD1, PD2間や隣接画素との間を移動することを抑制することができる。すなわち、n型半導体領域204A, 204Bに蓄積された電子のうち電荷クロストークする成分を更に抑制することができ、焦点検出性能を向上することができる。

【0085】

また、分離部210及び分離部212をn型半導体領域204A, 204Bとは逆導電型の半導体領域 (p型半導体領域) で形成する場合、分離部210のキャリア濃度は、分離部212のキャリア濃度の3倍以上、好ましくは10倍以上とすることが望ましい。また、分離部210の幅 $W_2$ は、分離部212の幅 $W_3$ よりも大きく ( $W_3 < W_2$ ) することが望ましい。

【0086】

このようにすることで、分離部210のポテンシャル障壁の高さ $2$ を、分離部212のポテンシャル障壁の高さ $3$ よりも大きく ( $3 < 2$ ) することができる。

【0087】

分離部210の少なくとも一部は、分離部214と同様のトレンチ分離としてもよい。このようにすることで、分離部210のポテンシャル障壁の高さ $2$ と、分離部212のポテンシャル障壁の高さ $3$ とは、ほぼ等しくなる。このときの条件は、(1)式のうち、以下の式(2)の関係となる場合である。このときには、画素12と隣接画素との間の電荷クロストークを更に抑制することができる。

$$3 < 2 = 1 \dots (2)$$

【0088】

分離部214のトレンチを埋め込む充填材は、典型的には、絶縁材料である。トレンチを絶縁材料で埋め込むことにより、分離部214のポテンシャル障壁を非常に高くすることができます。トレンチを埋め込む絶縁材料としては、特に限定されるものではないが、例えば、酸化シリコン、窒化シリコン、窒化酸化シリコン、炭化シリコン等が挙げられる。

【0089】

その他、トレンチを埋め込む絶縁材料としては、負の固定電荷を有する膜、例えば少なくとも一部が結晶化した絶縁膜が挙げられる。少なくとも一部が結晶化した絶縁膜としては、ハフニウム、ジルコニウム、アルミニウム、タンタル、チタン、イットリウム、ラン

10

20

30

40

50

タノイド等の金属酸化物であって、少なくとも一部が結晶化した領域を有する絶縁膜が挙げられる。これらの絶縁材料は、所定の温度による結晶化アニールを行うことによって膜中に負の電荷が形成される。このため、半導体基板や分離部の表面を正孔蓄積状態とさせることができ、界面準位に起因した暗電流成分を抑制することができる。したがって、トレンチ表面で発生する欠陥の影響を低減することができ、ノイズの発生を低減することができる。

#### 【0090】

分離部214のトレンチを埋め込む充填材は、半導体基板200よりも屈折率の低い材料であると更に好ましい。分離部214のトレンチ内に半導体基板200よりも屈折率の低い材料を充填することで、半導体基板200と分離部214との界面における反射を積極的に高めることができる。このようにすることで、分離部214における電荷的なクロストークだけでなく、光学的なクロストークをも抑制することができ、焦点検出性能を更に向上することができる。半導体基板200よりも屈折率の低い材料としては、半導体基板200がシリコンの場合、酸化シリコン、窒化シリコン、窒化酸化シリコン、炭化シリコン等が挙げられる。トレンチ内を中空にしても同様の効果が得られる。半導体基板200と分離部214との界面における反射を高める観点からは、充填材の少なくとも一部に金属材料を含んでもよい。

#### 【0091】

また、分離部214のトレンチを埋め込む充填材は、半導体基板200と同じ材料であってもよい。充填材を半導体基板200と同じ材料にすると、半導体基板200と分離部214との間の屈折率差をほぼゼロにすることことができ、半導体基板200を伝搬する光の形状と分離部214を伝搬する光の形状とが連続的に繋がり、光を効率よく伝搬できるようになる。これにより、半導体基板200の表面における光のモード不整合を抑制して入射光の反射を低減することができ、感度の低下を抑制することができる。半導体基板200がシリコンの場合、充填材としては、エピタキシャル成長による単結晶シリコン、多結晶シリコン或いはアモルファスシリコンを適用することができる。

#### 【0092】

また、分離部214の幅W1を $1/(4 \times n)$ 以下にすることで、感度の低下を更に抑制することができる。ここで、 $\lambda$ は、入射する光の中心波長であり、カラーフィルタを配置する場合、カラーフィルタを透過する光の中心波長である。nは、分離部214の屈折率である。分離部214の幅W1を $1/(4 \times n)$ 以下とすることで、波動光学的に入射光の波面が乱される割合を低減することができ、感度の低下を抑制することができる。

#### 【0093】

分離部214のトレンチに充填材を埋め込む際、トレンチの内壁には、酸化シリコン等の絶縁材料よりなるライナー膜を設けてもよい。トレンチの内壁に絶縁材料よりなるライナー膜を設けることで、トレンチに埋め込む絶縁材の種類によらず、分離部214として好適なポテンシャル障壁を形成することができる。

#### 【0094】

このように、本実施形態によれば、1つの画素に複数の光電変換部を含む撮像装置において、受光光量に応じた適切な画像の取得と焦点検出精度の向上とを実現することができる。

#### 【0095】

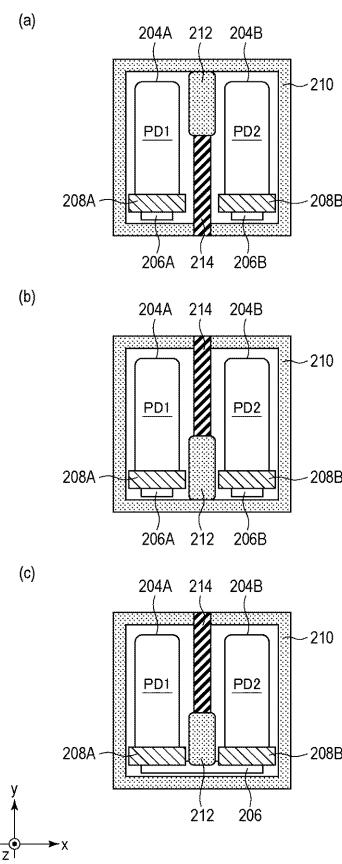

##### [第2実施形態]

本発明の第2実施形態による撮像装置について、図7を用いて説明する。図7は、本実施形態による撮像装置の画素の構成例を示す図である。図1乃至図6に示す第1実施形態による撮像装置と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

#### 【0096】

本実施形態では、第1実施形態に撮像装置の画素構成を裏面照射型の撮像装置に適用した例について説明する。

#### 【0097】

10

20

30

40

50

図7は、本実施形態による撮像装置における画素12の光電変換部PD1, PD2が設けられた部分の構造を示す図である。図7(a)は、半導体基板200を光の入射する面側(裏面側)から見た平面図である。図7(b)は、半導体基板200を光の入射する面とは反対の面側(表面側)から見た平面図である。図7(c)は、図7(a)のA-A線断面図である。図7(d)は、図7(a)のB-B線断面図である。

#### 【0098】

半導体基板200には、p型半導体領域202が設けられている。p型半導体領域202内には、光電変換部PD1の電荷蓄積部を構成するn型半導体領域204Aと、光電変換部PD2の電荷蓄積部を構成するn型半導体領域204Bとが設けられている。n型半導体領域204A, 204Bは、半導体基板200の表面側(図7(c), (d)において下側)から裏面側(図7(c), (d)において上側)に渡って配されている。n型半導体領域204A, 204Bは、例えば、半導体基板200の表面側から不純物をイオン注入することにより形成される。

10

#### 【0099】

半導体基板200の表面側には、図7(b)に示すように、n型半導体領域204Aから離間してn型半導体領域206Aが、n型半導体領域204Bから離間してn型半導体領域206Bが、それぞれ設けられている。n型半導体領域204Aとn型半導体領域206Aとの間の半導体基板200の表面上には、図示しないゲート絶縁膜を介して、転送トランジスタM1のゲート電極208Aが設けられている。また、n型半導体領域204Bとn型半導体領域206Bとの間の半導体基板200の表面上には、図示しないゲート絶縁膜を介して、転送トランジスタM2のゲート電極208Bが設けられている。

20

#### 【0100】

半導体基板200の、光電変換部PD1, PD2及び転送トランジスタM1, M2が設けられた領域の周囲には、この領域を囲うように分離部210が設けられている。分離部210は、半導体基板200の表面側から裏面側に渡って配されている。分離部210は、p型半導体領域202よりもキャリア濃度の高いp型半導体領域を含む。分離部210の少なくとも一部は、STI法等により形成した素子分離絶縁領域でもよい。

20

#### 【0101】

分離部210で囲まれた領域内の、光電変換部PD1及び転送トランジスタM1が設けられた領域と、光電変換部PD2及び転送トランジスタM2が設けられた領域との間には、分離部212及び214が設けられている。

30

#### 【0102】

分離部214は、図7(a), (d)に示すように、半導体基板200の裏面(第1の表面)側から表面(第2の表面)側に渡る領域のうちの裏面側の一部分に設けられている。分離部212は、光電変換部PD1及び転送トランジスタM1が設けられた領域と光電変換部PD1及び転送トランジスタM1が設けられた領域との間の、分離部214が設けられた部分を除く部分に設けられている。半導体基板200の裏面側において、分離部212は、画素12の中心付近に配置されており、分離部214は、y方向に沿って分離部212を挟むように、分離部212の両端部に配置されている。すなわち、光の入射する面側から見た分離部210, 212, 214の配置は、第1実施形態による撮像装置と同じであると言える。

40

#### 【0103】

分離部214は、第1実施形態による撮像装置の場合と同様、トレンチ分離により構成される。分離部212も、第1実施形態による撮像装置の場合と同様、光電変換部PD1, PD2の電荷蓄積部(n型半導体領域204A, 204B)に対してポテンシャル障壁を形成する半導体領域により構成される。

#### 【0104】

分離部212は、例えば、半導体基板200の表面側から不純物をイオン注入することにより形成される。分離部212は、図7(c)に示すA-A線断面では、半導体基板200の表面側から裏面側まで配置され、図7(d)に示すB-B線断面では、半導体

50

基板 200 の表面側から分離部 214 の上まで配置されている。分離部 212 は、半導体基板 200 の裏面側から不純物をイオン注入することにより形成してもよい。

【0105】

裏面照射型の撮像装置では、配線層 232 やゲート電極 208A, 208B は半導体基板 200 の表面側に形成され、マイクロレンズ 240 は半導体基板 200 の裏面側に配置され、半導体基板 200 の裏面側から光が入射する構成となる。

【0106】

図 7 (e) は、半導体基板 200 の裏面から深さ  $L_1$  の間の領域における最小のポテンシャル障壁の高さを A - A 線断面に沿って繋ぐことにより描いたポテンシャル分布図である。図 7 (f) は、半導体基板 200 の表面から深さ  $L_1$  の間の領域における最小のポテンシャル障壁の高さを B - B 線断面に沿って繋ぐことにより描いたポテンシャル分布図である。

10

【0107】

分離部 214, 210, 212 の信号電荷（電子）に対するポテンシャル障壁の高さをそれぞれ 1, 2, 3 とすると、ポテンシャル障壁の高さ 1, 2, 3 は、第 1 実施形態の場合と同様、以下の関係を有している。

$$3 < 2 < 1$$

【0108】

半導体基板 200 の裏面側における分離部 214 の y 方向の長さの合計の長さを  $T_1$ 、

x 方向の幅を  $W_1$ 、分離部 212 の y 方向の長さを  $T_3$ 、x 方向の幅を  $W_3$ 、分離部 210 の x 方向の幅を  $W_2$  とする。この場合において、長さ  $T_1$ ,  $T_3$  及び幅  $W_1$ ,  $W_2$ ,  $W_3$  は、第 1 実施形態の場合と同様、以下の関係にあることが望ましい。

20

$$T_3 > T_1, W_3 > W_1, W_3 > W_2$$

【0109】

光電変換部 PD1, PD2 間の分離を PN 接合分離だけで行う場合、第 1 実施形態で説明した理由と同様の理由により、「良好な焦点検出性能」、「二一特性のない合成出力」、「十分な飽和電荷量」の 3 つを同時に実現することが困難となる。特に、裏面照射型の撮像装置の場合、半導体基板 200 の表面側から不純物をイオン注入することにより光電変換部 PD1, PD2 間に分離部 212 を形成するため、裏面側における不純物の横方向への広がりはより大きくなる。光電変換部 PD1, PD2 間のキャリア濃度を高くするとポテンシャル障壁が高くなるが、横方向の広がりが更に大きくなつて光電変換部 PD1, PD2 の体積が小さくなり、ひいては飽和電荷量が小さくなる。また、光電変換部 PD1, PD2 間のポテンシャル障壁が高くなりすぎると、第 1 実施形態で説明したように、合成出力に二一特性が表れる可能性がある。反対に、光電変換部 PD1, PD2 間のキャリア濃度を低くしすぎると、第 1 実施形態で説明したように、ポテンシャル障壁が低くなり焦点検出性能を悪化させる可能性がある。

30

【0110】

本実施形態の構成のように、半導体基板 200 の裏面側において分離部 212 と分離部 214 とによって光電変換部 PD1, PD2 間を分離することにより、上記課題を解決することができる。すなわち、分離部 214 を設けることで、分離部 214 のポテンシャル障壁の高さ 1 は非常に大きくなり、分離部 214 はほぼ完全に電荷の移動をブロックする（図 7 (f) 参照）。半導体基板 200 の裏面側に分離部 214 に隙間を設けることにより、ポテンシャル障壁の高さ 3 は低くなり（図 7 (e) 参照）、電荷はこの隙間を通つて光電変換部 PD1, PD2 間を移動することができる。この隙間、すなわち分離部 212 のポテンシャル障壁の高さ 3 は、分離部 212 の間隔  $T_3$ 、幅  $W_3$ 、キャリア濃度により設計することができる。これにより、式（1）の関係を満たし、「良好な焦点検出性能」、「二一特性のない合成出力」、「十分な飽和電荷量」の 3 つを同時に実現することが可能となる。

40

【0111】

このように、本実施形態によれば、複数の光電変換部を有する画素を有する裏面照射型

50

の撮像装置においても、受光光量に応じた適切な画像の取得と焦点検出精度の向上とを実現することができる。

【0112】

[第3実施形態]

本発明の第3実施形態による撮像装置について、図8を用いて説明する。図8は、本実施形態による撮像装置の画素の構成例を示す図である。図1乃至図7に示す第1及び第2実施形態による撮像装置と同様の構成要素には同一の符号を付し、説明を省略し或いは簡潔にする。

【0113】

図8は、本実施形態による撮像装置における画素12の光電変換部PD1, PD2が設けられた部分の構造を示す図である。図8(a)は、光電変換部PD1, PD2を光の入射方向から見た平面図である。図8(b)は、図7(a)のB-B線断面図である。図8(c)は、半導体基板200の表面から深さL1の間の領域における最小のポテンシャル障壁の高さをB-B線断面に沿って繋ぐことにより描いたポテンシャル分布図である。

10

【0114】

本実施形態による撮像装置は、図8に示すように、分離部214の周囲にp型半導体領域216を更に有するほかは、第1実施形態による撮像装置と同様である。このp型半導体領域216は、光電変換部PD1, PD2の電荷蓄積部(n型半導体領域204A, 204B)とは逆の導電型の半導体領域である。光電変換部PD1, PD2の電荷蓄積部がp型半導体領域の場合には、n型半導体領域となる。

20

【0115】

分離部214の周囲にp型半導体領域216を設けることにより、半導体基板200にトレンチを掘ることで形成した分離部214の境界付近で発生するノイズを低減することができる。

【0116】

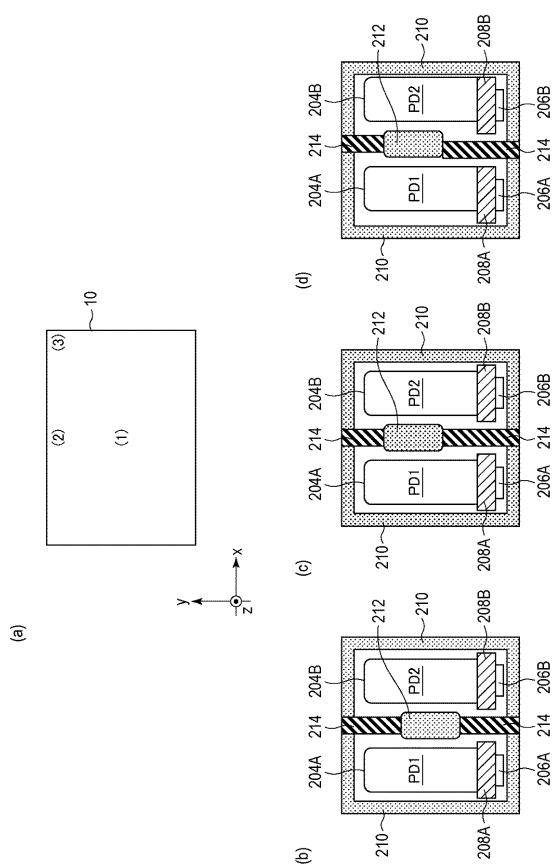

[第4実施形態]

本発明の第4実施形態による撮像装置について、図9を用いて説明する。図9は、本実施形態による撮像装置の画素の構成例を示す図である。図1乃至図8に示す第1乃至第3実施形態による撮像装置と同様の構成要素には同一の符号を付し、説明を省略し或いは簡潔にする。

30

【0117】

第1実施形態による撮像装置では、分離部214は、y方向に沿って分離部212を挟むように、分離部212の両端部に配置することで、画素12の中心付近に配置していたが、分離部214の配置は、これに限定されるものではない。分離部214は、画素12の中心部に配置することが好ましい一態様ではあるが、光電変換部PD1と光電変換部PD2との間における電荷の移動を許容する観点からは、少なくとも一部の領域が光電変換部PD1と光電変換部PD2との間に位置していればよい。

【0118】

したがって、例えば図9(a)及び図9(b)に示すように、必ずしも分離部214の両端部に分離部212を配置する必要はない。図9(a)は、分離部214をゲート電極208A, 208B側に配置した例である。図9(b)は、分離部212をゲート電極208A, 208B側に配置した例である。

40

【0119】

また、例えば図9(c)に示すように、図9(b)の配置において、分離部214と分離部210との間に隙間を設けてよい。この場合、n型半導体領域206Aとn型半導体領域206Bとをこの隙間で接続して1つのn型半導体領域206としてもよい。

【0120】

図9(b)のように浮遊拡散領域FDが2つのn型半導体領域206A, 206Bを含む場合、これらに接続される配線を設けるには2つのコンタクトプラグが必要である。こ

50

れに対し、図9(c)のように浮遊拡散領域FDが1つのn型半導体領域206を含む場合、コンタクトプラグは1つでよい。したがって、コンタクトプラグとの間で生じる容量を削減することができ、ノイズを低減することができる。

#### 【0121】

図9(a)の配置において、分離部212と分離部210との間に隙間を設け、n型半導体領域206Aとn型半導体領域206Bとをこの隙間で接続し、1つのn型半導体領域206としてもよい。

#### 【0122】

##### [第5実施形態]

本発明の第5実施形態による撮像装置について、図10を用いて説明する。図10は、本実施形態による撮像装置の画素の構成例を示す図である。図1乃至図9に示す第1乃至第4実施形態による撮像装置と同様の構成要素には同一の符号を付し、説明を省略し或いは簡潔にする。

#### 【0123】

第1実施形態による撮像装置では、マイクロレンズ240から入射する光が最も集中する場所に分離部214を配置する観点から、分離部214を画素12の中心付近に配置する例を示した。しかしながら、画素12に入射する光の入射角(主光線角度)は、画素領域10内における画素12の位置によって異なってくる。したがって、上記観点に基づいて分離部214を配置する場合、画素12内の分離部214を配置する場所は、画素領域10内における画素12の位置に応じて変えることが望ましい。本実施形態では、画素内における分離部212の配置場所を、その画素12が画素領域10内において位置する場所に応じて定める例を示す。

#### 【0124】

画素12に入射する光が最も集中する場所は、画素アレイとマイクロレンズアレイのサイズの関係などにもよるが、一例では、画素領域10の中心部から遠い画素12ほど、その画素12が画素領域10の中心部に対して位置する方向にシフトする。このような場合、分離部212は、画素領域10における画素12の場所に応じて、例えば図10に示すように配置することができる。

#### 【0125】

ここで、図10(a)に示すように、画素領域10内の場所(1),(2),(3)に着目する。場所(1)は、画素領域10の中心付近である。場所(2)は、画素領域10の中心に対して+y方向に位置する周辺付近(上辺中央付近)である。場所(3)は、画素領域10の中心に対して+x方向、+y方向に位置する角部付近(右上角部付近)である。このとき、場所(1),(2),(3)の画素12は、それぞれ、図10(b),(c),(d)に示すようなレイアウトとすることができます。

#### 【0126】

画素領域10の中心付近(場所(1))では、図10(b)に示すように、第1実施形態の場合と同様、分離部212は、画素12の中心付近に配置する。画素領域10の中心から周辺付近に近づくにつれ、徐々に分離部212の位置をずらして配置する。画素領域10の上辺中央付近(場所(2))では、図10(c)に示すように、分離部212を、場所(1)における画素12内の位置よりも+y方向にシフトして配置する。画素領域10の右上角部付近(場所(3))では、図10(d)に示すように、分離部212を、場所(2)における画素12内の位置よりも+x方向にシフトして配置する。分離部212の移動に応じて、分離部214、光電変換部PD1,PD2、転送トランジスタM1,M2等の配置場所を移動するようにしてもよい(図10(d)参照)。

#### 【0127】

このようにして、分離部214の配置場所に光が集中するようにすることで、特に画素領域10の周辺部における感度低下を抑制することができる。

#### 【0128】

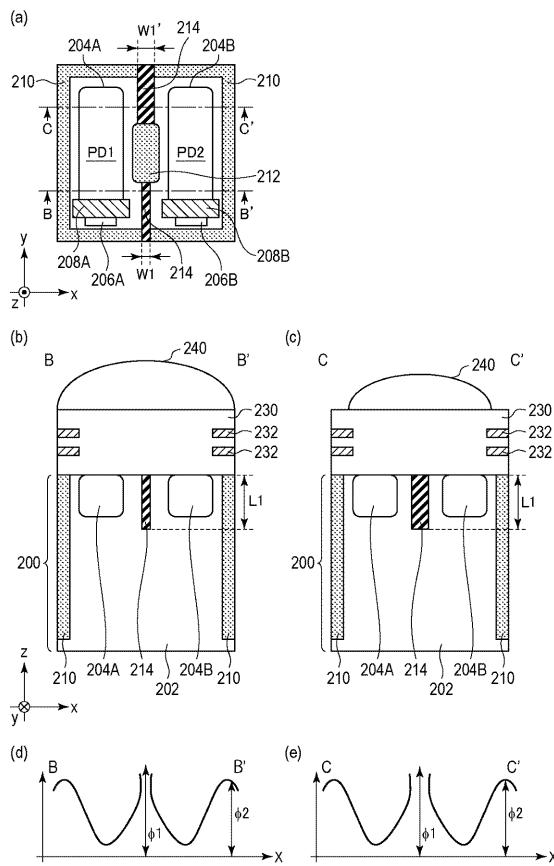

##### [第6実施形態]

10

20

30

40

50

本発明の第6実施形態による撮像装置について、図11を用いて説明する。図1乃至図10に示す第1乃至第5実施形態による撮像装置と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

【0129】

図11は、本実施形態による撮像装置の構成例を示す図である。図11(a)は、光電変換部PD1, PD2を光の入射方向から見た平面図である。図11(b)は、図11(a)のB-B線断面図である。図11(c)は、図11(a)のC-C線断面図である。図11(d)は、半導体基板200の裏面から深さL1の間の領域における最小のポテンシャル障壁の高さをB-B線断面に沿って繋ぐことにより描いたポテンシャル分布図である。図11(e)は、半導体基板200の表面から深さL1の間の領域における最小のポテンシャル障壁の高さをC-C線断面に沿って繋ぐことにより描いたポテンシャル分布図である。

10

【0130】

本実施形態による撮像装置は、分離部214の幅が場所によって異なっているほかは、第1実施形態による撮像装置と同様である。すなわち、本実施形態による撮像装置では、分離部212を挟む2つの分離部214の幅が、互いに異なっている。これら2つのうち、ゲート電極208A, 208Bに近い側に配置された分離部214の幅をW1、ゲート電極208A, 208Bから遠い側に配置された分離部214の幅をW1'とするとき、幅W1が幅W1'よりも狭くなっている。

20

【0131】

分離部214の幅W1を幅W1'よりも狭くすることで、ゲート電極208A, 208Bのx方向の幅、並びに、浮遊拡散領域FD(n型半導体領域206A, 206B)のx方向の幅を大きくすることができる。これにより、電荷の転送路の幅が広がり設計の自由度を上げることができ、光電変換部PD1, PD2の飽和電荷量を更に増加しつつ、転送特性をも向上することができる。トレンチ分離からなる分離部214は、幅を狭めても十分な分離特性を得られることから、第1実施形態の場合と同様、光電変換部PD1, PD2間を明確に分離することができる。したがって、第1実施形態で説明した理由により、「良好な焦点検出性能」、「ニー特性のない合成出力」、「十分な飽和電荷量」の3つを同時に実現するとも可能となる。

30

【0132】

なお、本実施形態では、幅W1が幅W1'よりも狭くなるようにしたが、幅W1'が幅W1よりも狭くなる構成としてもよい。

【0133】

[第7実施形態]

本発明の第7実施形態による撮像装置について、図12を用いて説明する。図1乃至図11に示す第1乃至第6実施形態による撮像装置と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

【0134】

図12は、本実施形態による撮像装置の光電変換部PD1, PD2を光の入射方向から見た平面図である。

40

【0135】

本実施形態による撮像装置は、分離部214の幅が途中から変化しているほかは、第1実施形態による撮像装置と同様である。すなわち、本実施形態による撮像装置では、分離部214の幅が、分離部212に近い部分と分離部212から遠い部分とで異なっている。分離部212に近い部分の分離部214の幅を幅W1、分離部212から遠い部分の分離部214の幅をW1'とするとき、幅W1'が幅W1よりも狭くなっている。分離部214の幅が途中から変化する構成とすることで、分離部214のポテンシャル形状を調整し、ポテンシャル障壁の高さW3を調整することができる。

【0136】

図12では、W1 < W1'となるように、分離部214の幅を、分離部212との境界

50

付近へ向かって徐々に幅が狭くなる構成としているが、W1 > W1となるように徐々に幅が広がるようにしてもよい。

【0137】

[第8実施形態]

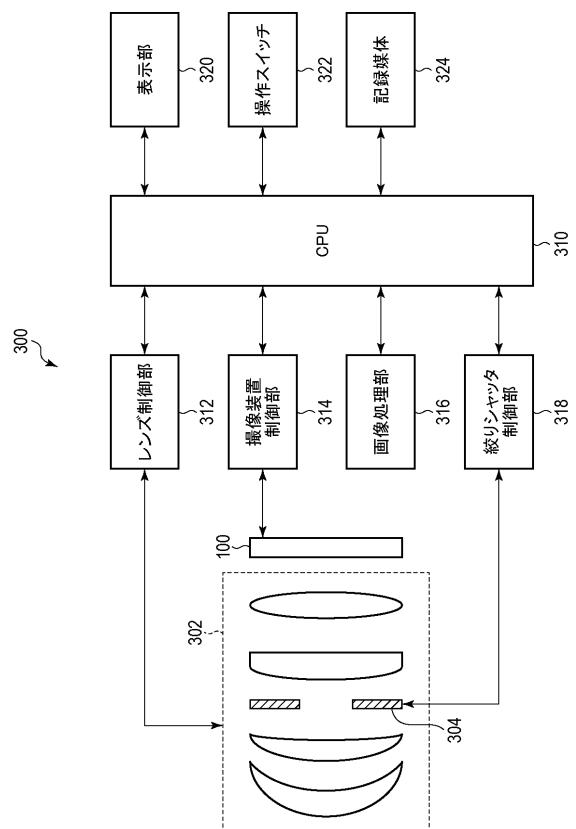

本発明の第8実施形態による撮像システムについて、図13を用いて説明する。図13は、本実施形態による撮像システムの概略構成を示すブロック図である。図1乃至図12に示す撮像装置と同様の構成要素には同一の符号を付し説明を省略し或いは簡潔にする。

【0138】

上記第1乃至第7実施形態で述べた撮像装置100は、種々の撮像システムに適用可能である。適用可能な撮像システムとしては、特に限定されるものではないが、例えば、デジタルスチルカメラ、デジタルカムコーダ、監視カメラ、複写機、ファックス、携帯電話、車載カメラ、観測衛星などが挙げられる。また、レンズなどの光学系と撮像装置とを備えるカメラモジュールも、撮像システムに含まれる。図13にはこれらのうちの一例として、デジタルスチルカメラのブロック図を例示している。

10

【0139】

撮像システム300は、図13に示すように、撮像光学系302、CPU310、レンズ制御部312、撮像装置制御部314、画像処理部316、絞りシャッタ制御部318、表示部320、操作スイッチ322、記録媒体324を備える。

20

【0140】

撮像光学系302は、被写体の光学像を形成するための光学系であり、レンズ群、絞り304等を含む。絞り304は、その開口径を調節することで撮影時の光量調節を行なう機能を備えるほか、静止画撮影時には露光秒時調節用シャッタとしての機能も備える。レンズ群及び絞り304は、光軸方向に沿って進退可能に保持されており、これらの運動した動作によって変倍機能（ズーム機能）や焦点調節機能を実現する。撮像光学系302は、撮像システムに一体化されていてもよいし、撮像システムへの装着が可能な撮像レンズでもよい。

20

【0141】

撮像光学系302の像空間には、その撮像面が位置するように撮像装置100が配置されている。撮像装置100は、第1乃至第7実施形態で説明した撮像装置100であり、CMOSセンサ（画素領域10）とその周辺回路（周辺回路領域）とを含んで構成される。撮像装置100は、複数の光電変換部を有する画素が2次元配置され、これらの画素に對してカラーフィルタが配置されることで、2次元単板カラーセンサを構成している。撮像装置100は、撮像光学系302により結像された被写体像を光電変換し、画像信号や焦点検出信号として出力する。

30

【0142】

レンズ制御部312は、撮像光学系302のレンズ群の進退駆動を制御して変倍操作や焦点調節を行うためのものであり、その機能を実現するように構成された回路や処理装置により構成されている。絞りシャッタ制御部318は、絞り304の開口径を変化して（絞り値を可変として）撮影光量を調節するためのものであり、その機能を実現するように構成された回路や処理装置により構成される。

40

【0143】

CPU310は、カメラ本体の種々の制御を司るカメラ内の制御装置であり、演算部、ROM、RAM、A/Dコンバータ、D/Aコンバータ、通信インターフェイス回路等を含む。CPU310は、ROM等に記憶されたコンピュータプログラムに従ってカメラ内の各部の動作を制御し、撮像光学系302の焦点状態の検出（焦点検出）を含むAF、撮像、画像処理、記録等の一連の撮影動作を実行する。CPU310は、信号処理部でもある。

【0144】

撮像装置制御部314は、撮像装置100の動作を制御するとともに、撮像装置100から出力された信号をA/D変換してCPU310に送信するためのものであり、それら

50

機能を実現するように構成された回路や制御装置により構成される。A / D 変換機能は、撮像装置 100 が備えていてもかまわない。画像処理部 316 は、A / D 変換された信号に対して 変換やカラー補間等の画像処理を行って画像信号を生成するためのものであり、その機能を実現するように構成された回路や制御装置により構成される。表示部 320 は、液晶表示装置 (LCD) 等の表示装置であり、カメラの撮影モードに関する情報、撮影前のプレビュー画像、撮影後の確認用画像、焦点検出時の合焦状態等を表示する。操作スイッチ 322 は、電源スイッチ、レリーズ (撮影トリガ) スイッチ、ズーム操作スイッチ、撮影モード選択スイッチ等で構成される。記録媒体 324 は、撮影済み画像等を記録するためのものであり、撮像システムに内蔵されたものでもよいし、メモリカード等の着脱可能なものでもよい。

10

#### 【0145】

このようにして、第 1 乃至第 7 実施形態による撮像装置 100 を適用した撮像システム 300 を構成することにより、高精度の焦点調節が可能であり高精細な画像を取得しうる高性能の撮像システムを実現することができる。

#### 【0146】

##### [変形実施形態]

本発明は、上記実施形態に限らず種々の変形が可能である。

例えば、上記第 1 及び第 2 実施形態では、分離部 214, 210, 212 の信号電荷に対するポテンシャル障壁の高さをそれぞれ 1, 2, 3 として、これらが  $3 < 2 < 1$  の関係を有することが望ましいことを示した。しかしながら、例えば隣接する画素との間隔が十分にある場合など、隣接する画素への電荷の流出を無視できるような場合には、分離部 214 のポテンシャル障壁の高さ 1 と分離部 212 のポテンシャル障壁の高さ 3 の関係だけを考慮するようにしてもよい。この場合、 $3 < 1$  となる。

20

#### 【0147】

また、図 2 に示した画素回路は一例であり、これに限定されるものではない。例えば、図 2 の画素回路では、2 つの光電変換部 PD1, PD2 で読み出し回路部 (リセットトランジスタ M3、増幅トランジスタ M4、選択トランジスタ M5) を共有しているが、それに対応して読み出し回路部を設けてもよい。

#### 【0148】

また、上記実施形態では、第 1 実施形態による撮像装置の変形例を第 3 乃至第 7 実施形態において説明したが、これら実施形態で説明した付加的な構成は、第 2 実施形態による撮像装置に適用することもできる。また、第 3 乃至第 7 実施形態で説明した付加的構成は、2 以上のものを任意に組み合わせることも可能である。

30

#### 【0149】

また、第 8 実施形態に示した撮像システムは、本発明の撮像装置を適用しうる撮像システムの一例を示したものであり、本発明の撮像装置を適用可能な撮像システムは図 13 に示した構成に限定されるものではない。

#### 【0150】

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

40

#### 【符号の説明】

#### 【0151】

10 ... 画素領域

12 ... 画素

14 ... 制御信号線

16A, 16B ... 垂直信号線

20 ... 垂直走査回路

30A, 30B ... 読み出し回路

50

4 0 A , 4 0 B ... 水平走查回路

50A, 50B...出力アンプ

60...制御回路

1 0 0 ... 摄像装置

## 2 0 0 ... 半導体基板

202, 216 ... p型半導体領域

2 0 4 A , 2 0 4 B , 2 0 6 A ,

2 1 0 , 2 1 2 , 2 1 4

【 四 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

## フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

G 0 2 B 7/34

(72)発明者 乾 文洋

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 曽田 岳彦

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 沖田 彰

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

F ターム(参考) 2H011 BA23 BA33 BB02

2H151 BA06 CB09 CB22 CB26 CE24 CE33

4M118 AA02 AA10 AB01 AB03 BA14 CA04 CA22 CB13 DD04 FA06

FA26 FA27 FA28 GA02 GA08 GC07 GD03 GD04

5C024 CY47 EX12 EX43 GX14

5F032 AA13 AA35 AA44 AA45 AA46 AA47 AA54 AB02 BA02 BA03

CA15 CA17 CA21 DA12 DA43