(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-111373

(P2009-111373A)

(43) 公開日 平成21年5月21日(2009.5.21)

| (51) Int.Cl.            | F 1           | テーマコード (参考) |

|-------------------------|---------------|-------------|

| HO 1 L 21/02 (2006.01)  | HO 1 L 27/12  | B 5 F 1 1 O |

| HO 1 L 27/12 (2006.01)  | HO 1 L 21/265 | Q 5 F 1 5 2 |

| HO 1 L 21/265 (2006.01) | HO 1 L 21/20  |             |

| HO 1 L 21/20 (2006.01)  | HO 1 L 29/78  | 6 2 6 C     |

| HO 1 L 29/786 (2006.01) | HO 1 L 29/78  | 6 2 7 D     |

審査請求 未請求 請求項の数 13 O L (全 26 頁) 最終頁に続く

|              |                              |          |                                                |

|--------------|------------------------------|----------|------------------------------------------------|

| (21) 出願番号    | 特願2008-261507 (P2008-261507) | (71) 出願人 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成20年10月8日 (2008.10.8)       | (72) 発明者 | 大沼 英人<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (31) 優先権主張番号 | 特願2007-264983 (P2007-264983) | (72) 発明者 | 新宮 崇史<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (32) 優先日     | 平成19年10月10日 (2007.10.10)     | (72) 発明者 | 掛端 哲弥<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (33) 優先権主張国  | 日本国 (JP)                     | (72) 発明者 | 栗城 和貴<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

|              |                              |          | 最終頁に続く                                         |

(54) 【発明の名称】 SOI 基板の作製方法

## (57) 【要約】

【課題】ガラス基板など耐熱温度が低い基板を用いた場合にも、実用に耐えうる半導体層を備えたSOI基板の製造方法を提供することを目的のとする。

【解決手段】表面に接合層が形成され、所定の深さに剥離層が形成された半導体基板と、歪点が700以下のベース基板とを用意し、半導体基板の表面とベース基板の表面とを対向させ、接合層の表面とベース基板とを接合し、加熱処理を行うことにより接合層を境として半導体基板の一部を分離させ、ベース基板上に単結晶半導体層を形成する工程を含み、ベース基板として、少なくとも加熱処理の前後において等方的に収縮する基板を用いる。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

表面に接合層が形成され、所定の深さに剥離層が形成された半導体基板と、歪点が 700 以下のベース基板とを用意し、

前記半導体基板の表面と前記ベース基板の表面とを対向させ、前記接合層の表面と前記ベース基板とを接合し、

熱処理を行うことにより前記接合層を境として前記半導体基板の一部を分離させ、前記ベース基板上に単結晶半導体層を形成する工程を含み、

前記ベース基板として、前記熱処理により等方的に収縮する基板を用いることを特徴とする SOI 基板の作製方法。

**【請求項 2】**

表面に絶縁層が形成され、前記絶縁層上に接合層が形成され、所定の深さに剥離層が形成された半導体基板と、歪点が 700 以下のベース基板とを用意し、

前記半導体基板の表面と前記ベース基板の表面とを対向させ、前記接合層の表面と前記ベース基板とを接合し、

熱処理を行うことにより前記接合層を境として前記半導体基板の一部を分離させ、前記ベース基板上に単結晶半導体層を形成する工程を含み、

前記ベース基板として、前記熱処理により等方的に収縮する基板を用いることを特徴とする SOI 基板の作製方法。

**【請求項 3】**

請求項 2 において、

前記絶縁層として、有機シランガスを用いて化学気相成長法により形成される酸化シリコン膜を用いることを特徴とする SOI 基板の作製方法。

**【請求項 4】**

請求項 1 乃至請求項 3 のいずれか一項において、

前記接合層として、窒素含有層を用いることを特徴とする SOI 基板の作製方法。

**【請求項 5】**

表面に接合層が形成され、所定の深さに剥離層が形成された半導体基板と、表面に絶縁層が形成され歪点が 700 以下のベース基板とを用意し、

前記半導体基板の表面と前記ベース基板の表面とを対向させ、前記接合層の表面と前記絶縁層の表面とを接合し、

熱処理を行うことにより前記接合層を境として前記半導体基板の一部を分離させ、前記ベース基板上に単結晶半導体層を形成する工程を含み、

前記ベース基板として、前記熱処理により等方的に収縮する基板を用いることを特徴とする SOI 基板の作製方法。

**【請求項 6】**

請求項 5 において、

前記接合層として、有機シランガスを用いて化学気相成長法により形成される酸化シリコン膜を用い、

前記絶縁層として、窒素含有層を用いることを特徴とする SOI 基板の作製方法。

**【請求項 7】**

請求項 1 乃至請求項 6 のいずれか一項において、

前記熱処理を、400 以上 700 以下で行うことと特徴とする SOI 基板の作製方法。

**【請求項 8】**

請求項 1 乃至請求項 7 のいずれか一項において、

前記ベース基板として、前記半導体基板と熱膨張係数が同等又は前記半導体基板より熱膨張係数が大きい基板を用いることを特徴とする SOI 基板の作製方法。

**【請求項 9】**

請求項 8 において、

10

20

30

40

50

前記ベース基板の熱膨張係数を、前記半導体基板の熱膨張係数の0.85倍～2.0倍とすることを特徴とするSOI基板の作製方法。

【請求項10】

請求項8において、

前記半導体基板としてシリコン基板を用い、

前記ベース基板として熱膨張係数が、 $2.3 \times 10^{-6} \sim 5.0 \times 10^{-6}$  / である基板を用いることを特徴とするSOI基板の作製方法。

【請求項11】

請求項1乃至請求項10のいずれか一項において、

前記ベース基板として、ガラス基板を用いることを特徴とするSOI基板の作製方法。

10

【請求項12】

請求項11において、

前記ガラス基板として、表面が研磨されたものを用いることを特徴とするSOI基板の作製方法。

【請求項13】

請求項11又は請求項12において、

前記ガラス基板として、表面粗さが0.3nm以下のものを用いることを特徴とするSOI基板の作製方法。

【発明の詳細な説明】

20

【技術分野】

【0001】

本発明は、SOI(Silicon on Insulator)基板に関する。また、SOI基板を用いて製造される半導体装置に関する。

【背景技術】

【0002】

近年、バルク状のシリコンウェハに代わり、絶縁表面に薄い単結晶半導体層が存在するSOI基板を使った集積回路が開発されている。SOI基板を使うことで、トランジスタのドレインと基板間ににおける寄生容量が低減されるため、SOI基板は半導体集積回路の性能を向上させるものとして注目されている。

【0003】

30

SOI基板を製造する方法の1つに、スマートカット法が知られている(例えば、特許文献1参照)。スマートカット法によるSOI基板の作製方法の概要を以下に説明する。まず、シリコンウェハにイオン注入法を用いて水素イオンを注入することによって表面から所定の深さにイオン注入層を形成する。次に、酸化シリコン膜を介して、水素イオンを注入したシリコンウェハを別のシリコンウェハに接合させる。その後、加熱処理を行うことで、イオン注入層が劈開面となり、水素イオンを注入したウェハが薄膜状に剥離し、接合させたシリコンウェハ上にシリコン膜を形成することができる。スマートカット法は水素イオン注入剥離法と呼ぶこともある。

【0004】

一方、このようなスマートカット法を用いて単結晶シリコン薄膜をガラス基板上に形成する技術の一例として、本出願人によるものが知られている(例えば、特許文献2参照)。

40

【特許文献1】特開2000-124092号公報

【特許文献2】特開平11-163363号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ガラス基板はシリコンウェハよりも大面積でかつ安価な基板であり、主に、液晶表示装置の製造に用いられている。ガラス基板をベース基板に用いることで、大面積で安価なSOI基板を作製することが可能になる。しかし、基板コストを下げるために液晶パネルなどで使われる耐熱性が低いガラス基板に単結晶シリコンを接合させてSOI基板を形成する

50

場合、熱処理前後においてガラス基板が収縮してしまうという問題が生じる。特に、特定の方向にガラス基板が収縮すると、ベース基板上に形成される単結晶シリコン層に歪みが生じることにより貼り合わせ不良が発生し、当該単結晶シリコン層でトランジスタを作製しても、十分な特性が得られないおそれがある。

#### 【0006】

上述した問題に鑑み、本発明は、SOI基板において、ベース基板としてガラス基板等の耐熱温度が低い基板を用いる場合であっても、当該ベース基板の収縮により生じる貼り合わせ不良等の影響を低減することを目的の一とする。

#### 【課題を解決するための手段】

#### 【0007】

本発明は、ベース基板と単結晶半導体基板を貼り合わせた後、単結晶半導体基板を分離してベース基板上に単結晶半導体層を形成するSOI基板の作製方法において、ベース基板として熱処理前後において等方的に収縮する基板を用いるものである。

#### 【0008】

本発明のSOI基板の作製方法の一は、表面に接合層が形成され、所定の深さに剥離層が形成された半導体基板と、歪点が700以下のベース基板とを用意し、半導体基板の表面とベース基板の表面とを対向させ、接合層の表面とベース基板とを接合し、熱処理を行うことにより剥離層を境として半導体基板の一部を分離させ、ベース基板上に単結晶半導体層を形成する工程を含み、ベース基板として、少なくとも熱処理により等方的に収縮する基板を用いる。なお、本明細書において、収縮とは熱処理前後により基板が縮むことをいう。また、等方的に収縮するとは、ベース基板の表面と平行な面においてそれぞれ特定の方位における収縮率が同程度であることをいう。好ましくは、ベース基板の表面と平行な面においてそれぞれの特定の方位における収縮率が平均値（それぞれ特定の方位の収縮率を平均した値）から10%以内であることをいう。

#### 【0009】

また、本発明のSOI基板の作製方法の一は、表面に絶縁層が形成され、絶縁層上に接合層が形成され、所定の深さに剥離層が形成された半導体基板と、歪点が700以下のベース基板とを用意し、半導体基板の表面とベース基板の表面とを対向させ、接合層の表面とベース基板とを接合し、熱処理を行うことにより剥離層を境として半導体基板の一部を分離させ、ベース基板上に単結晶半導体層を形成する工程を含み、ベース基板として、少なくとも熱処理により等方的に収縮する基板を用いる。

#### 【0010】

また、本発明のSOI基板の作製方法の一は、上記構成において、絶縁層として、有機シランガスを用いて化学気相成長法により形成される酸化シリコン膜を用いる。また、接合層として、窒素含有層を用いる。

#### 【0011】

また、本発明のSOI基板の作製方法の一は、表面に接合層が形成され、所定の深さに剥離層が形成された半導体基板と、表面に絶縁層が形成され歪点が700以下のベース基板とを用意し、半導体基板の表面とベース基板の表面とを対向させ、接合層の表面と絶縁層の表面とを接合し、加熱処理を行うことにより剥離層を境として半導体基板の一部を分離させ、ベース基板上に単結晶半導体層を形成する工程を含み、ベース基板として、熱処理により等方的に収縮する基板を用いる。この場合において、接合層として、有機シランガスを用いて化学気相成長法により形成される酸化シリコン膜を用い、絶縁層として、窒素含有層を用いることができる。

#### 【0012】

また、本発明のSOI基板の作製方法の一は、上記構成において、加熱処理を、400以上700以下で行うことを行っている。

#### 【0013】

また、本発明のSOI基板の作製方法の一は、上記構成において、ベース基板として、半導体基板と熱膨張係数が同等又は半導体基板より熱膨張係数が大きい基板を用いることを

10

20

30

40

50

特徴としている。例えば、ベース基板の熱膨張係数を、半導体基板の熱膨張係数の0.85倍～2倍とすることができる。この場合、半導体基板としてシリコン基板を用い、ベース基板として熱膨張係数が、 $2.3 \times 10^{-6}$ ～ $5.0 \times 10^{-6}$ /である基板を用いることができる。なお、熱膨張率係数とは、温度の上昇によって物体の長さ、体積が膨張する割合を1K( )当たりで示したものである。

【0014】

また、本発明のSOI基板の作製方法の一は、上記構成において、ベース基板として、ガラス基板を用いることを特徴としている。ガラス基板としては、表面粗さ( $R_a$ )が0.3nm以下のものを用いることが好ましい。また、表面が研磨されたガラス基板をベース基板として適用してもよい。

10

【0015】

また、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路及び電子機器は全て半導体装置に含まれる。

【0016】

また、本明細書中において表示装置とは、発光装置や液晶表示装置を含む。発光装置は発光素子を含み、液晶表示装置は液晶素子を含む。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機EL(Electro-Luminescence)、有機EL等が含まれる。

【発明の効果】

【0017】

本発明により、SOI基板において、ベース基板としてガラス基板など耐熱温度が低い基板を用いた場合であっても、当該ベース基板の収縮により生じる貼り合わせ不良等の影響を低減することができる。

20

【発明を実施するための最良の形態】

【0018】

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態および詳細を変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

30

【0019】

(実施の形態1)

本実施の形態では、SOI基板の作製方法の一例に関して図面を参照して説明する。

【0020】

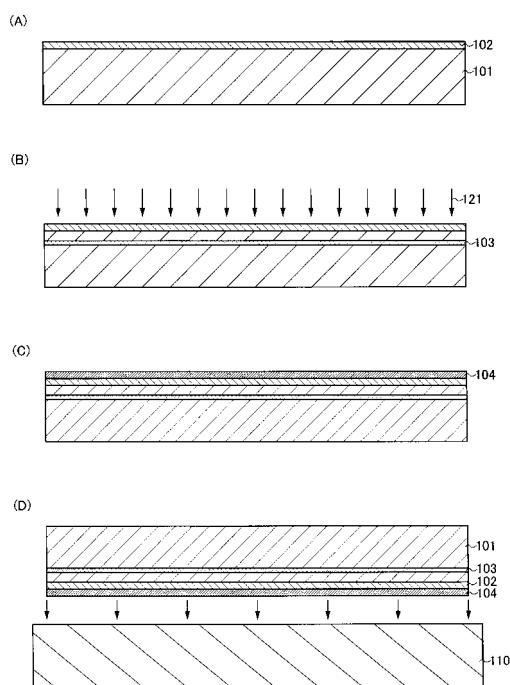

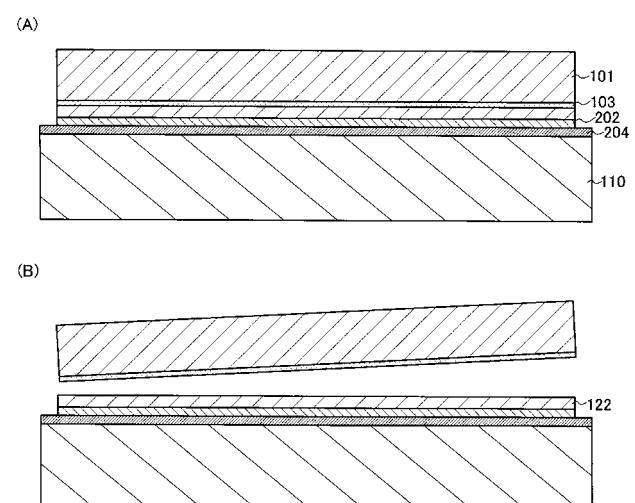

まず、半導体基板101を準備し、半導体基板101の表面に絶縁層102を形成する(図1(A)参照)。

【0021】

半導体基板101は、市販の半導体基板を用いることができ、例えば、単結晶のシリコン基板やゲルマニウム基板、ガリウムヒ素やインジウムリン等の化合物半導体基板が挙げられる。市販のシリコン基板としては、直径5インチ(125mm)、直径6インチ(150mm)、直径8インチ(200mm)、直径12インチ(300mm)サイズの円形のものが代表的である。なお、形状は円形に限らず矩形状等に加工したシリコン基板を用いることも可能である。

40

【0022】

絶縁層102は、平滑面を有する絶縁層を用いることが好ましく、酸化シリコン層が適している。好ましくは、酸化シリコン層の表面の平均面粗さ( $R_a$ )が0.5nm以下、自乗平均粗さ( $R_{ms}$ )が0.6nm以下、より好ましくは、平均面粗さが0.3nm以下、自乗平均粗さが0.4nm以下となるように形成する。

【0023】

50

特に、有機シランを用いて化学気相成長法により作製される酸化シリコン層が好ましい。有機シランを用いて形成された酸化シリコン層を用いることによって、絶縁層102の表面を平坦にすることができるためである。

【0024】

有機シランとしては、テトラエトキシシラン（略称；TEOS：化学式Si(OCH<sub>3</sub>)<sub>4</sub>）、テトラメチルシラン（TMS：化学式Si(CH<sub>3</sub>)<sub>4</sub>）、トリメチルシラン（(CH<sub>3</sub>)<sub>3</sub>SiH）、テトラメチルシクロテトラシロキサン（TMCTS）、オクタメチルシクロテトラシロキサン（OMCTS）、ヘキサメチルジシラザン（HMDS）、トリエトキシシラン（SiH(OCH<sub>3</sub>)<sub>3</sub>）、トリスジメチルアミノシラン（SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>）等のシリコン含有化合物を用いることができる。

10

【0025】

ここでは、有機シランを原料ガスに用いた化学気相成長法により成膜される酸化シリコン層を半導体基板101上に形成する。他にも、シランを原料ガスに用いた化学気相成長法により成膜される酸化シリコン層又は酸化窒化シリコン層を適用することもできる。

【0026】

次に、絶縁層102を介して、電界で加速されたイオンでなるイオンビーム121を半導体基板101に照射して、半導体基板101の表面から所定の深さの領域に、剥離層103を形成する（図1（B）参照）。イオンビーム121は、ソースガスを励起して、ソースガスのプラズマを生成し、プラズマから電界の作用により、プラズマに含まれるイオンを引き出すことで生成される。

20

【0027】

剥離層103が形成される領域の深さは、イオンビーム121の加速エネルギーとイオンビーム121の入射角によって調節することができる。加速エネルギーは加速電圧、ドーズ量などにより調節できる。イオンの平均侵入深さとほぼ同じ深さの領域に剥離層103が形成される。イオンを添加する深さで、半導体基板101から分離される半導体層の厚さが決定される。剥離層103が形成される深さは10nm以上500nm以下であり、好ましい深さの範囲は50nm以上200nm以下である。

【0028】

イオンを半導体基板101に添加するには、質量分離を伴うイオン注入法を用いてもよいし、質量分離を伴わないイオンドーピング法を用いてもよい。

30

【0029】

ソースガスに水素(H<sub>2</sub>)を用いる場合、水素ガスを励起してH<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>を含むプラズマを生成することができる。ソースガスから生成されるイオン種の割合は、プラズマの励起方法、プラズマを発生させる雰囲気の圧力、ソースガスの供給量などを調節することで、変化させることができる。イオンビーム121に、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>の総量に対してH<sub>3</sub><sup>+</sup>が50%以上含まれるようにするが好ましく、H<sub>3</sub><sup>+</sup>の割合は80%以上がより好ましい。

【0030】

H<sub>3</sub><sup>+</sup>は他の水素イオン種(H<sup>+</sup>、H<sub>2</sub><sup>+</sup>)よりも、水素原子の数が多く、その結果質量が大きいので、同じエネルギーで加速される場合、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>よりも半導体基板101のより浅い領域に添加される。よって、イオンビーム121に含まれるH<sub>3</sub><sup>+</sup>の割合を高くすることにより、水素イオンの平均侵入深さのばらつきが小さくなるので、半導体基板101に水素の深さ方向の濃度プロファイルはより急峻になり、そのプロファイルのピーク位置を浅くすることができる。よって、イオンビーム121に含まれるH<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>の総量に対してH<sub>3</sub><sup>+</sup>が50%以上含まれるようにするが好ましく、H<sub>3</sub><sup>+</sup>の割合は80%以上がより好ましい。

40

【0031】

水素ガスを用いて、イオンドーピング法でイオン添加を行う場合、加速電圧10kV以上200kV以下、ドーズ量1×10<sup>16</sup>ions/cm<sup>2</sup>以上6×10<sup>16</sup>ions/cm<sup>2</sup>以下とすることができる。この条件で水素イオンを添加することで、イオンビーム1

50

21に含まれるイオン種および、その割合にもよるが、剥離層103を半導体基板101の深さ10nm以上500nm以下の領域に形成することができる。

【0032】

また、イオンビーム121のソースガスにヘリウム(He)を用いることもできる。ヘリウムを励起して生成されるイオン種がHe<sup>+</sup>が殆どであるため、質量分離を伴わないイオンドーピング法でも、He<sup>+</sup>を主なイオンとして半導体基板101に添加することができる。よって、イオンドーピング法で、効率良く、微小な空孔を剥離層103に形成することができる。ヘリウムを用いて、イオンドーピング法でイオン添加を行う場合、加速電圧10kV以上200kV以下、ドーザ量 $1 \times 10^{16}$ ions/cm<sup>2</sup>以上 $6 \times 10^{16}$ ions/cm<sup>2</sup>以下とすることができる。

10

【0033】

ソースガスに塩素ガス(Cl<sub>2</sub>ガス)、フッ素ガス(F<sub>2</sub>ガス)などのハロゲンガスを用いることもできる。

【0034】

次に、絶縁層102上に窒素含有層104を形成する(図1(C)参照)。

【0035】

窒素含有層104は、ベース基板と貼り合わされる層(接合層)として機能する。また、後に半導体基板101の一部をベース基板に貼り合わせて単結晶構造を有する半導体層(以下、「単結晶半導体層」と記す)を設けた際に、ベース基板に含まれる可動イオンや水分等の不純物が単結晶半導体層に拡散することを防ぐためのバリア層としても機能する。

20

【0036】

窒素含有層104は、少なくとも窒素、珪素を含む膜であり、例えば、CVD法等を用いて窒化シリコン層、窒化酸化シリコン層又は酸化窒化シリコン層を単層構造又は積層構造で形成する。窒素含有層104は、10nm以上200nm以下、好ましくは50nm以上100nm以下の範囲で設けることが好ましい。また、窒素含有層104は、接合層として機能するため平滑面を有する絶縁層を用いることが好ましく、表面の平均面粗さ(Ra)が0.5nm以下、自乗平均粗さ(Rms)が0.6nm以下、より好ましくは、平均面粗さが0.3nm以下、自乗平均粗さが0.4nm以下となるように形成することができる。

30

【0037】

例えば、窒素含有層104として、プラズマCVD法を用いて低温(100以上~350以下、好ましくは150以上~300以下)で成膜した窒化酸化シリコン層が適している。プラズマCVD法を用い低温で形成することによって、平滑面を有する窒化酸化シリコン層が得ることができる。また、窒素含有層104を低温で成膜することにより、膜中に含まれるHの含有量を多くすることができ、ベース基板との貼り合わせを強固に行うことが可能になる。また、低温で行うことにより、半導体基板101に形成した剥離層103から脱ガスが起こることを防止することができる。なお、半導体基板101から単結晶半導体層を剥離する加熱処理は、窒素含有層の成膜温度よりも高い加熱処理温度が適用される。

40

【0038】

また、本実施の形態では、絶縁層102として平滑面を有する酸化シリコン層を設けることにより、当該絶縁層102上に形成される窒素含有層104の表面を平坦とすることが可能となる。なお、半導体基板101の表面が平坦である場合には、絶縁層102を設けない構成としてもよく、例えば、半導体基板101側から酸化窒化シリコン層、窒化酸化シリコン層の単層、又は酸化窒化シリコン層と窒化酸化シリコン層を積層させて窒素含有層104とすることができます。

【0039】

本明細書中において、酸化窒化シリコンとは、その組成として、窒素よりも酸素の含有量が多いものであって、好ましくは、ラザフォード後方散乱法(RBS: Rutherford Backscattering Spectrometry)及び水素前方散乱法

50

(HFS: Hydrogen Forward Scattering)を用いて測定した場合に、濃度範囲として酸素が50~70原子%、窒素が0.5~15原子%、シリコンが25~35原子%、水素が0.1~10原子%の範囲で含まれるものという。また、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多いものであって、好ましくは、RBS及びHFSを用いて測定した場合に、濃度範囲として酸素が5~30原子%、窒素が20~55原子%、シリコンが25~35原子%、水素が10~30原子%の範囲で含まれるものという。ただし、酸化窒化シリコン又は窒化酸化シリコンを構成する原子の合計を100原子%としたとき、窒素、酸素、シリコン及び水素の含有比率が上記の範囲内に含まれるものとする。

## 【0040】

10

次に、半導体基板101とベース基板110とを貼り合わせる(図1(D)参照)。半導体基板101上に形成された接合層として機能する窒素含有層104とベース基板110の表面とを密着させることにより接合が形成される。この接合は、ファンデルワールス力が作用しており、ベース基板110と半導体基板101を圧接することにより、Si-HやSi-OHを結合種として、水素結合による強固な接合を形成することが可能となる。

## 【0041】

なお、半導体基板101とベース基板110を貼り合わせる前に、メガソニック洗浄、又はメガソニック洗浄及びオゾン水洗浄を行うことにより、基板表面の有機物等のゴミを除去し、表面を親水化できるため好ましい。また、窒素含有層104の表面にプラズマ処理を行うことにより、基板表面の有機物等のゴミを除去してもよい。

20

## 【0042】

ベース基板110は、絶縁表面を有する基板を用いる。具体的には、ベース基板110としては、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われるガラス基板を用いることができる。また、ベース基板110として、歪点が700以下の基板を用いる。例えば、ベース基板110として、旭ガラス社製のガラス基板(商品名AN100)を用いることができる。

## 【0043】

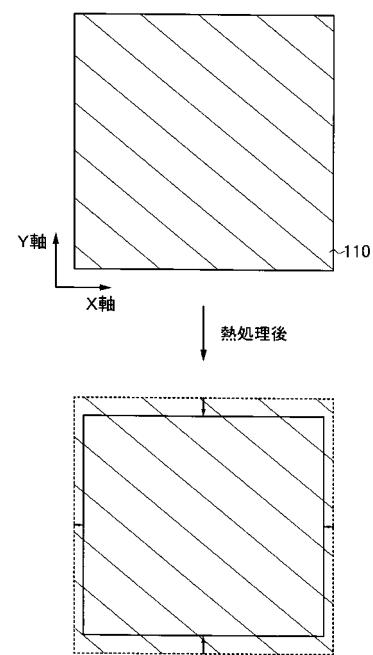

一般的に、ベース基板110として大面積化が可能で安価なガラス基板を用いた場合には、低コスト化を図ることができる。しかし、ガラス基板は、半導体基板と比較して、熱処理前後により、シュリンクする(縮む)場合がある。また、ガラス基板の製法等に依存して、収縮率が異なる場合や、特定の方向によって収縮率が異なる場合(図13参照)がある。

30

## 【0044】

そのため、半導体基板101とベース基板110とを貼り合わせた後に熱処理を行う際に、熱処理によりベース基板110の縮み方が特定の方向によって異なる(異方性がある)場合には、ベース基板110上に形成される単結晶半導体層にも特定の方向に歪みが生じるおそれがある。その結果、特定の方向に応力が生じることにより貼り合わせ不良が発生し、当該単結晶半導体層を用いてトランジスタ等の素子を形成した場合には、素子の特性に影響が生じる可能性がある。

## 【0045】

40

そのため、本実施の形態では、ベース基板110として、熱処理による収縮が特定の方向に依存せず、熱処理により等方的に収縮する基板を用いる。このようなベース基板を用いることにより、ベース基板110上に形成される単結晶半導体層に特定の方向に歪みが生じることを抑制することができる。なお、等方的に収縮するとは、ベース基板110の表面と平行な面においてそれぞれ特定の方位における収縮率が同程度であることをいう。好ましくは、ベース基板110の表面と平行な面においてそれぞれの特定の方位における収縮率が平均値(それぞれ特定の方位の収縮率を平均した値)から10%以内であることをいう。例えば、収縮率の平均値が150ppmである場合には、それぞれ特定の方位(例えば、X軸方向、Y軸方向(X軸と90°異なる方向))における収縮率が135ppm~165ppmの範囲内であることをさす。

50

## 【0046】

さらに、本実施の形態では、ベース基板110の熱膨張係数が半導体基板101と同程度か、又は当該半導体基板101より大きい基板を用いることが好ましい。このようなベース基板を用いることによって、熱処理の際に半導体基板101とベース基板110に生じる応力の差を低減し、半導体基板101とベース基板110が剥がれることを抑制することができる。ベース基板110の熱膨張係数を、半導体基板101の熱膨張係数の0.85倍～2倍とすることが好ましい。例えば、半導体基板101として単結晶シリコン基板を用いた場合には、シリコンの熱膨張係数が $2.6 \times 10^{-6}$ /(300 迄)であるため、ベース基板110(例えば、ガラス基板)として熱膨張係数が $2.3 \times 10^{-6}$ ～ $5.0 \times 10^{-6}$ /(300 迄)の基板を用いることが好ましい。

10

## 【0047】

また、ベース基板110の表面は平滑であることが好ましく、表面の平均面粗さ( $R_a$ )が0.5nm以下、自乗平均粗さ( $R_{ms}$ )が0.6nm以下、より好ましくは、平均面粗さが0.3nm以下、自乗平均粗さが0.4nm以下となるように形成することが好ましい。例えば、ベース基板110としてガラス基板を用いる場合には、あらかじめガラス基板の表面に研磨処理を行ってもよい。

## 【0048】

ベース基板110として、ガラス基板を用いることにより、例えば、第6世代(1500mm×1850mm)、第7世代(1870mm×2200mm)、第8世代(2200mm×2400mm)といわれる大面積のマザーガラス基板を用いることができる。大面積のマザーガラス基板をベース基板110として用い、複数の半導体基板と貼り合わせてSOD基板を製造することにより、SOD基板の大面積化が実現できる。その結果、1枚の基板から製造できる表示パネルの数(面取り数)を増大させることができるとなり、生産性を向上させることができる。

20

## 【0049】

また、ベース基板110と窒素含有層104との接合を良好に行うために、接合面を活性化しておいてもよい。例えば、接合を形成する面の一方又は双方に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行うことで接合面を活性化することもできる。このような表面処理により、400以下の温度であっても異種材料間の接合を形成することが容易となる。

30

## 【0050】

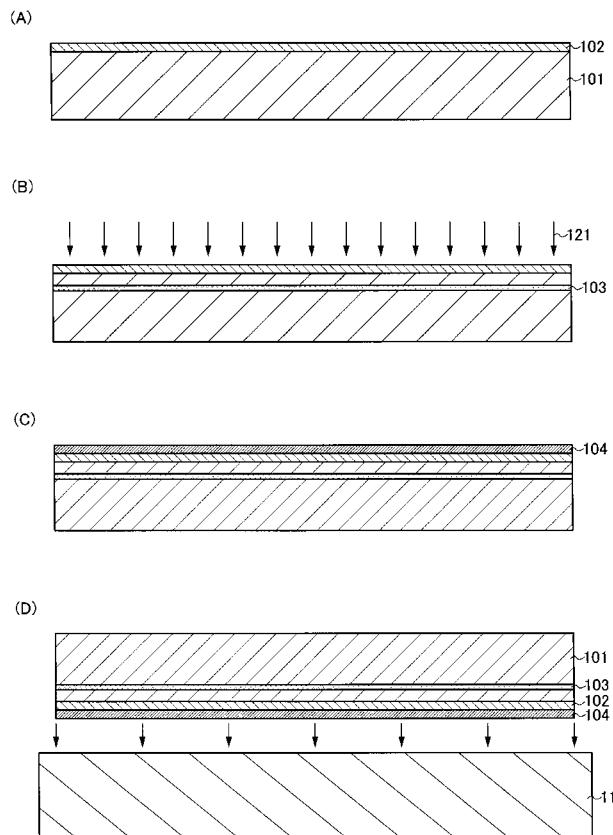

また、窒素含有層104を介してベース基板110と半導体基板101を貼り合わせた後(図2(A)参照)に、加熱処理と加圧処理の一方又は両方を行うことが好ましい。加熱処理や加圧処理を行うことによりベース基板110と半導体基板101の接合強度を向上させることができる。加熱処理の温度は、ベース基板110の耐熱温度以下で行う。例えば、本実施の形態では、200で行えばよい。加圧処理は、接合面に垂直な方向に圧力が加わるように行い、ベース基板110及び半導体基板101の耐圧性を考慮して行う。

40

## 【0051】

次に、加熱処理を行い剥離層103を劈開面として半導体基板101の一部をベース基板110から剥離する(図2(B)参照)。加熱処理の温度は絶縁層102の成膜温度以上、ベース基板110の耐熱温度以下で行うことが好ましい。例えば、400乃至700の加熱処理を行うことにより、剥離層103に形成された微小な空洞の体積変化が起こり、当該剥離層103に沿って劈開する。絶縁層102はベース基板110と接合しているので、ベース基板110上には半導体基板101と同じ結晶性の単結晶半導体層122が残存することとなる。なお、加熱処理としてRTA(Rapid Thermal Anneal)装置等の急速加熱を行うことができる装置を用いる場合には、ベース基板110の歪点より高い温度で加熱処理を行ってもよい。

50

**【 0 0 5 2 】**

以上の工程により、ベース基板 110 上に絶縁層 102 及び窒素含有層 104 を介して単結晶半導体層 122 が設けられた SOI 基板が得られる。

**【 0 0 5 3 】**

本実施の形態では、図 2 (A)、(B) において、熱処理を行っているが、上述したようにベース基板 110 として熱処理により等方的に収縮する基板を用いることによって、特定方向に収縮することを防止できる。その結果、剥離後にベース基板 110 上に設けられた単結晶半導体層 122 において特定方向に生じる歪みを低減することができる。

**【 0 0 5 4 】**

なお、本実施の形態で示した SOI 基板の作製方法は、上述した方法に限られない。例えば、窒素含有層 104 の形成前でなく、窒素含有層 104 を形成した後に、絶縁層 102 及び窒素含有層 104 を介して水素等のイオンを導入することにより、半導体基板 101 の表面から所定の深さの領域に剥離層 103 を形成してもよい。イオン導入後に窒素含有層 104 の表層をエッチングし、イオンの添加により窒素含有層 104 の表面に形成された損傷層を除去してもよい。

**【 0 0 5 5 】**

また、窒素含有層 104 を介してイオンの導入を行った後、窒素含有層 104 の表面にシリコンを吸着させた後、大気に曝すことにより窒素含有層 104 上に薄い酸化膜（例えば、SiO<sub>x</sub>）を形成してもよい。この場合、イオンの導入後に窒素含有層 104 の表面を親水化でき、ベース基板 110 との結合を強固にすることができる。なお、酸化膜を形成後、表面にプラズマ照射若しくはラジカル処理を行うことで接合面を活性化してもよい。

**【 0 0 5 6 】**

また、絶縁層 102 の形成後でなく形成前に、水素等のイオンを導入することにより、半導体基板 101 の表面から所定の深さの領域に剥離層 103 を形成してもよい。なお、この場合、イオンの導入に伴い半導体基板 101 の表面に不純物等が付着することや、表面がエッチングされることを防止するために、半導体基板 101 の表面に保護層を形成し、当該保護層を介してイオンの導入を行うことが好ましい。

**【 0 0 5 7 】**

保護層としては、例えば、半導体基板 101 の表面にオゾン水、過酸化水素水、硫酸過水、オゾン雰囲気下で処理を行うことにより得られた酸化膜を用いることができる。また、他にも、保護層として酸化雰囲気中にハロゲン（例えば、塩素）を添加した酸化を行うことにより得られた酸化膜を用いることができる。酸化膜中にハロゲン元素を含ませた場合には、金属などの不純物を捕獲して半導体基板 101 の汚染を防止する保護層としての機能を発現させることができる。

**【 0 0 5 8 】**

その後、半導体基板 101 上に形成された保護層の上に絶縁層 102 及び窒素含有層 104 を形成してもよいし、イオンの導入後保護層を除去した後に半導体基板 101 上に絶縁層 102 及び窒素含有層 104 を形成してもよい。また、窒素含有層 104 を設けずに保護層を接合層としてベース基板 110 と接合させてもよい。

**【 0 0 5 9 】**

なお、本実施の形態で示した SOI 基板の作製方法は、本明細書の他の実施の形態で示した作製方法と適宜組み合わせることができる。

**【 0 0 6 0 】****( 実施の形態 2 )**

本実施の形態では、上記実施の形態と異なる SOI 基板の作製方法に関して図面を参照して説明する。具体的には、表面に窒素含有層が設けられたベース基板と半導体基板とを貼り合わせる場合に関して説明する。

**【 0 0 6 1 】**

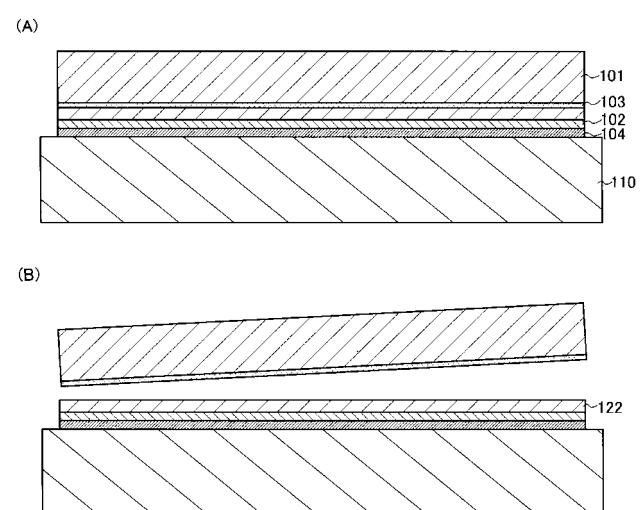

まず、半導体基板 101 を準備し、半導体基板 101 の表面に絶縁層 202 を形成する（図 3 (A) 参照）。

10

20

30

40

50

## 【0062】

本実施の形態では、絶縁層202はベース基板との接合層として機能し、半導体基板101がベース基板と接合を形成する面に設ける。単層構造としても積層構造としてもよいが、ベース基板と接合する面（以下、「接合面」とも記す）が平滑面を有し親水性表面となる絶縁層を用いることが好ましい。平滑面を有し親水性表面を形成できる絶縁層としては、酸化シリコン層が適している。好ましくは、酸化シリコン層の平均面粗さ（Ra）が0.5nm以下、自乗平均粗さ（Rms）が0.6nm以下、より好ましくは、平均面粗さが0.3nm以下、自乗平均粗さが0.4nm以下とする。

## 【0063】

特に、有機シランを用いて化学気相成長法により作製される酸化シリコン層が好ましい。有機シランを用いて形成された酸化シリコン層を用いることによって、ベース基板と単結晶半導体層との接合を強固にすることができるためである。

## 【0064】

有機シランとしては、テトラエトキシシラン（略称；TEOS：化学式Si（OC<sub>2</sub>H<sub>5</sub>）<sub>4</sub>）、テトラメチルシラン（TMS：化学式Si（CH<sub>3</sub>）<sub>4</sub>）、トリメチルシラン（（CH<sub>3</sub>）<sub>3</sub>SiH）、テトラメチルシクロテトラシロキサン（TMCTS）、オクタメチルシクロテトラシロキサン（OMCTS）、ヘキサメチルジシラザン（HMDS）、トリエトキシシラン（SiH（OC<sub>2</sub>H<sub>5</sub>）<sub>3</sub>）、トリスジメチルアミノシラン（SiH（N（CH<sub>3</sub>）<sub>2</sub>）<sub>3</sub>）等のシリコン含有化合物を用いることができる。

## 【0065】

ここでは、有機シランを原料ガスに用いた化学気相成長法により成膜される酸化シリコン層を半導体基板101上に形成する。他にも、シランを原料ガスに用いた化学気相成長法により成膜される酸化シリコン層又は酸化窒化シリコン層を適用することもできる。化学気相成長法による成膜では、半導体基板101に形成した剥離層103から脱ガスが起こらない程度の温度を適用する。例えば、成膜温度を350以下とすることが好ましい。なお、半導体基板101から単結晶半導体層を剥離する加熱処理は、化学気相成長法による成膜温度よりも高い加熱処理温度が適用される。

## 【0066】

次に、絶縁層202を介して、電界で加速されたイオンであるイオンビーム121を半導体基板101に照射して、半導体基板101の表面から所定の深さの領域に、剥離層103を形成する（図3（B）参照）。なお、剥離層103の形成方法の詳細については実施の形態1を参照できるため、ここでは省略する。

## 【0067】

次に、表面に窒素含有層204が形成されたベース基板を用意し、半導体基板101とベース基板110とを貼り合わせる（図3（C）参照）。半導体基板101上に形成された接合層として機能する絶縁層202と、ベース基板110上に形成された窒素含有層204の表面とを密着させることにより接合が形成される。この接合は、ファンデルワールス力が作用しており、ベース基板110と半導体基板101を圧接することにより、Si-HやSi-OHを結合種として、水素結合による強固な接合を形成することが可能となる。

## 【0068】

なお、半導体基板101とベース基板110を貼り合わせる前に、メガソニック洗浄、又はメガソニック洗浄及びオゾン水洗浄を行うことにより、基板表面のゴミを除去し、表面を親水化できるため好ましい。また、窒素含有層204の表面にプラズマ処理を行うことにより、基板表面の有機物等のゴミを除去してもよい。

## 【0069】

ベース基板110としては、上記実施の形態1で示したように、熱処理による収縮が特定の方向に依存せず、熱処理により等方的に収縮する基板を用いる。なお、ベース基板110については実施の形態1を参照できるため、ここでは省略する。

## 【0070】

10

20

30

40

50

窒素含有層 204 は、半導体基板 101 上に形成された絶縁層 202 と貼り合わされる層となり、後にベース基板 110 上に単結晶半導体層を設けた際に、ベース基板 110 に含まれる可動イオンや水分等の不純物が単結晶半導体層に拡散することを防ぐためのバリア層として機能する。

【0071】

窒素含有層 204 は、CVD 法やスパッタリング法等を用いて窒化シリコン層、窒化酸化シリコン層又は酸化窒化シリコン層を単層構造又は積層構造で形成する。窒素含有層 204 は、10 nm 以上 200 nm 以下、好ましくは 50 nm 以上 100 nm 以下の範囲で設けることが好ましい。また、窒素含有層 204 は、平滑面を有する絶縁層を用いることが好ましく、表面の平均面粗さ (Ra) が 0.5 nm 以下、自乗平均粗さ (Rms) が 0.6 nm 以下、より好ましくは、平均面粗さが 0.3 nm 以下、自乗平均粗さが 0.4 nm 以下となるように形成することが好ましい。

10

【0072】

例えば、窒素含有層 204 として、プラズマ CVD 法を用いて低温 (100 以上 ~ 350 以下、好ましくは 150 以上 ~ 300 以下) で成膜した窒化酸化シリコン層が適している。プラズマ CVD 法を用い低温で形成することによって、平滑面を有する窒化酸化シリコン層が得ることができる。また、窒素含有層 204 を低温で成膜することにより、膜中に含まれる H の含有量を多くすることができ、ベース基板との貼り合わせを強固に行うことが可能になる。

20

【0073】

また、本実施の形態では、ガラス等のベース基板 110 上に窒素含有層 204 を形成するため、ベース基板 110 の表面が平滑であることが好ましい。例えば、ベース基板 110 として、表面の平均面粗さ (Ra) が 0.5 nm 以下、自乗平均粗さ (Rms) が 0.6 nm 以下、より好ましくは、平均面粗さが 0.3 nm 以下、自乗平均粗さが 0.4 nm 以下のガラス基板を用いることが好ましい。従って、例えば、あらかじめ表面の研磨処理を行ったガラス基板上に、窒素含有層 204 を形成してもよい。

20

【0074】

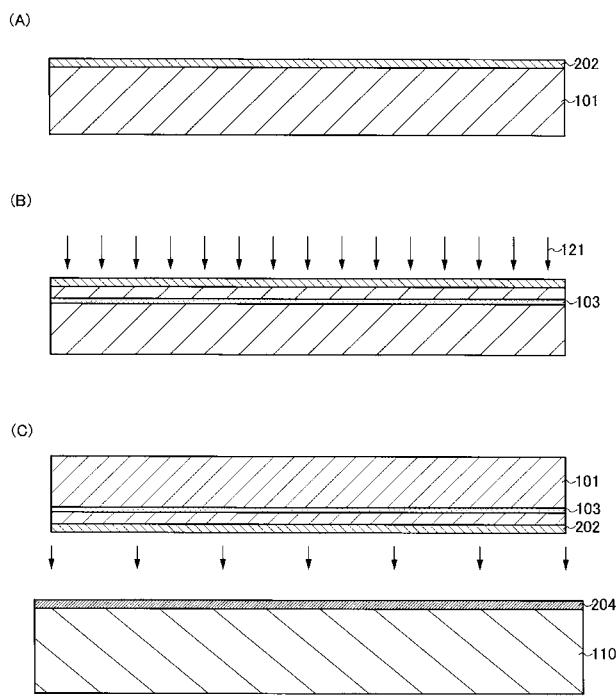

また、絶縁層 202 及び窒素含有層 204 を介してベース基板 110 と半導体基板 101 を貼り合わせた後 (図 4 (A) 参照) は、加熱処理と加圧処理の一方又は両方を行うことが好ましい。加熱処理や加圧処理を行うことによりベース基板 110 と半導体基板 101 の接合強度を向上させることが可能となる。加熱処理の温度は、ベース基板 110 の耐熱温度以下で行う。例えば、本実施の形態では、200 で行えばよい。加圧処理は、接合面に垂直な方向に圧力が加わるように行い、ベース基板 110 及び半導体基板 101 の耐圧性を考慮して行う。

30

【0075】

次に、加熱処理を行い剥離層 103 を劈開面として半導体基板 101 の一部をベース基板 110 から剥離する (図 4 (B) 参照)。加熱処理の温度は絶縁層 202 の成膜温度以上、ベース基板 110 の耐熱温度以下で行うことが好ましい。例えば、400 乃至 700 の加熱処理を行うことにより、剥離層 103 に形成された微小な空洞の体積変化が起こり、当該剥離層 103 に沿って劈開する。絶縁層 202 は窒素含有層 204 を介してベース基板 110 と接合しているので、ベース基板 110 上には半導体基板 101 と同じ結晶性の単結晶半導体層 122 が残存することとなる。

40

【0076】

以上の工程により、ベース基板 110 上に絶縁層 202 及び窒素含有層 204 を介して単結晶半導体層 122 が設けられた SOI 基板が得られる。

【0077】

本実施の形態では、図 4 (A)、(B) において、熱処理を行っているが、上述したようにベース基板 110 として熱処理により等方的に収縮する基板を用いることによって、特定方向に収縮することを防止できる。その結果、剥離後にベース基板 110 上に設けられた単結晶半導体層 122 において特定方向に生じる歪みを低減することができる。

50

## 【0078】

なお、本実施の形態で示したSOI基板の作製方法は、本明細書の他の実施の形態で示した作製方法と適宜組み合わせることができる。

## 【0079】

## (実施の形態3)

本実施の形態では、上記実施の形態で作製したSOI基板を用いて、半導体装置を作製する方法を説明する。

## 【0080】

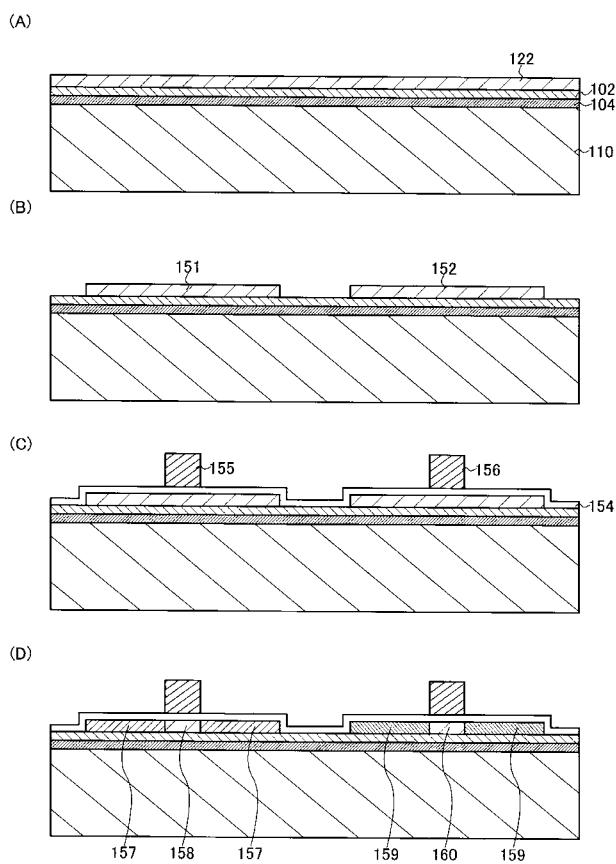

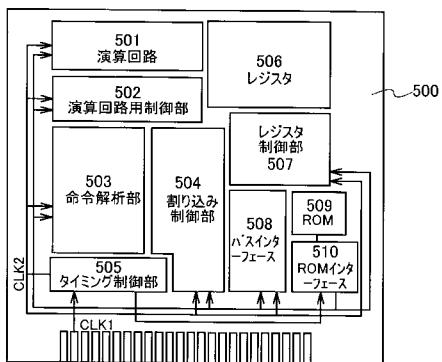

まず、図5および図6を参照して、半導体装置の作製方法として、nチャネル型薄膜トランジスタ、およびpチャネル型薄膜トランジスタを作製する方法を説明する。複数の薄膜トランジスタ(TFT)を組み合わせることで、各種の半導体装置を形成することができる。

10

## 【0081】

SOI基板として、実施の形態1の方法で作製したSOI基板を用いることとする。図5(A)は、図1を用いて説明した方法で作製されたSOI基板の断面図である。

## 【0082】

エッチングにより、SOI基板の単結晶半導体層122を素子分離して、図5(B)に示すように半導体層151、152を形成する。半導体層151はnチャネル型のTFTを構成し、半導体層152はpチャネル型のTFTを構成する。

20

## 【0083】

図5(C)に示すように、半導体層151、152上に絶縁層154を形成する。次に、絶縁層154を介して半導体層151上にゲート電極155を形成し、半導体層152上にゲート電極156を形成する。

## 【0084】

なお、単結晶半導体層122のエッチングを行う前に、TFTのしきい値電圧を制御するために、硼素、アルミニウム、ガリウムなどのアクセプタとなる不純物元素、またはリン、ヒ素などのドナーとなる不純物元素を単結晶半導体層122添加することが好ましい。例えば、nチャネル型TFTが形成される領域にアクセプタを添加し、pチャネル型TFTが形成される領域にドナーを添加する。

30

## 【0085】

次に、図5(D)に示すように半導体層151にn型の低濃度不純物領域157を形成し、半導体層152にp型の高濃度不純物領域159を形成する。まず、半導体層151にn型の低濃度不純物領域157を形成する。このため、pチャネル型TFTとなる半導体層152をレジストでマスクし、ドナーを半導体層151に添加する。ドナーとしてリンまたはヒ素を添加すればよい。イオンドーピング法またはイオン注入法によりドナーを添加することにより、ゲート電極155がマスクとなり、半導体層151に自己整合的にn型の低濃度不純物領域157が形成される。半導体層151のゲート電極155と重なる領域はチャネル形成領域158となる。

## 【0086】

次に、半導体層152を覆うマスクを除去した後、nチャネル型TFTとなる半導体層151をレジストマスクで覆う。次に、イオンドーピング法またはイオン注入法によりアクセプタを半導体層152に添加する。アクセプタとして、ボロンを添加することができる。アクセプタの添加工程では、ゲート電極155がマスクとして機能して、半導体層152にp型の高濃度不純物領域159が自己整合的に形成される。高濃度不純物領域159はソース領域またはドレイン領域として機能する。半導体層152のゲート電極156と重なる領域はチャネル形成領域160となる。ここでは、n型の低濃度不純物領域157を形成した後、p型の高濃度不純物領域159を形成する方法を説明したが、先にp型の高濃度不純物領域159を形成することもできる。

40

## 【0087】

次に、半導体層151を覆うレジストを除去した後、プラズマCVD法等によって窒化シ

50

リコン等の窒素化合物や酸化シリコン等の酸化物からなる単層構造または積層構造の絶縁膜を形成する。この絶縁層を垂直方向の異方性エッチングすることで、図6(A)に示すように、ゲート電極155、156の側面に接するサイドウォール絶縁層161、162を形成する。この異方性エッチングにより、絶縁層154もエッチングされる。

【0088】

次に、図6(B)に示すように、半導体層152をレジスト165で覆う。半導体層151にソース領域またはドレイン領域として機能する高濃度不純物領域を形成するため、イオン注入法またはイオンドーピング法により、半導体層151に高ドーズ量でドナーを添加する。ゲート電極155およびサイドウォール絶縁層161がマスクとなり、n型の高濃度不純物領域167が形成される。次に、ドナーおよびアクセプタの活性化のための加熱処理を行う。

10

【0089】

活性化の加熱処理の後、図6(C)に示すように、水素を含んだ絶縁層168を形成する。絶縁層168を形成後、350以上450以下の温度による加熱処理を行い、絶縁層168中に含まれる水素を半導体層151、152中に拡散させる。絶縁層168は、プロセス温度が350以下のプラズマCVD法により窒化シリコンまたは窒化酸化シリコンを堆積することで形成できる。半導体層151、152に水素を供給することで、半導体層151、152中および絶縁層154との界面での捕獲中心となるような欠陥を効果的に補償することができる。

20

【0090】

その後、層間絶縁層169を形成する。層間絶縁層169は、酸化シリコン膜、BPSG(Boron Phosphorus Silicon Glass)膜などの無機材料でなる絶縁膜、または、ポリイミド、アクリルなどの有機樹脂膜から選ばれた単層構造の膜、積層構造の膜で形成することができる。層間絶縁層169にコンタクトホールを形成した後、図6(C)に示すように配線170を形成する。配線170の形成には、例えば、アルミニウム膜またはアルミニウム合金膜などの低抵抗金属膜をバリアメタル膜で挟んだ3層構造の導電膜で形成することができる。バリアメタル膜は、モリブデン、クロム、チタンなどの金属膜で形成することができる。

30

【0091】

以上の工程により、nチャネル型TFTとpチャネル型TFTを有する半導体装置を作製することができる。SOI基板の作製過程で、チャネル形成領域を構成する半導体層の金属元素の濃度を低減させているので、オフ電流が小さく、しきい値電圧の変動が抑制されたTFTを作製することができる。

30

【0092】

図5および図6を参照してTFTの作製方法を説明したが、容量、抵抗などTFTと共に各種の半導体素子を形成することで、高付加価値の半導体装置を作製することができる。以下、図面を参照しながら半導体装置の具体的な態様を説明する。

【0093】

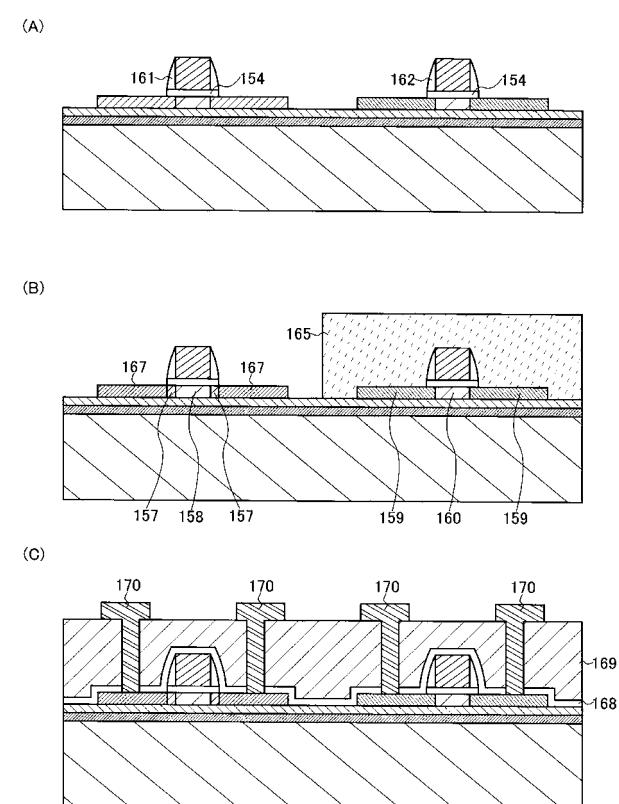

まず、半導体装置の一例として、マイクロプロセッサについて説明する。図7はマイクロプロセッサ500の構成例を示すブロック図である。

40

【0094】

マイクロプロセッサ500は、演算回路501(Arithmetic logic unit。ALUともいう。)、演算回路制御部502(ALU Controller)、命令解析部503(Instruction Decoder)、割り込み制御部504(Interrupt Controller)、タイミング制御部505(Timing Controller)、レジスタ506(Register)、レジスタ制御部507(Register Controller)、バスインターフェース508(Bus I/F)、読み出し専用メモリ509、およびメモリインターフェース510を有している。

【0095】

50

バスインターフェース 508 を介してマイクロプロセッサ 500 に入力された命令は、命令解析部 503 に入力され、デコードされた後、演算回路制御部 502、割り込み制御部 504、レジスタ制御部 507、タイミング制御部 505 に入力される。演算回路制御部 502、割り込み制御部 504、レジスタ制御部 507、タイミング制御部 505 は、デコードされた命令に基づき様々な制御を行う。

【0096】

演算回路制御部 502 は、演算回路 501 の動作を制御するための信号を生成する。また、割り込み制御部 504 は、マイクロプロセッサ 500 のプログラム実行中に、外部の入出力装置や周辺回路からの割り込み要求を処理する回路であり、割り込み制御部 504 は、割り込み要求の優先度やマスク状態を判断して、割り込み要求を処理する。レジスタ制御部 507 は、レジスタ 506 のアドレスを生成し、マイクロプロセッサ 500 の状態に応じてレジスタ 506 の読み出しや書き込みを行う。タイミング制御部 505 は、演算回路 501、演算回路制御部 502、命令解析部 503、割り込み制御部 504、およびレジスタ制御部 507 の動作のタイミングを制御する信号を生成する。例えば、タイミング制御部 505 は、基準クロック信号 CLK1 を元に、内部クロック信号 CLK2 を生成する内部クロック生成部を備えている。図 7 に示すように、内部クロック信号 CLK2 は他の回路に入力される。

10

【0097】

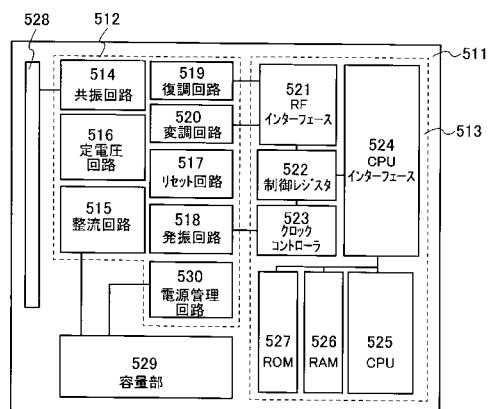

次に、非接触でデータの送受信を行う機能、および演算機能を備えた半導体装置の一例を説明する。図 8 は、このような半導体装置の構成例を示すブロック図である。図 8 に示す半導体装置は、無線通信により外部装置と信号の送受信を行って動作するコンピュータ（以下、「RFCPU」という）と呼ぶことができる。

20

【0098】

図 8 に示すように、RFCPU511 は、アナログ回路部 512 とデジタル回路部 513 を有している。アナログ回路部 512 として、共振容量を有する共振回路 514、整流回路 515、定電圧回路 516、リセット回路 517、発振回路 518、復調回路 519 と、変調回路 520、電源管理回路 530 を有している。デジタル回路部 513 は、RFインターフェース 521、制御レジスタ 522、クロックコントローラ 523、CPUインターフェース 524、中央処理ユニット 525、ランダムアクセスメモリ 526、読み出し専用メモリ 527 を有している。

30

【0099】

RFCPU511 の動作の概要は以下の通りである。アンテナ 528 が受信した信号は共振回路 514 により誘導起電力を生じる。誘導起電力は、整流回路 515 を経て容量部 529 に充電される。この容量部 529 はセラミックコンデンサーや電気二重層コンデンサーなどのキャパシタで形成されていることが好ましい。容量部 529 は、RFCPU511 を構成する基板に集積されている必要はなく、他の部品として RFCPU511 に組み込むこともできる。

【0100】

リセット回路 517 は、デジタル回路部 513 をリセットし初期化する信号を生成する。例えば、電源電圧の上昇に遅延して立ち上がる信号をリセット信号として生成する。発振回路 518 は、定電圧回路 516 により生成される制御信号に応じて、クロック信号の周波数とデューティー比を変更する。復調回路 519 は、受信信号を復調する回路であり、変調回路 520 は、送信するデータを変調する回路である。

40

【0101】

例えば、復調回路 519 はローパスフィルタで形成され、振幅変調（ASK）方式の受信信号を、その振幅の変動をもとに、二値化する。また、送信データを振幅変調（ASK）方式の送信信号の振幅を変動させて送信するため、変調回路 520 は、共振回路 514 の共振点を変化させることで通信信号の振幅を変化させている。

【0102】

クロックコントローラ 523 は、電源電圧または中央処理ユニット 525 における消費電

50

流に応じてクロック信号の周波数とデューティー比を変更するための制御信号を生成している。電源電圧の監視は電源管理回路 530 が行っている。

【0103】

アンテナ 528 から R F C P U 511 に入力された信号は復調回路 519 で復調された後、R F インターフェース 521 で制御コマンドやデータなどに分解される。制御コマンドは制御レジスタ 522 に格納される。制御コマンドには、読み出し専用メモリ 527 に記憶されているデータの読み出し、ランダムアクセスメモリ 526 へのデータの書き込み、中央処理ユニット 525 への演算命令などが含まれている。

【0104】

中央処理ユニット 525 は、C P U インターフェース 524 を介して読み出し専用メモリ 527、ランダムアクセスメモリ 526、制御レジスタ 522 にアクセスする。C P U インターフェース 524 は、中央処理ユニット 525 が要求するアドレスより、読み出し専用メモリ 527、ランダムアクセスメモリ 526、制御レジスタ 522 のいずれかに対するアクセス信号を生成する機能を有している。

10

【0105】

中央処理ユニット 525 の演算方式は、読み出し専用メモリ 527 に O S ( オペレーティングシステム ) を記憶させておき、起動とともにプログラムを読み出し実行する方式を採用することができる。また、専用回路で演算回路を構成して、演算処理をハードウェア的に処理する方式を採用することもできる。ハードウェアとソフトウェアを併用する方式では、専用の演算回路で一部の演算処理を行い、プログラムを使って、残りの演算を中央処理ユニット 525 が処理する方式を適用できる。

20

【0106】

次に、図 9 ~ 図 11 を用いて、半導体装置として表示装置について説明する。

【0107】

上記実施の形態 1、2 で説明した S O I 基板の作製工程では、ガラス基板をベース基板 110 に適用することが可能となる。従って、ベース基板 110 にガラス基板を用い、複数の半導体層を貼り合わせることで、一辺が 1 メートルを超える大面積な S O I 基板を製造することができる。

【0108】

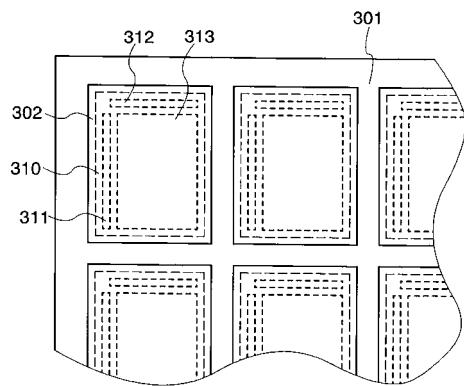

S O I 基板のベース基板に表示パネルを製造するマザーガラスと呼ばれる大面積ガラス基板を用いることができる。図 9 はベース基板 110 にマザーガラスを用いた S O I 基板の正面図である。このような大面積な S O I 基板に複数の半導体素子を形成することで、液晶表示装置、エレクトロルミネッセンス表示装置を作製することができる。また、このような表示装置だけでなく、S O I 基板を用いて、太陽電池、フォト I C 、半導体記憶装置など各種の半導体装置を製造することができる。

30

【0109】

図 9 に示すように、1 枚のマザーガラス 301 には、複数の半導体基板から剥離された単結晶半導体層 302 が貼り合わせられている。マザーガラス 301 から複数の表示パネルを切り出すために、単結晶半導体層 302 に表示パネルの形成領域 310 が含まれるようにすることができる。表示パネルは、走査線駆動回路、信号線駆動回路、画素部を有する。そのため表示パネルの形成領域 310 には、これらが形成される領域 ( 走査線駆動回路形成領域 311 、信号線駆動回路形成領域 312 、画素形成領域 313 ) を含んでいる。

40

【0110】

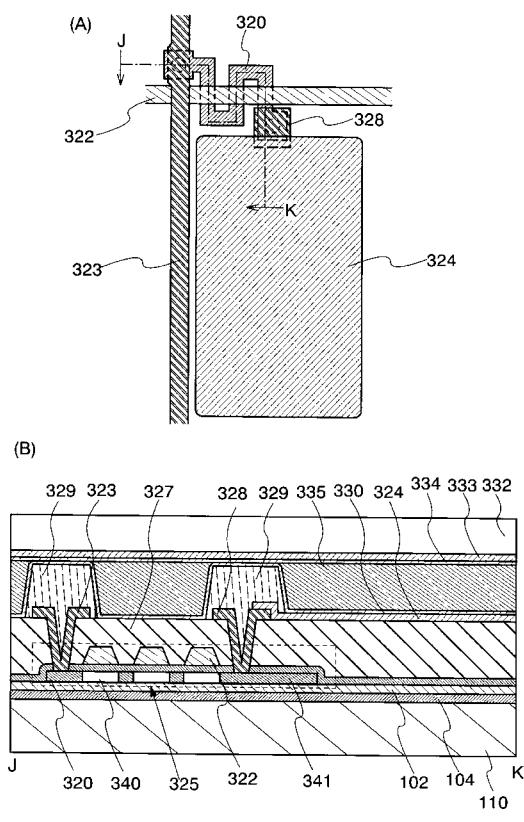

図 10 は液晶表示装置を説明するための図面である。図 10 ( A ) は液晶表示装置の画素の平面図であり、図 10 ( B ) は、J - K 切断線による図 10 ( A ) の断面図である。

【0111】

図 10 ( A ) に示すように、画素は、単結晶半導体層 320 、単結晶半導体層 320 と交差している走査線 322 、走査線 322 と交差している信号線 323 、画素電極 324 、画素電極 324 と単結晶半導体層 320 を電気的に接続する電極 328 を有する。単結晶

50

半導体層 320 は、S O I 基板に貼り合わせられた単結晶半導体層 302 から形成された層であり、画素の T F T 325 を構成する。

【 0 1 1 2 】

S O I 基板には実施の形態 1 の方法で作製した S O I 基板が用いられている。図 10 ( B ) に示すように、ベース基板 110 上に、窒素含有層 104 、絶縁層 102 及び単結晶半導体層 320 が積層されている。ベース基板 110 は分割されたマザーガラス 301 である。T F T 325 の単結晶半導体層 320 は、S O I 基板の半導体層をエッチングにより素子分離して形成された層である。単結晶半導体層 320 には、チャネル形成領域 340 、ドナーが添加された n 型の高濃度不純物領域 341 が形成されている。T F T 325 のゲート電極は走査線 322 に含まれ、ソース電極およびドレイン電極の一方は信号線 323 に含まれている。

10

【 0 1 1 3 】

層間絶縁膜 327 上には、信号線 323 、画素電極 324 および電極 328 が設けられている。層間絶縁膜 327 上には、柱状スペーサ 329 が形成されている。信号線 323 、画素電極 324 、電極 328 および柱状スペーサ 329 を覆って配向膜 330 が形成されている。対向基板 332 には、対向電極 333 、対向電極を覆う配向膜 334 が形成されている。柱状スペーサ 329 は、ベース基板 110 と対向基板 332 の隙間を維持するために形成される。柱状スペーサ 329 によって形成される隙間に液晶層 335 が形成されている。信号線 323 および電極 328 と高濃度不純物領域 341 との接続部は、コンタクトホールの形成によって層間絶縁膜 327 に段差が生じるので、この接続部では液晶層 335 の液晶の配向が乱れやすい。そのため、この段差部に柱状スペーサ 329 を形成して、液晶の配向の乱れを防ぐ。

20

【 0 1 1 4 】

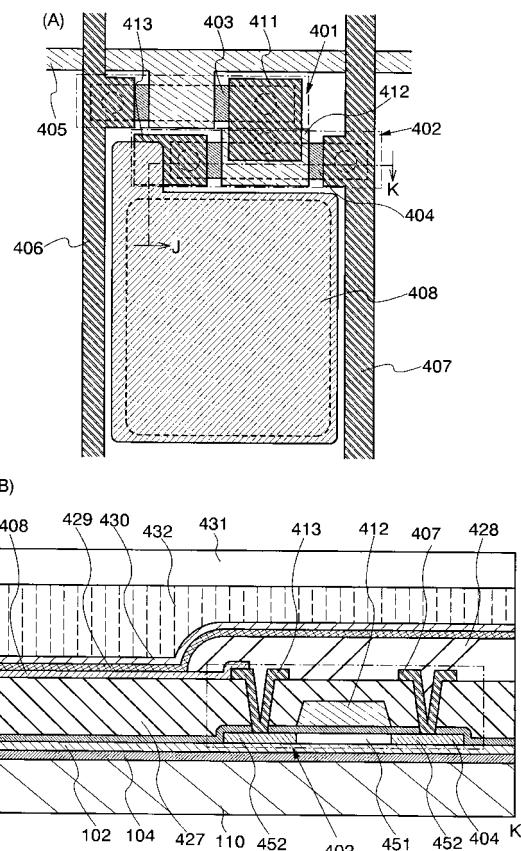

次に、エレクトロルミネンス表示装置（以下、E L 表示装置という。）について図 11 を参照して説明する。図 11 ( A ) は E L 表示装置の画素の平面図であり、図 11 ( B ) は、J - K 切断線による図 11 ( A ) の断面図である。

【 0 1 1 5 】

図 11 ( A ) に示すように、画素は、T F T でなる選択用トランジスタ 401 、表示制御用トランジスタ 402 、走査線 405 、信号線 406 、および電流供給線 407 、画素電極 408 を含む。エレクトロルミネンス材料を含んで形成される層（E L 層）が一対の電極間に挟んだ構造の発光素子が各画素に設けられている。発光素子の一方の電極が画素電極 408 である。また、半導体層 403 は、選択用トランジスタ 401 のチャネル形成領域、ソース領域およびドレイン領域が形成されている。半導体層 404 は、表示制御用トランジスタ 402 のチャネル形成領域、ソース領域およびドレイン領域が形成されている。半導体層 403 、404 は、S O I 基板に貼り合わせられた単結晶半導体層 302 から形成された層である。

30

【 0 1 1 6 】

選択用トランジスタ 401 において、ゲート電極は走査線 405 に含まれ、ソース電極またはドレイン電極の一方は信号線 406 に含まれ、他方は電極 411 として形成されている。表示制御用トランジスタ 402 は、ゲート電極 412 が電極 411 と電気的に接続され、ソース電極またはドレイン電極の一方は、画素電極 408 に電気的に接続される電極 413 として形成され、他方は、電流供給線 407 に含まれている。

40

【 0 1 1 7 】

表示制御用トランジスタ 402 は p チャネル型の T F T である。図 11 ( B ) に示すように、半導体層 404 には、チャネル形成領域 451 、および p 型の高濃度不純物領域 452 が形成されている。なお、S O I 基板は、実施の形態 1 の方法で作製した S O I 基板が用いられている。

【 0 1 1 8 】

表示制御用トランジスタ 402 のゲート電極 412 を覆って、層間絶縁膜 427 が形成されている。層間絶縁膜 427 上に、信号線 406 、電流供給線 407 、電極 411 、41

50

3などが形成されている。また、層間絶縁膜427上には、電極413に電気的に接続されている画素電極408が形成されている。画素電極408は周辺部が絶縁性の隔壁層428で囲まれている。画素電極408上にはEL層429が形成され、EL層429上には対向電極430が形成されている。補強板として対向基板431が設けられており、対向基板431は樹脂層432によりベース基板110に固定されている。

【0119】

EL表示装置の階調の制御は、発光素子の輝度を電流で制御する電流駆動方式と、電圧でその基礎を制御する電圧駆動方式とがあるが、電流駆動方式は、画素ごとでトランジスタの特性値の差が大きい場合、採用することは困難であり、そのためには特性のばらつきを補正する補正回路が必要になる。SOI基板の作製工程、およびゲッタリング工程を含む製造方法でEL表示を作製することで、選択用トランジスタ401および表示制御用トランジスタ402は画素ごとに特性のばらつきがなくなるため、電流駆動方式を採用することができる。

10

【0120】

つまり、SOI基板を用いることで、様々な電気機器を作製することができる。電気機器としては、ビデオカメラ、デジタルカメラ、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポなど）、コンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍など）、記録媒体を備えた画像再生装置（具体的にはDVD（d i g i t a l v e r s a t i l e d i s c）などの記録媒体に記憶された音声データを再生し、かつ記憶された画像データを表示しうる表示装置を備えた装置）などが含まれる。

20

【0121】

図12を用いて、電気機器の具体的な態様を説明する。図12（A）は携帯電話機901の一例を示す外観図である。この携帯電話機901は、表示部902、操作スイッチ903などを含んで構成されている。表示部902に、図10で説明した液晶表示装置または図11で説明したEL表示装置を適用することで、表示むらが少なく画質の優れた表示部902とすることができます。

【0122】

また、図12（B）は、デジタルプレーヤー911の構成例を示す外観図である。デジタルプレーヤー911は、表示部912、操作部913、イヤホン914などを含んでいる。イヤホン914の代わりにヘッドホンや無線式イヤホンを用いることができる。表示部912に、図10で説明した液晶表示装置または図11で説明したEL表示装置を適用することで、画面サイズが0.3インチから2インチ程度の場合であっても、高精細な画像および多量の文字情報を表示することができる。

30

【0123】

また、図12（C）は、電子ブック921の外観図である。この電子ブック921は、表示部922、操作スイッチ923を含んでいる。電子ブック921にはモデムを内蔵していてもよいし、図8のRFCPUを内蔵させて、無線で情報を送受信できる構成としてもよい。表示部922には、図10で説明した液晶表示装置、または図11で説明したEL表示装置を適用することで、高画質の表示を行うことができる。

40

【実施例1】

【0124】

本実施例では、ガラス基板に熱処理を行った場合の収縮率について説明する。

【0125】

まず、ガラス基板を用意し、当該ガラス基板上に所定の間隔を設けて複数のマーカーを形成した。続いて、ガラス基板に熱処理を行った後に、X軸方向とY軸方向の収縮した量（収縮量）をそれぞれ測定し、収縮率を求めた。

【0126】

ガラス基板としては、旭ガラス社製のガラス基板（商品名AN100）を用いた。また、ガラス基板として5インチ角の正方形状のものを用いた。なお、ガラス基板において、あ

50

る2辺に平行な方向をX軸方向とし、他の2辺に平行な方向をY軸方向とした。

【0127】

マーカーとしては、ガラス基板上に100nmの酸化窒化シリコン膜と50nmのアモルファスシリコン膜を順に積層した後、アモルファスシリコン膜を選択的に除去してパターンングされたアモルファスシリコン膜をガラス基板の四隅に設けた。

【0128】

X軸方向の収縮率は、マーカーに基づいて熱処理後のガラス基板のX軸方向における収縮量を測定した後に、当該収縮量をX軸方向における熱処理前のマーカー間距離で除して求めた。本実施例では、収縮率(ppm) = (収縮量(μm) / マーカー間距離(mm)) × 1000として求めた。なお、X軸方向におけるガラス基板の両端部(右端と左端)で求めた収縮率の平均をX軸方向の収縮率とした。また、Y軸方向の収縮率もX軸方向と同様に求めた。

10

【0129】

熱処理は、600で4時間行い、その後ガラス基板を冷却した。

【0130】

本実施例では、同様のガラス基板を4枚用意し、4枚の基板(基板A～基板D)について同じ条件で実験を行った。表1に基板A～基板Dにおける収縮率の測定結果を示す。

【0131】

【表1】

|     | X軸方向収縮率(ppm) | Y軸方向収縮率(ppm) | 収縮率平均(ppm) |

|-----|--------------|--------------|------------|

| 基板A | 168.4        | 177.2        | 172.8      |

| 基板B | 170.0        | 176.4        | 173.2      |

| 基板C | 167.8        | 174.0        | 170.9      |

| 基板D | 166.1        | 175.2        | 170.7      |

20

【0132】

試料A～試料Dのいずれのガラス基板においても、X軸方向の収縮率とY軸方向の収縮率との差が小さく、X軸方向とY軸方向における収縮率が平均値(X軸方向の収縮率とY軸方向の収縮率を平均した値)から10%以内であることが確認できた。

【図面の簡単な説明】

30

【0133】

【図1】本発明のSOI基板の作製方法の一例を示す図。

【図2】本発明のSOI基板の作製方法の一例を示す図。

【図3】本発明のSOI基板の作製方法の一例を示す図。

【図4】本発明のSOI基板の作製方法の一例を示す図。

【図5】本発明のSOI基板を用いた半導体装置の作製方法の一例を示す図。

【図6】本発明のSOI基板を用いた半導体装置の作製方法の一例を示す図。

【図7】本発明のSOI基板を用いた半導体装置の一例を示す図。

【図8】本発明のSOI基板を用いた半導体装置の一例を示す図。

【図9】本発明のSOI基板を用いた表示装置の一例を示す図。

40

【図10】本発明のSOI基板を用いた表示装置の一例を示す図。

【図11】本発明のSOI基板を用いた表示装置の一例を示す図。

【図12】本発明のSOI基板を用いた電子機器を示す図である。

【図13】熱処理前後におけるベース基板の収縮を示す図。

【符号の説明】

【0134】

101 半導体基板

102 絶縁層

103 剥離層

104 窒素含有層

50

|       |             |    |

|-------|-------------|----|

| 1 1 0 | ベース基板       |    |

| 1 2 1 | イオンビーム      |    |

| 1 2 2 | 単結晶半導体層     |    |

| 1 5 1 | 半導体層        |    |

| 1 5 2 | 半導体層        |    |

| 1 5 4 | 絶縁層         |    |

| 1 5 5 | ゲート電極       |    |

| 1 5 6 | ゲート電極       |    |

| 1 5 7 | 低濃度不純物領域    | 10 |

| 1 5 8 | チャネル形成領域    |    |

| 1 5 9 | 高濃度不純物領域    |    |

| 1 6 0 | チャネル形成領域    |    |

| 1 6 1 | サイドウォール絶縁層  |    |

| 1 6 5 | レジスト        |    |

| 1 6 7 | 高濃度不純物領域    |    |

| 1 6 8 | 絶縁層         |    |

| 1 6 9 | 層間絶縁層       |    |

| 1 7 0 | 配線          |    |

| 2 0 2 | 絶縁層         |    |

| 2 0 4 | 窒素含有層       | 20 |

| 3 0 1 | マザーガラス      |    |

| 3 0 2 | 単結晶半導体層     |    |

| 3 1 0 | 形成領域        |    |

| 3 1 1 | 形成領域        |    |

| 3 1 2 | 信号線駆動回路形成領域 |    |

| 3 1 3 | 画素形成領域      |    |

| 3 2 0 | 単結晶半導体層     |    |

| 3 2 2 | 走査線         |    |

| 3 2 3 | 信号線         |    |

| 3 2 4 | 画素電極        | 30 |

| 3 2 5 | TFT         |    |

| 3 2 7 | 層間絶縁膜       |    |

| 3 2 8 | 電極          |    |

| 3 2 9 | 柱状スペーサ      |    |

| 3 3 0 | 配向膜         |    |

| 3 3 2 | 対向基板        |    |

| 3 3 3 | 対向電極        |    |

| 3 3 4 | 配向膜         |    |

| 3 3 5 | 液晶層         |    |

| 3 4 0 | チャネル形成領域    | 40 |

| 3 4 1 | 高濃度不純物領域    |    |

| 4 0 1 | 選択用トランジスタ   |    |

| 4 0 2 | 表示制御用トランジスタ |    |

| 4 0 3 | 半導体層        |    |

| 4 0 4 | 半導体層        |    |

| 4 0 5 | 走査線         |    |

| 4 0 6 | 信号線         |    |

| 4 0 7 | 電流供給線       |    |

| 4 0 8 | 画素電極        |    |

| 4 1 0 | 電極          | 50 |

|       |               |    |

|-------|---------------|----|

| 4 1 1 | 電極            |    |

| 4 1 2 | ゲート電極         |    |

| 4 1 3 | 電極            |    |

| 4 2 7 | 層間絶縁膜         |    |

| 4 2 8 | 隔壁層           |    |

| 4 2 9 | E L 層         |    |

| 4 3 0 | 対向電極          |    |

| 4 3 1 | 対向基板          |    |

| 4 3 2 | 樹脂層           |    |

| 4 5 1 | チャネル形成領域      | 10 |

| 4 5 2 | 高濃度不純物領域      |    |

| 5 0 0 | マイクロプロセッサ     |    |

| 5 0 1 | 演算回路          |    |

| 5 0 2 | 演算回路制御部       |    |

| 5 0 3 | 命令解析部         |    |

| 5 0 4 | 制御部           |    |

| 5 0 5 | タイミング制御部      |    |

| 5 0 6 | レジスタ          |    |

| 5 0 7 | レジスタ制御部       |    |

| 5 0 8 | バスインターフェース    | 20 |

| 5 0 9 | 専用メモリ         |    |

| 5 1 0 | メモリインターフェース   |    |

| 5 1 1 | R F C P U     |    |

| 5 1 2 | アナログ回路部       |    |

| 5 1 3 | デジタル回路部       |    |

| 5 1 4 | 共振回路          |    |

| 5 1 5 | 整流回路          |    |

| 5 1 6 | 定電圧回路         |    |

| 5 1 7 | リセット回路        |    |

| 5 1 8 | 発振回路          | 30 |

| 5 1 9 | 復調回路          |    |

| 5 2 0 | 変調回路          |    |

| 5 2 1 | R F インターフェース  |    |

| 5 2 2 | 制御レジスタ        |    |

| 5 2 3 | クロックコントローラ    |    |

| 5 2 4 | C P Uインターフェース |    |

| 5 2 5 | 中央処理ユニット      |    |

| 5 2 6 | ランダムアクセスメモリ   |    |

| 5 2 7 | 専用メモリ         |    |

| 5 2 8 | アンテナ          | 40 |

| 5 2 9 | 容量部           |    |

| 5 3 0 | 電源管理回路        |    |

| 9 0 1 | 携帯電話機         |    |

| 9 0 2 | 表示部           |    |

| 9 0 3 | 操作スイッチ        |    |

| 9 1 1 | デジタルプレーヤー     |    |

| 9 1 2 | 表示部           |    |

| 9 1 3 | 操作部           |    |

| 9 1 4 | イヤホン          |    |

| 9 2 1 | 電子ブック         | 50 |

9 2 2 表示部

9 2 3 操作スイッチ

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

302 半導体層

310 表示パネル形成領域

311 走査線駆動回路形成領域

312 信号線駆動回路形成領域

313 画素形成領域

【図10】

【図11】

【図 1 2】

【図 1 3】

## フロントページの続き

(51) Int.Cl.

F I

テーマコード(参考)

H 01 L 21/336 (2006.01)

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

F ターム(参考) 5F110 BB02 BB04 CC02 DD02 DD06 DD07 DD13 DD14 DD15 DD17

EE32 GG02 GG03 GG04 GG12 GG32 HJ01 HJ13 HJ23 HL03

HL04 HL06 HL12 HM15 NN03 NN22 NN23 NN24 NN27 NN40

NN65 NN71 NN72 QQ11 QQ17 QQ19 QQ23

5F152 LM09 LP01 LP07 MM04 MM19 NN14 NP13 NP14 NQ03 NQ04

NQ05 NQ06