(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5514559号

(P5514559)

(45) 発行日 平成26年6月4日(2014.6.4)

(24) 登録日 平成26年4月4日(2014.4.4)

(51) Int.Cl.

F 1

|             |               |                  |

|-------------|---------------|------------------|

| <b>H05K</b> | <b>3/46</b>   | <b>(2006.01)</b> |

| <b>H01L</b> | <b>23/12</b>  | <b>(2006.01)</b> |

| <b>H01L</b> | <b>23/473</b> | <b>(2006.01)</b> |

|      |      |   |

|------|------|---|

| HO5K | 3/46 | L |

| HO5K | 3/46 | Q |

| HO5K | 3/46 | H |

| HO5K | 3/46 | U |

| HO5K | 3/46 | B |

請求項の数 16 (全 38 頁) 最終頁に続く

(21) 出願番号

特願2010-4394 (P2010-4394)

(22) 出願日

平成22年1月12日(2010.1.12)

(65) 公開番号

特開2011-146445 (P2011-146445A)

(43) 公開日

平成23年7月28日(2011.7.28)

審査請求日

平成24年12月27日(2012.12.27)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 荒井 直

長野県長野市小島田町80番地 新光電気

工業株式会社内

審査官 川内野 真介

最終頁に続く

(54) 【発明の名称】配線基板及びその製造方法並びに半導体パッケージ

## (57) 【特許請求の範囲】

## 【請求項 1】

積層された複数のセラミック層及び内部配線を備え、前記内部配線と電気的に接続された電極が一方の面から露出しているセラミック基板と、

主面に形成された配線パターンと、一端が前記配線パターンと電気的に接続され、他端が前記主面の反対面である裏面から露出しているビアフィルと、を含む配線層を備えたシリコン基板と、を有し、

前記シリコン基板の前記裏面は、前記セラミック基板の前記一方の面にポリマー層を介して接合され、

前記シリコン基板の前記ビアフィルは、前記ポリマー層を貫通し、前記セラミック基板の前記電極と直接接合されて一体的に設けられており、

前記シリコン基板には第1ビアホールが設けられ、

前記ポリマー層には前記第1ビアホールに連通する第2ビアホールが設けられ、

前記シリコン基板の主面及び前記第1ビアホールの内側面には酸化膜が設けられ、

前記ビアフィルは、前記シリコン基板及び前記ポリマー層の厚さ方向において、前記酸化膜及び前記ポリマー層と接している配線基板。

## 【請求項 2】

前記第1ビアホールの直径は、前記電極の前記一方の面からの露出面の直径よりも大きく、

前記第2ビアホールの直径は、前記電極の前記一方の面からの露出面の直径と同じとさ

10

20

れ、かつ、前記第1ビアホールの内側面に設けられた酸化膜の内側の直径と同じとされている請求項1記載の配線基板。

**【請求項3】**

前記各セラミック層のうち、前記シリコン基板から遠いセラミック層の熱膨張係数は、前記シリコン基板に近いセラミック層の熱膨張係数よりも大きい請求項1又は2記載の配線基板。

**【請求項4】**

前記各セラミック層は、アルミナコーチェライトを含有する請求項1乃至3の何れか一項記載の配線基板。

**【請求項5】**

前記各セラミック層は、それぞれ異なる量のアルミナコーチェライトを含有する請求項4記載の配線基板。

**【請求項6】**

前記シリコン基板の前記裏面側には、前記セラミック基板の前記一方の面を露出する中空部が設けられている請求項1乃至5の何れか一項記載の配線基板。

**【請求項7】**

前記中空部内の前記セラミック基板の前記一方の面には、MEMSデバイスが搭載されている請求項6記載の配線基板。

**【請求項8】**

前記中空部内の前記セラミック基板の前記一方の面には、コンデンサが搭載されている請求項6記載の配線基板。

**【請求項9】**

前記中空部は、冷媒が供給される冷媒流路である請求項6記載の配線基板。

**【請求項10】**

積層された複数のセラミック層及び内部配線を備え、前記内部配線と電気的に接続された電極が一方の面から露出しているセラミック基板を準備する第1工程と、

主面及び前記主面の反対面である裏面を有するシリコンからなる基板本体を準備し、前記セラミック基板の前記一方の面にポリマー層を介して前記基板本体の前記裏面を接合する第2工程と、

前記基板本体の前記主面に、前記電極と電気的に接続する配線層を形成する第3工程と、を有し、

前記第2工程は、主面及び前記主面の反対面である裏面を有するシリコンからなる基板本体を準備する第2A工程と、

前記基板本体の前記主面に酸化膜を形成するとともに、前記基板本体の前記電極に対応する位置に、内側面に酸化膜が形成されたビアホールを形成する第2B工程と、

前記セラミック基板の前記一方の面又は前記基板本体の前記裏面にポリマー層を形成する第2C工程と、

前記電極の位置と前記ビアホールの位置とを合わせて、前記セラミック基板の前記一方の面に前記ポリマー層を介して前記基板本体の前記裏面を接合する第2D工程と、を含み、

前記第3工程は、前記ビアホール内に露出する前記ポリマー層を除去し、前記ポリマー層に貫通孔を形成して前記電極を露出する第3A工程と、

前記酸化膜が形成された前記ビアホール及び前記貫通孔に導体を充填して前記電極と電気的に接続されたビアフィルを形成するとともに、前記基板本体の前記主面に前記ビアフィルと電気的に接続された配線パターンを形成して、前記ビアフィルと前記配線パターンとを含む前記配線層を形成する第3B工程と、を含み、

前記第3B工程では、前記基板本体及び前記ポリマー層の厚さ方向において、前記酸化膜及び前記ポリマー層と接するように前記ビアフィルを形成する配線基板の製造方法。

**【請求項11】**

前記第2B工程は、前記基板本体の前記主面の前記電極に対応する位置に凹部を形成す

10

20

30

40

50

る工程と、

前記基板本体の前記主面並びに前記凹部の内側面及び底面に酸化膜を形成する工程と、

前記基板本体を前記裏面側から研磨して薄型化して前記凹部を貫通させ、前記内側面に前記酸化膜が形成されたビアホールを形成する工程と、を有する請求項1\_0記載の配線基板の製造方法。

#### 【請求項 1\_2】

前記第1工程では、前記セラミック基板を複数個準備し、

前記第2工程では、前記基板本体に代えて、主面及び前記主面の反対面である裏面を有し、個片化されると前記基板本体となる複数の領域を有する第1基板を準備し、前記第1基板の前記裏面の前記複数の領域のそれぞれに、ポリマー層を介して前記セラミック基板の前記一方の面を接合し、10

前記第3工程では、前記第1基板の前記主面上に、前記電極と電気的に接続する配線層を形成し、

前記第3工程の後、前記第1基板の前記複数の領域のそれぞれにポリマー層を介して前記セラミック基板が接合された構造体を前記複数の領域間で切断して個片化し、前記基板本体にポリマー層を介して前記セラミック基板が接合され前記基板本体に前記電極と電気的に接続する前記配線層が形成された複数の配線基板を作製する請求項1\_0又は1\_1項記載の配線基板の製造方法。

#### 【請求項 1\_3】

前記第2工程は、主面及び前記主面の反対面である裏面を有し、個片化されると前記基板本体となる複数の領域を有する第1基板を準備する第2E工程と、20

前記第1基板の前記主面上に酸化膜を形成するとともに、前記第1基板の前記セラミック基板のそれぞれの前記電極に対応する位置に、内側面上に酸化膜が形成されたビアホールを形成する第2F工程と、

前記セラミック基板のそれぞれの前記一方の面又は前記第1基板の前記裏面にポリマー層を形成する第2G工程と、

前記セラミック基板のそれぞれの前記電極の位置と、対応する前記ビアホールの位置とを合わせて、前記第1基板の前記裏面の前記複数の領域のそれぞれに、前記ポリマー層を介して前記セラミック基板のそれぞれの前記一方の面を接合する第2H工程と、を有する請求項1\_2記載の配線基板の製造方法。30

#### 【請求項 1\_4】

前記第2F工程は、前記第1基板の前記主面上の前記電極に対応する位置に凹部を形成する工程と、

前記第1基板の前記主面並びに前記凹部の内側面及び底面上に酸化膜を形成する工程と、

前記第1基板を前記裏面側から研磨して薄型化して前記凹部を貫通させ、前記内側面上に前記酸化膜が形成されたビアホールを形成する工程と、を有する請求項1\_3記載の配線基板の製造方法。

#### 【請求項 1\_5】

前記第3工程は、前記ビアホール内に露出する前記ポリマー層を除去し、前記ポリマー層に貫通孔を形成して前記電極を露出する第3C工程と、40

前記酸化膜が形成された前記ビアホール及び前記貫通孔に導体を充填して前記電極と電気的に接続されたビアフィルを形成するとともに、前記第1基板の前記主面上に前記ビアフィルと電気的に接続された配線パターンを形成して、前記ビアフィルと前記配線パターンとを含む前記配線層を形成する第3D工程と、を有する請求項1\_3又は1\_4記載の配線基板の製造方法。

#### 【請求項 1\_6】

請求項1乃至9の何れか一項記載の配線基板の前記シリコン基板の前記主面上に半導体チップが搭載された半導体パッケージ。

#### 【発明の詳細な説明】

#### 【技術分野】

10

20

30

40

50

**【0001】**

本発明は、シリコンとセラミックとを有する配線基板及びその製造方法、並びに前記配線基板を有する半導体パッケージに関する。

**【背景技術】****【0002】**

従来より、配線基板上に、はんだバンプ等を介して半導体チップを搭載した半導体パッケージが知られている。このような半導体パッケージにおいて、配線基板は、半導体チップとマザーボード等の実装基板とを接続する際のインターポーラとして機能する。以下、図面を参照しながら、インターポーラとして機能する配線基板を有する従来の半導体パッケージについて例示する。

10

**【0003】**

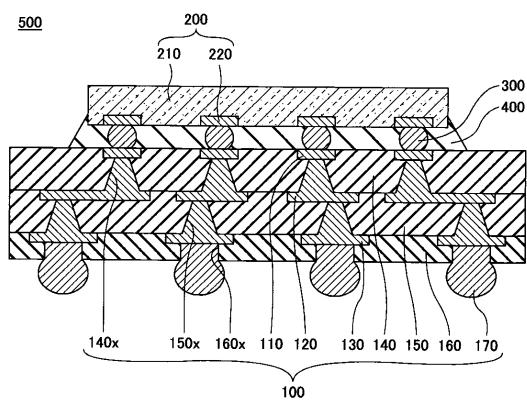

図1は、従来の半導体パッケージを例示する断面図である。図1を参照するに、半導体パッケージ500において、配線基板100の略中央部には、はんだバンプ300を介して半導体チップ200が実装され、アンダーフィル樹脂400で封止されている。

**【0004】**

配線基板100は、第1配線層110、第1絶縁層140、第2配線層120、第2絶縁層150、第3配線層130、ソルダーレジスト層160が順次積層された構造である。第1配線層110と第2配線層120とは、第1絶縁層140に設けられた第1ビアホール140×を介して電気的に接続されている。第2配線層120と第3配線層130とは、第2絶縁層150に設けられた第2ビアホール150×を介して電気的に接続されている。

20

**【0005】**

ソルダーレジスト層160の開口部160×内に露出する第3配線層130上には、はんだボール等の外部接続端子170が形成されている。第1配線層110は、半導体チップ200の電極パッド220と接続される電極パッドとして機能する。外部接続端子170は、マザーボード等の実装基板と接続される端子として機能する。なお、配線基板100は、配線幅やビアホール径等の制約により、多層になることが一般的である。

**【0006】**

半導体チップ200は、半導体基板210と、電極パッド220とを有する。半導体基板210は、例えばシリコン(Si)等からなる基板に半導体集積回路(図示せず)が形成されたものである。電極パッド220は、半導体基板210の一方の側に形成されており、半導体集積回路(図示せず)と電気的に接続されている。

30

**【0007】**

配線基板100の第1配線層110と半導体チップ200の電極パッド220とは、はんだバンプ300を介して電気的に接続されている。半導体チップ200と配線基板100の対向する面の間には、アンダーフィル樹脂400が充填されている。

**【0008】**

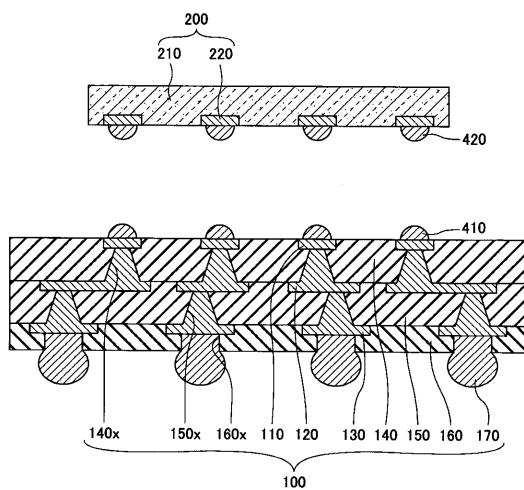

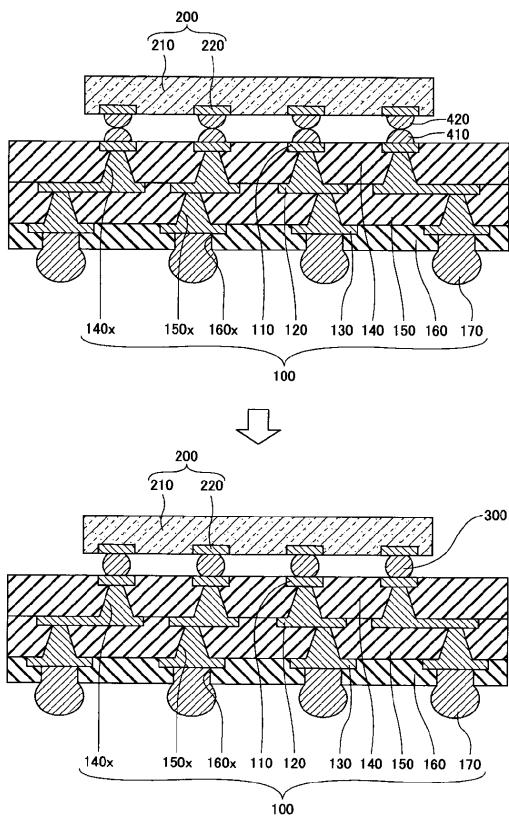

続いて、従来の半導体パッケージの製造方法について簡単に説明する。図2及び図3は、従来の半導体パッケージの製造工程を例示する図である。図2及び図3において、図1と同一部品については、同一符号を付し、その説明は省略する場合がある。

40

**【0009】**

始めに、図2に示す工程では、それぞれ周知の方法で作製された配線基板100と半導体チップ200とを用意する。配線基板100の第1配線層110上には、プレソルダー410が形成されている。半導体チップ200の電極パッド220上には、プレソルダー420が形成されている。

**【0010】**

次いで、図3に示す工程では、配線基板100の第1配線層110側と半導体チップ200の電極パッド220側とを対向させて、プレソルダー410と420とが対応する位置に来るよう配置する。そして、プレソルダー410と420を例えば230に加熱し、はんだを融解させることにより、はんだバンプ300を形成する。

50

**【0011】**

次いで、図3下側に示す構造において、半導体チップ200と配線基板100の対向する面の間にアンダーフィル樹脂400を充填することにより、図1に示す半導体チップ200を搭載した半導体パッケージ500が完成する。なお、アンダーフィル樹脂400の硬化収縮の影響により配線基板100に反りが生じるため、配線基板100にはある程度以上の厚さが必要である。

**【0012】**

半導体パッケージ500は、外部接続端子170を介してマザーボード等の実装基板と接続される。このように、半導体パッケージ500において、配線基板100は、半導体チップ200とマザーボード等の実装基板とを接続する際のインターポーザとして機能する。

10

**【先行技術文献】****【特許文献】****【0013】**

**【特許文献1】**特表2003-503855号公報

**【発明の概要】****【発明が解決しようとする課題】****【0014】**

しかしながら、ダウンサイジングの進化の中で、半導体チップの微細化が進んでいるため、半導体チップを搭載するインターポーザ側にも微細配線が要求され、図1に示すような従来の配線基板では対応が困難になりつつある。そこで、微細配線に対応可能なシリコンをベースとした多層構造のインターポーザが検討されているが、多層構造にするためには製造設備に対する投資額が大きくなり、製造コストが増大するという問題があった。

20

**【0015】**

本発明は、上記の点に鑑みてなされたものであり、製造コストの増大を抑制でき、かつ、微細配線に対応可能な配線基板及びその製造方法並びに前記配線基板を有する半導体パッケージを提供することを課題とする。

**【課題を解決するための手段】****【0016】**

本配線基板は、積層された複数のセラミック層及び内部配線を備え、前記内部配線と電気的に接続された電極が一方の面から露出しているセラミック基板と、主面に形成された配線パターンと、一端が前記配線パターンと電気的に接続され、他端が前記主面の反対面である裏面から露出しているビアフィルと、を含む配線層を備えたシリコン基板と、を有し、前記シリコン基板の前記裏面は、前記セラミック基板の前記一方の面上にポリマー層を介して接合され、前記シリコン基板の前記ビアフィルは、前記ポリマー層を貫通し、前記セラミック基板の前記電極と直接接合されて一体的に設けられており、前記シリコン基板には第1ビアホールが設けられ、前記ポリマー層には前記第1ビアホールに連通する第2ビアホールが設けられ、前記シリコン基板の主面及び前記第1ビアホールの内側面には酸化膜が設けられ、前記ビアフィルは、前記シリコン基板及び前記ポリマー層の厚さ方向において、前記酸化膜及び前記ポリマー層と接していることを要件とする。

30

**【0017】**

本配線基板の製造方法は、積層された複数のセラミック層及び内部配線を備え、前記内部配線と電気的に接続された電極が一方の面から露出しているセラミック基板を準備する第1工程と、主面及び前記主面の反対面である裏面を有するシリコンからなる基板本体を準備し、前記セラミック基板の前記一方の面上にポリマー層を介して前記基板本体の前記裏面を接合する第2工程と、前記基板本体の前記主面上に、前記電極と電気的に接続する配線層を形成する第3工程と、を有し、前記第2工程は、主面及び前記主面の反対面である裏面を有するシリコンからなる基板本体を準備する第2A工程と、前記基板本体の前記主面上に酸化膜を形成するとともに、前記基板本体の前記電極に対応する位置に、内側面に酸化膜が形成されたビアホールを形成する第2B工程と、前記セラミック基板の前記一方の面

40

50

又は前記基板本体の前記裏面にポリマー層を形成する第2C工程と、前記電極の位置と前記ビアホールの位置とを合わせて、前記セラミック基板の前記一方の面上に前記ポリマー層を介して前記基板本体の前記裏面を接合する第2D工程と、を含み、前記第3工程は、前記ビアホール内に露出する前記ポリマー層を除去し、前記ポリマー層に貫通孔を形成して前記電極を露出する第3A工程と、前記酸化膜が形成された前記ビアホール及び前記貫通孔に導体を充填して前記電極と電気的に接続されたビアフィルを形成するとともに、前記基板本体の前記主面上に前記ビアフィルと電気的に接続された配線パターンを形成して、前記ビアフィルと前記配線パターンとを含む前記配線層を形成する第3B工程と、を含み、前記第3B工程では、前記基板本体及び前記ポリマー層の厚さ方向において、前記酸化膜及び前記ポリマー層と接するように前記ビアフィルを形成することを要件とする。

10

#### 【0018】

本半導体パッケージは、本発明に係る配線基板の前記シリコン基板の前記主面上に半導体チップが搭載されることを要件とする。

#### 【発明の効果】

#### 【0019】

開示の技術によれば、製造コストの増大を抑制でき、かつ、微細配線に対応可能な配線基板及びその製造方法並びに前記配線基板を有する半導体パッケージを提供することができる。

#### 【図面の簡単な説明】

#### 【0020】

【図1】従来の半導体パッケージを例示する断面図である。

20

【図2】従来の半導体パッケージの製造工程を例示する図（その1）である。

【図3】従来の半導体パッケージの製造工程を例示する図（その2）である。

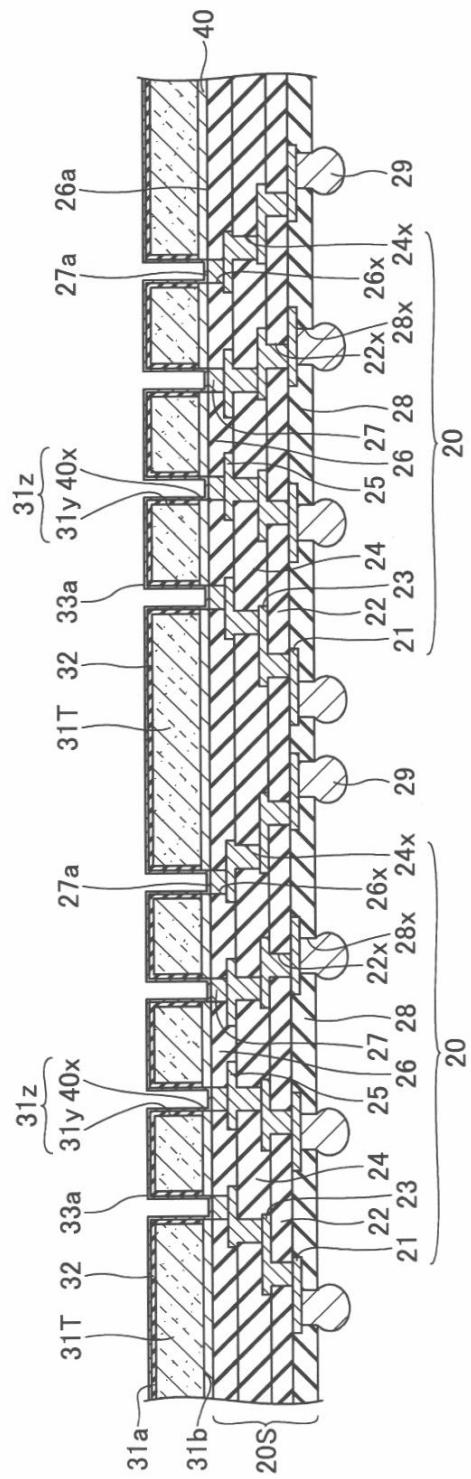

【図4】第1の実施の形態に係る配線基板を例示する断面図である。

【図5】第1の実施の形態に係る配線基板の製造工程を例示する図（その1）である。

【図6】第1の実施の形態に係る配線基板の製造工程を例示する図（その2）である。

【図7】第1の実施の形態に係る配線基板の製造工程を例示する図（その3）である。

【図8】第1の実施の形態に係る配線基板の製造工程を例示する図（その4）である。

【図9】第1の実施の形態に係る配線基板の製造工程を例示する図（その5）である。

【図10】第1の実施の形態に係る配線基板の製造工程を例示する図（その6）である。

30

【図11】第1の実施の形態に係る配線基板の製造工程を例示する図（その7）である。

【図12】第1の実施の形態に係る配線基板の製造工程を例示する図（その8）である。

【図13】第1の実施の形態に係る配線基板の製造工程を例示する図（その9）である。

【図14】第1の実施の形態に係る配線基板の製造工程を例示する図（その10）である

。

【図15】第1の実施の形態に係る配線基板の製造工程を例示する図（その11）である

。

【図16】第1の実施の形態に係る配線基板の製造工程を例示する図（その12）である

。

【図17】第1の実施の形態に係る配線基板の製造工程を例示する図（その13）である

40

。

【図18】第1の実施の形態に係る配線基板の製造工程を例示する図（その14）である

。

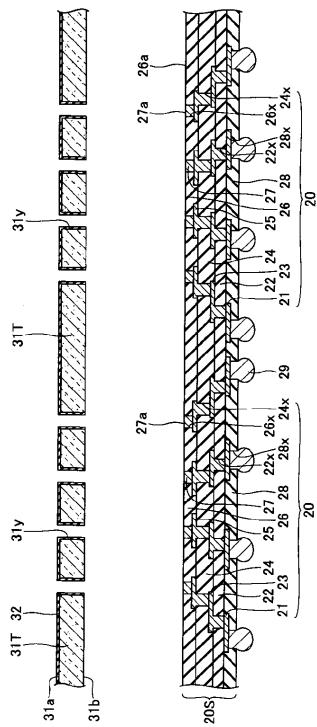

【図19】第2の実施の形態に係る配線基板の製造工程を例示する図（その1）である。

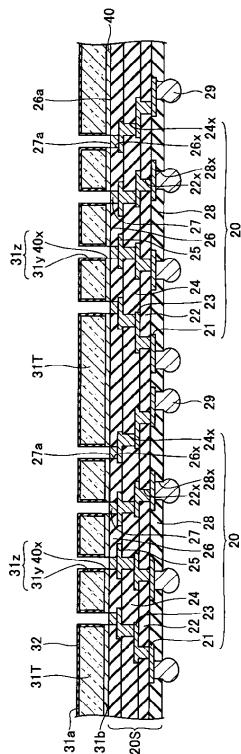

【図20】第2の実施の形態に係る配線基板の製造工程を例示する図（その2）である。

【図21】第2の実施の形態に係る配線基板の製造工程を例示する図（その3）である。

【図22】第2の実施の形態に係る配線基板の製造工程を例示する図（その4）である。

【図23】第2の実施の形態に係る配線基板の製造工程を例示する図（その5）である。

【図24】第3の実施の形態に係る半導体パッケージを例示する断面図である。

【図25】第3の実施の形態に係る半導体パッケージの製造工程を例示する図（その1）

50

である。

【図26】第3の実施の形態に係る半導体パッケージの製造工程を例示する図(その2)である。

【図27】第3の実施の形態の変形例1に係る半導体パッケージを例示する断面図である。

【図28】第3の実施の形態の変形例2に係る半導体パッケージを例示する断面図である。

【図29】第3の実施の形態の変形例3に係る半導体パッケージを例示する断面図である。

【発明を実施するための形態】

10

【0021】

以下、図面を参照して発明を実施するための形態について説明する。

【0022】

第1の実施の形態

[第1の実施の形態に係る配線基板の構造]

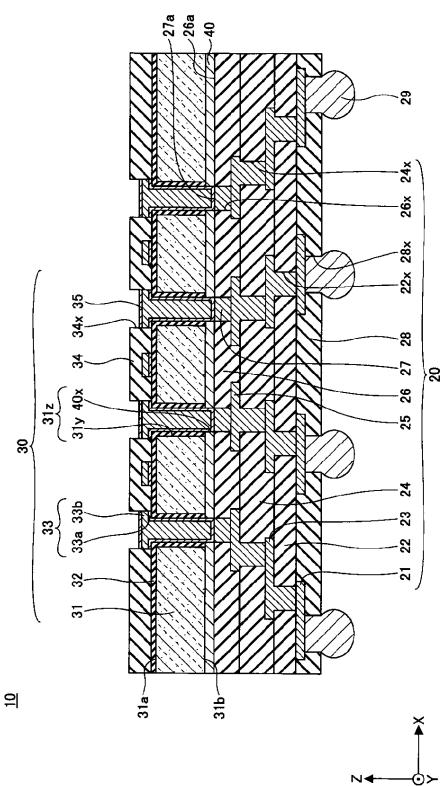

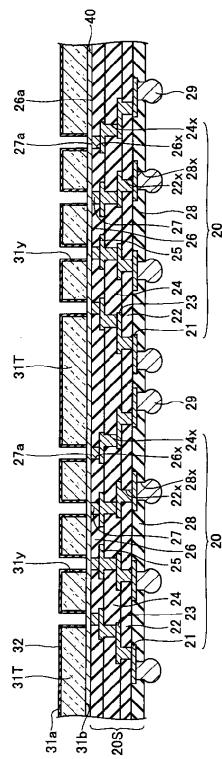

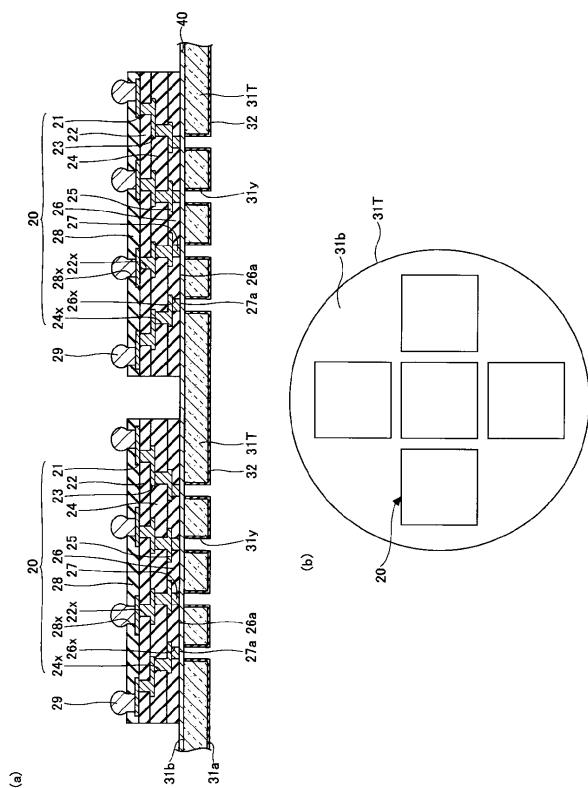

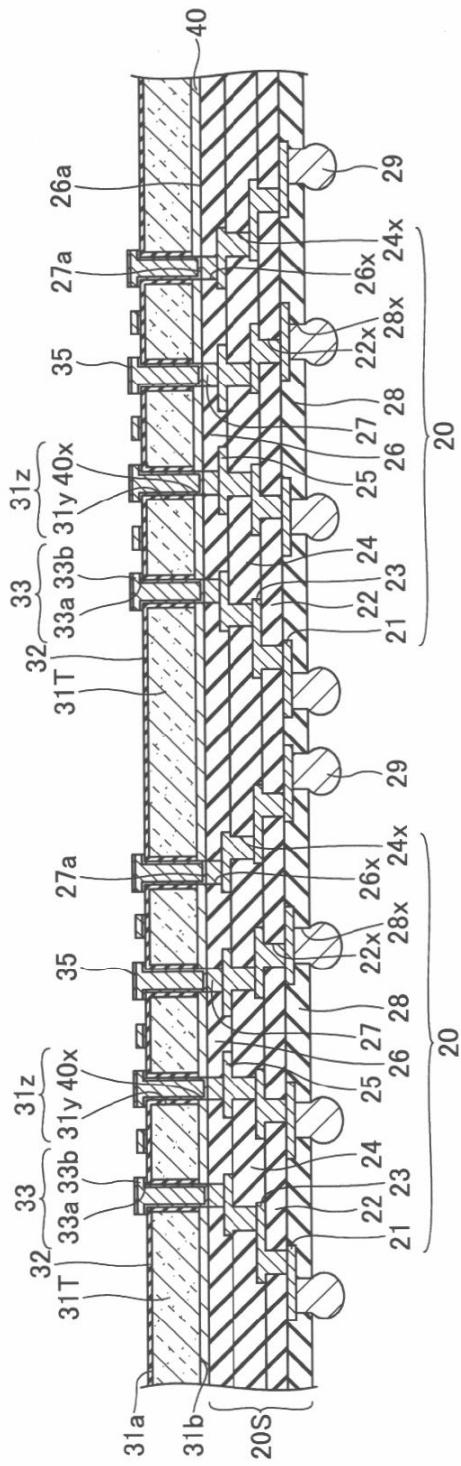

図4は、第1の実施の形態に係る配線基板を例示する断面図である。図4を参照するに、配線基板10は、セラミック基板20上にポリマー層40を介してシリコン基板30が接合された構造(所謂ポリマー接合)を有し、セラミック基板20には外部接続端子29が設けられている。

【0023】

20

配線基板10の平面形状は例えば矩形状であり、その寸法は、例えば幅15mm(X方向)×奥行き15mm(Y方向)程度とすることができる。セラミック基板20の厚さ(Z方向)は、例えば50~1000μm程度とすることができる。シリコン基板30の厚さ(Z方向)は、例えば50~500μm程度とすることができる。ポリマー層40の厚さ(Z方向)は、例えば5~20μm程度とすることができる。以下、セラミック基板20、外部接続端子29、シリコン基板30、及びポリマー層40について詳説する。

【0024】

30

セラミック基板20は、第1配線層21と、第1セラミック層22と、第2配線層23と、第2セラミック層24と、第3配線層25と、第3セラミック層26と、電極27と、ソルダーレジスト層28とを有する。セラミック基板20において、第1セラミック層22、第2セラミック層24、及び第3セラミック層26は、絶縁層として用いられている。セラミック基板20は、所謂L T C C (Low Temperature Co-fire Ceramic)と呼ばれる低温同時焼結セラミック多層基板である。但し、セラミック基板20として、所謂H T C C (High Temperature Co-fire Ceramic)と呼ばれる高温同時焼結セラミック多層基板等を用いても構わない。

【0025】

40

所謂L T C Cは、所謂H T C Cに比べて薄型化が可能である。又、所謂L T C Cは900程度の低温で焼成するため、電極や配線層の材料として銅(Cu)、銀(Ag)、金(Au)等の融点が低く導電率の高い材料を用いることが可能であり、配線抵抗を小さくすることができる。但し、所謂L T C Cは、所謂H T C Cに比べて酸やアルカリに弱く、所謂H T C Cに比べて低剛性である。

【0026】

一方、所謂H T C Cは、所謂L T C Cに比べて薄型化が困難である。又、所謂H T C Cは、1600程度の高温で焼成するため、電極や配線層の材料として銅(Cu)、銀(Ag)、金(Au)等の融点が低く導電率の高い材料を用いることはできず、タンゲステンやモリブデン等の融点が高く導電率の低い材料を用いる必要があり、配線抵抗を小さくすることができない。但し、所謂H T C Cは、所謂L T C Cに比べて酸やアルカリに強く、所謂L T C Cに比べて高剛性である。

【0027】

このように、所謂L T C Cと所謂H T C Cとは互いに異なる特徴を有するため、用途に

50

応じて何れか適切な方を選定すればよい。本実施の形態では、セラミック基板 20 として、所謂 L T C C を用いる場合を例に以下の説明を行う。

#### 【 0 0 2 8 】

第 1 配線層 21 は、第 1 セラミック層 22 の一方の面に形成されている。第 1 配線層 21 の材料としては、例えば銅 (Cu) 等を用いることができる。第 1 配線層 21 の材料として、銀 (Ag) や金 (Au) 等を用いても構わない。第 1 配線層 21 の厚さは、例えば 5 μm 程度とすることができます。

#### 【 0 0 2 9 】

第 1 セラミック層 22 の材料としては、例えば酸化ナトリウム (Na<sub>2</sub>O)、酸化アルミニウム (Al<sub>2</sub>O<sub>3</sub>)、酸化ホウ素 (B<sub>2</sub>O<sub>3</sub>)、二酸化珪素 (SiO<sub>2</sub>) を含むガラスにアルミナコーチェライトを添加したもの等を用いることができる。第 1 セラミック層 22 の厚さは、例えば 10 μm 程度とすることができます。10

#### 【 0 0 3 0 】

ここで、コーチェライトとは、酸化マグネシウム (MgO) と酸化アルミニウム (Al<sub>2</sub>O<sub>3</sub>) と二酸化珪素 (SiO<sub>2</sub>) とを含む化合物であり、組成の一例として 2MgO · 2Al<sub>2</sub>O<sub>3</sub> · 5SiO<sub>2</sub> を挙げることができる。又、アルミナコーチェライトとは、コーチェライトに酸化アルミニウム (Al<sub>2</sub>O<sub>3</sub>) を配合したものである。

#### 【 0 0 3 1 】

第 2 配線層 23 は、第 1 セラミック層 22 の他方の面に形成されている。第 2 配線層 23 は、第 1 セラミック層 22 を貫通し第 1 配線層 21 の上面を露出する第 1 ビアホール 22 × 内に充填されたビアフィル、及び第 1 セラミック層 22 上に形成された配線パターンを含んで構成されている。第 2 配線層 23 は、第 1 ビアホール 22 × 内に露出した第 1 配線層 21 と電気的に接続されている。第 2 配線層 23 の材料としては、例えば銅 (Cu) 等を用いることができる。第 2 配線層 23 の材料として、銀 (Ag) や金 (Au) 等を用いても構わない。第 2 配線層 23 を構成する配線パターンの厚さは、例えば 5 μm 程度とすることができます。20

#### 【 0 0 3 2 】

第 2 セラミック層 24 は、第 1 セラミック層 22 上に、第 2 配線層 23 を覆うように形成されている。第 2 セラミック層 24 の材料としては、例えば酸化ナトリウム (Na<sub>2</sub>O)、酸化アルミニウム (Al<sub>2</sub>O<sub>3</sub>)、酸化ホウ素 (B<sub>2</sub>O<sub>3</sub>)、二酸化珪素 (SiO<sub>2</sub>) を含むガラスにアルミナコーチェライトを添加したもの等を用いることができる。第 2 セラミック層 24 の厚さは、例えば 10 μm 程度とすることができます。30

#### 【 0 0 3 3 】

第 3 配線層 25 は、第 2 セラミック層 24 上に形成されている。第 3 配線層 25 は、第 2 セラミック層 24 を貫通し第 2 配線層 23 の上面を露出する第 2 ビアホール 24 × 内に充填されたビアフィル、及び第 2 セラミック層 24 上に形成された配線パターンを含んで構成されている。第 3 配線層 25 は、第 2 ビアホール 24 × 内に露出した第 2 配線層 23 と電気的に接続されている。第 3 配線層 25 の材料としては、例えば銅 (Cu) 等を用いることができる。第 3 配線層 25 の材料として、銀 (Ag) や金 (Au) 等を用いても構わない。第 3 配線層 25 を構成する配線パターンの厚さは、例えば 5 μm 程度とすることができます。40

#### 【 0 0 3 4 】

第 3 セラミック層 26 は、第 2 セラミック層 24 上に、第 3 配線層 25 を覆うように形成されている。第 3 セラミック層 26 の材料としては、例えば酸化ナトリウム (Na<sub>2</sub>O)、酸化アルミニウム (Al<sub>2</sub>O<sub>3</sub>)、酸化ホウ素 (B<sub>2</sub>O<sub>3</sub>)、二酸化珪素 (SiO<sub>2</sub>) を含むガラスにアルミナコーチェライトを添加したもの等を用いることができる。第 3 セラミック層 26 の厚さは、例えば 10 μm 程度とすることができます。

#### 【 0 0 3 5 】

なお、アルミナコーチェライトの添加量を変えることにより、第 1 セラミック層 22、第 2 セラミック層 24、及び第 3 セラミック層 26 の CTE (Coefficient of thermal 50

expansion、熱膨張率)を調整することができる。第1セラミック層22、第2セラミック層24、及び第3セラミック層26のCTEを調整する技術的な意義については、後述する。

#### 【0036】

電極27は、第3セラミック層26を貫通し第3配線層25の上面を露出する第3ビアホール26x内に充填されたビアフィルを含んで構成されている。電極27の面27aは、第3セラミック層26の面26aと略面一とされている。つまり、電極27の面27aは、第3セラミック層26の面26aから露出している。電極27は、第3ビアホール26x内に露出した第3配線層25と電気的に接続されている。電極27の材料としては、例えば銅(Cu)等を用いることができる。電極27の材料として、銀(Ag)や金(Au)等を用いても構わない。電極27の厚さは、例えば5μm程度とすることができる。10

#### 【0037】

ソルダーレジスト層28は、第1セラミック層22の一方の面上に、第1配線層21を覆うように形成されている。ソルダーレジスト層28は開口部28xを有し、第1配線層21の一部はソルダーレジスト層28の開口部28x内に露出している。ソルダーレジスト層28の材料としては、例えばエポキシ系樹脂やイミド系樹脂等を含む感光性樹脂組成物等を用いることができる。ソルダーレジスト層28の厚さは、例えば15μm程度とすることができる。

#### 【0038】

必要に応じ、開口部28x内に露出する第1配線層21上に、金属層等を形成してもよい。金属層の例としては、Au層や、Ni/Au層(Ni層とAu層をこの順番で積層した金属層)、Ni/Pd/Au層(Ni層とPd層とAu層をこの順番で積層した金属層)等を挙げることができる。20

#### 【0039】

外部接続端子29は、セラミック基板20のソルダーレジスト層28の開口部28x内に露出する第1配線層21上に(第1配線層21上に金属層等が形成されている場合には、金属層等の上に)形成されている。

#### 【0040】

平面視において、外部接続端子29の形成されている領域は、後述する開口部34x内に露出している配線層33(半導体チップと接続される電極パッドとして機能する)の形成されている領域の周囲に拡張されている。つまり、半導体チップが接続される領域の周囲にも外部接続端子29が位置するように、第1配線層21~第3配線層25を引き回している。このように、配線基板10は、所謂ファンアウト構造を有する。30

#### 【0041】

隣接する外部接続端子29のピッチは、隣接する開口部34x内に露出している配線層33のピッチ(例えば80μm程度)よりも拡大することが可能となり、例えば400μm程度とすることができます。但し、配線基板10は、目的に応じて所謂ファンイン構造を有しても構わない。

#### 【0042】

外部接続端子29は、マザーボード等の実装基板(図示せず)に設けられたパッドと電気的に接続される端子として機能する。外部接続端子29としては、例えば、はんだボール等を用いることができる。はんだボールの材料としては、例えばPbを含む合金、SnとCuの合金、SnとAgの合金、SnとAgとCuの合金等を用いることができる。なお、外部接続端子29として、リードピンを用いても構わない。40

#### 【0043】

但し、第1の実施の形態では外部接続端子29を形成しているが、外部接続端子29は必ずしも形成する必要はない。要は、必要なときに外部接続端子29等を形成できるように、第1配線層21の一部がソルダーレジスト層28から露出し、パッドとして用いることができるようになれば十分である。

#### 【0044】

10

20

30

40

50

シリコン基板30は、セラミック基板20上にポリマー層40を介して接合（所謂ポリマー接合）されている。ポリマー層40の材料としては、例えばベンゾシクロブテン（B C B）、ポリベンゾオキサゾール（P B O）、ポリイミド（P I）等のポリマー性の絶縁樹脂を用いることができる。これらの絶縁樹脂は、半導体プロセスにおいて実績のある材料であるとともに、350<sup>10</sup>を超える耐熱温度を有する点で好適である。

#### 【0045】

シリコン基板30は、基板本体31と、絶縁層32と、第1金属層33aと第2金属層33bとを含む配線層33と、ガイドレジスト層34と、第3金属層35とを有する。

#### 【0046】

基板本体31は、シリコンから構成されている。基板本体31の厚さは、例えば50～500<sup>10</sup>μm程度とすることができます。ビアホール31zは、基板本体31の面31a（正面）から面31b（裏面）に貫通するビアホール31y及びポリマー層40を貫通するビアホール40xからなり、セラミック基板20の電極27の面27aを露出する貫通孔である。ビアホール31zの配設ピッチは、適宜選択することが可能であるが、例えば80μm程度とすることができます。ビアホール31zは、例えば平面視において（基板本体31の面31a又は31b側から見て）円形であり、その直径は、例えば10～200μm程度とすることができます。

#### 【0047】

絶縁層32は、基板本体31の面31a及びビアホール31yの内側面に形成されている。絶縁層32は、基板本体31と配線層33との間を絶縁するための膜である。<sup>20</sup>絶縁層32としては、熱酸化膜（SiO<sub>2</sub>）を用いることができる。絶縁層32の厚さは、例えば1～2μm程度とすることができます。

#### 【0048】

配線層33は、第1金属層33aと第2金属層33bとを含んで構成されている。配線層33は、ビアホール31z（絶縁層32が形成されたビアホール31y及びビアホール40x）に充填されたビアフィル、及び基板本体31の面31aに絶縁層32を介して形成された配線パターンを含んで構成されている。配線層33は、セラミック基板20の電極27と電気的に接続されている。

#### 【0049】

なお、本実施の形態では、ビアホール31yの直径を電極27の面27aの直径よりも大きくし、ビアホール40xの直径を電極27の面27aの直径と同程度として、電極27の面27aがビアホール40xの底面部分に露出する配線層33のみと接するようにしている。又、この際、ビアホール31y及びビアホール40xの中心軸と電極27の面27aの中心軸を一致させるようにしている。しかしながら、必ずしもこのような構造には限定されない。

#### 【0050】

配線層33は、シリコンから構成された基板本体31に半導体プロセスにより形成可能であるため、超微細なビアホール及び超微細な配線パターンとすることができます。配線層33を構成する配線パターンは、例えばライン／スペース=1／1μm～10／10μm程度とすることができます。配線層33を構成する配線パターンの厚さは、例えば1～10μm程度（ライン／スペース=1／1μm～10／10μm程度の場合）とすることができます。

#### 【0051】

ガイドレジスト層34は、基板本体31の面31aに形成された絶縁層32上に、配線層33を覆うように形成されている。ガイドレジスト層34は開口部34xを有し、配線層33の一部はガイドレジスト層34の開口部34x内に露出している。開口部34x内に露出している配線層33は、半導体チップと接続される電極パッドとして機能する。ガイドレジスト層34の材料としては、例えばベンゾシクロブテン（B C B）、ポリベンゾオキサゾール（P B O）、ポリイミド（P I）等の絶縁樹脂を用いることができる。ガイドレジスト層34の材料として、エポキシ系樹脂やイミド系樹脂等を含む感光性樹脂組成

10

20

30

40

50

物等を用いても構わない。ガイドレジスト層34の厚さは、例えば5～30μm程度とすることができる。

#### 【0052】

第3金属層35は、ガイドレジスト層34の開口部34x内に露出する配線層33上に形成されている。第3金属層35は、開口部34x内に露出している配線層33が半導体チップと接続される際の接続信頼性を向上するために設けられている。従って、ガイドレジスト層34に覆われている配線層33上には第3金属層35を形成しなくても構わない。第3金属層35の例としては、Au層や、Ni/Au層(Ni層とAu層をこの順番で積層した金属層)、Ni/Pd/Au層(Ni層とPd層とAu層をこの順番で積層した金属層)等を挙げることができる。又、第3金属層35の他の例としては、例えばSnAgやSnAgCu等のはんだめつきを挙げができる。但し、仕様によっては、ガイドレジスト層34の開口部34x内に露出する配線層33上に第3金属層35を形成しなくても構わない。10

#### 【0053】

このように、配線基板10は、半導体チップ(図示せず)とマザーボード等の実装基板(図示せず)とを接続するインターポーラとしての機能を有する。ところで、シリコン基板30のCTEは、略3ppm/℃程度である。又、シリコン基板30側に接続される半導体チップがシリコンである場合のCTEも、略3ppm/℃程度である。このように、半導体チップとシリコン基板30のCTEが略一致しているため、半導体チップとシリコン基板30とを接続する際等に加熱されても、CTEの違いに起因する熱応力(ストレス)が半導体チップとシリコン基板30との接続部に生じ難い。そのため、半導体チップとシリコン基板30との接続信頼性を高めることができる。20

#### 【0054】

一方、セラミック基板20とシリコン基板30との間にはポリマー層40が存在しているため、セラミック基板20のCTEをシリコン基板30のCTE(3ppm/℃程度)に合わせ込まなくても構わない。セラミック基板20とシリコン基板30とを接続する際等に加熱されても、ポリマー層40がCTEの違いに起因する熱応力(ストレス)を吸収するため、セラミック基板20とシリコン基板30との接続部には熱応力(ストレス)が生じ難い。そのため、セラミック基板20のCTEをシリコン基板30のCTE(3ppm/℃程度)に合わせ込まなくても、セラミック基板20とシリコン基板30との接続信頼性を確保することができる。30

#### 【0055】

セラミック基板20のCTEをシリコン基板30のCTE(3ppm/℃程度)に合わせ込まなくても問題がないこと、及び、セラミック基板20側に接続される主に樹脂基板からなるマザーボード等の実装基板のCTEが略18ppm/℃程度であることを考慮すると、シリコン基板30とマザーボード等の実装基板との間に配置されるセラミック基板20のCTEは、10ppm/℃～12ppm/℃程度とすることが好ましい。なお、前述のように、各セラミック層のCTEは、アルミナコーデライトの添加量を変えることにより調整することができる。

#### 【0056】

このように、セラミック基板20とシリコン基板30とをポリマー層40を介して接合(所謂ポリマー接合)することにより、セラミック基板20のCTEをシリコン基板30のCTE(3ppm/℃程度)に合わせ込まなくても、セラミック基板20とシリコン基板30との接続信頼性を確保することができる。又、セラミック基板20のCTEを主に樹脂基板からなるマザーボード等の実装基板のCTE(略18ppm/℃程度)に近い値(10ppm/℃～12ppm/℃程度)とすることにより、セラミック基板20とマザーボード等の実装基板との接続信頼性を確保することができる。40

#### 【0057】

但し、セラミック基板20とマザーボード等の実装基板との接続信頼性をより高めたい場合には、セラミック基板20において、シリコン基板30側からマザーボード等の実装50

基板側に近づくにつれて CTE を徐々に増加させることもできる。一例を挙げれば、シリコン基板 30 に最も近い第 3 セラミック層 26 の CTE は 10 ppm / ~ 12 ppm / 程度とし、マザーボード等の実装基板に最も近い第 1 セラミック層 22 の CTE は 15 ppm / ~ 17 ppm / 程度とし、その中間に配置される第 2 セラミック層 24 の CTE は 13 ppm / ~ 14 ppm / 程度とするが如くである。

#### 【0058】

このように、セラミック基板 20においてシリコン基板 30 側からマザーボード等の実装基板側に近づくにつれて CTE を徐々に増加させて、マザーボード等の実装基板の CTE とマザーボード等の実装基板に最も近い第 1 セラミック層 22 の CTE とを略一致させると、マザーボード等の実装基板とセラミック基板 20 とを接続する際等に加熱されても、CTE の違いに起因する熱応力（ストレス）がマザーボード等の実装基板とセラミック基板 20との接続部に生じ難い。そのため、セラミック基板 20 とマザーボード等の実装基板との接続信頼性をより一層高めることができる。10

#### 【0059】

又、同様の理由により、セラミック基板 20 内にも CTE の違いに起因する熱応力（ストレス）が生じ難いため、各接続部の接続信頼性を高めることができる。

#### 【0060】

以上が、セラミック基板 20 及びシリコン基板 30 を有する配線基板 10 の構造である。20

#### 【0061】

##### [第 1 の実施の形態に係る配線基板の製造方法]

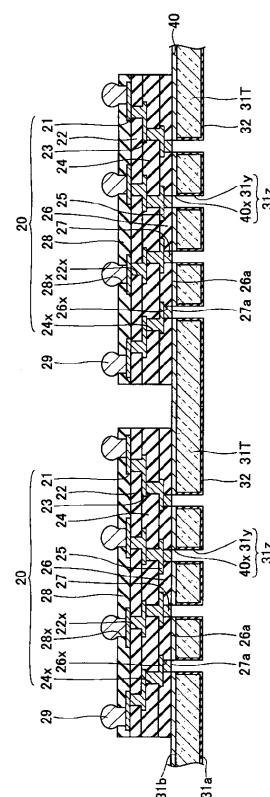

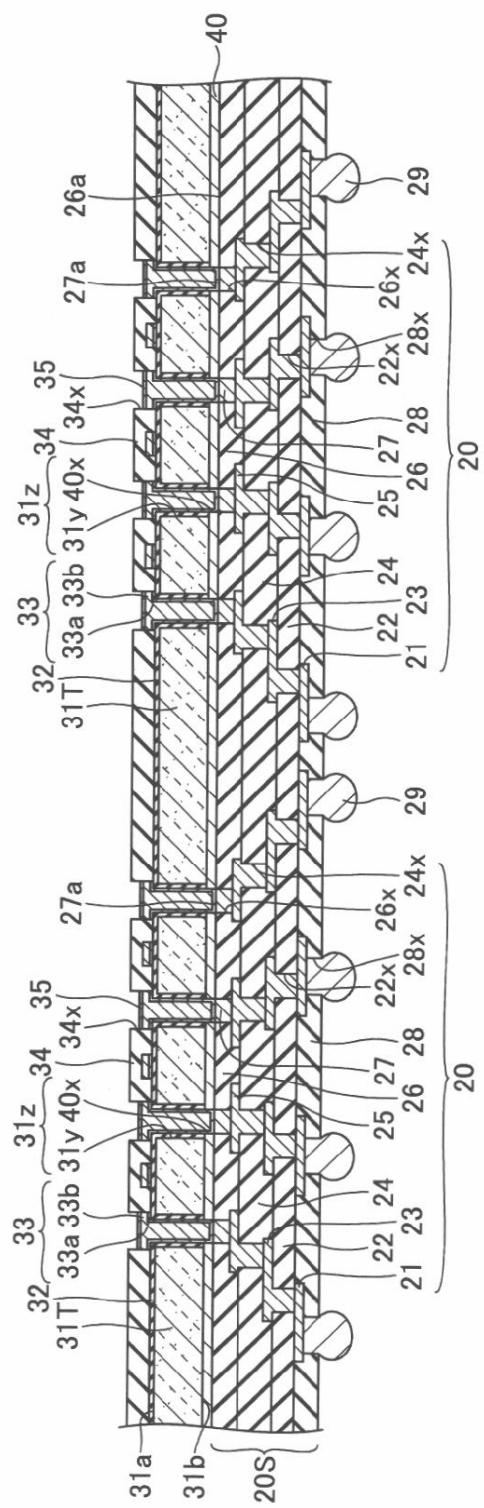

続いて、第 1 の実施の形態に係る配線基板の製造方法について説明する。図 5 ~ 図 18 は、第 1 の実施の形態に係る配線基板の製造工程を例示する図である。図 5 ~ 図 18 において、図 4 と同一部分については、同一符号を付し、その説明は省略する場合がある。

#### 【0062】

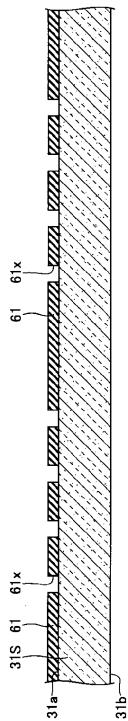

始めに、図 5 に示す工程では、基板本体 31S を準備し、基板本体 31S の面 31a に、セラミック基板 20S の電極 27 に対応する開口部 61x を有するレジスト層 61 を形成する。基板本体 31S は、最終的に個片化されて基板本体 31（図 4 参照）となる複数の領域を有する基板である。基板本体 31S としては、例えば薄型化されていない 6 インチ（約 150 mm）、8 インチ（約 200 mm）、12 インチ（約 300 mm）等のシリコンウェハ等を用いることができる。基板本体 31S の厚さは、例えば 0.625 mm（6 インチの場合）、0.725 mm（8 インチの場合）、0.775 mm（12 インチの場合）等とすることができます。但し、基板本体 31S は、シリコンウェハ等の平面形状が円形の基板でなくても良く、例えば平面形状が矩形の基板であっても構わない。30

#### 【0063】

レジスト層 61 を形成するには、基板本体 31S の面 31a に、例えばエポキシ系樹脂やイミド系樹脂等を含む感光性樹脂組成物からなる液状又はペースト状のレジストを塗布する。或いは、基板本体 31S の面 31a に、例えばエポキシ系樹脂やイミド系樹脂等を含む感光性樹脂組成物からなるフィルム状のレジストをラミネートする。そして、塗布又はラミネートしたレジストを露光、現像することで開口部 61x を形成する。これにより、開口部 61x を有するレジスト層 61 が形成される。なお、予め開口部 61x を形成したフィルム状のレジストを基板本体 31S の面 31a にラミネートしても構わない。40

#### 【0064】

開口部 61x は電極 27 に対応する位置に形成されるが、その配設ピッチは、例えば 80 μm 程度とすることができます。開口部 61x は、例えば平面視において（基板本体 31S の面 31a 又は 31b 側から見て）円形であり、その直径は、例えば 10 ~ 200 μm 程度とすることができます。なお、本実施の形態では、開口部 61x の直径は、電極 27 の面 27a の直径よりも大きくしている。

#### 【0065】

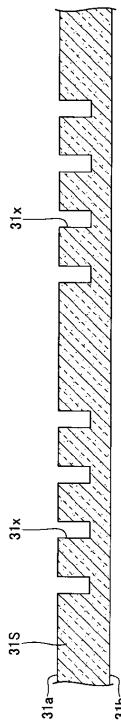

次いで、図 6 に示す工程では、図 5 に示すレジスト層 61 をマスクとして基板本体 31

Sをエッティングすることにより、凹部31xを形成する。そして、図5に示すレジスト層61を除去する。これにより、セラミック基板20Sの電極27に対応する位置に凹部31xが形成される。凹部31xは、例えばSF<sub>6</sub>を用いた反応性イオンエッティング(DRIE: Deep Reactive Ion Etch)等の異方性エッティング法により形成することができる。

凹部31xの配設ピッチは、開口部61xの配設ピッチに対応し、例えば80μm程度とすることができる。凹部31xは、例えば平面視において(基板本体31Sの面31a側から見て)円形であり、その直径は、開口部61xの直径に対応し、例えば10~200μm程度とすることができます。凹部31xの深さは、後述する図8に示す工程で、貫通孔(ピアホール31y)が形成できる程度とする。

#### 【0066】

10

次いで、図7に示す工程では、基板本体31Sの面31a並びに凹部31xの内側面及び底面に、絶縁層32を形成する。絶縁層32としては、熱酸化膜(SiO<sub>2</sub>)を用いることができる。絶縁層32は、基板本体31Sの表面近傍の温度を例えば1000以上とするウェット熱酸化法により熱酸化することで形成することができる。絶縁層32の厚さは、例えば1~2μm程度とすることができます。

#### 【0067】

このように、絶縁層32をウェット熱酸化法等の熱酸化法で形成することにより、絶縁材料をスピンドルコート法等で塗布する場合に比べて製造工程を簡略化することが可能となり、配線基板10の製造コストを低減することができる。又、ウェット熱酸化法による絶縁層32の形成は、ドライ熱酸化法による絶縁層32の形成に比べて膜厚を厚くすることができる点で好適である。

20

#### 【0068】

但し、絶縁特性をより向上させたい場合や挿入損出を低減させたい場合には、スピンドルコート法等によりベンゾシクロブテン(BCB)等からなる絶縁層を形成する方が好ましい。スピンドルコート法等により形成されたベンゾシクロブテン(BCB)等からなる絶縁層は、熱酸化法により形成された絶縁層32よりも厚くすることが可能である。絶縁層を厚くすることにより、基板本体31Sと配線層33との間の静電容量を小さくすることが可能となり、挿入損出を低減させることができる。

#### 【0069】

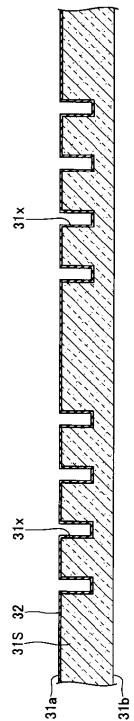

次いで、図8に示す工程では、基板本体31Sを面31b側から研磨又は研削して基板本体31Sを薄型化する。基板本体31Sの薄型化により、図7に示す凹部31xは貫通し、セラミック基板20Sの電極27に対応する位置に、内側面が絶縁層32で被覆されたピアホール31yが形成される。基板本体31Sの薄型化には、例えばバックサイドグラインダー等を用いることができる。以降、薄型化後の基板本体31Sを基板本体31Tと称する。基板本体31Tの厚さは、例えば50~500μm程度とすることができます。なお、基板本体31Sを薄型化した後、研磨又は研削した面(基板本体31Tの面31b)に、熱酸化法等により絶縁層を設けても良い。

30

#### 【0070】

次いで、図9に示す工程では、セラミック基板20Sを準備する。セラミック基板20Sは、最終的に個片化されてセラミック基板20(図4参照)となる複数の領域を有する基板である。セラミック基板20Sは、所謂LTC(C)(Low Temperature Co-fire Ceramic)と呼ばれる低温同時焼結セラミック多層基板である。なお、セラミック基板20Sには外部接続端子29が形成されているが、必ずしもこの時点で形成されていなくてもよく、必要な時に形成すればよい。

40

#### 【0071】

セラミック基板20Sの有する各セラミック層の材料としては、例えば酸化ナトリウム(Na<sub>2</sub>O)、酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)、酸化ホウ素(B<sub>2</sub>O<sub>3</sub>)、二酸化珪素(SiO<sub>2</sub>)を含むガラスにアルミナコーティングを添加したもの等を用いることができる。セラミック基板20Sの平面形状は例えば円形と/orすることができ、その直径は例えば6インチ(約150mm)、8インチ(約200mm)、12インチ(約300mm)

50

等とすることができます。セラミック基板 20S の厚さは、例えば 50 ~ 1000 μm 程度とすることができます。

#### 【0072】

セラミック基板 20S は、例えば以下のようにして作製することができる。始めに、例えば酸化ナトリウム (Na<sub>2</sub>O)、酸化アルミニウム (Al<sub>2</sub>O<sub>3</sub>)、酸化ホウ素 (B<sub>2</sub>O<sub>3</sub>)、二酸化珪素 (SiO<sub>2</sub>) を含むガラスの粉末にアルミナコーチェライトの粉末を添加した材料に有機バインダーと溶剤を加え、混練しスラリーを作り成膜装置でシート化する。成膜装置より吐出したスラリーは、キャリアアテーブ上に塗布され乾燥ゾーンを通過した後グリーンシートとなり、所定のサイズに切断される。次に、このグリーンシートに最終的にビアホールとなる穴を開け、最終的にビアフィル及び配線パターンとなる導電材料を印刷した後に積層し、焼結することにより、セラミック基板 20S が作製される。10

#### 【0073】

次いで、図 10 に示す工程では、セラミック基板 20S と基板本体 31T とを、ポリマー層 40 を介して貼り合わせる。具体的には、始めに、セラミック基板 20S の面 26a 又は基板本体 31T の面 31b の何れか一方の面上に、ポリマー層 40 の材料である液状又はペースト状のベンゾシクロブテン (BCB)、ポリベンゾオキサゾール (PBO)、ポリイミド (PI) 等のポリマー性の絶縁樹脂をスピンドルコート法等により塗布する。或いは、セラミック基板 20S の面 26a 又は基板本体 31T の面 31b の何れか一方の面上に、フィルム状のベンゾシクロブテン (BCB)、ポリベンゾオキサゾール (PBO)、ポリイミド (PI) 等のポリマー性の絶縁樹脂をラミネートする。そして、セラミック基板 20S の電極 27 の中心と基板本体 31T のビアホール 31y の中心とを位置合わせし、セラミック基板 20S と基板本体 31T とをポリマー層 40 を介して貼り合わせる。未硬化のポリマー層 40 は粘着性を有するため、セラミック基板 20S と基板本体 31T とはポリマー層 40 を介して仮固定される。20

#### 【0074】

なお、セラミック基板 20S の面 26a 又は基板本体 31T の面 31b の何れか一方の面上に、予めビアホール 31y の位置に対応する開口部を形成したフィルム状のベンゾシクロブテン (BCB)、ポリベンゾオキサゾール (PBO)、ポリイミド (PI) 等のポリマー性の絶縁樹脂をラミネートしてもよい。この場合には、セラミック基板 20S 上にポリマー層 40 を介して基板本体 31T を接合することにより、ビアホール 31y 及びポリマー層 40 の開口部内に電極 27 の面 27a が露出する。30

#### 【0075】

次いで、図 11 に示す工程では、ビアホール 31y 内に露出するポリマー層 40 を除去してポリマー層 40 にビアホール 40x を形成し、電極 27 の面 27a を露出させる。そして、ポリマー層 40 を 250 ~ 350 ℃ 程度に加熱して硬化させる。これにより、セラミック基板 20S と基板本体 31T とは、ポリマー層 40 を介して接合（所謂ポリマー接合）される。内側面に絶縁層 32 が形成されたビアホール 31y とビアホール 40x とは、連続する 1 つの貫通孔となる（この貫通孔をビアホール 31z と称する）。

#### 【0076】

ポリマー層 40 としてポジ型の感光性絶縁樹脂を用いている場合には、基板本体 31T をマスクとしてビアホール 31y 内に露出するポリマー層 40 を紫外光等により露光し更に現像して、ビアホール 31y 内に露出するポリマー層 40 を除去することにより、ポリマー層 40 にビアホール 40x を形成することができる。又、ポリマー層 40 として非感光性絶縁樹脂を用いている場合には、基板本体 31T をマスクとして CO<sub>2</sub> レーザー等のレーザー光を照射し、ビアホール 31y 内に露出するポリマー層 40 を除去することにより、ポリマー層 40 にビアホール 40x を形成することができる。但し、この場合には、ポリマー層 40 のビアホール 40x 内に露出する電極 27 の面 27a に残渣が生じるため、アルゴンガスや CF<sub>4</sub> ガス等を用いてポリマー層 40 のビアホール 40x 内に露出する電極 27 の面 27a のクリーニング処理を行う必要がある。40

#### 【0077】

なお、前述の図10に示す工程において、セラミック基板20Sの面26a又は基板本体31Tの面31bの何れか一方の面に、予めビアホール31yの位置に対応する開口部を形成したフィルム状のベンゾシクロブテン(BCB)、ポリベンゾオキサゾール(PBO)、ポリイミド(PI)等のポリマー性の絶縁樹脂をラミネートした場合には、図11に示す工程を削除することができる。

#### 【0078】

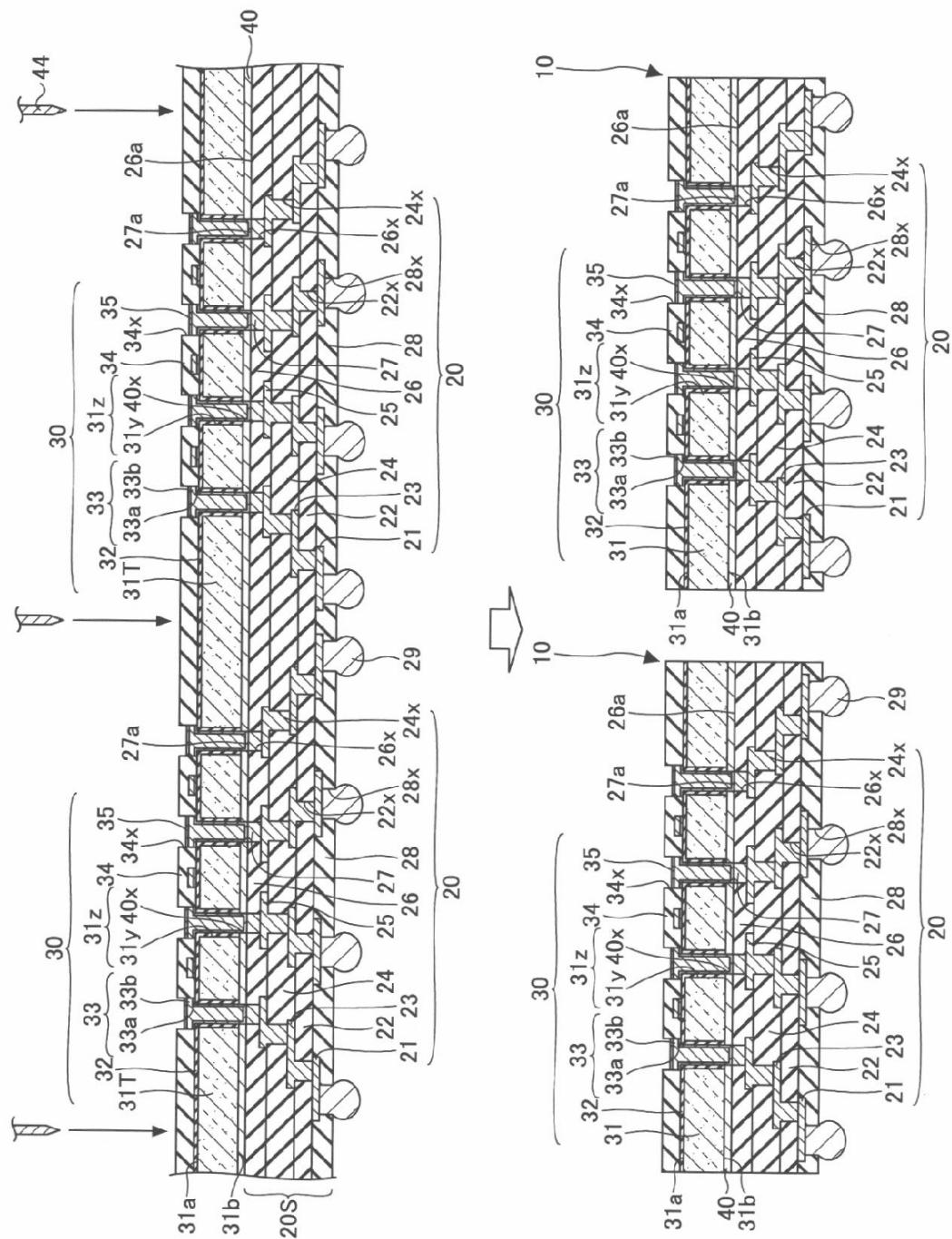

次いで、図12に示す工程では、250～350程度に加熱してポリマー層40を硬化させた後、ビアホール31z内に露出した電極27の面27a、絶縁層32上(ビアホール31yの内側面を覆う絶縁層32上も含む)、及びビアホール40xの内側面上に第1金属層33aを形成する。第1金属層33aは、例えばスパッタ法等により形成することができる。第1金属層33aとしては、例えばTi/Cu層(Ti層とCu層をこの順番で積層した金属層)やCr/Cu層(Cr層とCu層をこの順番で積層した金属層)等を用いることができる。第1金属層33aを構成する各層の厚さは、例えばTi層を0.1～0.2μm程度、Cr層を0.05～0.1μm程度、Cu層を0.1～0.5μm程度とすることができます。

10

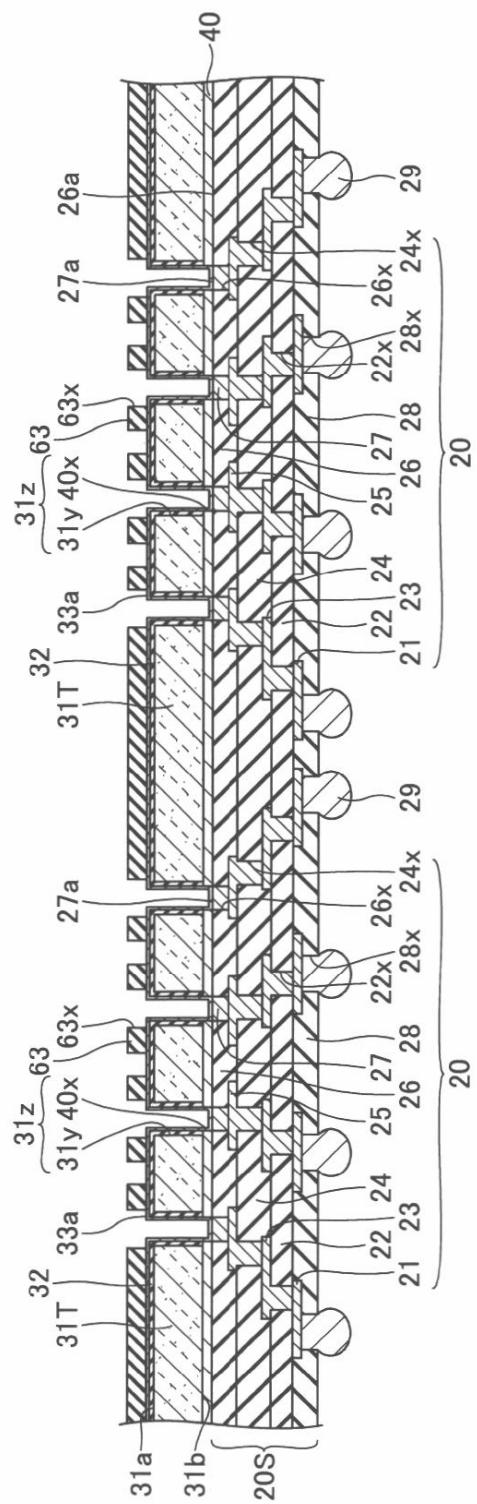

#### 【0079】

次いで、図13に示す工程では、第1金属層33a上に、配線層33に対応する開口部63xを有するレジスト層63を形成する。具体的には、第1金属層33a上に、例えばエポキシ系樹脂やイミド系樹脂等を含む感光性樹脂組成物からなる液状又はペースト状のレジストを塗布する。或いは、第1金属層33a上に、例えばエポキシ系樹脂やイミド系樹脂等を含む感光性樹脂組成物からなるフィルム状のレジストをラミネートする。そして、塗布又はラミネートしたレジストを露光、現像することで開口部63xを形成する。これにより、開口部63xを有するレジスト層63が形成される。なお、予め開口部63xを形成したフィルム状のレジストを第1金属層33a上にラミネートしても構わない。

20

#### 【0080】

次いで、図14に示す工程では、開口部63x内に露出する第1金属層33a上に第2金属層33bを形成する。第2金属層33bは、例えば第1金属層33aを給電層に利用した電解めっき法により形成することができる。第2金属層33bとしては、例えばCu層等を用いることができる。

30

#### 【0081】

次いで、図15に示す工程では、第2金属層33b上に第3金属層35を形成する。第3金属層35は、例えば第1金属層33aを給電層に利用した電解めっき法により形成することができる。第3金属層35としては、例えばAu層や、Ni/Au層(Ni層とAu層をこの順番で積層した金属層)、Ni/Pd/Au層(Ni層とPd層とAu層をこの順番で積層した金属層)等を用いることができる。第3金属層35として、例えばSnAgやSnAgCu等のはんだめっきを用いても構わない。但し、仕様に応じて、第3金属層35は形成しなくても構わない。第3金属層35の厚さは、例えば0.5～5μm程度とすることができます。

#### 【0082】

なお、第3金属層35は、配線層33が半導体チップと接続される際の接続信頼性を向上するために設けられている。そのため、最終的にガイドレジスト層34から露出しない部分には第3金属層35を形成する必要はない。そこで、予め最終的にガイドレジスト層34から露出しない部分の配線層33をマスクしてから第3金属層35を形成することが好ましい。これにより、第3金属層35を構成するAu等の材料コストを削減することができる。

40

#### 【0083】

次いで、図16に示す工程では、図15に示すレジスト層63を除去した後、第2金属層33bをマスクにして、第2金属層33bに覆われていない部分の第1金属層33aをエッチングにより除去する。これにより、第1金属層33a及び第2金属層33bを含み、内側面に絶縁層32が形成されたビアホール31y及びビアホール40xに充填された

50

ビアフィル、及び基板本体31Tの面31aに絶縁層32を介して形成された配線パターンを含んで構成される配線層33が形成される。

#### 【0084】

配線層33を構成する配線パターンは、例えばライン／スペース = 1 / 1 μm ~ 10 / 10 μm程度とすることができます。配線層33を構成する配線パターンの厚さは、例えば1 ~ 10 μm程度（ライン／スペース = 1 / 1 μm ~ 10 / 10 μm程度の場合）とすることができる。このように、配線層33はセミアディティブ法により形成することができる。但し、配線層33は、セミアディティブ法以外に、サブトラクティブ法等の各種の配線形成方法を用いて形成しても構わない。

#### 【0085】

シリコン基板30は配線層33のみを有し、多層化されていないため、設備投資額を抑制でき、かつ、高い歩留まりで製造することが可能となり、製造コストを低減することができる。

#### 【0086】

次いで、図17に示す工程では、基板本体31Tの面31aに形成された絶縁層32上に、第3金属層35を露出する開口部34xを有するガイドレジスト層34を形成する。具体的には、例えば第3金属層35上にマスクを配置し、基板本体31Tの面31aに形成された絶縁層32上にマスクを介して、例えばベンゾシクロブテン（BCB）、ポリベンゾオキサゾール（PBO）、ポリイミド（PI）等の絶縁樹脂をスピンドルコート法等により塗布して硬化させる。そして、マスクを除去することで開口部34xを形成する。これにより、開口部34xを有するガイドレジスト層34が形成され、第3金属層35はガイドレジスト層34の開口部34x内に露出する。ガイドレジスト層34の厚さは、例えば2 ~ 30 μm程度とすることができる。

#### 【0087】

なお、ガイドレジスト層34の材料として、エポキシ系樹脂やイミド系樹脂等を含む感光性樹脂組成物等を用いても構わない。その場合には、基板本体31Tの面31aに形成された絶縁層32上に、配線層33及び第3金属層35を覆うように、例えばエポキシ系樹脂やイミド系樹脂等を含む感光性樹脂組成物からなるソルダーレジストを塗布する。そして、塗布したソルダーレジストを露光、現像することで開口部34xを形成する。これにより、開口部34xを有するガイドレジスト層34が形成される。

#### 【0088】

次いで、図18に示す工程では、図17に示す構造体を所定の位置で切断して個片化することにより、図4に示すセラミック基板20及びシリコン基板30を有する配線基板10が完成する。図17に示す構造体の切断は、ダイシングブレード44を用いたダイシング等によって行うことができる。なお、所定の位置とは、セラミック基板20Sのセラミック基板20となる複数の領域間並びに基板本体31T及びポリマー層40のそれに対応する位置である。なお、基板本体31Tは切断されて、基板本体31となる。

#### 【0089】

以上のように、第1の実施の形態によれば、積層された複数のセラミック層及び内部配線を備え、この内部配線と電気的に接続された電極が一方の面から露出しているセラミック基板を準備する。又、主面及び主面の反対面である裏面を有するシリコンからなる基板本体を準備し、準備した基板本体の主面に絶縁層を形成するとともに、基板本体のセラミック基板の電極に対応する位置に、内側面に絶縁層が形成されたビアホールを形成する。そして、セラミック基板の一方の面又は基板本体の裏面にポリマー層を形成し、セラミック基板の電極の位置と基板本体のビアホールの位置とを合わせて、セラミック基板の一方の面にポリマー層を介して基板本体の裏面を接合する。

#### 【0090】

更に、ビアホール内に露出するポリマー層を除去し、ポリマー層に貫通孔を形成してセラミック基板の電極を露出する。そして、絶縁層が形成されたビアホール及びポリマー層の貫通孔に導体を充填してセラミック基板の電極と電気的に接続されたビアフィルを形成

10

20

30

40

50

するとともに、基板本体の正面にビアフィルと電気的に接続された配線パターンを形成して、ビアフィルと配線パターンとを含む配線層を形成してシリコン基板を完成させる。

#### 【0091】

その結果、超微細なビアホール及び超微細な配線パターンが形成できるというシリコン基板の特徴と、剛性及び熱伝導性が良好であり低成本で多層化が可能であるセラミック基板の特徴を兼ね備えた配線基板を実現することができる。

#### 【0092】

又、シリコン基板は1層の配線層のみを有し、多層化されていないため、設備投資額を抑制でき、かつ、高い歩留まりで製造することが可能となる。その結果、シリコン基板とセラミック基板とを有する配線基板の製造コストを低減することが可能となるため、この配線基板を半導体チップとマザーボード等の実装基板とを接続する際のインターポーラとして機能させることにより、半導体チップの微細化に対応できるインターポーラを低成本で実現することができる。10

#### 【0093】

又、セラミック基板とシリコン基板とをポリマー層を介して接合（所謂ポリマー接合）することにより、セラミック基板のCTEをシリコン基板のCTE（3 ppm / 度）に合わせ込まなくとも、セラミック基板とシリコン基板との接続信頼性を確保することができる。又、セラミック基板のCTEを主に樹脂基板からなるマザーボード等の実装基板のCTE（略18 ppm / 度）に近い値（10 ppm / ~12 ppm / 度）とすることにより、第1の実施の形態に係る配線基板が半導体チップとマザーボード等の実装基板とのインターポーラとして機能する際に、セラミック基板とマザーボード等の実装基板との接続信頼性を確保することができる。20

#### 【0094】

又、シリコン基板から遠いセラミック層のCTEを、シリコン基板に近いセラミック層のCTEよりも大きくしてマザーボード等の実装基板のCTEに近い値とすることにより、セラミック基板とマザーボード等の実装基板との接続部にCTEの違いに起因する熱応力（ストレス）が生じ難くなるため、第1の実施の形態に係る配線基板が半導体チップとマザーボード等の実装基板とのインターポーラとして機能する際に、セラミック基板とマザーボード等の実装基板との接続信頼性をより一層高めることができる。

#### 【0095】

又、第1の実施の形態に係る配線基板に半導体チップを搭載した半導体パッケージを製造する際に、半導体チップはシリコン基板上に搭載されるが、半導体チップがシリコンである場合に半導体チップとシリコン基板のCTEは略等しいため、CTEの違いに起因する熱応力（ストレス）が半導体チップとシリコン基板との接続部に生じ難い。その結果、半導体チップとシリコン基板との接続信頼性が十分に確保できるため、半導体パッケージを製造する際に、半導体チップとシリコン基板との間にアンダーフィル樹脂を充填する必要性が低くなる。30

#### 【0096】

又、基板本体と配線パターンとの間を絶縁するための絶縁層をウェット熱酸化法等の熱酸化法で形成することにより、絶縁材料をスピンドルコート法等で塗布する場合に比べて製造工程を簡略化することが可能となり、配線基板の製造コストを低減することができる。40

#### 【0097】

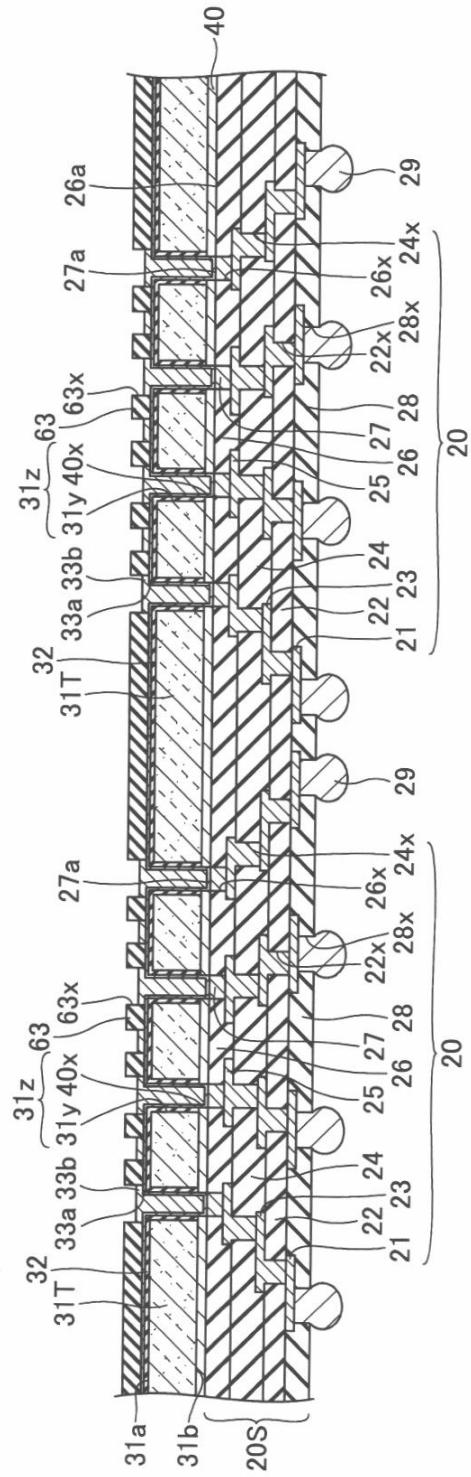

##### 第2の実施の形態

第2の実施の形態では、図4に示す配線基板10を、第1の実施の形態とは異なる製造方法で製造する例を示す。図19～図23は、第2の実施の形態に係る配線基板の製造工程を例示する図である。図19～図23において、図4と同一部分については、同一符号を付し、その説明は省略する場合がある。

#### 【0098】

始めに、図19に示す工程では、第1の実施の形態の図5～図8と同様の工程を行うことにより、面31a上及びビアホール31yの内側面に絶縁層32が形成された基板本体50

31Tを準備する。基板本体31Tの厚さは、例えば50～500μm程度とすることができる。又、セラミック基板20Sを個片化した複数のセラミック基板20を準備する。なお、図19は、図9等とは反転して描かれている。

#### 【0099】

次いで、図20に示す工程では、各セラミック基板20と基板本体31Tとを、ポリマー層40を介して貼り合わせる。なお、図20において、(a)は断面図、(b)は平面図である。具体的には、始めに、各セラミック基板20の面26a又は基板本体31Tの面31bの何れか一方の面に、ポリマー層40の材料である液状又はペースト状のベンゾシクロブテン(BCB)、ポリベンゾオキサゾール(PBO)、ポリイミド(PI)等のポリマー性の絶縁樹脂をスピンドルコート法等により塗布する。或いは、各セラミック基板20の面26a又は基板本体31Tの面31bの何れか一方の面に、フィルム状のベンゾシクロブテン(BCB)、ポリベンゾオキサゾール(PBO)、ポリイミド(PI)等のポリマー性の絶縁樹脂をラミネートする。そして、各セラミック基板20の電極27と、対応する基板本体31Tのビアホール31yとを位置合わせて、各セラミック基板20と基板本体31Tとをポリマー層40を介して貼り合わせる。未硬化のポリマー層40は粘着性を有するため、各セラミック基板20と基板本体31Tとはポリマー層40を介して仮固定される。

10

#### 【0100】

なお、各セラミック基板20の面26a又は基板本体31Tの面31bの何れか一方の面に、予めビアホール31yの位置に対応する開口部を形成したフィルム状のベンゾシクロブテン(BCB)、ポリベンゾオキサゾール(PBO)、ポリイミド(PI)等のポリマー性の絶縁樹脂をラミネートしてもよい。この場合には、各セラミック基板20上にポリマー層40を介して基板本体31Tを接合することにより、ビアホール31y及びポリマー層40の開口部内に電極27の面27aが露出する。

20

#### 【0101】

次いで、図21に示す工程では、ビアホール31y内に露出するポリマー層40を除去してポリマー層40にビアホール40xを形成し、電極27の面27aを露出させる。そして、ポリマー層40を250～350℃程度に加熱して硬化させる。これにより、各セラミック基板20と基板本体31Tとは、ポリマー層40を介して接合(所謂ポリマー接合)される。内側面に絶縁層32が形成されたビアホール31yとビアホール40xとは、連続する1つの貫通孔となる(この貫通孔をビアホール31zと称する)。

30

#### 【0102】

ポリマー層40としてポジ型の感光性絶縁樹脂を用いている場合には、基板本体31Tをマスクとしてビアホール31y内に露出するポリマー層40を紫外光等により露光し更に現像して、ビアホール31y内に露出するポリマー層40を除去することにより、ポリマー層40にビアホール40xを形成することができる。又、ポリマー層40として非感光性絶縁樹脂を用いている場合には、基板本体31TをマスクとしてCO<sub>2</sub>レーザー等のレーザー光を照射し、ビアホール31y内に露出するポリマー層40を除去することにより、ポリマー層40にビアホール40xを形成することができる。但し、この場合には、ポリマー層40のビアホール40x内に露出する電極27の面27aに残渣が生じるため、アルゴンガスやCF<sub>4</sub>ガス等を用いてポリマー層40のビアホール40x内に露出する電極27の面27aのクリーニング処理を行う必要がある。

40

#### 【0103】

なお、前述の図20に示す工程において、各セラミック基板20の面26a又は基板本体31Tの面31bの何れか一方の面に、予めビアホール31yの位置に対応する開口部を形成したフィルム状のベンゾシクロブテン(BCB)、ポリベンゾオキサゾール(PBO)、ポリイミド(PI)等のポリマー性の絶縁樹脂をラミネートした場合には、図21に示す工程を削除することができる。

#### 【0104】

予め各セラミック基板20の電気特性検査等を実施して良否判定をし、良品のセラミック

ク基板 20 のみを基板本体 31T にポリマー接合することにより、配線基板 10 の歩留まりを向上させることができる。

#### 【0105】

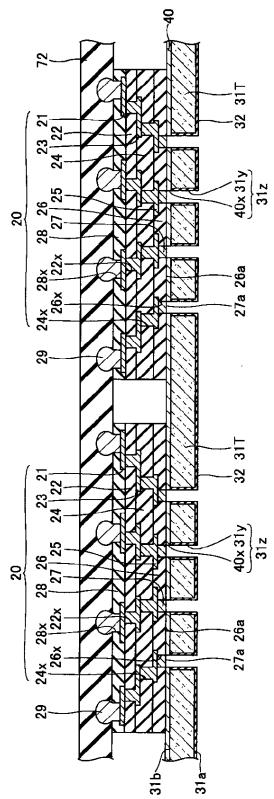

次いで、図 22 に示す工程では、各セラミック基板 20 の基板本体 31T の反対側に支持基板 72 を貼り付ける。支持基板 72 としては、耐熱性及び耐薬性に優れた材料を用いることが好ましい。又、支持基板 72 としては、外部接続端子 29 の高さを吸収できる柔軟性を有する材料を用いることが好ましい。支持基板 72 の一例としては、熱剥離テープや P D M S (Poly-dimethyl-siloxane) 系テープ、或いは補強板に P D M S 系テープ等を貼り付けたもの等を用いることができる。支持基板 72 の厚さは、例えば 500 μm 程度とすることができる。

10

#### 【0106】

次いで、図 23 に示す工程では、図 22 に示す構造体を上下反転させて支持基板 72 を下側にし、第 1 の実施の形態の図 12 ~ 図 17 に示す工程と同様の工程を行って配線層 33 等を形成した後、支持基板 72 を除去して、図 23 の上側に示す構造体を作製する。そして、図 23 の上側に示す構造体を所定の位置で切断して個片化することにより、図 4 に示すセラミック基板 20 及びシリコン基板 30 を有する配線基板 10 が完成する。図 23 の上側に示す構造体の切断は、ダイシングブレード 44 を用いたダイシング等によって行うことができる。なお、所定の位置は、各セラミック基板 20 を含んで個片化できればどこでもよいが、例えば、各セラミック基板 20 の外縁部とすることができます。なお、基板本体 31T は切断されて、基板本体 31 となる。

20

#### 【0107】

以上のように、第 2 の実施の形態によれば、積層された複数のセラミック層及び内部配線を備え、この内部配線と電気的に接続された電極が一方の面から露出しているセラミック基板が個片化された複数のセラミック基板を準備する。又、主面及び主面の反対面である裏面を有し、個片化されると基板本体となる複数の領域を有する基板を準備し、準備した基板の主面に絶縁層を形成するとともに、準備した基板のセラミック基板のそれぞれの電極に対応する位置に、内側面に絶縁層が形成されたビアホールを形成する。そして、セラミック基板のそれぞれの一方の面又は準備した基板の裏面にポリマー層を形成し、セラミック基板のそれぞれの電極の位置と、対応するビアホールの位置とを合わせて、セラミック基板のそれぞれの一方の面にポリマー層を介して準備した基板の裏面を接合する。

30

#### 【0108】

更に、ビアホール内に露出するポリマー層を除去し、ポリマー層に貫通孔を形成してセラミック基板の電極を露出する。そして、絶縁層が形成されたビアホール及びポリマー層の貫通孔に導体を充填してセラミック基板の電極と電気的に接続されたビアフィルを形成するとともに、準備した基板の主面にビアフィルと電気的に接続された配線パターンを形成して、ビアフィルと配線パターンとを含む配線層を形成してシリコン基板を完成させる。その後、作製した構造体を切断して個片化し、セラミック基板とシリコン基板とがポリマー層を介して接合された複数の配線基板を作製する。

#### 【0109】

その結果、第 1 の実施の形態と同様の効果を奏するが、更に以下の効果を奏する。すなわち、個片化された複数のセラミック基板を、個片化されると基板本体となる複数の領域を有する基板の一方の面にポリマー接合してから配線基板を作製するため、予め各セラミック基板の電気特性検査等を実施して良否判定をし、良品のセラミック基板のみを前記本体にポリマー接合することが可能となり、配線基板の歩留まりを向上させることができる。

40

#### 【0110】

##### 第 3 の実施の形態

第 3 の実施の形態では、第 1 の実施の形態に係る配線基板 10 (図 4 参照) に半導体チップを搭載した半導体パッケージの例を示す。第 3 の実施の形態において、第 1 の実施の形態と共に通する部分についてはその説明を省略し、第 1 の実施の形態と異なる部分を中心

50

に説明する。

**【0111】**

[第3の実施の形態に係る半導体パッケージの構造]

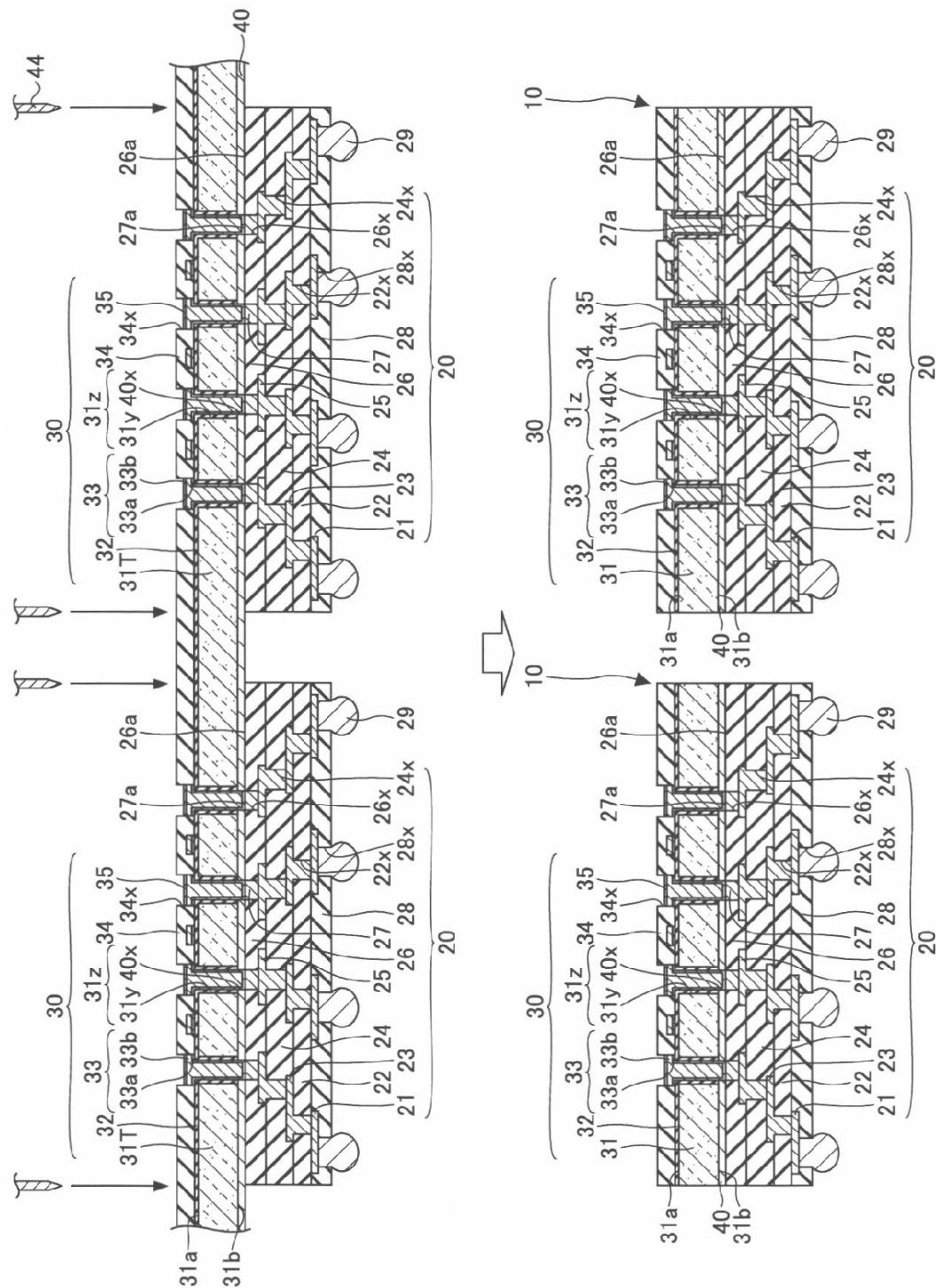

図24は、第3の実施の形態に係る半導体パッケージを例示する断面図である。図24において、図4と同一部品については、同一符号を付し、その説明は省略する場合がある。図24を参照するに、半導体パッケージ80は、図4に示す配線基板10と、半導体チップ81と、はんだバンプ90とを有する。

**【0112】**

半導体チップ81は、半導体基板82と、電極パッド83とを有する。半導体基板82は、例えばシリコン(Si)やゲルマニウム(Ge)等からなる基板に半導体集積回路(図示せず)が形成されたものである。電極パッド83は、半導体基板82の一方の側に形成されており、半導体集積回路(図示せず)と電気的に接続されている。電極パッド83の材料としては、例えばアルミニウム(Al)等を用いることができる。電極パッド83の材料として、銅(Cu)とアルミニウム(Al)をこの順番で積層したもの、銅(Cu)とアルミニウム(Al)とシリコン(Si)をこの順番で積層したもの等を用いても構わない。

10

**【0113】**

はんだバンプ90は、配線基板10の第3金属層35と半導体チップ81の電極パッド83とを電気的に接続している。はんだバンプ90の材料としては、例えばPbを含む合金、SnとCuの合金、SnとAgの合金、SnとAgとCuの合金等を用いることができる。以上が、第3の実施の形態に係る半導体パッケージの構造である。

20

**【0114】**

[第3の実施の形態に係る半導体パッケージの製造方法]

続いて、第3の実施の形態に係る半導体パッケージの製造方法について説明する。図25及び図26は、第3の実施の形態に係る半導体パッケージの製造工程を例示する図である。図25及び図26において、図24と同一部品については、同一符号を付し、その説明は省略する場合がある。

**【0115】**

始めに、図25に示す工程では、配線基板10を準備し、第3金属層35上にプレソルダー91を形成する。又、半導体チップ81を準備し、電極パッド83上にプレソルダー92を形成する。プレソルダー91及び92は、第3金属層35上及び電極パッド83上に、例えばPbを含む合金、SnとCuの合金、SnとAgの合金、SnとAgとCuの合金等からなるはんだペーストを塗布し、リフローを行うことにより形成することができる。

30

**【0116】**

次いで、図26に示す工程では、配線基板10の第3金属層35側と半導体チップ81の電極パッド83側とを対向させて、プレソルダー91と92とが対応する位置に来るよう配置する。そして、プレソルダー91及び92を例えば230℃に加熱することで、プレソルダー91及び92は溶融して1つの合金となり、はんだバンプ90が形成される。これにより、図24に示す半導体パッケージ80が完成する。

40

**【0117】**

以上のように、第3の実施の形態によれば、第1の実施の形態に係る配線基板に接続端子を介して半導体チップを搭載した半導体パッケージを製造する。ここで、搭載される半導体チップがシリコンである場合には、配線基板を構成するシリコン基板と半導体チップのCTEは略等しい。その結果、配線基板と半導体チップとの接続部には、CTEの違いに起因する熱応力(ストレス)が生じ難く、配線基板と半導体チップとの接続信頼性を向上することができる。又、配線基板と半導体チップとの接続信頼性が向上した結果、半導体パッケージを製造する際に、半導体チップとシリコン基板との間にアンダーフィル樹脂を充填する工程を省略することができる。

**【0118】**

50

又、配線基板を構成するセラミック基板とシリコン基板とをポリマー層を介して接合（所謂ポリマー接合）することにより、セラミック基板のCTEをシリコン基板のCTE（3 ppm / 程度）に合わせ込まなくても、セラミック基板とシリコン基板との接続信頼性を確保することができるため、配線基板を構成する各セラミック基板のCTEを主に樹脂基板からなるマザーボード等の実装基板のCTE（略18 ppm / 程度）に近い値（10 ppm / ~12 ppm / 程度）とすることができます。その結果、第3の実施の形態に係る半導体パッケージをマザーボード等の実装基板と接続した場合に、配線基板とマザーボード等の実装基板との接続部には、CTEの違いに起因する熱応力（ストレス）が生じ難く、配線基板とマザーボード等との接続信頼性を高めることができる。

## 【0119】

10

又、配線基板のセラミック基板を構成する各セラミック層のうち、シリコン基板から遠いセラミック層のCTEを、シリコン基板に近いセラミック層のCTEよりも大きくし、マザーボード等の実装基板のCTEに近い値とすることができます。その結果、第3の実施の形態に係る半導体パッケージをマザーボード等の実装基板と接続した場合に、配線基板とマザーボード等の実装基板との接続部には、CTEの違いに起因する熱応力（ストレス）が更に生じ難く、配線基板とマザーボード等との接続信頼性をより一層高めることができます。

## 【0120】

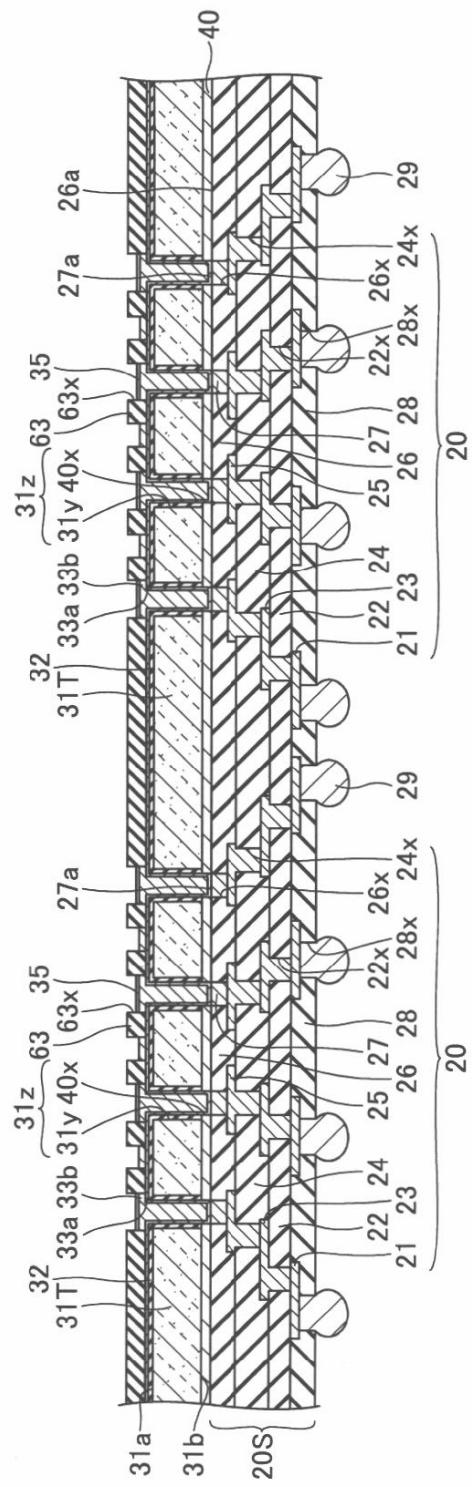

## 第3の実施の形態の変形例1

第3の実施の形態の変形例1では、第3の実施の形態に係る半導体パッケージ80（図24参照）の変形例を示す。第3の実施の形態の変形例1において、第3の実施の形態と共に通する部分についてはその説明を省略し、第3の実施の形態と異なる部分を中心に説明する。

20

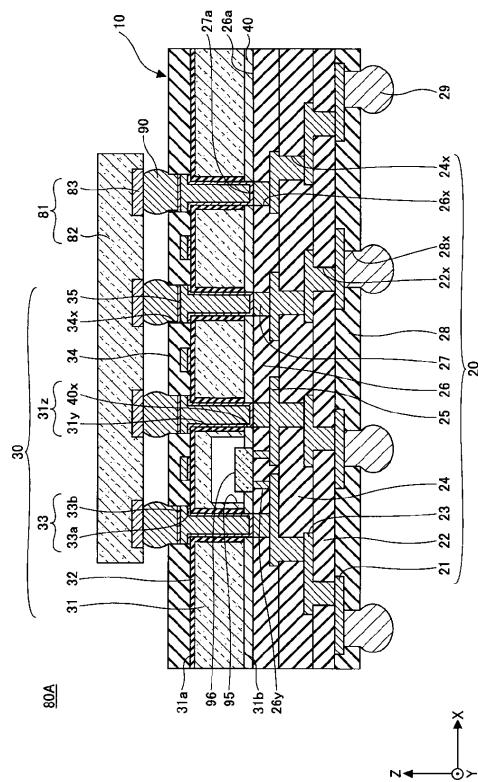

## 【0121】

図27は、第3の実施の形態の変形例1に係る半導体パッケージを例示する断面図である。図27において、図24と同一部品については、同一符号を付し、その説明は省略する場合がある。図27を参照するに、半導体パッケージ80Aは、配線基板10の基板本体31に中空部95を設け、中空部95中にMEMSデバイス96を埋め込んだ構造を有する。

## 【0122】

30

中空部95は、基板本体31とセラミック基板20とをポリマー接合する前に、例えばSF<sub>6</sub>を用いた反応性イオンエッチング（DRIE : Deep Reactive Ion Etch）等の異方性エッチング法により、基板本体31に形成することができる。MEMSデバイス96は、第4ピアホール26y内に充填されたビアフィルにより第3配線層25と電気的に接続されている。MEMSデバイス96は、基板本体31とセラミック基板20とをポリマー接合する前に、セラミック基板20に搭載することができる。ポリマー層40は、セラミック基板20の面26aに、例えば予めピアホール31y及びMEMSデバイス96の位置に対応する開口部を形成したフィルム状のベンゾシクロブテン等のポリマー性の絶縁樹脂をラミネートすることにより形成することができる。MEMSデバイス96の一例としては、例えば圧力センサーや加速度センサー等を挙げることができる。半導体チップ81は、MEMSデバイス96を制御する機能を有する。

40

## 【0123】

以上のように、第3の実施の形態の変形例1によれば、第3の実施の形態と同様の効果を奏するが、更に以下の効果を奏する。すなわち、配線基板の基板本体に中空部を設け、中空部にMEMSデバイスを埋め込んだ構造とし、半導体チップに配線基板の有するMEMSデバイスを制御する機能を持たせることにより、MEMSデバイスを有し、その制御が可能な半導体パッケージを実現できる。

## 【0124】

## 第3の実施の形態の変形例2

第3の実施の形態の変形例2では、第3の実施の形態に係る半導体パッケージ80（図

50

24参照)の他の変形例を示す。第3の実施の形態の変形例2において、第3の実施の形態と共に通する部分についてはその説明を省略し、第3の実施の形態と異なる部分を中心に説明する。

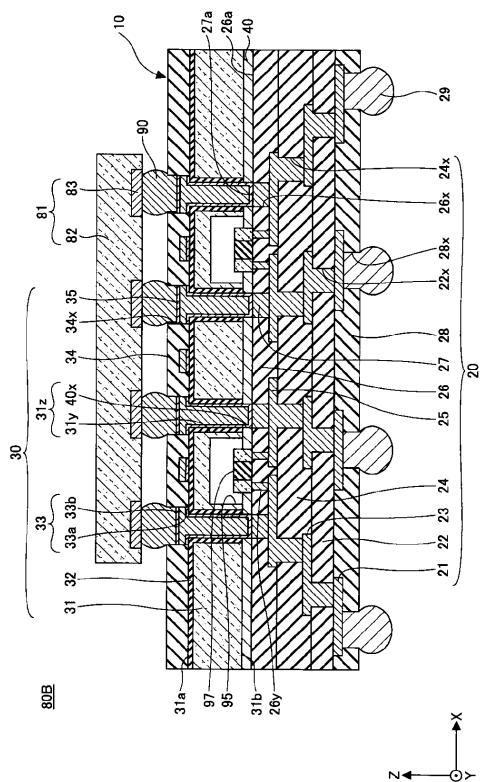

#### 【0125】

図28は、第3の実施の形態の変形例2に係る半導体パッケージを例示する断面図である。図28において、図24と同一部品については、同一符号を付し、その説明は省略する場合がある。図28を参照するに、半導体パッケージ80Bは、配線基板10の基板本体31に中空部95を設け、中空部95中にコンデンサ97(チップキャパシタ)を埋め込んだ構造を有する。

#### 【0126】

中空部95は、基板本体31とセラミック基板20とをポリマー接合する前に、例えばSF<sub>6</sub>を用いた反応性イオンエッティング(DRIE: Deep Reactive Ion Etch)等の異方性エッティング法により、基板本体31に形成することができる。コンデンサ97は、第4ビアホール26y内に充填されたビアフィルにより第3配線層25と電気的に接続されている。コンデンサ97は、半導体チップ81の直下に形成するが好ましい。コンデンサ97は、基板本体31とセラミック基板20とをポリマー接合する前に、セラミック基板20に搭載することができる。ポリマー層40は、セラミック基板20の面26aに、例えば予めビアホール31y及びコンデンサ97の位置に対応する開口部を形成したフィルム状のベンゾシクロブテン等のポリマー性の絶縁樹脂をラミネートすることにより形成することができる。

10

#### 【0127】

以上のように、第3の実施の形態の変形例2によれば、第3の実施の形態と同様の効果を奏するが、更に以下の効果を奏する。すなわち、配線基板の基板本体に中空部を設け、中空部にコンデンサを埋め込んだ構造とすることにより、半導体チップ直下にコンデンサを配置することが可能になり、半導体パッケージの電気的特性を向上することできる。なお、中空部95には、コンデンサ(チップキャパシタ)以外にも、抵抗やインダクタ等の各種電子部品を搭載することができる。

20

#### 【0128】

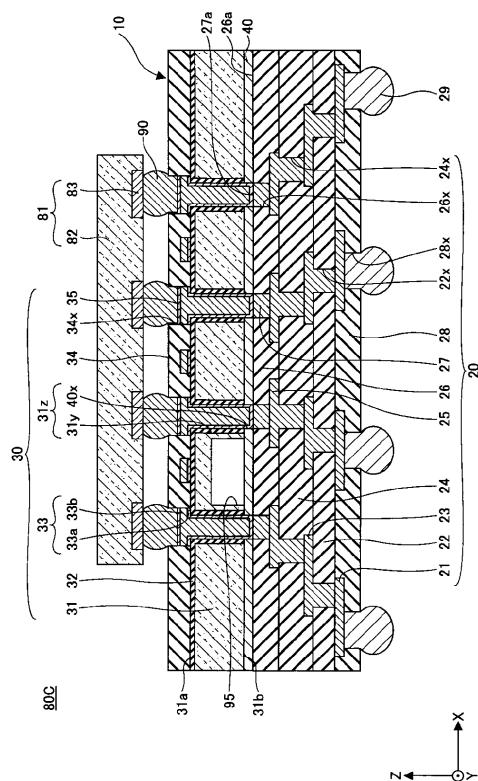

##### 第3の実施の形態の変形例3

第3の実施の形態の変形例3では、第3の実施の形態に係る半導体パッケージ80(図24参照)の他の変形例を示す。第3の実施の形態の変形例3において、第3の実施の形態と共に通する部分についてはその説明を省略し、第3の実施の形態と異なる部分を中心に説明する。

30

#### 【0129】

図29は、第3の実施の形態の変形例3に係る半導体パッケージを例示する断面図である。図29において、図24と同一部品については、同一符号を付し、その説明は省略する場合がある。図29を参照するに、半導体パッケージ80Cは、配線基板10の基板本体31に中空部95を設け、中空部95を水等の冷媒が供給される冷媒流路として用いている。

#### 【0130】

中空部95は、基板本体31とセラミック基板20とをポリマー接合する前に、例えばSF<sub>6</sub>を用いた反応性イオンエッティング(DRIE: Deep Reactive Ion Etch)等の異方性エッティング法により、基板本体31に形成することができる。中空部95は、半導体チップ81の直下に形成するが好ましい。

40

#### 【0131】

以上のように、第3の実施の形態の変形例3によれば、第3の実施の形態と同様の効果を奏するが、更に以下の効果を奏する。すなわち、配線基板の基板本体に中空部を設け、中空部を水等の冷媒が供給される冷媒流路として用いることにより、半導体チップ直下に冷媒流路を配置することが可能になり、半導体パッケージの放熱特性を向上することできる。

50

## 【0132】

以上、好ましい実施の形態について詳説したが、上述した実施の形態に制限されることはなく、特許請求の範囲に記載された範囲を逸脱することなく、上述した実施の形態に種々の変形及び置換を加えることができる。

## 【0133】

例えば、基板本体の主面に凹部を形成し、基板本体の主面並びに凹部の内側面及び底面に絶縁層を形成し、更に基板本体を裏面側から研磨して薄型化して凹部を貫通させ、内側面に絶縁層が形成されたピアホールを形成する工程に代えて、以下のような工程にしても構わない。すなわち、基板本体を裏面側から研磨して薄型化し、薄型化した基板本体を貫通するピアホールを形成し、薄型化した基板本体の表面（主面及びピアホールの内側面も含む）に絶縁層を形成する工程にしても構わない。10

## 【符号の説明】

## 【0134】

|                            |           |    |

|----------------------------|-----------|----|

| 1 0                        | 配線基板      |    |

| 2 0、 2 0 S                 | セラミック基板   |    |

| 2 1                        | 第1配線層     |    |

| 2 2                        | 第1セラミック層  |    |

| 2 2 x                      | 第1ピアホール   |    |

| 2 3                        | 第2配線層     |    |

| 2 4                        | 第2セラミック層  | 20 |

| 2 4 x                      | 第2ピアホール   |    |

| 2 5                        | 第3配線層     |    |

| 2 6                        | 第3セラミック層  |    |

| 2 6 a、 2 7 a、 3 1 a、 3 1 b | 面         |    |

| 2 6 x                      | 第3ピアホール   |    |

| 2 6 y                      | 第4ピアホール   |    |

| 2 7                        | 電極        |    |

| 2 8                        | ソルダーレジスト層 |    |

| 2 8 x、 3 4 x、 6 1 x、 6 3 x | 開口部       |    |

| 2 9                        | 外部接続端子    | 30 |

| 3 0                        | シリコン基板    |    |

| 3 1、 3 1 S、 3 1 T          | 基板本体      |    |

| 3 1 x                      | 凹部        |    |

| 3 1 y、 3 1 z、 4 0 x        | ピアホール     |    |

| 3 2                        | 絶縁層       |    |

| 3 3                        | 配線層       |    |

| 3 3 a                      | 第1金属層     |    |

| 3 3 b                      | 第2金属層     |    |

| 3 4                        | ガイドレジスト層  |    |

| 3 5                        | 第3金属層     | 40 |

| 4 0                        | ポリマー層     |    |

| 4 4                        | ダイシングブレード |    |

| 6 1、 6 3                   | レジスト層     |    |

| 7 2                        | 支持基板      |    |

| 8 0、 8 0 A、 8 0 B、 8 0 C   | 半導体パッケージ  |    |

| 8 1                        | 半導体チップ    |    |

| 8 2                        | 半導体基板     |    |

| 8 3                        | 電極パッド     |    |

| 9 0                        | はんだバンプ    |    |

| 9 1、 9 2                   | プレソルダー    | 50 |

- 9 5 中空部

9 6 MEMS デバイス

9 7 コンデンサ

【図1】

従来の半導体パッケージを例示する断面図

【図2】

従来の半導体パッケージの製造工程を例示する図(その1)

【図3】

従来の半導体パッケージの製造工程を例示する図(その2)

【図4】

第1の実施の形態に係る配線基板を例示する断面図

【図5】

第1の実施の形態に係る配線基板の製造工程を例示する図(その1)

【図6】

第1の実施の形態に係る配線基板の製造工程を例示する図(その2)

【図7】

第1の実施の形態に係る配線基板の製造工程を例示する図(その3)

【図8】

第1の実施の形態に係る配線基板の製造工程を例示する図(その4)

【図9】

第1の実施の形態に係る配線基板の製造工程を例示する図(その5)

【図10】

第1の実施の形態に係る配線基板の製造工程を例示する図(その6)

【図 1 1】

## 第1の実施の形態に係る配線基板の製造工程を例示する図(その7)

【 図 1 9 】

## 第2の実施の形態に係る配線基板の製造工程を例示する図(その1)

【図20】

## 第2の実施の形態に係る配線基板の製造工程を例示する図(その2)

【 囮 2 1 】

第2の実施の形態に係る配線基板の製造工程を例示する図(その3)

【図22】

第2の実施の形態に係る配線基板の製造工程を例示する図(その4)

【図27】

第3の実施の形態の変形例1に係る半導体パッケージを例示する断面図

【図28】

第3の実施の形態の変形例2に係る半導体パッケージを例示する断面図

【図29】

第3の実施の形態の変形例3に係る半導体パッケージを例示する断面図

【図12】

第1の実施の形態に係る配線基板の製造工程を例示する図(その8)

【図13】

第1の実施の形態に係る配線基板の製造工程を例示する図(その9)

【図14】

第1の実施の形態に係る配線基板の製造工程を例示する図(その10)

【図15】

## 第1の実施の形態に係る配線基板の製造工程を例示する図(その11)

【図16】

第1の実施の形態に係る配線基板の製造工程を例示する図(その12)

【図17】

## 第1の実施の形態に係る配線基板の製造工程を例示する図(その13)

【図18】

## 第1の実施の形態に係る配線基板の製造工程を例示する図(その14)

【図23】

第2の実施の形態に係る配線基板の製造工程を例示する図(その5)

---

フロントページの続き

(51)Int.Cl.

F I

|         |       |   |

|---------|-------|---|

| H 0 1 L | 23/12 | J |

| H 0 1 L | 23/46 | Z |

| H 0 1 L | 23/12 | N |

| H 0 1 L | 23/12 | B |

| H 0 5 K | 3/46  | T |

(56)参考文献 特開2007-266182(JP,A)

米国特許出願公開第2008/0284037(US,A1)

特開2002-299486(JP,A)

特開2006-012687(JP,A)

特開2007-123371(JP,A)

特開2008-160019(JP,A)

特開2004-056145(JP,A)

特開2001-185643(JP,A)

特開昭57-166051(JP,A)

特開2004-349603(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 0 5 K 3 / 4 6

H 0 1 L 2 3 / 1 2

H 0 1 L 2 3 / 3 2

H 0 1 L 2 3 / 4 7 3