(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4369109号

(P4369109)

(45) 発行日 平成21年11月18日(2009.11.18)

(24) 登録日 平成21年9月4日(2009.9.4)

(51) Int.Cl.

F 1

|             |           |             |      |

|-------------|-----------|-------------|------|

| HO1L 29/786 | (2006.01) | HO1L 29/78  | 620  |

| HO1L 21/336 | (2006.01) | HO1L 29/78  | 627G |

| GO2F 1/1368 | (2006.01) | HO1L 29/78  | 616U |

| HO1L 21/20  | (2006.01) | HO1L 29/78  | 627Z |

| HO1L 21/268 | (2006.01) | GO2F 1/1368 |      |

請求項の数 14 (全 44 頁) 最終頁に続く

(21) 出願番号

特願2002-330011 (P2002-330011)

(22) 出願日

平成14年11月13日 (2002.11.13)

(65) 公開番号

特開2003-218362 (P2003-218362A)

(43) 公開日

平成15年7月31日 (2003.7.31)

審査請求日 平成17年11月3日 (2005.11.3)

(31) 優先権主張番号 特願2001-349308 (P2001-349308)

(32) 優先日 平成13年11月14日 (2001.11.14)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 早川 昌彦

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 河本 充雄

(56) 参考文献 特開2001-127301 (JP, A)

)

特開平08-321466 (JP, A)

特開平11-191628 (JP, A)

特開平02-084773 (JP, A)

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の非晶質シリコン膜を形成し、

前記第1の非晶質シリコン膜上に開口部が設けられたマスク膜を形成し、

前記開口部において露出している前記第1の非晶質シリコン膜表面に半導体の結晶化工

ネルギーを低下させる金属元素を添加し、

前記第1の非晶質シリコン膜を結晶化して第1の結晶質シリコン膜を形成し、

前記マスク膜を除去し、

前記第1の結晶質シリコン膜をエッチングして一対の第1の島状結晶質シリコン層を形

成し、前記一対の第1の島状結晶質シリコン層と密着して積層された一対の第1の領域と、前

記一対の第1の島状結晶質シリコン層と積層されていなく前記一対の第1の領域の間に設

けられた第2の領域と、を含む島状非晶質シリコン層を形成し、連続発振したレーザー光の照射領域を、前記一対の第1の領域の一方から前記一対の第

1の領域の他方に向けて移動させることにより、前記島状非晶質シリコン層を結晶化して

第2の島状結晶質シリコン層を形成し、前記第2の領域の少なくとも一部をチャネル形成領域として用いるとともに、前記一対

の第1の領域をソース領域及びドレイン領域として用いることを特徴とする半導体装置の

作製方法。

## 【請求項 2】

10

20

シリコン膜中のゲルマニウム濃度が 1 原子 % 以上 10 原子 % 以下である非晶質シリコンゲルマニウム膜を、半導体の結晶化工エネルギーを低下させる金属元素を用いて結晶化することにより、結晶質シリコンゲルマニウム膜を形成し、

前記結晶質シリコンゲルマニウム膜をエッチングして一対の島状結晶質シリコンゲルマニウム層を形成し、

前記一対の島状結晶質シリコンゲルマニウム層と密着して積層された一対の第 1 の領域と、前記一対の島状結晶質シリコンゲルマニウム層と積層されていなく前記一対の第 1 の領域の間に設けられた第 2 の領域と、を含む島状非晶質シリコン層を形成し、

連続発振したレーザー光の照射領域を、前記一対の第 1 の領域の一方から前記一対の第 1 の領域の他方に向けて移動させることにより、前記島状非晶質シリコン層を結晶化して島状結晶質シリコン層を形成し、

前記第 2 の領域の少なくとも一部をチャネル形成領域として用いるとともに、前記一対の第 1 の領域をソース領域及びドレン領域として用いることを特徴とする半導体装置の作製方法。

#### 【請求項 3】

シリコン膜中のゲルマニウム濃度が 1 原子 % 以上 10 原子 % 以下である非晶質シリコンゲルマニウム膜を形成し、

前記非晶質シリコンゲルマニウム膜表面に半導体の結晶化工エネルギーを低下させる金属元素を添加し、

前記非晶質シリコンゲルマニウム膜を結晶化して結晶質シリコンゲルマニウム膜を形成し、

前記結晶質シリコンゲルマニウム膜をエッチングして一対の島状結晶質シリコンゲルマニウム層を形成し、

前記一対の島状結晶質シリコンゲルマニウム層と密着して積層された一対の第 1 の領域と、前記一対の島状結晶質シリコンゲルマニウム層と積層されていなく前記一対の第 1 の領域の間に設けられた第 2 の領域と、を含む島状非晶質シリコン層を形成し、

連続発振したレーザー光の照射領域を、前記一対の第 1 の領域の一方から前記一対の第 1 の領域の他方に向けて移動させることにより、前記島状非晶質シリコン層を結晶化して島状結晶質シリコン層を形成し、

前記第 2 の領域の少なくとも一部をチャネル形成領域として用いるとともに、前記一対の第 1 の領域をソース領域及びドレン領域として用いることを特徴とする半導体装置の作製方法。

#### 【請求項 4】

下地膜の表面に半導体の結晶化工エネルギーを低下させる金属元素を塗布し、

前記下地膜上にシリコン膜中のゲルマニウム濃度が 1 原子 % 以上 10 原子 % 以下である非晶質シリコンゲルマニウム膜を形成し、

前記非晶質シリコンゲルマニウム膜を結晶化して結晶質シリコンゲルマニウム膜を形成し、

前記結晶質シリコンゲルマニウム膜をエッチングして一対の島状結晶質シリコンゲルマニウム層を形成し、

前記一対の島状結晶質シリコンゲルマニウム層と密着して積層された一対の第 1 の領域と、前記一対の島状結晶質シリコンゲルマニウム層と積層されていなく前記一対の第 1 の領域の間に設けられた第 2 の領域と、を含む島状非晶質シリコン層を形成し、

連続発振したレーザー光の照射領域を、前記一対の第 1 の領域の一方から前記一対の第 1 の領域の他方に向けて移動させることにより、前記島状非晶質シリコン層を結晶化して島状結晶質シリコン層を形成し、

前記第 2 の領域の少なくとも一部をチャネル形成領域として用いるとともに、前記一対の第 1 の領域をソース領域及びドレン領域として用いることを特徴とする半導体装置の作製方法。

#### 【請求項 5】

10

20

30

40

50

請求項 1において、

前記一対の第 1 の島状結晶質シリコン層の側面に凹凸形状が形成されており、

前記凹凸形状は、前記第 2 の領域と接するように設けられていることを特徴とする半導体装置の作製方法。

【請求項 6】

第 1 の非晶質シリコン膜を形成し、

前記第 1 の非晶質シリコン膜上に開口部が設けられたマスク膜を形成し、

前記開口部において露出している前記第 1 の非晶質シリコン膜表面に半導体の結晶化工エネルギーを低下させる金属元素を添加し、

前記第 1 の非晶質シリコン膜を結晶化して第 1 の結晶質シリコン膜を形成し、

10

前記マスク膜を除去し、

前記第 1 の結晶質シリコン膜をエッチングして一対の第 1 の島状結晶質シリコン層を形成し、

前記一対の第 1 の島状結晶質シリコン層と密着して積層された一対の第 1 の領域と、前記一対の第 1 の島状結晶質シリコン層と積層されていなく前記一対の第 1 の領域の間に設けられた第 2 の領域と、を含む島状非晶質シリコン層を形成し、

パルス発振したレーザー光の照射領域を前記一対の第 1 の領域及び前記第 2 の領域に照射しながら移動させることにより、前記島状非晶質シリコン層を結晶化して第 2 の島状結晶質シリコン層を形成し、

前記第 2 の領域の少なくとも一部をチャネル形成領域として用いるとともに、前記一対の第 1 の領域をソース領域及びドレン領域として用いることを特徴とする半導体装置の作製方法。

20

【請求項 7】

シリコン膜中のゲルマニウム濃度が 1 原子 % 以上 10 原子 % 以下である非晶質シリコンゲルマニウム膜を、半導体の結晶化工エネルギーを低下させる金属元素を用いて結晶化することにより、結晶質シリコンゲルマニウム膜を形成し、

前記結晶質シリコンゲルマニウム膜をエッチングして一対の島状結晶質シリコンゲルマニウム層を形成し、

前記一対の島状結晶質シリコンゲルマニウム層と密着して積層された一対の第 1 の領域と、前記一対の島状結晶質シリコンゲルマニウム層と積層されていなく前記一対の第 1 の領域の間に設けられた第 2 の領域と、を含む島状非晶質シリコン層を形成し、

30

パルス発振したレーザー光の照射領域を前記一対の第 1 の領域及び前記第 2 の領域に照射しながら移動させることにより、前記島状非晶質シリコン層を結晶化して島状結晶質シリコン層を形成し、

前記第 2 の領域の少なくとも一部をチャネル形成領域として用いるとともに、前記一対の第 1 の領域をソース領域及びドレン領域として用いることを特徴とする半導体装置の作製方法。

【請求項 8】

シリコン膜中のゲルマニウム濃度が 1 原子 % 以上 10 原子 % 以下である非晶質シリコンゲルマニウム膜を形成し、

40

前記非晶質シリコンゲルマニウム膜表面に半導体の結晶化工エネルギーを低下させる金属元素を添加し、

前記非晶質シリコンゲルマニウム膜を結晶化して結晶質シリコンゲルマニウム膜を形成し、

前記結晶質シリコンゲルマニウム膜をエッチングして一対の島状結晶質シリコンゲルマニウム層を形成し、

前記一対の島状結晶質シリコンゲルマニウム層と密着して積層された一対の第 1 の領域と、前記一対の島状結晶質シリコンゲルマニウム層と積層されていなく前記一対の第 1 の領域の間に設けられた第 2 の領域と、を含む島状非晶質シリコン層を形成し、

パルス発振したレーザー光の照射領域を前記一対の第 1 の領域及び前記第 2 の領域に照

50

射しながら移動させることにより、前記島状非晶質シリコン層を結晶化して島状結晶質シリコン層を形成し、

前記第2の領域の少なくとも一部をチャネル形成領域として用いるとともに、前記一対の第1の領域をソース領域及びドレイン領域として用いることを特徴とする半導体装置の作製方法。

#### 【請求項9】

下地膜の表面に半導体の結晶化工エネルギーを低下させる金属元素を塗布し、

前記下地膜上にシリコン膜中のゲルマニウム濃度が1原子%以上10原子%以下である非晶質シリコンゲルマニウム膜を形成し、

前記非晶質シリコンゲルマニウム膜を結晶化して結晶質シリコンゲルマニウム膜を形成し、10

前記結晶質シリコンゲルマニウム膜をエッチングして一対の島状結晶質シリコンゲルマニウム層を形成し、

前記一対の島状結晶質シリコンゲルマニウム層と密着して積層された一対の第1の領域と、前記一対の島状結晶質シリコンゲルマニウム層と積層されていなく前記一対の第1の領域の間に設けられた第2の領域と、を含む島状非晶質シリコン層を形成し、

パルス発振したレーザー光の照射領域を前記一対の第1の領域及び前記第2の領域に照射しながら移動させることにより、前記島状非晶質シリコン層を結晶化して島状結晶質シリコン層を形成し、15

前記第2の領域の少なくとも一部をチャネル形成領域として用いるとともに、前記一対の第1の領域をソース領域及びドレイン領域として用いることを特徴とする半導体装置の作製方法。20

#### 【請求項10】

請求項6において、

前記パルス発振したレーザー光の照射により、前記一対の第1の島状結晶質シリコン層の一方を種に成長した結晶と、前記一対の第1の島状結晶質シリコン層の他方を種に成長した結晶と、がぶつかって形成された結晶粒界が前記第2の領域に発生し、

前記チャネル形成領域には、前記結晶粒界が含まれないことを特徴とする半導体装置の作製方法。25

#### 【請求項11】

請求項6において、

前記チャネル形成領域は複数設けられ、

前記パルス発振したレーザー光の照射により、前記一対の第1の島状結晶質シリコン層の一方を種に成長した結晶と、前記一対の第1の島状結晶質シリコン層の他方を種に成長した結晶と、がぶつかって形成された結晶粒界が前記第2の領域に発生し、30

前記結晶粒界は、複数ある前記チャネル形成領域のうち隣接する前記チャネル形成領域の間に配置されることを特徴とする半導体装置の作製方法。

#### 【請求項12】

請求項2乃至請求項4のいずれか一項において、

前記一対の島状結晶質シリコンゲルマニウム層の側面に凹凸形状が形成されており、40

前記凹凸形状は、前記第2の領域と接するように設けられていることを特徴とする半導体装置の作製方法。

#### 【請求項13】

請求項7乃至請求項9のいずれか一項において、

前記パルス発振したレーザー光の照射により、前記一対の島状結晶質シリコンゲルマニウム層の一方を種に成長した結晶と、前記一対の島状結晶質シリコンゲルマニウム層の他方を種に成長した結晶と、がぶつかって形成された結晶粒界が前記第2の領域に発生し、45

前記チャネル形成領域には、前記結晶粒界が含まれないことを特徴とする半導体装置の作製方法。

#### 【請求項14】

50

請求項 7 乃至請求項 9 のいずれか一項において、

前記チャネル形成領域は複数設けられ、

前記パルス発振したレーザー光の照射により、前記一対の島状結晶質シリコンゲルマニウム層の一方を種に成長した結晶と、前記一対の島状結晶質シリコンゲルマニウム層の他方を種に成長した結晶と、がぶつかって形成された結晶粒界が前記第 2 の領域に発生し、

前記結晶粒界は、複数ある前記チャネル形成領域のうち隣接する前記チャネル形成領域の間に配置されることを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【0001】

【発明が属する技術分野】

10

本発明は結晶構造を有する結晶質半導体膜で活性層を形成した半導体装置及びその作製方法に関する。特に、本発明は結晶質半導体膜で活性領域を形成する薄膜トランジスタ、前記薄膜トランジスタを用いた集積回路などの半導体装置、それらの半導体装置の作製方法に関する。なお、本明細書において半導体装置とは、半導体特性を利用して機能する装置全般のことをいい、例えば半導体集積回路、アクティブマトリクス型表示装置、半導体集積回路やアクティブマトリクス型表示装置などを搭載した電子機器などその他の電子機器が含まれる。

【0002】

【従来の技術】

20

フラットパネルディスプレイの1種であるアクティブマトリクス型ディスプレイの開発においては、画素部の素子や、画素部を駆動する集積回路のトランジスタとして、結晶構造を有する結晶質半導体膜を活性層に用いた薄膜トランジスタ（以下、TFTと記す。）を作製する技術が開発され、同一のガラス基板や石英基板上に、画素部と当該画素部の駆動に必要な駆動回路などの集積回路を集積したモノシリック型ディスプレイが、実現されている。現在では、非晶質シリコン膜を結晶化した多結晶シリコン膜を用いた TFT で作製されたアクティブマトリクス型液晶表示装置を搭載したノートパソコンや携帯電話など、様々な商品が販売されている。

【0003】

モノシリック型のアクティブマトリクス型ディスプレイのさらなる高画素化・高精細化を実現するには、動作速度の速い、即ち高い電界効果移動度の TFT が求められている。高い電界効果移動度とするためには、非晶質シリコン膜を結晶化した結晶質シリコン膜を用いて TFT を作製する必要があり、このため、シリコン膜など結晶化技術について鋭意研究がされている。結晶化技術として、非晶質半導体膜を加熱炉や R T A 装置により加熱して固相成長させる方法、レーザー光の照射により加熱して結晶化させる方法などが知られている。

30

【0004】

TFT の電界効果移動度を高くするには、散乱されることなく、キャリアをチャネルでスムーズに移動させればよいが、現在実用化されている結晶質シリコン膜を用いた TFT では、チャネルに多くの粒界があるため、シリコンウェハを用いたトランジスタほど TFT の電界効果移動度を高くすることができない。

40

【0005】

そこで、TFT の電界効果移動度を単結晶シリコンウェハのトランジスタに近づけるため、チャネルの半導体の結晶粒を大きくすることが試みられている。結晶粒を大きくすることで、TFT のチャネルでの半導体の結晶粒界の数が少なくなるため、キャリアが結晶粒界で散乱される確率を少なくすることができるからである。

【0006】

また、半導体中のキャリアの流れ易さは、結晶方位によっても異なることが知られているが、従来の結晶化技術ではチャネルの内を流れるキャリアの方向の結晶方位をそろえることは非常に困難である。上記のような従来の結晶化技術では、非晶質シリコン膜に偶発的に発生した結晶核を種として結晶成長するため、結晶粒界を全くなくすこともできないし

50

、また結晶粒界の位置や、結晶方位を制御することも非常に困難である。

**【0007】**

このように結晶粒界の位置や結晶方位をそろえることができないということは、結晶化されたシリコン膜は場所ごとに結晶構造が違うということであり、よって同じシリコン膜を用いてTFTを作製しても、場所ごとにTFTの特性がばらつくという原因の1つともなる。

**【0008】**

さらに、TFTには、電界効果移動度の他、スイッチング素子として、しきい値電圧値が小さいこと、サブスレッショルド値(S値)が小さいという特性も求められている。これらの特性を良くするには、チャネル部の半導体膜の膜厚を薄くすると良いことが知られている。これは、チャネル部の半導体膜を薄くすると膜厚方向(縦方向)への空乏層(チャネル)の広がりが抑制されるため、I-V特性のサブスレッショルド領域の特性が改善されるためである。

10

**【0009】**

多結晶シリコン膜を用いたTFTの場合であれば、通常チャネル形成領域の膜厚は60nm以下程度までに薄くすることが望ましい。しかしながら、加熱炉などを用いた固相成長による結晶化の場合、膜厚が薄くなると、結晶粒径が大きくなりにくくなる。

**【0010】**

また、YAGレーザーなどの連続発振レーザー光や、エキシマレーザーなどのパルス発振レーザー光による結晶化の場合も、成長の場合と同様に、非晶質シリコン膜の膜厚を薄くすることは難しい。それは、アブレーションしやすくなり、最適なエネルギーのマージンが狭くなるという新たな問題点が生ずるからであり、連続発振レーザー光の場合では、60nm以上、エキシマレーザーの場合では50nm以上の厚さにしないと、最適なエネルギーを設定することが難しくなり、また再現性よく結晶化することも難しくなる。

20

**【0011】**

また従来から、TFTのチャネル部の半導体膜を薄くするには、熱酸化を用いる方法が知られているが、この方法では、石英基板やシリコンウエハのような耐熱性のある限定された基板しか用いることができない。

**【0012】**

例えば、下記の特許文献1には、従来のエキシマレーザー光による結晶化のプロセスマージンが狭いという問題点を解消するための非晶質シリコン膜の結晶化方法が記載されている。

30

**【0013】**

特許文献1には、2本の帯状の非晶質シリコン膜を形成し、それをエキシマレーザーにより溶融再結晶化し、2本の多結晶シリコン膜を形成する。その上層に非晶質シリコン膜を形成する。そして固相成長法により、2本の帯状の多結晶シリコン膜を種結晶として、上層の非晶質シリコン膜を結晶化させて、多結晶シリコン膜を形成していることが記載されている。また、この上層の多結晶シリコン膜は、下層の2本の帯状多結晶シリコン膜を種として結晶成長させることにより、結晶粒の粒径を均一にし、かつ大きな粒径とすることできることが記載されている。

40

**【0014】**

**【特許文献1】**

特開2001-127301公報(公報5~7頁、第1実施形態参照)

**【0015】**

**【発明が解決しようとする課題】**

上述したように従来のレーザーニールによる結晶化や、電気炉を用いた固相成長による非晶質シリコンの結晶化では、偶発的に発生した結晶核からの結晶成長によるものであり、結晶核の生成位置と生成密度を制御することができず、しかも、結晶質半導体膜の面方位を制御することはされていない。

**【0016】**

50

例えば、上記の特許文献1には、結晶粒を大粒径化し、その大きさを均一にすることは記載されているが、結晶の面方位を制御することは記載されていない。

#### 【0017】

本発明は、上記の問題点を解消し、電界効果移動度が高く、スレッショルド特性がよい薄膜トランジスタを提供し、また多数の薄膜トランジスタを特性のばらつきが小さくなるように作製することを目的とするものである。

#### 【0018】

また、本発明は、チャネルとなる結晶質半導体膜の結晶粒界の位置、及び結晶粒の結晶方位を制御することにより、結晶粒界の方向がチャネル長方向に平行になるように、かつ結晶成長する軸の方位が一様になるように結晶成長させることを可能にする方法を提供するものである。なおかつ、ガラス基板のような600程度の歪み点の基板が利用可能な方法であることを特徴とする。

10

#### 【0019】

##### 【課題を解決するための手段】

上述したように、従来の電気炉やレーザー光を用いた非晶質シリコン膜の結晶化は、偶発的に発生した結晶核からの結晶成長によるものであり、結晶核の生成位置と生成密度を制御することができず、しかも、結晶質半導体膜の結晶面の方位をそろえることや、結晶粒界の位置を制御することができない。

上述の課題を解消するため、薄膜トランジスタをなどの半導体素子のチャネル形成領域に用いられる結晶質半導体層の新たな作製方法を提供する。

20

#### 【0020】

本発明にかかる半導体装置は、2つの第1の結晶質半導体層と、前記2つの第1の結晶質半導体層上に接して設けられた第2の結晶質半導体層とが積層された半導体を備えた薄膜トランジスタを有する半導体装置であって、前記薄膜トランジスタのソース領域および前記ドレイン領域は、それぞれ、前記第1の結晶質半導体層と第2の結晶質半導体層とが積層した部分に設けられ、チャネル形成領域は前記第2の結晶質半導体層でなり、前記第2の結晶質半導体層のチャネル形成領域は、{001}、{101}および{111}の結晶面のうち、{111}の割合が最も高いことを特徴とする。

#### 【0021】

また、本発明にかかる他の半導体装置は、2つの第1の結晶質半導体層と、前記2つの第1の結晶質半導体層上に接して設けられた第2の結晶質半導体層とが積層された半導体層を備えた薄膜トランジスタを有する半導体装置であって、前記薄膜トランジスタのソース領域および前記ドレイン領域は、それぞれ、前記第1の結晶質半導体層と第2の結晶質半導体層とが積層した部分に設けられ、チャネル形成領域は前記第2の結晶質半導体層でなり、前記第2の結晶質半導体層のチャネル形成領域は、{001}、{101}および{111}の結晶面のうち、{101}の割合が最も高いことを特徴とする。

30

#### 【0022】

半導体の結晶方位の分布は反射電子回折パターン(EBSP: Electron Backscatter diffraction Pattern)により求める。EBSPは走査型電子顕微鏡(SEM: Scanning Electron Microscope)に専用の検出器を設け、一次電子の後方散乱から結晶方位を検出する手法である(以下、この手法を便宜上EBSP法と呼ぶ。)。

40

#### 【0023】

結晶構造を持った試料に電子線が入射すると、後方にも非弾性散乱が起こり、その中には試料中でブレーキング回折による結晶方位に特有の線状パターン(一般に菊地像と呼ばれる。)も合わせて観察される。EBSP法は検出器スクリーンに映った菊地像を解析することにより試料の結晶方位を求めている。

#### 【0024】

多結晶構造の試料は各結晶粒が異なった結晶方位を持っている。試料の電子線が当たる位置を移動させつつ方位解析を繰り返すこと(マッピング測定)で、面状の試料について結晶方位または配向の情報を得ることができる。入射電子線の太さは、走査型電子顕微鏡の電

50

子銃のタイプにより異なるが、ショットキー電界放射型の場合、スポット径が 10 ~ 20 nm の非常に細い電子線が照射される。マッピング測定では、測定点数が多いほど、また測定領域が広いほど、結晶配向のより平均化した情報を得ることができる。実際には、 $100 \times 100 \mu\text{m}^2$  の領域で、10000点(1 μm 間隔) ~ 40000点(0.5 μm 間隔)の程度の測定を行っている。

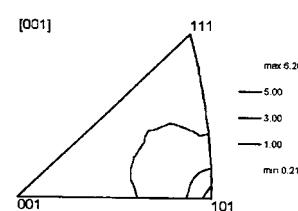

#### 【0025】

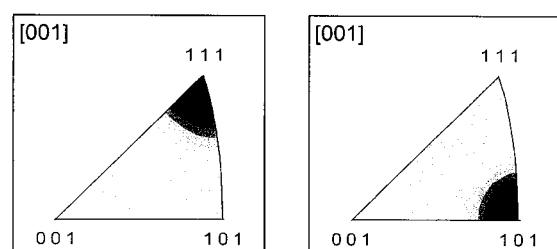

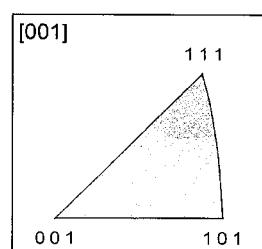

マッピング測定により各結晶粒の結晶方位がすべて求まると、膜に対する結晶配向の状態を統計的に知ることができる。図35は、多結晶構造のシリコン膜のEBSP法により求められる標準三角形の一例を示す。標準三角形は多結晶構造の試料の優先配向を表示する際によく用いられるもので、試料のある特定の面(ここでは膜表面)が、どの格子面に一致しているかを集合的に表示したものである。10

#### 【0026】

図35(A)の扇形状の枠は一般に標準三角形と呼ばれるもので、この中に立方晶系における全ての指数が含まれている。またこの図35中における長さは、結晶方位における角度に対応している。たとえば {001} と {101} の間は 45 度、 {101} と {111} の間は 35.26 度、 {111} と {001} の間は 54.74 度である。また、白抜きの点線は {101} からのずれ角 5 度及び 10 度の範囲を示している。

#### 【0027】

図35(A)は、マッピングにおける全測定点(この例では 11,655 点)を標準三角形内にプロットしたものである。 {101} 付近で点の密度が濃くなっていることがわかる。図35(B)は、このような点の集中度を等高線表示したものである。図中の数値は各結晶粒が完全に無秩序な配向だと仮定した場合、すなわち標準三角形内に点を偏りなく分布させた場合に対する倍率を示しており無次元数である。20

#### 【0028】

特定の指数(ここでは {101} )に優先配向していることがわかった場合、その指数近傍にどの程度の結晶粒が集まっているか、その割合を数値化することで、優先配向の度合いをよりイメージしやすくなる。

#### 【0029】

例えば図35(A)に例示した標準三角形において、 {101} からのずれ角(許容値の角度)を 5 度以内、 10 度以内と適宜に決めて、(図中に白点線で示す。)に存在する点数の全体に対する割合を配向率として次式により求めることができる。30

#### 【0030】

$\{101\}$  配向率 =  $\{101\}$  格子面と膜表面とがなす角度が許容値以内の測定点の数 ÷ 測定点の総数

#### 【0031】

この割合は、次のように説明することもできる。図35(A)のような {101} 付近に分布が集中している実際の結晶質シリコン膜においては、各結晶粒の <101> 方位は基板に垂直な方向であるが、基板に対する理想的な法線方向ではなく、各結晶粒の結晶軸は法線の周りにやや揺らぎを持って並んでいると考えられる。この揺らぎの角度(法線からのずれ角)を許容値として、例えば 5 度、 10 度と設定して、それより、結晶軸の法線方向からの揺らぎがこの許容値よりも小さいものを上記の式における右辺の分子として配向率を算出するのが、上記の式の意味するところである。40

#### 【0032】

例えば、ある結晶粒の <101> 方位は、許容角度が 5 度の範囲には含まれないが、許容角度が 10 度の範囲には含まれていることになる。後述のデータにおいては、上記のずれ角の許容値を 5 度と定め、それを満たす結晶粒の割合として、結晶の配向率を算出すればよい。

#### 【0033】

なお、本明細書中において、走査型電子顕微鏡としては、日立サイエンスシステムズ社製の S-4300SE 形走査電子顕微鏡を行い、専用の検出器には、TSL 社製の「Orient

10

20

30

40

50

ation Imaging Microscope」を用いている。

**【0034】**

本発明においては、チャネル形成領域となる半導体層を結晶化するために、下層に、結晶成長の種となる第1の結晶質半導体膜を形成し、当該の結晶質半導体膜の上に密着させて、上層に非晶質半導体膜を形成する。さらに、上層の非晶質半導体膜に連続発振レーザー光またはパルス発振レーザー光を基板に対して相対的に移動しながら照射することにより、下層の結晶質半導体を種にして、上層の非晶質半導体膜を結晶化させる。得られた上層の結晶質半導体層を薄膜トランジスタやダイオードなどの半導体素子のチャネルとして用い、また、下層の第1の結晶質半導体層と上層の第2の結晶質半導体層が重なっている領域を、ソース領域、ドレイン領域などの不純物領域に用いることを特徴とする。

10

**【0035】**

本発明においては、結晶の種となる下層の結晶質半導体膜の結晶方位をそろえ、結晶方位がそろっている結晶面から上層の非晶質半導体層をキャリアの流れる方向（チャネル長方向）に平行になるように結晶成長（ラテラル成長）させることで、チャネル長方向について、結晶質半導体層の結晶方位を一様なものとし、また結晶粒界の位置を制御する。

**【0036】**

このため、本発明の下層の第1結晶質半導体層を形成する方法の1つは、基板の上に非晶質半導体である第1の半導体膜を形成し、半導体の結晶化工エネルギーを低下させる金属元素を前記第1の半導体膜に選択的に添加し、加熱処理により、前記第1の半導体膜を結晶化し、結晶化された前記第1の半導体膜を所定の形状にパターニングして、第1の結晶質半導体層を形成することを含む方法である。得られる第1の結晶質半導体層は、{001} {101} および {111} の結晶面のうち、{111} の配向率が最も高くなっている。

20

**【0037】**

上記第1の非晶質半導体膜として、シリコン、シリコンとゲルマニウムの化合物 ( $\text{Si}_x \text{Ge}_{1-x}$  ( $0 < x < 1$ ))、ゲルマニウムの単体である非晶質ゲルマニウムが用いられる。

**【0038】**

前記金属元素は、シリコン (Si) やゲルマニウム (Ge) と反応して金属化合物を形成する金属元素であって、Pd, Pt, Ni, Cr, Fe, Co, Ti, Au, Cu, Rh のいずれかの元素を用いることができる。

30

**【0039】**

上記金属元素としては、Ni が最も好適に用いることができる。半導体がシリコンである場合を例に取ると、ニッケルとシリコンが反応してできるニッケルシリサイド ( $\text{Ni}_3\text{Si}_2$ ) は萤石型の結晶構造であり、 $\text{Ni}_3\text{Si}_2$  の格子定数は、他のシリサイドに対して、単結晶シリコンの格子定数に最も近いからと考えられる。

**【0040】**

前記金属元素を添加する方法は、金属元素や金属元素の化合物を溶解させた溶液や、金属元素や金属元素の化合物を含むペーストを塗布する方法や、スパッタ法やCVD法により金属元素や金属元素の化合物を非晶質半導体膜上に形成する方法や、プラズマドーピングやイオン注入法など金属元素のイオンを加速して半導体膜に添加する方法や、金属元素を含むプラズマで非晶質半導体膜を処理する方法などがあげられる。

40

**【0041】**

ニッケルなどの金属元素が半導体と反応して、金属化合物（シリコンの場合ならシリサイド）を形成するために要するエネルギーは、非晶質シリコン等の半導体を結晶化させるためのエネルギーよりも低い。そのため、非晶質シリコン膜などを金属元素と反応させて化合物を形成することで結晶化を行うことで、半導体膜に自然核が発生するよりも低い温度（エネルギー）で結晶化させることができる。

**【0042】**

上記の第1の結晶質半導体の結晶化方法においては、第1の非晶質半導体膜の部分的に金

50

属元素を添加することにより、ある所定の結晶面に対する配向率が高い結晶質半導体膜を形成する方法であるが、シリコンを主成分としゲルマニウムを含む非晶質半導体を第1の半導体膜として形成することで、金属元素を添加する位置を特に制御しなくとも、{001} {101} および{111}の結晶面のうち、{101}の配向率が最も高い結晶質半導体膜を形成することが可能になる。

#### 【0043】

すなわち、本発明の下層の第1の結晶質半導体層を形成する他の方法は、基板の上にゲルマニウムを含むシリコンを主成分とする非晶質半導体膜でなる第1の非晶質半導体膜を形成し、半導体の結晶化工エネルギーを低下させる金属元素を前記第1の非晶質半導体膜に添加し、前記第1の非晶質半導体膜を加熱することにより、結晶化し、結晶化された第1の結晶質半導体膜を所定の形状にパターニングして、結晶質半導体でなる第1結晶質半導体層を形成することを含むものである。 10

#### 【0044】

上記の第1の結晶質半導体層を形成する方法において、用いられる金属元素、および金属元素の添加方法、また非晶質半導体でなる第1の半導体を結晶化する方法は、上述した{111}の配向率が最も高い結晶質半導体層を形成する場合と同じにすることができる、前記金属元素としては、シリコン(Si)やゲルマニウム(Ge)と反応して金属化合物を形成する金属元素であって、Pd, Pt, Ni, Cr, Fe, Co, Ti, Au, Cu, Rhのいずれかの元素を用いることができる。 20

#### 【0045】

前記金属元素を添加する方法は、金属元素や金属元素の化合物を溶解させた溶液や、金属元素や金属元素の化合物を含むペーストを塗布する方法や、スパッタ法やCVD法により金属元素や金属元素の化合物を非晶質半導体膜上に形成する方法や、プラズマドーピングやイオン注入法など金属元素のイオンを加速して半導体膜に添加する方法や、金属元素を含むプラズマで非晶質半導体膜を処理する方法などがあげられる。 20

#### 【0046】

上記の金属元素を用いた非晶質半導体膜を結晶化のための加熱は、電気炉での加熱処理や、赤外光ランプによる熱放射を利用する方法など、非晶質半導体膜を固相成長できる手段が選ばれる。 30

#### 【0047】

また、本発明においては、金属元素を用いて第1の非晶質半導体膜を結晶化した場合には、結晶化後、結晶化された第1の半導体膜から意図的に添加した金属元素を除去するために、ゲッタリング処理を行ってもよい。 30

#### 【0048】

ゲッタリングの方法には、結晶化された半導体膜上にゲッタリングシンクとなる膜を形成し、加熱処理を行って、ゲッタリングシンクに金属元素を吸い取らせる方法があげられる。ゲッタリングシンクとなる膜は、アルゴンを含んだ非晶質シリコン膜や、リンを含んだ非晶質シリコン膜などを用いることができる。

#### 【0049】

これまで、種となる第1の半導体膜の結晶化方法として、金属元素を添加して結晶化する方法を説明したが、金属元素を添加しない結晶化方法を用いることができる。その結晶化方法の1つは、下層の非晶質半導体を連続発振レーザー光により結晶化するものであり、その1つは、基板の上に非晶質半導体でなる第1の半導体膜を形成し、連続発振レーザー光による照射領域を前記基板に対して相対的に移動させながら、前記第1の半導体膜に前記連続発振レーザー光を照射して、結晶化させ、結晶化された前記第1の半導体膜を所定の形状にパターニングし、結晶質半導体でなる第1の結晶質半導体層を形成するという構成を有する。 40

#### 【0050】

他の1つは、基板の上に非晶質半導体でなる第1の半導体膜を形成し、非晶質半導体でなる前記第1の半導体膜を所定の形状にパターニングして、第1の非晶質半導体層を形成し 50

、連続発振レーザー光による照射領域を前記基板に対して相対的に移動させながら、前記第1の非晶質半導体層に前記連続発振レーザー光を照射して、結晶化させて、第1の結晶質半導体層を形成することを有する方法である。

#### 【0051】

本発明では、第1の結晶質半導体層は所定の形状にパターニングされるが、その形状は、特徴的には、上層の第2の非晶質半導体膜を結晶化するための種結晶となると共に、薄膜トランジスタのソース領域や、ドレイン領域のような、電極や配線との接続部としても機能するようにパターニングされる。

#### 【0052】

そして、本発明では、上述したいずれかの方法により形成された第1の結晶質半導体層上に、前記第1の結晶質半導体層の上に接して、非晶質半導体でなる第2の半導体膜を形成し、前記第1の結晶質半導体層と重なる領域と重ならない領域とを含むように、前記第2の半導体膜を所定の形状にパターニングして、第2の非晶質半導体層を形成し、連続発振レーザー光を前記基板に対して相対的に移動させながら、前記第2の非晶質半導体層に照射して、前記第2の非晶質半導体層を結晶化し、第2の結晶質半導体層を形成する半導体装置の作製方法であって、前記第2の非晶質半導体層の結晶化において、前記第2の非晶質半導体層が前記第1の結晶質半導体層と重なっている領域から、前記第1の結晶質半導体層と重なっていない領域へと、前記連続発振レーザー光の照射領域を移動させることを特徴とする。

#### 【0053】

また、本発明では、第2の非晶質半導体層を結晶化するのに、連続発振レーザー光を照射する代りに、パルス発振レーザー光を照射してもよい。この場合はレーザー光の移動方法が異なり、前記第2の非晶質半導体層の結晶化において、前記第2の非晶質半導体層が前記第1の結晶質半導体層と重なっている領域と、前記第1の結晶質半導体層と重なっていない領域との双方が、前記パルス発振レーザー光の照射領域に含まれるように、前記パルス発振レーザー光を移動させる。

#### 【0054】

上述したように照射領域を移動しながら連続発振レーザー光またはパルス発振レーザー光を照射することで、前記第1の結晶質半導体層を種として、第2非晶質半導体層において被形成面（基板の平面）に対して水平方向に結晶成長が進行し、また、第1結晶質半導体層の結晶面を複写するように進行する。

したがって、第1の結晶質半導体層の結晶方位がそろっている面から結晶成長させることで、第2結晶質半導体層の第1結晶質半導体層と重なっていない領域を一定方向に、かつ結晶方位をそろえて結晶成長させることができる。

#### 【0055】

よって、上記結晶構造を有する第2結晶質半導体層の第1結晶質半導体層と重なっていない領域を半導体素子のチャネル形成領域とする場合には、この領域の結晶成長方向がチャネル長方向（キャリアの移動方向）と平行になるようとする。

#### 【0056】

本発明において、半導体の結晶構造が非晶質であるとは、狭義の意味での非晶質構造を指すだけでなく、部分的に微結晶を含む非晶質半導体をも含むものとする。

#### 【0057】

本発明において、連続発振レーザー光は、気体レーザー発振装置、固体レーザー発振装置から射出されるレーザー光が選択できる。例えば、固体レーザー発振装置としては、YAG、 $\text{YVO}_4$ 、YLF、 $\text{YAlO}_3$ などの結晶にCr、Nd、Er、Ho、Ce、Co、Ti又はTmをドープした結晶を使ったレーザー発振装置がある。このレーザー発振装置から射出される基本波の波長は、結晶にドープされる元素によっても異なるが、1 μmから2 μmの範囲の波長である。

#### 【0058】

また、気体レーザー発振装置としては、アルゴンレーザー、クリプトンレーザーなどの気

10

20

30

40

50

体レーザー発振装置が選択できる。

【0059】

本発明においては、パルス発振レーザーには、ArF、KrF、XeCl等のハロゲン化物の気体を用いたエキシマレーザー発振装置や、Cr、Nd、Er、Ho、Ce、Co、Ti又はTmをドープしたYAG、YVO<sub>4</sub>、YLF、YAlO<sub>3</sub>などの結晶を用いた固体レーザー発振装置を用いることができる。エキシマレーザー発振装置から射出されるレーザー光は、400nm～200nmの波長域の紫外光であるが、固体レーザー光の場合、結晶から励起される基本波の波長が1～2μm程度である。

【0060】

レーザー光のエネルギーが効率よく非晶質半導体膜の結晶化に使われるために、結晶化させる非晶質半導体膜に実際に照射される連続発振レーザー光の波長は、非晶質半導体膜で効果的に吸収される波長、可視域から紫外域の波長とするのが好ましい。したがって、レーザー発振装置で励起される基本波が1μmから2μmのレーザーの場合ならば、基本波の第2高調波～第4高調波を適用するのが好ましい。

代表的には、非晶質珪素膜の結晶化に際して、Nd:YVO<sub>4</sub>レーザー発振装置（連続発振でもパルス発振でも）の場合、結晶から励起される基本波の波長は1064nmであるので、照射するレーザー光は第2高調波（532nm）を用いるとよい。

【0061】

なお、本明細書において、半導体の結晶化以外にも連続発振レーザー光やパルス発振レーザー光を照射する場合は、上記のレーザー装置が利用できる。

【0062】

また、本発明において、連続発振レーザー光またはパルス発振レーザー光による照射領域を基板に対して移動するとは、基板を固定し、走査光学系によりレーザー光を移動させてレーザー光により走査すること、またはレーザー光による照射領域を固定し、移動機構を備えたステージによって基板を移動させることで、レーザー光を走査させること、さらに、レーザー光の照射領域と基板双方を移動させることも含む。

【0063】

また、本発明において、結晶化のエネルギーを低下させる作用を有する金属元素を用いて、第1の結晶質半導体層を形成する場合は、膜厚は50nm～100nm程度であればよい。これは膜厚が50nmよりも薄くなると、上記のような結晶成長が進行しにくくなるからである。また、膜厚が100nmを超えると、膜厚方向では結晶粒を1つにすることが難しく、また、結晶化に必要な金属元素が多くなるからである。

【0064】

また、連続発振レーザー光を用いて第1の結晶質半導体層を形成する場合は、30nm～400nm、より好ましくは100nm～150nmであればよい。

【0065】

また、従来では、連続発振レーザー光を用いて非晶質半導体膜を結晶化する場合は、照射エネルギーのマージン等の問題のため、その膜厚を60nmよりも厚くする必要がある。本発明では、第2の非晶質半導体膜を結晶化するために、連続発振レーザー光を用いるが、第2の結晶質半導体層は第1の結晶質半導体層を種として結晶成長させるので、結晶成長のための核生成位置を制御することができるようになる。そのため、第2の結晶質半導体層の厚さを60nm以下、10～60nmの範囲に薄くすることができ、さらに、10～40nmの範囲がより好ましい。

【0066】

また、パルス発振レーザー光を用いて結晶化する場合も、従来では50nmよりも薄い非晶質半導体膜を結晶化することは困難であったが、本発明の場合は、上記の同様の理由で、第2の結晶質半導体層の厚さを50nm以下、10～50nmの範囲に薄くすることができ、40nm以下がより好ましい。

【0067】

なお、第2の非晶質半導体層の厚さの下限は、成膜手段に大きく依存し、ピンホールがな

10

20

30

40

50

いこと、再現性の点などから、10 nm以上、20 nm以上が好ましい。

【0068】

【発明の実施の形態】

図1～25を用いて本発明の実施形態を説明する。

【0069】

【実施形態1】

本実施形態では、第1非晶質半導体膜に結晶化を促進する金属元素を選択的に添加することにより、第1結晶質半導体層を形成する方法の一例を説明する。本実施形態では、ニッケル(Ni)を用い、また金属元素の添加方法として、溶液を用いる方法を説明する。

【0070】

10

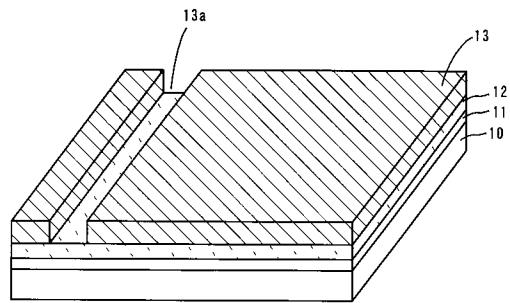

(図1参照)

結晶質半導体層を形成するための基板10を用意する。基板10は、バリウムホウケイ酸ガラス、またはアルミニウムホウケイ酸ガラスなどのガラスでなるものや、石英や、シリコンウエハなど、半導体装置の用途や、温度などプロセス条件によって適宜選択することができる。プロセス温度に耐え得れば、耐熱性の高いプラスチック材料、例えばポリカーボネイド、ポリイミド、アクリル材料でなる基板を用いることもできる。また基板10の形状は平面、曲面あるいは両方を有するものであり、平板状、帯状、長尺のものなど、プロセスや製造装置によって適宜選択される。

【0071】

20

基板10にガラスのような不純物を含むようなガラス基板を用いる場合には、非晶質半導体でなる第1の半導体膜12を形成する前に、半導体膜が汚染されるのを防ぐために、下地膜11となる絶縁膜を形成する。この絶縁膜としては、酸化珪素膜、窒化珪素膜、窒化酸化珪素膜、窒化アルミニウム膜、ダイヤモンドライクカーボン膜などの単層又はこれらを適宜組み合わせた多層膜を形成する。また、成膜方法は、スパッタリング法、プラズマCVD法等公知の方法を採用できる。

【0072】

次に、下地膜11に密着して、第1の非晶質半導体膜12を形成する。ここでは非晶質シリコン膜を形成する。形成方法は、スパッタリング法、プラズマCVD法、減圧CVD法などの公知の成膜方法を採用できる。

【0073】

30

また、非晶質半導体でなる第1の非晶質半導体膜12の厚さは50 nm～100 nmとすることができる。第1の非晶質半導体膜12は結晶化され、最終的にTFTのソース領域やドレイン領域を構成するため、あまり薄いと、ソース、ドレイン領域のシート抵抗が高くなってしまうからである。また、後述するように{111}の配向率を高くするために、膜が薄いと結晶化のためのマージンが非常に狭くなるため、50 nm以上とすることが望まれる。

【0074】

次に、マスク膜13を形成する。このマスク膜13は、半導体の結晶化工エネルギーを低下させる金属元素を第1の非晶質半導体膜12に選択的に添加するためのものである。マスク膜13としては、後に除去するため、第1非晶質半導体膜12とエッチング選択性がある膜が好ましく、レジストや酸化シリコン、窒化シリコンなどの絶縁膜を用いることができる。

40

【0075】

また、マスク膜13には、溝状(スリット状)の開口部13aが設けられており、この開口部13aを通して金属元素を非晶質半導体膜12に添加する。開口部13aの溝の大きさは特に限定はないが、その幅は10～40 μm、長手方向の長さは、回路配置にあわせて任意で設定すればよい。また開口部13aの形状は溝状に限定されるものではなく、点状など任意に決めることができる。

【0076】

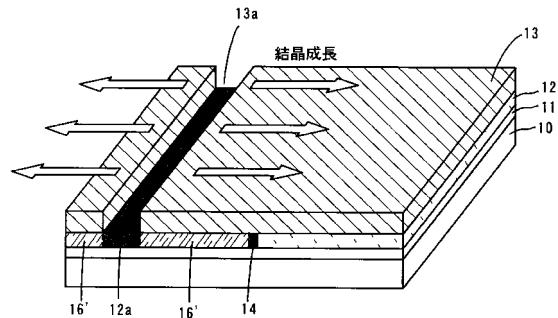

(図2参照)

50

次に、前記金属元素を添加するため、スピナーを用いて、ニッケルを含む溶液を基板全面に塗布して、ニッケル層14を形成する。溶液としては、酢酸ニッケル、硝酸ニッケル等の金属塩を水やエタノールに溶かした溶液を用いることができる。溶液を塗布する方法は、添加する金属元素の濃度を溶液の濃度を調節することで容易にできる点で有用である。

#### 【0077】

スピナーを用いて溶液を塗布すると、スピナーの回転により溶媒が乾燥し、溶液に溶けていたニッケルが基板平面に全面に残り、ニッケル層14を形成する。よって、ニッケル層14の厚さは単原子層程度であり、しかも完全な膜ではないと考えられるが、ニッケル原子が第1の非晶質半導体膜12の表面に接触させることができれば、所期の効果が得られることがわかっている。

10

#### 【0078】

ただし、非晶質シリコンが水をはじいてしまうため、水溶液を塗布する場合は均一に塗布できないので、マスク膜13の開口部13aにおいて露出している非晶質シリコンでなる第1の非晶質半導体膜12の表面に数nm程度のシリコンの酸化膜を形成して、表面の塗れ性を改善するとよい。

酸化膜が極薄ければ、ニッケルなどの金属元素は酸化膜中を通過して介して、領域12aにおいて第1の非晶質半導体膜12に選択的に接触させることができる。

#### 【0079】

酸化膜の形成方法は、スループットやプロセス温度を考慮すると、オゾンや酸素のような酸化性雰囲気でUV光を照射する方法、第1の非晶質半導体膜12の領域12aの表面にオゾンを含む水溶液をスピナーで塗布する方法など、短時間で、プロセス温度が低い方法が適当である。

20

#### 【0080】

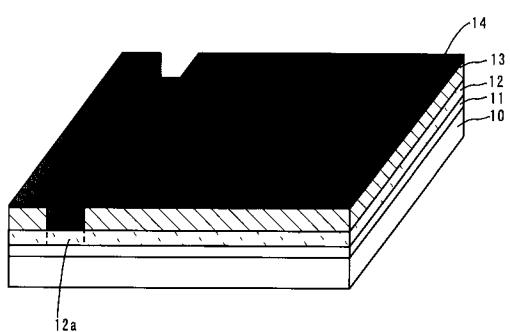

(図3参照)

マスク膜13が存在する状態で、加熱処理して、第1の非晶質半導体膜12を結晶化し、第1の結晶質半導体膜16を形成する。

加熱処理には、抵抗等を利用して加熱炉が用いられる。Niにより非晶質シリコン膜を結晶化する場合であれば、400～700、好ましくは500～600の温度で、4～24時間の加熱処理を行う。

#### 【0081】

30

また、シリコンを主成分としジルマニウムを含む非晶質半導体、1原子%～10原子%程度のジルマニウムを含む非晶質シリコン膜を結晶化させる場合であれば、非晶質シリコン膜の場合よりも加熱温度を若干高くする必要があり、500～700の温度、好ましくは550～600とする。

#### 【0082】

あるいは、アークランプやハロゲンランプなどの高出力のランプを利用したRTA方式の加熱装置において、加熱処理を行ってもよい。また、RTA方式の加熱装置において、アークランプやハロゲンランプによる加熱領域を線状にして、レーザー光の場合と同様に加熱領域を、ニッケルが添加された領域12aから、結晶成長させたい方向に基板に対して相対的に移動させて結晶成長させる方法も採用できる。

40

#### 【0083】

まず、結晶化は400～500の加熱処理により金属元素とシリコンが反応してシリサイドが形成され、これが結晶核となりその後の結晶成長に寄与する。ニッケルシリサイド(以下、NiSi<sub>2</sub>と記す)が形成される。NiSi<sub>2</sub>の構造はホタル石型構造であり、ダイアモンド型構造のシリコン格子間にニッケル原子を配置した構造となっている。NiSi<sub>2</sub>からニッケル原子が無くなるとシリコンの結晶が残ることになる。数々の実験の結果から、ニッケル原子は非晶質シリコン側に移動していくことが判明しており、この理由は非晶質シリコン中の固溶度の方が結晶シリコン中のそれよりも高いためであると考えられる。

#### 【0084】

50

よって、あたかもニッケルがニッケルシリサイド $1\cdot4$ を形成しつつ、第1の結晶質半導体膜（非晶質シリコン膜）1 $\cdot$ 2中を移動して、結晶質シリコン $1\cdot6'$ が形成されるようなモデルをたてることができる。

#### 【0085】

（図4参照）

以上のように、金属元素を選択的に添加することによって、いわゆるラテラル成長により非晶質シリコンでなる第1の非晶質半導体膜1 $\cdot$ 2が結晶化され、結晶質シリコンでなる第1の結晶質半導体膜1 $\cdot$ 6が形成される。加熱処理後、マスク膜1 $\cdot$ 3を除去する。

#### 【0086】

結晶質シリコンでなる第1の結晶質半導体膜1 $\cdot$ 6は、上述のように金属元素を選択的に添加して結晶化しているため、結晶粒の方位をそろえることができ、{001}{101}および{111}の結晶面のうち、{111}の割合が最も高い膜となることが、実験でわかっている。別の言い方をすると、基板表面（第1の結晶質半導体膜1 $\cdot$ 6の表面）の法線方向の結晶軸が<111>を示す結晶粒の割合が最も多い膜となっている、ということでもできる。結晶の配向については、測定データを用いて、実施形態2と共に後で説明する。

10

#### 【0087】

また、第1の非晶質半導体膜1 $\cdot$ 2を結晶化した後、連続発振レーザー光、パルス発振レーザー光または赤外光などを照射することで、第1の結晶質半導体膜1 $\cdot$ 6の結晶粒内にのこる結晶欠陥を少なくすることができます。

20

#### 【0088】

（図5参照）

エッチングにより、第1の結晶質半導体膜1 $\cdot$ 6を所定の形状にパターニングして、TFTのソース領域およびドレイン領域となる1対の第1の結晶質半導体層1 $\cdot$ 7を形成する。ただし、結晶成長の基点となった領域1 $\cdot$ 2aと結晶成長の終端の領域には、ニッケルが高濃度に含まれている。よって、このような領域は半導体素子に用いるのは好ましくないので、第1の結晶質半導体層1 $\cdot$ 7にはこれらの領域を含まないようにパターニングされる。

#### 【0089】

（図6（a）参照）

次に、第1の結晶質半導体層1 $\cdot$ 7に密着して、非晶質半導体でなる第2の非晶質半導体膜1 $\cdot$ 8を形成する。ここでは非晶質シリコン膜を形成する。また、成膜方法は、スパッタリング法、プラズマCVD法等の公知の方法を採用できる。

30

#### 【0090】

第2の非晶質半導体膜1 $\cdot$ 8の厚さは、10nm～60nm、好ましくは20nm～40nmとする。第2の非晶質半導体膜は結晶化され、最終的に薄膜トランジスタのチャネル形成領域となるため、第2の非晶質半導体膜1 $\cdot$ 8を60nm以下に薄く形成することで、チャネル形成領域の厚さが薄くなり、オフ状態でのリーク電流値を抑える効果や、オン電流／オフ電流比を高くする効果が期待できる。

#### 【0091】

（図6（b）、図6（c）参照）

40

次に、エッチングにより、TFTとなる領域を残して、第2の非晶質半導体膜（非晶質シリコン）1 $\cdot$ 8をパターニングして、第2の非晶質半導体層1 $\cdot$ 9を形成する。なお、2つの第1の結晶質半導体層1 $\cdot$ 7はそれぞれ、第2の非晶質半導体層1 $\cdot$ 9のパターンよりも大きく形成されていたため、このエッチングに用いられたマスクにより、第1の結晶質半導体膜1 $\cdot$ 7もパターニングされている。

#### 【0092】

図示のように、第2の非晶質半導体層1 $\cdot$ 9は、第1の結晶質半導体層1 $\cdot$ 7と重なる領域を含むようにパターニングされる。第1の結晶質半導体層1 $\cdot$ 7と重なっていない領域1 $\cdot$ 9aがTFTのチャネル形成領域となる領域である。図6（b）は上面図であり、同図（c）は同図（b）のx-x'断面図である。

50

**【 0 0 9 3 】**

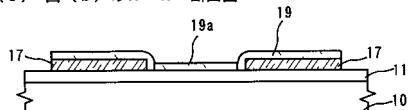

( 図 7 ( a ) ~ ( c ) 参照 )

図 7 ( a ) に示すように、連続発振レーザー光をその照射領域 2 1 が基板 1 0 に対して、チャネル長方向に平行な方向に、第 1 の結晶質半導体層 1 7 と重なっている領域から、重なっていない領域 1 9 a に向かって移動しながら照射する。

上記のように照射領域 2 1 を基板に対して相対的に移動しつつ、連続レーザー光を第 2 の非晶質半導体層 1 9 全体に照射することにより、第 2 の非晶質半導体層 1 9 全体を結晶化して、第 2 の結晶質半導体層 2 2 を形成する。

**【 0 0 9 4 】**

連続発振レーザー光による照射領域 2 1 は常時レーザーが照射されているので、照射領域では、第 2 の非晶質半導体層 1 9 は溶融されて、溶融部（液相） - 非溶融部（固相）の界面が形成される。よって、照射領域 2 1 を移動すると、この移動に伴って、液相 - 固相の界面が移動し、先に溶融していた部分が冷却して凝固していると考えられる。このような過程により第 2 の非晶質半導体層 1 9 が結晶化する。このため、第 2 の非晶質半導体層 1 9 は、溶融部分（照射領域 2 1 に該当する）の移動方向に結晶成長することとなり、基板 1 0 の表面（第 2 の非晶質半導体層 1 9 の表面）の水平方向に長い形状の結晶粒を成長させることができる（いわゆるラテラル成長）。

**【 0 0 9 5 】**

チャネル長方向に沿って 1 回ほど照射領域 2 1 を移動することで、少なくとも 1 つの第 2 の結晶質半導体層 1 9 全体に連続発振レーザー光が照射されるようにするために、図示のように連続発振レーザー光のビーム（光束）を一方向に拡大して、長軸のビームとなるようする。図 7 ( a ) ではビームの断面形状は四隅の丸い矩形状のように図示されているが、長楕円形であっても、線状であっても、矩形状であってもよい。

**【 0 0 9 6 】**

また、連続発振レーザー光の照射は、白抜きの矢印で示す移動方向に 1 回だけ移動しながら照射することに限定されるわけではなく、チャネル長方向に沿って往復したり、あるいは白抜きの矢印に示す 1 方向に複数回移動させたりすることも含む。

**【 0 0 9 7 】**

上述のように連続発振レーザー光による結晶化は、半導体を溶融させて結晶成長させるため、得られる結晶質半導体の結晶性は種となる結晶質半導体の結晶性に依存する。

**【 0 0 9 8 】**

よって、第 2 の結晶質半導体層 2 2 の領域（第 1 結晶質半導体層 1 7 と重なっていない領域）2 2 a は、第 1 の結晶質半導体層 1 7 を種として結晶成長するため、その結晶構造は第 1 の結晶質半導体層 1 7 の結晶構造を複写するように成長する。

**【 0 0 9 9 】**

第 1 の結晶質半導体層 1 7 の結晶は、{ 1 1 1 } に配向している割合が最も大きいため、第 2 の結晶質半導体層 2 2 の領域 2 2 a での結晶構造もまた、{ 0 0 1 }、{ 1 0 1 }、{ 1 1 1 } のうち、{ 1 1 1 } 配向率が最も高くなり、結晶面が { 1 1 1 } に揃ったものとすることができる。

**【 0 1 0 0 】**

( 図 7 ( d ) 参照 )

図 7 ( d ) は、第 2 の結晶質半導体層 2 2 における領域 2 2 a の、概略的な斜視図である。

本実施形態では、結晶化される第 2 の非晶質半導体膜を 6 0 nm 以下、さらには 4 0 nm 以下と薄くしても、チャネル形成領域となる領域 2 2 a のチャネル長方向の長さよりも結晶粒の結晶成長距離を十分に長することができますため、領域 2 2 a において、結晶成長方向であるチャネル長方向に平行な粒界 G B が存在するが、チャネル幅方向には存在しないようにすることを特徴とする。

**【 0 1 0 1 】**

連続発振レーザー光による結晶化によって、レーザー光の移動方向に、1 つの結晶を 1 0

10

20

30

40

50

$0 \mu m \sim 150 \mu m$  程度の距離まで結晶成長させることができるが、結晶化される半導体膜の膜厚が薄くなると、その結晶成長距離を長くすることが非常に難しくなることがわかっている。

#### 【0102】

本実施形態の場合、 $60 nm$  以下と薄くしても、領域 22a は第 1 の結晶質半導体層 17 を種として結晶成長させるため、その核生成位置を制御できること、あわせて TFT のような素子であれば通常、領域 22a の大きさはチャネル長 × チャネル幅程度の大きさであり、たかだか十数  $\mu m$  平方程度であることから、上記のように領域 22a において、結晶成長方向に平行なチャネル長方向に粒界 GB が存在するが、チャネル幅方向には存在しないようにすることが容易になる。

10

#### 【0103】

また、第 2 の結晶質半導体層 22 の領域 22a は膜厚方向には 1 つの結晶粒でなるため、領域 22a は、結晶粒界を少なくすることができると共に、上記のように粒界 GB は結晶成長方向に平行なチャネル長方向のみに形成されるようにできる。

#### 【0104】

このような結晶成長をさせるには、連続発振レーザー光の出力、照射領域の移動速度、照射領域の面積や移動方向の幅などを調節することで、連続発振レーザー光により半導体に与えるエネルギー密度を最適化することで実現することできる。

また、連続発振レーザー光を照射しているときに、基板を加熱したり、マイクロ波などを照射したりして、熱エネルギー、電磁エネルギーなどを半導体層に与えることで、結晶化のエネルギーを低下させるようにしてもよい。

20

#### 【0105】

以上の工程にて、薄膜トランジスタの活性層となる第 1 及び第 2 の結晶質半導体層が形成される。以降は、公知のトップゲート型薄膜トランジスタの製造方法にならって、薄膜トランジスタを形成することができる。

#### 【0106】

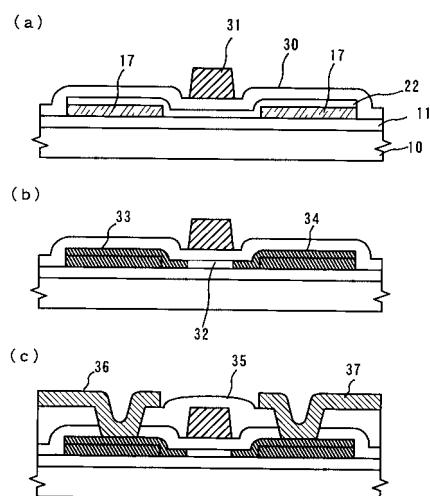

##### (図 8 (a) 参照)

例えば、第 2 の結晶質半導体層 22 上に、ゲート絶縁膜 30 を形成し、ゲート絶縁膜 30 上にゲート電極 31 を形成する。

#### 【0107】

30

##### (図 8 (b) 参照)

ゲート電極 32 をマスクにして、第 1 及び第 2 の結晶質半導体層 17、22 に、不純物をドープする。薄膜トランジスタを N チャネル型にするならば P (リン) をドープし、P チャネル型にする場合には B (ボロン) をドープする。その結果、第 1 及び第 2 の結晶質半導体層 17、22 が積層してなる活性層に、チャネル形成領域 32、ソース領域 33、ドレイン領域 34 およびが自己整合的に形成される。

#### 【0108】

##### (図 8 (c) 参照)

ゲート電極 32 上に層間絶縁膜 35 を形成する。ソース領域 33、ドレイン領域 34 を電極または配線に接続するために、層間絶縁膜 35 にコンタクトホールを形成し、ソース電極 36、ドレイン電極 37 を形成し、薄膜トランジスタが完成する。

40

#### 【0109】

ソース領域およびドレイン領域 33、34 は、第 1 の結晶質半導体層 17 と第 2 の結晶質半導体層 22 とが積層した部分に設けられている。チャネル形成領域 32 は、第 2 の結晶質半導体層 22 が第 1 の結晶質半導体層 17 と重なっていない領域 22a に設けられている。前記の構成は、トップゲート型 TFT および逆スタガーのようなボトムゲート型 TFT を作製した場合も共通である。

#### 【0110】

本実施形態の薄膜トランジスタにおいて、チャネル形成領域 32 を構成する第 2 の結晶質半導体層 22 は、結晶粒界がチャネル長方向に平行になり、キャリアの移動を妨げる粒界

50

をなくすように形成されるため、薄膜トランジスタの電界効果移動度を大きくすることができる。

#### 【0111】

また、多数の薄膜トランジスタを同一基板上に作製しても、チャネル形成領域となる第2の結晶質半導体層を{111}にそろえるようにしたため、素子ごとの特性のばらつきを抑えることができる。

#### 【0112】

また、10～40nm程度の薄いチャネル形成領域でも、上記のように結晶配向をそろえることができるため、電界効果移動度を大きくするだけでなく、しきい値電圧値、サブスレッショルド特性も良好なものとすることができます。

10

#### 【0113】

##### [実施形態2]

実施形態1では、金属元素を選択的に添加することにより、第1の結晶質半導体膜の結晶配向を{111}に優先配向させたものである。これに対して、本実施形態では、第1の非晶質半導体膜として、ゲルマニウムを添加したシリコン膜を用いることで、{101}に優先配向した第1の結晶質半導体膜を形成する方法を説明する。

#### 【0114】

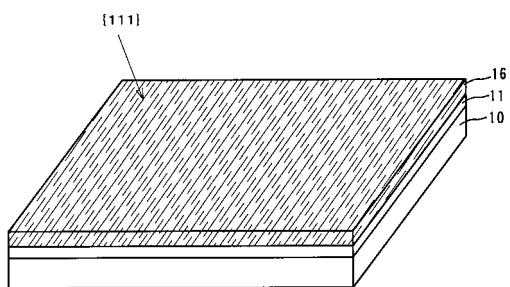

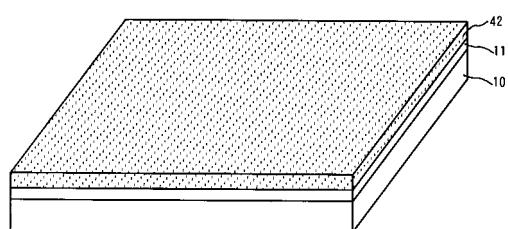

##### (図9参照)

まず、実施形態1と同様に、基板10に下地膜11を形成し、下地膜11上に、第1の非晶質半導体膜43として、非晶質のゲルマニウムを添加したシリコン膜を形成する。形成方法は、スパッタリング法、プラズマCVD法、減圧CVD法などの公知の成膜方法を採用できる。

20

#### 【0115】

プラズマCVD法を適用する場合には、SiH<sub>4</sub>とGeH<sub>4</sub>とからなる反応ガス、またはSiH<sub>4</sub>と、H<sub>2</sub>で希釈したGeH<sub>4</sub>とでなる反応ガスを加えて反応室に導入し、1～200MHzの高周波放電により分解し基板上に非晶質半導体膜を堆積させる。反応ガスは、SiH<sub>4</sub>の代わりにSi<sub>2</sub>H<sub>6</sub>またはSiF<sub>4</sub>を、GeH<sub>4</sub>の代わりにGeF<sub>4</sub>を採用しても良い。

減圧CVD法を用いる場合にも同じ反応ガスを用いることができ、Heで反応ガスを希釈したもの用いることが好ましい。また、400～500℃の温度で形成するとよい。

30

#### 【0116】

本実施形態において、第1の非晶質半導体膜42であるゲルマニウムを含むシリコンを主成分とする膜は、{101}の配向率を高くするために、そのゲルマニウムの含有量を1原子%～10原子%、好ましくは1～5原子%の範囲とする。ゲルマニウムの含有量は、CVD法の場合であれば、例えば、反応ガスとして用いられるSiH<sub>4</sub>とGeH<sub>4</sub>の流量比(分圧)で調節することができる。また、スパッタ法を用いる場合は、ターゲットに含まれるゲルマニウムの濃度や、反応ガスに用いたゲルマニウムを含むGeH<sub>4</sub>の流量により調節することができる。

#### 【0117】

##### (図10参照)

シリコンの結晶化工エネルギーを低下させる金属元素を前記第1の非晶質半導体膜42の表面全体に添加して、第1の非晶質半導体膜42の表面に金属元素を含む層を形成する。ここでは、スピナーを用いて酢酸ニッケル水溶液を塗布して、ニッケル層43を形成する。あるいは、第1の結晶質半導体膜42を形成する前に、下地膜11の表面に、上記のようにニッケル溶液を塗布してニッケル層43を形成してから、第1の非晶質半導体膜42を形成してもよい。

40

#### 【0118】

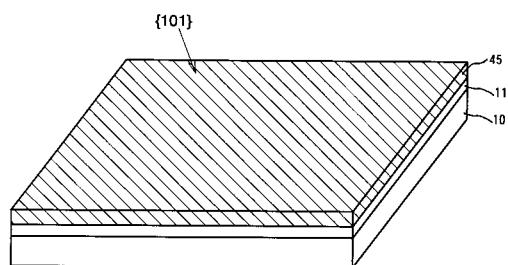

##### (図11参照)

前記金属元素を導入した後、当該金属元素を利用して非晶質半導体膜を結晶化することにより、{101}が優先的に配向している第1の結晶質半導体膜45を形成できる。結晶

50

化は加熱炉を用いた加熱処理、レーザー光または紫外線、赤外線などの強光の照射によって行うことができる。

#### 【0119】

加熱処理は500～700 の範囲で行うことが可能であるが、温度の上限は使用する基板の耐熱温度が一つの上限として考慮される。ガラス基板の場合にはその歪み点以下が上限温度の一つの根拠となる。さらに、温度の上限としては、第1の非晶質半導体膜42に偶発的な自然核が発生しないような温度にすることも考慮され、実施形態1において説明した金属元素とシリコンとの反応のみにより結晶成長が進行するような温度とする。

#### 【0120】

上記のように結晶化のために金属元素を添加し、また非晶質シリコン膜にゲルマニウムを含ませることで、{101}面の配向率が高い結晶質シリコン膜が得られるメカニズムは、現段階で明確ではないが、以下のような推測ができる。

10

#### 【0121】

実施形態1で説明したように、ニッケルを用いて非晶質シリコン膜を結晶化する場合、400～600 程度の加熱処理によりニッケルとシリコンが反応してニッケルシリサイド( $\text{Ni}_3\text{Si}_2$ )が形成される。このニッケルシリサイドが結晶核となりその後の結晶成長に寄与するが、 $\text{Ni}_3\text{Si}_2$ と結晶シリコンの界面エネルギーが最も小さくなるのは、[111]面とが接する場合であるので、結晶質シリコン膜の表面と平行な面は[101]面となり、この格子面が優先的に配向すると考えられる。

#### 【0122】

20

しかしながら、結晶成長方向が基板表面に対し平行な方向に、しかも柱状に成長する場合には、その柱状結晶を軸とした回転方向には自由度があるため、必ずしも{101}面が配向するとは限らず、実験では、実施形態1で示したように{111}が優先的に配向する傾向が高かった。

#### 【0123】

本実施形態では、第1の結晶質半導体膜の{101}格子面の配向を高めるために、柱状結晶の回転方向に制約を与え、自由度を低減させるために、非晶質シリコンにゲルマニウムを1原子%～10原子%程度添加することで、{101}への配向率を20%以上にするようにしたものである。

#### 【0124】

30

非晶質シリコンに1原子%～10原子%程度のゲルマニウムを含有させると、結晶核の発生密度が低下することがわかっている。これは、結晶核である $\text{Ni}_3\text{Si}_2$ が形成されるとき、シリコンとニッケルの原子間距離とゲルマニウムとニッケルの原子間距離の違いにより、ゲルマニウムが、 $\text{Ni}_3\text{Si}_2$ から排除されつつ上述の結晶成長が起っているためであると推測される。

#### 【0125】

したがって、この推測に従えば、シリコン膜に含まれるゲルマニウムは、シリコンの結晶の外側に偏析するような状態で存在しており、このような状態のゲルマニウムがシリコン結晶について、基板の法線方向の結晶軸の回転方向の自由度を低下させるために、結晶質シリコン膜の表面と平行な面は{101}面となり、この格子面が優先的に配向すると考えられる。

40

#### 【0126】

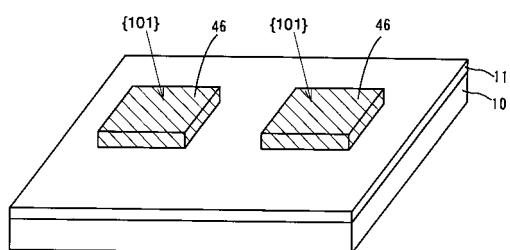

(図12参照)

{101}が優先して配向した第1の結晶質半導体膜45が形成される。以降の工程は、実施形態1と同様に行えばよい。第1の結晶質半導体膜45を所定の形状にパターニングして、一対の第1の結晶質半導体層46を形成する。一対の第1の結晶質半導体層46は、それぞれ、ソース領域、ドレイン領域を構成するものである。

#### 【0127】

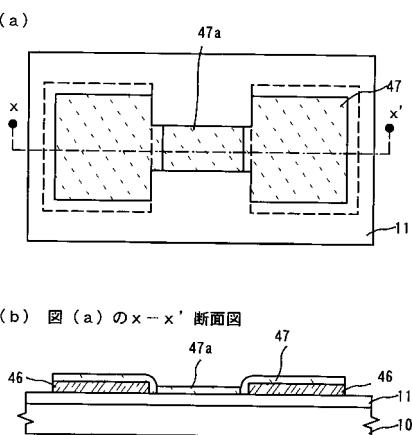

(図13参照)

第1の結晶質半導体層46に接して非晶質シリコンの非晶質半導体膜を形成し、実施形態

50

1と同様に所定の形状にパターニングして、第2の非晶質半導体層47を形成する。なお、図13(a)は上面図であり、同図(b)は同図(a)のX-X'断面図である。

#### 【0128】

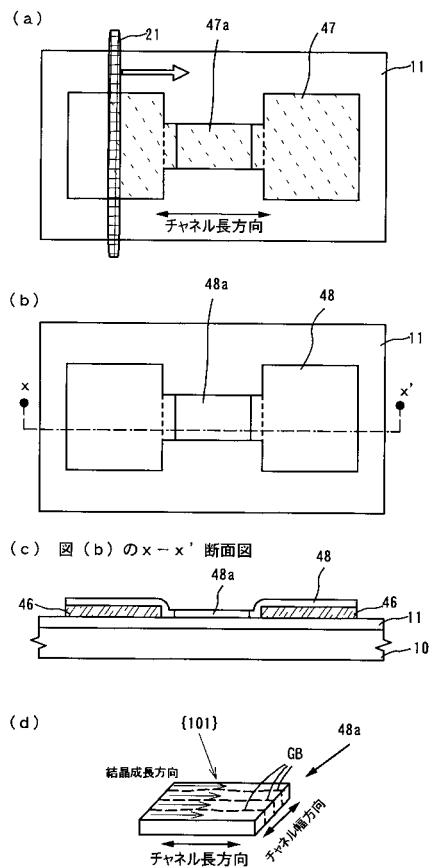

(図14(a)、(b)参照)

実施形態1と同様に、連続発振レーザー光をその照射領域21が基板10に対して、チャネル長方向に平行に、第1の結晶質半導体層46と重なっている領域から、重なっていない領域47aに向かって移動することで、第2の非晶質半導体層47全体がレーザー光に照射されるようにして結晶化し、第2の結晶質半導体層48を形成する。

#### 【0129】

連続発振レーザー光の照射は1度のみに限らず、複数照射する場合も含む。この場合は、連続発振レーザー光をチャネル長方向に沿って往復するように移動させたり、一方向に複数回移動させてもよい。

10

#### 【0130】

(図14(b)、(c)参照)

よって、第2の結晶質半導体層48は、第1の結晶質半導体層46と重なっていない領域48aを含め、第1の結晶質半導体層46を種として結晶化されるため、第1の結晶質半導体層46の結晶構造を複写するように結晶成長され、{001}{101}および{111}の結晶面のうち、{101}の割合が最も高い結晶質半導体とすることができます。

#### 【0131】

(図14(d)参照)

20

図14(d)は、第2の結晶質半導体層48の領域(第1の結晶質半導体層46と重なっていない領域)48aの、概略的な斜視拡大図である。実施形態1において説明したように、第2の非晶質半導体層47が60nm以下、例えば10~40nmと薄い場合でも、連続発振レーザー光による結晶化された第2の結晶質半導体層48において、少なくともチャネル形成領域となる領域48aにおいて、結晶成長方向であるチャネル長方向に平行な粒界GBが存在するが、チャネル幅方向には存在しないようにすることが可能である。

#### 【0132】

以上の工程にて、薄膜トランジスタの活性層となる第1及び第2の結晶質半導体層が形成される。以降は、実施形態1で示したように公知のトップゲート型薄膜トランジスタの製造方法にならって、薄膜トランジスタを形成することができる。もちろん、第1及び第2の結晶質半導体層を形成する前に、ゲート電極を形成して、ボトムゲート型の薄膜トランジスタを作製することもできる。

30

#### 【0133】

本実施形態の第1及び第2の結晶質半導体層を活性層に用いた薄膜トランジスタは、実施形態1と同様、チャネル形成領域を構成する第2の結晶質半導体層は、結晶粒界がチャネル長方向に平行であり、キャリアの移動を妨げる粒界をなくすように形成されるため、薄膜トランジスタの電界効果移動度を大きくすることができる。

#### 【0134】

また、本実施形態では、チャネル形成領域となる第2の結晶質半導体層48の結晶を{101}にそろえるようにしたため、多数の薄膜トランジスタを同一基板上に作製しても、素子ごとにチャネル形成領域の結晶配向をそろえることができるため、素子ごとの特性のばらつきを抑えることができる。

40

#### 【0135】

特に、10~40nm程度の薄いチャネル形成領域を形成することで、しきい値電圧値、サブスレッショルド特性も良好なものとするとともに、上記のように{101}に配向をそろえることで電界効果移動度を大きくすることができる。

#### 【0136】

また、本実施形態では、冒頭で示したように、チャネル形成領域が{101}に優先的に配向していることに特徴がある。一般にPチャネル型のTFTは、ホールがキャリアとなるため電界効果移動度を高くすることは、Nチャネル型のTFTよりも困難であるが、{

50

{101} 結晶面がホールの移動度が最も高くなることが知られており、本実施形態により、Pチャネル型TFTの電界効果移動度をより高くできるという効果が期待できる。

#### 【0137】

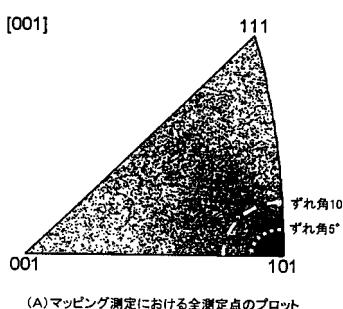

[第1の結晶質半導体膜の配向について]

ここでは、実施形態1及び2の方法で形成された第1の結晶質半導体膜について、上記したEBSP法により得られた標準三角形用いて、その結晶の配向について述べる(図36、37参照)。すでに、標準三角形については図35を用いて説明したが、図35(B)は配向の分布を等高線表示したものであるが、図36、図37も図35(B)と同様に等高線表示したものであるが、色(濃淡)によって等高線を示したものである。

#### 【0138】

標準三角形の濃度を示す数値は"times random"と呼ばれ、文字通り、ランダムな配向を仮定した場合に対する倍数を示している。つまり、全測定点を標準三角形の中に均等に分布させた場合の点密度を基準とし、実際のデータの逆極点の密度が基準の何倍となっているかを示している。よって1より大きい数値であれば、優先配向を持っていることになる。また、配向率の割合は、全測定の点数に対する割合を示すものである。

#### 【0139】

(図36)

図36(a)の標準三角形は、実施形態1の結晶質半導体膜のものであり、図36(b)の標準三角形は、実施形態2の結晶質半導体膜のものである。

#### 【0140】

図36(a)の試料の作製方法は、ガラス基板上に酸化珪素でなる下地膜を形成し、この下地膜上に第1の非晶質半導体膜としてゲルマニウム(Ge)を含まない非晶質シリコン膜を形成した。非晶質シリコン膜はプラズマCVD装置で成膜され、反応ガスとしてSiH<sub>4</sub>を用いた。SiH<sub>4</sub>の流量は100sccmとした。金属元素を選択的に添加するためには、酸化珪素でなるマスク膜を形成し、ニッケル濃度が10ppmの酢酸ニッケルの水溶液を選択的に塗布した。結晶化のための加熱条件は、温度570、加熱時間14時間である。

#### 【0141】

図36(a)の標準三角形から、実施形態1の試料は{111}が最も強く優先的に配向していることが容易に理解できる。

#### 【0142】

図36(b)の試料の作製方法は、石英基板上に第1の結晶質半導体膜として、ゲルマニウムを含む非晶質シリコン膜をCVD装置により成膜した。反応ガスとして、SiH<sub>4</sub>と、H<sub>2</sub>で希釈したGeH<sub>4</sub>とを用いた。反応ガスの流量は、SiH<sub>4</sub>が100sccm、H<sub>2</sub>で希釈したGeH<sub>4</sub>が10sccmである。金属元素を添加するために、ニッケル濃度が10ppmの酢酸ニッケルの水溶液を膜の表面の全面に塗布した。結晶化のために、温度500で1時間加熱した後、さらに580で4時間加熱した。

#### 【0143】

図36(b)の標準三角形から、実施形態2の試料は{101}最も強く優先的に配向する傾向があることが容易に理解できる。また、図36(a)と(b)のデータを対比することで、ゲルマニウムを添加することにより、結晶性シリコン膜において{101}配向が優先的に起ることが理解できる。図示の例では、60%もの高い配向率を示す。

#### 【0144】

なお、図36(b)の試料は基板に石英を用いているが、ガラス基板を用い、下地に酸化珪素膜が形成された試料の場合は、ニッケル酢酸の水溶液のニッケル濃度を0.1ppmとすることで、{101}配向率が60%以上にすることができる。

#### 【0145】

実験により、非晶質シリコン膜に添加するニッケルの濃度によって、{101}の配向率が変化することがわかっている。ガラス基板に下地膜を介してゲルマニウムを含む非晶質シリコン膜を形成し、酢酸ニッケル水溶液のニッケル濃度を変化させて、他の条件を同じ

10

20

30

40

50

にして、{101}配向率(許容値の角度=10度)の変化を調べた。ニッケル濃度が0.1 ppmのとき約60%、1 ppmのとき50%程度、10 ppmのとき30%程度、30 ppmのとき20%程度であった。すなわち、添加するニッケルが少ないほど{101}配向率が高くなる傾向があることがわかる。

#### 【0146】

さらに、実験により、実施形態2の例において、ゲルマニウムを含む結晶質シリコン膜の{101}の配向率は、ゲルマニウムの濃度に依存することもわかっている。

#### 【0147】

ガラス基板に下地膜を介してゲルマニウムを含む非晶質シリコン膜を形成し、酢酸ニッケル水溶液のニッケル濃度が10 ppmとし、非晶質シリコン膜を形成する際の、H<sub>2</sub>で希釈したGeH<sub>4</sub>の流量を変化させ、他の条件を同じにして、{101}配向率の変化を調べた。その結果、H<sub>2</sub>で希釈したGeH<sub>4</sub>の流量が、5 sccm、10 sccm、15 sccmである場合、それぞれの{101}配向率(許容値の角度=10度)は、20%程度、30%程度、20%程度である。

#### 【0148】

また、上記の条件で成膜されたシリコン膜中のゲルマニウムの濃度は、SIMSによる測定では、流量が5 sccm、10 sccm、15 sccmの場合、1.5原子%、3.5原子%、11.0原子%であった。

#### 【0149】

よって、添加されるニッケルの量や、用いる基板の種類にもよるが、許容値の角度が10度以内の場合に{101}配向を20%以上とするには、シリコン膜中のゲルマニウムの濃度は1原子%以上10原子%以下とすることが好ましい。

#### 【0150】

図36(c)は、参考例1の結晶質シリコン膜についての標準三角形である。図36(a)に示される実施形態1の試料は、酢酸ニッケル溶液を選択的に塗布して結晶化されたものであるのに対して、参考例1では、酢酸ニッケル溶液を非晶質シリコン膜の表面全面に塗布して、結晶化したものである。

#### 【0151】

参考例1の試料も、ニッケルを添加して結晶化された結晶質シリコン膜であるため、{111}に配向する傾向があることがわかる。しかしながら、図36(a)と(c)の標準三角形を対比するとわかるように、参考例1では{111}の配向率が14%と、実施形態1の試料が約49%であることと比較すると、低い値となっている。よって、金属元素を添加し、かつ、その添加箇所を選択的にしてラテラル成長させることで、{111}配向率を高くる効果があることがわかる。

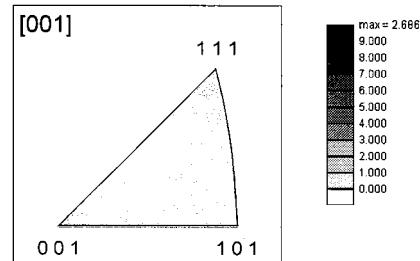

#### 【0152】

(図37参照)

また、図37は、参考例2の結晶質シリコン膜についての標準三角形で、いわゆるポリシリコンと呼ばれる多結晶シリコン膜のものである。石英基板上の非晶質シリコン膜を600、20時間加熱した試料である。

#### 【0153】

参考例2の多結晶シリコン膜は、{111}、{101}、{001}のいずれかに優先的に配向しているものではなく、結晶性に異方性がなく、ランダムな配向になっていることがわかる。

#### 【0154】

したがって、図36(a)、(b)と図37を対比することで、金属元素を添加すること、またゲルマニウムを非晶質シリコン膜に含ませることで、結晶化されたシリコン膜の結晶面にある特定の面方位に優先配向させるという効果があるということがわかる。

#### 【0155】

[実施形態3]

本実施形態では、連続発振レーザーを照射して下層の第1の結晶質半導体層を形成し、連

10

20

30

40

50

続発振レーザー光を照射することにより、第1の結晶質半導体層を種として上層の第2の非晶質半導体層を結晶化する例を説明する。

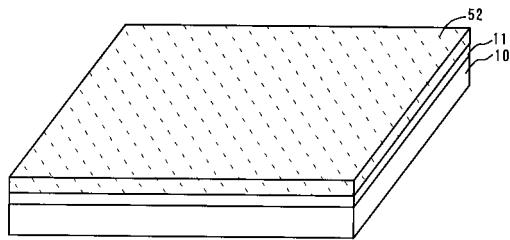

【0156】

(図15参照)

まず、実施形態1と同様に、基板10に下地膜11を形成し、下地膜11上に、第1の非晶質半導体膜として、非晶質シリコン膜52を形成する。形成方法は、スパッタリング法、プラズマCVD法、減圧CVD法などの公知の成膜方法を採用できる。

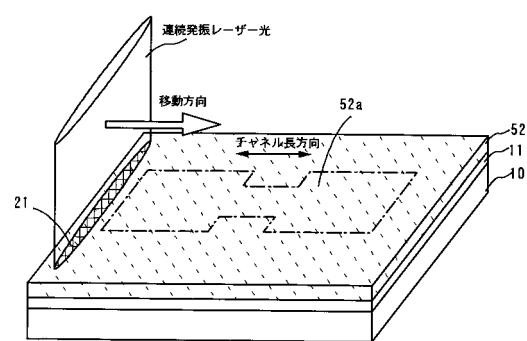

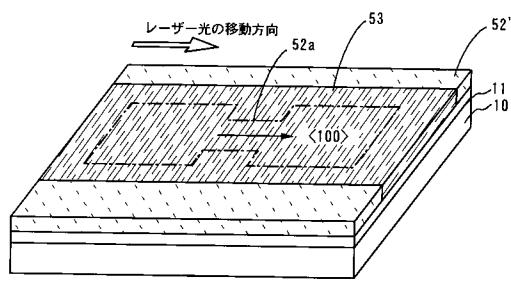

【0157】

(図16参照)

次に、連続発振レーザー光を照射して、第1の非晶質半導体膜52を結晶化させる。連続発振レーザー光による照射領域21を基板10に対して相対的に矢印の方向に移動しながら、レーザー光を照射する。図16において、第1の非晶質半導体膜52の一点鎖線で示す領域52aは、薄膜トランジスタが形成される素子領域であって、後述する第2の結晶質半導体層の外形を示す。

【0158】

上述したように、連続発振レーザー光の照射領域21の移動に伴って結晶成長するので、基板の平面に水平方向(横方向)に長い粒径の結晶粒を成長させることができる。また、連続発振レーザー光を用いた場合、実施形態1や2のように、特定の面方位に配向はしないが、照射領域21の移動方向について、<100>軸が成長しやすいという傾向があるということがわかっている。

【0159】

なお、本実施形態の場合も同様、レーザー光の照射は、一方向に1回ほど、照射領域21を移動することで、少なくとも領域52a全体が照射されるように、図示のように連続発振レーザー光14のビーム(光束)を一方向に拡大して、長軸のビームとなるようにする。図16ではビームの形状は長楕円形であるが、線状であっても、矩形状であっても、四隅の丸い矩形状であってもよい。

【0160】

また、本発明においては、連続発振レーザー光の照射は矢印の移動方向に1回だけ移動しながら照射することに限定されるわけではない。矢印に示す1方向に沿って往復したり、あるいは矢印に示す1方向に複数回移動させたりすることも含む。

【0161】

(図17参照)

また、第1の非晶質半導体膜52全面を結晶化する必要はなく、少なくとも、第1の結晶質半導体層となる領域52aを結晶化させて、結晶質半導体53とすればよい。

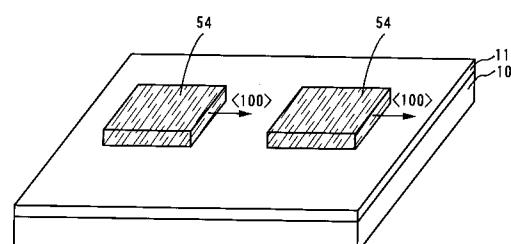

【0162】

(図18参照)

連続発振レーザー光による結晶化を行ったら、エッチングにより結晶化された領域53を所定の形状にパターニングして、結晶質シリコンでなる2つの第1の結晶質半導体層54を形成する。これらの第1の結晶質半導体層54は、薄膜トランジスタのチャネル形成領域を結晶化させるための種結晶であり、かつ薄膜トランジスタのソース領域、ドレイン領域となる層もある。

【0163】

上述したような基板の表面に水平方向な結晶成長、いわゆるラテラル成長をさせたため、第1の結晶質半導体層54の結晶構造は、膜厚方向には結晶粒が1つであり、これらの結晶粒は連続発振レーザー光の移動方向に長い形状となっている。

【0164】

結晶化される第1の非晶質半導体膜52の厚さは30nm以上とする。これは最終的に素子となる第1結晶質半導体層はソース領域やドレイン領域を構成する部分であり、ここでの電極、配線とのコンタクト抵抗が高くならないようにするため、ある程度の膜厚が必要

10

20

30

40

50

だからである。より好ましくは、非晶質半導体膜52の厚さは100nm以上とする。これは、結晶化する際に連続発振レーザー光の照射条件のマージンを広くするためであり、また、ある程度厚くすることにより、レーザー光の走査方向に<100>軸がそろいやすいためでもある。

#### 【0165】

また、第1の非晶質半導体膜52の膜厚の上限は、連続発振レーザー光の照射領域において膜全部が溶融するような厚さになるように、400nm以下、好ましくは150nm以下とする。

#### 【0166】

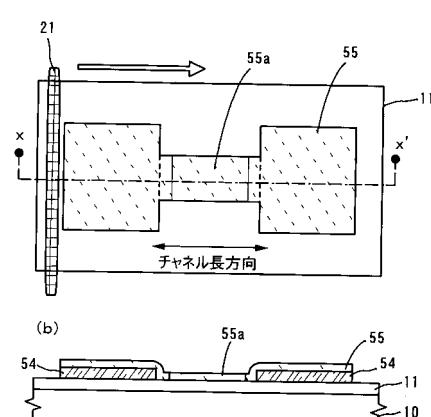

(図19(a)、(b)参照)

次に、第1の結晶質半導体層54に密着して、非晶質半導体でなる第2の非晶質半導体膜を形成する。ここでは非晶質シリコン膜を形成する。そして、第2の非晶質半導体膜を所定の形状にパターニングして、実施形態1と同様に、第2の非晶質半導体層55を形成する。第2の非晶質半導体層55の第1の結晶質半導体層54と重なっていない領域55aは、チャネル形成領域となる領域である。

#### 【0167】

第2の非晶質半導体膜55の厚さは、実施形態1、2と同様に、60nm以下の10nm～60nm範囲、好ましくは20nm～40nmとする。第2の非晶質半導体膜は結晶化され、最終的に薄膜トランジスタのチャネル形成領域を構成する膜である。第2の非晶質半導体膜55の膜厚を10nm～60nm程度に薄く形成することで、チャネル形成領域の厚さが薄くなり、オフ状態でのリーク電流値を抑える効果や、オン電流／オフ電流比を高くする効果がえられる。

#### 【0168】

(図20参照)

そして、第1の非晶質半導体膜52を結晶化した場合と同様に、連続発振レーザー光による照射領域21を基板10に対して相対的に、チャネル長方向に沿って移動しながら照射することにより、第2の非晶質半導体層55全体を結晶化し、第2の結晶質半導体層56を形成する。

#### 【0169】

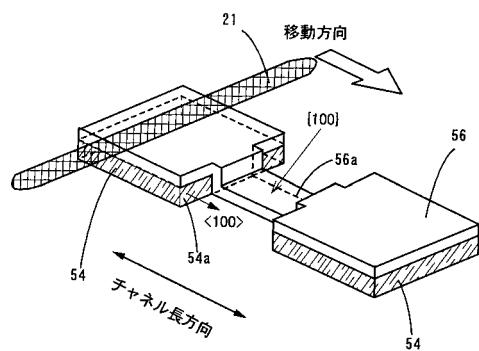

第2の結晶質半導体層56において、第1の結晶質半導体層54と重なっていない領域56aに薄膜トランジスタのチャネル形成領域が設けられる。本実施形態においても、連続発振レーザー光を用いて、第2の結晶質半導体層56を形成しているので、領域56aの粒界は結晶成長方向に平行なチャネル長方向のみに存在し、チャネル幅方向の結晶粒界が存在しないようにできる。

#### 【0170】

(図21参照)

図21を用いて、第2の非晶質半導体層54の結晶化について説明する。

実施形態1、2と同様、連続発振レーザー光をその照射領域21が基板10に対して、チャネル長方向に平行な方向に、第1の結晶質半導体層54と重なっている領域から、重なっていない領域55aに向かって移動しながら照射する。

#### 【0171】

本実施形態の第1の結晶質半導体層54は、実施形態1や2と異なり、面方位はランダムであるが、結晶成長方向に<100>軸が現れやすいことわかっている。この点に着目して、本実施形態では、連続発振レーザー光を用いて第2の非晶質半導体層をラテラル成長させる際に、第1の結晶質半導体層の結晶性に異方性を持つ側面54aが、チャネル形成領域となる領域56aの結晶成長に寄与できるように配置することで、この領域56aにおいて結晶軸を<100>となるように、すなわち結晶面を{100}にそろえるようにしたものである。そこで、第1及び第2の非晶質半導体膜を結晶化する際に、連続発振レーザー光の照射領域の移動方向をチャネル長方向にあわせている。

#### 【0172】

10

20

30

40

50

上記のように、本実施形態では、第1の結晶質半導体層の側面54aの面方位により、第2の結晶質半導体層の領域56aの結晶面の方位を決定づけるようにしているので、第1の結晶質半導体層54の厚さを100nm以上として、第2の非晶質半導体層を結晶化させる際に、第1の結晶質半導体層の側面54aから優先的な結晶成長が起りやすくするといい。

#### 【0173】

以上の工程にて、薄膜トランジスタの活性層となる第1及び第2の結晶質半導体層54、56が形成される。以下は、公知のトップゲート型薄膜トランジスタの製造方法にならつて、例えば、実施形態1で説明したように、薄膜トランジスタを形成すればよい。もちろん、ゲート電極を先に形成して、第1及び第2の結晶質半導体層を形成することで、ボトムゲート型薄膜トランジスタを形成できることはいうまでもない。10

#### 【0174】

##### [実施形態4]

実施形態3では、第1の結晶質半導体層の形成は、非晶質半導体でなる第1の非晶質半導体膜52の所定の領域を結晶化し、かかる後エッティングによりパターニングする方法をとった。

#### 【0175】

この形成方法に対して、エッティングにより、第1の非晶質半導体膜52を予め所定の形状にパターニングし、その後、実施形態3と同様に一定の方向に移動しながら連続発振レーザー光を照射して結晶化することで、第1の結晶質半導体層を形成することも可能である20。

#### 【0176】

##### [実施形態5]

上記の実施形態では、第1の結晶質半導体層の形状を立方体としたが、本発明では、第1の結晶質半導体層を種として第2の非晶質半導体層を結晶化することができれば、第1の結晶質半導体層の形状は立方体に限定されるものではない。本実施形態では、第1の結晶質半導体層の形状の変形例を示す。

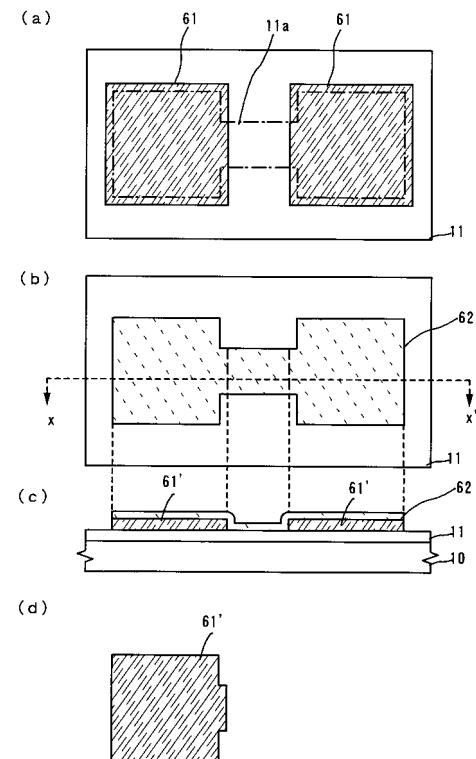

#### 【0177】

##### (図22(a)参照)

まず、実施形態1や2で説明したように、基板10に下地膜11を介して第1の結晶質半導体層61を形成する。なお、下地膜11の一点鎖線で示す領域11aは、後に形成される第2の結晶質半導体層の輪郭を示す。本実施形態も、上記の実施形態同様、第1の結晶質半導体層61を第2の結晶質半導体層からはみ出すように広くしている。30

#### 【0178】

##### (図22(b)、(c)、(d)参照)

次に、第1の結晶質半導体層61に密着して、基板10全面に、第2の非晶質半導体膜として、非晶質シリコン膜を成膜する。公知の方法で、レジストでなるマスクを形成し、このマスクを用いて、第2の非晶質半導体膜を所定の形状にエッティングし、第2の非晶質半導体層62を形成すると共に、第1の結晶質半導体層61もエッティングされる。

#### 【0179】

図22(c)は図22(b)の線x-x'による断面図であり、図22(d)は第1の結晶質半導体層61'の上面図である。以下、実施形態1乃至3で説明したように、連続発振レーザー光を用いて第2の非晶質半導体層62を結晶化し、第2の結晶質半導体層を形成する。得られた第1及び第2の結晶質半導体層が積層した半導体層に、チャネル形成領域、ソース領域及びドレイン領域などを形成し、薄膜トランジスタを作製することができる。

#### 【0180】

一般に、薄膜トランジスタの半導体層は、ソース領域やドレイン領域よりもチャネル形成領域の幅が狭い。そこで、本実施形態のように、種となる結晶面の幅をチャネル幅にあわせて細くしておくことに特徴がある。このように第1の結晶質半導体層61'を成形する4050

ことで、チャネル形成領域において、チャネル長方向に沿わないような結晶成長を抑制される効果が期待され、チャネル形成領域での結晶方位を揃えることが、より再現性よくできる。

**【0181】**

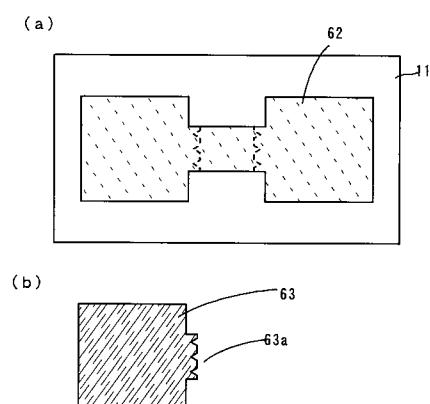

(図23参照)

次に、第1の結晶質半導体層において、第2の非晶質半導体層と接する側面に凹凸を設ける一例を図23に示す。図23において図22と同じ符号は同じ構成要素を示している。図23(a)は、図22(b)に対応し、第1の結晶質半導体層63と第2の結晶質半導体層64が形成された状態を示す。

**【0182】**

10

図23(b)は第1の結晶質半導体層63の上面図である。図示のように、第1の結晶質半導体層63の側面63aに鋸波状の凹凸が形成されている。この凹凸を形成することで、第1の結晶質半導体層63の側面からの結晶成長が優位に起ることが期待できるため、実施形態3や4の場合に特に有効である。

**【0183】**

なお側面の形状は図23に図示する形状に限ることなく、三角波や矩形波、正弦波、円弧などの形状の凹凸を付すこともできる。

**【0184】**

[実施形態6]

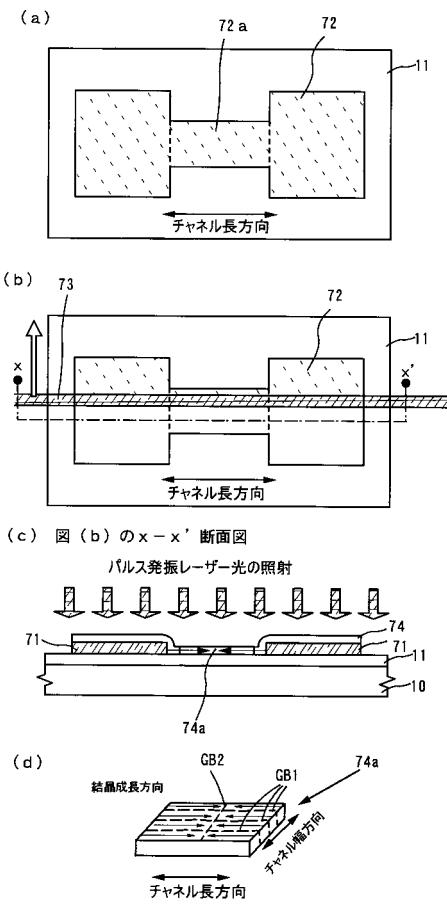

上記の実施形態1乃至3では、上層の第2の結晶質半導体層を形成するために、連続発振レーザー光を用いる例を説明したが、本発明においては、連続発振レーザーの代りに、パルス発振レーザー光を用いることもできる。本実施形態では、パルス発振レーザー光を用いる方法を説明する。

20

**【0185】**

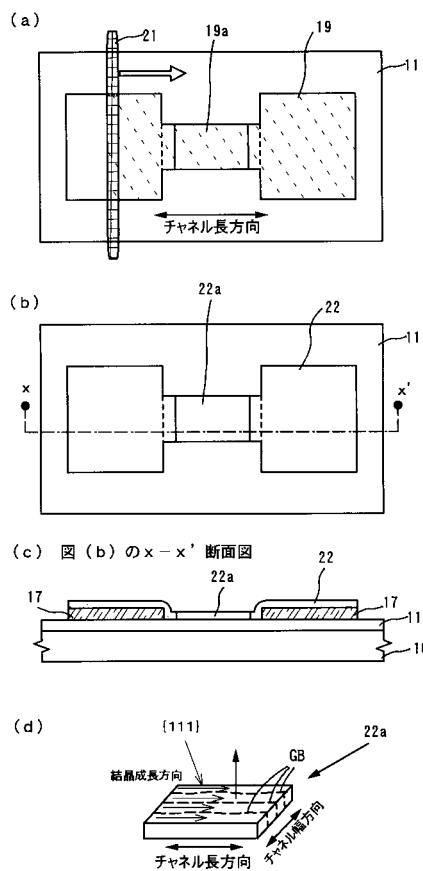

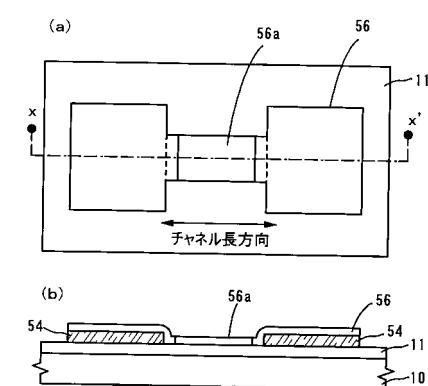

(図24(a)参照)

ここでは、実施形態1で説明したプロセスを例にして、本実施形態を説明する。実施形態1と同様に、図6までの工程を行う。即ち、下地膜11を介して、基板10に1対の第1の結晶質半導体層71を形成し、これら第1の結晶質半導体層71上に接して、第2の非晶質半導体層72を形成する。第2の結晶質半導体層の領域72aは薄膜トランジスタのチャネル形成領域となる領域である。

30

**【0186】**

そして、パルス発振レーザー光の照射領域73を基板10に対して一定の方向に、相対的に移動させることで、第2の非晶質半導体層72全体にパルス発振レーザー光を照射して、第2の結晶質半導体層74を形成する。第2の結晶質半導体層74の領域74aは第2の非晶質半導体層72の領域72aに対応する。

**【0187】**

(図24(b)、(c)参照)

パルス発振レーザー光の照射領域73を基板10基板の表面に平行であって、かつチャネル長方向と直交する方向に移動しながら、パルス発振レーザー光を照射する。照射領域73には、第2の非晶質半導体層72の第1の結晶質半導体層71と重なっている領域と、重なっていない領域72aが共に含まれるようにする。

40

**【0188】**

これはパルス発振レーザー光では、照射時間が数n秒~数十n秒程度と、連続発振レーザー光と比較して非常に短いため、連続発振レーザー光のように固相-液相界面を移動させながら照射することができないためである。そこで、本実施形態では、パルス発振レーザー光によって溶融される領域である照射領域73に、常に結晶成長の種となる第1結晶質半導体層71が含まれるようにしている。

**【0189】**

上述したようにパルス発振レーザー光を移動しながら照射することで、照射領域73において、常に第1の結晶質半導体層71のみから結晶成長させることができ、結晶成長方向

50

をチャネル長方向に平行にすることができる。すなわち、核生成位置と、結晶成長方向を制御することで、第2の結晶質半導体層72を第1の結晶質半導体層71の結晶構造を複写するように、ラテラル成長させることができる。

#### 【0190】

(図24(c)、(d)参照)

また、第2の結晶質半導体層74の領域74aは1対の第1の結晶質半導体層71のそれぞれから結晶成長するため、結晶成長方向に平行であるチャネル長方向に形成される複数の粒界GB1と、チャネル幅方向は、異なる第1の結晶質半導体層71を種に成長した粒界同士がぶつかって形成されるの1つの結晶粒界GB2が形成される。また、領域74aは膜厚方向には1つの結晶粒でなる。

10

#### 【0191】

このように結晶成長をさせるには、パルス発振レーザー光の出力、照射領域の移動速度、照射領域の面積や移動方向の幅などを調節することで、与えるエネルギー密度を最適化することで実現できる。また、パルス発振レーザー光を照射しているときに、基板を加熱したり、マイクロ波などを照射したりして、熱エネルギー、電磁エネルギーなどを半導体層に与えることで、結晶化のエネルギーを低下させるようにしてもよい。

#### 【0192】

以上の工程を経て、薄膜トランジスタの活性層となる第1及び第2の結晶質半導体層が形成される。以降は、公知の製造方法にならって、薄膜トランジスタを形成することができる。

20

#### 【0193】

なお、チャネル幅方向に平行な粒界GB2のような粒界は、後述する実施形態7のように回路構成を工夫することにより、チャネル形成領域に含まれないようにすることができる。

#### 【0194】

##### [実施形態7]

実施形態6の場合、パルス発振レーザー光による結晶化のため、第2の結晶質半導体層にチャネル幅方向の粒界GB2ができてしまう。しかしながら、この粒界がチャネル形成領域に含まれないように素子設計をすることで、この粒界の影響を無くすことができる。

30

#### 【0195】

(図25(a)参照)

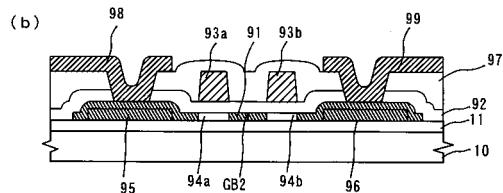

例えば、ソース領域85、ドレイン領域86を構成している第1結晶質半導体層を左右非対称に設けることで、チャネル形成領域84に第2の結晶質半導体層の粒界GB2を含ませないようにすることができる。図25(a)において、10は基板、11は下地膜、82はゲート絶縁膜、83はゲート電極、87は層間絶縁膜、88はソース電極、89はドレイン電極である。

#### 【0196】

(図25(b)参照)

また薄膜トランジスタの1つのチャネル形成領域を2つ以上にわけたマルチチャネル構造とすることで、チャネル長を稼ぐと共に、粒界GB2を避けるように形成することができる。

40

#### 【0197】

図25(b)において、10は基板、11は下地膜、92はゲート絶縁膜、93a、93bはゲート電極、94a、94bはチャネル形成領域、95は第1、第2の結晶質半導体層でなるソース領域、96は同様にドレイン領域である。領域91は2つのチャネル形成領域94a、94bを接続する不純物領域であり、ここに粒界GB2が含まれるように素子設計を行えばよい。97は層間絶縁膜、98はソース電極、99はドレイン電極である。

#### 【0198】

以上の実施形態1～7は適宜に組み合わせることが可能である。例えば、実施形態3にお

50

いて示した、第1の結晶質半導体層、第2の非晶質半導体層の形成方法を他の実施形態に適用することである。また、薄膜トランジスタはトップゲート型に限定されるものではなく、本発明をボトムゲート型、代表的には逆スタガー型の薄膜トランジスタに適用することが可能である。

【0199】

[実施形態8]

本発明の半導体装置は、薄膜トランジスタのような半導体素子に限定されるものでない。薄膜トランジスタなど、本発明の第1及び第2の結晶質半導体層を用いた素子でなる集積回路を用いた半導体装置全般を含む。例えば、アクティブマトリクス型液晶パネルや、アクティブマトリクス型エレクロトルミネッセンスパネルが薄膜トランジスタを利用した半導体装置の代表的な例である。

10

【0200】

さらに、本発明の半導体装置はこれらアクティブマトリクス型表示装置を搭載した電子機器をも含むものであり、携帯電話、携帯情報端末（PDA：Personal Digital Assistance）、ノートパソコン、パソコン用ディスプレイ、テレビなどをあげることができる。

【0201】

【実施例】

図26～図34を用いて、本発明の実施例を説明する。

【0202】

[実施例1]（図26～図31）

20

本実施例は、同一基板上に画素部と駆動回路とを備えたアクティブマトリクス型液晶パネルに本発明を実施した例を説明する。

【0203】

（図26参照）

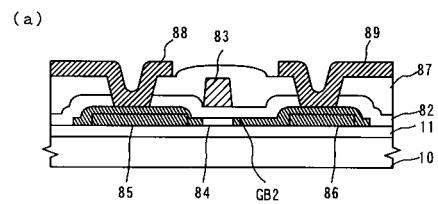

図26は、アクティブマトリクス型液晶パネルの概略図である。液晶パネルは、液晶を挟んで2枚の基板100と101の周囲がシール材により封止されている。基板100は、一般にTFT（薄膜トランジスタ）アレイ基板と呼ばれる基板である。基板100には、TFTをスイッチング素子に備えた画素部、TFTなどで構成された集積回路であるゲート線駆動回路104とソース線駆動回路105が設けられている。さらに、FPC（フレキシブルプリント配線板：Flexible Printed Circuit）106を貼り付ける外部入力端子107、駆動回路104と105の入力部と外部接続端子107を接続する配線108などが設けられている。

30

【0204】

他方の基板101は一般に対向基板と呼ばれる基板である。基板101には、画素部103と対向するように対向電極（図示せず）が設けられ、対向電極上に液晶を配向させるための配向膜が必要に応じて設けられる。カラーのパネルであれば、画素部103に対向する部分にカラーフィルタが設けられている。

【0205】

（図27、図28参照）

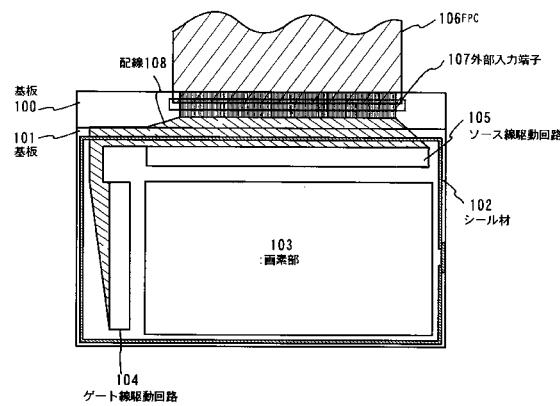

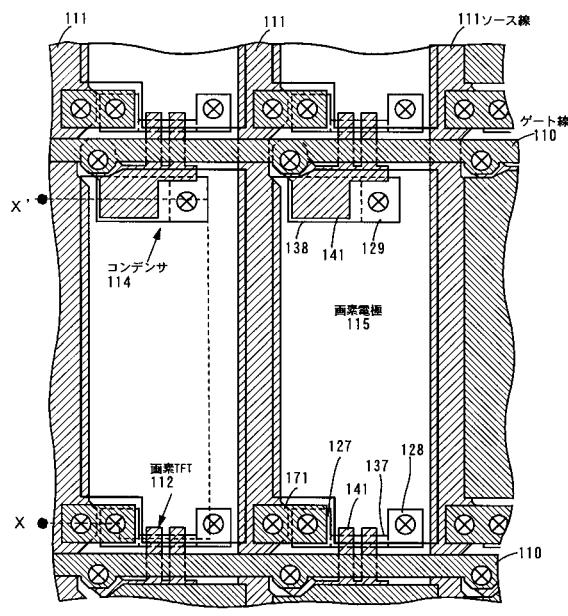

図27は画素の等価回路である。図28は基板100の画素部の上面図である。画素は、ゲート線駆動回路104から信号が伝送されるゲート線110とソース線駆動回路105から信号が伝送されるソース線111が交差して設けられている。この交差部に薄膜トランジスタ112、液晶素子113、コンデンサ114が設けられている。液晶素子113は画素TFT112に接続されている画素電極115、対向基板101に設けられている対向電極（図示せず）を電極に、液晶を誘電体とするコンデンサとなっている。コンデンサ114は液晶素子113の容量を補充するための素子である。

40

【0206】

以下、図29～図31を用いて、基板100の製造方法を説明する。なお、駆動回路104、105については、説明の都合により、回路の基本となるCMOS型の薄膜トランジスタの製造プロセスで代表させる。また図29～図31において、上側は駆動回路（CM

50

O S 型 T F T ) の断面図であり、下側は画素部の断面図であり、図 2 8 の X - X' に沿った線による断面図である。

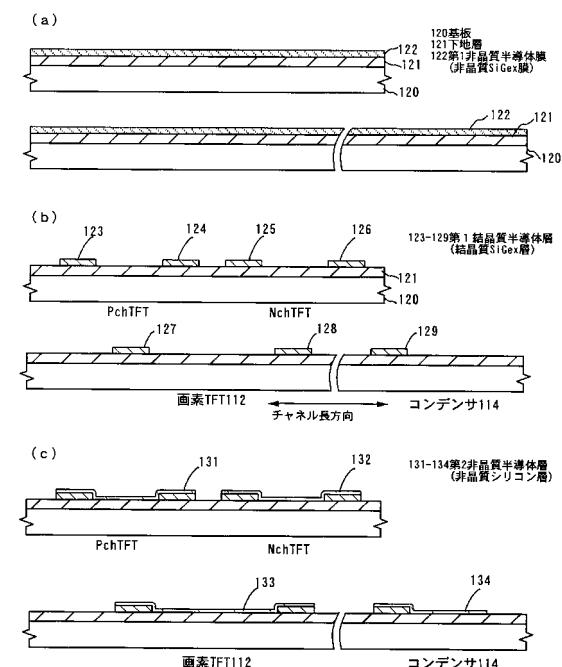

#### 【 0 2 0 7 】

( 図 2 9 ( a ) 参照 )

コーニング社の # 1 7 3 7 ガラスを基板 1 2 0 として用意する。基板 1 2 0 には、バリウムホウケイ酸ガラス、またはアルミニノホウケイ酸ガラスなどのガラスからなる基板や、石英基板を用いてもよい。

#### 【 0 2 0 8 】

下地膜 1 2 1 として、プラズマ C V D 装置においてシラン ( SiH<sub>4</sub> ) 、一酸化二窒素 ( N<sub>2</sub>O ) を原料ガスとして、窒化酸化シリコン膜 ( SiO<sub>x</sub>N<sub>y</sub> ) を厚さ 1 0 0 n m 成膜する。下地膜 1 2 1 の厚さは 2 0 ~ 2 0 0 n m 程度である。

10

#### 【 0 2 0 9 】

下地膜 1 2 1 に密着して、非晶質のゲルマニウムを含むシリコンを主成分とする膜 ( 以下、 SiGe<sub>x</sub> 膜と記す。 ) をプラズマ C V D 装置において形成する。原料ガスには、シラン ( SiH<sub>4</sub> ) と、水素ガス ( H<sub>2</sub> ) で 1 0 % に希釈したゲルマン ( GeH<sub>4</sub> ) とを用いる。流量は、 SiH<sub>4</sub> が 9 0 s c c m 、 H<sub>2</sub> で希釈された GeH<sub>4</sub> は 1 0 s c c m とする。高周波電力は 0 . 3 5 W / c m<sup>2</sup> ( 2 7 M H z ) であるが、繰り返し周波数 5 k H z ( デューティ比 2 0 % ) のパルス放電に変調して平行平板型のプラズマ C V D 装置の陰極に給電する。また、非晶質の SiGe<sub>x</sub> 膜の厚さは、 5 5 n m とする。

#### 【 0 2 1 0 】

20

非晶質の SiGe<sub>x</sub> 膜の表面全面に、スピナーを用いて 1 0 p p m 濃度のニッケル酢酸溶液を塗布し、加熱炉において加熱処理をして結晶化する。まず、 5 0 0 、 1 時間の加熱処理をし、 5 8 0 で 4 時間加熱して、結晶化し、 { 1 0 1 } の配向比率が 2 0 % 以上の結晶質 SiGe<sub>x</sub> 膜を形成する。

#### 【 0 2 1 1 】

( 図 2 9 ( b ) 参照 )

フォトリソグラフィ法によりレジストマスクを形成し、このマスクを用いて結晶質 SiGe<sub>x</sub> 膜をエッチングして、所望の形状の第 1 結晶質半導体層 1 2 3 ~ 1 2 9 を形成する。

#### 【 0 2 1 2 】

C M O S T F T の第 1 結晶質半導体層 1 2 3 、 1 2 4 は P チャネル型 T F T ( 以下、 P c h T F T という ) のソース領域、ドレイン領域となる層である。第 1 結晶質半導体層 1 2 5 、 1 2 6 は N チャネル型 T F T ( 以下、 N c h T F T という ) のソース領域、ドレイン領域となる層である。

30

#### 【 0 2 1 3 】

( 図 2 8 参照 )

画素部においては、第 1 結晶質半導体層 1 2 7 、 1 2 8 は画素 T F T ( N c h T F T ) のソース領域、ドレイン領域となる層である。第 1 結晶質半導体層 1 2 9 はコンデンサ 1 1 4 を形成する層であって、画素電極 1 1 5 との接続部となる層である。

#### 【 0 2 1 4 】

( 図 2 9 ( c ) 参照 )

40

次に、第 1 結晶質半導体層 1 2 3 ~ 1 2 9 に密着して、プラズマ C V D 装置においてシラン ( SiH<sub>4</sub> ) を原料ガスにして非晶質シリコン膜を厚さ 2 5 0 n m 成膜する。フォトリソグラフィ法によりレジストマスクを形成し、このマスクを用いて非晶質シリコン膜をエッチングして、所望の形状の第 2 非晶質半導体層 1 3 1 ~ 1 3 4 を形成する。

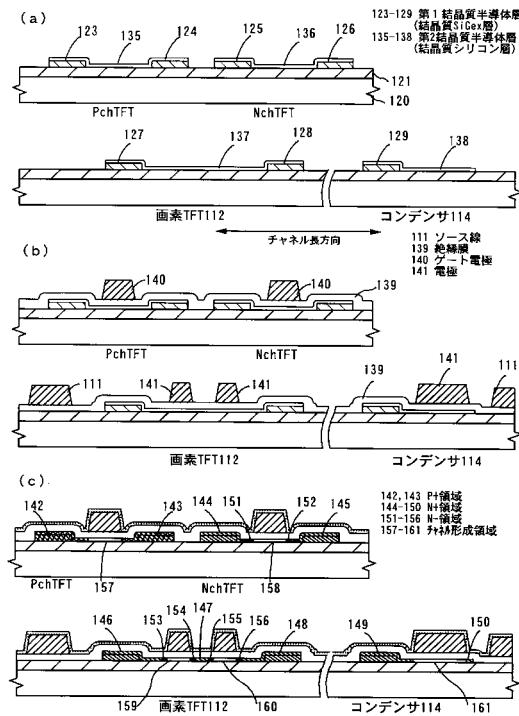

#### 【 0 2 1 5 】

( 図 3 0 ( a ) 参照 )

チャネル長方向に沿って走査しながら、第 2 非晶質半導体層 1 3 1 ~ 1 3 4 に対して連続発振レーザー光を照射して、結晶化し、第 2 結晶質半導体層 1 3 5 ~ 1 3 8 を形成する。

#### 【 0 2 1 6 】

連続発振レーザー光による結晶化は、連続発振レーザー装置として、 N d がドープされた

50

$\text{YVO}_4$ 結晶を用いた固体レーザーを用いる。また照射するレーザー光は基本波の第2高調波(532 nm)の光である。ビームの形状(断面形状)は、光学系により長軸200 μm、短軸20 μmの長楕円状に拡大されている。レーザー光の出力は3~6 W(ここでは5 Wとする)とし、基板の移動速度を5~100 cm/sec(ここでは50 cm/secとする)とし、レーザー光の照射雰囲気を大気雰囲気とする。また、連続発振レーザー光の照射は、ビームの短軸方向に照射領域が移動するように、レーザー光を固定し基板を移動しながら行う。また、移動方向がCMOSTFT、画素TFT112のチャネル長方向になるようとする。

#### 【0217】

以上の条件による結晶化により、第2結晶質半導体層は、チャネル形成領域が設けられる部分の結晶粒界をチャネル長方向に平行とし、チャネル幅方向の結晶粒界ができないよう10にする。

#### 【0218】

なお、第2非晶質半導体層を結晶化する前に、TFTのしきい値電圧を制御することを目的として、予めシリコン膜中にボロンやガリウムをドープしてもよい。ドープするタイミングは、非晶質シリコン膜を成膜しながら行うこともでき、また成膜後に、イオンドーピング装置によってドープすることもできる。ドープされたボロンやガリウムは第2非晶質半導体層を結晶化のために照射された連続発振レーザー光により活性化される。

#### 【0219】

(図30(b)参照)

次に、第2結晶質半導体層135~138に密着して絶縁膜139を形成する。絶縁膜139はTFTのゲート絶縁膜、コンデンサの誘電体として機能する。ここでは、絶縁膜139として、プラズマCVD装置において、シラン(SiH<sub>4</sub>)、一酸化二窒素(N<sub>2</sub>O)を原料ガスとして、窒化酸化シリコン膜(SiO<sub>x</sub>Ny)を厚さ110 nmに成膜する。

#### 【0220】

次に、絶縁膜139に密着して導電膜を形成し、フォトリソグラフィ法によりレジストによるマスクを形成し、このマスクを利用して、CMOSTFTのゲート電極140、画素部のゲート線111及び電極141を形成する。図28に示すように、この電極141は、画素TFTのゲート電極であり、かつ当該画素の次行に設けられるコンデンサの電極でもある。ここでは、導電膜として、スピッタリング装置においてタンゲステン膜(W膜)を厚さ300 nm成膜する。ICP(Inductively Coupled Plasma: 誘導結合型プラズマ)エッチング装置において、エッチング用ガスにCF<sub>4</sub>とCl<sub>2</sub>の混合ガスにより、タンゲステン膜をエッチングして、ゲート線111及び電極141を形成する。

#### 【0221】

(図30(c)参照)

次に、プラズマドーピング装置において、ドーピングを行い、N型およびP型の不純物領域を形成する。駆動回路のPchTFTの第1結晶質半導体層123、124および第2結晶質半導体層135にP型の不純物としてボロンをドープして、P型の導電性を示すP<sup>+</sup>領域142、143を形成する。また、駆動回路のNchTFT及び、画素TFT、コンデンサの第1結晶質半導体層125~129、第2結晶質半導体層136~138にN型の不純物としてリンをドープして、N型の導電性を示すN<sup>+</sup>領域144~150およびN<sup>-</sup>領域151~156を形成する。なおN<sup>-</sup>領域はN<sup>+</sup>領域よりも磷の濃度を低くして、抵抗を高くした領域である。

#### 【0222】

P<sup>+</sup>領域142、143はゲート電極140をマスクに自己整合的に形成される。またN<sup>+</sup>領域144~148はレジストマスクを用いて非自己整合的に形成され、N<sup>+</sup>領域149、150は電極141を用いて自己整合的に形成され、N<sup>-</sup>領域151~156は電極140と141を用いて自己整合的に形成される。また、これらの不純物領域を形成することで、チャネル形成領域158~161が画定される。

#### 【0223】

10

20

30

40

50

この工程で、コンデンサ 114 が完成する。コンデンサ 114 は、電極 141 と、電極 141 の電界によりチャネル形成領域 161 に誘起されるチャネルとを電極対に、絶縁膜 139 を誘電体とする構成をとる。

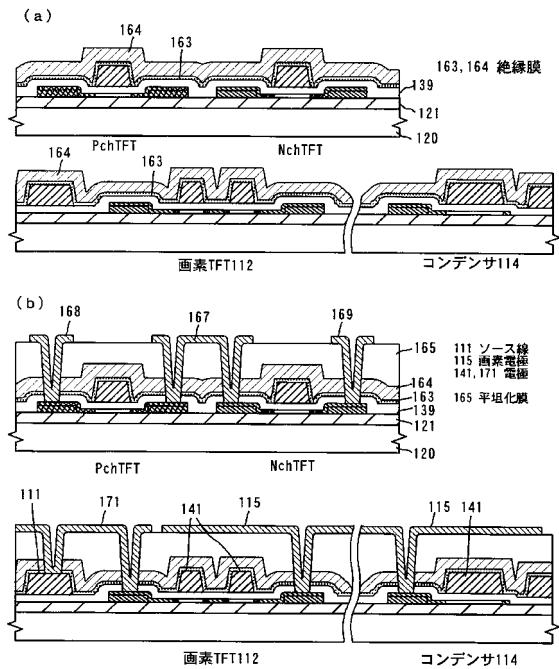

#### 【0224】

(図 31 (a) 参照)

次に、基板全面に絶縁膜 163 を形成する。この絶縁膜は、1 層目の層間絶縁膜であり、かつ不純物領域を活性化するための熱処理時に、ゲート線 110 等が酸化されることを防ぐための保護膜である。ここでは絶縁膜 163 として、酸化窒化シリコン膜をプラズマ CVD 装置において、厚さ 50 nm 成膜した。この酸化窒化シリコン膜は O の組成（濃度）が N の組成（濃度）よりも多くなるようにする。

10

#### 【0225】

次に、加熱処理装置において窒素雰囲気、550 °C で熱処理することで、先にドープされたリン、ボロンを活性化する。そして、基板全面に絶縁膜 164 を形成する。この絶縁膜は 2 層目の層間絶縁膜であり、ここでは酸化窒化シリコン膜をプラズマ CVD 装置において厚さ 100 nm 成膜する。

#### 【0226】

(図 31 (b) 参照)

基板表面を平坦化するため、平坦化膜 165 を形成する。平坦化膜 165 としては、無機材料としては、プラズマ CVD 法で TEOS (Tetraethyl Ortho silicate) を原料ガスに用いて成膜される酸化シリコン膜や、塗布法で形成される SOG, PSG, BSG を用いることができる。また、有機樹脂材料としては、塗布法で形成されるポリイミド、アクリル、BCB (ベンゾシクロロブテン) が適用できる。CVD 法よりも塗布法で成膜できる膜のほうが、平坦性がより高くできる。あるいは絶縁膜を形成した後、CMP 法により膜表面を研磨して、より平坦性を高めることもできる。ここでは平坦化膜 165 として、塗布法にてアクリル樹脂をゲート電極 141 上で厚さが 1 μm になるように形成する。次に、絶縁膜 163、164、平坦化膜 165 の所定の位置（図 28 参照）に、コンタクトホールを開口する。

20

#### 【0227】

画素電極 115 を反射型の電極とするため、アルミニウム (Al) または Ag を主成分とする膜、チタン (Ti)、それらの積層膜等、反射性の優れた材料でなる導電膜を成膜する。ここではアルミニウム膜をスパッタ法で成膜する。フォトリソグラフィ法によりレジストマスクを形成し、このマスクを用いてこのアルミニウム膜をエッチングして、Nch TFT と Pch TFT を接続するための電極 167、CMOSTFT の入力部 / 出力部となる配線 168 と 169、画素部のゲート信号線 110、画素電極 115、画素 TFT 112 とソース信号線 111 とを接続するための電極 170 が形成される（図 28 参照）。断面図には図示されていないが、図 28 に示すように電極 141 はコンタクトホールを介してゲート信号線 110 に接続されている。公知のサンドblast 法やエッチング法等の工程を追加して表面を凹凸化させて、鏡面反射を防ぎ、反射光を散乱させることによって白色度を増加させることができるので嬉しい。

30

#### 【0228】

以上の工程で、画素 TFT 及びコンデンサ 114 を含む画素部と CMOSTFT を含む駆動回路 104、105 を同一基板上に作製した TFT アレイ基板が完成する。

40

#### 【0229】

次いで、対向基板を用意し、後は公知のセル組工程を経て液晶パネルを完成する。なお、本実施例では、実施形態 2 で説明した方法に基づいて TFT などを作製したが、もちろん他の実施形態の方法を採用してもよい。

#### 【0230】

[実施例 2] (図 32、図 33)

本実施例では、同一基板上に画素部と駆動回路とを備えたアクティブラチクス型エレクトロルミネッセンス (EL) パネルに、本発明を実施した例を説明する。

50

**【 0 2 3 1 】**

アクティブマトリクス型ELパネルのTFTアレイ基板は、液晶パネルと同様画素部と、画素部のゲート線に信号を伝送するためのゲート線駆動回路、ソース線に信号を伝送するためのソース線駆動回路がTFTを用いた集積回路にて構成されている。

**【 0 2 3 2 】**

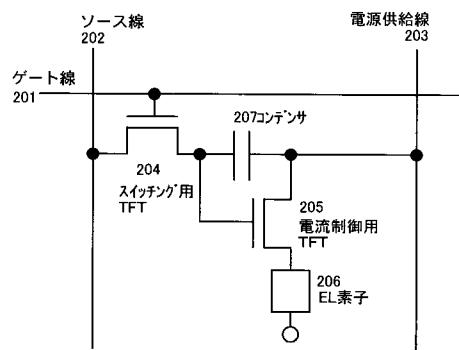

(図32参照)

図32は画素の基本的な等価回路図の一例である。ゲート線201、ソース線202の交差部にスイッチング用TFT204、電流制御用TFT205、EL素子206、コンデンサ207が設けられている。さらに、EL素子206に電流を供給するための電源供給線203が設けられている。本発明の結晶質半導体層は、駆動回路及び画素部のTFTに適用される。

10

**【 0 2 3 3 】**

EL素子206は発光素子であるダイオード素子であり、電流制御用TFT205を介して、電源供給線から電流が供給され、発光する。スイッチング用TFT204は電流制御用TFT205がオン状態となるタイミングを制御するためのものである。

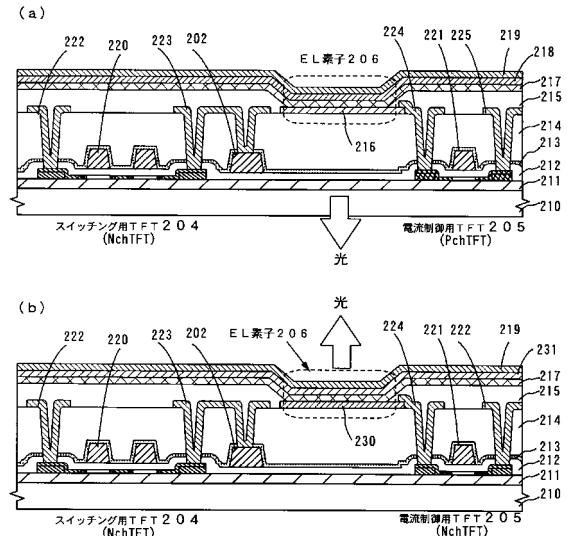

**【 0 2 3 4 】**

図33は画素部の断面図であり、(a)はEL素子から発した光がTFT基板を通して下側から放射する下方出射型の画素であり、(b)はEL素子からの光がTFT基板を通らずに、上方から放射する上方出射型の画素である。

**【 0 2 3 5 】**

(図33(a)参照)

基板210上に下地膜211を介してNch TFTでなるスイッチングTFT204とPch TFTでなる電流制御用TFT205が設けられている。電流制御用TFT205はドレインがEL素子206の陽極層216に接続している。

20

**【 0 2 3 6 】**

スイッチングTFT204と電流制御用TFT205の構成、及び絶縁膜212上に設けられたゲート電極220、221、ソース配線202と、層間絶縁物213、214上に設けられた電極222～224との接続構造は、実施例1と同様である。図示されていないが、実施例1と同様にコンデンサ207が設けられている。

**【 0 2 3 7 】**

EL素子206は、陽極層216、発光体を含む有機化合物層217、陰極層218からなり、その上にパッシベーション層219が形成されている。陽極層216の端部を覆うように隔壁層215が形成されている。

30

**【 0 2 3 8 】**

陽極層216を形成する材料は酸化インジウムや酸化スズ、酸化亜鉛などの仕事関数の高い材料を用い、陰極にはMgAg、AlMg、Ca、Mg、Li、AlLi、AlLiAgなどのアルカリ金属又はアルカリ土類金属、代表的にはマグネシウム化合物で形成される仕事関数の低い材料を用いる。

**【 0 2 3 9 】**

有機化合物層217は、発光層、正孔注入層、電子注入層、正孔輸送層、電子輸送層等が含まれる。また、有機化合物におけるルミネッセンスには、一重項励起状態から基底状態に戻る際の発光(蛍光)と三重項励起状態から基底状態に戻る際の発光(リン光)があり、これらの方あるいは両方の発光を含んでいる。

40

**【 0 2 4 0 】**

パッシベーション層219としては、窒化珪素、酸窒化珪素、ダイヤモンドライカーボン(DLC)など酸素や水蒸気に対しバリア性の高い材料の膜を形成する。このような構成によりEL素子206の発する光は陽極層216側から放射される構成となる。

**【 0 2 4 1 】**

(図33(b)参照)

一方、図33(b)の画素部も(a)と同様であり、異なる点は電流制御用TFT205

50

がNch TFTであること、EL素子206の陰極と陽極が入れ替わっていることである。電流制御用TFT205の電極224に接続される電極230が陰極であり、231が陽極層である。

#### 【0242】

以上のようにしてアクティブマトリクス型ELパネルを作製することができる。なお、画素部の回路は図32に示す回路に限定されるものではなく、駆動方法により様々な回路が設計できるが、いずれの場合も画素部のTFTを本発明の結晶質半導体層で形成することにより、画素毎に輝度のばらつきが小さいパネルが製造できる。

#### 【0243】

[実施例3] (図34参照)

10

実施例1で説明した非自発光型表示装置である液晶パネルや、自発光型表示装置であるELパネルは表示部として、様々な電子機器に搭載することができる。

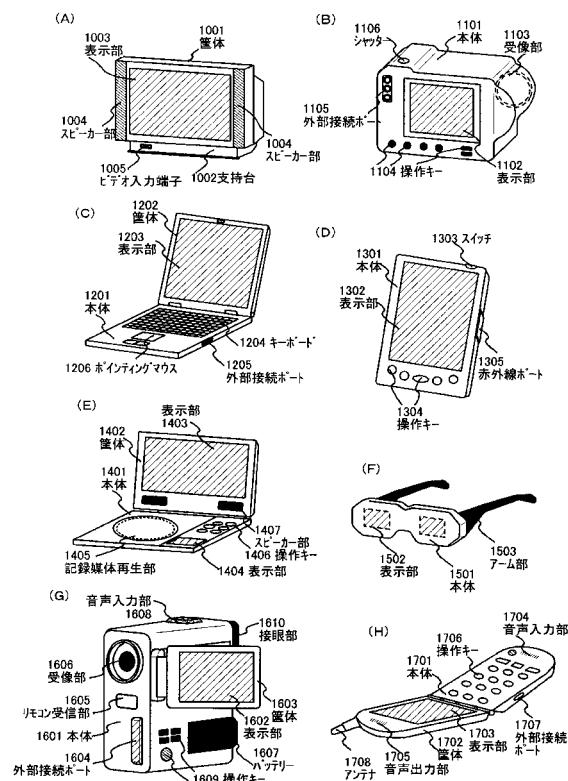

#### 【0244】

例えば、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうる表示装置を備えた装置)などが挙げられる。それら電子機器の具体例を図34に示す。

20

#### 【0245】

(図34(A)参照)

図34(A)は表示装置であり、パソコン用、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。

筐体1001、支持台1002、表示部1003、スピーカー部1004、ビデオ入力端子1005等を備えている。表示部1003として、実施例の直視型の液晶パネルやELパネルが搭載される。また、表示部1003をスクリーンとして、光学系により液晶パネルやELパネルに表示された映像を投写する投写型表示装置とするのも可能である。

#### 【0246】

なお、現状では、エレクトロルミネッセンス材料の輝度が小さいため、投写型に適用可能なものは液晶パネルであるが、将来、輝度の高いエレクトロルミネッセンス材料が開発されれば、本発明のTFTアレイ基板を用いた投写型のエレクトロルミネッセンス表示装置が実用化可能になる。

30

#### 【0247】

(図34(B)参照)

図34(B)はデジタルスチルカメラであり、本体1101、表示部1102、受像部1103、操作キー1104、外部接続ポート1105、シャッター1106等を含む。実施例の液晶パネルやELパネルが、表示部1102として搭載されている。また、デジタルスチルカメラとしては、静止が記録、再生機能のみではなく、動画像記録、再生機能を併せ持つものも含まれる。

40

#### 【0248】

(図34(C)参照)

図34(C)はノート型パーソナルコンピュータであり、本体1201、筐体1202、表示部1203、キーボード1204、外部接続ポート1205、ポインティングマウス1206等を含む。実施例の液晶パネルやELパネルが、表示部1203として搭載されている。

#### 【0249】

(図34(D)参照)

図34(D)はPDAであり、本体1301、表示部1302、スイッチ1303、操作キー1304、赤外線ポート1305等を含む。実施例の液晶パネルやELパネルが、表

50

示部 1302 として搭載されている。

**【0250】**

(図 34 (E) 参照)

図 34 (E) は記録媒体を備えた携帯型の画像再生装置（具体的には DVD 再生装置を想定している）であり、本体 1401、筐体 1402、表示部 1403、表示部 1404、記録媒体（DVD 等）再生部 1405、操作キー 1406、スピーカー部 1407 等を含む。表示部 1403 は主として、記録媒体に記録された画像情報を表示するものである。表示部 1404 は、記録媒体に記録された画像情報のタイトルや、操作方法などの主として文字・記号情報を表示するものである。実施例の液晶パネルや EL パネルが、表示部 1403、1404 として搭載されている。

10

**【0251】**

(図 34 (F) 参照)

図 34 (F) はゴーグル型ディスプレイであり、本体 1501、表示部 1502、アーム部 1503 を含む。実施例の液晶パネルや EL パネルが、表示部 1502 に用いられている。図示の表示装置は眼鏡型のフェイスマウント型の表示装置であるが、ヘッドマウント型のディスプレイにも適用可能であることは明らかである。

**【0252】**

また、表示部 1502 の方式には、パネルサイズ対角 1 インチ未満の液晶パネルや EL パネルを直視するタイプや、本体 1501 に光学系を内蔵し、このような微細なパネルに表示される映像を光学系により投射する投写型の 2 つの方式があげられる。

20

**【0253】**

(図 34 (G) 参照)

図 34 (G) はビデオカメラであり、本体 1601、表示部 1602、筐体 1603、外部接続ポート 1604、リモコン受信部 1605、受像部 1606、バッテリー 1607、音声入力部 1608、操作キー 1609、接眼部 1610 等を含む。実施例の液晶パネルや EL パネルが、表示部 1602 として搭載されている。

**【0254】**

(図 34 (H) 参照)

図 34 (H) は携帯電話であり、本体 1701、筐体 1702、表示部 1703、音声入力部 1704、音声出力部 1705、操作キー 1706、外部接続ポート 1707、アンテナ 1708 等を含む。実施例の液晶パネルや EL パネルが、表示部 1703 として搭載されている。

30

**【0255】**

以上の様に、本発明の TFT でなるアクティブマトリクス型表示パネルの適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能であり、図 34 はごく一例を図示したにすぎないものであり、その用途を限定するものではないことを付記する。

**【0256】**

**【発明の効果】**

本発明は、薄膜トランジスタやダイオードなどの半導体素子のチャネルとなる結晶質半導体層は、その下層の結晶質半導体層を種として、基板水平方向結晶成長（横成長させる）させるため、チャネル形成領域において半導体の結晶粒の粒界はチャネル長方向に平行に制御することができる。

40

さらに、この種となる下層の結晶質半導体層の結晶方位をそろえるようにしたため、チャネル形成領域において、チャネル長方向について半導体の結晶粒の結晶方位を揃えることができる。

**【0257】**

したがって、上記のようにチャネル形成領域の結晶粒の粒界の位置、及び結晶粒の結晶方位を制御することができるようになるため、高い電界効果移動度の薄膜トランジスタを素子ごとの特性のばらつきを抑えて集積化した回路を作製することが可能になる。

**【0258】**

50

また、上層の非晶質半導体層の膜厚を60nm以下、さらには40nm以下と薄くしても、種となる下層の結晶質半導体層があるため、上層の非晶質半導体層を上述のように結晶粒界の位置及び結晶方位を揃えて結晶成長させることができる。よって、例えば、このような結晶化技術を薄膜トランジスタの製造技術に適用すれば、チャネル形成領域となる半導体層を薄く、かつ上記のような優れた結晶性を有する物とすることができますため、オフ状態での電流のリークを小さくでき、かつオン電流／オフ電流比を高くすることができます。

#### 【0259】

また、本発明の結晶化方法は、ガラス基板を使用できるプロセス温度である。したがって、従来のように熱酸化を利用した薄膜化をせずとも、チャネル形成領域の厚さを60nm以下、さらには40nm以下と薄く設けることを可能にする。10

#### 【0260】

また、上記したように、チャネル形成領域となる半導体層を60nm以下、さらには40nm以下と薄くしても、配線もしくは電極とコンタクト部分に下層の第1結晶質半導体層及び上層の第2結晶質半導体層という2層の半導体層を設け、下層の結晶質半導体層の膜厚を調節することで、コンタクト抵抗が高くなることを避けることができる。

#### 【図面の簡単な説明】

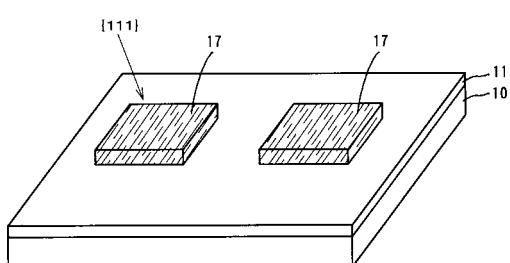

【図1】 第1の結晶質半導体層を形成する方法を示す斜視図である（実施形態1）。

【図2】 図1の続きを示す図であり、第1の結晶質半導体膜を形成する方法を示す図である（実施形態1）。20

【図3】 図2の続きを示す図であり、第1の結晶質半導体膜を形成する方法を示す図である（実施形態1）。

【図4】 図3の続きを示す図であり、第1の結晶質半導体膜を形成する方法を示す図である（実施形態1）。

【図5】 図4の続きを示す図であり、第1の結晶質半導体層を形成する方法を示す図である（実施形態1）。

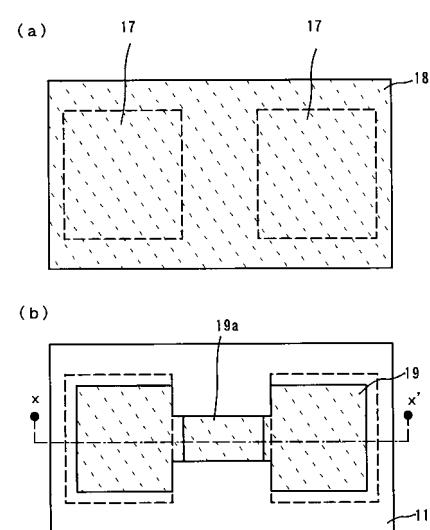

【図6】 図5の続きを示す図であり、第2の非晶質半導体層を形成する方法を示す図である（実施形態1）。

【図7】 図6の続きを示す図であり、連続発振レーザー光による結晶化により第2の結晶質半導体層を形成する方法を示す（実施形態1）。30

【図8】 図7の続きを示す図であり、薄膜トランジスタの作製行程を示す。（実施形態1）

【図9】 第1の結晶質半導体膜を形成する方法を示す斜視図である（実施形態2）。

【図10】 図9の続きを示す図であり、第1の結晶質半導体膜を形成する方法を示す図である（実施形態2）。

【図11】 図10の続きを示す図であり、第1の結晶質半導体膜を形成する方法を示す図である（実施形態2）。

【図12】 図11の続きを示す図であり、第1の結晶質半導体層を形成する方法を示す図である。（実施形態2）

【図13】 図12の続きを示す図であり、第2の非晶質半導体層を形成する方法を示す図である（実施形態2）。40

【図14】 図13の続きを示す図であり、連続発振レーザー光による結晶化により第2の結晶質半導体層を形成する方法を示す（実施形態2）。

【図15】 第1の結晶質半導体膜を形成する方法を示す斜視図である（実施形態2）。

【図16】 図9の続きを示す図であり、第1の結晶質半導体層を形成する方法を示す図である（実施形態3）。

【図17】 図10の続きを示す図であり、第1の結晶質半導体層を形成する方法を示す図である（実施形態3）。

【図18】 図11の続きを示す図であり、第1の結晶質半導体層を形成する方法を示す図である。（実施形態3）50

【図19】 図18の続きを示す図であり、第2の結晶質半導体層を形成する方法を示す図である（実施形態3）。

【図20】 図19の続きを示す図であり、第2の結晶質半導体層を形成する方法を示す図である（実施形態3）。

【図21】 図20の斜視図に対応し、連続発振レーザー光により、第2の結晶質半導体層を形成する方法を示す図である（実施形態3）。

【図22】 第1の結晶質半導体層を形成する方法を示す図である（実施形態5）。

【図23】 第1の結晶質半導体層を形成する方法を示す図である（実施形態5）。

【図24】 パルス発振レーザー光による結晶化により第2結晶質半導体層を形成する方法を示す図である。（実施形態6） 10

【図25】 薄膜トランジスタの断面図である。（実施形態7）

【図26】 アクティブマトリクス型液晶パネルの構成を示す概略図である。（実施例1）

【図27】 アクティブマトリクス型液晶パネルの画素部の等価回路図である。（実施例1）

【図28】 アクティブマトリクス型液晶パネルの画素部の上面図である。（実施例1）

【図29】 アクティブマトリクス型液晶パネルのTFTアレイ基板の作製方法を示す断面図である。（実施例1）

【図30】 図29の続きを示す図であり、アクティブマトリクス型液晶パネルのTFTアレイ基板の作製方法を示す断面図である。（実施例1） 20

【図31】 図30続きを示す図であり、アクティブマトリクス型液晶パネルのTFTアレイ基板の作製方法を示す断面図である。（実施例1）

【図32】 エレクトロルミネッセンスを用いた表示装置の画素部の等価回路図である。（実施例2）

【図33】 同画素部の断面図である。（実施例2）

【図34】 本発明が適用される電子機器の例示を示す図である。（実施例3）

【図35】 EBS-Pデータから得られる標準三角形の説明

【図36】 実施形態1、実施形態2及び参考例1の第1の結晶質半導体層についての標準三角形である。

【図37】 参考例2の第1の結晶質半導体層についての標準三角形である。 30

【符号の説明】

|     |                      |

|-----|----------------------|

| 1 0 | 基板                   |

| 1 1 | 下地膜                  |

| 1 2 | 第1の非晶質半導体膜（非晶質シリコン膜） |

| 1 7 | 第1の結晶質半導体層（結晶質シリコン層） |

| 2 2 | 第2の結晶質半導体層（結晶質シリコン層） |

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

(c) 図(b)のx-x'断面図

【図7】

【図8】

【図9】

【図10】

【図12】

【図11】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図28】

【図27】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

---

フロントページの続き

(51)Int.Cl.

F I

H 0 1 L 21/20

H 0 1 L 21/268

F

(58)調査した分野(Int.Cl., DB名)

H01L 29/786

H01L 21/20

H01L 21/268

H01L 21/336

G02F 1/1368