(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4697384号

(P4697384)

(45) 発行日 平成23年6月8日(2011.6.8)

(24) 登録日 平成23年3月11日(2011.3.11)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/06  | (2006.01) | HO1L 29/06 | 301F |

| HO1L 21/28  | (2006.01) | HO1L 21/28 | 301R |

| HO1L 21/822 | (2006.01) | HO1L 27/04 | R    |

| HO1L 27/04  | (2006.01) | HO1L 27/04 | H    |

| HO1L 29/41  | (2006.01) | HO1L 29/44 | S    |

請求項の数 5 (全 10 頁) 最終頁に続く

(21) 出願番号

特願2004-10063 (P2004-10063)

(22) 出願日

平成16年1月19日 (2004.1.19)

(65) 公開番号

特開2005-203658 (P2005-203658A)

(43) 公開日

平成17年7月28日 (2005.7.28)

審査請求日

平成18年10月6日 (2006.10.6)

(73) 特許権者 000106276

サンケン電気株式会社

埼玉県新座市北野3丁目6番3号

(74) 代理人 100082049

弁理士 清水 敬一

(72) 発明者 穂谷 淳

埼玉県新座市北野3丁目6番3号 サンケン電気株式会社内

審査官 安田 雅彦

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の半導体領域及び該第1の半導体領域とは異なる導電型により前記第1の半導体領域の表面の一部に形成される第2の半導体領域を有する半導体層と、

第1及び第2の開口部をもって前記半導体層の主面を被覆する絶縁膜と、

該絶縁膜を介して前記半導体層の主面上に互いに離間して形成される第1の電極及び第2の電極とを備え、

前記第2の半導体領域は、前記第1の開口部内の前記第1の電極に電気的に接続される第1の領域と、前記第2の開口部内の前記第2の電極に電気的に接続される第2の領域と、前記第1の領域と前記第2の領域との間に形成される抵抗領域とを有し、

前記第1の電極は、前記絶縁膜の第1の開口部内に配置されて前記第2の半導体領域の主面に接触する主電極部と、該主電極部に接続され且つ前記絶縁膜を介して前記第2の半導体領域の抵抗領域を被覆する延長部とを有し、

前記第2の電極は、前記絶縁膜の第2の開口部内に配置されて前記第2の半導体領域の主面に接触する主電極部を有し、

前記第2の半導体領域と同一の導電型の半導体領域から成る電界緩和領域を前記第2の半導体領域から離間して且つ前記第1の電極の延長部と前記第2の電極との間に形成し、前記電界緩和領域により、空乏層を連続的に形成して、前記第1の半導体領域と前記第2の半導体領域との界面に形成されるP N接合の電界集中を緩和することを特徴とする半導体装置。

10

20

**【請求項 2】**

前記第2の電極は、前記第2の半導体領域に並行に前記主電極部から延伸する延長部を有し、

該延長部は、前記絶縁膜を介して前記第1の半導体領域の主面を被覆する請求項1に記載の半導体装置。

**【請求項 3】**

前記絶縁膜を介して前記半導体層の主面上に前記第1の電極及び第2の電極から離間して形成される第3の電極と、前記半導体層の主面とは反対側の前記半導体層の底面に形成される接地電極とを備え、

前記半導体層は、前記第1の半導体領域とは異なる導電型により形成される第3の半導体領域を有し、

前記第2の半導体領域は、前記絶縁膜に形成される第3の開口部内の前記第3の電極に電気的に接続される第3の領域を有し、

前記第1の半導体領域と前記第2の半導体領域との界面に第1のPN接合を形成し、

前記第3の半導体領域内に形成される前記第1の半導体領域と前記第3の半導体領域との界面に第2のPN接合を形成し、

前記第1の電極から前記接地電極に向かう前記半導体層の深さ方向に双方向ダイオードを形成した請求項1又は2に記載の半導体装置。

**【請求項 4】**

前記第2の半導体領域は、前記第1の領域に接続される前記抵抗領域となる蛇行部と、該蛇行部と前記第2の領域との間に接続される直線状部とを有し、

前記第1の電極と第2の電極とは、前記蛇行部及び直線状部を通じて互いに電気的に接続され、

前記蛇行部は、前記絶縁膜を介して前記第1の電極の延長部により被覆され、

前記電界緩和領域は、前記直線状部の両側に且つ該直線状部から離間して前記第1の半導体領域内に形成される請求項3に記載の半導体装置。

**【請求項 5】**

前記第1の電極の延長部は、フィールドプレートを構成し、

前記電界緩和領域は、フィールド・リミッティング・リングを構成する請求項1～4の何れか1項に記載の半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は抵抗素子を内蔵する半導体装置、特に小面積で能動素子及び抵抗素子等を構成する半導体領域全周の耐圧を向上できる半導体装置に関する。

**【背景技術】****【0002】**

ダイオード又はトランジスタ等の能動素子及びこの能動素子と電気的に接続された抵抗素子を一体的に集積化した半導体装置は公知である。例えば、下記の特許文献1は多数の半導体層を形成した半導体基板の上面に絶縁膜を介して多結晶シリコン(ポリシリコン)から成る膜抵抗素子を設けた半導体装置を示す。多結晶シリコンから成る抵抗素子を形成するには、イオン注入や複雑で微細な加工技術を必要とし且つ所要の抵抗値を得るために比較的大きな面積で形成しなければならないため、半導体装置の大型化を招来する。特に、集積度の低い半導体装置では抵抗素子による半導体装置の大型化が大きな問題となる。また、下記の特許文献2に開示されるように半導体基板内に形成された拡散層によって抵抗素子を形成した半導体装置が提案されている。

**【0003】**

【特許文献1】特開平7-326772号公報(第3頁、図1)

【特許文献2】特公昭51-22794号公報(第4頁、図5-b)

**【0004】**

10

20

30

40

50

しかしながら、拡散層によって抵抗素子を形成した半導体装置においても、一般的に高い抵抗値を有する電流経路の長い拡散抵抗素子は形状が大型化するため、半導体装置の小型化が困難である。このため、本願出願人は、能動素子を構成する半導体領域の一部を拡散抵抗素子として使用する新規な半導体構造を開発し、特願2003-87467号として特許出願を行った。この半導体構造では、半導体構造の深さ方向に能動素子を形成し、半導体構造の正面と並行な横方向に抵抗素子を形成するため、半導体素子を大型化せずに、能動素子と抵抗素子とを併有する半導体素子を形成できる。

【発明の開示】

【発明が解決しようとする課題】

【0005】

10

ところで、上記の半導体素子では能動素子を構成する半導体領域で抵抗素子を形成するため、能動素子を高耐圧化するためには抵抗素子の耐圧を向上する必要がある。例えば下記の特許文献3に開示される半導体装置に示されるフィールドプレート構造及び下記の特許文献4に開示される半導体装置に示されるF L R (フィールド・リミッティング・リング [Field Limiting Ring])構造を設けて半導体装置の耐圧を向上することが知られている。

【0006】

【特許文献3】特開平5-299640号公報(第4頁、図6)

【特許文献4】特開平11-297994号公報(第8頁、図6及び図7)

【0007】

20

この場合、半導体領域に形成される抵抗素子の両端子間を電気的に分離するため、その全周に亘ってフィールドプレートを形成できず、抵抗素子を構成する半導体領域の耐圧をフィールドプレートにより向上することは不可能である。一方、半導体領域の全周に亘って形成されるF L R構造により、半導体領域全周の耐圧を向上することは可能であるが、半導体領域が大型化する問題点がある。即ち、F L R構造を備えた抵抗素子内に小さな曲率を有する屈曲形状や、緻密に配置された渦巻形状等に抵抗素子を形成することが困難となり、高い抵抗値を有する抵抗素子を小面積の半導体領域内に形成することができない。

【0008】

そこで、本発明の目的は、耐圧の高い小占有面積の半導体領域を設けた半導体装置を提供することにある。

30

【課題を解決するための手段】

【0009】

本発明による半導体装置は、第1の半導体領域(1)及び第2の半導体領域(2)とは異なる導電型により第1の半導体領域(1)の表面の一部に形成される第2の半導体領域(2)を有する半導体層(20)と、第1及び第2の開口部(4b, 4c)をもって半導体層(20)の正面(20a)を被覆する絶縁膜(4)と、絶縁膜(4)を介して半導体層(20)の正面(20a)上に互いに離間して形成される第1の電極(5)及び第2の電極(6)とを備える。第2の半導体領域(2)は、第1の開口部(4b)内の第1の電極(5)に電気的に接続される第1の領域(10)と、第2の開口部(4c)内の第2の電極(6)に電気的に接続される第2の領域(11)と、第1の領域(10)と第2の領域(11)との間に形成される抵抗領域(13)とを有する。第1の電極(5)は、絶縁膜(4)の第1の開口部(4b)内に配置されて第2の半導体領域(2)の正面(2a)に接触する主電極部(5a)と、主電極部(5a)に接続され且つ絶縁膜(4)を介して第2の半導体領域(2)の抵抗領域(13)を被覆する延長部(5b)とを有する。第2の電極(6)は、絶縁膜(4)の第2の開口部(4c)内に配置されて第2の半導体領域(2)の正面(2a)に接触する主電極部(6a)を有する。第2の半導体領域(2)と同一の導電型の半導体領域から成る電界緩和領域(31)を第2の半導体領域(2)から離間して且つ第1の電極(5)の延長部(5b)と第2の電極(6)との間に形成し、電界緩和領域(31)により、空乏層を連続的に形成して、第1の半導体領域(1)と第2の半導体領域(2)との界面に形成されるP N接合(41)の電界集中を緩和する。第1の電極(5)の延長部(5b)と第2の電極(6)との間に第2の半導体領域(2)から離間して電界緩和領域(31)を形成するとは、第1の電極(5)の延長部(5b)の端部に接する接線と第2の電極(6)の端部に接する

40

50

接線との間に、第2の半導体領域(2)から離間して電界緩和領域(31)を形成することを意味する。

【0010】

互いに離間して形成される第1の電極(5)と第2の電極(6)との間に介在する第2の半導体領域(2)は、抵抗素子となり、第1の電極(5)の延長部(5b)は、第1の半導体領域(1)と第2の半導体領域(2)との界面に形成される第1のPN接合から広がる空乏層(41)のカーバチャを緩和し、第1のPN接合(41)の曲部近傍に起こる電界集中を抑制するフィールドプレートを形成する。また、フィールドプレートによる電界緩和効果が得られない第1の電極(5)の延長部(5b)と第2の電極(6)との間の第2の半導体領域(2)にFLRとして作用する電界緩和領域(31)を設けることにより、第1の電極(5)の及ばない部分にも空乏層を連続的に形成して、フィールドプレートによる電界緩和効果を補完することができる。このため、第1の半導体領域(1)と第2の半導体領域(2)との界面に形成される第1のPN接合(41)に逆方向電圧が印加されたときに、第1の電極(5)の延長部(5b)と電界緩和領域(31)とにより、電界集中を良好に緩和できる空乏層を形成でき、PN接合の安定な高耐圧化を図るので、小さな占有面積で半導体領域全周の耐圧の向上が可能となる。10

【発明の効果】

【0011】

第1の電極(5)によるフィールドプレートと、電界緩和領域(31)によるFLRを併用して、半導体領域(2)の全周に連続的に曲率の大きな空乏層を形成することができる。このため、小さな占有面積で半導体領域のPN接合の曲部に起こる電界集中を緩和して半導体領域全周の耐圧を向上できるので、抵抗素子を内蔵する高耐圧の半導体装置の小型化を実現できる。20

【発明を実施するための最良の形態】

【0012】

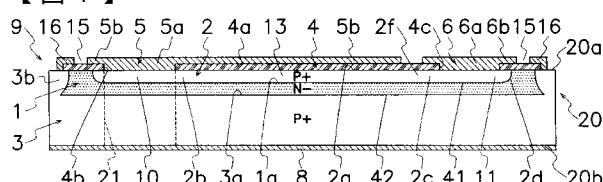

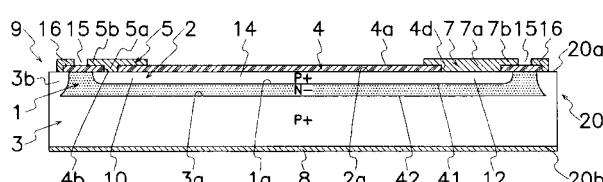

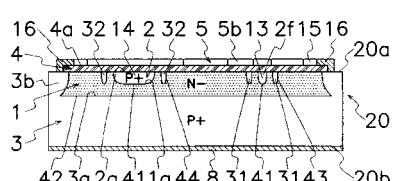

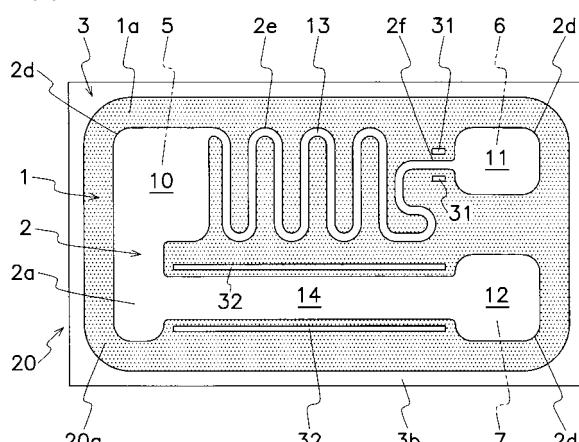

以下、双方向ダイオードを含む本発明による半導体装置の実施の形態を図1～図8について説明する。

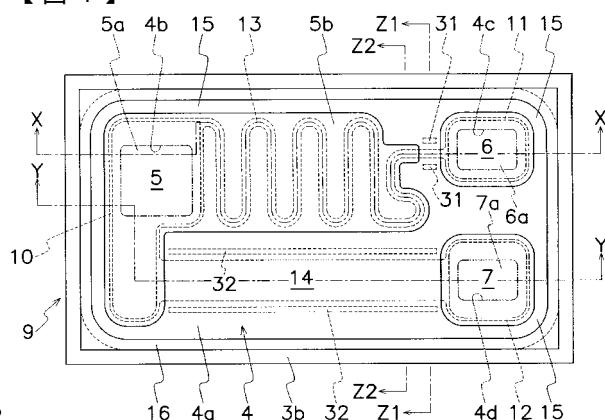

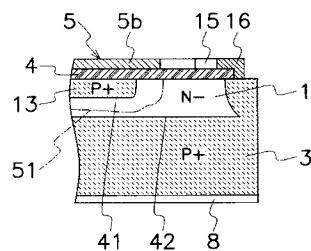

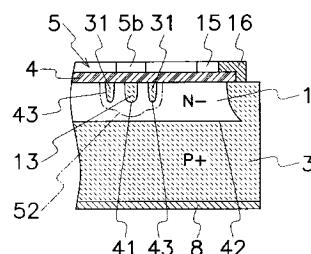

本実施の形態の半導体装置は、図1～図3に示すように、N-型半導体領域を構成する第1の半導体領域(1)と、第1の半導体領域(1)とは異なる導電型により第1の半導体領域(1)の主面(1a)上に隣接して形成されたP+型半導体領域を構成する第2の半導体領域(2)と、第1の半導体領域(1)とは異なる導電型により第1の半導体領域(1)の主面(1a)とは反対側の他面に隣接して形成されたP+型半導体領域の第3の半導体領域(3)とを有する半導体層(20)を備え、半導体層(20)の主面(20a)とは反対側の底面(20b)には、接地電極(8)が形成される。従って、第2の半導体領域(2)と第3の半導体領域(3)とは互いに同一の導電型であり、第2の半導体領域(2)及び第3の半導体領域(3)と第1の半導体領域(1)とは異なる導電型である。図4及び図5に示すように、互いに離間して形成された第1～第3の開口部(4b～4d)を有する絶縁膜(4)は、半導体層(20)の主面(20a)を被覆する。30

【0013】

図4に示すように、第1～第3の電極(5～7)は縁部導体(16)から間隙部(15)を介して離間した位置に配置される。第2の半導体領域(2)には第1の領域(10)、第2の領域(11)及び第3の領域(12)が互いに離間して形成され、第1～第3の領域(10～12)の各曲部には電界集中を緩和する湾曲接合部(2d)が設けられる。第1の電極(5)は、絶縁膜(4)の第1の開口部(4b)を通じて第2の半導体領域(2)の第1の領域(10)に電気的に接続され、第2の電極(6)は、絶縁膜(4)の第2の開口部(4c)を通じて第2の半導体領域(2)の第2の領域(11)に電気的に接続される。同様に、第3の電極(7)は、絶縁膜(4)の第3の開口部(4d)を通じて第2の半導体領域(2)の第3の領域(12)に電気的に接続される。第1の領域(10)と第2の領域(11)は、第2の半導体領域(2)によって形成された第1の抵抗領域(13)を通じて電気的に接続され、第1の領域(10)と第3の領域(12)は、第2の半導体領域(2)によって形成された第2の抵抗領域(14)により電気的に接続される。40

【0014】

図5に示すように、第2の半導体領域(2)の第1の領域(10)と第2の領域(11)との間を

50

接続する第1の抵抗領域(13)は、第1の領域(10)に接続された蛇行部(2e)と、蛇行部(2e)と第2の領域(11)との間に接続された直線状部(2f)とを有する。第1の抵抗領域(13)が幅狭の帯状の蛇行部(2e)を有することで、第1の領域(10)と第2の領域(11)との間に所望の長さを有する第1の抵抗領域(13)を比較的小さな占有面積で形成できる。このため、比較的小さな占有面積で第1の抵抗領域(13)に所要の高い抵抗値を付与することができる。また、第1の領域(10)と第3の領域(12)との間を接続する第2の抵抗領域(14)は、第1の抵抗領域(13)より幅が広く且つ直線的に延伸する帯状に形成される。このため、第2の抵抗領域(14)は、第1の抵抗領域(13)より低い抵抗値を有する。

#### 【0015】

本実施の形態では、複数回屈曲する幅狭の帯状に形成される第1の抵抗領域(13)は相対的に高い抵抗値、例えば5kΩに設定され、直線的な幅広の帯状に形成される第2の抵抗領域(14)は相対的に低い抵抗値、例えば240Ωに設定される。

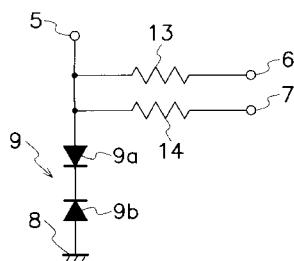

通常の動作時には第1及び第2の領域(10,11)間と第1及び第3の領域(10,12)間の抵抗素子が動作し、過電圧が印加された時は図6に示す双方向ダイオード(9)がオンしてバッケメタルとしての接地電極(8)を通じて電流を流すことができる。第1の抵抗領域(13)及び第2の抵抗領域(14)の抵抗値は、第1及び第2の抵抗領域(13,14)を構成する第2の半導体領域(2)の幅、長さ及び深さ並びに不純物濃度により適宜設定し又は調整することができる。

#### 【0016】

絶縁膜(4)は、例えば半導体層(20)の主面(20a)を熱酸化して形成されたシリコン酸化膜(SiO<sub>2</sub>)から成り、第1～第3の領域(10～12)と第1～第3の電極(5～7)とを電気的に接続する3つの開口部(4b～4d)が形成される。開口部(4b～4d)が形成された絶縁膜(4)は、第1の半導体領域(1)、第2の半導体領域(2)及び第3の半導体領域(3)が露出する半導体層(20)の主面(20a)を被覆し、絶縁膜(4)を介して互いに離間して配置される第1の電極(5)、第2の電極(6)及び第3の電極(7)は、各開口部(4b)を通じて第2の半導体領域(2)の第1の領域(10)、第2の領域(11)及び第3の領域(12)にそれぞれ電気的に接続される。

#### 【0017】

図1及び図2に示すように、第1～第3の電極(5～7)は、絶縁膜(4)の開口部(4b)を通じて第2の半導体領域(2)の第1～第3の領域(10～12)にそれぞれ接触する主電極部(5a～7a)と、主電極部(5a～7a)から第2の半導体領域(2)と並行に延伸し且つ絶縁膜(4)を介して第1の半導体領域(1)の主面(1a)を被覆する延長部(5b～7b)とを備える。第1～第3の電極(5～7)は例えば周知のアルミニウム(Al)蒸着等の方法により形成される。第1の電極(5)は一方のダイオード(9a)のアノード電極、第1の抵抗領域(13)の一端の電極及び第2の抵抗領域(14)の一端の電極を構成する。また、第2の電極(6)は第1の抵抗領域(13)の他端の電極を構成し、第3の電極(7)は第2の抵抗領域(14)の他端の電極を構成する。図4に示すように、第2の半導体領域(2)に形成された第1の抵抗領域(13)の蛇行部(2e)は、絶縁膜(4)を介して第1の電極(5)の延長部(5b)により被覆される。このため、第1の電極(5)の延長部(5b)が放熱体として良好に機能し、第1の抵抗領域(13)で発生した熱を延長部(5b)を通じて外部へ放出することができる。この結果、抵抗値の変動や半導体素子の特性変動を良好に防止することができる。

#### 【0018】

また、図3～図5に示すように、第1の電極(5)の延長部(5b)と第2の電極(6)との間に介在する第1の抵抗領域(13)の直線状部(2f)の外側には、直線状部(2f)から離間して第1の電界緩和領域(31)が形成されている。更に、図3～図5に示すように、第1の電極(5)と第3の電極(7)との間に介在する第2の抵抗領域(14)の外側には、第2の抵抗領域(14)から離間して第2の電界緩和領域(32)が形成されている。第1の電界緩和領域(31)及び第2の電界緩和領域(32)は、第2の半導体領域(2)と同一の導電型のP+型半導体領域から成る。

#### 【0019】

図1～図3に示すように、第3の半導体領域(3)は、第1の半導体領域(1)に隣接して、

10

20

30

40

50

半導体層(20)の正面(20a)に向けて下面から上方に広がる傾斜縁部(3b)を有する。第3の半導体領域(3)の傾斜縁部(3b)は、図5に示すように、第1の半導体領域(1)の外周縁を包围して枠状に形成される。傾斜縁部(3b)の上面には、縁部導体(16)が接続されている。図1～図3に示すように、第2の半導体領域(2)と第3の半導体領域(3)との間に第1の半導体領域(1)が形成されるので、第1の半導体領域(1)の正面(1a)に第2の半導体領域(2)が接触し、第1の半導体領域(1)の正面(1a)とは反対側の他面及び外周部に第3の半導体領域(3)の正面(3a)及びその傾斜縁部(3b)が接触する。第3の半導体領域(3)の正面(3a)とは反対側の他面は、半導体層(20)の他面(20b)として接地電極(8)に電気的に接続される。接地電極(8)は、例えばアルミニウム(AI)等から成る金属膜を半導体層(20)の他面(20b)にスパッタリング又は真空蒸着することにより形成することができる。

10

#### 【0020】

図1に示すように、第1の半導体領域(1)と第2の半導体領域(2)との界面には第1のP N接合(41)が形成され、第1の半導体領域(1)と第3の半導体領域(3)との界面には第2のP N接合(42)が形成されるため、主として破線部(21)で示す領域に第1の電極(5)から接地電極(8)に向かう半導体層(20)の深さ方向に能動素子としての双方向ダイオード(9)のP N P構造が形成される。即ち、双方向ダイオード(9)は、図6に示すように互いに逆極性に接続された一方のダイオード(9a)と他方のダイオード(9b)とを有し、一方のダイオード(9a)はアノード領域を形成する第2の半導体領域(2)とカソード領域を形成する第1の半導体領域(1)とにより構成され、他方のダイオード(9b)はアノード領域を形成する第3の半導体領域(3)とカソード領域を形成する第1の半導体領域(1)とにより構成される。

20

図3に示すように、第1の半導体領域(1)と第1の電界緩和領域(31)との界面には第3のP N接合(43)が形成され、第1の半導体領域(1)と第2の電界緩和領域(32)との界面には第4のP N接合(44)が形成される。

#### 【0021】

第1の半導体領域(1)と第2の半導体領域(2)との界面に形成された第1のP N接合(41)に逆方向電圧が印加されたとき、第1のP N接合(41)から空乏層が広がる。この空乏層は、第1～第3の電極(5～7)の延長部(5b～7b)によって構成されるフィールドプレートによつて、第1の半導体領域(1)内に良好に広げられる。即ち、図1に示すように、第2の電極(6)は、主電極部(6a)から第2の半導体領域(2)と並行に延伸し且つ絶縁膜(4)を介して第1の半導体領域(1)の正面(1a)を被覆する延長部(6b)を有し、延長部(6b)は、第1の電極(5)の延長部(5b)と同様にフィールドプレートを形成する。同様に、第3の電極(7)は、主電極部(7a)から第2の半導体領域(2)と並行に延伸し且つ絶縁膜(4)を介して第1の半導体領域(1)の正面(1a)を被覆する延長部(6b)を有し、延長部(6b)は、第1の電極(5)の延長部(5b)と同様にフィールドプレートを形成する。

30

#### 【0022】

また、第1～第3の電極(5～7)の延長部(5b～7b)によって構成されるフィールドプレートの効果が及ばない領域には、F L Rとして機能する第1の電界緩和領域(31)と第2の電界緩和領域(32)が形成されており、フィールドプレートによる電界集中緩和効果が補完されている。即ち、第1の電極(5)の延長部(5b)と第2の電極(6)の延長部(6b)との間には第1の電界緩和領域(31)が形成されており、第1の電極(5)の延長部(5b)及び第3の電極(7)の延長部(7b)との間には第2の電界緩和領域(32)が形成されている。このため、第1のP N接合(41)から広がる空乏層が、第1の半導体領域(1)と第1の電界緩和領域(31)との界面に形成された第3のP N接合(43)及び第1の半導体領域(1)と第2の電界緩和領域(32)との界面に形成された第4のP N接合(44)に到達すると、第3のP N接合(43)及び第4のP N接合(44)からも空乏層が広がり、空乏層のカーバチャ(曲率)を緩和することができる。この結果、第1のP N接合(41)の全周にわたって、電界集中を良好に緩和できる連続した空乏層を形成することができる。

40

#### 【0023】

半導体層(20)は、第3の半導体領域(3)を構成する厚さ200～300μm程度のP+型シリコン基板を出発母材として形成され、この基板の上面に、例えば厚さ40μm程度の

50

第1の半導体領域(1)をエピタキシャル成長で形成させる。次に、図示しないが周知のフォトリソグラフィ技術により所定の形状を有する拡散マスクを基板の正面に被覆する。拡散マスクに形成された開口には、第1～第3の領域(10～12)、第1及び第2の抵抗領域(13,14)及び第1及び第2の電界緩和領域(31,32)を形成する部分の第1の半導体領域(1)の上面が露出する。続いて、拡散マスクの開口を通じて第1の半導体領域(1)の正面(1a)にP型不純物を拡散して15μm程度の厚さで第2の半導体領域(2)と第1及び第2の電界緩和領域(31,32)を形成する。また、第3の半導体領域(3)のうち半導体層(20)の正面(20a)に露出する部分は、N型不純物を拡散して形成する。このように、エピタキシャル成長層により第1の半導体領域(1)を形成すれば、図6に示す双方向ダイオード(9)を構成する2つのダイオード(9a,9b)の耐圧をほぼ等しくすることができる。

10

#### 【0024】

本実施の形態の半導体装置では、下記の作用効果が得られる。

[1] 互いに離間して形成される第1の電極(5)と第2の電極(6)との間及び第1の電極(5)と第3の電極(7)との間にそれぞれ介在する第2の半導体領域(2)を異なる抵抗値を有する抵抗素子として使用することができる。

[2] F L Rとして機能する第1の電界緩和領域(31)と第2の電界緩和領域(32)によって、フィールドプレートによる電界集中緩和効果が補完され、P N接合(41)の全周にわたって、電界集中を良好に緩和できる曲率の大きい連続的な空乏層を形成することができる。このため、P N接合の高耐圧化を安定して図ることができる。また、フィールドプレート効果が及ばない領域をF L Rで補完する構造としたため、高耐圧化構造を比較的小さな占有面積で構築することができる。

20

[3] 第1及び第2の領域(10,11)間で連続する複数の蛇行部(2e)及び直線状部(2f)を有する第1の抵抗領域(13)に大きな抵抗値を付与することができる。また、第1の抵抗領域(13)の直線状部(2f)から離間して第1の電界緩和領域(31)を形成するので、複数の蛇行部(2e)を互いに隣接して配置でき、半導体層(20)に対する第2の半導体領域(2)の占有面積を比較的小さくすることができる。

[4] 第1の電極(5)の延長部(5b)が蛇行部(2e)の曲部に起こる電界集中を良好に緩和するフィールドプレートとして作用するので、第2の半導体領域(2)を相対的に幅狭に且つ小さな曲率で形成することができ、高い抵抗値を有し且つ高耐圧の第1の抵抗領域(13)を比較的小さな占有面積で形成できる。

30

[5] 半導体層(20)の深さ方向に能動素子を形成し、半導体層(20)の正面(20a)と並行な方向に抵抗素子を形成するので、半導体装置を大型化せずに、高耐圧の半導体装置を形成できる。

[6] 一方のダイオード(9a)のアノード領域の一部として第1及び第2の抵抗領域(13,14)を作用させて、双方向ダイオードの電流容量を増大させることができる。

[7] 相対的に抵抗値の高い第1の抵抗領域(13)を屈曲形状で形成したので、1つの半導体層(20)内に抵抗値の高い第1の抵抗領域(13)と抵抗値の低い第2の抵抗領域(14)とを集積できると共に、その占有面積を十分に小さくすることができる。

#### 【0025】

本発明の実施態様は前記の実施の形態に限定されず、種々の変更が可能である。例えば、3つ以上の抵抗領域(13,14)を第2の半導体領域(2)に設けてもよい。また、図示の波形パターンに限らず、半導体基板の形状又は抵抗値の設定等の諸条件により渦巻状等の様々な形状に第1の抵抗領域(13)を形成することができる。また、図示の一重の第1及び第2の電界緩和領域(31,32)に限定されず、二重以上の電界緩和領域を設けてもよい。更に、図6に示す抵抗値の異なる2つの抵抗領域(13,14)を備えた双方向ダイオードについて上記の実施の形態を説明したが、単方向ダイオード、サイリスタ、トランジスタ又はパワーI C等の異なる形態のP N接合を有する半導体素子を備えた半導体装置にも本発明を適用することができる。また、第1の電界緩和領域(31)を第1の電極(5)の延長部(5b)の側面側まで延伸させても良い。

40

#### 【産業上の利用可能性】

50

## 【0026】

本発明は、抵抗値の高い拡散抵抗を比較的小さい占有面積で集積でき、且つ素子の耐圧向上に効果が顕著である。

## 【図面の簡単な説明】

## 【0027】

【図1】図4に示す双方向ダイオードのX-X線に沿う断面図

【図2】図4に示す双方向ダイオードのY-Y線に沿う断面図

【図3】図4に示す双方向ダイオードのZ1-Z1線に沿う断面図

【図4】本発明を適用した双方向ダイオードの平面図

【図5】図4の双方向ダイオードの半導体層の正面を示す平面図

10

【図6】図4の双方向ダイオードの電気回路図

【図7】空乏層の形成状態を示す図4のZ2-Z2線に沿う一部断面図

【図8】空乏層の形成状態を示す図4のZ1-Z1線に沿う一部断面図

## 【符号の説明】

## 【0028】

(1)・・第1の半導体領域 (N-型半導体領域)、 (1a)・・正面、 (2)・・第2の半導体領域 (P+型半導体領域)、 (2a)・・正面、 (2b)・・一端、 (2c)・・他端、 (2d)・・湾曲接合部、 (2e)・・蛇行部、 (2f)・・直線状部、 (3)・・第3の半導体領域 (P+型半導体領域)、 (3a)・・正面、 (3b)・・傾斜縁部、 (4)・・絶縁膜、 (4a)・・正面、 (4b~4d)・・開口部、 (5~7)・・第1~第3の電極、 (5a~7a)・・主電極部、 (5b~7b)・・延長部、 (8)・・接地電極、 (9)・・双方向ダイオード、 (9a)・・一方のダイオード、 (9b)・・他方のダイオード、 (10~12)・・第1~第3の領域、 (13)・・第1の抵抗領域、 (14)・・第2の抵抗領域、 (15)・・間隙部、 (16)・・縁部導体、 (20)・・半導体層、 (20a)・・正面、 (20b)・・他面、 (21)・・破線部、 (31)・・第1の電界緩和領域、 (32)・・第2の電界緩和領域、 (41~44)・・第1~第4のPN接合、 (51,52)・・空乏層

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/866 (2006.01) H 01 L 29/90 S

H 01 L 29/44 Y

(56)参考文献 特開2004-296803(JP, A)

特開平10-189879(JP, A)

特開平05-291241(JP, A)

特開昭58-064059(JP, A)

## (58)調査した分野(Int.Cl., DB名)

H 01 L 21/822

H 01 L 29/06

H 01 L 29/41

H 01 L 29/861