(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4622115号

(P4622115)

(45) 発行日 平成23年2月2日(2011.2.2)

(24) 登録日 平成22年11月12日(2010.11.12)

(51) Int.Cl.

H04J 11/00 (2006.01)

F 1

H04J 11/00

Z

請求項の数 22 (全 45 頁)

(21) 出願番号 特願2001-36727 (P2001-36727)

(22) 出願日 平成13年2月14日 (2001.2.14)

(65) 公開番号 特開2001-308818 (P2001-308818A)

(43) 公開日 平成13年11月2日 (2001.11.2)

審査請求日 平成20年1月22日 (2008.1.22)

(31) 優先権主張番号 特願2000-46820 (P2000-46820)

(32) 優先日 平成12年2月18日 (2000.2.18)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100094053

弁理士 佐藤 隆久

(72) 発明者 迫田 和之

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

審査官 菊地 陽一

最終頁に続く

(54) 【発明の名称】信号成分分離装置、フィルタ装置、受信装置、通信装置、および、通信方法

## (57) 【特許請求の範囲】

## 【請求項 1】

マルチキャリア変調された信号群(シンボル群)からある信号群を分離する信号成分分離装置であって、

入力信号群を  $N / 2^{(m+1)}$  シンボル遅延するシンボル遅延手段と、

入力信号群を  $0 \text{ Hz}$  を基準として、 $- (k / 2^m)$  ラジアン位相シフトする位相オフセット調整手段と、

上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と、

上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と

からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されている、

ただし、 $m$  は二分岐回路の段数の位置を示すパラメータであり、

$N$  は 1 变調時間内に存在するシンボルの数であり、

$k$  は  $0 (\text{Hz})$  を基準としてサブキャリアの周波数オフセット

を持つ信号群が入力されていることを示すパラメータである、

信号成分分離装置。

## 【請求項 2】

10

20

複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる受信装置であって、

信号群を受信する受信手段と、

信号成分分離装置であって、入力した信号群を  $N / 2^{(m+1)}$  シンボル遅延するシンボル遅延手段と、入力した信号群を、 $- (k / 2^m)$  ラジアン位相シフトする位相オフセット調整手段と、上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と、上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と、からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されている、信号成分分離装置と、

ただし、 $m$  は二分岐回路の段数の位置を示すパラメータであり、

$N$  は 1 变調時間内に存在するシンボルの数であり、

$k$  は  $0$  (Hz) を基準としてサブキャリアの周波数オフセット

を持つ信号群が入力されていることを示すパラメータである、

上記信号成分分離装置で分離した信号群について直交変換を行う直交変換手段と、

上記直交変換した情報を復号する復号手段と、

を具備する、

受信装置。

### 【請求項 3】

複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる、送信装置と受信装置とを有する通信装置であって、

上記送信装置は、

複数チャネルの情報を独立に符号化する符号化手段と、

上記符号化した情報をそれぞれ所定の変調方式に基づいて変調して信号点配置を行う信号点配置手段と、

上記複数の信号点配置した信号を時間周期的に多重化する信号多重化手段と、

上記多重化した信号を逆直交変換する逆直交変換手段と、

上記直交変換した情報を送出する送信手段と、

を有し、

上記受信装置は、

上記送信手段とは異なる送信手段から送出された信号群を受信する受信手段と、

上記受信した信号群を選択分離する信号成分分離手段と、

上記選択分離された信号を直交変換する直交変換手段と、

上記直交変換した情報を復号する復号手段と

を有し、

上記信号成分分離手段は、

入力信号群を  $N / 2^{(m+1)}$  シンボル遅延するシンボル遅延手段と、

入力信号群を、 $- (k / 2^m)$  ラジアン位相シフトする位相オフセット調整手段と、

上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と、

上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と

からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されて構成されている、

ただし、 $m$  は二分岐回路の段数の位置を示すパラメータであり、

$N$  は 1 变調時間内に存在するシンボルの数であり、

$k$  は  $0$  (Hz) を基準としてサブキャリアの周波数オフセット

10

20

30

40

50

を持つ信号群が入力されていることを示すパラメータである、

通信装置。

【請求項 4】

上記送信装置における上記信号多重化手段は、上記複数の信号点配置した信号を所定のサブキャリア間隔で、チャネルごとに、周波数をずらして多重化する、

請求項 3 記載の通信装置。

【請求項 5】

上記送信装置における上記信号点配置手段における変調方式は直交周波数多重化方式（O F D M 方式）を用いる変調方式である、

請求項 3 記載の通信装置。

10

【請求項 6】

上記送信装置における上記逆直交変換処理手段は逆フーリエ変換処理を行い、

上記受信機における上記直交変換処理手段はフーリエ変換処理を行う、

請求項 3 記載の通信装置。

【請求項 7】

複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる受信装置であって、

信号群を受信する受信手段と、

信号成分分離装置であって、入力信号群を  $N / 2^{(m+1)}$  シンボル遅延するシンボル遅延手段と、入力信号群を  $- (k / 2^m)$  ラジアン位相シフトする位相オフセット調整手段と、上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と、上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と、からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されている信号成分分離装置と、

20

ただし、 $m$  は二分岐回路の段数の位置を示すパラメータであり、

$N$  は 1 变調時間内に存在するシンボルの数であり、

$k$  は 0 (Hz) を基準としてサブキャリアの周波数オフセット

を持つ信号群が入力されていることを示すパラメータである、

30

上記信号成分分離装置で分離したシンボル列のうち、所定のサブキャリアのシンボル群を 1 系列または複数系列選択して出力する信号選択手段と、

上記信号選択手段で選択出力した 1 系列または複数系列のシンボル群について周波数オフセット補償する周波数オフセット補償手段と、

上記周波数オフセット補償手段のそれぞれの出力信号について直交変換を行う 2 つの直交変換手段と、

上記直交変換した信号を復号する復号手段と、

を具備する、

受信装置。

【請求項 8】

40

上記周波数オフセット補償手段は、

上記周波数オフセット補償のために複素正弦波信号を出力する周波数オフセット補償信号発生手段と、

上記信号群と、上記周波数オフセット補償信号発生手段から出力される複素正弦波信号とを乗算する乗算手段と、

該乗算手段における乗算結果のシンボルを周波数軸に沿って並べ替えるシンボル並べ替え手段と

を有する、

請求項 7 記載の受信装置。

【請求項 9】

50

複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる、送信装置と受信装置とを有する通信装置であって、

上記送信装置は、

複数チャネルの情報を独立に符号化する符号化手段と、

上記符号化した情報をそれぞれ所定の変調方式に基づいて変調して信号点配置を行う信号点配置手段と、

上記複数の信号点配置した信号を時間周期的に多重化する信号多重化手段と、

上記多重化した信号を逆直交変換する逆直交変換手段と、

上記直交変換した信号群を送出する送信手段と、

を有し、

10

上記受信装置は、

上記送信手段とは異なる送信手段から送出された信号群を受信する受信手段と、

上記受信した信号群を分離する信号成分分離装置であって、

入力信号群を  $N / 2^{(m+1)}$  シンボル遅延するシンボル遅延手段と、

入力信号群を、 $- (k / 2^m)$  ラジアン位相シフトする位相オフセット調整手段と、

上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と、

上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と、

からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されている信号成分分離装置と、

ただし、 $m$  は二分岐回路の段数の位置を示すパラメータであり、

$N$  は 1 変調時間内に存在するシンボルの数であり、

$k$  は 0 (Hz) を基準としてサブキャリアの周波数オフセット

を持つ信号群が入力されていることを示すパラメータである、

上記信号成分分離装置で分離したシンボル列のうち、所定のサブキャリアのシンボル群を 1 系列または複数系列選択して出力する信号選択手段と、

30

上記信号選択手段で選択出力した 1 系列または複数系列のシンボル群について周波数オフセット補償する周波数オフセット補償手段と、

上記周波数オフセット補償手段のそれぞれの出力信号について直交変換を行う 2 つの直交変換手段と、

上記直交変換した信号を復号する復号手段と、

を具備する、

通信装置。

#### 【請求項 10】

上記周波数オフセット補償手段は、

上記周波数オフセット補償のために複素正弦波信号を出力する周波数オフセット補償信号発生手段と、

40

上記信号群と、上記周波数オフセット補償信号発生手段から出力される複素正弦波信号とを乗算する乗算手段と、

該乗算手段における乗算結果のシンボルを周波数軸に沿って並べ替えるシンボル並べ替え手段と

を有する、

請求項 9 記載の通信装置。

#### 【請求項 11】

複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる受信装置であって、

50

信号群を受信する受信手段と、

信号成分分離装置であって、入力信号群を  $N / 2^{(m+1)}$  シンボル遅延するシンボル遅延手段と、入力信号群を、 $- (k / 2^m)$  ラジアン位相シフトする位相オフセット調整手段と、上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と、上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と、からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されている信号成分分離装置と、

ただし、 $m$  は二分岐回路の段数の位置を示すパラメータであり、

10

$N$  は 1 变調時間内に存在するシンボルの数であり、

$k$  は  $0$  (Hz) を基準としてサブキャリアの周波数オフセット

を持つ信号群が入力されていることを示すパラメータである、

上記信号成分分離手段で分離した 1 系列または複数系列のシンボル群について周波数オフセット補償する周波数オフセット補償手段と、

上記周波数オフセット補償手段のそれぞれの出力信号について直交変換を行う 2 つの直交変換手段と、

上記直交変換した信号を復号する復号手段と、

を具備する、

受信装置。

20

### 【請求項 1 2】

上記周波数オフセット補償手段は、

上記周波数オフセット補償のために複素正弦波信号を出力する周波数オフセット補償信号発生手段と、

上記信号群と、上記周波数オフセット補償信号発生手段から出力される複素正弦波信号とを乗算する乗算手段と、

該乗算手段における乗算結果のシンボルを周波数軸に沿って並べ替えるシンボル並べ替え手段と

を有する、

請求項 1 1 記載の受信装置。

30

### 【請求項 1 3】

複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる、送信装置と受信装置とを有する通信装置であって、

上記送信装置は、

複数チャネルの情報を独立に符号化する符号化手段と、

上記符号化した情報をそれぞれ所定の変調方式に基づいて変調して信号点配置を行う信号点配置手段と、

上記複数の信号点配置した信号を時間周期的に多重化する信号多重化手段と、

上記多重化した信号を逆直交変換する逆直交変換手段と、

上記直交変換した信号群を送出する送信手段と、

40

を有し、

上記受信装置は、

上記送信手段とは異なる送信手段から送出された信号群を受信する受信手段と、

上記受信した信号群を分離する信号成分分離装置であって、

入力信号群を  $N / 2^{(m+1)}$  シンボル遅延するシンボル遅延手段と、

入力信号群を、 $- (k / 2^m)$  ラジアン位相シフトする位相オフセット調整手段と、

上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と、

50

上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と、

からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されている信号成分分離装置と、

ただし、 $m$ は二分岐回路の段数の位置を示すパラメータであり、

$N$ は1変調時間内に存在するシンボルの数であり、

$k$ は0(Hz)を基準としてサブキャリアの周波数オフセット

を持つ信号群が入力されていることを示すパラメータである、

上記信号成分分離装置で分離した1系列または複数系列のシンボル群について周波数オフセット補償する周波数オフセット補償手段と、10

上記周波数オフセット補償手段のそれぞれの出力信号について直交変換を行う2つの直交変換手段と、

上記直交変換した信号を復号する復号手段と、

を具備する、

通信装置。

【請求項14】

マルチキャリア変調された信号群から特定の信号を抽出するフィルタ装置であって、

信号成分分離装置であって、入力信号群を $N/2^{(m+1)}$ シンボル遅延するシンボル遅延手段と、入力信号群を $- (k/2^m)$ ラジアン位相シフトする位相オフセット調整手段と、上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と、上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と、からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されている信号成分分離装置と、20

ただし、 $m$ は二分岐回路の段数の位置を示すパラメータであり、

$N$ は1変調時間内に存在するシンボルの数であり、

$k$ は0(Hz)を基準としてサブキャリアの周波数オフセット

を持つ信号群が入力されていることを示すパラメータである、30

上記信号成分分離装置で分離したシンボル列のうち、特定のサブキャリアのシンボル群を選択して出力する信号選択手段と、

上記信号選択手段で選択出力したシンボル群について周波数オフセット補償する周波数オフセット補償手段と、

を具備する、

フィルタ装置。

【請求項15】

複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる受信装置であって、

マルチキャリア変調された信号群を受信する受信手段と、40

上記受信手段で受信したマルチキャリア変調された信号群から特定の信号を抽出するフィルタ装置と、

該フィルタ装置で抽出した信号について直交変換を行う直交変換手段と、

上記直交変換した信号を復号する復号手段と

を具備し、

上記フィルタ装置は、

信号成分分離装置であって、入力信号群を $N/2^{(m+1)}$ シンボル遅延するシンボル遅延手段と、入力信号群を $- (k/2^m)$ ラジアン位相シフトする位相オフセット調整手段と、上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する一50

方のシンボル列を算出する加算手段と、上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して当該信号成分分離装置に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と、からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されている信号成分分離装置と、

ただし、 $m$ は二分岐回路の段数の位置を示すパラメータであり、

$N$ は1変調時間内に存在するシンボルの数であり、

$k$ は0(Hz)を基準としてサブキャリアの周波数オフセット

を持つ信号群が入力されていることを示すパラメータである、

上記信号成分分離装置で分離したシンボル列のうち、特定のサブキャリアのシンボル群を選択して出力する信号選択手段と、

上記信号選択手段で選択出力したシンボル群について周波数オフセット補償する周波数オフセット補償手段と、

を具備する、

受信装置。

【請求項16】

マルチキャリア変調された信号群から特定の信号を抽出するフィルタ装置であって、

サブキャリアを選択するサブキャリア選択手段と、

上記選択されたサブキャリアに応じて、入力された信号群から特定の信号群を選択して出力する、少なくとも1段の信号選択手段と、

上記信号選択手段で選択した信号について周波数オフセット補償する周波数オフセット補償手段と

を具備し、

上記信号選択手段は、

上記選択されたサブキャリアに応じて、入力された信号群を位相シフトする位相オフセット調整手段と、

入力された信号群を $N/2^{(m+1)}$ シンボル遅延するシンボル遅延手段と、

上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して当該フィルタ装置に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と

を有する、

ただし、 $m$ は二分岐回路の段数の位置を示すパラメータであり、

$N$ は1変調時間内に存在するシンボルの数であり、

$k$ は0(Hz)を基準としてサブキャリアの周波数オフセット

を持つ信号群が入力されていることを示すパラメータである、

フィルタ装置。

【請求項17】

複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる受信装置であって、

マルチキャリア変調された信号群を受信する受信手段と、

上記受信手段で受信したマルチキャリア変調された信号群から特定の信号を抽出するフィルタ装置と、

該フィルタ装置で抽出した信号について直交変換を行う直交変換手段と、

上記直交変換した信号を復号する復号手段と

を具備し、

上記フィルタ装置は、

サブキャリアを選択するサブキャリア選択手段と、

上記選択されたサブキャリアに応じて、入力された信号群から特定の信号群を選択して出力する、少なくとも1段の信号選択手段と、

上記信号選択手段で選択した信号について周波数オフセット補償する周波数オフセット補償手段と

10

20

30

40

50

を具備し、

上記信号選択手段は、

上記選択されたサブキャリアに応じて、入力された信号群を位相シフトする位相オフセット調整手段と、

入力された信号群を  $N / 2^{(m+1)}$  シンボル遅延するシンボル遅延手段と、

上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して上記信号選択出力手段に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と

を有する、

ただし、mは二分岐回路の段数の位置を示すパラメータであり、

10

Nは1変調時間内に存在するシンボルの数であり、

kは0(Hz)を基準としてサブキャリアの周波数オフセット

を持つ信号群が入力されていることを示すパラメータである、

受信装置。

【請求項18】

マルチキャリア変調された信号群から特定の信号を抽出するフィルタ装置であって、

選択すべきチャネルに応じた複素正弦波信号を出力する通過サブキャリア選択信号出力手段と、

上記通過サブキャリア選択出力手段から出力された複素正弦波信号と、入力信号群との乗算を行う乗算手段と、

20

上記乗算手段における乗算結果のうち、特定の信号群を選択する少なくとも1段の信号成分分離手段と、

上記信号成分分離装置の出力を周波数軸上に並べ替えるシンボル並べ替え手段と

を具備し、

上記信号成分分離手段は、

入力信号群を  $N / 2^{(m+1)}$  シンボル遅延するシンボル遅延手段と、

上記シンボル遅延手段の出力信号と上記入力信号群とを加算して周波数軸上交互に位置する一方のシンボル列を算出する加算手段と

からなる回路が二分岐方式で段階的かつ階層的に接続されている、

ただし、mは二分岐回路の段数の位置を示すパラメータであり、

30

Nは1変調時間内に存在するシンボルの数であり、

kは0(Hz)を基準としてサブキャリアの周波数オフセット

を持つ信号群が入力されていることを示すパラメータである、

フィルタ装置。

【請求項19】

複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる受信装置であって、

マルチキャリア変調された信号群を受信する受信手段と、

上記受信手段で受信したマルチキャリア変調された信号群から特定の信号を抽出するフィルタ装置と、

40

該フィルタ装置で抽出した信号について直交変換を行う直交変換手段と、

上記直交変換した信号を復号する復号手段と

を具備し、

上記フィルタ装置は、

選択すべきチャネルに応じた複素正弦波信号を出力する通過サブキャリア選択信号出力手段と、

上記通過サブキャリア選択出力手段から出力された複素正弦波信号と、入力信号群との乗算を行う乗算手段と、

上記乗算手段における乗算結果のうち、特定の信号群を選択する少なくとも1段の信号成分分離手段と、

50

上記信号成分分離装置の出力を周波数軸上に並べ替えるシンボル並べ替え手段とを有し、

上記信号成分分離手段は、

入力信号群を  $N / 2^{(m+1)}$  シンボル遅延するシンボル遅延手段と、

上記シンボル遅延手段の出力信号と上記入力信号群とを加算して周波数軸上交互に位置する一方のシンボル列を算出する加算手段と

からなる回路が二分岐方式で段階的かつ階層的に接続されている、

ただし、mは二分岐回路の段数の位置を示すパラメータであり、

Nは1変調時間内に存在するシンボルの数であり、

kは0(Hz)を基準としてサブキャリアの周波数オフセット

を持つ信号群が入力されていることを示すパラメータである、

受信装置。

**【請求項20】**

複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる受信装置であって、

マルチキャリア変調された信号群を受信する受信手段と、

入力信号群をスイッチングするスイッチング手段と、

上記受信手段で受信したマルチキャリア変調された信号群を保持するバッファ手段と、

上記スイッチング手段の後段に接続され、入力された信号群のうち特定の信号群を選択出力するフィルタ装置と、

上記フィルタ装置で抽出した信号について直交変換を行う直交変換手段と、

上記直交変換した信号を復号する復号手段と

を具備し、

上記スイッチング手段は1シンボル分の信号群を上記フィルタ装置に出力し、上記バッファ手段はその間、入力された1シンボル分の信号群を保持し、上記フィルタ装置への信号送出終了後、上記バッファ手段に保持した信号群を上記スイッチング手段を介して上記フィルタ装置に送出し、

上記フィルタ装置は、上記スイッチング手段を介して入力された信号群のうち指定されたサブキャリアのみ選択出力し、

上記フィルタ装置は、

入力信号群を  $N / 2^{(m+1)}$  シンボル遅延するシンボル遅延手段と、入力信号群を、 $-(k / 2^m)$  ラジアン位相シフトする位相オフセット調整手段と、上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して当該フィルタ装置に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と、上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して当該フィルタ装置に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と、からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されている信号成分分離装置と、

ただし、mは二分岐回路の段数の位置を示すパラメータであり、

Nは1変調時間内に存在するシンボルの数であり、

kは0(Hz)を基準としてサブキャリアの周波数オフセット

を持つ信号群が入力されていることを示すパラメータである、

上記信号成分分離装置で分離したシンボル列のうち、特定のサブキャリアのシンボル群を選択して出力する信号選択手段と、

上記信号選択手段で選択出力したシンボル群について周波数オフセット補償する周波数オフセット補償手段と、

を具備する、

受信装置。

**【請求項21】**

複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重

10

20

30

40

50

通信に用いる受信装置であって、

マルチキャリア変調された信号群を受信する受信手段と、

上記受信手段で受信したマルチキャリア変調された信号群のうち偶数キャリアの信号群を選択して出力する第1のフィルタ装置と、

上記受信手段で受信したマルチキャリア変調された信号群のうち奇数キャリアの信号群を選択して出力する第2のフィルタ装置と、

上記第2のフィルタ装置の出力信号群を保持するバッファ手段と、

上記第1のフィルタ装置の出力信号群をスイッチングするスイッチング手段と、

上記スイッチング手段の後段に接続され、スイッチングされた出力信号について直交変換を行う直交変換手段と、

上記直交変換した信号を復号する復号手段と

を具備し、

上記スイッチング手段は上記第1のフィルタ装置の出力信号を上記直交変換手段に送出し、上記直交変換手段への信号送出終了後、上記バッファ手段に保持した信号群を上記スイッチング手段を介して上記直交変換手段に送出し、

上記第1および第2のフィルタ装置はそれぞれ、

入力信号群を  $N / 2^{(m+1)}$  シンボル遅延するシンボル遅延手段と、入力信号群を  $- (k / 2^m)$  ラジアン位相シフトする位相オフセット調整手段と、上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して当該フィルタ装置に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と、上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して当該フィルタ装置に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と、からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されている信号成分分離装置と、

ただし、mは二分岐回路の段数の位置を示すパラメータであり、

Nは1変調時間内に存在するシンボルの数であり、

kは0(Hz)を基準としてサブキャリアの周波数オフセット

を持つ信号群が入力されていることを示すパラメータである、

上記信号成分分離装置で分離したシンボル列のうち、特定のサブキャリアのシンボル群を選択して出力する信号選択手段と、

上記信号選択手段で選択出力したシンボル群について周波数オフセット補償する周波数オフセット補償手段と

を具備する、

受信装置。

## 【請求項22】

送信手段において、複数チャネルの情報を独立に符号化し、上記符号化した情報をそれぞれ所定の変調方式に基づいて変調して信号点配置を行い、上記複数の信号点配置した信号を時間周期的に多重化し、上記多重化した信号を逆直交変換し、当該送信手段が上記直交変換した情報を送出する符号化送信工程と、

受信手段において、上記送信手段とは異なる送信手段から送出された信号を受信し、上記受信した直交変換処理後の多重化信号のうち、希望するチャネルの信号のみ選択出力し、上記選択出力された信号を直交変換し、上記直交変換した情報を復号する受信復号工程と

を有する通信方法であって、

上記受信工程における信号選択処理は、

入力信号群を  $N / 2^{(m+1)}$  シンボル遅延し、

入力信号群を0Hzを基準として、 $- (k / 2^m)$  ラジアンだけ位相シフトし、

上記シンボル遅延した信号と上記位相シフトした信号を加算して上記受信手段に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出するか、上記シンボル遅延した信号から上記位相シフトした信号を減算して上記受信手段に入力さ

10

20

30

40

50

れた多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する、

方法を二分岐的かつ段階的に行う、

ただし、 $m$ は二分岐処理の段の位置を示すパラメータであり、

$N$ は1変調時間内に存在するシンボルの数であり、

$k$ は0(Hz)を基準としてサブキャリアの周波数オフセット

を持つ信号群が入力されていることを示すパラメータである、

通信方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

10

本発明は通信装置(通信システム)、送信機および受信機、並びに、通信方法に関するものであり、特に、マルチキャリア変調を行うデジタル通信装置(システム)、デジタル通信装置(システム)に用いる無線送信機(無線送信装置)無線受信機(無線受信装置)、並びに、その通信方法に関する。

より特定的には、本発明は直交周波数分割多重化(OFDM:Orthogonal Frequency Division Multiplexing)方式で多重化されたマルチキャリア信号をシンボル系列に分離する信号成分分離装置、マルチキャリア信号から特定のシンボルを抽出するフィルタ装置、および、これら信号成分分離装置、フィルタ装置などを有する信号受信装置に関する。

##### 【0002】

##### 【従来の技術】

20

OFDM方式による変調信号の例としてDAB(Digital Audio Broadcasting、デジタル・オーディオ放送)システムを例示する。

EUREKA147プロジェクトが開発した移動受信可能な高品質デジタル音声地上放送方式としてDABシステムが知られている。DABシステムを衛星放送に適用したデジタル衛星音声放送も実用化が進められている。

##### 【0003】

そのようなデジタル通信システム(装置)に使用される変調方式としては、マルチパスフェージング、ゴーストなどに強いという特徴を有するOFDM方式が提案されている。OFDM方式は通常、直交する数十~数百の搬送波を使用するマルチキャリア変調方式であり、各搬送波をQAM、PSKなどの変調方式で変調する。

30

DABシステムなどにおいては、マルチキャリア通信を適用して多重チャネルのデジタル音声信号を伝送する。

##### 【0004】

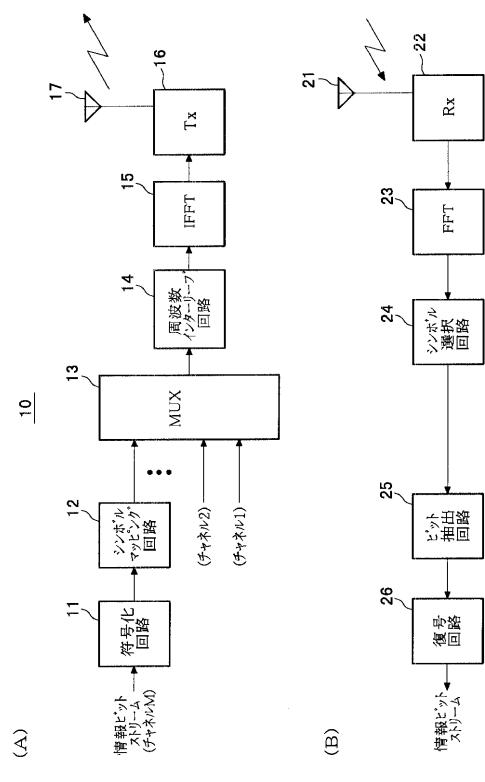

図21(A)、(B)はマルチキャリア変調方式として、DABシステムなどに適用されるOFDM方式を用いたデジタル無線通信システムの一構成例を示す図である。図21(A)、(B)はDABシステムの一部を簡略化して図解している。

以下の説明では、DABシステムを例示して、多重化に関する部分を中心に説明を行う。

##### 【0005】

図21(A)に図解したOFDM方式の無線通信システムの無線送信装置10は、符号化回路11と、シンボルマッピング回路12と、マルチブレクサ(信号多重化処理回路)13と、周波数インターリーブ回路14と、逆高速フーリエ変換(IFFT:Inverse Fast Fourier Transform)回路15と、無線送信回路16と、アンテナ17とを有する。

40

##### 【0006】

情報ビットストリームは、符号化回路11において符号化ならびにインターリーブなどの処理がなされた後に、シンボルマッピング回路12において各ビットが送信シンボルにマッピングされる。この作業はチャネル毎に各々別個に行われ、図21(A)に示した例においては、たとえば、チャネルあたり毎秒64kps(シンボル/秒)のシンボルが生成されている。

##### 【0007】

これらのシンボルストリームは、マルチブレクサ13において単純に直列に連結されるこ

50

とにより多重化されたシンボルストリームとなる。たとえば、64 k s p s のチャネルを18チャネル分多重すると、多重されたシンボルストリームの伝送レートは1152 k s p s (= 18 × 64 k s p s) となる。

この多重されたシンボルストリームは周波数インターリーブ回路14における周波数インターリーブ処理によりシンボルの並び替えが行われる。この作業により各チャネルのシンボルはばらばらに並ぶことになる。

【0008】

その後、シンボルストリームは逆高速フーリエ変換(IFT)回路15におけるIFT処理によりばらばらに並ぶシンボルが周波数軸上にならべられ、これらの周波数軸上で10のシンボル表現が時間軸上のシンボルに変換されて送信回路16からアンテナ17を介して空中に送出される。

【0009】

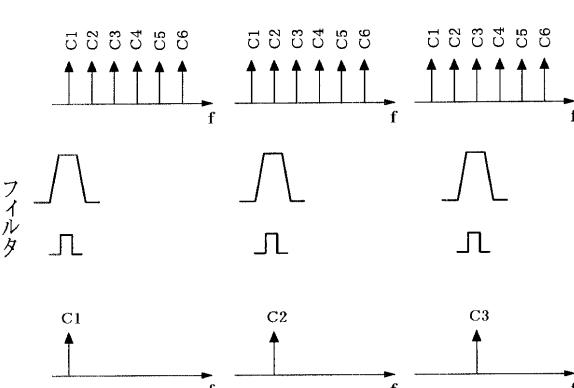

送信装置10から出力される6キャリアにマルチキャリア化されたシンボル列の例を図22に図解する。

【0010】

これまで、上述したマルチキャリア化された複数のシンボル(シンボル系列)の特定のシンボルのみを抽出することは行われていなかった。

そこで、無線信号受信機において、図22に例示したシンボル系列から所望のシンボルまたはキャリア成分を抽出する方法を既存の技術を用いて行う場合を想定する。

【0011】

図23はマルチキャリア信号を分離する第1の方法を示す図である。

この方法は、それぞれ対応するキャリアの周波数帯域特性を有する帯域フィルタを複数設けて、それぞれの帯域通過フィルタで対応するシンボルを抽出する。そのようなフィルタとしては、たとえば、くし型フィルタを用いることができる。

【0012】

しかしながら、このような方法は、OFDMのようにキャリアの間隔が詰まっている変調方式のシンボルの分離には向きである。すなわち、OFDM方式による変調方式ではある周波数帯域に多数のキャリアが詰まっているので、隣接する信号成分のアイソレーションが十分にとれないので、隣接する周波数のキャリア信号を識別するには各帯域通過フィルタは急峻な周波数特性を持たねばならない。

【0013】

たとえば、くし型フィルタでそのような急峻な周波数特性を持つ精度の高いフィルタを各種準備することは困難であるし、価格などの面で相当高価格になるので、実現することが困難である。

【0014】

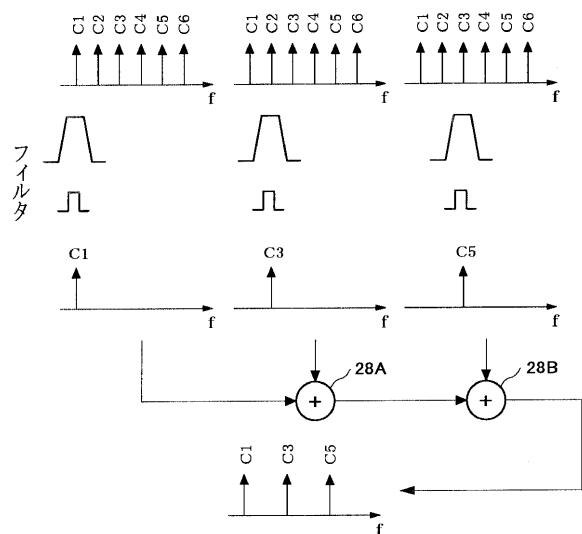

図24はマルチキャリア信号を分離する第2の方法を示す図である。

図24において、受信回路22で受信した信号を高速フーリエ変換(FFT)回路23で高速フーリエ変換を行い周波数軸上に並んだ受信シンボル系列を生成し、デマルチプレクサ(信号分離装置)29においてシンボル系列をばらばらのシンボルに分離して、特定のシンボルのみ選択可能にする。

しかしながら、この方法は、特定のシンボルを抽出する場合でも、全てのシンボルについて高速フーリエ変換を行うから、複雑なFFT回路23を設けなければならず、装置構成が複雑になる。

【0015】

図25は一定間隔のキャリア信号成分のみ抽出する場合の概略構成図である。図25において、複数の異なる通過帯域特性を有する複数の帯域通過フィルタを設けて、フィルタにより帯域制限した信号同士を加算回路28A、28Bで加算して所望の信号を得る。この場合も、帯域フィルタとして、たとえば、くし型フィルタを用いる。

しかしながら、この方法も、図23の方法と同様、マルチキャリア方式なのでキャリアが詰まっていて信号成分のアイソレーションが十分にとれない、および、急峻な周波数特性

10

20

30

40

50

を持つ精度の高いフィルタを準備することが価格などの面で困難になるという問題に遭遇する。

【0016】

図21(B)は、図21(A)に図解したDABシステムにおける無線信号受信機の概略構成図である。

図21(B)のOFDM方式の無線通信システム1の無線受信装置20は、アンテナ21と、受信回路22と、高速フーリエ変換(FFT)回路23と、シンボル選択回路24と、ビット抽出回路25と、復号回路26とを有する。

【0017】

受信回路22でアンテナ21で受信した所望の周波数帯域の信号を周波数変換してベースバンド信号成分のみを抽出することにより、ベースバンド信号を得る。このようにして得られたベースバンド信号は、情報が周波数軸上に並んでいる信号の時間軸上での表現となっているので、FFT回路23においてFFT処理して周波数軸上に並んでいるサブキャリアを抽出する。

このとき、FFT処理によって出力されるシンボルは受信した信号帯域全体のサブキャリア群となる(たとえば、本例においては1152ksp/s分の情報が含まれている)。

【0018】

シンボル選択回路24は、サブキャリア群の中から、図21(A)に図解した送信側で行われた周波数インターリーブにより配置された所望のチャネルのシンボルの存在位置からシンボルを抽出する。これにより所望のチャネルの情報である64kbp/sが抽出されることになる。

【0019】

ビット抽出回路25においてこのようにして得られた所望のチャネルのシンボルストリームから受信ビットストリームを抽出して符号化ビットストリームを得た後、復号回路26においてこれをデコードすることにより、所望のチャネルの情報ビットストリームを得ている。

【0020】

【発明が解決しようとする課題】

このように、OFDMのシステムにおいては、サブキャリア毎に異なるチャネルのシンボルを割り当てることにより多重化が行われているが、無線受信装置20は、送信されてきた全チャネル分の多重化信号を全て受信し、さらにはFFT回路23により全チャネル分のシンボルを抽出した後にシンボル選択回路24においてチャネルの選定を行っており、本来必要であった1チャネル分の情報に必要とされる演算量を上回る演算がFFT回路23においてFFT処理が行われることになる。

すなわち、無線受信装置20が欲していないチャネルの分をも含めてFFT回路23においてFFT信号処理を行っていることになり、FFT回路23の回路規模が大きくなるという問題がある。

【0021】

上述した問題を解決する方法として、本願の発明者は、たとえば、平成11年5月20日に出願した、特願平11-140442号に記載された発明を提案している。特願平11-140442号に記載された発明はシンボル系列から交互のサブキャリアごとシンボル列を分離する回路を二分岐方式で多段に階層的に設けている。

【0022】

本発明は、特願平11-140442号に記載された発明とは異なる方法で上記問題を解決するとともに、さらに、1シンボルのみを効率よく抽出することを目的とする。

【0023】

本発明の目的は、シンボル系列を効率よく二分岐的に分離可能な信号成分分離装置を提供することにある。

【0024】

本発明の他の目的は、シンボル系列から特定のシンボルを効率よく抽出可能なフィルタ装

10

20

30

40

50

置を提供することにある。

【0025】

本発明のさらに他の目的は、上記信号成分分離装置および／またはフィルタ回路を有する受信装置を提供することにある。

【0026】

本発明のさらに他の目的は、上記受信装置と送信装置とを有する通信システムを提供することにある。

【0027】

本発明の他の目的は、上記受信処理と上記送信処理を行う通信方法を提供することある。

10

【0028】

【課題を解決するための手段】

本発明の第1の観点によれば、マルチキャリア変調された信号群（シンボル群）からある信号群を分離する信号成分分離装置であって、

入力信号群を  $N / 2^{(m+1)}$  シンボル遅延するシンボル遅延手段と、

入力信号群を  $0 \text{ Hz}$  を基準として  $- (k / 2^m)$  ラジアン位相シフトする位相オフセット調整手段と、

上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して上記信号選択出力手段に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と、

20

上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して上記信号選択出力手段に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と

からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されている、信号成分分離装置が提供される。

ただし、 $m$  は二分岐回路の段数の位置を示すパラメータであり、

$N$  は 1 变調時間内に存在するシンボルの数であり、

$k$  は  $0 \text{ (Hz)}$  を基準としてサブキャリアの周波数オフセットを持つ信号群が入力されていることを示すパラメータである。

【0029】

30

本発明の第2の観点によれば、上記信号成分分離装置を適用した、複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる受信装置が提供される。

当該受信装置は、

信号群を受信する受信手段と、

入力した信号群を  $N / 2^{(m+1)}$  シンボル遅延するシンボル遅延手段と、入力した信号群を  $- (k / 2^m)$  ラジアン位相シフトする位相オフセット調整手段と、上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して上記信号選択出力手段に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と、上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して上記信号選択出力手段に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と、からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されている、信号成分分離装置と、

40

上記信号成分分離装置で分離した信号群について直交変換を行う直交変換手段と、

上記直交変換した情報を復号する復号手段と

を具備する。

【0030】

本発明の第3の観点によれば、上記受信装置を適用した、複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる、送信装置と受信装置とを有する、通信装置が提供される。

50

当該通信装置の上記送信装置は、複数チャネルの情報を独立に符号化する符号化手段と、上記符号化した情報をそれぞれ所定の変調方式に基づいて変調して信号点配置を行う信号点配置手段と、上記複数の信号点配置した信号を時間周期的に多重化する信号多重化手段と、上記多重化した信号を逆直交変換する逆直交変換手段と、上記直交変換した情報を送出する送信手段と、を有する。

当該通信装置の上記受信装置は、上述した受信装置の構成要素、すなわち、上記送出された信号群を受信する受信手段と、上記受信した信号群を選択分離する信号成分分離手段と、上記選択分離された信号を直交変換する直交変換手段と、上記直交変換した情報を復号する復号手段とを有する。

上記信号成分分離手段は、上述した構成を有する。

10

【0031】

好ましくは、上記送信装置における上記信号多重化手段は、上記複数の信号点配置した信号を所定のサブキャリアでチャネルごと周波数をずらして多重化する。

【0032】

また好ましくは、上記送信装置における上記信号点配置手段における変調方式は直交周波数多重化方式（O F D M方式）を用いる変調方式である。

【0033】

また好ましくは、上記送信装置における上記逆直交変換処理手段は逆フーリエ変換処理を行い、上記受信機における上記直交変換処理手段はフーリエ変換処理を行う。

【0034】

本発明の第4の観点によれば、複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる受信装置であって、

信号群を受信する受信手段と、

入力信号群を $N / 2^{(m+1)}$ 遅延するシンボル遅延手段と、入力信号群を $- (k / 2^m)$ ラジアン位相シフトする位相オフセット調整手段と、上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して上記信号選択出力手段に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と、上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して上記信号選択出力手段に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と、からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されている信号成分分離装置と、

上記信号成分分離装置で分離したシンボル列のうち、所定のサブキャリアのシンボル群を1系列または複数系列選択して出力する信号選択手段と、

上記信号選択手段で選択出力した1系列または複数系列のシンボル群について周波数オフセット補償する周波数オフセット補償手段と、

上記周波数オフセット補償手段のそれぞれの出力信号について直交変換を行う2つの直交変換手段と、

上記直交変換した信号を復号する復号手段と

を具備する受信装置が提供される。

【0035】

好ましくは、上記周波数オフセット補償手段は、上記周波数オフセット補償のために複素正弦波信号を出力する周波数オフセット補償信号発生手段と、上記信号群と、上記周波数オフセット補償信号発生手段から出力される複素正弦波信号とを乗算する乗算手段と、該乗算手段における乗算結果のシンボルを周波数軸に沿って並べ替えるシンボル並べ替え手段とを有する。

【0036】

本発明の第5の観点によれば、第4の観点の受信装置を用いた、複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる、送信装置と受信装置とを有する通信装置が提供される。

【0037】

20

30

40

50

本発明の第 6 の観点によれば、複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる受信装置であって、

信号群を受信する受信手段と、

入力信号群を  $N / 2^{(m+1)}$  遅延するシンボル遅延手段と、入力信号群を  $- (k / 2^m)$  ラジアン位相シフトする位相オフセット調整手段と、上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して上記信号選択出力手段に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と、上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して上記信号選択出力手段に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と、からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されている信号成分分離装置と、

上記信号成分分離手段で分離した 1 系列または複数系列のシンボル群について周波数オフセット補償する周波数オフセット補償手段と、

上記周波数オフセット補償手段のそれぞれの出力信号について直交変換を行う 2 つの直交変換手段と、

上記直交変換した信号を復号する復号手段と

を具備する受信装置が提供される。

【 0 0 3 8 】

本発明の第 7 の観点によれば、上記受信装置を適用した、複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる、送信装置と受信装置とを有する通信装置が提供される。

【 0 0 3 9 】

本発明の第 8 の観点によれば、マルチキャリア変調された信号群から特定の信号を抽出するフィルタ装置であって、

入力信号群を  $N / 2^{(m+1)}$  遅延するシンボル遅延手段と、入力信号群を  $- (k / 2^m)$  ラジアン位相シフトする位相オフセット調整手段と、上記シンボル遅延手段の出力信号と上記位相オフセット調整手段の出力信号を加算して上記信号選択出力手段に入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出する加算手段と、上記シンボル遅延手段の出力信号から上記位相オフセット調整手段の出力信号を減算して上記信号選択出力手段に入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する減算手段と、からなる二分岐回路が二分岐方式で段階的かつ階層的に接続されている信号成分分離装置と、

上記信号成分分離装置で分離したシンボル列のうち、特定のサブキャリアのシンボル群を選択して出力する信号選択手段と、

上記信号選択手段で選択出力したシンボル群について周波数オフセット補償する周波数オフセット補償手段と

を具備するフィルタ装置が提供される。

【 0 0 4 0 】

本発明の第 9 の観点によれば、上記フィルタ装置を適用した、複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる受信装置であって、

マルチキャリア変調された信号群を受信する受信手段と、

上記受信手段で受信したマルチキャリア変調された信号群から特定の信号を抽出するフィルタ装置と、

該フィルタ装置で抽出した信号について直交変換を行う直交変換手段と、

上記直交変換した信号を復号する復号手段と

を具備する受信装置が提供される。

【 0 0 4 1 】

本発明の第 10 の観点によれば、マルチキャリア変調された信号群から特定の信号を抽出するフィルタ装置であって、

10

20

30

40

50

サブキャリアを選択するサブキャリア選択手段と、

上記選択されたサブキャリアに応じて、入力された信号群から特定の信号群を選択して出力する、少なくとも1段の信号選択手段と、

上記信号選択手段で選択した信号について周波数オフセット補償する周波数オフセット補償手段と

を具備する、フィルタ装置が提供される。

【0042】

本発明の第11の観点によれば、上記フィルタ装置を適用した、複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる受信装置であって、

10

マルチキャリア変調された信号群を受信する受信手段と、

上記受信手段で受信したマルチキャリア変調された信号群から特定の信号を抽出するフィルタ装置と、

該フィルタ装置で抽出した信号について直交変換を行う直交変換手段と、

上記直交変換した信号を復号する復号手段と

を具備する受信装置が提供される。

【0043】

本発明の第12の観点によれば、マルチキャリア変調された信号群から特定の信号を抽出するフィルタ装置であって、

20

選択すべきチャネルに応じた複素正弦波信号を出力する通過サブキャリア選択信号出力手段と、

上記通過サブキャリア選択出力手段から出力された複素正弦波信号と、入力信号群との乗算を行う乗算手段と、

上記乗算手段における乗算結果のうち、特定の信号群を選択する少なくとも1段の信号成分分離手段と、

上記信号成分分離装置の出力を周波数軸上に並べ替えるシンボル並べ替え手段と

を具備するフィルタ装置が提供される。

【0044】

本発明の第13の観点によれば、上記フィルタ装置を適用した、複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる受信装置であって、

30

マルチキャリア変調された信号群を受信する受信手段と、

上記受信手段で受信したマルチキャリア変調された信号群から特定の信号を抽出するフィルタ装置と、

該フィルタ装置で抽出した信号について直交変換を行う直交変換手段と、

上記直交変換した信号を復号する復号手段と

を具備する受信装置が提供される。

【0045】

本発明の第14の観点によれば、複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる受信装置であって、

40

マルチキャリア変調された信号群を受信する受信手段と、

入力信号群をスイッチングするスイッチング手段と、

上記受信手段で受信したマルチキャリア変調された信号群を保持するバッファ手段と、

上記スイッチング手段の後段に接続され、入力された信号群のうち特定の信号群を選択出力するフィルタ装置と、

上記フィルタ装置で抽出した信号について直交変換を行う直交変換手段と、

上記直交変換した信号を復号する復号手段と

を具備し、

上記スイッチング手段は1シンボル分の信号群を上記フィルタ装置に出力し、上記バッファ手段はその間、入力された1シンボル分の信号群を保持し、上記フィルタ装置への信号

50

送出終了後、上記バッファ手段に保持した信号群を上記スイッチング手段を介して上記フィルタ装置に送出し、

上記フィルタ装置は、上記スイッチング手段を介して入力された信号群のうち指定されたサブキャリアのみ選択出力する、

受信装置が提供される。

## 【0046】

上記フィルタ装置は、上述した各種のフィルタ装置を適用できる。

## 【0047】

本発明の第15の観点によれば、複数チャネルのサブキャリアが周期的に配置されているマルチキャリア変調による多重通信に用いる受信装置であって、

10

マルチキャリア変調された信号群を受信する受信手段と、

上記受信手段で受信したマルチキャリア変調された信号群のうち偶数キャリアの信号群を選択して出力する第1のフィルタ装置と、

上記受信手段で受信したマルチキャリア変調された信号群のうち奇数キャリアの信号群を選択して出力する第2のフィルタ装置と、

上記第2のフィルタ装置の出力信号群を保持するバッファ手段と、

上記第1のフィルタ装置の出力信号群をスイッチングするスイッチング手段と、

上記スイッチング手段の後段に接続され、スイッチングされた出力信号について直交変換を行う直交変換手段と、

上記直交変換した信号を復号する復号手段と

20

を具備し、

上記スイッチング手段は上記第1のフィルタ装置の出力信号を上記直交変換手段に送出し、上記直交変換手段への信号送出終了後、上記バッファ手段に保持した信号群を上記スイッチング手段を介して上記直交変換手段に送出する、

受信装置が提供される。

## 【0049】

本発明の第16の観点によれば、通信方法であって、

複数チャネルの情報を独立に符号化し、

上記符号化した情報をそれぞれ所定の変調方式に基づいて変調して信号点配置を行い、

30

上記複数の信号点配置した信号を時間周期的に多重化し、

上記多重化した信号を逆直交変換し、

上記直交変換した情報を送出する

符号化送信工程と、

上記送出された信号を受信し、

上記受信した直交変換処理後の多重化信号のうち、希望するチャネルの信号のみ選択出力し、

上記選択出力された信号を直交変換し、

上記直交変換した情報を復号する

受信復号工程と

を有する通信方法であって、

40

上記受信工程における信号選択処理は、

$N / 2^{(m+1)}$  シンボル遅延し、

$(k / 2^m)$  ラジアンだけ位相シフトし、

上記シンボル遅延した信号と上記位相シフトした信号を加算して上記入力された多重化信号のうち周波数軸上交互に位置する一方のシンボル列を算出するか、上記シンボル遅延した信号から上記位相シフトした信号を減算して上記入力された多重化信号のうち周波数軸上交互に位置する他方のシンボル列を算出する

方法を二分岐的かつ段階的に行う

通信方法が提供される。

## 【0050】

50

**【発明の実施の形態】**

本発明の通信装置（通信システム）、送信装置（送信機）および受信装置（受信機）、並びに、通信方法について、添付図面を参照して好適実施の形態を述べる。

**【0051】**

下記の実施の形態においては、通信システムとして無線通信システムについて例示するが、本発明は無線通信システムに限定されず、有線通信システムにも適用できる。しかしながら下記の実施の形態においては、無線通信システム、たとえば、DABシステムに類似する直交周波数分割多重化（OFDM）方式を用いて通信システムについて例示する。

**【0052】**

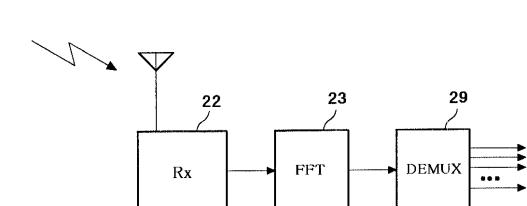

**通信装置の第1実施の形態**

10

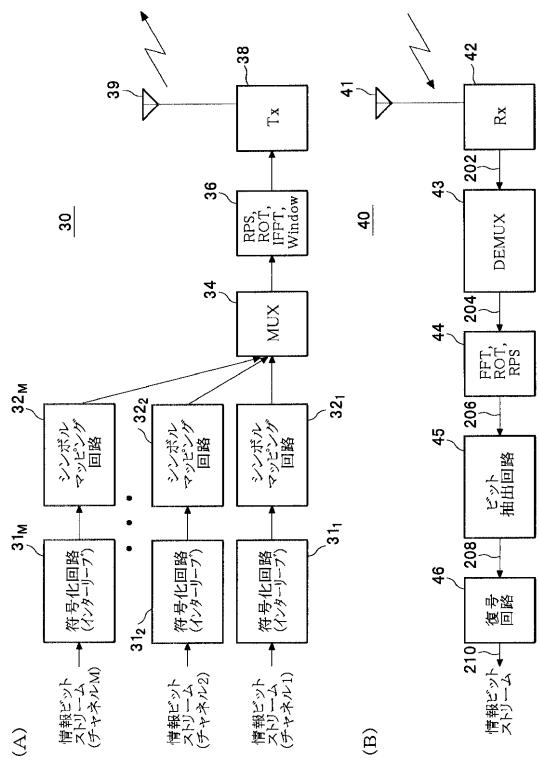

図1（A）、（B）、図2（A）、（B）、（C）、および、図3を参照して本発明の通信システム、送信装置、受信装置、並びに、通信方法の第1実施の形態を述べる。

**【0053】**

図1（A）、（B）は本発明の通信システム、送信装置および受信装置、並びに、通信方法の1実施の形態としてのマルチキャリア変調方式としてOFDM方式を用いたデジタル無線通信システムの構成図であり、図1（A）はOFDM方式の無線通信システムの送信装置30の構成図であり、図1（B）はOFDM方式の無線通信システムの受信装置40の構成図である。

**【0054】**

送信装置30と受信装置40とで、OFDM方式の無線通信システムを構成している。

20

**【0055】**

**送信装置（送信機）30**

送信装置（送信機）30について述べる。

図1（A）に図解したOFDM方式の無線通信システムの送信装置30は、第1チャネル用符号化回路31<sub>1</sub>、および第1チャネル用シンボルマッピング回路32<sub>1</sub>、第2チャネル用符号化回路31<sub>2</sub>、および第2チャネル用シンボルマッピング回路32<sub>2</sub>、～、第Mチャネル用符号化回路31<sub>M</sub>、および第Mチャネル用シンボルマッピング回路32<sub>M</sub>を有する。この例は、Mチャネルの情報ビットストリームを符号化する例を示す。

送信装置30はさらに、マルチプレクサ（信号多重化処理回路）34と、スクランブル処理・IFFT・ガードタイム付加・窓かけ処理回路36と、送信回路38と、アンテナ39とを有する。

30

**【0056】**

送信装置30は、このように、複数の符号化回路31<sub>1</sub>～31<sub>M</sub>と複数のシンボルマッピング回路32<sub>1</sub>～32<sub>M</sub>に対して、1系統のマルチプレクサ34、スクランブル処理・IFFT・ガードタイム付加・窓かけ処理回路36、送信回路38を有している。符号化回路31およびシンボルマッピング回路32はチャネル数だけ設けられる。

**【0057】**

チャネル1～チャネルMのそれぞれ独立した情報ビットストリームについて、符号化回路31<sub>1</sub>～31<sub>M</sub>においてそれぞれ独立して符号化、インターリーブ等の処理が行われる。

40

**【0058】**

符号化回路31<sub>1</sub>～31<sub>M</sub>における符号化処理の具体例を述べる。OFDM方式の無線通信システムがたとえばDABシステムのようなオーディオ信号の伝送に適用される場合、情報ビットストリームのビット信号はオーディオ信号であるから、符号化回路31<sub>1</sub>～31<sub>M</sub>はそれぞれオーディオ信号について符号化処理を行う。符号化回路31<sub>1</sub>～31<sub>M</sub>は必要に応じて、さらにインターリーブ処理を行なう。

**【0059】**

符号化回路31<sub>1</sub>～31<sub>M</sub>において生成された各チャネルの符号化ビット信号はシンボルマッピング回路32<sub>1</sub>～32<sub>M</sub>において、送信シンボルにマッピングされ、シンボルストリームが生成される。

**【0060】**

50

シンボルマッピング回路 32<sub>1</sub> ~ 32<sub>M</sub>においては、O F D M 方式に適用する各種の変調方式を適用することができる。そのような変調方式としては、多値 Q A M、P S K など各種の変調方式が適用できる。

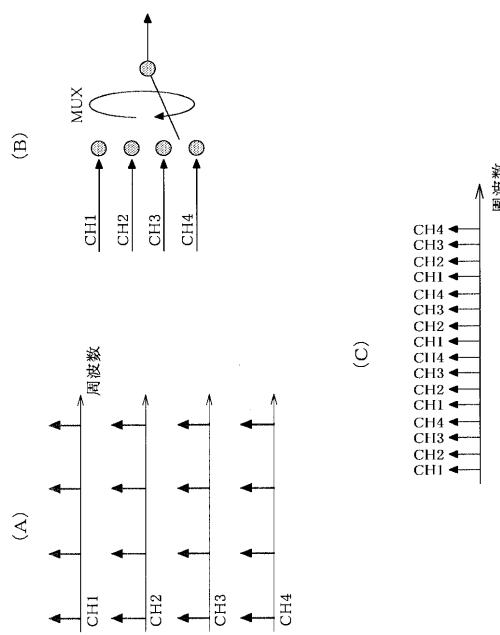

このようにシンボルマッピング回路 32<sub>1</sub> ~ 32<sub>M</sub>において、図 2 ( A ) に図解したように、各チャネルで各自独立したシンボルストリームが生成される。

#### 【 0 0 6 1 】

複数チャネルごとのシンボルストリームはマルチプレクサ 34において多重化され、多重シンボルストリームとして生成される。マルチプレクサ 34 は、図 2 ( B ) に図解したスイッチ回路を有しており、マルチプレクサ 34 の多重化処理によって、図 2 ( A ) に図解した複数チャネルのシンボルが図 2 ( C ) に図解したように周波数軸上に複数のチャネルのシンボルが並んだ多重化シンボルストリームとなる。

10

#### 【 0 0 6 2 】

マルチプレクサ 34において多重化された多重化シンボルストリームは、スクランブル処理・I F F T・ガードタイム付加・窓かけ処理回路 36において、ランダム位相シフト処理 ( R P S : Random Phase Shift ) 、ランダム直交変換処理 ( R O T : Random Orthogonal Transform ) 等などによりスクランブルされる。

20

#### 【 0 0 6 3 】

スクランブル処理・I F F T・ガードタイム付加・窓かけ処理回路 36において逆フーリエ変換処理 ( I F F T 処理 ) によって周波数ドメイン多重化シンボルストリームから時間ドメインの多重化シンボルストリームに変換される。

さらにスクランブル処理・I F F T・ガードタイム付加・窓かけ処理回路 36においてガードタイムの付加ならびに窓かけ処理 ( ウィンドー処理 ) が施される。

20

#### 【 0 0 6 4 】

スクランブル処理・I F F T・ガードタイム付加・窓かけ処理回路 36 は、後述するスクランブル処理、逆高速フーリエ変換 ( I F F T : Inverse Fast Fourier Transform ) 処理、ガードタイム処理、窓かけ処理 ( ウィンドー処理 ) などを総称して 1 つの手段として示したものであり、これらの処理を個別の回路または個別の手段に分離して処理してもよい。

#### 【 0 0 6 5 】

スクランブル処理・I F F T・ガードタイム付加・窓かけ処理回路 36 における、スクランブル処理、ガードタイム付加・窓かけ処理は本発明にとって必須ではない。しかしながら、スクランブル処理を行うと、通信の秘匿性 ( 機密性 ) が高まる。

30

#### 【 0 0 6 6 】

直交変換の代表例として、I F F T を例示したが、スクランブル処理・I F F T・ガードタイム付加・窓かけ処理回路 36 における I F F T に代えて、他の直交変換処理、たとえば、逆離散コサイン変換 ( I D C T : Inverse Discrete Cosine Transform ) 処理を行うこともできる。

#### 【 0 0 6 7 】

以上から、スクランブル処理・I F F T・ガードタイム付加・窓かけ処理回路 36 は基本的には、直交変換処理を行う回路または手段である。

40

#### 【 0 0 6 8 】

スクランブル処理・I F F T・ガードタイム付加・窓かけ処理回路 36 の出力シンボルは、送信回路 38 において高周波信号と疊込まれ所望の周波数帯域に周波数変換された後、アンテナ 39 を介して空中に送信される。

#### 【 0 0 6 9 】

図 2 ( A ) ~ ( C ) を参照してマルチプレクサ 34 の内部の構成ならびにこの多重化方法により生成される各チャネルのシンボルの並びについて説明する。

図 2 ( A ) ~ ( C ) は、図 1 に図解したマルチプレクサ 34 における多重送信の基本概念を示す図である。

図 1 ( A ) に図解したマルチプレクサ 34 は基本的に、図 2 ( B ) に図解したスイッチ

50

グ回路として構成されている。

【0070】

図2(A)は、マルチプレクサ34において多重化された各チャネルのシンボルストリームを示している。ここでは、チャネル1(CH1)からチャネル4(CH4)まで4つのチャネルについて例示している。それぞれのチャネルのシンボルストリームは個別にマルチプレクサ34に挿入されている。

【0071】

図2(B)はマルチプレクサ34における処理の概念を示したものである。入力されてきた各チャネルのシンボルストリームをサイクリックにスイッチング処理して、各チャネルのシンボルが周期的に現れるようにシンボルを配置する。多重化されたシンボルストリームを図2(C)に示す。

10

【0072】

この例示は、最大4チャネルの多重化を行う場合を例にとったため各チャネルのシンボルの出現周期は4であるが、最大のチャネル多重数はこれに限定されることはなく、任意の整数nに関して $2^n$ (n=1, 2, 3, 4, ...)に設定することができる。その場合の各チャネルのシンボルの出現周期は、最大の多重数と同じ $2^n$ となる。

【0073】

マルチプレクサ34における多重化処理を $2^2$ チャネルの処理とした場合、実際に通信に用いられるチャネル数が最大の多重数よりも小さい場合には、使われていないチャネルのシンボルとして振幅が「0(ゼロ)」のヌル(Nu11)シンボルを挿入して、マルチプレクサ34における周期的な多重化処理を行う。

20

【0074】

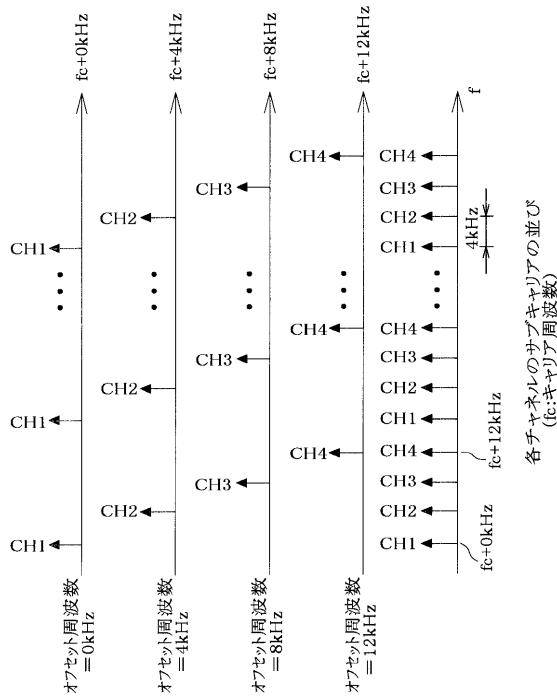

図3は複数チャネルのサブキャリアの並びを示す図である。

図3に図解した例示においては、チャネル数が4で、サブキャリア間隔が隣接するチャネルごと4kHzのOFDM処理を行っている場合、すなわち1シンボル変調時間が250μs=1/4kHzである場合を例示している。多重信号のサブキャリア間隔は4kHzであるが、チャネル1～チャネル4は1サブキャリア単位で周波数軸上に周期的に出現するため、各チャネルのサブキャリアは、16kHz=4×4kHzおきに出現している。図3における記号 $f_c$ はキャリア(搬送波)周波数(帯域信号の中心周波数)を示す。

30

【0075】

本発明の実施の形態においては、マルチキャリア変調による多重通信を行うときに、複数チャネルのサブキャリアが周期的に配置されるようにしている。その理由は、多数のシンボルの変調を容易にするためであり、さらに後述する受信装置40におけるチャネル選択回路43においてチャネル分離を容易にするためである。

【0076】

受信装置の第1実施の形態

図1(B)に図解したOFDM方式の無線通信システムの受信装置40について述べる。この実施の形態において、送信装置30と同様、多重チャネル数が4でサブキャリア間隔が4kHzのOFDM処理を行っている場合、すなわち1シンボル変調時間が250μs=1/4kHzである場合を例示する。さらに、説明の都合上、多重信号の信号帯域が1024kHzで、サブキャリアが256本存在する場合を例示する。これは、1チャネルあたりのサブキャリア数が64本(=256本/4)の多重である場合に相当する。

40

【0077】

受信装置40は、受信アンテナ41と、高周波受信回路42と、信号成分分離装置(デマルチプレクサ、または、チャネル選択回路)43と、FFT・デスクランブル処理手段44と、ビット抽出回路45と、復号回路46とを有する。

【0078】

OFDM方式の無線通信システムの送信装置30より送信された信号は、受信アンテナ41で受信され、高周波受信回路42においてベースバンド帯域にダウンコンバートされる。さらに、図解しないA/D変換器においてデジタル信号に変換されて、接続線202

50

より信号成分分離装置 4 3 に入力される。

【 0 0 7 9 】

信号成分分離装置 4 3 には、チャネル 1 ~ チャネル 4 までの信号が周波数軸上に並べられている信号が時間軸上での表現で入力されることになる。

信号成分分離装置 4 3 は、送信装置 3 0 におけるマルチブレクサ 3 4 の処理とは逆に、複数のチャネルごとに信号を分離する（デマルチブレクシングする）。この信号成分分離装置 4 3 の詳細な回路構成と処理方法については、図 4 ~ 図 7 を参照して後述する。

【 0 0 8 0 】

高周波受信回路 4 2 から信号成分分離装置 4 3 に入力されるシンボル数は、1 变調時間あたり 256 個であるが、（簡単のためここではオーバーサンプルは考えない）、所望のチャネルのサブキャリア本数はその 1/4 であるから、チャネル選択回路 4 3 では周波数軸上でのデシメーション（decimation）が行われ、64 個（= 256 個 / 4）のシンボルが出力される。これにより、FFT・デスクランブル処理手段 4 4 における FFT 処理のシンボル数が 1/4 に減少する。

10

【 0 0 8 1 】

信号成分分離装置 4 3 の出力シンボルが信号線 204 を介して FFT・デスクランブル処理手段 4 4 に入力される。

FFT・デスクランブル処理手段 4 4 において、送信装置 3 0 におけるスクランブル処理・IFFT・ガードタイム付加・窓かけ処理回路 3 6 で行った IFFT（逆高速フーリエ変換）とは逆の高速フーリエ変換（FFT）処理が行われ、周波数軸上に並んでいるシンボル列が抽出される。

20

【 0 0 8 2 】

信号成分分離装置 4 3 において所望のチャネルのシンボルが選択されて抽出されて FFT・デスクランブル処理手段 4 4 に印加されているから、FFT 処理により抽出されたシンボルは、所望のチャネル以外の他のチャネルのシンボルは含まれていない。すなわち、処理手段 4 4 における処理は所望のチャネルを受信するのに必要最低限のポイント数をもつ FFT 処理で充分である。その結果、FFT・デスクランブル処理手段 4 4 における FFT 処理回路が小規模になる。

【 0 0 8 3 】

このようにして抽出された所望のチャネルのシンボルストリームは、スクランブル処理・IFFT・ガードタイム付加・窓かけ処理回路 3 6 におけるランダム位相シフト処理、ランダム直交変換処理等などの処理に対応する処理を行い、送信装置 3 0 において行われたスクランブルを解いた後、信号線 206 を介してビット抽出回路 4 5 に入力される。

30

【 0 0 8 4 】

ビット抽出回路 4 5 において、シンボルが変調されている変調方式に応じてビットを抽出し、符号化ビットストリームを復号回路 4 6 へ印加する。そのような変調方式としては、OFDM 方式において適用される QPSK、8PSK、16QAM など様々な変調方式を適用できる。

【 0 0 8 5 】

復号回路 4 6 は、送信装置 3 0 における複数チャネルの符号化回路 311 ~ 31M で行われた符号化やインターリープとは逆のデインターリープおよび復号処理を行うことにより、情報ビットストリームを抽出する。

40

【 0 0 8 6 】

多数のサブキャリアのシンボル列の信号を受信した受信装置 4 0 に信号成分分離装置 4 3 を設けることにより、FFT・デスクランブル処理手段 4 4 、ビット抽出回路 4 5 、復号回路 4 6 におけるサンプルレートを所望のチャネル分に低下させて（デシメーションして）から行うことが可能となり、FFT・デスクランブル処理手段 4 4 以降の回路 4 5 ~ 4 6 の処理量を大幅に、たとえば、（1/多重数分）に低減することが可能となる。

【 0 0 8 7 】

特に、信号成分分離装置 4 3 を FFT・デスクランブル処理手段 4 4 の前段に設けて FFT

50

T・デスクランブル処理手段44におけるFFT処理のデータ数を減少させているので、FFT処理のためのメモリ容量が少なくなり、受信装置40の小規模化に大きく貢献する。また、FFT・デスクランブル処理手段44におけるFFT処理時間を短縮できる。

【0088】

各チャネルのサブキャリアは、システムの周波数帯域全体にまたがって配置されることから、本実施の形態をDABシステムのような多数のチャネルが多重化されている無線通信システムに適用した場合、大きな周波数ダイバーシティ効果が期待できる。これにより、フェーディングによる通信品質の劣化を抑えることが可能となる。

【0089】

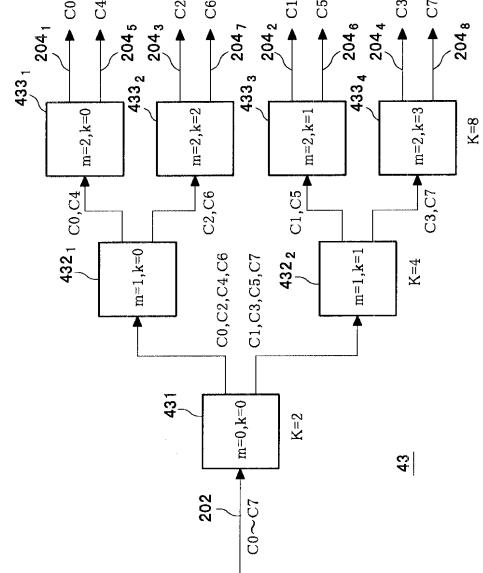

信号成分分離装置43

10

図4～図7を参照して、図1(B)に示した信号成分分離装置43の実施の形態について述べる。

図4は信号成分分離装置43の構成図である。

図5は図4に図解した信号成分分離装置43を構成する二分岐回路の回路図である。

図6は図5に図解したシンボル遅延回路43aの態様を示す図である。

図7は図5に図解した位相オフセット調整回路43bの態様を示す図である。

本実施の形態においては、サブキャリアが $2^3$ チャネル = 8チャネルC0～C7の場合について述べる。

【0090】

図4に図解した信号成分分離装置43は、1個の第1段目の二分岐回路431と、2個の第2段目の二分岐回路432<sub>1</sub>、432<sub>2</sub>と、4個の第3段目の二分岐回路433<sub>1</sub>～433<sub>4</sub>を有する。信号成分分離装置43のこの回路構成は、シンボルを順次、二分岐する二分岐回路431：432<sub>1</sub>、432<sub>2</sub>：433<sub>1</sub>～433<sub>4</sub>が2の巾乗の形態で拡散するように（または、2の巾乗の形態でピラミッドのように階層的に）構成されている。

20

【0091】

二分岐回路の意味は、シンボル列が入力されたとき、サブキャリアごと交互に2系統に分岐したシンボル列を抽出するからである。

【0092】

信号成分分離装置43は、図4に図解したように、個別の二分岐回路431、432<sub>1</sub>、432<sub>2</sub>、および、433<sub>1</sub>～433<sub>4</sub>を組み合わせて構成することができるし、これらの二分岐回路を1個のDSP（デジタル信号プロセッサ）で構成することもできる。以下、個別に二分岐回路を設けて、それを組み合わせた場合について述べる。

30

【0093】

図4における記号の意味を説明する。

記号Nは高周波受信回路42から出力され、信号成分分離装置43で受信したシンボル系列の1変調時間あたりのサンプルポイント数を示す。

記号K（大文字）は信号成分分離装置43の内部の各段の二分岐回路において分離するシンボルの分離数を示す。第1段の二分岐回路431は2系列のシンボル列に分離するからK = 2であり、第2段の2つの二分岐回路432<sub>1</sub>、432<sub>2</sub>で4系列のシンボル列に分離するからK = 4であり、第3段の4つの二分岐回路433<sub>1</sub>～433<sub>4</sub>で8系列のシンボル列に分離するからK = 8である。

40

記号mは二分岐回路の段の位置を示す。第1段をm = 0とする。

記号k（小文字）はその二分岐回路に0(Hz)を基準としていくつのサブキャリア分の周波数オフセットを持つ信号群が入力されていることを示すパラメータである。

【0094】

二分岐回路はそれぞれ、パラメータ（m, k）を用いて表すことができる。その具体的な意味については図5を参照して述べる。

【0095】

信号成分分離装置43は、高周波受信回路42から出力されたベースバンド帯域のマルチキャリア・デジタル信号（マルチキャリア多重信号）をサブキャリア単位に分離する。

50

高周波受信回路 4 2 で受信したシンボル列は周期的に配列されているから、信号成分分離装置 4 3 は受信信号を  $2^c$  キャリアおきの  $2^c$  個に分離する。c は任意の整数であり、 $2^c = 2, 4, 8, 16, \dots$  となる。

【 0 0 9 6 】

図 5 は図 4 に図解した二分岐回路の一般的な回路構成を示す。

二分岐回路は、シンボル遅延回路 4 3 a と、位相オフセット調整回路 4 3 b と、加算回路 4 3 c と、減算回路 4 3 d とで構成される。

【 0 0 9 7 】

m 段のシンボル遅延回路 4 3 a は、そのシンボル遅延回路 4 3 a に入力されるシンボルの数のメモリ容量を有し、入力されたシンボル系列をシンボル個数  $N / (2^{(m+1)})$  だけ遅延する。段数 m は、第 1 段の段数  $m = 0$  とする。シンボル遅延回路 4 3 a は、実質的には 1 变調時間内の N シンボルについて、 $(2^{(m+1)})$  シンボルを遅延する。

シンボル遅延回路 4 3 a は、たとえば、FIFO (First-In First-Out) メモリ、通常のランダムアクセスメモリなどで構成できる。

【 0 0 9 8 】

図 6 に  $m = 0 \sim m = 3$  についてのシンボル遅延回路 4 3 a の遅延量を図解する。

【 0 0 9 9 】

図 5 に図解した第 1 段の二分岐回路 4 3 1 に、高周波受信回路 4 2 から 8 チャネル C 0 ~ C 7 のシンボル系列が入力された場合、 $m = 0, 2^{(m+1)} = 2$  であるから、第 1 段の二分岐回路 4 3 1 のシンボル遅延回路 4 3 a はシンボル数 N の半分だけ遅延する。

【 0 1 0 0 】

同様に、第 2 段の二分岐回路 4 3 2<sub>1</sub> , 4 3 2<sub>2</sub> におけるシンボル遅延回路 4 3 a は、第 1 段の二分岐回路 4 3 1 のシンボル遅延回路 4 3 a の半分のメモリ容量を有し、シンボル数  $N / 4$  だけ遅延する。

第 3 段の二分岐回路 4 3 2<sub>1</sub> ~ 4 3 2<sub>4</sub> におけるシンボル遅延回路 4 3 a は第 1 段の二分岐回路 4 3 1 のシンボル遅延回路 4 3 a の  $1 / 4$  のメモリ容量を有し、シンボル数  $N / 8$  だけ遅延する。

【 0 1 0 1 】

各段の二分岐回路において、出力されるシンボルの数が入力されたシンボルの数の半数となることから、デシメーションが行われたことと等価になり、後段の二分岐回路に入力されるシンボル数は前段の二分岐回路に入力されるシンボル数の半分になり、シンボル遅延回路 4 3 a のメモリ容量も、後段にいくにしたがい、前段の半分になる。

【 0 1 0 2 】

m 段の位相オフセット調整回路 4 3 b は、 $- (k / (2^m))$  (ラジアン) だけ、入力されたシンボルの位相をずらす (位相オフセットする)。

図 3 に図解したように、サブキャリア群により 0 (Hz) を基準として周波数オフセットがあるので、位相オフセット調整回路 4 3 b は、このオフセットにより発生する位相の回転を調整するための位相シフトを行う。その位相シフト量は、0 (Hz) を基準としてサブキャリア分の周波数オフセットを示す k (小文字) と段数 m とに応じた量の角度、 $- (k / 2^m)$  (ラジアン) である。

【 0 1 0 3 】

図 7 に各種パラメータ m , k についての位相オフセット調整回路 4 3 b の位相シフト状態を図解する。

【 0 1 0 4 】

第 1 段の二分岐回路 4 3 1 における位相オフセット調整回路 4 3 b は、パラメータが  $m = 0, k$  (小文字) = 0 であるから、位相の回転は行わない。

【 0 1 0 5 】

第 2 段の二分岐回路 4 3 2<sub>1</sub> の位相オフセット調整回路 4 3 b は、パラメータが  $m = 1, k = 0$  であるから、第 1 段の二分岐回路 4 3 1 における位相オフセット調整回路 4 3 b と同様、位相回転を行わない。

10

20

30

40

50

しかし、第2段の二分岐回路432<sub>2</sub>の位相オフセット調整回路43bは、パラメータがm = 1, k (小文字) = 1であるから、- / 2 (ラジアン)だけ位相を回転する。この位相回転は、図解のごとく、I軸とQ軸とを入れ換えて、かつ、極性を反転することを意味する。シンボルの位相の回転は、/ 2の倍数のときは信号の極性の逆転、または、I軸とQ軸との入れ換えを行うだけでよい。

【0106】

第3段の二分岐回路433<sub>1</sub> ~ 433<sub>4</sub>のそれぞれの位相オフセット調整回路43bは、パラメータ、m = 2, k (小文字) = 1 ~ 3について、図解のごとく、位相シフトを行う。k = 0の場合は位相シフトを行わない。

【0107】

このように、二分岐回路における位相オフセット調整回路43bによる位相シフトは、極性の反転、加減算、係数乗算によって実現できる。

【0108】

図5に図解した二分岐回路の動作について述べる。

二分岐回路は入力された信号を交互に分離し、シンボル列を周波数軸上でデシメーションする回路である。

【0109】

図5に図解のごとく、8チャネルのサブキャリアC0, C1, C2, C3 ~ C7の信号列(サブキャリア群)が第1段の二分岐回路431に入力された場合、シンボル遅延回路43aにおいてシンボル数(N/2)だけ遅延したシンボルと、位相オフセット調整回路43bにおいて、k = 0であり、位相シフトされていないシンボル列とを加算回路43cで加算すると、サブキャリアC0, C2, C4, C6のシンボル系列のみが分離して抽出される。

【0110】

減算回路43dにおいて、シンボル遅延回路43aにおいてシンボル数N/2だけ遅延したシンボルから位相オフセット調整回路43bにおいて位相シフトしていないシンボル列を減じるとサブキャリアC1, C3, C5, C7のシンボル系列のみが分離して抽出される。このように、第1段の二分岐回路431は入力された交互のサブキャリアごと、シンボル系列を分離する。

【0111】

分離されたシンボル系列は、それぞれ周波数軸上の分解能が半分にデシメーションされており、出力されるシンボル数は両出力ともN/2シンボルになる。

【0112】

第2段の二分岐回路432<sub>1</sub>にサブキャリアC0, C2, C4, C6が入力されると、シンボル遅延回路43aにおいてシンボル数N/4だけ遅延したシンボルと、位相オフセット調整回路43bにおいて、k = 0であり位相回転されていないシンボル列とを加算回路43cで加算すると、サブキャリアC0, C4のシンボル系列が抽出される。

二分岐回路432<sub>1</sub>の減算回路43dにおいて、シンボル遅延回路43aにおいてN/4だけ遅延したシンボルから位相オフセット調整回路43bにおいて位相回転されていないシンボル列を減じると、サブキャリアC2, C6のシンボル系列が抽出される。

【0113】

このように、第2段の二分岐回路431<sub>1</sub>においても入力されたサブキャリアを交互に分離してシンボル系列を出力する。分離されたシンボル系列はそれぞれ、周波数軸上の分解能が半分になっており、デシメーションされている。

【0114】

なお、第2段の二分岐回路431<sub>1</sub>におけるシンボル遅延回路43aのメモリ容量は、第1段の二分岐回路431におけるシンボル遅延回路43aのメモリ容量の半分である。

【0115】

第2段の二分岐回路432<sub>2</sub>にサブキャリアC1, C3, C5, C7が入力されると、シンボル遅延回路43aにおいてN/4(サンプリング時間)だけ遅延したシンボルと、位

10

20

30

40

50

相オフセット調整回路 4 3 bにおいて、 $k = 1$  ,  $m = 1$  であり、 $- \pi / 2$  (ラジアン) だけ位相シフトされたシンボル列とを加算回路 4 3 c で加算するとサブキャリア C 1 , C 5 のシンボル系列が抽出される。

【 0 1 1 6 】

二分岐回路 4 3 2<sub>1</sub> の減算回路 4 3 d において、シンボル遅延回路 4 3 a において  $N / 4$  だけ遅延したシンボルから位相オフセット調整回路 4 3 b において  $- \pi / 2$  (ラジアン) だけ位相シフトされたシンボル列を減じるとサブキャリア C 3 , C 7 のシンボル系列が抽出される。

【 0 1 1 7 】

このように、第 2 段の二分岐回路 4 3 1<sub>2</sub> においても、入力されたサブキャリアが交互に分離されたシンボル系列を抽出する。分離されたシンボル系列はそれぞれ、周波数軸上で分解能が半分になっており、デシメーションされている。 10

【 0 1 1 8 】

なお、第 2 段の二分岐回路 4 3 1<sub>2</sub> におけるシンボル遅延回路 4 3 a のメモリ容量は、第 1 段の二分岐回路 4 3 1 におけるシンボル遅延回路 4 3 a のメモリ容量の半分である。

【 0 1 1 9 】

第 3 段の二分岐回路 4 3 3<sub>1</sub> ~ 4 3 3<sub>4</sub> においても、上記同様のシンボル分離とデシメーションを行う。

その結果、最終的には第 3 段の二分岐回路 4 3 3<sub>1</sub> ~ 4 3 3<sub>4</sub> の各出力線から、チャネル C 0 , C 4 , C 2 , C 6 , C 1 , C 5 , C 3 , C 7 のシンボルが分離されて出力される。 20

【 0 1 2 0 】

これら 1 サブキャリアごとのシンボルに分離されたシンボルは、たとえば、図 8 を参照して後述する周波数オフセット補償回路 (周波数オフセット補償・除去手段) を通して周波数オフセットが補正された後に、図 1 (B) に図解した FFT・デスクランブル処理手段 4 4 に印加される。FFT・デスクランブル処理手段 4 4 以降の動作は前述した。

FFT・デスクランブル処理手段 4 4 には周波数軸上の分解能を落とした信号が印加されるから、FFT・デスクランブル処理手段 4 4 の回路構成は簡単になる。

【 0 1 2 1 】

このように二分岐回路を階層的に組み合わせた構成した信号成分分離装置 4 3 によれば、各段で入力したサブキャリアごと交互にシンボルを交互に分離するとともに、周波数軸上における信号成分の分解能を順次  $1 / 2$  に低下させる (デシメーションする) ことができる。 30

【 0 1 2 2 】

信号成分分離装置 4 3 の各部を構成している二分岐回路は、基本的に同じ回路構成をしており、第 1 段から段 2 段、第 3 段にいくに従い、シンボル遅延回路 4 3 a のメモリ容量が順次半分になっていくこと、および、位相オフセット調整回路 4 3 b における位相シフト量を異ならせる他は、基本的に同じ回路構成をしている。したがって、簡単な構成の二分岐回路を組み合わせて構成される信号成分分離装置 4 3 の構成も簡単である。さらに、デシメーションが  $1 / (2 \times 2)$  単位で行われるから、多数のサブキャリアが変調されたマルチキャリアにおいても、回路構成が簡単になる。 40

【 0 1 2 3 】

以上の実施の形態は 8 シンボル列について例示したが、8 シンボル列、16 シンボル列、32 シンボル列などの分離が可能であることはどの分離も上記と同様の方法に従って実現できる。また、2 シンボル列、4 シンボル列への分離が可能であることは言うまでもない。

【 0 1 2 4 】

受信装置の第 2 実施の形態

図 8 は本発明の第 2 実施の形態としての受信装置 4 0 A の構成図である。

図 8 に図解した受信装置 4 0 A は、図 1 (B) に図解した受信装置 4 0 と同様、図 1 (A) に図解した送信装置 3 0 から送出されたマルチキャリア信号を受信する。 50

## 【0125】

受信装置40Aは、信号成分分離装置43と、信号選択回路47と、2つの周波数オフセット補償回路48A、48Bを有する。

この実施の形態では、2つの周波数オフセット補償回路48A、48Bを設けた例を図解しているが、周波数オフセット補償回路は複数並列に設けることができる。

## 【0126】

周波数オフセット補償回路48A、48Bの後段には、図1(B)に図解した、FFT・デスクランブル処理手段44、ビット抽出回路45、復号回路46などが、周波数オフセット補償回路の個数に合わせた系、本実施の形態では2系統、設けられる。

## 【0127】

信号成分分離装置43は、図4に図解したと同様の二分岐回路を階層化した構成をとることができる。したがって、信号成分分離装置43からはサブキャリア単位で信号成分を、 $2^C$ 通りに(ただし、Cは任意の整数)、分離した信号成分が得られる。

## 【0128】

信号選択回路47は、信号成分分離装置43で分離した信号成分のうち希望するサブキャリアのシンボルを選択して出力する。図4の図解から明らかのように、信号成分分離装置43の最終段の二分岐回路の出力がどのサブキャリア群に対応するか一義的に決まっているので、信号選択回路47におけるシンボルの選択は容易である。この例では信号選択回路47は2つのシンボルを選択出力しているが、信号選択回路47における選択シンボル数は、1または任意の複数にすることができる。

10

## 【0129】

周波数オフセット補償回路48A、48Bは、信号選択回路47で選択したサブキャリア群の信号が、図3に図解したように周波数オフセットがあるので、それを補償する。

## 【0130】

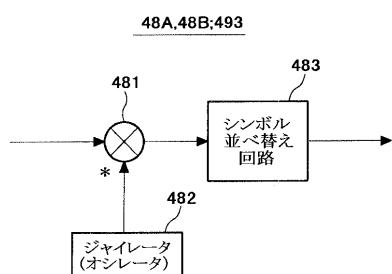

図9は周波数オフセット補償回路48A、48Bの回路構成例を示す図である。

周波数オフセット補償回路48A、48Bはそれぞれ、乗算器481と、ジャイレータ(オシレータ)482と、シンボル並べ替え回路483とを有する。

## 【0131】

乗算器481に入力される信号は、0(Hz)を基準として、下記に示すプラス方向に異なる周波数オフセットを有している。

30

## 【0132】

## 【数1】

$$e \times p ( j 2 ( k / N ) i + k )$$

## 【0133】

このオフセットを除去するため、ジャイレータ482は、下記に示す上記オフセットと共に複素正弦波の信号を乗算器481に出力する。このように、ジャイレータ482は、下記の複素成分信号を発生する信号発生装置である。

## 【0134】

## 【数2】

$$e \times p ( - j 2 ( k / N ) i + k )$$

## 【0135】

乗算器481は信号選択回路47で選択されたシンボルと、ジャイレータ482からの上記複素正弦波信号との乗算を行い、周波数変換してオフセット成分を除去する。

40

## 【0136】

シンボル並べ替え回路483は周波数変換した結果のうち、前半部分と後半部分を入れ替えて、その結果を出力する。

## 【0137】

本実施の形態において、図1(B)のFFT・デスクランブル処理手段44におけるFFT処理の前に、複数、本実施の形態では2つの処理対象とするシンボル数の削減が行われているので、FFT回路の構成が簡単になり、処理速度が向上する。

50

## 【0138】

すなわち、本実施の形態によれば、FFT・デスクランブル処理手段で扱うシンボル数は上述した図1(B)の半分となる。

シンボル数をNで表すと、FFT回路を構成しているゲート数は、( $\log N$ )に比例したゲート数となる。したがって、FFT回路に入力されるシンボル数が少なくなると、FFT回路のゲート数は極端に減少する。

図1(B)のFFT・デスクランブル処理手段44におけるFFTのゲート数と、図8に図解した受信装置におけるFFT・デスクランブル処理手段の2つのFFT回路のゲート数の和を比較すると、本実施の形態のFFT・デスクランブル処理手段の2つのFFT回路のゲート数の和のほうが小さくなる。このことは、2つのFFT・デスクランブル処理手段を設けたほうが、図1(B)に図解の1つのFFT・デスクランブル処理手段44より回路構成が簡単になることを意味する。さらに構成の簡単なFFT回路は動作速度を高めることができる。したがって、図8の受信装置40Aを用いると、全体の回路構成が簡単になり、動作速度も向上するという利点がある。

10

## 【0139】

なお、信号選択回路47におけるサブキャリア群の選択は2つに限らず、1サブキャリア群だけでもよいし、2以上の複数のサブキャリア群を選択することもできる。

## 【0140】

受信装置の第3実施の形態

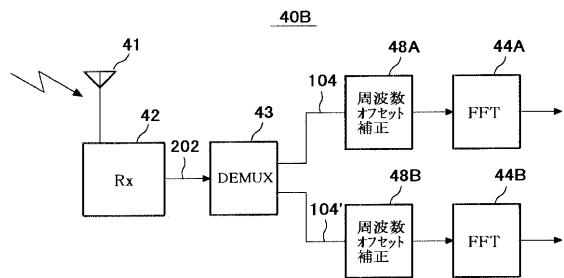

図10は本発明の第3実施の形態としての受信装置40Bの構成図である。

20

図10に図解した受信装置40Bは、図1(B)に図解した受信装置40と同様、または、図8に図解した受信装置40Aと同様、図1(A)に図解した送信装置30から送出されたマルチキャリア信号を受信する。

## 【0141】

受信装置40Bは、高周波受信回路42と、信号成分分離装置43と、2系列の周波数オフセット補償回路48A、48Bとを有する。

この実施の形態では、2つの周波数オフセット補償回路48A、48Bを設けた例を図解しているが、周波数オフセット補償回路は複数並列に設けることができる。

## 【0142】

周波数オフセット補償回路48A、48Bの後段には、図1(B)に図解した、FFT・デスクランブル処理手段44、ビット抽出回路45、復号回路46などが、周波数オフセット補償回路の個数に合わせた系統、本実施の形態では2系統、設けられる。

30

## 【0143】

信号成分分離装置43には、たとえば、図4に図解した第1段の二分岐回路431と、第2段の二分岐回路432<sub>1</sub>と、第3段目の二分岐回路433<sub>1</sub>、433<sub>2</sub>を設ける。その結果、信号成分分離装置43からはC0、C4、C2、C6のサブキャリア群と、C1、C5、C3、C7のサブキャリア群とが分離される。

## 【0144】

周波数オフセット補償回路48A、48Bは、信号成分分離装置43で分離したサブキャリア群の信号が、図3に図解したように周波数オフセットがあるので、それを補償する。周波数オフセット補償回路48A、48Bは、第2実施の形態において述べた。すなわち、周波数オフセット補償回路48A、48Bの回路構成例を図9に図解し、その動作は上述したので、説明を省略する。

40

## 【0145】

FFT・デスクランブル処理手段44A、44Bはそれぞれ、周波数オフセット補償回路48A、48Bで周波数オフセット補償された、C0、C4、C2、C6のサブキャリア群、C1、C5、C3、C7のサブキャリア群についてFFT処理などを行う。

## 【0146】

FFT・デスクランブル処理手段44A、44Bで扱うシンボル数は上述した図1(B)の半分となる。シンボル数をNで表すと、FFT回路を構成しているゲート数は、( $10$

50

$g_N$  ) に比例したゲート数となる。したがって、FFT回路に入力されるシンボル数が少なくなると、FFT回路のゲート数は極端に減少する。図1(B)のFFT・デスクランブル処理手段44におけるFFTのゲート数と、図10に図解したFFT・デスクランブル処理手段44A、44Bの2つのFFT回路のゲート数の和を比較すると、FFT・デスクランブル処理手段44A、44Bの2つのFFT回路のゲート数の和のほうが小さくなる。このことは、2つのFFT・デスクランブル処理手段44A、44Bを設けたほうが、図1(B)に図解の1つのFFT・デスクランブル処理手段44より回路構成が簡単になることを意味する。さらに構成の簡単なFFT回路は動作速度を高めることができる。

したがって、図10の受信装置40Bを用いると、全体の回路構成が簡単になり、動作速度も向上するという利点がある。 10

#### 【0147】

以上の例示は、周波数オフセット補償回路、および、FFT・デスクランブル処理手段44A、44Bを2系統設ける場合について述べたが、これらを2の巾乗の数だけ並列に設けることができる。

#### 【0148】

##### 受信装置の第4実施の形態

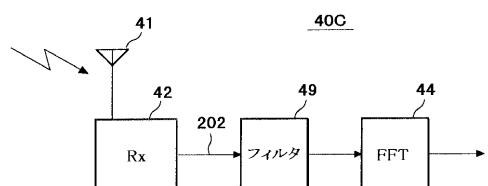

図11は本発明の第4実施の形態の受信装置40Cの概略構成図である。

受信装置40Cも、上述した第1～第3実施の形態の受信装置40、40A、40Bと同様、図1(A)の送信装置30から送出されたマルチキャリア信号を分離して復号する。 20

#### 【0149】

受信装置40Cは、受信アンテナ41、高周波受信回路42、フィルタ装置49、FFT・デスクランブル処理手段44を有する。

FFT・デスクランブル処理手段44以降の回路は、図1(B)と同様である。

#### 【0150】

図11に図解した受信装置40Cと上述した受信装置40、40A、40Bとの相違を述べると、受信装置40Cは受信装置40、40A、40Bのように信号成分分離装置43を用いて複数のシンボル系列を抽出するのではなく、フィルタ装置49により所望の1つのサブキャリア群の信号成分のみを抽出して、その結果を、FFT・デスクランブル処理手段44以降の回路で処理する。 30

#### 【0151】

高周波受信回路42は上述したように、受信アンテナ41アンテナで受信した高周波信号をベースバンド帯域に周波数変換を行い、ベースバンド帯域に周波数変換したアナログ信号からデジタル信号(9シンボル列)に変換する。

#### 【0152】

フィルタ装置49は、高周波受信回路42からのデジタル・シンボル列を入力してサブキャリア単位でフィルタして、所望のサブキャリア群のみ抽出する。フィルタ装置49は、出力されるサブキャリア群を表現するのに最低必要なサンプル数しか出力しない。その結果、周波数軸上の大幅なデシメーションが実現される。

#### 【0153】

信号成分分離装置(二分岐回路)とフィルタ装置との相違を述べる。信号成分分離装置は、1信号群を入力して、1信号群を分離した2信号群を出力する。これに対して、フィルタ装置は、1信号群を入力して、特定の周波数帯域の1信号群を選択して出力する。 40

#### 【0154】

FFT・デスクランブル処理手段44以降の回路は、図1(B)の受信装置40などの回路を参照して述べたと同様の処理を行う。

#### 【0155】

##### フィルタ装置の第1実施の形態

図12は図11に示したフィルタ装置の第1の実施の形態の回路例である。

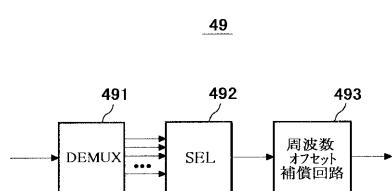

図12に図解したフィルタ装置49は、信号成分分離装置(デマルチプレクサ)491と 50

、シンボル群選択回路 492 と、周波数オフセット補償回路（周波数オフセット補償・除去回路）493 とで構成されている。

【0156】

フィルタ装置 49 の構成は、図 8 の回路構成、すなわち、信号成分分離装置 43、信号選択回路 47、周波数オフセット補償・除去回路 48A、48B と類似しており、フィルタ装置 49 は実質的に図 8 のこれらの回路 43、47、48A、48B と同等の処理を行う。

【0157】

信号成分分離装置 491 は図 8 の信号成分分離装置 43 と同様、図 4 に図解した二分岐回路の組み合わせの回路構成である。

シンボル群選択回路 492 は図 8 の信号選択回路 47 と同様である。

周波数オフセット補償・除去回路 493 は図 9 に図解した周波数オフセット補償・除去回路 48A、48B と同様の回路構成である。

【0158】

信号成分分離装置 491 は、高周波受信回路 42 から出力されたシンボル列について所望のサブキャリア間隔でシンボルを分離する。

周波数オフセット補償・除去回路（周波数オフセット補償回路）493 は、図 9 に図解した回路構成をしており、入力されたシンボル（信号）を基準を 0 (Hz) としてサブキャリア群に周波数変換を行い、周波数オフセット除去を行う。

【0159】

図 11 の FFT・デスクランブル処理手段 44 は選択されたシンボルについてのみ FFT 処理を行うので、DFT のポイント数を小さく抑えることができ、FFT・デスクランブル処理手段 44 の回路構成は簡単になる。

【0160】

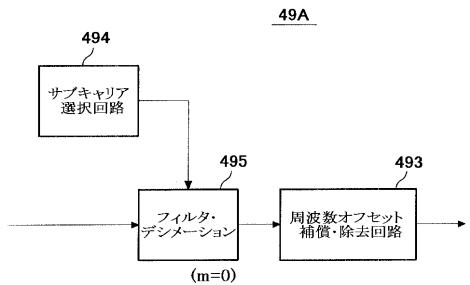

フィルタ装置の第 2 実施の形態

図 13 は図 11 のフィルタ装置の第 2 の実施の形態の回路例である。

第 2 実施の形態のフィルタ装置は、受信したサブキャリア群を、奇数組のキャリアと偶数組のキャリアとに 2 分岐するフィルタ装置である。

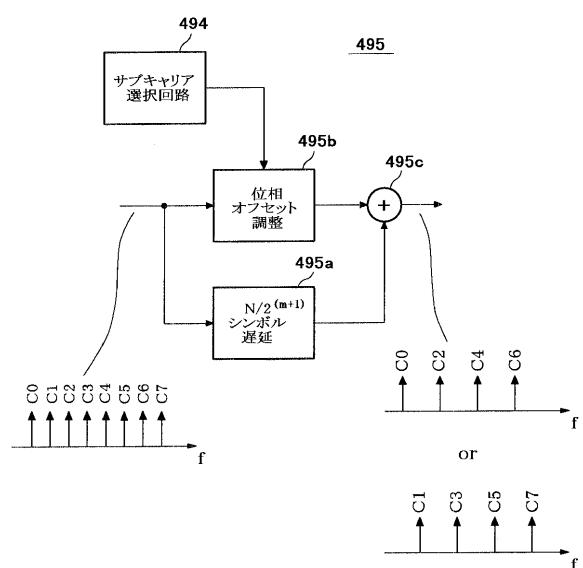

第 2 実施の形態のフィルタ装置 49A は、サブキャリア選択回路 494 と、フィルタ・デシメーション回路 495 と、周波数オフセット補償・除去回路 493 とを有する。

【0161】

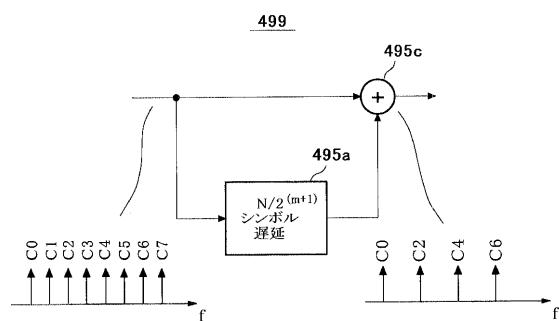

図 14 は図 13 に図解したフィルタ・デシメーション回路 495 の回路構成例を示す図である。

フィルタ・デシメーション回路 495 は、シンボル遅延回路 495a と、位相オフセット調整回路 495b と、加算回路 495c とで構成されている。

【0162】

フィルタ・デシメーション回路 495 の回路構成は、図 5 に図解した信号成分分離装置 43 の 1 単位の二分岐回路に類似している。すなわち、シンボル遅延回路 495a はシンボル遅延回路 43a に対応し、位相オフセット調整回路 495b は位相オフセット調整回路 43b に対応し、加算回路 495c は加算回路 43c に対応している。ただし、フィルタ・デシメーション回路 495 には、減算回路 43d は設けられていない。その理由は、フィルタ・デシメーション回路 495 においては、図 5 に図解した二分岐回路のように偶数サブキャリアと奇数サブキャリアの両者を必要とせず、いずれか一方のみの出力でよいからである。

【0163】

シンボル遅延回路 495a は、入力されたサブキャリア C0 ~ C7 を、パラメータ N、m によって定められたポイント分、すなわち、 $N / (2^{m+1})$  だけ、予め遅延する。本実施の形態においては、 $m = 0$  であり、シンボル遅延回路 495a の遅延は  $N / 2$  となる。

【0164】

サブキャリア選択回路 494 が希望するサブキャリアを選択する。

10

20

30

40

50

位相オフセット調整回路 495b は、入力されたサブキャリア C0 ~ C7 に対して、サブキャリア選択回路 494 で選択した通過サブキャリア群に応じて位相シフトを行う。

【0165】

位相オフセット調整回路 495b で行う回転位相の値（位相シフト量）は、 $- ( \quad / 2^m )$  (ラジアン) である。パラメータ  $m$  は、通過させるサブキャリア群およびパラメータ  $m$  によって決定される値であり、下記の表 1 に示す規則性をもっている。下記表において、C0 ~ C7 は、0 Hz から並んだサブキャリアを意味する。

【0166】

【表 1】

| 通過キャリア | $m=2$      | $m=1$      | $m=0$      |

|--------|------------|------------|------------|

| C0     | $\alpha=0$ | $\alpha=0$ | $\alpha=0$ |

| C4     | $\alpha=4$ |            |            |

| C2     | $\alpha=2$ | $\alpha=2$ |            |

| C6     | $\alpha=6$ |            |            |

| C1     | $\alpha=1$ | $\alpha=1$ |            |

| C5     | $\alpha=5$ |            |            |

| C3     | $\alpha=3$ | $\alpha=3$ | $\alpha=1$ |

| C7     | $\alpha=7$ |            |            |

10

20

【0167】

フィルタ・デシメーション回路 495 を多段にすることにより、K (大文字) = 8, 16, 32 などのフィルタ装置を構成することができる。その場合、各々の段の位相オフセット調整回路 495b で行われる回転位相の値は下記の表 2 に示す値となる。ただし、表 2 には K = 8 までを例示した。

【0168】

【表 2】

30

| m            | 0       | 1                 | 2        | ...               |    |     |

|--------------|---------|-------------------|----------|-------------------|----|-----|

| 回転位相値／通過キャリア | 0       | $-\frac{1}{2}\pi$ | C0<br>C4 | $-\frac{1}{4}\pi$ | C0 | ... |

|              |         |                   |          | $-\frac{3}{4}\pi$ | C4 | ... |

|              |         | $-\frac{2}{2}\pi$ | C2<br>C6 | $-\frac{1}{4}\pi$ | C2 | ... |

|              |         |                   |          | $-\frac{5}{4}\pi$ | C6 | ... |

|              |         |                   | C1<br>C5 | $-\frac{1}{4}\pi$ | C1 | ... |

|              | - $\pi$ | $-\frac{1}{2}\pi$ | C3<br>C7 | $-\frac{5}{4}\pi$ | C5 | ... |

|              |         |                   |          | $-\frac{3}{4}\pi$ | C3 | ... |

|              |         | $-\frac{3}{2}\pi$ | C3<br>C7 | $-\frac{7}{4}\pi$ | C7 | ... |

|              |         |                   |          | $-\frac{1}{4}\pi$ |    | ... |

|              |         |                   |          |                   |    | ... |

## 【0169】

本実施の形態において、位相オフセット調整回路495bで行う回転位相の値は、偶数キャリアを通過させるときには0(r a d)であり、奇数キャリアを通過させるときには( $r a d$ )である。どちらの回転位相が適用されるかは、サブキャリア選択回路404により適宜指示される。

## 【0170】

加算回路495cは、位相オフセット調整回路495bで行った回転位相処理したサブキャリアと、シンボル遅延回路495aで遅延したサブキャリアとを加算する。

その結果、たとえば、フィルタ・デシメーション回路495に、サブキャリアC0～C7が入力されたとき、フィルタ・デシメーション回路495からは、サブキャリア選択回路494で指定されたいずれか一方のサブキャリア系列のシンボルが出力される。

## 【0171】

図13のフィルタ装置49A内の周波数オフセット補償・除去回路493は、図12の周波数オフセット補償・除去回路493と同様、図9に図解したと同様の回路構成をしている。周波数オフセット補償・除去回路493は、上述した図8の周波数オフセット補償・除去回路48A、48B、または、図12の周波数オフセット補償・除去回路493と同様の動作を行う。

## 【0172】

図13に図解したフィルタ装置49Aにおいては、フィルタ・デシメーション回路495により周波数軸上でのデシメーションが行われ、出力シンボルの数が半分になる。したがって、それ以降の信号処理が、簡単で、迅速になる。

## 【0173】

フィルタ装置の第3実施の形態

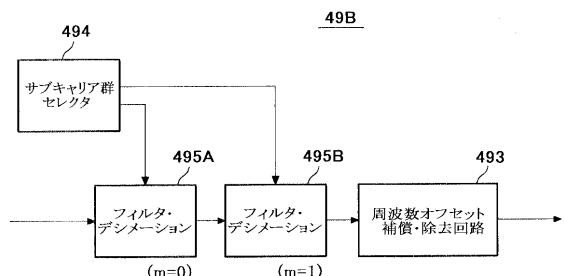

図15は、図11に図解したフィルタ装置の第3の実施の形態の回路図である。

図15に図解したフィルタ装置49Bは、サブキャリア選択回路494と、第1のフィル

10

20

30

40

50

タ・デシメーション回路 4 9 5 A と、第 2 のフィルタ・デシメーション回路 4 9 5 B と、周波数オフセット補償・除去回路 4 9 3 とを有する。

フィルタ装置 4 9 B は、図 13 に図解したフィルタ装置 4 9 A のフィルタ・デシメーション回路 4 9 5 を直列に設けられた 2 段のフィルタ・デシメーション回路 4 9 5 A、4 9 5 B に置き換えた回路である。フィルタ・デシメーション回路 4 9 5 A、4 9 5 B は共に、図 14 に図解した回路構成であり、第 1 段のフィルタ・デシメーション回路 4 9 5 A は  $m = 0$  であり、第 2 段のフィルタ・デシメーション回路 4 9 5 B は  $m = 1$  であり、このパラメータ  $m$  を適用すると、図 6 に図解したように、それぞれのフィルタ・デシメーション回路 4 9 5 A、4 9 5 B における遅延量が規定される。

【0174】

10

周波数オフセット補償・除去回路 4 9 3 は図 9 に図解した回路と同様の回路構成をとることができる。

【0175】

位相オフセット調整回路 4 9 5 b で行う回転位相の値（位相シフト量）は、 $- ( \quad / 2^m )$ （ラジアン）である。パラメータ  $m$  は、通過させるサブキャリア群およびパラメータ  $m$  によって決定される値であり、表 1 に示す規則性をもっている。

【0176】

フィルタ・デシメーション回路 4 9 5 を多段にすることにより、 $K$ （大文字） = 8, 16, 32 などのフィルタ装置を構成することができる。その場合、各々の段の位相オフセット調整回路 4 9 5 b で行われる回転位相の値は表 2 に示す値となる。

20

本実施の形態において、位相オフセット調整回路 4 9 5 b で行う回転位相の値は、偶数キャリアを通過させるときには 0 (rad) であり、奇数キャリアを通過させるときには (rad) である。どちらの回転位相が適用されるかは、サブキャリア選択回路 4 0 4 により適宜指示される。

【0177】

加算回路 4 9 5 c は、位相オフセット調整回路 4 9 5 b で行った回転位相処理したサブキャリアと、シンボル遅延回路 4 9 5 a で遅延したサブキャリアとを加算する。

その結果、たとえば、フィルタ・デシメーション回路 4 9 5 に、サブキャリア C 0 ~ C 7 が入力されたとき、フィルタ・デシメーション回路 4 9 5 からは、サブキャリア選択回路 4 9 4 で指定されたいずれか一方のサブキャリア系列のシンボルが出力される。

30

【0178】

図 15 に図解したフィルタ装置 4 9 B は、2 段のフィルタ・デシメーション回路 4 9 5 A、4 9 5 B を設けているので、4 つのサブキャリア群のいずれかを出力するフィルタ装置となる。すなわち、周波数軸上で 1 / 4 のデシメーションを行った信号を出力する回路である。

本実施の形態においては、2 個のフィルタ・デシメーション回路 4 9 5 A、4 9 5 B を 2 段に直列連結した場合を例示したが、さらに 3 段、4 段と多段 ( $m$ ) に連結し、 $2^3$ 、 $2^4$ 、 $2^m$  のサブキャリア群に分離し、そのうちの 1 つのサブキャリア群を通過させることができとなる。その場合、各フィルタ・デシメーション回路のパラメータ  $m$  の規則性は図 4 と同様である。また、回転させる位相の値については、表 1 および表 2 に示した規則性による決定される。

40

【0179】

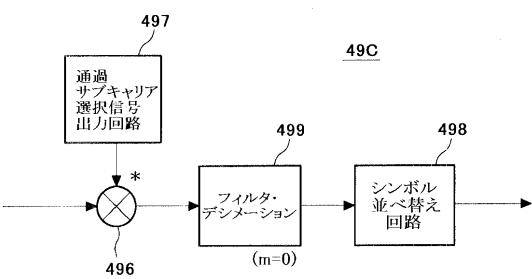

#### フィルタ装置の第 4 実施の形態

図 16 は、図 11 に図解したフィルタ装置の第 4 の実施の形態の回路例である。

フィルタ装置 4 9 C は、乗算器 4 9 6 と、通過サブキャリア選択信号出力回路 4 9 7 と、フィルタ・デシメーション回路 4 9 9 と、シンボル並べ替え回路 4 9 8 とを有する。

【0180】

乗算器 4 9 6 に入力されるシンボル列の周波数オフセットは、図 9 の乗算器 4 8 1 に入力されるシンボル列の周波数オフセットと同じである。

【0181】

50

通過サブキャリア選択信号出力回路 497 は、その周波数オフセットを除去するため、図 9 に図解したジャイレータ（オシレータ）482 と同様、選択すべきチャネルに応じた複素正弦波信号を乗算器 496 に出力する。

【0182】

乗算器 496 は、高周波受信回路 42 からのシンボル系列と通過サブキャリア選択信号出力回路 497 から出力された複素正弦波信号との乗算を行う。この演算は、フィルタ装置 49C に入力されたシンボル系列のうち、フィルタ装置 49C で選択するシンボル（サブキャリア成分）に 0 (Hz) が含まれるように周波数オフセットを持たせるためである。したがって、通過サブキャリア選択信号出力回路 497 からは選択するサブキャリアのうち、0 (Hz) から正周波数方向で最も近いサブキャリア分の周波数の信号と共に出力し、乗算器 496 がその共役信号と入力されたシンボルとの乗算を行い、周波数オフセットを除去する。

【0183】

フィルタ・デシメーション回路 499 について、図 17 を参照して述べる。

図 17 は、図 16 に図解したフィルタ・デシメーション回路 499 の回路例である。

フィルタ・デシメーション回路 499 は、シンボル遅延回路 495a と加算回路 495c などで構成されている。

フィルタ・デシメーション回路 499 の回路構成は、図 5 に図解した二分岐回路から位相オフセット調整回路 43b と減算回路 43d を削除した回路構成であり、図 14 に図解したフィルタ・デシメーション回路 495 の回路構成から位相オフセット調整回路 495b を削除した回路構成である。

フィルタ・デシメーション回路 499 は、入力されたサブキャリアのうち、0 (Hz) を基準として偶数番目のサブキャリアのチャネルのシンボル系列のみを選択出力する回路である。

フィルタ・デシメーション回路 499 によっても、出力されるシンボル数が 1 / 2 となり、周波数軸上でデシメーションが行われることになる。

【0184】

シンボル並べ替え回路 498 は、フィルタ・デシメーション回路 499 から出力されたシンボル群（サブキャリア群）の順序を、前半部分と後半部分とを入れ換えて、後半部分のシンボルのみを有効なシンボルとして出力する。

【0185】

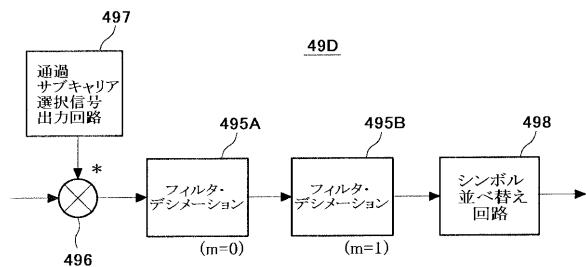

フィルタ装置の第 5 実施の形態

図 18 は、図 11 に図解したフィルタ装置の第 5 の実施の形態の回路例である。

フィルタ装置 49D は、乗算器 496 と、チャネル選択信号出力回路 497 と、第 1 および第 2 のフィルタ・デシメーション回路 499A、499B と、シンボル並べ替え回路 498 とを有する。

第 1 および第 2 のフィルタ・デシメーション回路 499A、499B はそれぞれ、図 17 を参照して述べたフィルタ・デシメーション回路 499 と同様の回路構成をしている。

【0186】

フィルタ装置 49D は、図 16 に図解したフィルタ装置 49C に、第 2 のフィルタ・デシメーション回路 499B を追加したものである。フィルタ・デシメーション回路 499B の追加により、図 15 に図解した 2 段のフィルタ・デシメーション回路 495A、495B の回路構成と同様、図 16 に図解したフィルタ装置 49C より、さらに通過キャリアを 1 / 2 に制限することができる。

その他は、図 16 に図解したフィルタ装置 49C と同様である。

【0187】

なお、フィルタ・デシメーション回路 499 をさらに多段に直列接続することにより、たとえば、m 段直列接続することにより、通過キャリアを 1 / 2<sup>m</sup> に制限することができる。

【0188】

10

20

30

40

50

### 受信装置の第5実施の形態

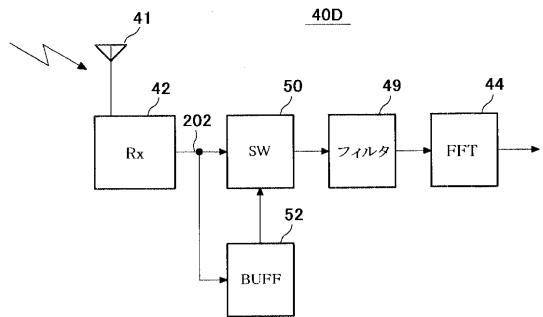

図19は本発明の第5実施の形態の受信装置の構成図である。

受信装置40Dは、受信アンテナ41、高周波受信回路42、スイッチ回路50、バッファ回路52、フィルタ装置49、FFT・デスクランブル処理手段44、および、図解を省略した図1(B)に図解のビット抽出回路45、復号回路46を有する。

#### 【0189】

高周波受信回路42は上記同様の動作を行う。

#### 【0190】

スイッチ回路50は初期状態において、高周波受信回路42の信号をフィルタ装置49に出力する。

10

その間、バッファ回路52は、1シンボル分の信号が全てフィルタ装置49に転送されるまで、高周波受信回路42の信号を蓄積し続ける。

#### 【0191】

フィルタ装置49は上述した各種の実施の形態として示したフィルタ装置49であり、高周波受信回路42からスイッチ回路50を通過して入力された信号のうちの指定された一部のサブキャリアのみ、たとえば、偶数キャリアのみの信号を抽出して、周波数軸上でのデシメーションを行い、その選択信号をFFT・デスクランブル処理手段44に出力する。

#### 【0192】

FFT・デスクランブル処理手段44は、高周波受信回路42で受信したサブキャリア数より少ないサブキャリア数についてFFT処理を行う回路として構成されている。すなわち、FFT・デスクランブル処理手段44は小型、高速動作可能に構成されている。FFT・デスクランブル処理手段44でFFT処理などを行った後、図1(A)に図解したビット抽出回路45、復号回路46などにおける処理が行われる。

20

#### 【0193】

バッファ回路52は、高周波受信回路42からの1シンボル分の信号が全てフィルタ装置49に転送された後、スイッチ回路50を経由してフィルタ装置49に信号の送出を開始する。

スイッチ回路50は高周波受信回路42の信号がフィルタ装置49に転送し終わると、バッファ回路52からの信号をフィルタ装置49に印加するよう切り替わる。

30

フィルタ装置49は、先に通過させなかった信号成分のうち本通信において必要となる信号成分を通過させた信号、たとえば、奇数キャリアを抽出し、FFT・デスクランブル処理手段44に印加する。

FFT・デスクランブル処理手段44は、再度入力された信号をFFT処理して受信シンボルを抽出し、ビット抽出回路45以降の回路の処理を行わせる。

#### 【0194】

図19に図解した回路構成をとることにより、高周波受信回路42において受信したシンボルをFFT処理するに本来必要なFFT回路より小規模の回路で、受信シンボルの抽出が可能となる。すなわち、図19の回路構成をとると、FFT・デスクランブル処理手段44の回路規模を小規模にすることができる。

40

#### 【0195】

図19に図解した受信装置の回路構成は、受信シンボルを半分にした場合を例示したが、フィルタ装置49における通過キャリアをさらに減縮することにより、4分割、8分割などにすることができる。その結果、FFT・デスクランブル処理手段44の回路規模は一段と小型になる。

#### 【0196】

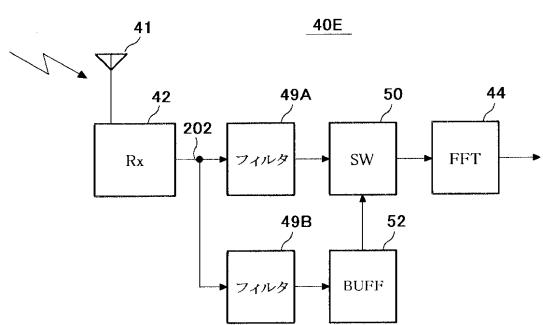

### 受信装置の第6実施の形態

図20は本発明の第6実施の形態の受信装置の構成図である。

受信装置40Eは、受信アンテナ41、高周波受信回路42、第1のフィルタ装置49A、第2のフィルタ装置49B、スイッチ回路50、バッファ回路52、FFT・デスクランブル

50

ンブル処理手段 4 4、および、図解を省略した図 1 ( B ) に図解のビット抽出回路 4 5、復号回路 4 6 を有する。

【 0 1 9 7 】

高周波受信回路 4 2 は上記同様の動作を行う。

【 0 1 9 8 】

フィルタ装置 4 9 A, 4 9 B は、上述した各種のフィルタ装置 4 9 の回路構成をとることができ、第 1 のフィルタ装置 4 9 A は、たとえば、偶数キャリアの信号の抽出を行い、第 2 のフィルタ装置 4 9 B は、たとえば、奇数キャリアの信号の抽出を行う。すなわち、本実施の形態においては、フィルタ装置 4 9 A, 4 9 B はそれぞれ、シンボルを 1 / 2 にデシメーションを行う。

10

【 0 1 9 9 】

スイッチ回路 5 0 は初期状態において、フィルタ装置 4 9 A から出力される偶数キャリアの信号を FFT・デスクランブル処理手段 4 4 に出力する。

その間、フィルタ装置 4 9 B で選択された奇数キャリアの信号がバッファ回路 5 2 に蓄積されていく。

【 0 2 0 0 】

バッファ回路 5 2 はフィルタ装置 4 9 A で抽出された FFT・デスクランブル処理手段 4 4 に印加する信号が全て FFT・デスクランブル処理手段 4 4 に転送されるまで、フィルタ装置 4 9 B からの信号を蓄積し続ける。

【 0 2 0 1 】

FFT・デスクランブル処理手段 4 4 は、フィルタ装置 4 9 A から出力された高周波受信回路 4 2 で受信したサブキャリア数より少ないサブキャリア数について FFT 处理を行う回路として構成されている。すなわち、FFT・デスクランブル処理手段 4 4 は小型、高速動作可能に構成されている。FFT・デスクランブル処理手段 4 4 で FFT 处理などを行った後、図 1 ( A ) に図解したビット抽出回路 4 5、復号回路 4 6 などにおける処理が行われる。

20

【 0 2 0 2 】

バッファ回路 5 2 は、フィルタ装置 4 9 A からの偶数キャリアの信号が全て FFT・デスクランブル処理手段 4 4 に転送された後、スイッチ回路 5 0 を経由して FFT・デスクランブル処理手段 4 4 に蓄積した信号を FFT・デスクランブル処理手段 4 4 に転送する。

30

【 0 2 0 3 】

スイッチ回路 5 0 はフィルタ装置 4 9 A から FFT・デスクランブル処理手段 4 4 への信号転送が終わると、バッファ回路 5 2 からの信号を FFT・デスクランブル処理手段 4 4 に印加するように切り替わる。

【 0 2 0 4 】

フィルタ装置 4 9 B、バッファ回路 5 2 は、先に通過させなかった信号成分のうち本通信において必要となる信号成分を通過させた信号、たとえば、奇数キャリアを生成し、FFT・デスクランブル処理手段 4 4 に印加する。

【 0 2 0 5 】

FFT・デスクランブル処理手段 4 4 は、再度入力された信号を FFT 处理して受信シンボルを抽出し、ビット抽出回路 4 5 以降の回路の処理を行わせる。

40

【 0 2 0 6 】

図 2 0 に図解した受信装置の回路構成をとることにより、高周波受信回路 4 2 において受信したシンボルを FFT 处理するに本来必要な FFT 回路より小規模の回路で、受信シンボルの抽出が可能となる。

すなわち、図 2 0 の回路構成をとると、FFT・デスクランブル処理手段 4 4 の回路規模を小規模にすることができる。

【 0 2 0 7 】

図 2 0 に図解した回路構成は、受信シンボルを半分にデシメーションした場合を例示したが、フィルタ装置 4 9 A, 4 9 B における通過キャリアをさらに減縮することにより、4

50

分割、8分割などにすることができる。その結果、FFT・デスクランブル処理手段44の回路規模は一段と小型になる。

【0208】

本発明の通信システム、送信装置（送信機）30、受信装置（受信機）40、および、受信装置（受信機）40の一部を構成する信号成分分離装置、フィルタ装置は上述した構成に限らず、種々の変形態様、または、上述した実施の形態を適宜組み合わせることができる。

【0209】

以上、本発明の実施の形態として、無線通信システムを例示したが、本発明は無線通信システムに限らず、有線通信システムなどにも適用できる。

10

【0210】

【発明の効果】

本発明によればマルチキャリア変調信号を適切に分離可能な信号成分分離装置が提供できた。

【0211】

本発明によれば、1入力マルチキャリア変調信号群から $2^c$ （cは任意の整数）の信号群に信号を分離する信号成分分離装置が提供できた。

【0212】

本発明によれば、1入力マルチキャリア変調信号群から特定の1出力信号群に選択するフィルタ装置が提供できた。

20

【0213】

本発明によれば上記信号成分分離装置を有する適切な受信装置が提供できた。

本発明の受信装置は、FFTの回路規模を小型にすることができる、さらに、FFT処理が高速である。

【0214】

本発明によれば上記フィルタ装置を有する適切な受信装置が提供できた。

本発明の受信装置は、FFTの回路規模を小型化であり、FFT処理が高速である。

【0215】

本発明によれば、マルチキャリア変調を行う送信装置と上記受信装置とが協動する通信システムを提供できる。

30

【0216】

本発明によれば、マルチキャリア変調とその復調を行う通信方法が提供できた。

【図面の簡単な説明】

【図1】図1（A）、（B）は、本発明の通信システム、送信装置および受信装置、並びに、通信方法の1実施の形態としてのマルチキャリア変調方式としてOFDM方式を用いた、たとえば、DABシステムに適用するディジタル無線通信システムの構成図であり、図1（A）はOFDM方式の無線通信システムの送信装置の構成図であり、図1（B）はOFDM方式の無線通信システムの受信装置の構成図である。

【図2】図2（A）～（C）は、図1（A）に図解した送信装置の処理を示すグラフであり、図2（A）は、各チャネルで各自独立したシンボルストリームを示し、図2（B）は、図1（A）に図解したマルチプレクサの概略構成図であり、図2（C）は、マルチキャリア変調信号を示すグラフである。

40

【図3】図3は、図1（A）の送信装置による変調された複数チャネルのサブキャリアの並びを示すグラフである。

【図4】図4は、図1（B）に図解した信号成分分離装置の構成図である。

【図5】図5は、図4に図解した信号成分分離装置を構成する二分岐回路の構成図である。

【図6】図6は、図5に図解したシンボル遅延回路の態様を示す図である。

【図7】図7は、図5に図解した位相オフセット調整回路の態様を示す図である。

【図8】図8は、本発明の第2実施の形態としての受信装置の構成図である。

50

【図9】図9は、図8に図解したの周波数オフセット補償・除去回路の構成図である。

【図10】図10は、本発明の第3実施の形態としての受信装置の構成図である。

【図11】図11は、本発明の第4実施の形態の受信装置の概略構成図である。

【図12】図12は、図11に示したフィルタ装置の第1の実施の形態の構成図である。

【図13】図13は、図11のフィルタ装置の第2の実施の形態の構成図である。

【図14】図14は、図13に図解したフィルタ・デシメーション回路の構成図である。

【図15】図15は、図11に図解したフィルタ装置の第3の実施の形態の構成図である。

【図16】図16は、図11に図解したフィルタ装置の第4の実施の形態の構成図である。

10

【図17】図17は、図16に図解したフィルタ・デシメーション回路の構成図である。

【図18】図18は、図11に図解したフィルタ装置の第5の実施の形態の構成図である。

【図19】図19は、本発明の第5実施の形態の受信装置の構成図である。

【図20】図20は、本発明の第6実施の形態の受信装置の構成図である。

【図21】図21(A)、(B)は、マルチキャリア変調方式として、DABシステムなどに適用されるOFDM方式を用いたディジタル無線通信システムの一構成例を示す図であり、図21(A)は送信装置の構成図であり、図21(B)は受信装置の構成図である。

【図22】図22は、図21(A)の送信装置から出力されるマルチキャリア化されたシンボル列の例を示したグラフである。

20

【図23】図23は、マルチキャリア信号を分離する従来の第1の方法を示すグラフである。

【図24】図24は、マルチキャリア信号を分離する従来の第2の方法を示す受信装置の構成図である。

【図25】図25は、従来の一定周期のキャリアを抽出することを示すグラフである。

【符号の説明】

10・・・無線送信装置

11・・・符号化回路

12・・・シンボルマッピング回路

30

13・・・マルチプレクサ(信号多重化処理回路)

14・・・周波数インターリーブ回路

15・・・逆高速フーリエ変換(IFFT)

16・・・無線送信回路

17・・・アンテナ

20・・・無線受信装置

21・・・アンテナ

22・・・受信回路

23・・・高速フーリエ変換(FFT)

24・・・シンボル選択回路

40

25・・・ビット抽出回路

26・・・復号回路

30・・・送信装置(送信機)

31・・・符号化回路

32・・・シンボルマッピング回路

34・・・マルチプレクサ(信号多重化処理回路)

36・・・スクランブル処理・IFFT・ガードタイム付加

・窓かけ処理回路

38・・・送信回路

39・・・アンテナ

50

|                               |    |

|-------------------------------|----|

| 4 0 .. 受信装置（受信機）              |    |

| 4 1 .. 受信アンテナ                 |    |

| 4 2 .. 高周波受信回路                |    |

| 4 3 .. 信号成分分離装置               |    |

| 4 3 a .. シンボル遅延回路             |    |

| 4 3 b .. 位相オフセット調整回路          |    |

| 4 3 c .. 加算回路                 |    |

| 4 3 d .. 減算回路                 |    |

| 4 4 .. FFT・デスクランブル処理手段        |    |

| 4 5 .. ピット抽出回路                | 10 |

| 4 6 .. 復号回路                   |    |

| 4 7 .. 信号選択回路                 |    |

| 4 8 A , 4 8 B .. 周波数オフセット補償回路 |    |

| 4 8 1 .. 乗算器                  |    |

| 4 8 2 .. ジャイレータ（オシレータ）        |    |

| 4 8 3 .. シンボル並べ替え回路           |    |

| 4 9 .. フィルタ装置                 |    |

| 4 9 1 .. 信号成分分離装置（デマルチブレクサ）   |    |

| 4 9 2 .. シンボル群選択回路            |    |

| 4 9 3 .. 周波数オフセット補償・除去回路      | 20 |

| 4 9 4 .. サブキャリア選択回路           |    |

| 4 9 5 .. フィルタ・デシメーション回路       |    |

| 4 9 5 a .. シンボル遅延回路           |    |

| 4 9 5 b .. 位相オフセット調整回路        |    |

| 4 9 5 c .. 加算回路               |    |

| 4 9 6 .. 乗算器                  |    |

| 4 9 7 .. 通過サブキャリア選択信号出力回路     |    |

| 4 9 8 .. シンボル並べ替え回路           |    |

| 4 9 9 .. フィルタ・デシメーション回路       |    |

| 5 0 .. スイッチ回路                 | 30 |

| 5 2 .. バッファ回路                 |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図13】

【図11】

【図12】

【図14】

【図15】

【図16】

【図17】

【図19】

【図18】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

---

フロントページの続き

(56)参考文献 国際公開第00/003508 (WO, A1)

特開平11-041197 (JP, A)

特開2000-332722 (JP, A)

特開2001-223668 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04J 11/00