RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(A n'utiliser que pour les

commandes de reproduction).

**2 488 466**

A1

**DEMANDE

DE BREVET D'INVENTION**

(21)

**N° 81 11996**

(54) Circuit de synchronisation pour la réception de signaux MIC.

(51) Classification internationale (Int. Cl. <sup>3</sup>). H 04 L 7/00; G 08 C 19/28.

(22) Date de dépôt..... 18 juin 1981.

(33) (32) (31) Priorité revendiquée : *Italie, 30 juin 1980, n° 23104 A/80.*

(41) Date de la mise à la disposition du

public de la demande ..... B.O.P.I. — « Listes » n° 6 du 12-2-1982.

(71) Déposant : Société dite : ITALTEL SOCIETA ITALIANA TELECOMUNICAZIONI SPA, résidant

en Italie.

(72) Invention de : Roberto Delle Donne.

(73) Titulaire : *Idem* (71)

(74) Mandataire : Office Blétry,

2, bd de Strasbourg, 75010 Paris.

L'invention est relative à un circuit pour la synchronisation de la partie réceptrice d'un système de transmission pour signaux MIC (Modulation par Impulsions Codées) et plus précisément à une disposition de circuit qui est apte à vérifier et à signaler si les données reçues de la ligne sont synchrones avec la synchronisation locale (alignement de trame) pilotée par l'horloge obtenue (au moyen d'un circuit connu en soi) à partir desdites données, ainsi qu'à accomplir certains processus simples qui ont pour but de rétablir le synchronisme.

10 Dans une forme préférée de réalisation, l'invention est constituée par un circuit intégré qui comprend aussi des circuits aptes à mettre en évidence quelques autres situations de mauvais fonctionnement de la connexion, ainsi qu'un synchroniseur qui tire de l'horloge de ligne des signaux de synchronisation utilisés 15 dans le terminal MIC.

16 L'invention peut être utilisée utilement dans n'importe quel système MIC ; elle a toutefois été étudiée d'une manière spécifique pour faire fonction, avec une mémoire élastique, d'organe d'interface entre un système de transmission MIC et 20 un central à division de temps pour la commutation desdits canaux MIC, en particulier un central de transit d'un réseau pour la commutation intégrée de signaux téléphoniques et de signaux donnés.

25 Ce central de transit est décrit, par exemple, dans le brevet italien n° 1.037.256.

26 Suivant l'invention le circuit de synchronisation pour la réception de signaux MIC est caractérisé par le fait qu'il comprend en combinaison entre eux :

- des moyens de synchronisation aptes à tirer de l'horloge de ligne non seulement les signaux de synchronisation requis par la partie réceptrice du système MIC, mais aussi des signaux impulsifs coincidant avec le dernier bit du canal 0 de la trame A,

5 respectivement de la trame B ;

- des moyens d'alignement de trame aptes à relever, à la suite de la comparaison entre le signal des données provenant de la ligne et lesdits signaux impulsifs, le manque et le rétablissement du synchronisme de trame, produisant, respectivement 10 supprimant, une signalisation d'alarme ; les moyens d'alignement sont en outre aptes à produire, pendant la phase de rétablissement du synchronisme, un signal apte à remettre à zéro lesdits moyens de synchronisation ;

- des moyens de révélation d'alarme aptes à relever, en 15 comparant entre eux le signal des données provenant de la ligne, lesdits signaux impulsifs et des signaux produits dans lesdits moyens d'alignement de trame, la présence et la cessation d'un critère d'alarme envoyé par le terminal MIC éloigné ainsi que les mauvais fonctionnements dans la connexion MIC.

- 20 L'invention sera mieux décrite avec référence à un exemple de réalisation non limitatif décrit dans les figures dans lesquelles :

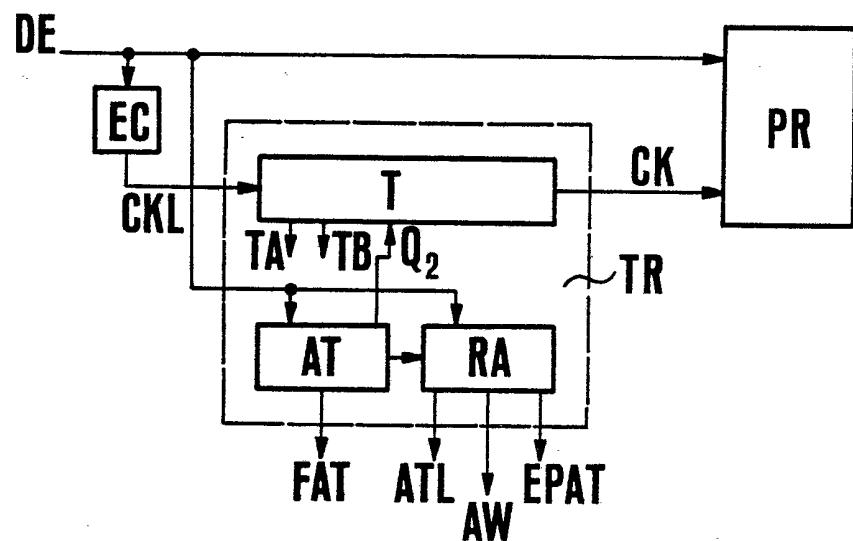

- la figure 1 représente le diagramme à blocs d'un circuit intégré suivant l'invention ;

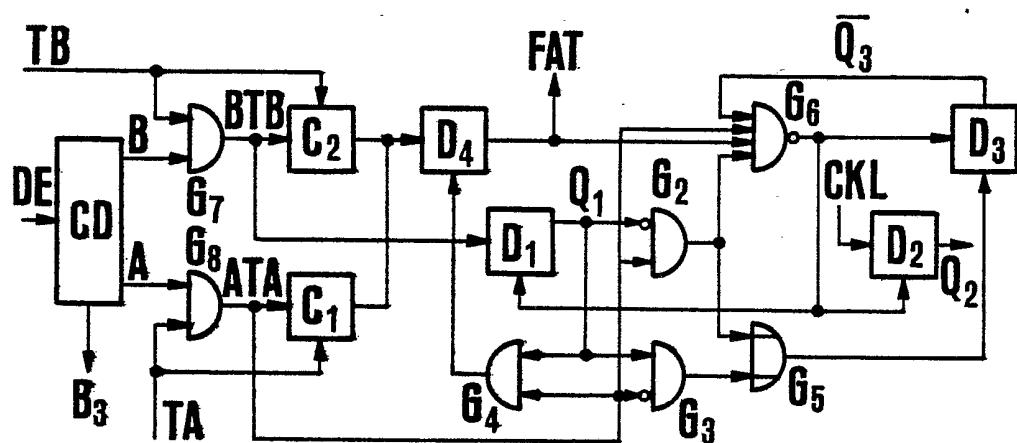

- 25 - la figure 2 représente le diagramme à blocs du circuit d'alignement de trame (AT) ;

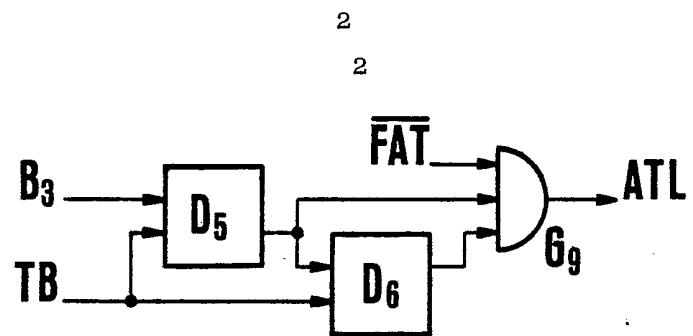

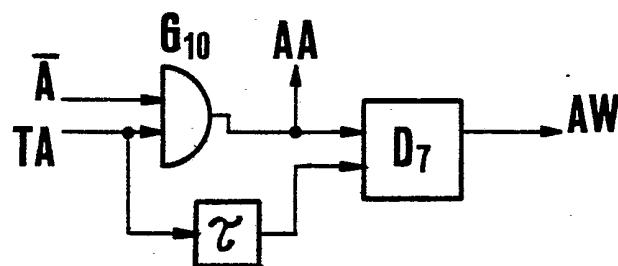

- les figures 3-5 représentent les diagrammes à blocs des circuits révélateurs des alarmes (RA).

- 30 Dans le diagramme à blocs de la figure 1 on a indiqué le circuit de synchronisation TR suivant l'invention qui reçoit les données en entrée DE de la ligne et l'horloge de ligne CKL d'un circuit d'extraction d'horloge EC, non décrit ici parce qu'il est connu en soi et que, de toutes façons, il est étranger à cette description.

- 35 Dans le circuit de synchronisation TR on a distingué :

- un synchroniseur T, connu en soi, qui fournit des signaux de synchronisation CK à la partie réceptrice du système MIC (indiquée dans la figure par le bloc PR) et qui produit en outre

deux impulsions  $T_A$ ,  $T_B$  en coïncidence avec le dernier bit du canal 0 de la trame A, respectivement de la trame B : ces impulsions sont utilisées dans le circuit TR comme cela sera mieux décrit ci-dessous ;

- 5 - un circuit d'alignement de trame AT qui vérifie le synchronisme correct entre les données reçues DE et les sorties du synchroniseur T, produisant le signal FAT pendant tout le temps où ce synchronisme n'existe pas ; dans le cadre de la procédure pour rétablir le synchronisme, qui sera décrit avec référence à la figure 2, AT produit un signal  $Q_2$  qui met à zéro le synchroniseur T ;

- 10 - les circuits RA aptes à relever le mauvais fonctionnement de la connexion produisant les alarmes ATL (alarme du terminal éloigné), AW (contenu du canal 0 de la trame TA erroné), EPAT (taux d'erreur en ligne trop élevé) ; ces circuits RA utilisent non seulement les signaux  $T_A$  et  $T_B$ , mais aussi des signaux produits dans le circuit d'alignement AT, comme cela sera mieux indiqué par la suite.

20 Dans la figure 2 on a illustré le circuit d'alignement de trame AT. On sait que les configurations des octets qui constituent les canaux 0 des trames A (parole A) et B (parole B) sont normalisées ; même la procédure adaptée pour reconnaître la perte et le rétablissement de l'alignement de trame a été fixée à un niveau international, c'est-à-dire :

- 25 - on considère l'alignement comme étant perdu si, trois fois de suite, la parole A dans la trame A ou la parole B dans la trame B ne sont pas reconnues ;

- on considère l'alignement comme étant récupéré si la parole A dans la trame A, la parole B dans la trame B et la parole A dans la trame A sont successivement reconnues ;

- 30 - si, une fois que la parole A dans la trame A a été reconnue, on ne reconnaît pas la parole B dans la trame B, la recherche reprend depuis le début une trame après.

35 Le diagramme de la figure 2 représente une disposition de circuit apte à effectuer ladite procédure.

La perte du synchronisme est reconnue au moyen des circuits de décodage CD qui reconnaissent dans les données en entrée DE les paroles A et B. Le signal TA fait avancer un compteur pour trois  $C_1$  et, en même temps, il rend possible le transit

à travers la porte  $G_8$  du signal A qui met à zéro  $C_1$ . Si au cours de trois trames consécutives (trois impulsions TA) la parole A n'est pas reconnue dans le canal 0 de la trame A (c'est-à-dire si  $ATA = 0$ )  $C_1$  fait commuter le bistable  $D_4$  qui produit, entre autres, l'alarme FAT. Il en est de même pour la parole B ( $G_7$ ,  $C_2$  ; TB, BTB).

L'alarme ( $FAT = 1$ ) autorise le transit à travers la porte  $G_6$  de l'impulsion ATA successive qui fait commuter le bistable  $D_3$  (interdisant  $G_6$ ) et remet à zéro les bilstables  $D_1$  ( $Q_1 = 0$  rend apte la porte  $G_2$  et interdit les portes  $G_3$  et  $G_4$ ) et  $D_2$  qui fait passer une impulsion ( $Q_2$ ) de l'horloge de ligne CKL qui remet à zéro la minuterie T établissant un alignement provisoire.

Une fois que la première phase de la procédure pour la récupération du synchronisme est accomplie, les alternatives suivantes sont possibles :

- a) Dans la trame successive la parole B n'est pas reconnue (BTB = 0).  $D_1$  ne commute pas et l'impulsion ATA successive traverse  $G_2$  et  $G_5$  et remet à zéro  $D_3$  (rendant ensuite apte  $G_6$ ) : la situation préexistante a été rétablie et la procédure de récupération du synchronisme repart à zéro ( $FAT = 1$ ) ;

- b) la parole B est reconnue.  $BTB = 1$  fait commuter  $D_1$  ( $Q_1 = 1$ ) interdisant  $G_2$  et rendant aptes  $G_3$  et  $G_4$  ;

- b<sub>1</sub>) la parole A successive n'est pas reconnue :  $ATA = 1$ , en passant à travers  $G_3$  et  $G_5$ , remet à zéro  $D_3$  qui rend apte  $G_6$  et la procédure de recherche du synchronisme repart à zéro ;

- b<sub>2</sub>) la parole A successive est reconnue :  $ATA = 1$  passe à travers  $G_4$  remettant à zéro  $D_4$  et faisant cesser l'alarme FAT.

Les figures 3, 4 et 5 décrivent les circuits indiqués globalement par RA, dans la figure 1 et aptes à produire les alarmes ATL, AW, EPAT.

Le circuit de la figure 3 reconnaît l'alarme envoyée par le terminal éloigné ATL, cette alarme étant constituée par un "1" comme troisième bit de la parole B au cours de deux trames successives.

Le circuit comprend deux bilstables en cascade ( $D_5$ ,  $D_6$ ) qui sont commutés par le signal TB et qui sont rendus aptes par le

troisième bit de la parole B ( $B_3$ ), tiré des circuits de décodage CD de la figure 2, respectivement du signal présent à la sortie de  $D_5$ . Puisque l'alarme ATL n'a pas de sens si le récepteur MIC est hors d'alignement, la porte  $G_9$ , à laquelle sont connectées les sorties des bistables  $D_5$  et  $D_6$  est interdite par l'alarme FAT.

Le circuit de la figure 4 est relatif à la production de l'alarme AM qui indique le manque de reconnaissance de la parole A dans le canal 0 de la trame A ( $TA = 1$ ).

Il se compose essentiellement d'un bistable  $D_7$  qui, à chaque impulsion de synchronisation, transfère à sa sortie la valeur logique de son entrée des données, c'est-à-dire du signal AA présent à la sortie d'une porte  $G_{10}$  aux entrées de laquelle sont appliqués les signaux A et TA. Le signal de synchronisation est obtenu en retardant, au moyen du circuit  $\tau$ , le signal TA pendant un temps plus grand que le temps nécessaire pour la commutation éventuelle de la valeur logique du signal AA.

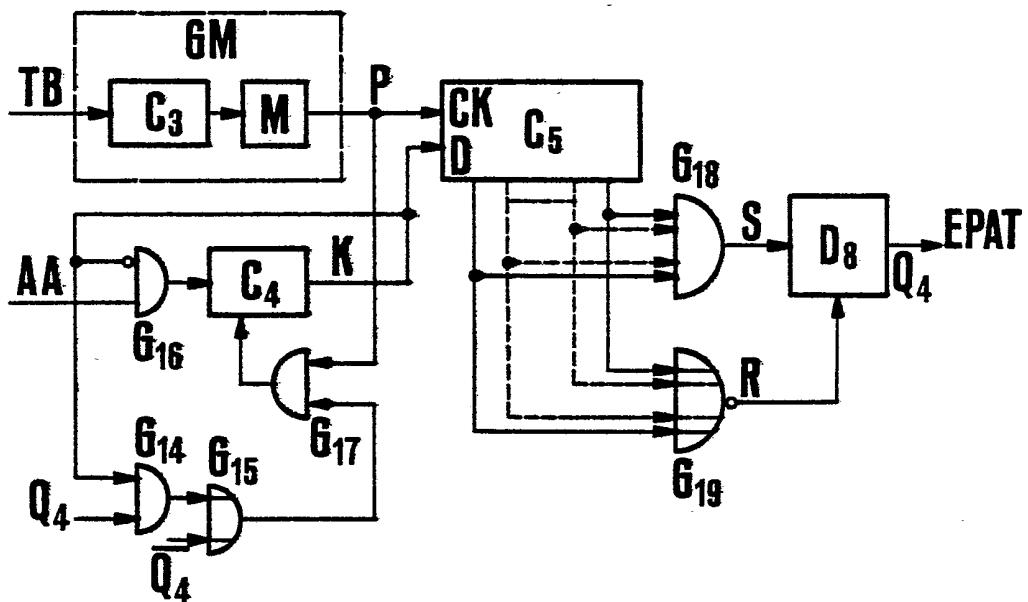

Dans la figure 5 on a illustré schématiquement le circuit TE qui contrôle le taux d'erreur, en produisant l'alarme EPAT lorsque  $n$  fois de suite la parole A n'est pas reconnue au moins  $m$  fois en un temps P préétabli ; l'alarme cesse lorsque la parole A n'est pas reconnue moins de  $m$  fois dans le temps  $n$  P.

Le temps P est défini par deux impulsions consécutives d'une séquence émise par un générateur GM de marques de temps constitué, dans l'exemple indiqué dans la figure, par un compteur  $C_3$  dont l'avance est provoquée par les impulsions TB (ou TA) que pilote un monostable M.

Les impulsions AA (non reconnaissance de la parole A) sont comptées par un compteur pour  $m$   $C_4$  qui, lorsqu'il a complété sa capacité, amène à "1" sa sortie K faisant avancer d'un pas le compteur pour  $n$   $C_5$  et interdisant le passage d'autres impulsions AA à travers la porte  $G_{16}$  jusqu'au moment où il est remis à zéro par la séquence P.

Le compteur  $C_5$ , une fois qu'il a épuisé sa capacité de comptage, commute le bistable  $D_8$  dont la sortie  $Q_4 = 1$  constitue le signal d'alarme EPAT.

En l'absence d'alarme la porte  $G_{17}$  est rendue apte à faire passer les impulsions de remise à zéro P par le fait que  $Q_4 = 1$  ; en présence d'alarme  $Q_4 = 1$  rend apte la porte  $G_{14}$  : si

dans le temps préétabli (n P) le compteur  $C_4$  épouse sa capacité de comptage, son signal de sortie ( $K = 1$ ) passe d'un côté à travers  $G_{14}$  et  $G_{15}$  et rend apte  $G_{17}$  à faire passer l'impulsion P successive qui remet à zéro  $C_4$ , de l'autre il fait avancer  $C_5$  empêchant que le bistable  $D_8$  soit ramené à zéro.

5 Dans une forme préférée de réalisation illustrée dans la figure, le compteur  $C_5$  est constitué par un registre à décalage à n positions, ayant comme horloge la séquence P et comme données la sortie K du compteur  $C_4$  : la condition d'alarme 10 ( $Q_4 = 1$ ) se traduit par le fait, reconnu au moyen de la porte  $G_{18}$ , que dans toutes les cellules de  $G_5$  on a enregistré un "1" (n fois de suite  $C_4$  a compté au moins m impulsions AA en un temps P) ; la condition de fin d'alarme, reconnue au moyen du circuit NOR  $G_{19}$ , se traduit par le fait que dans toutes les 15 cellules de  $C_5$  on a enregistré un "0" (dans le temps n P le compteur  $C_4$  a compté moins de m impulsions AA et n'a été en mesure de charger un "1" dans aucune cellule du registre à décalage  $C_5$ ).

20 Sans sortir des limites de l'invention il est possible d'apporter aux circuits indiqués des variantes suggérées par les connaissances et par l'expérience qui constituent un bagage commun pour le technicien de la branche.

- REVENDICATIONS -

1. Circuit de synchronisation pour la réception de signaux MIC, caractérisé par le fait qu'il comprend en combinaison entre eux : des moyens de synchronisation (T) aptes à tirer de l'horloge de ligne (CKL) non seulement les signaux de synchronisation (CK) requis par la partie réceptrice (PR) du système MIC, mais aussi des signaux impulsifs ( $T_A$ ,  $T_B$ ) coïncidant avec le dernier bit du canal 0 de la trame A, respectivement de la trame B des moyens d'alignement de trame (AT) aptes à relever, à la suite de la comparaison entre le signal des données provenant de la ligne (DE) et lesdits signaux impulsifs ( $T_A$ ,  $T_B$ ), le manque et le rétablissement du synchronisme de trame, produisant, respectivement supprimant une signalisation d'alarme (FAT), lesdits moyens d'alignement (AT) étant en outre aptes à produire, pendant la phase de rétablissement du synchronisme, un signal ( $Q_2$ ) apte à remettre à zéro lesdits moyens de synchronisation (T) ; des moyens de révélation d'alarmes (RA) aptes à relever, en comparant entre eux le signal des données provenant de la ligne (DE), lesdits signaux impulsifs ( $T_A$ ,  $T_B$ ) et des signaux produits dans lesdits moyens d'alignement de trame (AT), la présence et la cessation d'un critère d'alarme (ATL) envoyé par le terminal MIC éloigné ainsi que les mauvais fonctionnements dans la connexion MIC.

2. Circuit de synchronisation suivant la revendication 1, caractérisé par le fait que les moyens d'alignement de trame (AT) comprennent des circuits de décodage (CD) aptes à révéler dans le signal des données (DE) provenant de la ligne les paroles A et B ; un premier et un deuxième compteur pour trois ( $C_1$ ,  $C_2$ ), aptes à compter lesdits signaux impulsifs ( $T_A$ ,  $T_B$ ), remis à zéro par les signaux (ATA, BTB) présents à la sortie d'un premier ( $G_8$ ),

respectivement d'un deuxième circuit porte ( $G_7$ ), aux entrées desquels sont appliqués la parole A et un desdits signaux impulsifs (TA), respectivement la parole B et l'autre signal impulsif (TB) ; un premier bistable ( $D_4$ ) qui est commuté par les signaux présents à la sortie du premier et du deuxième compteur ( $C_1$ ,  $C_2$ ), la sortie du premier bistable ( $D_4$ ) constituant la signalisation d'alarme (FAT) et rendant apte un troisième circuit porte ( $G_6$ ) ; ledit troisième circuit porte ( $G_6$ ) aux autres entrées duquel sont connectées la sortie (ATA) du premier circuit porte ( $G_8$ ), 5 la sortie d'un quatrième circuit porte ( $G_2$ ) et la sortie ( $Q_3$ ) d'un deuxième bistable ( $D_3$ ), la sortie du troisième circuit porte ( $G_6$ ) faisant commuter le deuxième bistable ( $D_3$ ) et remettant à zéro un troisième ( $D_2$ ) et un quatrième bistable ( $D_1$ ) ; ledit deuxième bistable ( $D_3$ ) dont la commutation interdit le troisième 10 circuit porte ( $G_6$ ) ; ledit troisième bistable qui est commuté par l'horloge de ligne (CKL) pour produire un signal impulsif ( $Q_2$ ) qui remet à zéro les moyens de synchronisation (T) ; ledit quatrième bistable ( $D_1$ ) qui est commuté par le signal (BTB) présent à la sortie de la deuxième porte ( $G_7$ ), la sortie ( $Q_1$ ) du 15 quatrième bistable ( $D_1$ ) rendant apte une cinquième porte ( $G_4$ ) et une sixième porte ( $G_3$ ) et, inversée, la quatrième porte ( $G_2$ ) ; ladite quatrième porte ( $G_2$ ) dont la deuxième entrée est connectée à la sortie de la première porte ( $G_8$ ) ; ladite cinquième porte ( $G_4$ ) dont la deuxième entrée est connectée à la sortie de ladite 20 première porte ( $G_8$ ) et dont la sortie remet à zéro le premier bistable ( $D_4$ ) ; ladite sixième porte ( $G_3$ ) dont la deuxième entrée inversée est connectée à la sortie de la première porte ( $G_8$ ) et dont la sortie s'additionne à la sortie de la quatrième porte ( $G_2$ ) pour remettre à zéro le deuxième bistable ( $D_3$ ). 25

30 3. Circuit de synchronisation suivant la revendication 1, caractérisé par le fait que le circuit faisant partie des moyens de révélation d'alarmes (RA) et apte à révéler le critère d'alarme (ATL) envoyé par le terminal MIC éloigné comprend un cinquième ( $D_5$ ) et un sixième bistable ( $D_6$ ) qui sont commutés par le signal impulsif (TB) associé à la trame B, le cinquième bistable ( $D_5$ ) étant rendu apte par le troisième bit ( $B_3$ ) de la parole B, le 35 sixième bistable ( $D_6$ ) étant rendu apte par la sortie du cinquième bistable ( $D_5$ ), les sorties du cinquième et du sixième bistable

étant connectées à deux entrées d'une septième porte ( $G_9$ ) à la troisième entrée de laquelle, inversée, est appliquée la signalisation d'alarme (FAT) produite par les moyens d'alignement de trame (AT), la sortie de la septième porte ( $G_9$ ) constituant le critère d'alarme (ATL).

5 4. Circuit de synchronisation suivant les revendications 2 et 3, caractérisé par le fait que le troisième bit de la parole B ( $B_3$ ) est extrait des données provenant de la ligne par les circuits de décodage (CD) faisant partie des moyens d'alignement de trame (AT).

10 5. Circuit de synchronisation suivant la revendication 1, caractérisé par le fait que le circuit faisant partie des moyens de révélation d'alarmes (RA) et apte à relever la non reconnaissance de la parole A dans le canal 0 de la trame A comprend une huitième porte ( $G_{10}$ ) aux entrées de laquelle sont appliqués le signal impulsif (TA) relatif à la trame A et un signal ( $\bar{A}$ ) indiquant la non reconnaissance de la parole A et dont la sortie (AA) est connectée à l'entrée des données d'un septième bistable ( $D_7$ ) dont l'horloge est obtenue en retardant le signal impulsif (TA), la sortie du septième bistable assumant à chaque coup d'horloge le niveau logique présent à l'entrée des données.

15 6. Circuit de synchronisation suivant les revendications 2 et 5, caractérisé par le fait que le signal ( $\bar{A}$ ) appliqué à l'entrée de la huitième porte ( $G_{10}$ ) est obtenu en inversant le signal (A) produit par les circuits de décodage (CD) faisant partie des moyens d'alignement de trame (AT).

20 7. Circuit de synchronisation suivant la revendication 1, caractérisé par le fait que le circuit (TE) faisant partie des moyens de révélation d'alarmes (RA) et apte à relever un taux d'erreur supérieur à un maximum préétabli active sa propre sortie si  $n$  fois de suite la parole A n'est pas reconnue au moins  $m$  fois en un premier temps (P) préétabli et désactive ladite sortie si la parole A n'est pas reconnue au moins  $m$  fois en un deuxième temps préétabli,  $n$  fois plus grand que ledit premier temps P.

25 8. Circuit de synchronisation suivant la revendication 7, caractérisé par le fait que ledit circuit (TE) comprend un générateur (GM) débitant une séquence d'impulsions définissant ledit premier temps (P) ; un troisième compteur pour  $m$  ( $C_4$ ) apte à

compter des impulsions (AA), indiquant la non reconnaissance de la parole A, qui parviennent à son entrée à travers une neuvième porte ( $G_{16}$ ) à la deuxième entrée de laquelle, inversée, est appliqué le signal (K) présent à la sortie du troisième 5 compteur ( $C_4$ ) ; un registre à décalage ( $C_5$ ) comprenant n cellules, dont l'entrée des données est connectée à la sortie (K) du troisième compteur et dont l'entrée de synchronisation est connectée au générateur (GM) ; un premier ( $G_{18}$ ) et un deuxième décodeur ( $G_{19}$ ) connectés aux cellules du registre à décalage et aptes à faire commuter, respectivement remettre à zéro, un 10 huitième bistable ( $D_8$ ) lorsque toutes les cellules sont présentes "1", respectivement "0", la sortie ( $Q_4$ ) du huitième bistable ( $D_8$ ) constituant la sortie dudit circuit (EPAT) ; une deuxième porte ( $G_{14}$ ) rendue apte par le signal ( $Q_4$ ) présent à la sortie du 15 huitième bistable ( $D_8$ ), dont la deuxième entrée est connectée à la sortie du troisième compteur ( $C_4$ ) et dont la sortie s'additionne au signal ( $\bar{Q}_4$ ) présent à la sortie inversée du huitième bistable ( $D_8$ ), pour rendre apte une onzième porte ( $G_{17}$ ) ; ladite 20 onzième porte ( $G_{17}$ ) dont la deuxième entrée est connectée à la sortie du générateur (GM) et dont la sortie remet à zéro le troisième compteur ( $C_4$ ).

9. Circuit de synchronisation suivant les revendications 1 et 8, caractérisé par le fait que le générateur (GM) comprend un quatrième compteur ( $C_3$ ), qui est amené à avancer par un des signaux impulsifs ( $T_A, T_B$ ) produits par les moyens de 25 synchronisation (T), que pilote un monostable (M).

10. Circuit de synchronisation suivant les revendications 5 et 8, caractérisé par le fait que la première entrée de la neuvième porte ( $G_{16}$ ) est connectée à la sortie de la 30 huitième porte ( $G_{10}$ ).

11. Circuit de synchronisation suivant l'une quelconque des revendications précédentes, caractérisé par le fait qu'il peut être réalisé en une seule unité à circuit intégré.

1

2

fig.1

fig.2

2488466

fig.3

fig.4

fig.5