(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4761906号

(P4761906)

(45) 発行日 平成23年8月31日(2011.8.31)

(24) 登録日 平成23年6月17日(2011.6.17)

(51) Int.Cl.

G06F 17/50 (2006.01)

F 1

G06F 17/50 668S

G06F 17/50 668C

G06F 17/50 668X

請求項の数 4 (全 19 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2005-279917 (P2005-279917) |

| (22) 出願日  | 平成17年9月27日 (2005.9.27)       |

| (65) 公開番号 | 特開2007-94512 (P2007-94512A)  |

| (43) 公開日  | 平成19年4月12日 (2007.4.12)       |

| 審査請求日     | 平成20年6月13日 (2008.6.13)       |

|           |                                                        |

|-----------|--------------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部 1753 番地 |

| (74) 代理人  | 100088672<br>弁理士 吉竹 英俊                                 |

| (74) 代理人  | 100088845<br>弁理士 有田 貴弘                                 |

| (72) 発明者  | 吉川 篤志<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内              |

審査官 松浦 功

最終頁に続く

(54) 【発明の名称】半導体集積回路の設計方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のノードの接続によって構成され、クロック信号の伝達経路となるクロック系バスおよびデータ信号の伝達経路となるデータ系バスを有した半導体集積回路の設計方法であつて、

(a) 前記クロック系バスおよび前記データ系バスを1つのバスとして統合し、統合されたバスを構成する前記複数のノードのランダムばらつき成分の標準偏差を算出するステップと、

(b) 前記ランダムばらつき成分の標準偏差と、前記統合されたバスを構成する前記複数のノードのシステムティックばらつき成分の標準偏差とに基づいてチップ内ばらつき成分の標準偏差を算出するステップと、

(c) 前記チップ内ばらつき成分と、前記統合されたバス全体の基準遅延とに基づいて、遅延変動を算出するステップと、を備える、半導体集積回路の設計方法。

## 【請求項 2】

前記ステップ(a)は、

前記複数のノードのそれぞれのランダムばらつき成分に、遅延の重み付けを行つて前記ランダムばらつき成分の標準偏差を算出する、請求項1記載の半導体集積回路の設計方法。

## 【請求項 3】

前記複数のノードは、固定遅延成分を有した多段構成のノードを含み、

前記ステップ( a )は、

前記多段構成のノードを、各段で分割してそれぞれ個別ノードとし、前記個別ノードについて前記ランダムばらつき成分の標準偏差の算出に組み込む、請求項 1 記載の半導体集積回路の設計方法。

**【請求項 4】**

( d )前記チップ内ばらつき成分に、他のチップのばらつき成分を含めた、全てのばらつきを含む成分の標準偏差を算出するステップと、

( e )前記チップ内ばらつき成分の標準偏差の最大値が、前記全てのばらつきを含む成分の標準偏差の最大値を越えないように、前記チップ内ばらつき成分の標準偏差のカバー範囲を設定するステップとを更に備える、請求項 1 記載の半導体集積回路の設計方法。 10

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本発明は半導体集積回路の設計方法に関し、特に統計的な手法を用いたタイミング解析を利用した設計方法に関する。

**【背景技術】**

**【0 0 0 2】**

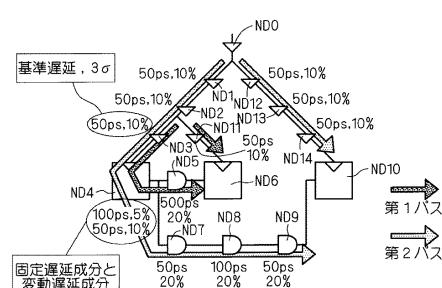

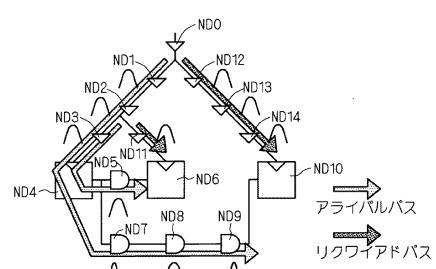

図 1 1 には、半導体集積回路のタイミング解析の一手法として知られているスタティックタイミング解析 ( S T A : Static Timing Analysis ) の概念を説明する模式図を示す。 20

**【0 0 0 3】**

図 1 1 においては、 N D 0 ~ N D 1 4 までの 1 5 個のノードを有する半導体集積回路を例に採って示している。ここで、ノードとは遅延を持つ素子と定義し、論理ゲートや配線などがこれに含まれ、ノード N D 4 、 N D 6 および N D 1 0 はフリップフロップを、ノード N D 5 、 N D 7 ~ N D 9 はアンド論理ゲートを、その他は特に限定しない論理ゲートを想定している。

**【0 0 0 4】**

スタティックタイミング解析は、素子特性のばらつきのうち、チップ内 ( On Chip ) ばらつき ( O C V ) により生じる遅延変動を補正するように設定した係数により解析結果を表現するものであり、図 1 1 に示すように、アライバルパス ( データ系パス ) とリクワイアドパス ( クロック系パス ) のそれぞれに対して、各ノードの基準遅延に掛ける補正係数を算出する。 30

**【0 0 0 5】**

図 1 1 においては、アライバルパスは、ノード N D 0 から始まってノード N D 1 ~ N D 4 、 N D 7 ~ N D 9 を経由してノード N D 1 0 に至る経路と、ノード N D 2 から始まって、ノード N D 3 ~ N D 5 を経由してノード N D 6 に至る経路との 2 つを有し、リクワイアドパスは、ノード N D 0 から始まってノード N D 1 2 ~ N D 1 4 を経由してノード N D 1 0 に至る経路と、ノード N D 2 から始まって、ノード N D 1 1 を経由してノード N D 6 に至る経路との 2 つを有している。

**【0 0 0 6】**

アライバルパスおよびリクワイアドパスには係数を個別に与えることができ、図 1 1 においては、チップ内ばらつきを  $\pm 6\%$  と考えて、アライバルパスは基準遅延  $\times 1.06$  ( $+ 6\%$ ) 、リクワイアドパスは基準遅延  $\times 0.94$  ( $- 6\%$ ) と設定した解析例を示している。 40

**【0 0 0 7】**

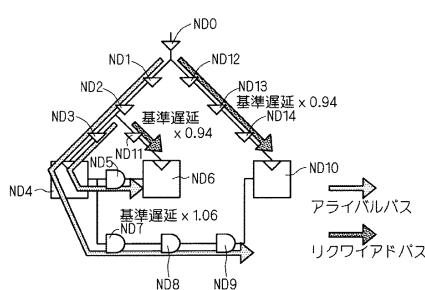

また、図 1 2 にはタイミング解析の他の手法として知られている統計的 S T A の概念を説明する模式図を示す。

**【0 0 0 8】**

なお、図 1 2 においては、図 1 1 に示した半導体集積回路と同じノード構成を有するものとし、図 1 1 に示した半導体集積回路と同一の構成については同一の符号を付し、重複する説明は省略する。 50

**【 0 0 0 9 】**

図12に示すように、統計的STAでは、ばらつきを考慮した遅延を分布として扱うものであり、各ノードにおける遅延は正規分布と仮定することにより、遅延を平均値と標準偏差で表現し、正規分布の伝播解析を行う。

**【 0 0 1 0 】**

半導体プロセスの微細化に伴って、チップ内ばらつきの成分、その中でも特にランダムに生じるばらつき成分が大きくなると考えられている。そのため、あらゆる回路構成をカバーするように設計時にチップ内ばらつきの値を過大に設定すれば、必要以上のマージンを確保してしまう可能性があるため、半導体集積回路の性能や設計収束性が低下すると考えられる。

10

**【 0 0 1 1 】**

逆に設計時にチップ内ばらつきの値を過小に設定すれば、必要なマージンが確保できない可能性があるため、誤動作する可能性が高くなると考えられる。

**【 0 0 1 2 】**

図11を用いて説明したように、従来的なスタティックタイミング解析では、チップ内ばらつきの補正係数を一定値に仮定するため、回路構成によって統計学的に相殺されるランダムばらつきの成分を正確に与えることはできない。

**【 0 0 1 3 】**

また、特許文献1に開示されるように、ランダムばらつきの成分をセル段数（ゲート段数）に応じて計算する手法も提案されているが、アライバルパスとリクワイアドパスを個別に考慮するため、不要なマージンを含むと考えられる。

20

**【 0 0 1 4 】**

一方、統計的STAでは、遅延を正規分布で表し、ランダムばらつきの成分などを統計学的に考慮するため、より現実的な計算結果となる。しかしながら、STAに比べて処理時間が大きくなることから、現状は大規模半導体集積回路の設計に利用することはできない。

**【 0 0 1 5 】**

【特許文献1】特開2005-122298号公報（図3、図4）

**【発明の開示】****【発明が解決しようとする課題】**

30

**【 0 0 1 6 】**

本発明は上記のような問題点を解消するためになされたもので、設計時に、より現実的なプロセスばらつきを考慮でき、必要以上の設計マージンを設定することなく、半導体集積回路の性能向上や設計収束性が期待でき、また必要なマージンの確保によって品質向上も期待できるとともに、計算が簡単で高速処理が可能な設計方法を提供することを目的とする。

**【課題を解決するための手段】****【 0 0 1 7 】**

本発明に係る請求項1記載の半導体集積回路の設計方法は、複数のノードの接続によって構成され、クロック信号の伝達経路となるクロック系バスおよびデータ信号の伝達経路となるデータ系バスを有した半導体集積回路の設計方法であって、前記クロック系バスおよび前記データ系バスを1つのバスとして統合し、統合されたバスを構成する前記複数のノードのランダムばらつき成分の標準偏差を算出するステップ(a)と、前記ランダムばらつき成分の標準偏差と、前記統合されたバスを構成する前記複数のノードのシステムティックばらつき成分の標準偏差とに基づいてチップ内ばらつき成分の標準偏差を算出するステップ(b)と、前記チップ内ばらつき成分と、前記統合されたバス全体の基準遅延とに基づいて、遅延変動を算出するステップ(c)とを備えている。

40

**【発明の効果】****【 0 0 1 9 】**

本発明に係る請求項1記載の半導体集積回路の設計方法によれば、クロック系バスおよ

50

びデータ系バスを1つのバスとして統合し、統合されたバスを構成する複数のノードのランダムばらつき成分の標準偏差を算出し、当該チップ内ばらつき成分と、統合されたバス全体の基準遅延とに基づいて、遅延変動を算出するので、半導体集積回路の設計時に、チップ内のランダムばらつき成分を、より現実的な値として得ることができるので、必要以上の設計マージンを設定することなく半導体集積回路の性能向上や設計収束性が期待でき、また必要なマージンの確保によって品質向上も期待できるとともに、計算が簡単で高速処理が可能となる。

#### 【発明を実施するための最良の形態】

##### 【0021】

<実施の形態>

10

##### <A. 発明の基本概念>

まず、本発明に係る半導体集積回路の設計方法の基本概念について説明する。

半導体プロセスに起因する半導体素子特性のばらつきの成分を分類して、各ばらつき成分によって生じる遅延変動の割合（平均遅延に対するずれ）を正規分布と想定して、以下のように標準偏差で表す。

##### 【0022】

すなわち、半導体チップ（以下、チップと呼称）内の複数のノードが有するランダムばらつき成分の標準偏差を  $r$ 、チップ内の複数のノードが有するシステムティックばらつき成分の標準偏差を  $s$ 、他のチップ（Off Chip）のばらつき成分の標準偏差を  $f$ とする。なお、以下においては、便宜的に  $r$ 、 $s$ 、 $f$ をランダムばらつき成分、システムティックばらつき成分、他のチップのばらつき成分と呼称する。

20

##### 【0023】

ここで、ランダムばらつき成分とは、例えば、隣り合う半導体素子間で明確な特性の相違を呈する成分であり、システムティックばらつき成分とは、隣り合う半導体素子間では明確な特性の相違は呈さないものの、ある程度離れた位置の半導体素子との間では明確な特性の相違を呈するような成分である。

##### 【0024】

また、他のチップのばらつき成分とは、同じウエハ上に形成されたチップ間での平均特性の相違や、異なるウエハ上に形成されたチップ間での平均特性の相違や、異なるロットで形成されたチップ間での平均特性の相違を呈するような成分である。

30

##### 【0025】

各ばらつき成分の分布を正規分布と仮定すると、全てのばらつきを含む成分とチップ内のばらつき成分の標準偏差は、統計学的に以下のように定義することができる。

##### 【0026】

すなわち、全てのばらつきを含む成分の標準偏差（単に、全てのばらつきを含む成分と呼称する場合もあり）を  $a_{\text{all}}$  とすると、 $a_{\text{all}}$  は下記の式（1）で定義される。

##### 【0027】

##### 【数1】

$$\sigma_{\text{all}} = \sqrt{\sigma_r^2 + \sigma_s^2 + \sigma_f^2} \quad \cdots (1)$$

40

##### 【0028】

また、チップ内の全てのばらつき成分の標準偏差（単に、チップ内ばらつき成分と呼称する場合もあり）を  $\sigma_{\text{chip}}$  とすると、 $\sigma_{\text{chip}}$  は下記の式（2）で定義される。

##### 【0029】

##### 【数2】

$$\sigma_{\text{chip}} = \sqrt{\sigma_r^2 + \sigma_s^2} \quad \cdots (2)$$

##### 【0030】

50

ここで、チップ内ばらつき成分のうち、ランダムばらつき成分に着目する。

ランダムばらつき成分は、論理ゲートの回路構造や配線のパターンによって変動するため、各ノードに対して個別に値を定義する必要がある。なお、ノードとは遅延を持つ素子として定義され、論理ゲートや配線などに相当する。

#### 【0031】

また、各ノードのばらつきがバス全体に与える影響は各ノードの基準遅延（平均遅延）に依存するため、バス全体のばらつきを計算するために各ノードのランダムばらつき成分に遅延の重み付けをした計算式を用いる。

#### 【0032】

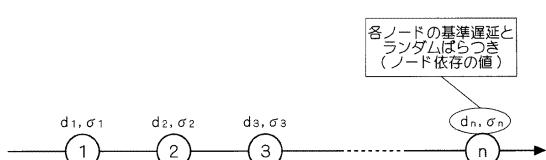

具体的には、図1に示すようなn個のノードを持つ半導体集積回路を想定する。なお、図1において、dnおよびnは、それぞれ各ノードにおける基準遅延およびランダムばらつきを示す。

#### 【0033】

図1に示すn個のノードを持つ半導体集積回路に対して、チップ内ランダムばらつき成分の標準偏差rを以下の数式(3)で表す。なお、数式(3)においては、i番目のノードの基準遅延およびランダムばらつき成分を、それぞれdiおよびriとして表す。

#### 【0034】

#### 【数3】

$$\sigma_r(n) = \sqrt{\frac{d_1^2 \times \sigma_1^2 + d_2^2 \times \sigma_2^2 + d_3^2 \times \sigma_3^2 + \cdots + d_{n-1}^2 \times \sigma_{n-1}^2 + d_n^2 \times \sigma_n^2}{d_1 + d_2 + d_3 + \cdots + d_{n-1} + d_n}}$$

$$= \sqrt{\frac{\sum_{i=1}^n d_i^2 \times \sigma_i^2}{\sum_{i=1}^n d_i}} \quad \cdots (3)$$

#### 【0035】

このような遅延の重み付けを行うことで、より現実的なランダムばらつき成分の標準偏差を得ることができる。

#### 【0036】

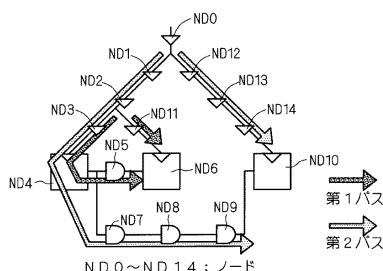

以下、本発明に係る半導体集積回路の設計方法として、数式(3)を利用した設計方法について、図2に示す半導体集積回路を例に採って説明する。

#### 【0037】

図2においては、ND0～ND14までの15個のノードを有する半導体集積回路を示しており、ノードND4、ND6およびND10はフリップフロップを、ノードND5、ND7～ND9はアンド論理ゲートを、その他は特に限定しない論理ゲートを想定している。

#### 【0038】

そして、図2においては、ノードND0から始まってノードND1～ND4、ND7～ND9を経由してノードND10に至る経路と、ノードND12～ND14を経由してノードND10に至る経路とを第2パスとして定義し、また、ノードND2から始まって、ノードND3～ND5を経由してノードND6に至る経路と、ノードND11を経由してノードND6に至る経路とを第1パスとして定義している。

#### 【0040】

そして、着目するバスのセットアップやホールドなどのタイミング検証は、アライバルバスとリクワイアドバスの遅延を求めて、その相対差から設計条件を設定する。

例えばセットアップ条件は、以下の数式(4)で定義する。

#### 【0041】

10

20

30

40

50

【数4】

アライバルパス-リクワイアドパス<クロック周期- $\alpha$  … (4)

【0042】

また、ホールド条件は、以下の式(5)で定義する。

【0043】

【数5】

アライバルパス-リクワイアドパス> $\beta$  … (5)

10

【0044】

なお、数値  $\alpha$  および  $\beta$  は、例えばフリップフロップのセットアップ時間およびホールド時間、また、クロックスキュー、ジッタなどの要素で決まる値であり、式(4)のセットアップ条件においてはアライバルパスとリクワイアドパスにおける遅延の相対差が、クロック周期よりも確実に小さくなるように、クロック周期から数値  $\alpha$  を差し引いた値で条件が設定されている。

【0045】

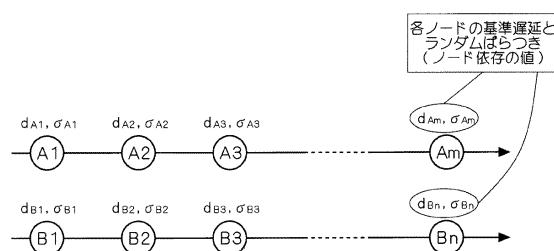

ここで、チップ内ばらつきを考慮すべき半導体集積回路は図3のように模式的に表現することができる。

20

【0046】

本発明に係る半導体集積回路の設計方法においては、図11および図12に示したように、従来は個別のバスとして取り扱っていたアライバルバス（データ信号の伝達経路となるデータ系バス）およびリクワイアドバス（クロック信号の伝達経路となるクロック系バス）を、統計学的な観点から1本のバスとして扱うことを発明の基本概念とする。図3において、ノードA1～Amまでのm個のノードで構成されるアライバルバスと、ノードB1～Bnまでのn個のノードで構成されるリクワイアドバスとに分けることができるが、本発明に係る半導体集積回路の設計方法によれば、アライバルバスおよびリクワイアドバスを、統計学的な観点から1本のバスとして扱うので、図3に示す半導体集積回路におけるランダムばらつき成分  $r(m,n)$  は以下の式(6)で表すことができる。

30

【0047】

【数6】

$$\sigma_r(m, n) = \sqrt{\frac{\sum_{i=1}^m d_{Ai}^2 \times \sigma_{Ai}^2 + \sum_{i=1}^n d_{Bi}^2 \times \sigma_{Bi}^2}{\sum_{i=1}^m d_{Ai} + \sum_{i=1}^n d_{Bi}}} \dots (6)$$

【0048】

40

なお、上記式(6)において、 $d_{Ai}$  および  $A_i$  は、それぞれアライバルバスの  $i$  番目のノードの遅延およびランダムばらつき成分を表し、 $d_{Bi}$  および  $B_i$  は、それぞれリクワイアドバスの  $i$  番目のノードの遅延およびランダムばらつき成分を表す。

【0049】

ここで、複数段のゲート回路を含む多段セルなどの多段構成のノードでは、初段のゲート回路の出力負荷は一定なので固定遅延成分を持つことになり、当該多段セルを1つのノードとして取り扱うと、正確なランダムばらつき成分  $r$ を得ることができない。

【0050】

このような場合、各段のゲート回路ごとに分割して個別ノードとして取り扱うことで、式(6)を適用することができ、正確なランダムばらつき成分  $r$ を得ることができる

50

。

## 【0051】

そして、数式(6)から得られるランダムばらつき成分  $r$ を数式(2)に代入することで、チップ内ばらつき成分  $\sigma_{chip}$ を得ることができ、その値からチップ内ばらつきによって生じる遅延変動  $D_{ocv}$ の値を決めることができる。遅延変動  $D_{ocv}$ は以下の数式(7)で表すことができる。

## 【0052】

## 【数7】

$$D_{ocv} = D_{base} \times \sigma_{chip} = (d_{A1} + d_{A2} + \dots + d_{Am} + d_{B1} + d_{B2} + \dots + d_{Bn}) \times \sigma_{chip}$$

10

$$= \left( \sum_{i=1}^m d_{Ai} + \sum_{i=1}^n d_{Bi} \right) \times \sigma_{chip} \quad \dots (7)$$

## 【0053】

なお、上記数式(7)において、 $D_{base}$ はパス全体（アライバルパス+リクワイアドパス）の基準遅延（平均遅延）を表し、各ノードの遅延の合計値で定義する。

## 【0054】

数式(7)で得られる値は、基準遅延に対してチップ内ばらつき成分  $\sigma_{chip}$ により生じる遅延変動分とを考えることができるので、半導体集積回路の設計時にこの値を利用するこことにより、チップ内ばらつきの成分を考慮することができる。

20

## 【0055】

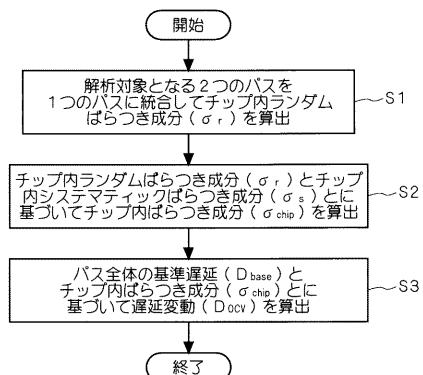

以上説明した、本発明に係る半導体集積回路の設計方法の基本概念を図4のフローチャートにまとめて示す。

## 【0056】

すなわち、図4に示すステップS1において、解析対象となる2つのパス（アライバルパスおよびリクワイアドパス）を、1つのパスとして統合し、当該1つのパス（統合パス）を構成する複数のノードについてチップ内ランダムばらつき成分（ $r$ ）を算出する。

## 【0057】

次に、ステップS2において、チップ内ランダムばらつき成分（ $r$ ）と、チップ内システムティックばらつき成分（ $s$ ）とに基づいてチップ内ばらつき成分  $\sigma_{chip}$ を算出する。

30

## 【0058】

その後、ステップS3において、パス全体の基準遅延（ $D_{base}$ ）と、チップ内ばらつき成分（ $\sigma_{chip}$ ）とに基づいて遅延変動（ $D_{ocv}$ ）を算出する。

なお、具体的な計算例については後に説明する。

## 【0059】

< B . 発明の適用例 >

次に、本発明に係る半導体集積回路の設計方法の適用例について説明する。

アライバルパスおよびリクワイアドパスを、統計学的な観点から1つのパスとして扱うことで、設計時にチップ内のランダムばらつき成分  $r$ を、より現実的な値（統計的STAに近い値）として得ることができる。

40

## 【0060】

チップ内のシステムティックばらつき成分  $s$ や、他のチップのばらつき成分  $f$ については従来的な手法でも現実的な値が得られるので、ランダムばらつき成分  $r$ のより現実的な値が得られれば、チップ内ばらつき成分  $\sigma_{chip}$ や全てのばらつき  $all$ を求ることは比較的容易である。

## 【0061】

そして、チップ内ばらつき成分  $\sigma_{chip}$ や全てのばらつき  $all$ を得ることができれば、パスごとに、ばらつきを考慮した設計検証ポイントを設定することができる。以下、ばらつきを考慮した設計検証ポイントの設定方法について説明する。

50

## 【0062】

まず、他のチップのばらつき成分のみについて考慮するものとし、全てのばらつき成分を除外した遅延（全てのばらつきを考慮した遅延の平均値とも言える）を  $D_{average}$  とし、他のチップのばらつき成分は標準偏差1 分をカバーするものと考えると、パス全体の基準遅延  $D_{base}$  の範囲は、以下の数式（8）で表される。

## 【0063】

## 【数8】

$$D_{average} \times (1 - \sigma_f) \leq D_{base} \leq D_{average} \times (1 + \sigma_f) \quad \cdots (8)$$

10

## 【0064】

そして、上記範囲を全てカバーする場合の基準遅延  $D_{base}$  の最大値は以下の数式（9）で表される。

## 【0065】

## 【数9】

$$D_{base} = D_{average} \times (1 + \sigma_f) \quad \cdots (9)$$

## 【0066】

この場合に、チップ内ばらつきを考慮すると、単純には全てのばらつきを含む遅延  $D_{all}$  の範囲は、以下の数式（10）で表される。

20

## 【0067】

## 【数10】

$$D_{base} \times (1 - \sigma_{chip}) \leq D_{all} \leq D_{base} \times (1 + \sigma_{chip}) \quad \cdots (10)$$

## 【0068】

そして、上記範囲を全てカバーする場合の遅延  $D_{all}$  の最大値は以下の数式（11）で表される。

## 【0069】

30

## 【数11】

$$D_{all} = D_{base} \times (1 - \sigma_{chip}) = D_{average} \times (1 + \sigma_f) \times (1 + \sigma_{chip})$$

$$= D_{average} \times (1 + \sigma_f) \times (1 + \sqrt{\sigma_r^2 + \sigma_s^2}) \quad \cdots (11)$$

## 【0070】

次に、全てのばらつき  $all$  について考慮するならば、全てのばらつき成分を含む遅延  $D_{all}$  の範囲は、標準偏差1 分をカバーするものとすれば、以下の数式（12）によって表すことができる。

40

## 【0071】

## 【数12】

$$D_{average} \times (1 - \sigma_{all}) \leq D_{all} \leq D_{average} \times (1 + \sigma_{all}) \quad \cdots (12)$$

## 【0072】

そして、上記範囲を全てカバーする場合の全てのばらつき成分を含む遅延  $D_{all}$  の最大値は以下の数式（13）で表される。

## 【0073】

## 【数13】

$$D_{all} = D_{average} \times (1 + \sigma_{all}) \cdots (13)$$

## 【0074】

数式(13)より、統計学的な最大値は以下の数式(14)となる。

## 【0075】

## 【数14】

$$D_{all} = D_{average} \times (1 + \sigma_{all}) = D_{average} \times (1 + \sqrt{\sigma_f^2 + \sigma_r^2 + \sigma_s^2}) \cdots (14) \quad 10$$

## 【0076】

数式(14)によって与えられる全てのばらつき成分を含む遅延  $D_{all}$  は、数式(11)によって与えられる遅延  $D_{all}$  よりも小さい値となり、設計時に数式(11)を使用する場合は、必要以上のマージンを考慮することになる。

## 【0077】

そこで、遅延  $D_{all}$  が数式(14)の値を越えず、かつ数式(10)の遅延  $D_{all}$  をカバーできるような基準遅延  $D_{base}$  を設定するようとする。

## 【0078】

すなわち、数式(11)を用いるのではなく、以下の数式(15)を使用し、数式(15)を満たすように  $D_{base}$  を設定する。 20

## 【0079】

## 【数15】

$$D_{base} \times (1 + \sigma_{chip}) = D_{average} \times (1 + \sigma_{all}) = D_{average} \times (1 + \sqrt{\sigma_f^2 + \sigma_r^2 + \sigma_s^2}) \cdots (15)$$

## 【0080】

数式(15)を使用することで、各パスにおけるチップ内ばらつき成分  $\sigma_{chip}$  を考慮した、全てのばらつき成分を含む遅延  $D_{all}$  の範囲を設定することができ、当該範囲の最大値および最小値が設計検証ポイントとなる。なお、遅延  $D_{all}$  の範囲の具体的な設定例について後で説明する。 30

## 【0081】

< C . 遅延変動分の算出例 >

以下、遅延変動  $D_{ocv}$  の具体的な算出例について説明する。

半導体プロセスのばらつきの成分を分類して、各ばらつき成分によって生じる遅延変動の割合（基準遅延に対する変動の割合）を正規分布と想定して、その標準偏差を以下のように仮定する。すなわち、

チップ内のランダムばらつき成分による遅延変動の割合を 3 でカバーするものとし、

3  $r = 20\%$  とする。 40

## 【0082】

また、チップ内のシステムティックばらつき成分による遅延変動の割合を 3 でカバーするものとし、3  $s = 3\%$  とする。

## 【0083】

また、他のチップのばらつき成分を考慮した遅延変動の割合を 3 でカバーするものとし、3  $f = 20\%$  とする。

## 【0084】

ここで、チップ内のランダムばらつき成分は回路構成や配線パターンによって変動するため、考えられるあらゆる構成の最大値としている。またばらつきをカバーする範囲を広めるために、全て 3 で表現している。 50

**【0085】**

これらの値から、全てのばらつきを含む成分とチップ内ばらつき成分の最大値を数式(1)および(2)から求めることができる。

**【0086】**

すなわち、数式(1)より、

全てのばらつきを含む成分 3 all 28.4%、

数式(2)より、

チップ内ばらつき成分 3 chip 20.2% が得られる。

**【0087】**

ここで、図2に示した第1および第2バスを有する半導体集積回路の各ノードに対して 10

、図5に示すような基準遅延およびランダムばらつき成分の値を仮定する。

**【0088】**

すなわち、ノードND1～ND3、ND11～ND14については、何れも基準遅延50ps(ピコ秒)、ランダムばらつき成分10%とする。また、ノードND5については、基準遅延500ps、ランダムばらつき成分20%とし、ノードND7、ND9については、基準遅延50ps、ランダムばらつき成分20%とし、ノードND8については、基準遅延100ps、ランダムばらつき成分20%とする。

**【0089】**

なお、ノードND4、ND6およびND10を構成するフリップフロップを多段セルと考え、特にノードND4については、初段ゲート回路内の固定遅延成分と出力ゲート回路内の変動遅延成分とに分割し、基準遅延100ps、ランダムばらつき成分5%のセルと、基準遅延50ps、ランダムばらつき成分10%のセルとを有しているものとして扱う。ただし、フリップフロップの構成によっては、更に分割が必要となる場合もある。 20

**【0090】**

図5に示す第1および第2のバスに対して数式(6)を適用すると、ランダムばらつき成分3rは以下のように計算できる。

**【0091】**

すなわち、第1バスについては、以下の数式(16)から、 $3r = 13.4\%$ となる。

**【0092】****【数16】**

$$3\sigma_r = \frac{\sqrt{50ps^2 \times 10\%^2 + 100ps^2 \times 5\%^2 + 50ps^2 \times 10\%^2 + 500ps^2 \times 20\%^2 + 50ps^2 \times 10\%^2}}{50ps + 100ps + 50ps + 500ps + 50ps} \dots (16)$$

**【0093】**

また、第2バスについては、以下の数式(17)から、 $3r = 4.4\%$ となる。

**【0094】**

【数17】

$$\sigma_r = \sqrt{\frac{50ps^2 \times 10\%^2 + 50ps^2 \times 10\%^2 + 50ps^2 \times 5\%^2 + 50ps^2 \times 5\%^2 + 100ps^2 \times 20\%^2 + 100ps^2 \times 20\%^2 + 50ps^2 \times 20\%^2 + 50ps^2 \times 20\%^2 + 50ps^2 \times 10\%^2 + 50ps^2 \times 10\%^2}{50ps + 50ps + 50ps + 100ps + 50ps + 100ps + 50ps + 50ps + 50ps + 50ps + 50ps}}$$

… (17)

10

20

30

40

【0095】

これらの値から、第1および第2パスのそれぞれについて、全てのばらつきを含む成分およびチップ内ばらつき成分は、数式(1)および(2)から以下のように計算することができる。

【0096】

50

すなわち、第1パスについては、以下の数式(18)および(19)から、 $3\sigma_{all} = 24.8\%$ となり、 $3\sigma_{chip} = 14.6\%$ となる。

【0097】

【数18】

$$3\sigma_{all} = 3 \times \sqrt{\sigma_r^2 + \sigma_s^2 + \sigma_f^2} = \sqrt{13.4\%^2 + 3\%^2 + 20\%^2} = 24.3\% \quad \cdots (18)$$

【0098】

【数19】

$$3\sigma_{chip} = 3 \times \sqrt{\sigma_r^2 + \sigma_s^2} = \sqrt{13.4\%^2 + 3\%^2} = 13.7\% \quad \cdots (19)$$

10

【0099】

また、第2パスについては、以下の数式(20)および(21)から、 $3\sigma_{all} = 20.7\%$ となり、 $3\sigma_{chip} = 5.3\%$ となる。

【0100】

【数20】

$$3\sigma_{all} = 3 \times \sqrt{\sigma_r^2 + \sigma_s^2 + \sigma_f^2} = \sqrt{4.4\%^2 + 3\%^2 + 20\%^2} = 20.7\% \quad \cdots (20)$$

【0101】

20

【数21】

$$3\sigma_{chip} = 3 \times \sqrt{\sigma_r^2 + \sigma_s^2} = \sqrt{4.4\%^2 + 3\%^2} = 5.3\% \quad \cdots (21)$$

【0102】

このように、全てのばらつきを含む成分、チップ内ばらつき成分とも第1および第2パスで異なっていることが判る。

【0103】

そして、第1および第2パスのそれぞれについて、チップ内ばらつき成分 $3\sigma_{chip}$ によって生じる遅延変動 $D_{OCV}$ は、数式(7)から以下のように計算できる。ただし、何れもパス全体の基準遅延に対しての遅延変動として表されている。

30

【0104】

すなわち、第1パスについては、以下の数式(22)から、 $D_{OCV} = 102.6\text{ps}$ となる。

【0105】

【数22】

$$D_{OCV} = \text{第1パス全体の基準遅延} \times 3\sigma_{chip} = (50\text{ps} + 100\text{ps} + 50\text{ps} + 500\text{ps} + 50\text{ps}) \times 13.7\% = 103.0\text{ps} \quad \cdots (22)$$

【0106】

40

また、第2パスについては、以下の数式(23)から、 $D_{OCV} = 34.3\text{ps}$ となる。

【0107】

【数23】

$$D_{OCV} = \text{第2パス全体の基準遅延} \times 3\sigma_{chip} = (50\text{ps} + 50\text{ps} + 50\text{ps} + 100\text{ps} + 50\text{ps} + 50\text{ps} + 100\text{ps} + 50\text{ps} + 50\text{ps} + 50\text{ps}) \times 5.3\% = 34.3\text{ps} \quad \cdots (23)$$

【0108】

半導体集積回路の設計時に、上述した過程を経て得られた遅延変動 $D_{OCV}$ を考慮してお

50

けば、チップ内ばらつき成分  $3 \text{ chip}$  の範囲をカバーした遅延を組み込んだ設計が可能となる。

#### 【0109】

なお、上述した計算例では  $3 \text{ chip}$  をカバーするものとしたが、カバーする範囲を変更しても同様に遅延を考慮することができる。また、遅延が遅くなるものとして説明したが、遅延が速くなる場合も同様に考慮することができる。

#### 【0110】

また、システムティックばらつき成分  $s$  に関しては固定値の例を示したが、場所依存性を持たせるなど関数表現であっても同様に扱うことができる。

#### 【0111】

そして、基準遅延としては、ばらつきを考慮しない場合のティピカルな遅延、他のチップのばらつき成分を考慮した遅延の平均値など、様々な場合を想定することができる。

#### 【0112】

また、パス1本では  $3$  のカバー範囲で良い場合でも、クリティカルパスが複数本ある場合には  $3$  以上を考慮するなど、クリティカルパスの本数によって想定するカバー範囲を変更すれば良い。

#### 【0113】

< D . 全てのばらつき成分を含む遅延の設定例 >

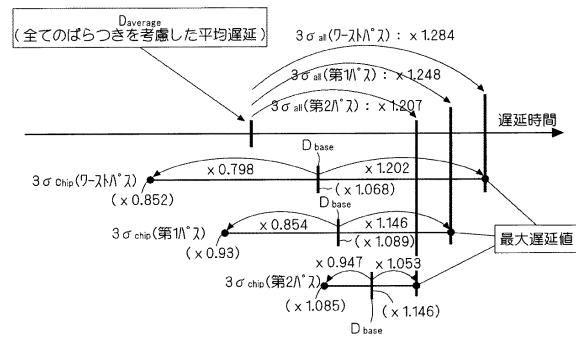

次に、全てのばらつき成分を含む遅延  $D_{all}$  の範囲の具体的な設定例について、図6および図7を用いて説明する。なお、以下では、図5に示した半導体集積回路を例に採り説明を行う。

#### 【0114】

まず、第1および第2のパスを含む全てのパスについて、パスごとに全てのばらつきを含む成分  $all$  およびチップ内ばらつき成分  $chip$  を、式(16)～(21)で説明した手法で求める。ここで、図5に示した半導体集積回路には、第1および第2のパス以外にも複数のパスが存在するものとし、理論的に考えられるもっともばらつきの大きなパスをワーストパスと呼称すると、各パスのばらつき成分は以下のように表される。

#### 【0115】

ワーストパスの  $3 \text{ all} = 28.4\%$

ワーストパスの  $3 \text{ chip} = 20.2\%$

第1パスの  $3 \text{ all} = 24.3\%$

第1パスの  $3 \text{ chip} = 13.7\%$

第2パスの  $3 \text{ all} = 20.7\%$

第2パスの  $3 \text{ chip} = 5.3\%$

そして、上記値に基づいて、パスごとに  $3 \text{ all}$  および  $3 \text{ chip}$  をカバーするものとし、パスごとにカバー範囲を以下のように設定する。

#### 【0116】

すなわち、全てのばらつきを含む成分が  $3 \text{ all}$  を超える場合、またはチップ内ばらつきの成分が  $3 \text{ chip}$  を超える場合のどちらか一方でも生じる場合は半導体集積回路の性能を保証しない、という設定を行う。

#### 【0117】

換言すれば、全てのばらつきを含む成分が  $3 \text{ all}$  を超えず、かつチップ内ばらつきの成分が  $3 \text{ chip}$  を超えないという、もっとも条件の厳しい範囲を設計条件とする。

#### 【0118】

この設計条件を反映したものが式(15)であり、式(15)に基づいて設計検証ポイントを設定する方法を模式的に示したものが図6である。

#### 【0119】

図6に示すように、全てのばらつきを考慮した平均遅延である  $D_{average}$  に対し、各パスごとに算出される  $(1 + 3 \text{ all})$  の係数を掛けたものが、各パスの全てのばらつき成分を含む遅延  $D_{all}$  の最大値（以下、最大遅延値と呼称）となる。

10

20

40

50

**【 0 1 2 0 】**

なお、各パスごとに算出される(1+3 all)の値は、ワーストパスが1.284、第1パスが1.243、第2パスが1.207となる。

**【 0 1 2 1 】**

そして、各パスの最大遅延値に対して、式(15)を満たすように各パスごとに基準遅延D<sub>base</sub>を設定することで、見かけ上の基準遅延D<sub>base</sub>を決めることができる。

**【 0 1 2 2 】**

すなわち、各パスごとに算出される(1+3 chip)の係数を掛けすることで、各パスの最大遅延値に達する値が、各パスの見かけ上の基準遅延D<sub>base</sub>となる。なお、D<sub>average</sub>を1とした場合に、ワーストパスの見かけ上の基準遅延D<sub>base</sub>は1.068、第1パスの見かけ上の基準遅延D<sub>base</sub>は1.093、第2パスの見かけ上の基準遅延D<sub>base</sub>は1.146となる。10

**【 0 1 2 3 】**

そして、各パスの見かけ上の基準遅延D<sub>base</sub>に対して、各パスごとに算出される(1-3 chip)の係数を掛けすることで、各パスの全てのばらつき成分を含む遅延D<sub>all</sub>の最小値(以下、最小遅延値と呼称)が得られる。なお、D<sub>average</sub>を1とした場合に、ワーストパスの最小遅延値は0.852、第1パスの最小遅延値は0.943、第2パスの最小遅延値は1.085となる。

**【 0 1 2 4 】**

以上の手法により、各パスにおける全てのばらつき成分を含む遅延D<sub>all</sub>の許容範囲(式(10)で規定される範囲)を設定することができ、その最大遅延値および最小遅延値を設計検証ポイントとし、半導体集積回路の設計時にはこれらの値を超えないように遅延設計を行う。20

**【 0 1 2 5 】**

以上説明した手法により遅延D<sub>all</sub>の許容範囲を設定する場合、図6から判るように、パスによって基準遅延が見かけ上変化する。

**【 0 1 2 6 】**

基準遅延がパスによって異なると、基準遅延の計算をするために必要な各ノードのゲート回路や配線の情報(ライブラリ)が複雑になり、設計手法も複雑になる場合が想定される。30

**【 0 1 2 7 】**

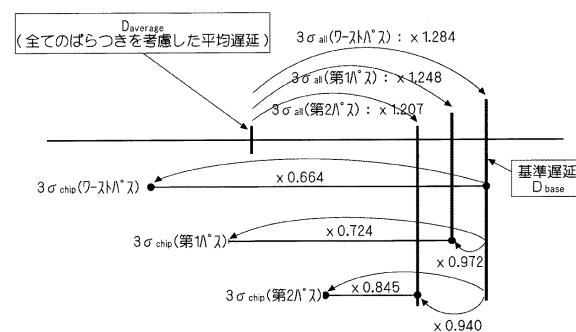

そこで、基準遅延を1箇所に設定することで、設計手法を単純化する方法について図7を用いて説明する。

**【 0 1 2 8 】**

図7に示すように、全てのばらつきを考慮した平均遅延であるD<sub>average</sub>に対し、ワーストパスで算出される(1+3 all)の係数を掛けたものを基準遅延として一義的に定める。この値は、ワーストパスにおける最大遅延値であることは言うまでもない。

**【 0 1 2 9 】**

この基準遅延は、D<sub>average</sub>を1とした場合に1.284となり、これに対して係数0.664を掛けた値が、ワーストパスの最小遅延値となる。なお、ワーストパスの最小遅延値は0.852である。40

**【 0 1 3 0 】**

また、基準遅延に対して係数0.734を掛けた値が、第1パスの最小遅延値となる。なお、第1パスの最小遅延値は0.943である。

**【 0 1 3 1 】**

また、基準遅延に対して係数0.845を掛けた値が、第2パスの最小遅延値となる。なお、第2パスの最小遅延値は1.085である。

**【 0 1 3 2 】**

また、各パスの最大遅延値は、ワーストパスについては既に決まっており、基準遅延に対して0.968(1.243/1.284)を掛けた値が第1パスの最大遅延値となり50

、基準遅延に対して 0.940 (1.207 / 1.284) を掛けた値が第 2 パスの最大遅延値となる。

#### 【0133】

このように、ワーストパスの最大遅延値を基準遅延とし、他のパスについては当該基準遅延に対する補正係数をライブラリとして持つことによって、それぞれのパスの最大遅延値および最小遅延値を設定することができる。

#### 【0134】

この方法を探ることで、何れのパスについても基準遅延は共通となり、基準遅延がパスによって変化することないので、基準遅延の計算をするために必要な各ノードのゲート回路や配線のライブラリは単純なもので済み、設計手法を簡単化できる。このため、現状の設計手法の延長で本発明に係る設計方法を適用することが可能となる。10

#### 【0135】

また、チップ内のランダムばらつき成分  $r$  の、より現実的な値を半導体集積回路の設計に反映させることによって、必要以上の設計マージンの削除によって性能向上や設計収束性が期待でき、また必要なマージンの確保によって品質向上も期待できる。

#### 【0136】

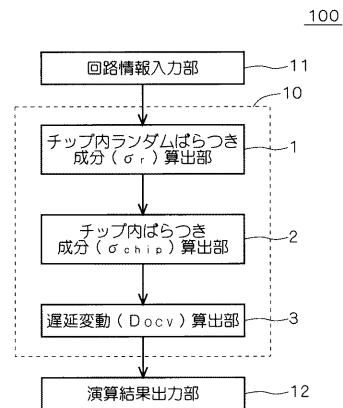

< E . 半導体集積回路の設計装置の構成 >

以上の説明では、半導体集積回路の設計方法を述べたが、当該設計方法は、以下に説明する半導体集積回路の設計装置により実行することができる。

#### 【0137】

図 8 は本発明に係る半導体集積回路の設計装置 100 の構成を示すブロック図である。半導体集積回路の設計装置 100 は、設計対象となる半導体集積回路の回路情報が入力される回路情報入力部 11、回路情報入力部 11 で受けた回路情報に基づいて所定の演算を施す演算部 10、演算部 10 での演算結果を出力する演算結果出力部 12 とを備えている。なお、回路情報にはノード間の接続関係を示すネットリスト、各ノードの遅延情報などが含まれている。20

#### 【0138】

演算部 10 は、解析対象となる 2 つのパス（アライバルパスおよびリクワイアドパス）を、1 つのパスとして統合し、当該 1 つのパス（統合パス）を構成する複数のノードについてチップ内ランダムばらつき成分 ( $r$ ) を算出するチップ内ランダムばらつき成分算出部 1 と、チップ内ランダムばらつき成分算出部 1 で算出されたチップ内ランダムばらつき成分 ( $r$ ) と、チップ内システムティックばらつき成分 ( $s$ ) とに基づいてチップ内ばらつき成分  $chip$  を算出するチップ内ばらつき成分算出部 2 と、パス全体の基準遅延 ( $D_{base}$ ) と、チップ内ばらつき成分 ( $chip$ ) とに基づいて遅延変動 ( $D_{ocv}$ ) を算出する、遅延変動算出部 3 とを有している。30

#### 【0139】

遅延変動算出部 3 で得られた遅延変動 ( $D_{ocv}$ ) は、演算結果出力部 12 に与えられ、演算結果出力部 12 を介して図示しない表示装置に遅延変動 ( $D_{ocv}$ ) を表示したり、データとして出力するなどして、後続する半導体集積回路の設計に遅延変動 ( $D_{ocv}$ ) の情報を与える。40

#### 【0140】

なお、遅延変動 ( $D_{ocv}$ ) の情報を半導体集積回路の設計に反映させることは当業者であれば周知であるので、具体的な装置構成や説明は省略する。

#### 【0141】

< F . 半導体集積回路の設計装置の実現例 >

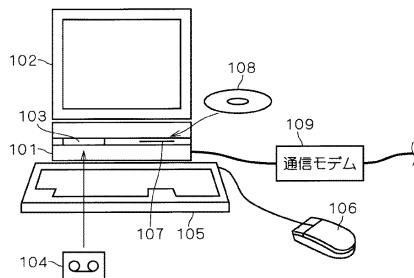

以上説明した、半導体集積回路の設計装置 100 の実現にあたっては、例えば図 9 に示すようなコンピュータシステムを利用すれば良い。

#### 【0142】

すなわち、図 9 に示すように半導体集積回路の設計装置 100 は、コンピュータ本体 101、ディスプレイ装置 102、磁気テープあるいは磁気ディスク等の磁気記録媒体 103 と

4が装着される磁気記録再生装置103、キーボード105、マウス106、CD(compact disc)やDVD(digital video disc)等の光ディスク108が装着される光ディスク装置107、および通信モデム109を備えている。

**【0143】**

半導体集積回路の設計装置100を構成する演算部10の、チップ内ランダムばらつき成分算出部1、チップ内ばらつき成分算出部2および遅延変動算出部3の機能は、コンピュータプログラム(半導体集積回路の設計プログラム)をコンピュータ上で実行することにより実現することができ、その場合は当該プログラムは磁気記録媒体104あるいは光ディスク108等の記録媒体によって供給される。また、当該プログラムは信号の形態で通信路上を伝搬させ、他のコンピュータから通信回線を経由して通信モデム109を介してコンピュータ本体101に供給することも可能で、記録媒体にダウンロードさせて使用することも可能である。10

**【0144】**

半導体集積回路の設計プログラムはコンピュータ本体101で実行され、操作者はディスプレイ装置102を見ながらキーボード105またはマウス106を操作することによって回路設計を自動的に行うことができる。

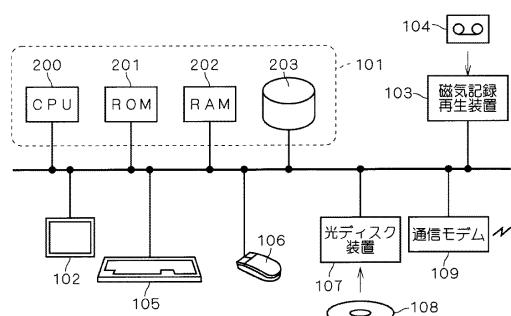

**【0145】**

図10に、図9に示すコンピュータシステムの構成をブロック図として示す。図10に示したコンピュータ本体101は、CPU(CENTRAL PROCESSING UNIT)200、ROM(READ ONLY MEMORY)201、RAM(RANDOM ACCESS MEMORY)202、およびハードディスク203を有している。20

**【0146】**

CPU200は、ディスプレイ装置102、磁気記録再生装置103、キーボード105、マウス106、光ディスク装置107、通信モデム109、ROM201、RAM202、ハードディスク203との間でデータを入出力しながら処理を行う。

**【0147】**

磁気記録媒体104あるいは光ディスク108に記録された半導体集積回路の設計プログラムは、CPU200によって一旦、ハードディスク203に格納される。CPU200はハードディスク203から適宜、半導体集積回路の設計プログラムをRAM202にロードして実行することで半導体集積回路の設計を行う。30

**【0148】**

このように、半導体集積回路の設計装置100をコンピュータシステムで実現し、本発明に係る半導体集積回路の設計方法をコンピュータプログラムにより実行することで、本発明に係る半導体集積回路の設計方法を汎用的に利用することができる。

**【0149】**

以上説明したコンピュータシステムは一例であり、半導体集積回路の設計プログラムを実行できるのであればこれに限定されるものではなく、記録媒体としても磁気記録媒体104や光ディスク108に限定されるものではない。

**【産業上の利用可能性】**

**【0150】**

同期設計を行う全てのSOC(System On Chip)半導体製品。40

**【図面の簡単な説明】**

**【0151】**

【図1】n個のノードを持つ半導体集積回路を模式的に表す図である。

【図2】本発明に係る実施の形態の設計方法を説明するための半導体集積回路を模式的に表す図である。

【図3】チップ内ばらつきを考慮すべき半導体集積回路を模式的に表す図である。

【図4】本発明に係る半導体集積回路の設計方法の基本概念を説明するフローチャートである。

【図5】半導体集積回路の各ノードに対して、基準遅延およびランダムばらつき成分の値50

を示した図である。

【図6】全てのばらつき成分を含む遅延の範囲の具体的な設定例を説明する図である。

【図7】全てのばらつき成分を含む遅延の範囲の具体的な設定例を説明する図である。

【図8】本発明に係る半導体集積回路の設計装置の構成を示すブロック図である。

【図9】本発明に係る半導体集積回路の設計装置を実現するコンピュータシステムの外観図である。

【図10】本発明に係る半導体集積回路の設計装置を実現するコンピュータシステムの構成を示す図である。

【図11】スタティックタイミング解析の概念を説明する模式図である。

【図12】統計的スタティックタイミング解析の概念を説明する模式図である。 10

【符号の説明】

【0152】

ND0 ~ ND14 ノード。

【図1】

【図2】

【図3】

【図4】

【図5】

【図 6】

【図 8】

【図 7】

【図 9】

【図 10】

【図 12】

【図 11】

---

フロントページの続き

(56)参考文献 特開2005-122298(JP,A)

特開2002-222232(JP,A)

特開平07-182381(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 17 / 50

C i N i i

J S T P l u s ( J D r e a m I I )