(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 602 13 601 T2 2007.08.09

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 402 395 B1

(51) Int Cl.<sup>8</sup>: **G06F 15/78 (2006.01)**

(21) Deutsches Aktenzeichen: **602 13 601.6**

(86) PCT-Aktenzeichen: **PCT/US02/12234**

(96) Europäisches Aktenzeichen: **02 723 894.8**

(87) PCT-Veröffentlichungs-Nr.: **WO 2002/095598**

(86) PCT-Anmeldetag: **17.04.2002**

(87) Veröffentlichungstag

der PCT-Anmeldung: **28.11.2002**

(97) Erstveröffentlichung durch das EPA: **31.03.2004**

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **02.08.2006**

(47) Veröffentlichungstag im Patentblatt: **09.08.2007**

(30) Unionspriorität:

**861112 18.05.2001 US**

(84) Benannte Vertragsstaaten:

**DE, FR, GB, IE**

(73) Patentinhaber:

**Xilinx, Inc., San Jose, Calif., US**

(72) Erfinder:

**DAO, Kim, Khang, San Jose, CA 95131, US;

BAXTER, A., Glenn, Los Gatos, CA 95033, US**

(74) Vertreter:

**derzeit kein Vertreter bestellt**

(54) Bezeichnung: **PROGRAMMIERBARE HARDWARELOGIK, WELCHE EIN PROGRAMMIERBARES INTERFACE UND EINE ZENTRALE RECHENEINHEIT BEINHALTET**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****GEBIET DER ERFINDUNG**

**[0001]** Die vorliegende Erfindung betrifft eine programmierbare Logikvorrichtung und insbesondere eine programmierbare Logikvorrichtung mit einem Schnittstellenkern und einer zentralen Verarbeitungseinheit.

**BESCHREIBUNG DER VERWANDTEN TECHNIK**

**[0002]** Ein Mikroprozessor ist eine allgemein bekannte integrierte Schaltung, die einen Computer steuert. Die Art und Weise, auf die der Mikroprozessor den Computer steuert, bestimmt die Geschwindigkeit und Leistungsfähigkeit des Computers. Um den Computer steuern zu können, verarbeitet der Mikroprozessor eine Unmenge von Anweisungen, die ihn jeweils dazu auffordern, eine bestimmte Operation durchzuführen. Ein typischer Mikroprozessor enthält eine zentrale Verarbeitungseinheit (CPU), die die gewünschten arithmetischen und logischen Funktionen ausführt, sowie eine Eingabe/Ausgabeeinheit, die es der CPU ermöglicht, Eingangs-werte von den restlichen Bestandteilen des Computers zu empfangen, um diese Funktionen ausführen zu kön-nen, und/oder ihre Ergebnisse den restlichen Bestandteilen des Computers mitzuteilen.

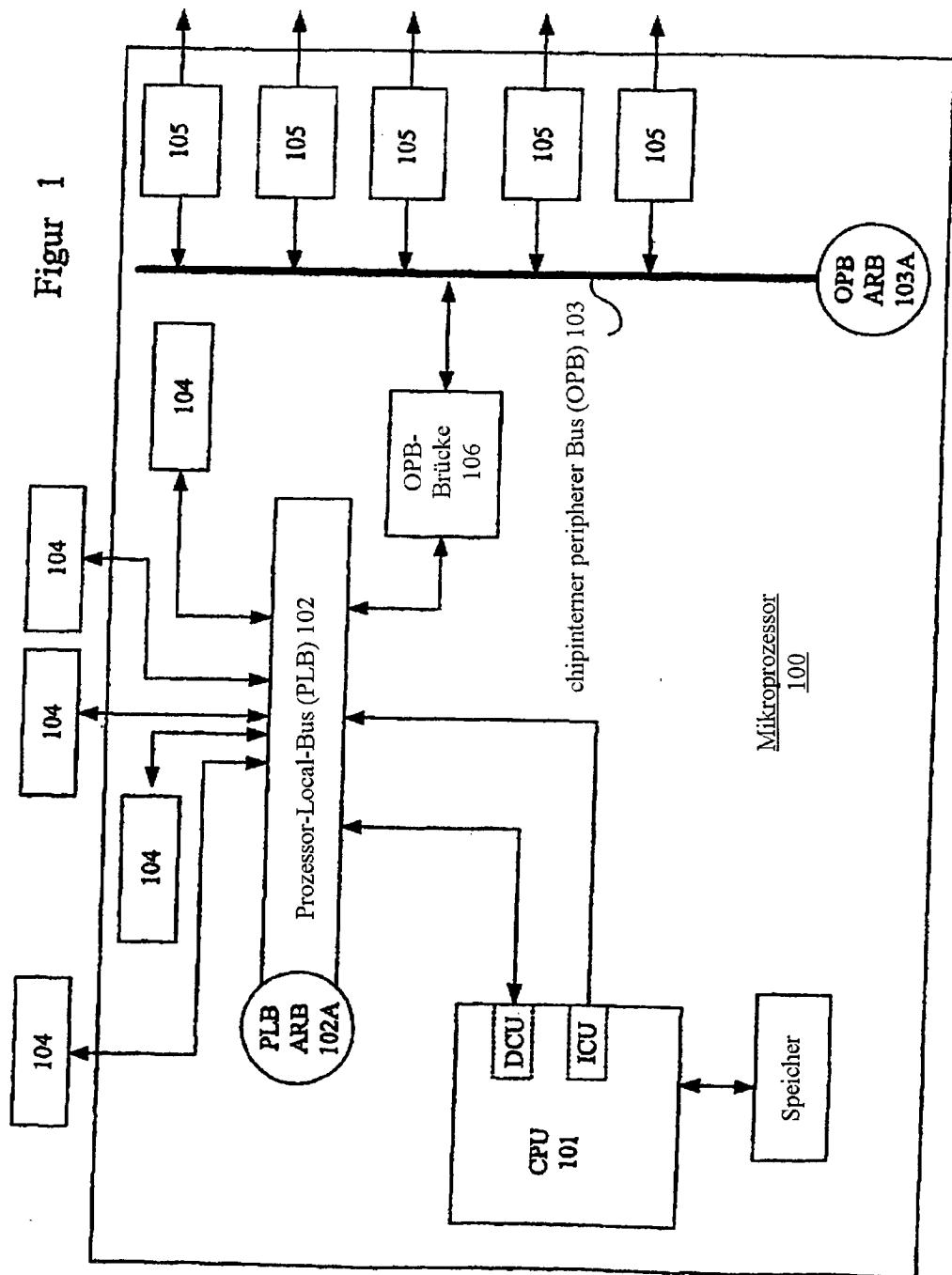

**[0003]** **Fig. 1A** stellt einen bekannten Mikroprozessor **100** dar, der eine CPU **101** und zwei Erweiterungsbusse **102** und **103** enthält. Mit Hilfe der Erweiterungsbusse kann die CPU **101** mit anderen Vorrichtungen kom-munizieren, wodurch sich der Arbeitsbereich des Mikroprozessors ausweitet. Der Erweiterungsbuss **102**, der auch als Prozessor-Local-Bus (PLB) bezeichnet wird, verbindet die CPU **101** mit Hochgeschwindigkeitsvorrichtungen **104**. Zu diesen Hochgeschwindigkeitsvorrichtungen **104** könnten Speicher- und Hochleistungsperipheriegeräte gehören. Eine Vorrichtung, die die Steuerung des PLB **102** übernimmt und für ihren eigenen Transfer sorgt, wird als „Master“ bezeichnet, während eine Vorrichtung, die vom Master Befehle zum Senden von Daten empfängt, als „Slave“ bezeichnet wird.

**[0004]** Der Erweiterungsbuss **103**, der auch als chipintegrierter peripherer Bus (On-chip Peripheral Bus = OPB) bezeichnet wird, sorgt für den Zugang der CPU **101** zu langsamem Vorrichtungen **105**. Zu diesen lang-samen Vorrichtungen **105** könnten UART-Chips und Ethernet-Verbindungen gehören. Es sei angemerkt, daß zu langsamem Vorrichtungen **105** genauso wie zu Hochgeschwindigkeitsvorrichtungen **104** sowohl Master als auch Slaves gehören können. Um jedoch zu verhindern, daß diese langsamem Vorrichtungen **105** die Leistung der CPU **101** beeinflussen, ist der OPB **103** nicht direkt mit der CPU **101** verbunden. Stattdessen wird der OPB **103** über eine OPB-Brücke **106** an den PLB **102** gekoppelt. Es sei angemerkt, daß die meisten Systeme davon ausgehen, daß die Segmentierung von Bussen erfolgt, damit langsame Vorrichtungen keine wertvolle Band-breite auf dem Hauptbus verbrauchen. Es ist jedoch häufig von Vorteil, die Segmentierung als Bus parallel zum Hauptbus zu behandeln, die den vorteilhaften Betrieb von Peripheriegeräten mit höherer Geschwindigkeit bei geringer Auswirkung auf den Hauptbus ermöglicht. Bei der OPB-Brücke **106** handelt es sich um ein System-bauelement, das für den Transport von Daten von einem Bus zum anderen ausgelegt ist. Die OPB-Brücke **106** kann Datenformate und Protokolle automatisch umwandeln und erleichtert dadurch die Übertragung von Infor-mationen zwischen OPB **103** und PLB **102**.

**[0005]** Anwendungsspezifische integrierte Schaltungen (ASICs) sind im Fachbereich der integrierten Schal-tungen ebenfalls allgemein bekannt. Bei einem ASIC handelt es sich um einen Chip, der für eine vorgegebene Anwendung bestimmt ist. Zum Bau eines ASIC werden mehrere Grundschaltungszellen miteinander verbun-den. Diese Schaltungszellen sind in der Regel in einer vom ASIC-Hersteller gelieferten Bibliothek zu finden. Einige Hersteller liefern derzeit Mikroprozessorzellen zum Integrieren in den ASIC. Diese Mikroprozessorarten werden „integrierte“ Mikroprozessoren genannt.

**[0006]** Programmierbare Logikvorrichtungen (Programmable Logic Devices = PLDs) sind im Fachbereich der integrierten Schaltungen ebenfalls allgemein bekannt. Eine PLD kann vom Anwender vor Ort programmiert werden, um logische Strukturen zu implementieren. Eine PLD-Art ist das anwenderprogrammierbare Gate-Arra-y (Field-Programmable Gate Array = FPGA). Bei einer typischen Architektur enthält ein FPGA ein Array aus konfigurierbaren Logikbausteinen (Configurable Logic Blocks = CLBs), das von programmierbaren Eingabe/Ausgabebausteinen (Input/Output Blocks = IOBs) umgeben ist. Die IOBs sorgen für die Schnittstelle zwi-schen den Anschlußstiften und den CLBs, während die CLBs die Funktionselemente für die Konstruktion von Logik auf dem FPGA bereitstellen. Die CLBs und die IOBs sind durch eine Hierarchie von programmierbaren Leitwegeressourcen miteinander verbunden. Diese CLBs, IOBs und programmierbaren Leitwegeressourcen werden durch das Laden eines Konfigurationsbitstroms in das FPGA individuell angepaßt. Dieser Konfigurati-onsbitstrom wird mit Hilfe von Software-Tools erzeugt.

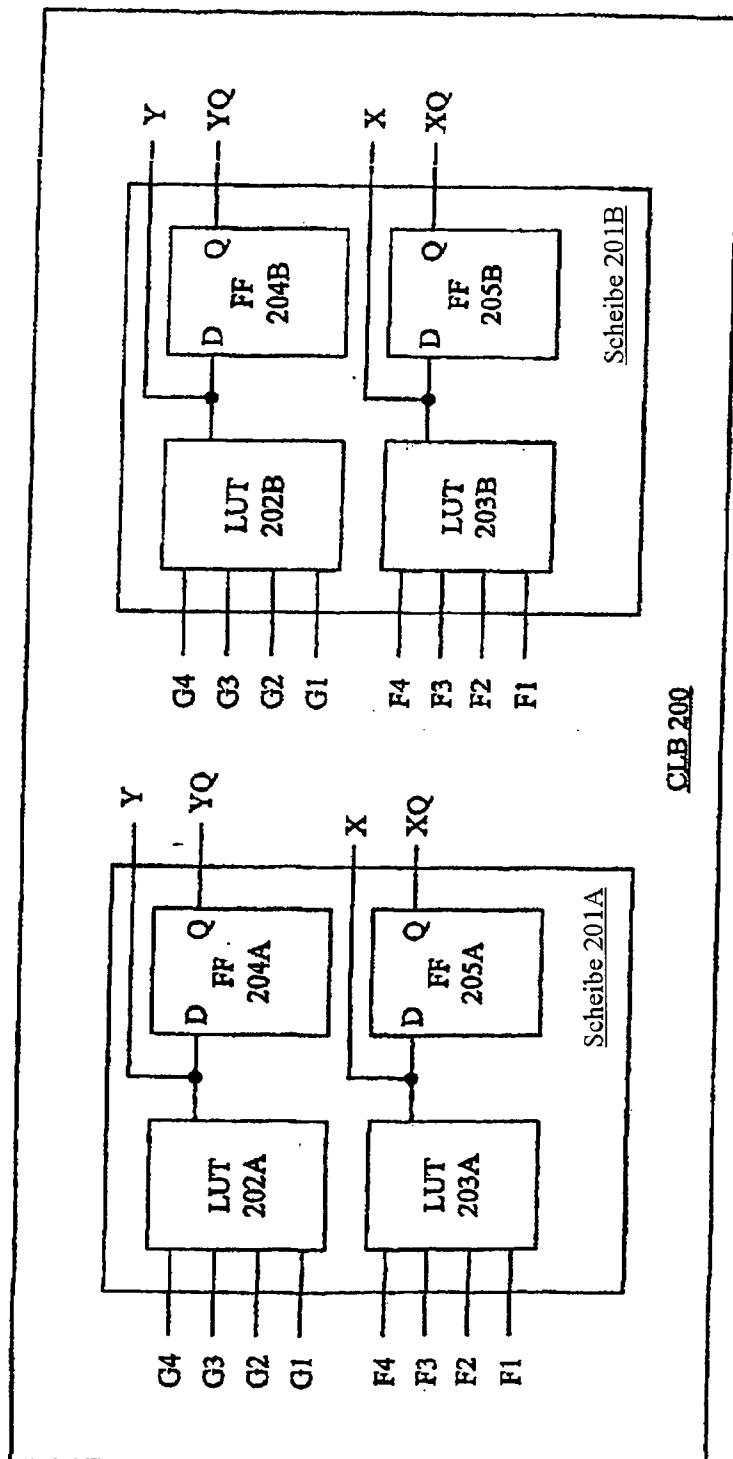

**[0007]** [Fig. 2](#) stellt ein vereinfachtes Blockdiagramm eines CLB **200** bei dem von Xilinx, Inc. vertriebenen FPGA Virtex™ dar. Der CLB **200** enthält zwei „Scheiben“ **201A** und **201B**. Jede Scheibe **201** enthält einen ersten LUT **202** für das Empfangen mehrerer erster Eingangssignale G1–G4 von der programmierbaren Leiterbahn und einen zweiten LUT **203** für das Empfangen mehrerer zweiter Eingangssignale F1–F4, die ebenfalls von der programmierbaren Leiterbahn kommen. Jede Scheibe **201** enthält des weiteren ein Flip-Flop **204** für das Empfangen eines Ausgangssignals Y (an seinem Anschluß D) von dem LUT **202** und für das Ausgeben eines Signals YQ (an seinem Anschluß Q). Auf ähnliche Weise enthält jede Scheibe **201** des weiteren ein Flip-Flop **205** für das Empfangen eines Ausgangssignals X (an seinem Anschluß D) von dem LUT **203** und für das Ausgeben eines Signals XQ (an seinem Anschluß Q). Weitere Einzelheiten zu dem FPGA Virtex™ werden auf den Seiten 3–7 bis 3–17 und den Seiten 3–76 bis 3–87 in dem von Xilinx, Inc. veröffentlichten Dokument "The Programmable Logic Data Book 2000" offen gelegt.

**[0008]** Einige FPGAs wie das FPGA Virtex können so programmiert werden, daß sie Bausteine mit einer vorgegebenen Funktionalität enthalten, die als „Kern“ bezeichnet werden. Bei einer Ausführungsform kann der Kern einen vorgegebenen Satz Konfigurationsbits enthalten, die das FPGA so programmieren, dass es eine oder mehrere Funktionen ausführt. Bei einer weiteren Ausführungsform kann ein Kern Quellcode oder Schemata enthalten, die die Logik und Konnektivität einer Struktur beschreiben. Typische Kerne können unter anderem digitale Signalverarbeitungsfunktionen (Digital Signal Processing = DSP), Speicher, Speicherelemente und mathematische Funktionen bereitstellen. Kerne können für bestimmte FPGAs mit einem optimal geplanten Layout versehen werden. Kerne können auch parametrisierbar sein, d.h. sie können es dem Anwender ermöglichen, Parameter einzugeben, um eine bestimmte Kernfunktionalität zu aktivieren oder zu ändern.

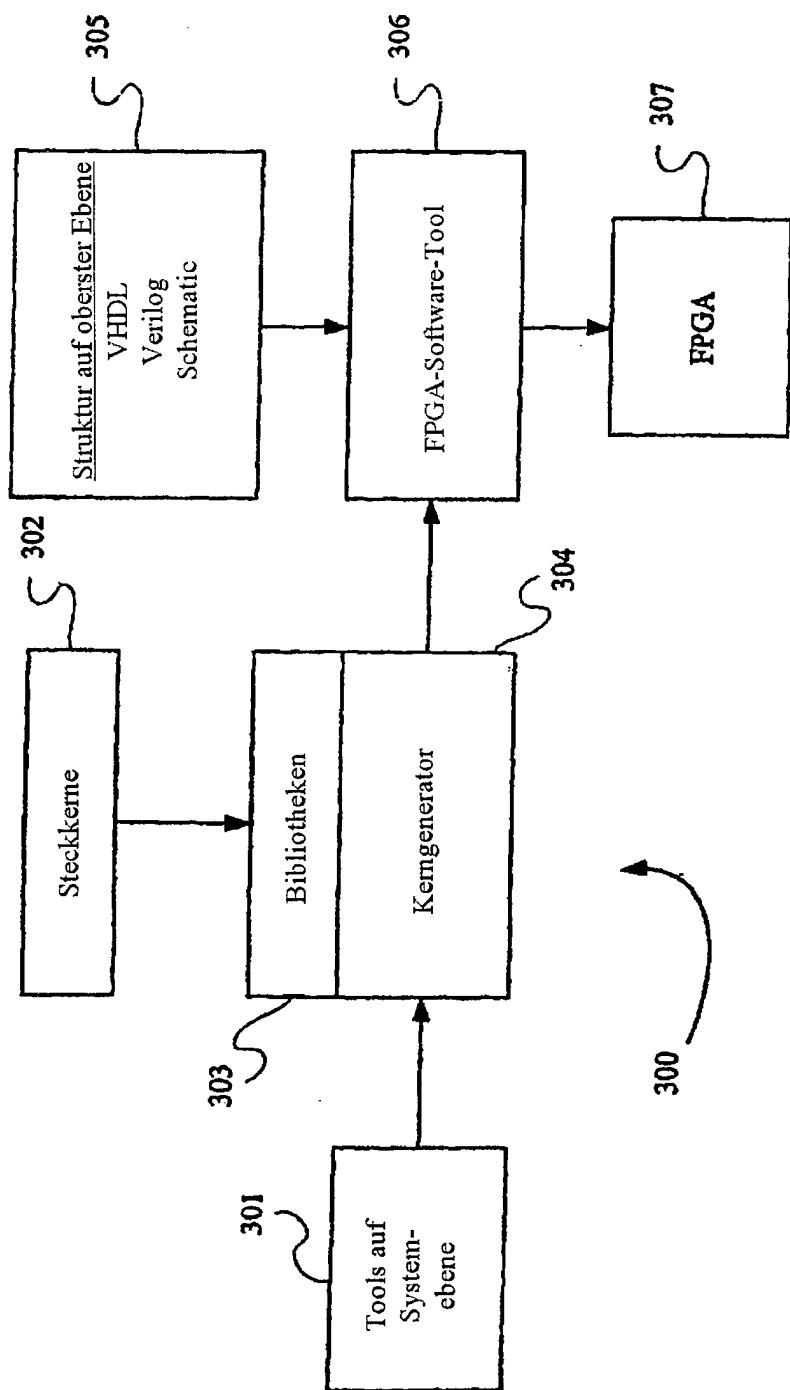

**[0009]** [Fig. 3](#) stellt einen IP-Prozeßaufbau **300** für die Verwendung eines oder mehrerer Kerne in einem FPGA dar. Es sei angemerkt, daß sich IP hier auf allgemeines geistiges Eigentum (Intellectual Property) wie beispielsweise Logikstrukturen für ein FPGA bezieht. Sowohl vom Anwender bereitgestellte Logikstrukturen als auch von der Inhaberin der vorliegenden Erfindung oder anderen entwickelten Kerne werden als IP angesehen. Bei dem Aufbau **300** kann ein Kerngenerator **304**, der von Tools **301** auf Systemebene aktiviert wird, einen oder mehrere Steckkerne von Drittanbietern aufnehmen. Alternativ dazu kann der Kerngenerator **304** einen Kern verwenden, der innerhalb eines Satzes Bibliotheken **303** bereitgestellt wird, wobei diese Bibliotheken **303** Bestandteile des Kerngenerators **304** sind. Wenn der Kern ausgewählt worden ist, kann er einem FPGA-Software-Tool **306** zugeführt werden. Zu beispielhafter FPGA-Software könnte die Software Alliance™, Foundation™ oder Foundation ISE™ gehören, die alle von der Inhaberin der vorliegenden Erfindung lizenziert werden. Diese Software kann ebenso von einem Anwender eine Struktur **305** auf oberster Ebene erhalten. Diese Struktur auf oberster Ebene bestimmt die Logikstruktur, die zusätzlich zu dem/den Kernen auf dem FPGA implementiert wird. Bei einer Ausführungsform kann das FPGA-Software-Tool **306** Strukturen **305** auf oberster Ebene in VHDL, Verilog oder standardmäßiger schematischer Form erhalten. Das FPGA-Software-Tool **306** erzeugt den Konfigurationsbitstrom, der ein FPGA **307** so programmiert, dass die von dem/den Kernen und der Struktur auf oberster Ebene bestimmten Funktionen bereitgestellt werden.

**[0010]** Im Zuge technologischer Verbesserungen tauchen FPGAs zunehmend in bisher ASIC-typischen Anwendungen auf. Bei einem FPGA bestehen jedoch größere Einschränkungen hinsichtlich der physischen Ressourcen als bei einem ASIC. Aus diesem Grunde ist das Bereitstellen von Mikroprozessor-Bestandteilen auf einem FPGA keine einfache Aufgabe und erfordert spezielle Überlegungen.

## KURZDARSTELLUNG DER ERFINDUNG

**[0011]** Gemäß der vorliegenden Erfindung enthält eine programmierbare Logikvorrichtung (PLD) eine zentrale Verarbeitungseinheit (CPU) und eine mit der CPU gekoppelte programmierbare Schnittstelle. Die PLD enthält des weiteren mindestens eine Vorrichtung, die entweder über die programmierbare Schnittstelle Informationen an die CPU liefert, über die programmierbare Schnittstelle Informationen von der CPU empfängt oder über die programmierbare Schnittstelle mit einer anderen Vorrichtung kommuniziert. Die programmierbare Schnittstelle enthält einen Koppelpunkt-Schalter zum Koppeln der mehreren Vorrichtungen. Der Koppelpunkt-Schalter enthält sowohl Adress/Steuerwege als auch Datenwege.

**[0012]** Bei einer Ausführungsform können die Adress/Steuerwege von einem ersten Satz programmierbarer Ressourcen auf der PLD und die Datenwege von einem zweiten Satz programmierbarer Ressourcen auf der PLD gebildet werden. Der erste und der zweite Satz programmierbarer Ressourcen können sich unterscheiden oder sich auf der PLD überlappen.

**[0013]** Bei einer Ausführungsform enthält die PLD des weiteren einen chipinternen peripheren Bus (On-chip

Peripheral Bus = OPB), der mit der programmierbaren Schnittstelle gekoppelt ist. Ein Brückenmodul koppelt den OPB mit der programmierbaren Schnittstelle. Eine erste Gruppe von Vorrichtungen auf der PLD (einschließlich Masters und Slaves) kann mit dem OPB gekoppelt sein. Somit kann diese erste Gruppe von Masters und Slaves mit Hilfe des Brückenmoduls mit der programmierbaren Schnittstelle kommunizieren. Zu der ersten Gruppe von Masters und Slaves können Peripheriegeräte gehören, die sich in der Regel als langsame Vorrichtungen bezeichnen lassen. Bei einer Ausführungsform wird mindestens einer dieser Masters und Slaves mit Hilfe eines Kerns auf der PLD erzeugt. Bei einer anderen Ausführungsform befindet sich mindestens einer dieser Masters und Slaves nicht auf dem Chip. Bei noch einer weiteren Ausführungsform kann ein Kern dafür benutzt werden, eine Vorrichtung (der ersten Gruppe) zu erzeugen, die sowohl Master- als auch Slave-Funktionalität aufweist. Die erste Gruppe von Vorrichtungen kann sich auf der PLD oder außerhalb des Chips befinden.

**[0014]** Eine zweite Gruppe von Vorrichtungen auf der PLD, zu der auch Masters und Slaves gehören, kann mit der programmierbaren Schnittstelle gekoppelt werden. Zu der zweiten Gruppe von Vorrichtungen können Hochgeschwindigkeitsvorrichtungen wie Speichervorrichtungen oder Vorrichtungen mit doppelter Datenrate gehören. Die zweite Gruppe von Vorrichtungen kann sich auf der PLD oder nicht auf dem Chip befinden. Bei einer Ausführungsform enthält einer der Masters in der zweiten Gruppe von Vorrichtungen eine Hochgeschwindigkeits-Busschnittstelle, die mit der programmierbaren Schnittstelle und dem OPB gekoppelt ist, wobei die Hochgeschwindigkeits-Busschnittstelle für die Kommunikation mit einer chipexternen Vorrichtung sorgt. Die PLD der vorliegenden Erfindung lässt sich problemlos in ein System integrieren, das andere Bestandteile enthält, wobei die programmierbare Schnittstelle und die Hochgeschwindigkeits-Busschnittstelle vorteilhaftweise für den effizienten Zugang dieser Bestandteile zu den die CPU betreffenden Funktionen sorgen.

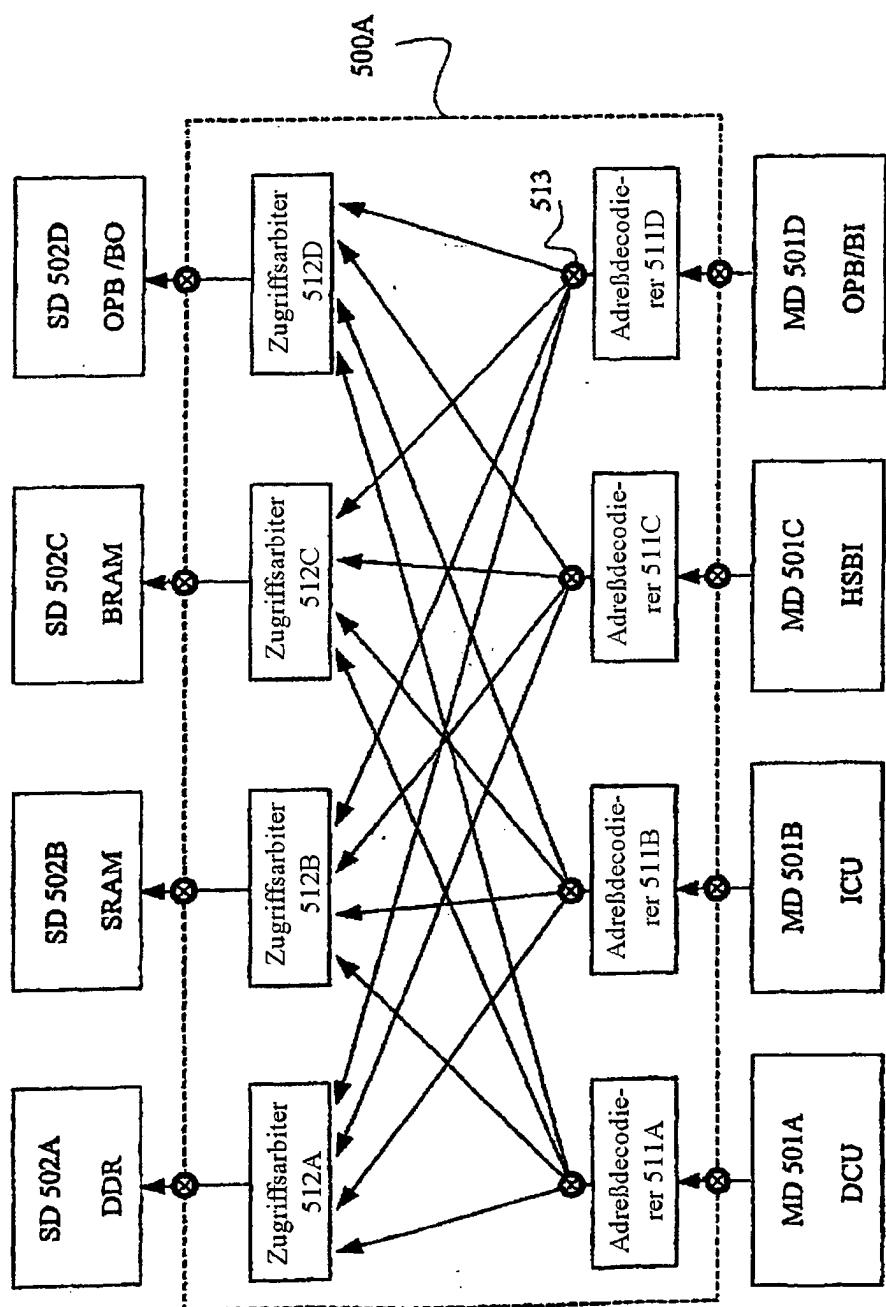

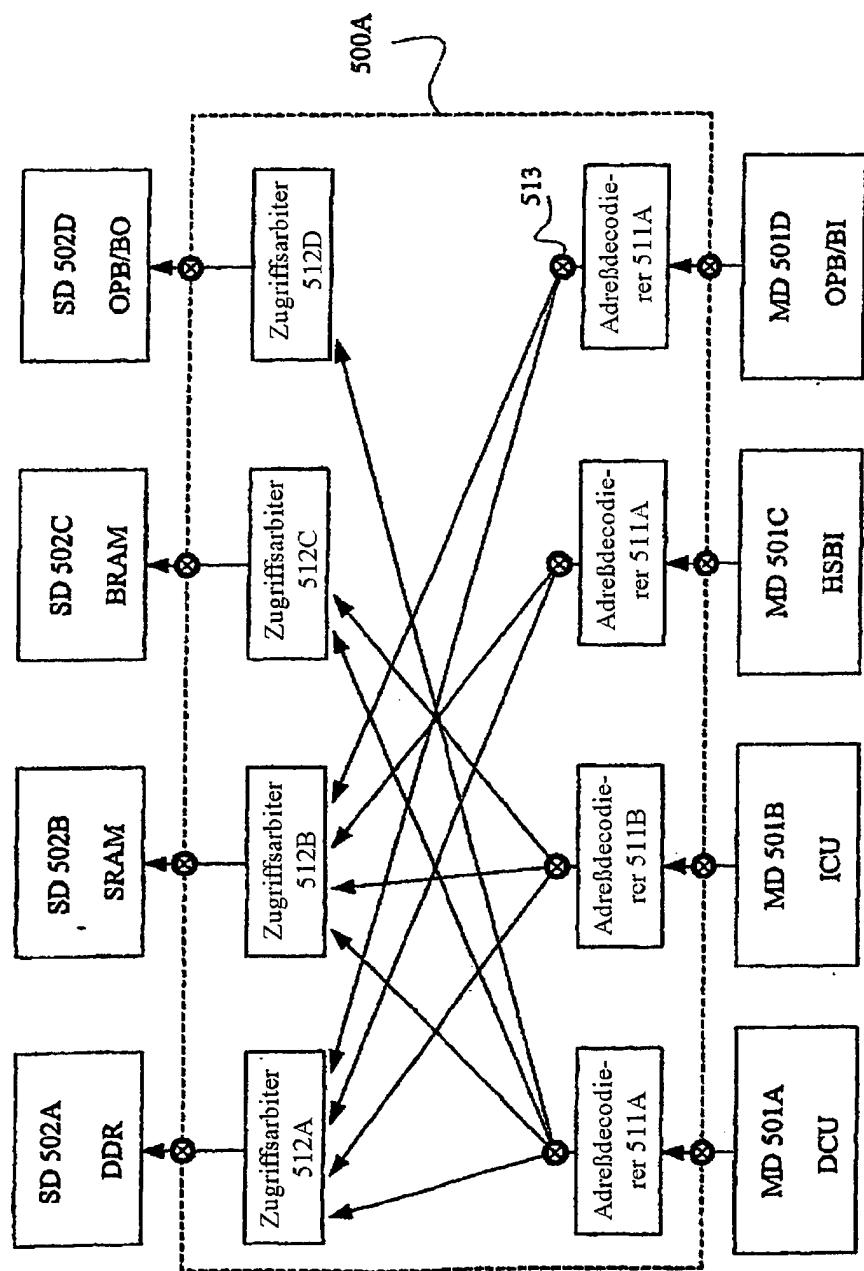

**[0015]** Bei einer Ausführungsform der vorliegenden Erfindung enthält die programmierbare Schnittstelle einen Koppelpunkt-Schalter. Bei der Adress/Steuerlogik kann der Koppelpunkt-Schalter mehrere Adressdecodierer für das Empfangen von Adressen aus den Masters und mehrere Zugriffsarbiter für das Empfangen decodierter Adressen aus den Adressdecodierern und das Arbitrieren von Transaktionen zwischen den Masters und den Slaves enthalten. Der Koppelpunkt-Schalter kann für eine vollständige oder unvollständige Konnektivität zwischen den Adressdecodierern und den Zugriffsarbitern sorgen.

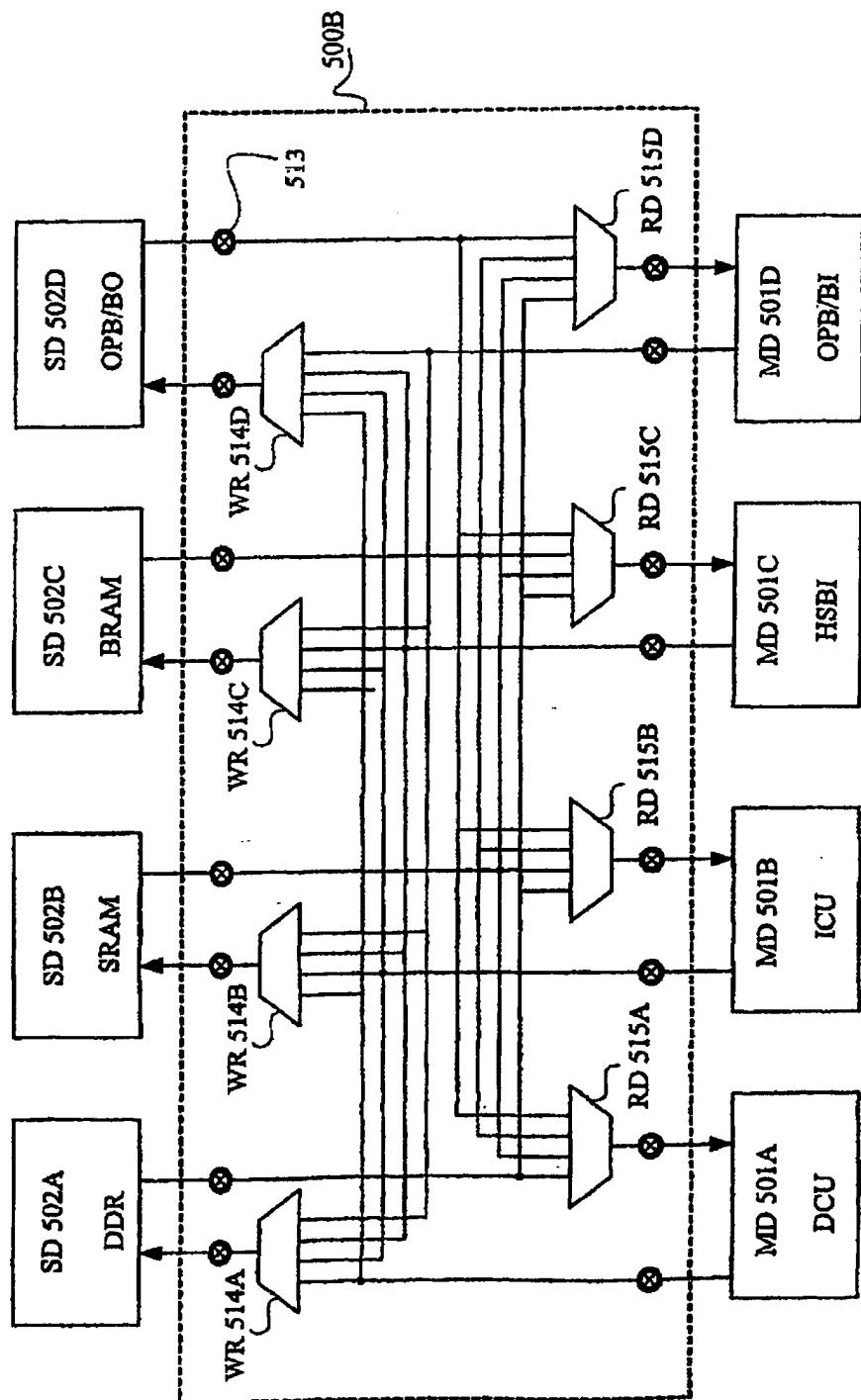

**[0016]** Bei der Datenlogik kann der Koppelpunkt-Schalter mehrere Schreibmultiplexer für das Empfangen von Schreibdaten aus den Masters enthalten, wobei jeder Schreibmultiplexer die Schreibdaten gezielt einem Slave zur Verfügung stellt, und mehrere Lesemultiplexer für das Empfangen von Lesedaten aus den Slaves, wobei jeder Lesemultiplexer die Lesedaten gezielt einem Master zur Verfügung stellt. Die Schreib- und die Lesemultiplexer können von den mehreren Zugriffsarbitern gesteuert werden. Der Koppelpunkt-Schalter kann für eine vollständige oder unvollständige Konnektivität zwischen jedem Schreibmultiplexer und den mehreren Master-Vorrichtungen sorgen. Der Koppelpunkt-Schalter kann ebenso für eine vollständige oder unvollständige Konnektivität zwischen jedem Lesemultiplexer und den mehreren Slave-Vorrichtungen sorgen. Bei einer Ausführungsform enthält die Adress/Steuer- und/oder die Datenlogik des weiteren Register für das Pipelining von Transaktionen zwischen den Masters und den Slaves.

**[0017]** Gemäß einer anderen Ausführungsform der vorliegenden Erfindung enthält ein anwenderprogrammierbares Gate-Array (FPGA) mit einer integrierten zentralen Verarbeitungseinheit (CPU) einen von einem Kern erzeugten Hybridschalter, wobei der Hybridschalter für die Kommunikation zwischen der CPU und der auf dem FPGA implementierten Anwenderlogik sorgt. Bei dieser Ausführungsform enthält die CPU eine Master-Vorrichtung, und die Logik weist mehrere Slave-Vorrichtungen und mehrere Master-Vorrichtungen auf. Dieser Hybridschalter enthält sowohl Koppelpunkt-Konfigurationen als auch Konfigurationen mit gemeinsam genutztem Bus, die Wege zwischen den Master-Vorrichtungen und den Slave-Vorrichtungen bereitstellen.

**[0018]** Insbesondere enthält der Hybridschalter mehrere Adressdecodierer für das Empfangen von Adressen aus den Masters und mehrere Zugriffsarbiter für das Empfangen decodierter Adressen aus den Adressdecodierern und das Arbitrieren von Transaktionen zwischen den Masters und den Slaves. Mindestens ein Zugriffsarbiter sorgt für die Arbitrierung von mehr als einem Slave, und mindestens ein Zugriffsarbiter sorgt für die Arbitrierung von nur einem Slave. Der Koppelpunkt-Schalter kann ebenso mehrere Schreibmultiplexer für das Empfangen von Schreibdaten aus den Masters und für das Zuführen von Schreibdaten zu dem Slave enthalten. Bei einer Ausführungsform führt mindestens ein Schreibmultiplexer seine Schreibdaten mehr als einem Slave zu, und mindestens ein Schreibmultiplexer führt seine Schreibdaten nur einem Slave zu. Der Koppelpunkt-Schalter kann ebenso mehrere Lesemultiplexer für das Empfangen von Lesedaten aus den Slaves und für das gezielte Zuführen der Lesedaten zu den Masters enthalten. Bei einer Ausführungsform führt mindestens ein Lesemultiplexer seine Lesedaten mehr als einem Master zu, und mindestens ein Lesemultiplexer führt

seine Lesedaten nur einem Master zu. Die Schreib- und die Lesemultiplexer können von den mehreren Zugriffsschaltern gesteuert werden. Der Hybridschalter kann wie der Koppelpunkt-Schalter der vorliegenden Erfindung Pipelining für Transaktionen zwischen den Masters und den Slaves enthalten.

**[0019]** Gemäß einer Ausführungsform der vorliegenden Erfindung enthält ein anwenderprogrammierbares Gate-Array (FPGA) mehrere Master-Vorrichtungen, wobei ein integrierter Mikroprozessor mindestens aus einer solchen Master-Vorrichtung, mehreren Slave-Vorrichtungen und einem Mittel für das gezielte Bereitstellen von Konnektivität zwischen den mehreren Master-Vorrichtungen und den mehreren Slave-Vorrichtungen besteht. Das Mittel für das gezielte Bereitstellen von Konnektivität kann durch einen Kern erzeugt werden.

**[0020]** Bei der Adress/Steuerlogik kann das Mittel für das gezielte Bereitstellen von vollständiger Konnektivität ein Mittel für das Decodieren von Adressen aus den Master-Vorrichtungen und ein Mittel für die Arbitrierung von Transaktionen zwischen den mehreren Master-Vorrichtungen und den mehreren Slave-Vorrichtungen auf der Grundlage der decodierten Adressen enthalten. Bei einer Ausführungsform sorgt das Mittel für das gezielte Bereitstellen von Konnektivität für vollständige Konnektivität zwischen dem Mittel für das Decodieren und dem Mittel für die Arbitrierung, während das Mittel für das gezielte Bereitstellen von Konnektivität bei anderen Ausführungsformen für eine unvollständige Konnektivität zwischen dem Mittel für das Decodieren und dem Mittel für die Arbitrierung sorgt.

**[0021]** Bei der Datenlogik kann das Mittel für das gezielte Bereitstellen von Konnektivität ein Mittel für das Empfangen von Schreibdaten aus den mehreren Master-Vorrichtungen und das gezielte Zuführen der Schreibdaten zu vorgesehenen Slave-Vorrichtungen enthalten und ein Mittel für das Empfangen von Lesedaten aus den mehreren Slave-Vorrichtungen und das gezielte Zuführen der Lesedaten zu vorgesehenen Master-Vorrichtungen. Bei einer Ausführungsform werden das Mittel für das Empfangen der Schreibdaten und das Mittel für das Empfangen der Lesedaten von dem Mittel für die Arbitrierung gesteuert.

**[0022]** Das Mittel für das gezielte Bereitstellen von Konnektivität kann für eine vollständige oder unvollständige Konnektivität zwischen dem Mittel für das Empfangen von Schreibdaten und den mehreren Master-Vorrichtungen sorgen. Außerdem kann das Mittel für das gezielte Bereitstellen von Konnektivität für eine vollständige oder unvollständige Konnektivität zwischen dem Mittel für das Empfangen von Lesedaten und den mehreren Slave-Vorrichtungen sorgen.

**[0023]** Die vorliegende Erfindung kann vorteilhafterweise in bekannten PLD-Software-Tools enthalten sein. Bei einer Ausführungsform kann ein Kerngenerator, der durch Tools auf Systemebene aktiviert wird, einen von Dritten bereitgestellten programmierbaren Schnittstellenkern der vorliegenden Erfindung aufnehmen. Alternativ dazu kann der Kerngenerator einen programmierbaren Schnittstellenkern verwenden, der in einem Satz Bibliotheken bereitgestellt wird, die Bestandteil des Kerngenerators sind. Wenn der programmierbare Schnittstellenkern ausgewählt worden ist, kann er einem PLD-Software-Tool zur Verfügung gestellt werden. Diese Software kann ebenfalls von einem Anwender eine Struktur auf oberster Ebene erhalten. Dieses PLD-Software-Tool erzeugt den Konfigurationsbitstrom, der eine PLD so programmiert, dass sie die von dem programmierbaren Schnittstellenkern und der Struktur auf oberster Ebene vorgesehenen Funktionen bereitstellt.

**[0024]** Es ist wichtig, dass der programmierbare Schnittstellenkern der vorliegenden Erfindung mehrere Compliance-Ebenen aufweisen kann. Ein Kern kann beispielsweise nur eine bestimmte Funktionalität bei der PLD zulassen. Bei einer Ausführungsform ist beispielsweise eine Teilmenge der Funktionen des Prozessor-Local-Busses (PLB) zugelassen. Bei anderen Ausführungsformen, wie den Ausführungsformen, die bestehendes IP oder nicht parametrisiertes IP enthalten, könnte die vorliegende Erfindung die Teilmenge auf die Funktionalität zurechtschneiden, die von diesem IP gefordert wird (oder auf eine vorgegebene Compliance-Ebene auf der Grundlage dieses IP).

**[0025]** Gemäß der vorliegenden Erfindung wird ein Verfahren für das Bereitstellen einer Schnittstelle zwischen einer zentralen Verarbeitungseinheit (CPU) auf einer programmierbaren Logikvorrichtung (PLD) und vom Anwender implementierter Logik auf der PLD angegeben. Das Verfahren umfaßt das gezielte Bereitstellen von Konnektivität zwischen mehreren von der Logik bereitgestellten Master-Vorrichtungen und mehreren von der Logik bereitgestellten Slave-Vorrichtungen, wobei zur CPU mindestens eine Master-Vorrichtung gehört. Zu dem Schritt des gezielten Bereitstellens von Konnektivität im Verlauf der Adress/Steuerlogik gehört das Decodieren von Adressen aus den Master-Vorrichtungen mit Hilfe von Adressdecodierern und das Arbitrieren von Transaktionen zwischen den mehreren Master-Vorrichtungen und den mehreren Slave-Vorrichtungen mit Hilfe von Zugriffsschaltern und der decodierten Adressen. Bei einer Ausführungsform sorgt der Schritt des gezielten Bereitstellens von Konnektivität für vollständige Konnektivität zwischen den Adressdecodierern und den

Zugriffssarbitern. Bei einer weiteren Ausführungsform sorgt der Schritt des gezielten Bereitstellens von Konnektivität für eine unvollständige Konnektivität zwischen den Adreßdecodierern und den Zugriffssarbitern.

**[0026]** Bei dem Verfahren der vorliegenden Erfindung gehört zu dem Schritt des gezielten Bereitstellens von Konnektivität in der Datenlogik das Empfangen von Schreibdaten aus den mehreren Master-Vorrichtungen und das gezielte Zuführen der Schreibdaten zu vorgesehenen Slave-Vorrichtungen unter Verwendung eines ersten Satzes Multiplexer sowie das Empfangen von Lesedaten aus den mehreren Slave-Vorrichtungen und das gezielte Zuführen der Lesedaten zu vorgesehenen Master-Vorrichtungen unter Verwendung eines zweiten Satzes Multiplexer. Der Schritt des gezielten Bereitstellens von Konnektivität kann für eine vollständige oder unvollständige Konnektivität zwischen dem ersten Satz Multiplexer und den mehreren Master-Vorrichtungen sorgen. Der Schritt des gezielten Bereitstellens von Konnektivität kann ebenso für eine vollständige oder unvollständige Konnektivität zwischen dem zweiten Satz Multiplexer und den mehreren Slave-Vorrichtungen sorgen.

**[0027]** Bei dem Verfahren der vorliegenden Erfindung gehört zu dem Schnitt des gezielten Bereitstellens von Konnektivität das Pipelining von Transaktionen zwischen den mehreren Master-Vorrichtungen und den mehreren Slave-Vorrichtungen. Dieses Pipelining kann vorteilhaftweise in der Adreß/Steuerlogik sowie der Datenlogik bereitgestellt werden, wodurch sich bei beiden die Leistung verbessert.

**[0028]** Gemäß der vorliegenden Erfindung wird ein Verfahren für das Bereitstellen einer Schnittstelle zwischen einer zentralen Verarbeitungseinheit (CPU) auf einer programmierbaren Logikvorrichtung (PLD) und vom Anwender implementierter Logik auf der PLD angegeben. Das Verfahren umfaßt das Auswählen eines Kerns aus einer Bibliothek, wobei der Kern gezielt für Konnektivität zwischen mehreren von der Logik bereitgestellten Master-Vorrichtungen und mehreren von der Logik bereitgestellten Slave-Vorrichtungen sorgt, wobei zur CPU mindestens eine Master-Vorrichtung gehört. Zu dem Verfahren gehört des weiteren das Einstellen mindestens eines Parameters in dem Kern, was die Konnektivität beeinflußt.

**[0029]** Bei einer weiteren Ausführungsform wird der Informationsgehalt jedes Kerns, der für den Aufbau des Systems benötigt wird, zur Analyse der Daten in einer zentralen Einrichtung gesammelt. Diese Daten stehen dem Anwender zur Verfügung, damit er bei der Instanziierung von Kernen oder der Parametrisierung Alternativen wählen kann. Eine bestimmte Wahl bei der Parametrisierung des Kerns kann beispielsweise zu einer unterschiedlichen Leistung des Gesamtsystems führen.

**[0030]** Die vorliegende Erfindung bietet im Vergleich zu den üblichen integrierten CPUs in der ASIC-Umgebung eine Anzahl wesentlicher Vorteile. Die vorliegende Erfindung sorgt erstens für beträchtliche Flexibilität, indem sie Funktionen bereitstellt, die auf der Grundlage der Bedürfnisse des Anwenders und/ oder der zugehörigen Struktur parametrisiert werden können. Diese parametrisierten Funktionen können in programmierbaren Ressourcen auf der PLD implementiert werden, wodurch sie jederzeit modifiziert werden können. Zweitens können aufgrund dieser programmierbaren Ressourcen nur die Ressourcen implementiert werden, die tatsächlich für die programmierbare Schnittstelle benötigt werden, wodurch es dem Anwender möglich wird, die Verwendung der restlichen PLD zu optimieren. So können beispielsweise sowohl die Adreß/Steuerlogik als auch die Datenlogik „getrimmt“ werden. Anders ausgedrückt können Wege (und die mit ihnen verbundene Logik), die von der Struktur des Anwenders nicht benötigt werden, eliminiert werden, wodurch sich die Signalschwindigkeit erhöht und die Siliziumfläche verringert. Bei einem weiteren Beispiel kann die Anzahl der Master- oder Slave-Vorrichtungen erhöht werden, da zusätzliche Fläche zur Verfügung steht. Drittens kann die vorliegende Erfindung auf effiziente Weise die Funktionen des Prozessor-Local-Busses einschränken, wodurch die PLD dem Leistungsniveau eines ASIC nahekommen beziehungsweise dieses sogar übersteigen kann.

#### KURZE BESCHREIBUNG DER FIGUREN

**[0031]** [Fig. 1](#) zeigt eine vereinfachte schematische Darstellung eines Mikroprozessors mit einer zentralen Verarbeitungseinheit, einem Prozessor-Local-Bus und einem chipinternen peripheren Bus.

**[0032]** [Fig. 2](#) stellt ein vereinfachtes Blockdiagramm eines konfigurierbaren Logikbausteins bei dem von der Inhaberin der vorliegenden Erfindung vertriebenen FPGA Virtex dar.

**[0033]** [Fig. 3](#) stellt einen IP-Prozeßaufbau für die Verwendung eines oder mehrerer Kerne in einem FPGA dar.

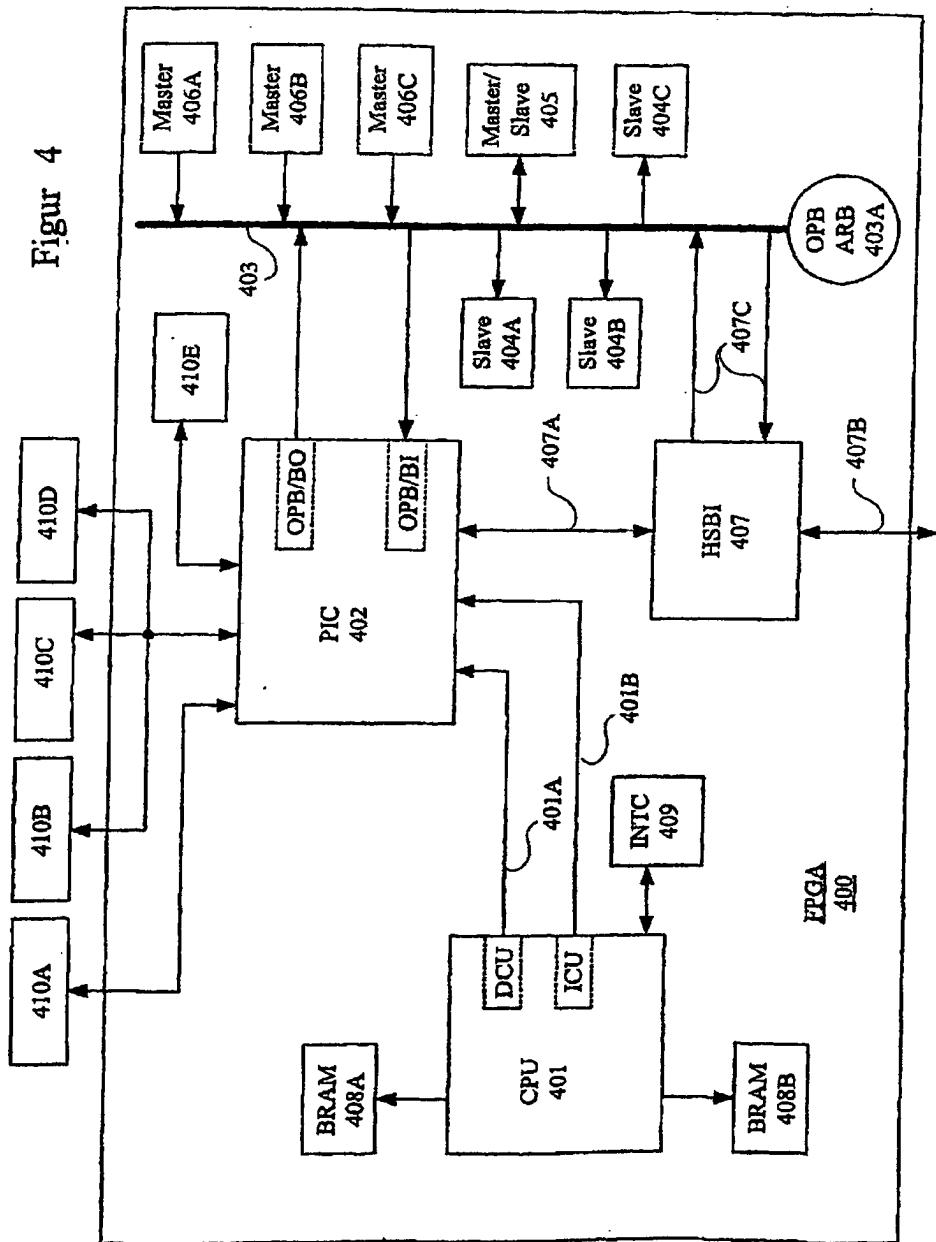

**[0034]** [Fig. 4](#) stellt ein FPGA-Grundsystem mit integriertem Prozessor gemäß der vorliegenden Erfindung dar.

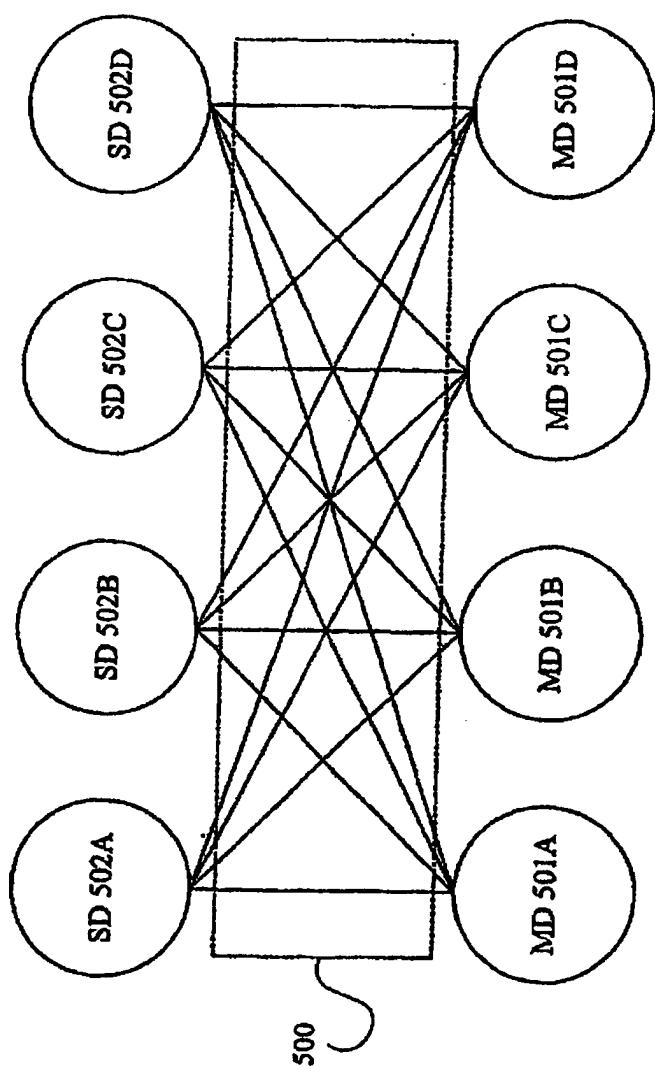

[0035] [Fig. 5A](#) zeigt eine vereinfachte schematische Darstellung eines 4x4-Koppelpunkt-Schalters gemäß der vorliegenden Erfindung.

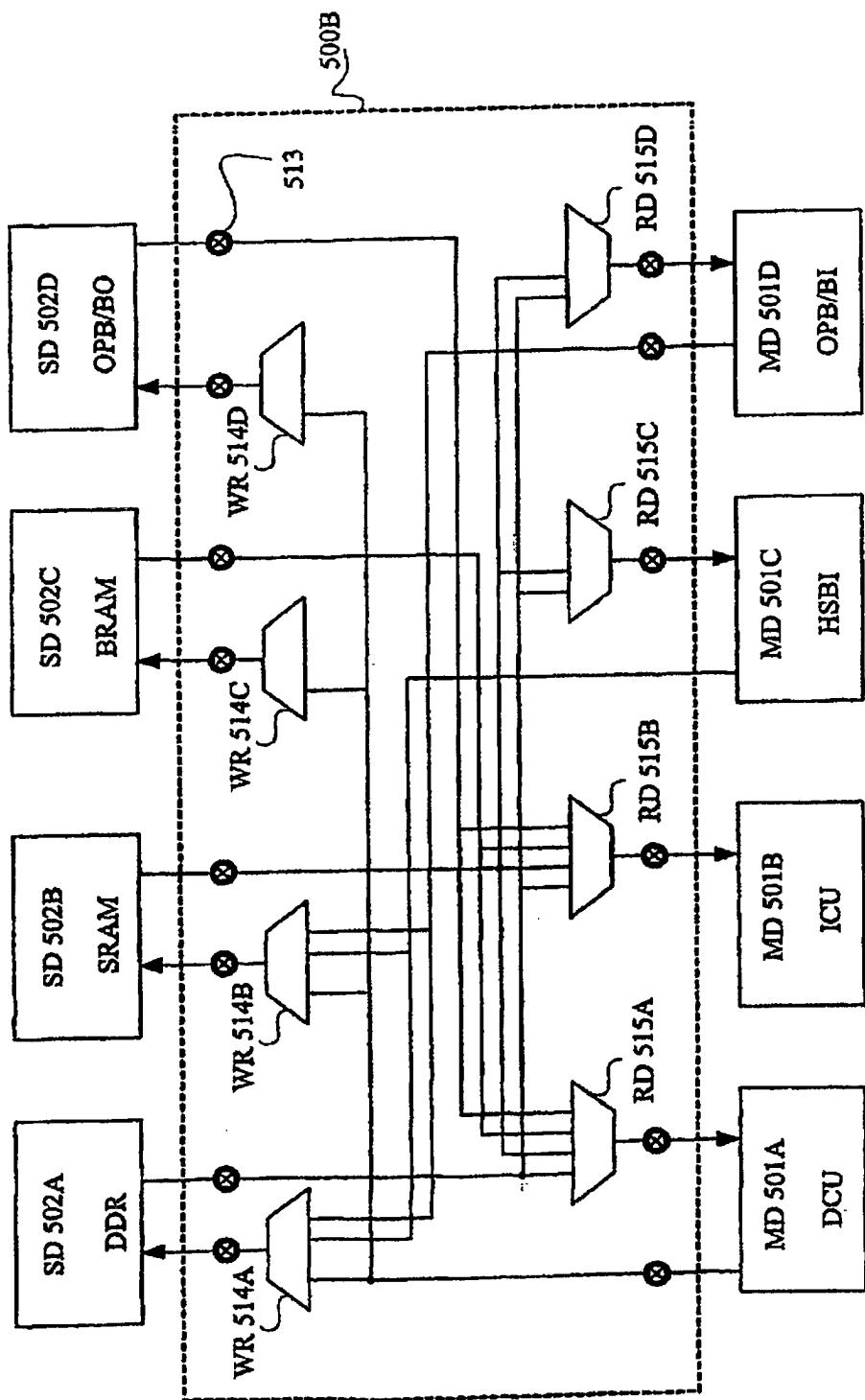

[0036] [Fig. 5B](#) zeigt eine ausführlichere schematische Darstellung einer Implementierung des Koppelpunkt-Schalters aus [Fig. 5A](#) in der Adreßlogik.

[0037] [Fig. 5C](#) zeigt eine ausführlichere schematische Darstellung einer Implementierung des Koppelpunkt-Schalters aus [Fig. 5A](#) in der Datenlogik.

[0038] [Fig. 5D](#) stellt eine Ausführungsform des Koppelpunkt-Schalters aus [Fig. 5B](#) dar, bei der die Adreß/Steuerlogik getrimmt ist.

[0039] [Fig. 5E](#) stellt eine Ausführungsform des Koppelpunkt-Schalters aus [Fig. 5C](#) dar, bei der die Datenlogik getrimmt ist.

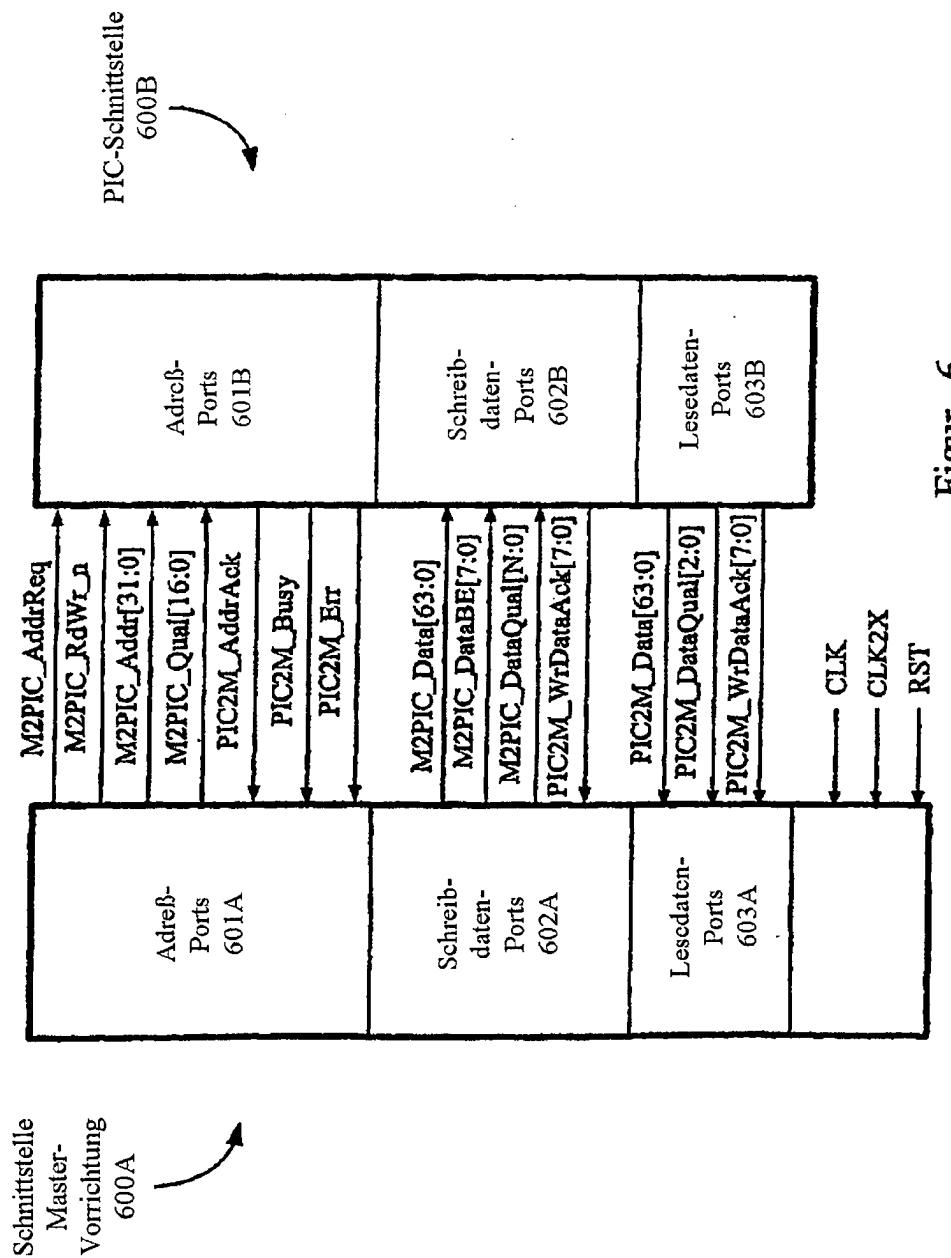

[0040] [Fig. 6](#) stellt eine Übersicht über die für eine Master-Vorrichtung und den programmierbaren Schnittstellenkern der vorliegenden Erfindung bereitgestellten Anschlüsse dar und die Signale, die zwischen diesen Anschlüssen übertragen werden könnten.

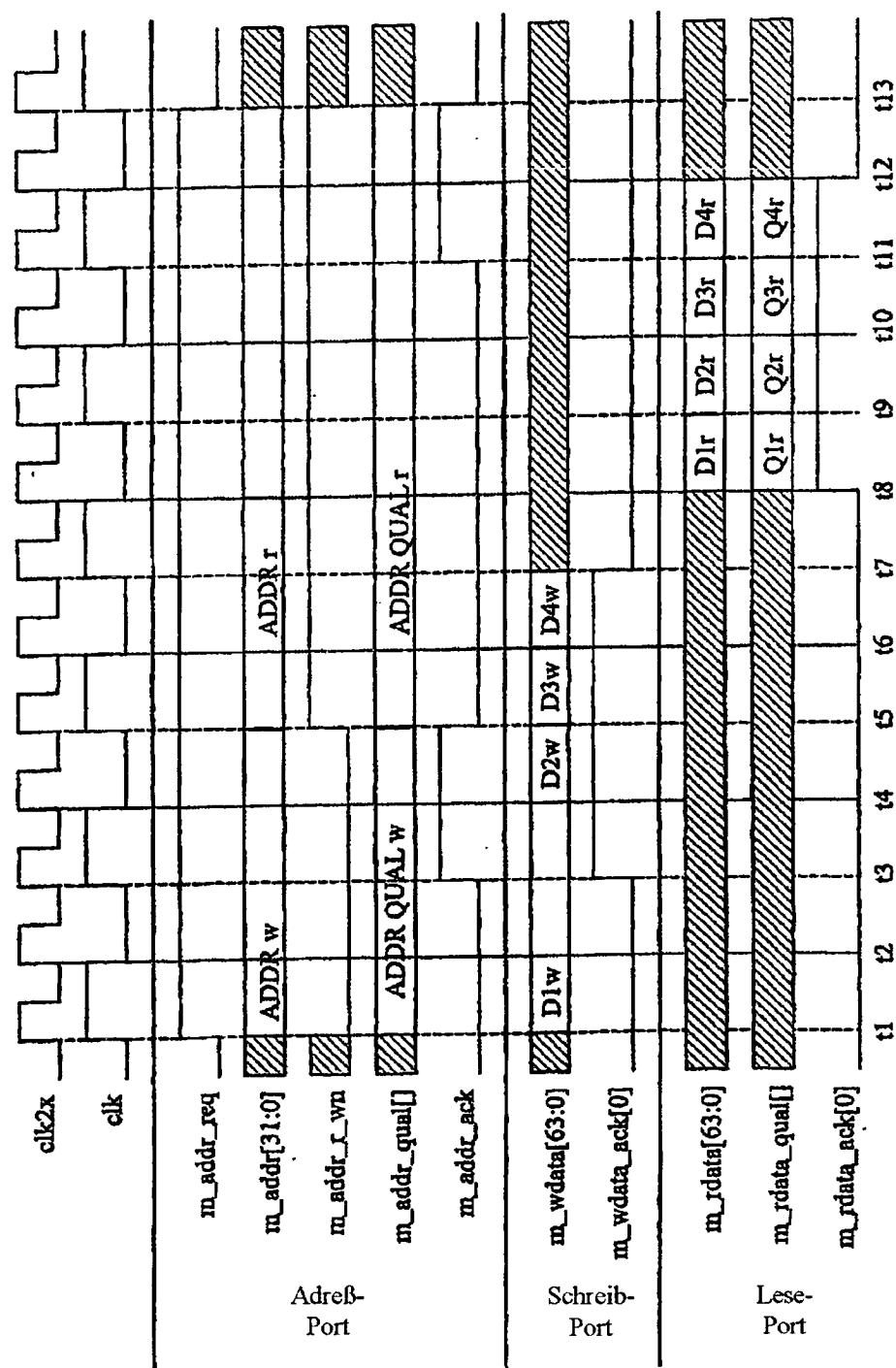

[0041] [Fig. 7](#) stellt ein Zeitdiagramm eines Masters während einer 8-Datenwörter-Schreiboperation dar, der eine 8-Datenwörter-Leseoperation folgt.

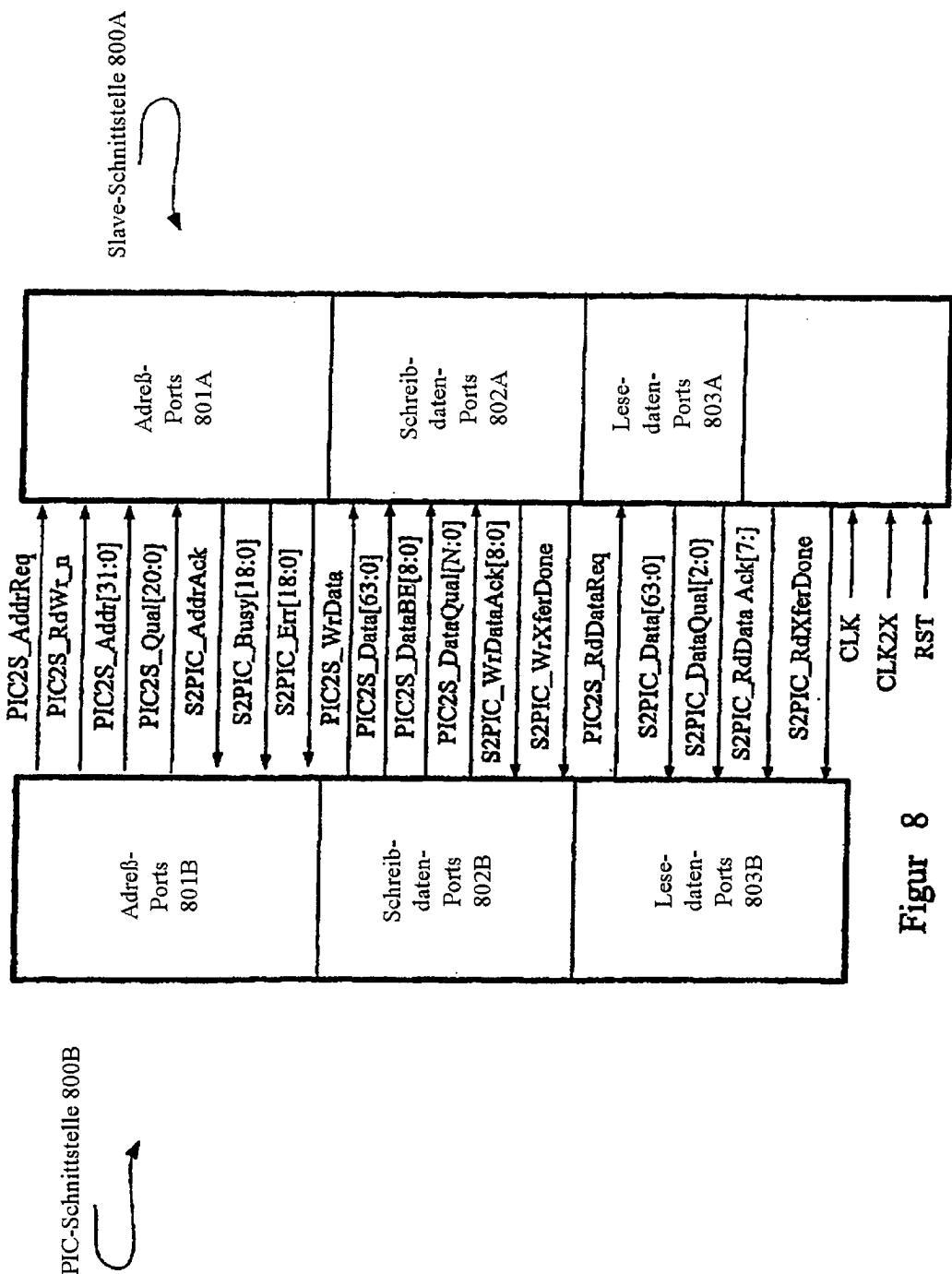

[0042] [Fig. 8](#) stellt eine Übersicht über die für eine Slave-Vorrichtung und den programmierbaren Schnittstellenkern der vorliegenden Erfindung bereitgestellten Ports dar und die Signale, die zwischen diesen Ports übertragen werden könnten.

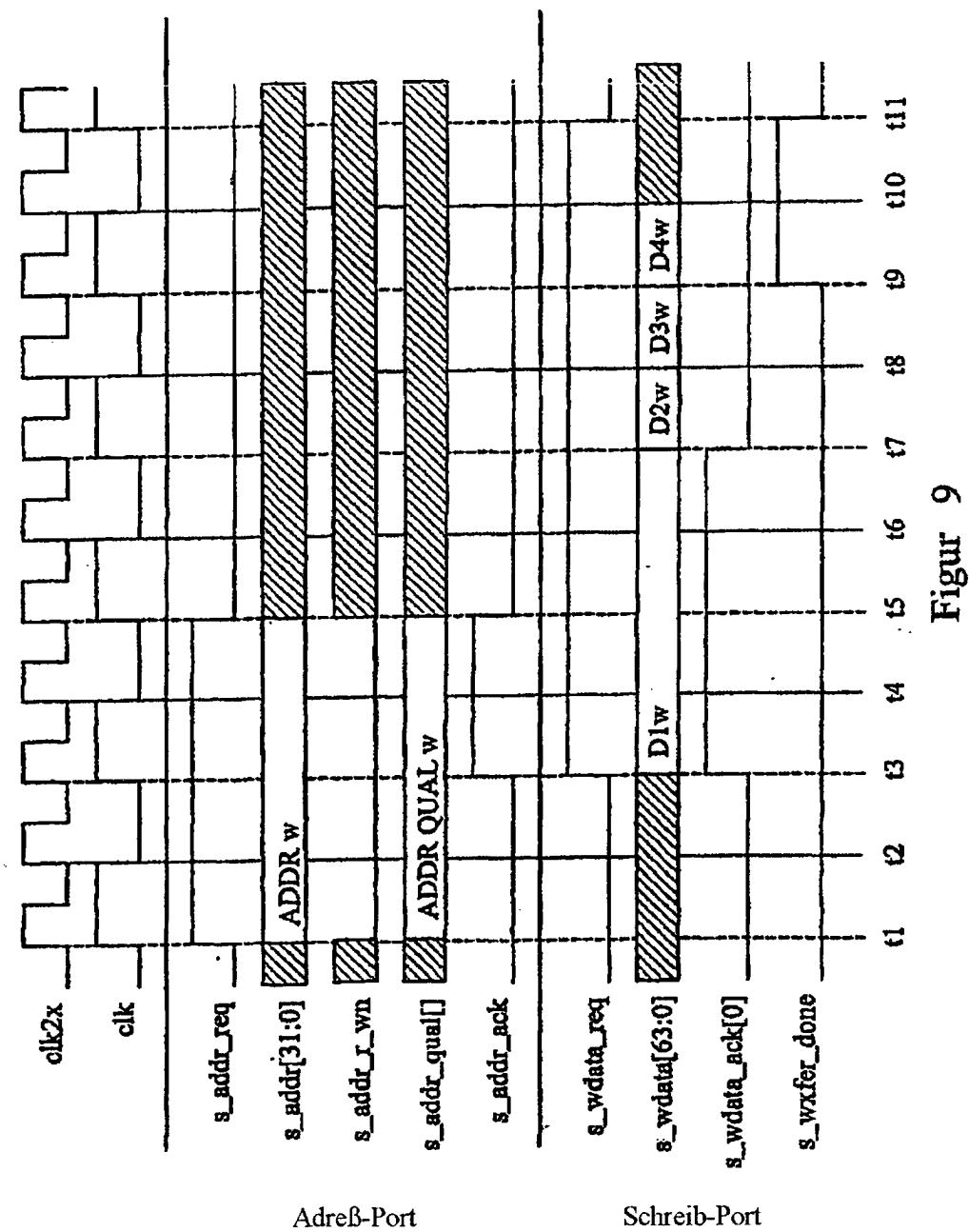

[0043] [Fig. 9](#) stellt ein Zeitdiagramm eines Slaves während einer 8-Datenwörter-Schreiboperation dar.

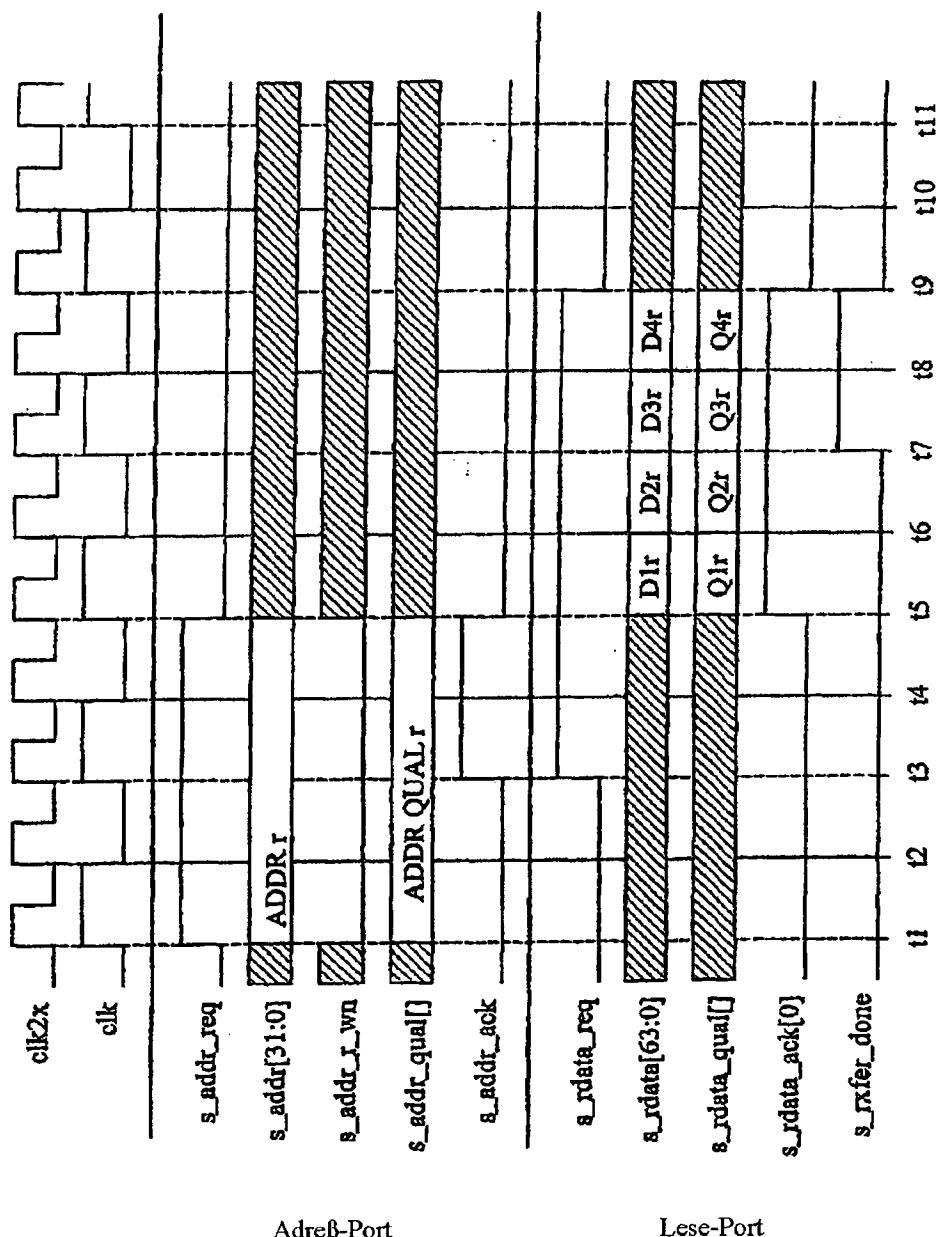

[0044] [Fig. 10](#) stellt ein Zeitdiagramm eines Slaves während einer 8-Datenwörter-Leseoperation dar.

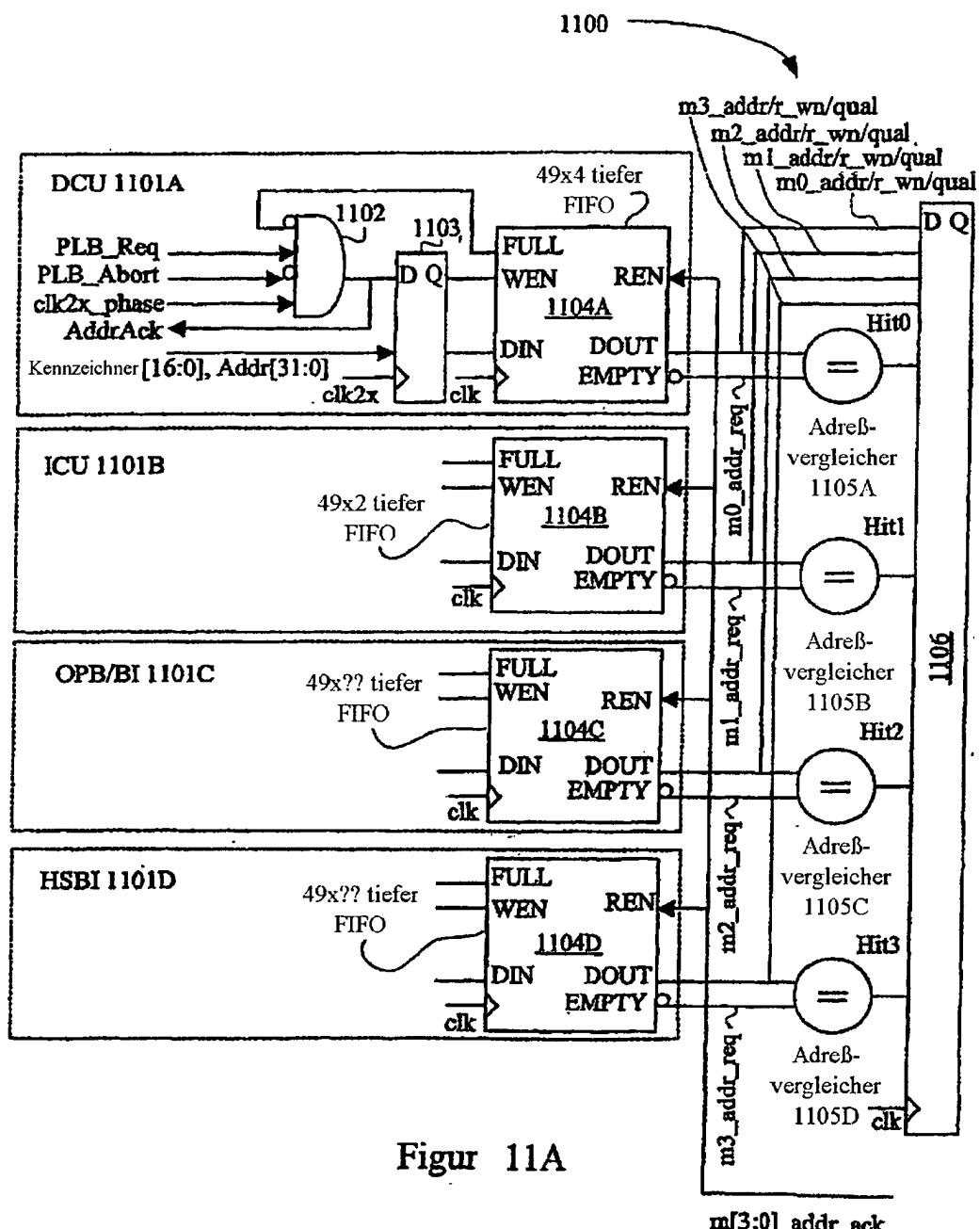

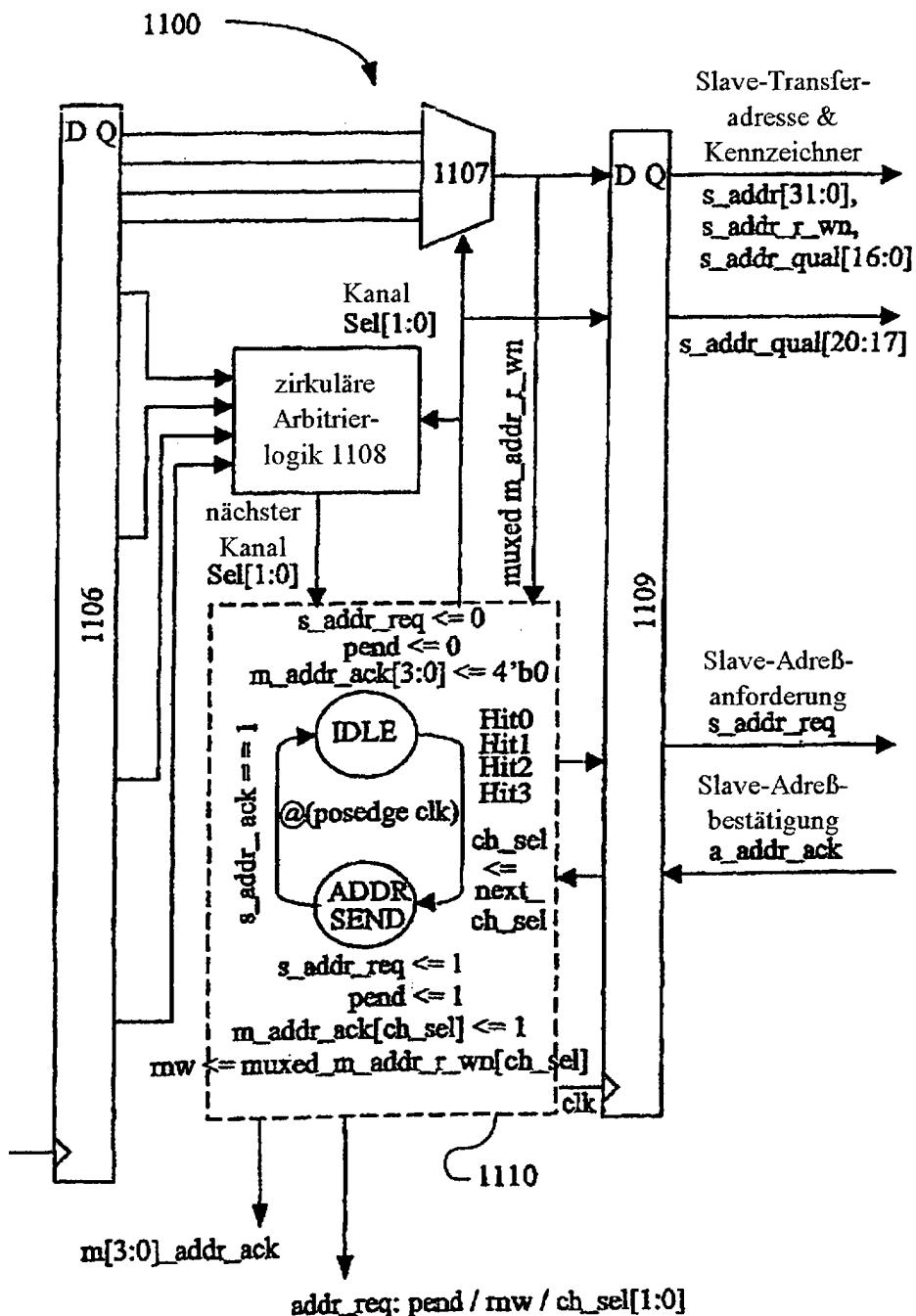

[0045] Die [Fig. 11A](#) und [Fig. 11B](#) stellen eine Ausführungsform der Adreß/Steuerlogik in einem programmierbaren Schnittstellenkern gemäß der vorliegenden Erfindung dar, wobei der Weg verschiedene mit dem Kern verbundene Adreß/Steuerlogiksignale enthält.

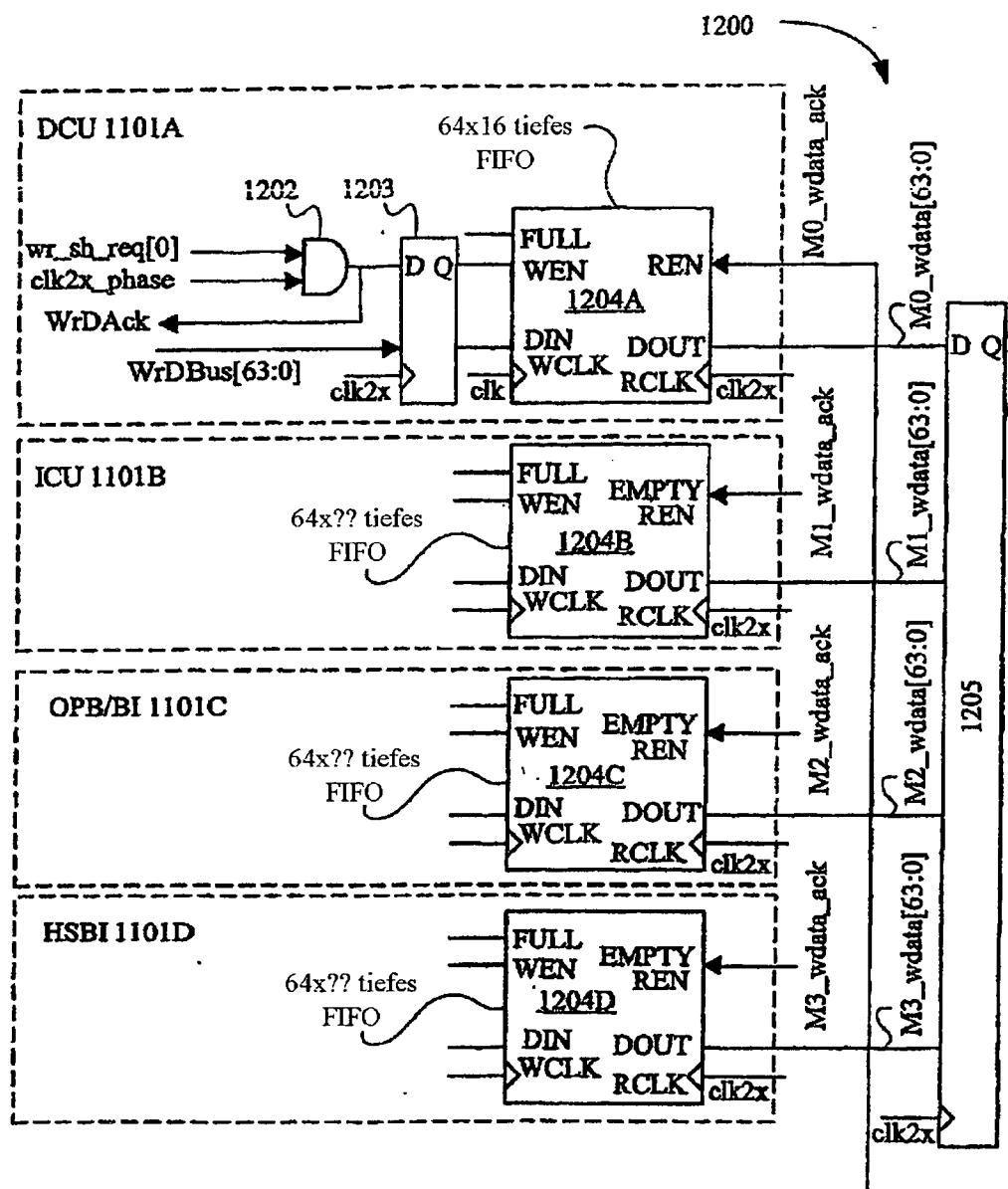

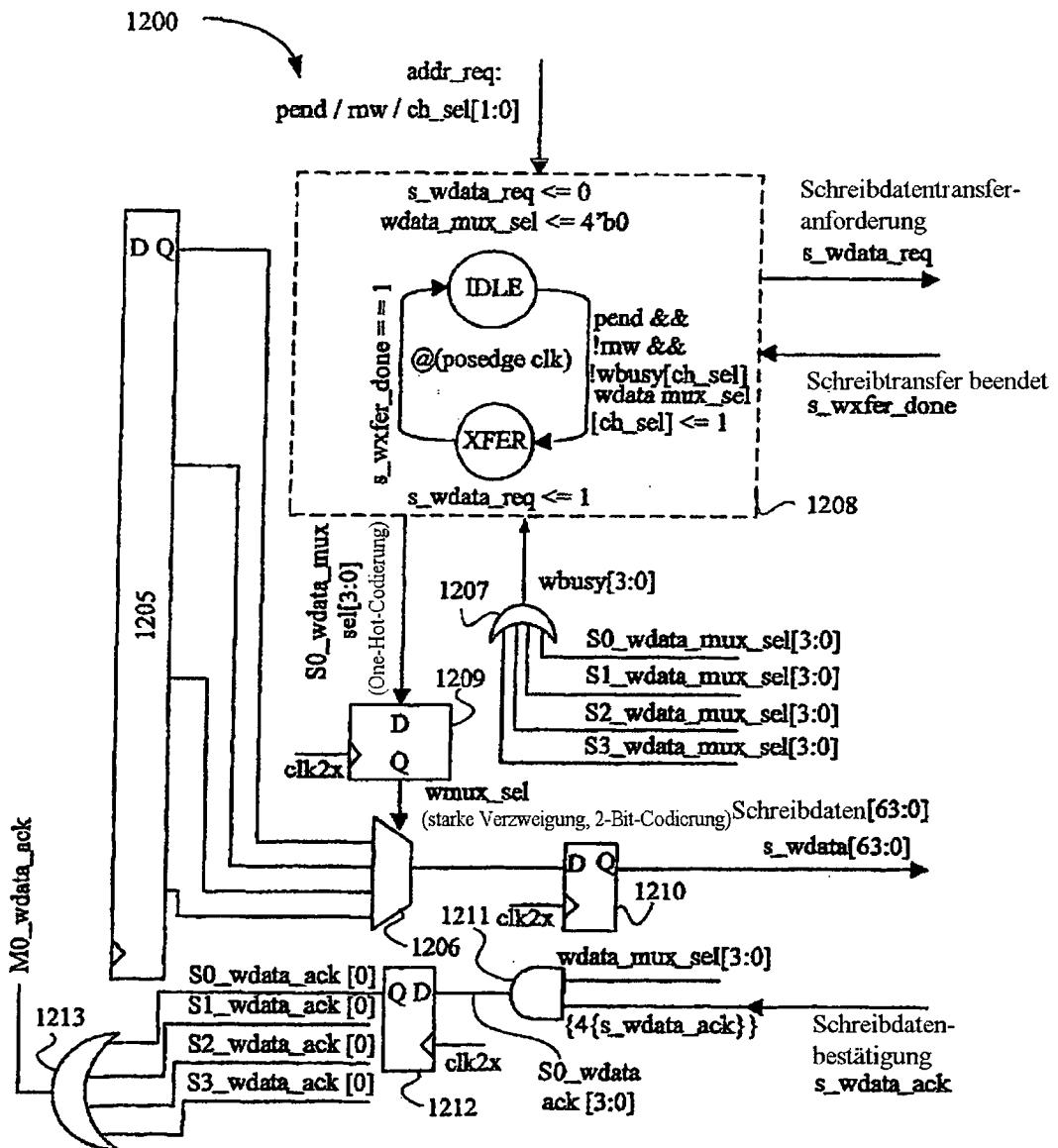

[0046] Die [Fig. 12A](#) und [Fig. 12B](#) stellen eine Ausführungsform der mit der Schreibdatenlogik gemäß der vorliegenden Erfindung verbundenen Schaltungen dar, wobei die Logik verschiedene mit dem Kern verbundene Schreibsignale enthält.

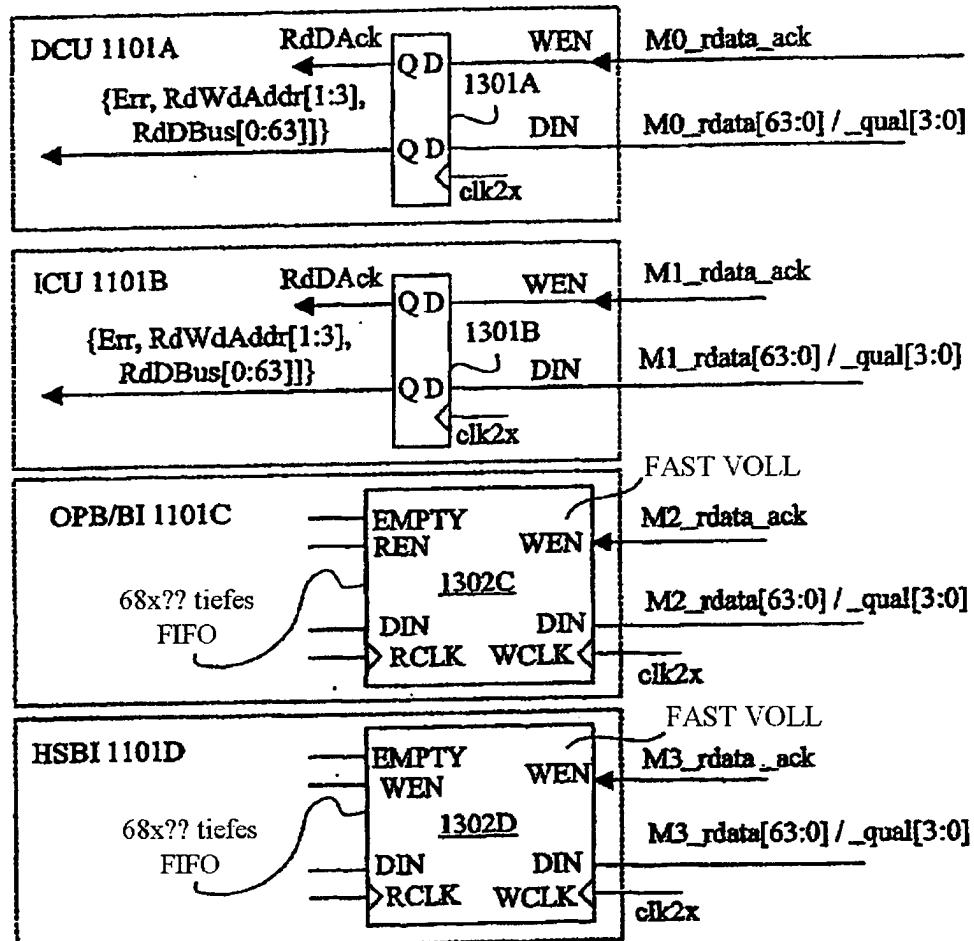

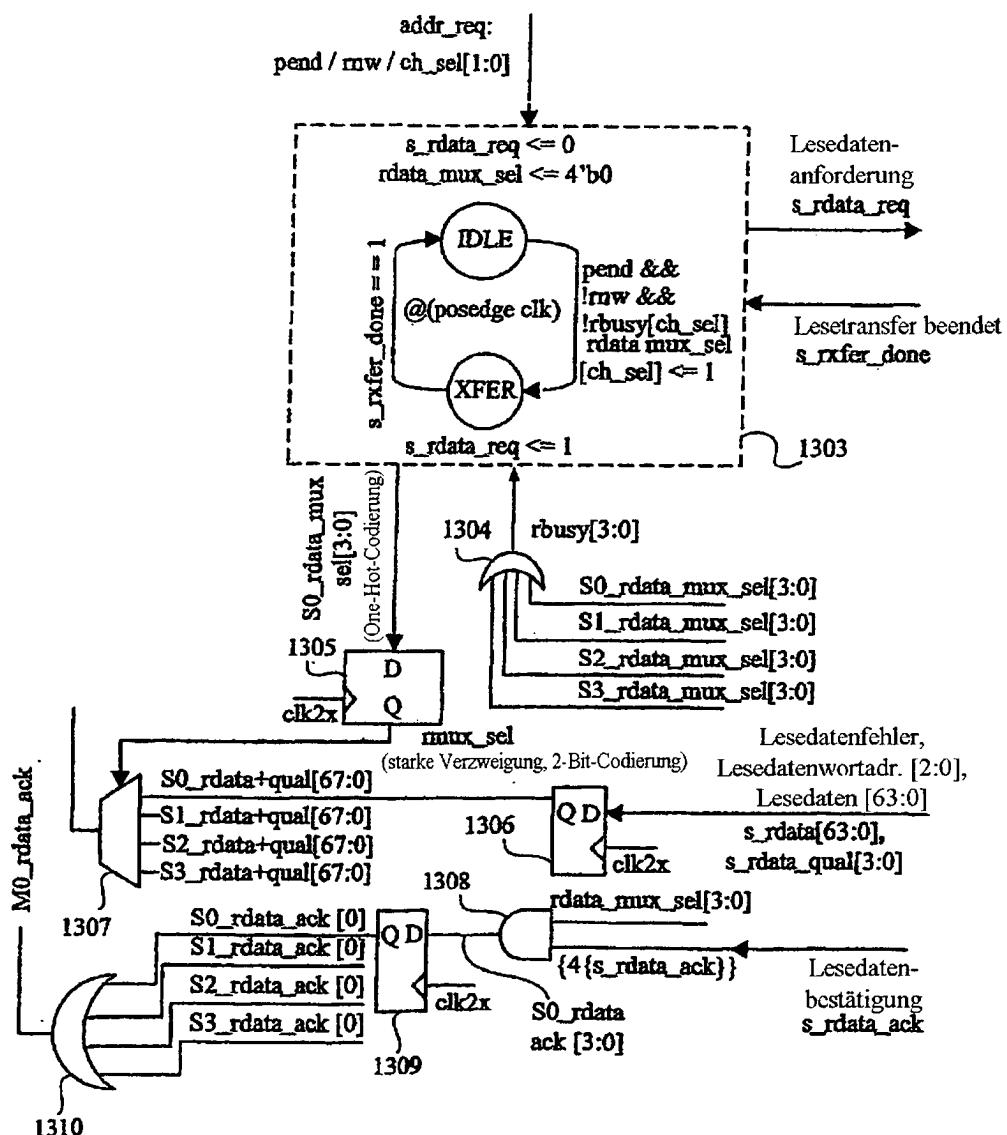

[0047] Die [Fig. 13A](#) und [Fig. 13B](#) stellen eine Ausführungsform der mit der Lesedatenlogik gemäß der vorliegenden Erfindung verbundenen Schaltungen dar, wobei die Logik verschiedene mit dem Kern verbundene Lesesignale enthält.

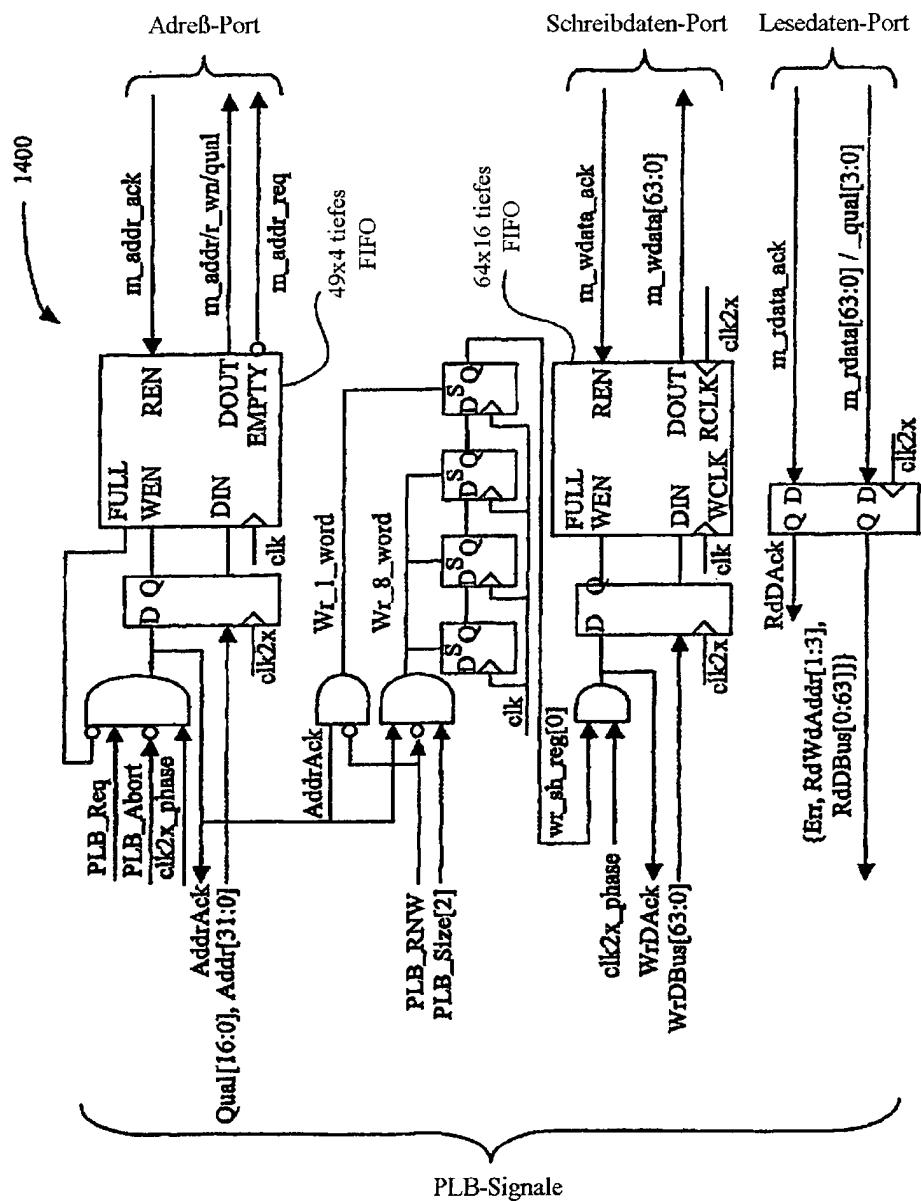

[0048] [Fig. 14](#) stellt eine Ausführungsform der Schnittstelle der Daten-Cache-Speichereinheit oder der Befehls-Cache-Speichereinheit zum Prozessor-Local-Bus dar.

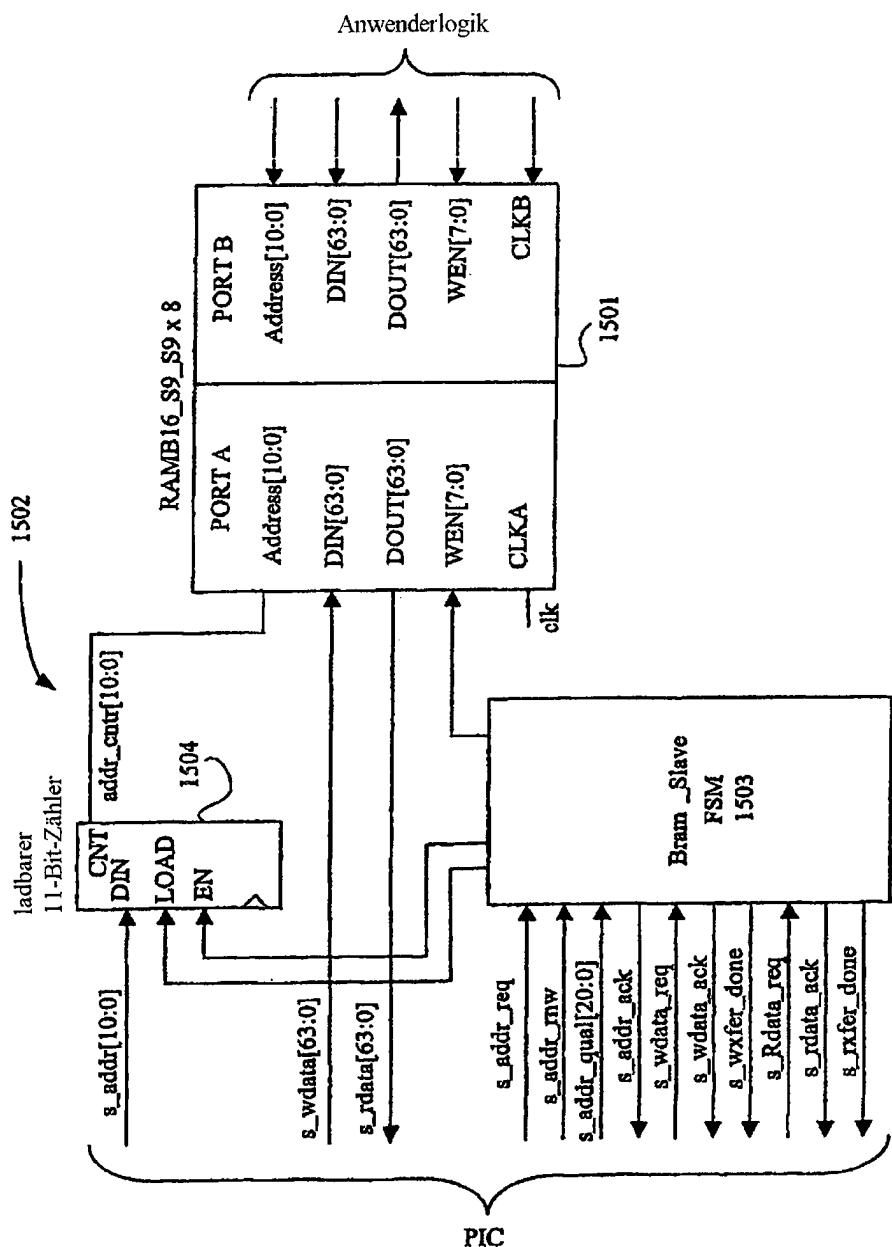

[0049] [Fig. 15](#) stellt die Schnittstelle eines Block-RAM (BRAM) mit Dual-Port-Funktionalität zu dem programmierbaren Schnittstellenkern der vorliegenden Erfindung dar.

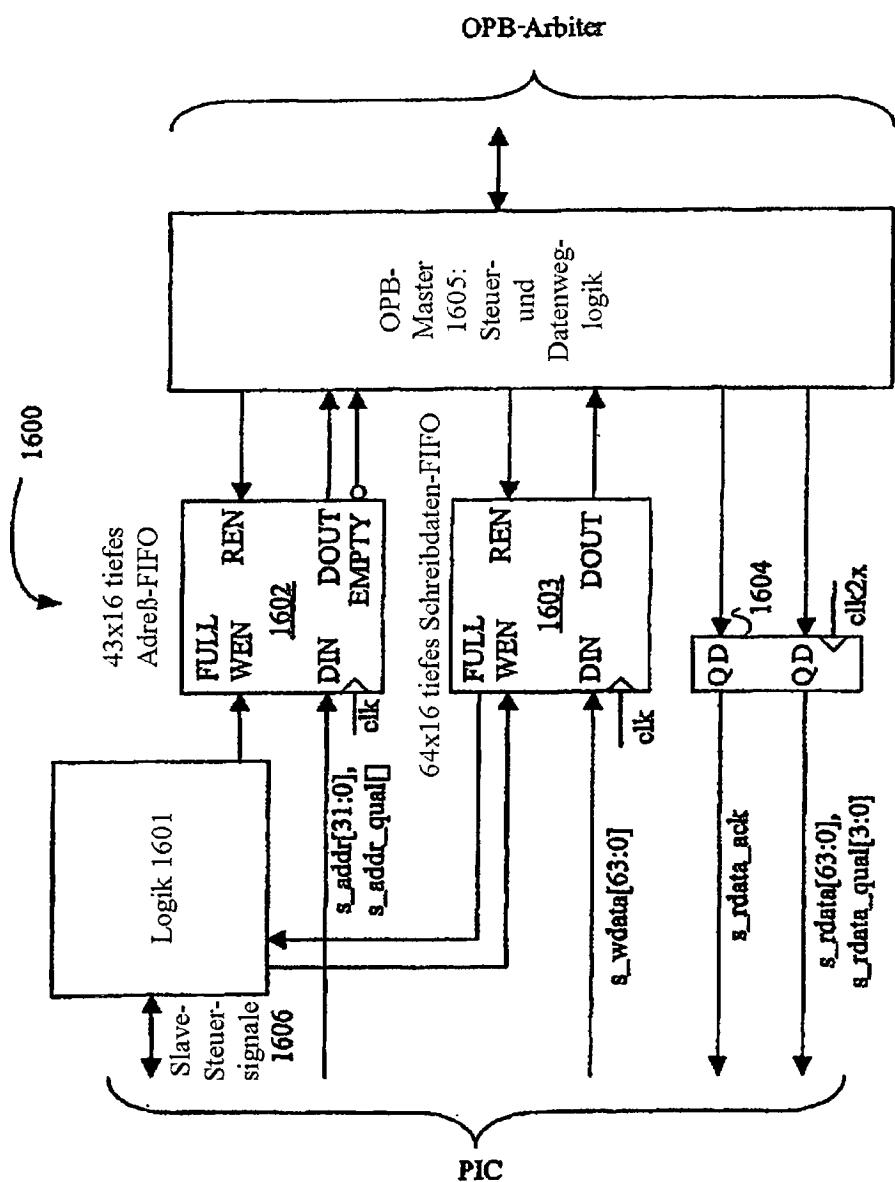

[0050] [Fig. 16](#) zeigt eine schematische Darstellung einer Ausführungsform eines Bridge-out-Moduls auf hoher Ebene in dem programmierbaren Schnittstellenkern gemäß der vorliegenden Erfindung.

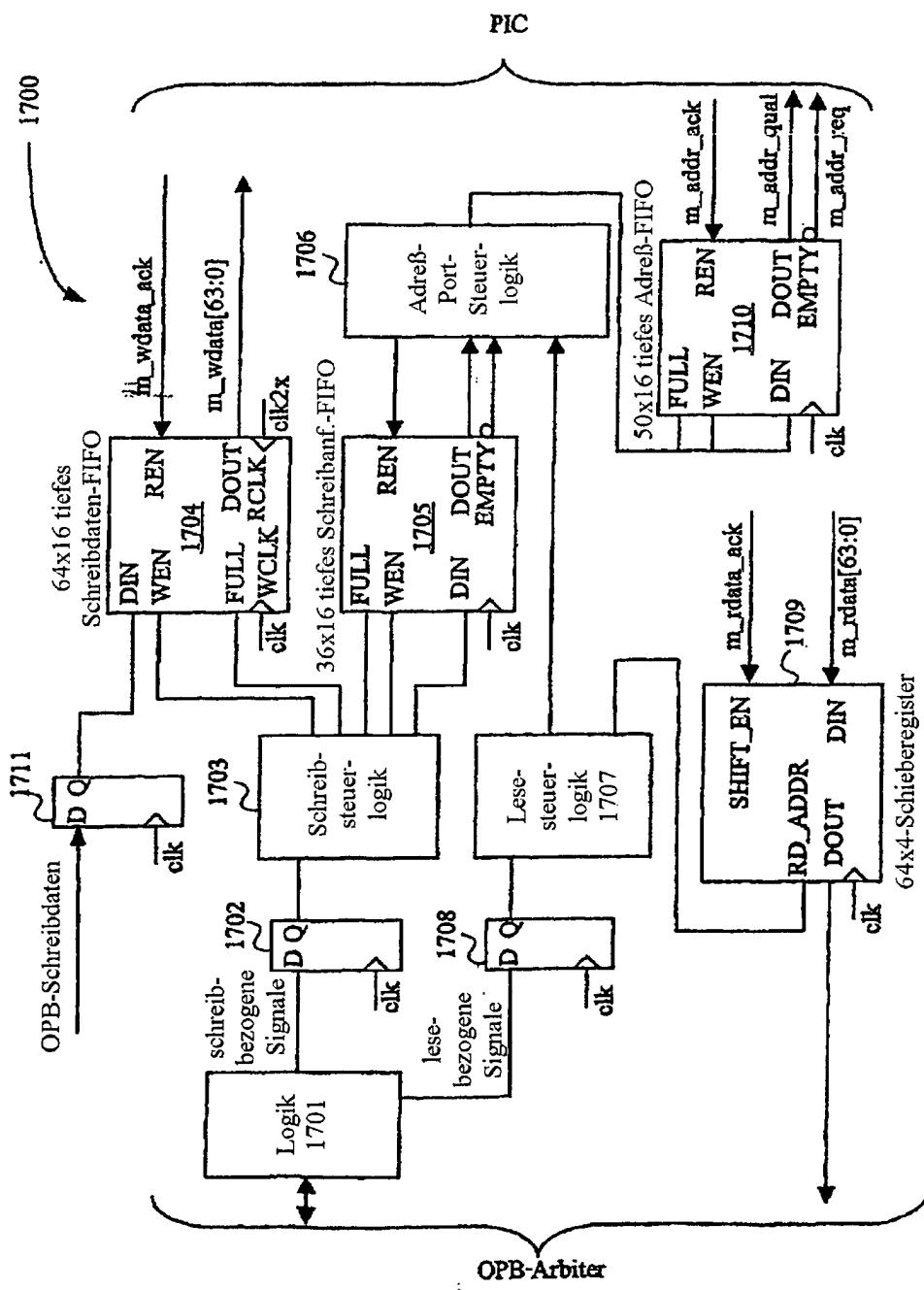

[0051] [Fig. 17](#) zeigt eine schematische Darstellung einer Ausführungsform eines Bridge-in-Moduls auf hoher Ebene in dem programmierbaren Schnittstellenkern gemäß der vorliegenden Erfindung.

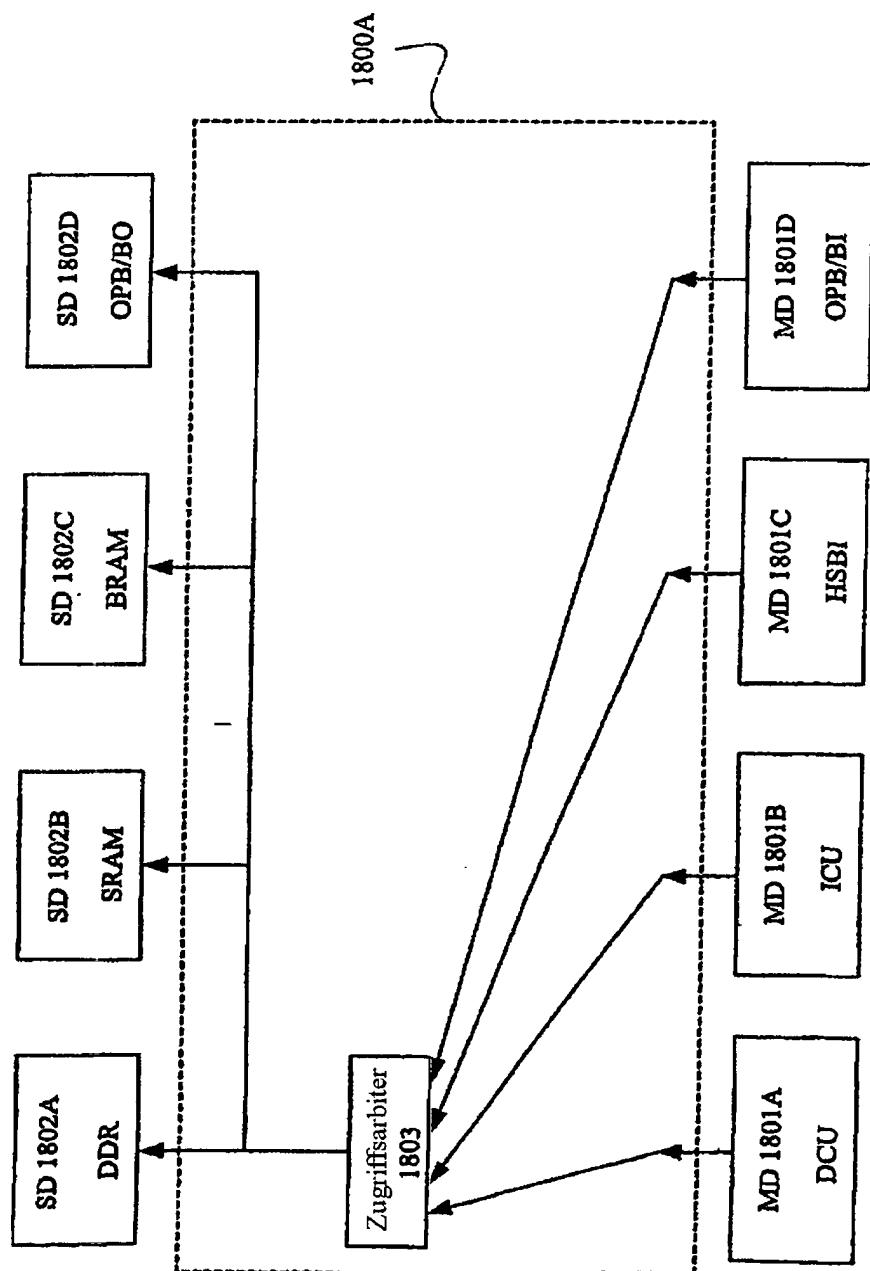

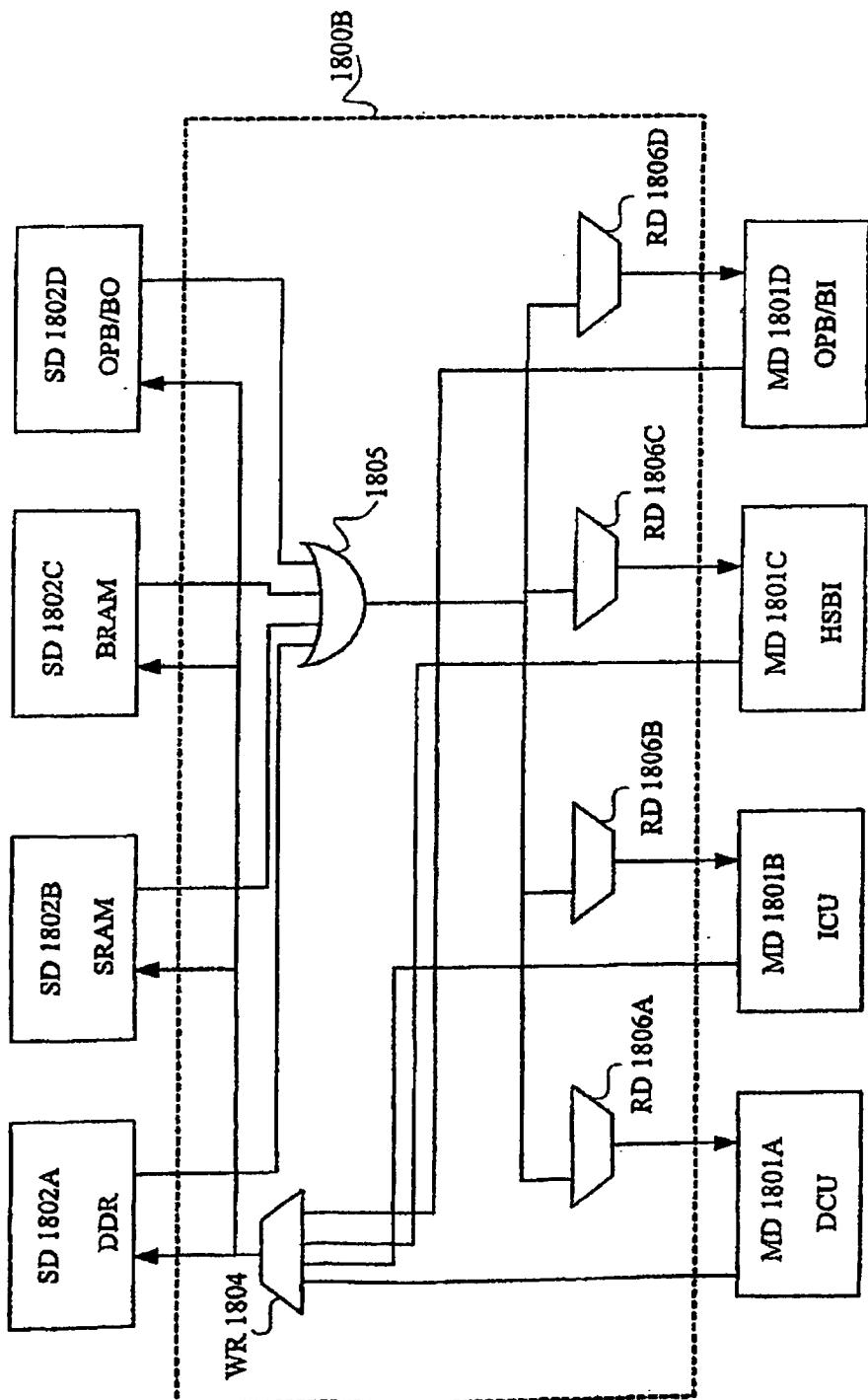

[0052] Die [Fig. 18A](#) und [Fig. 18B](#) stellen die Adreß/Steuerlogik beziehungsweise die Datenlogik einer Architektur mit gemeinsam genutztem Bus dar.

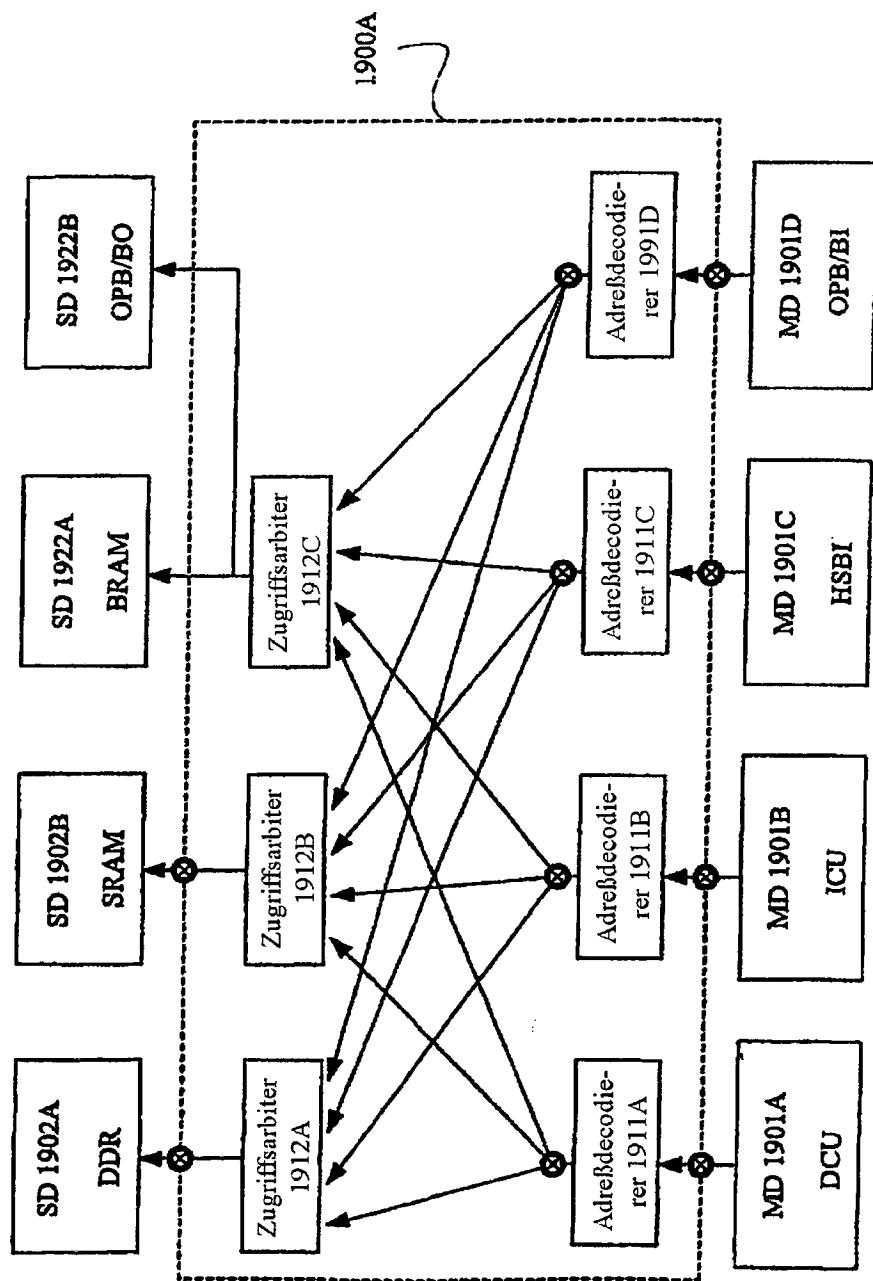

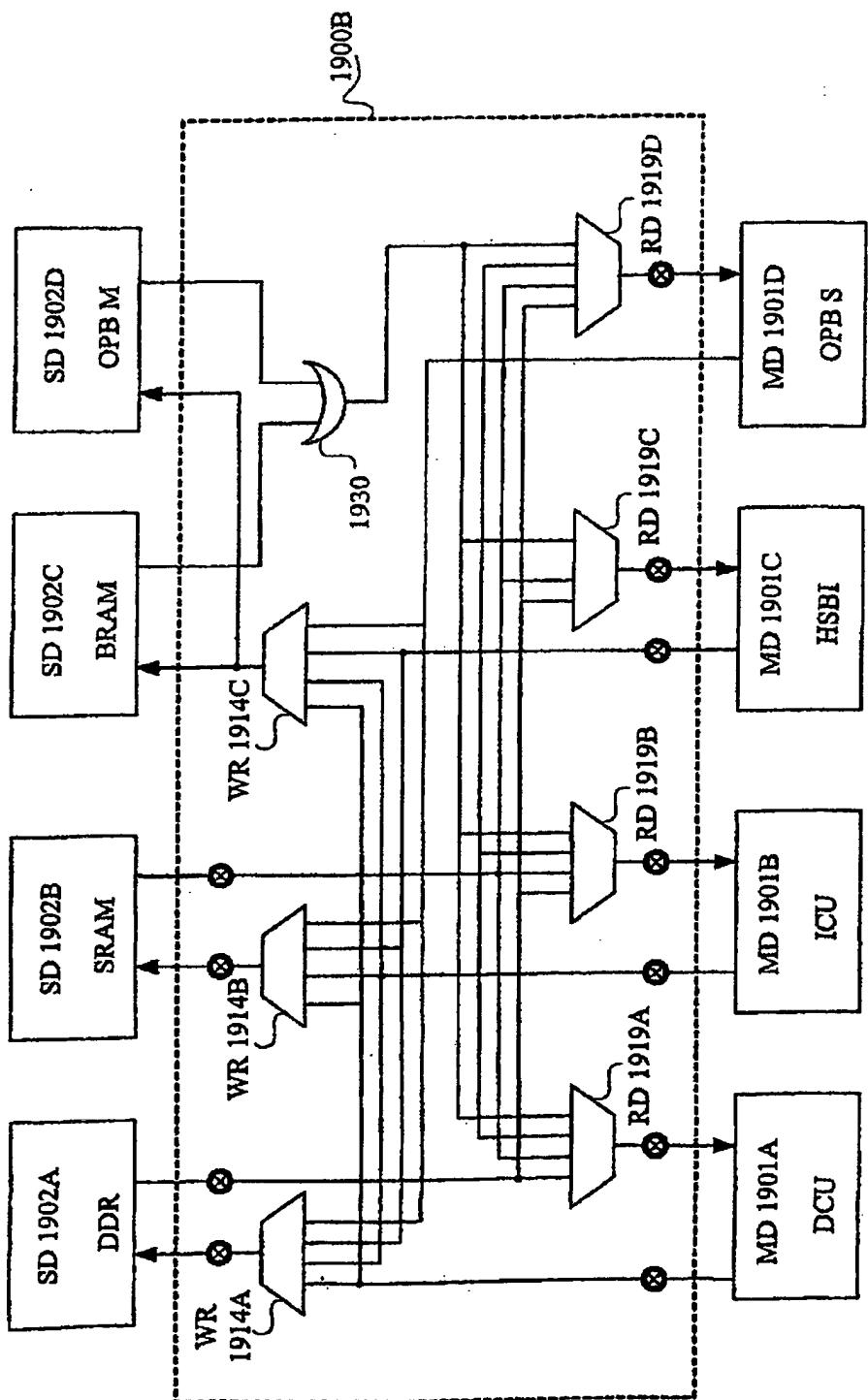

[0053] Die [Fig. 19A](#) und [Fig. 19B](#) stellen die Adreß/Steuerlogik beziehungsweise die Datenlogik einer Architektur mit Hybridekoppelpunkt/gemeinsam genutztem Bus gemäß einer Ausführungsform der vorliegenden Erfindung dar.

## AUSFÜHRLICHE BESCHREIBUNG DER FIGUREN

**[0054]** Das folgende Inhaltsverzeichnis soll dem Leser einen Überblick über die Strukturierung des Themas bieten.

## INHALTSVERZEICHNIS

- I. Terminologie und Richtlinien

- A. Definitionen

- B. Signalbezeichnungs- und Nummerierungsrichtlinien

- C. Timing-Richtlinien

- II. Erkennen der Unterschiede zwischen Ressourcen

- III. Eingrenzen von Bus-Funktionen

- A. PLB-Teilmengenfunktionen

- 1. Arbitrierungssteuerfunktionen

- 2. Datentransferfunktionen

- B. PLB-Obermengenfunktionen

- C. Signale: Abbilden (Mapping) von PLB auf PIC

- IV. FPGA-Implementierung: Allgemeines

- A. Zentrale Verarbeitungseinheit

- B. Programmierbarer Schnittstellenkern (Programmable Interface Core = PIC)

- C. Master- & Slave-Vorrichtungen

- D. Chipinterner peripherer Bus (On-chip Peripheral Bus = OPB)

- E. Hochgeschwindigkeits-Busschnittstelle

- V. FPGA-Implementierung: Einzelheiten

- A. Master-/Slave-Vorrichtungen: Ports & Timing

- 1. Kommunikation zwischen Master-Vorrichtung und PIC

- a. Adreß-Ports für Masters

- b. Schreib-Ports für Masters

- c. Lese-Ports für Masters

- 2. Timing der Master-Vorrichtung

- 3. Kommunikation zwischen Slave-Vorrichtung und PIC

- a. Adreß-Ports für Slaves

- b. Schreib-Ports für Slaves

- c. Lese-Ports für Slaves

- 4. Timing der Slave-Vorrichtung

- B. Programmierbarer Schnittstellenkern

- C. DCU/ICU: Schnittstelle zum PLB

- D. BRAM: Schnittstelle zum PLB

- E. OPB-Brückenmodule

- 1. Bridge-Out-Modul

- 2. Bridge-In-Modul

- F. Programmierbarer Hybrid-Schnittstellenkern

- G. Software-Tools

## I. TERMINOLOGIE UND RICHTLINIEN

**[0055]** Die vorliegende Erfindung wird unter Verwendung bestimmter Terminologie und Richtlinien beschrieben, mit denen Fachleute vertraut sein mögen oder auch nicht. Aus diesem Grund werden die nachfolgenden Definitionen, Signal- und Nummerierungsrichtlinien sowie Timing-Richtlinien genauer beschrieben, um dem Leser die vorliegende Erfindung besser verständlich zu machen.

## A. DEFINITIONEN

**[0056]** Die in dieser Beschreibung verwendeten Akronyme, Abkürzungen und Fachbegriffe werden im Anschluß an diesen Abschnitt in alphabetischer Reihenfolge definiert. Es sei darauf hingewiesen, daß einige Akronyme, Abkürzungen und Fachbegriffe eventuell in der ausführlichen Beschreibung definiert werden.

|                 |                                                                                                                                                                                                                                                         |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BEAR:           | Busfehler-Adreßregister (Bus Error Address Register)                                                                                                                                                                                                    |

| BESR:           | Busfehler-Syndromregister (Bus Error Syndrome Register)                                                                                                                                                                                                 |

| BRAM:           | Block-RAM (Block Random Access Memory (RAM)) auf einer programmierbaren Logikvorrichtung                                                                                                                                                                |

| Burst:          | eine Transaktion, bei der mehr als eine Dateneinheit übertragen und die in der Regel für das schnelle Bewegen eines Datenblocks zwischen einem Master und einem Slave verwendet wird                                                                    |

| Cache-Speicher: | kleiner, schneller Speicher in der CPU zum Speichern von Dateninhalt einschließlich Befehle und/oder Daten, auf den in der letzten Zeit zugegriffen wurde                                                                                               |

| Kern:           | vorstrukturierter Abschnitt einer programmierbaren Logikvorrichtung, der eine bestimmte Funktion bereitstellt und in der Regel mit Hilfe einer vorgegebenen Anzahl physischer Ressourcen auf der programmierbaren Logikvorrichtung implementiert wird   |

| CPU:            | zentrale Verarbeitungseinheit, die in der Regel eine Steuereinheit und eine Rechen- und Logikeinheit (Arithmetic and Logic Unit = ALU) enthält                                                                                                          |

| DCU:            | Daten-Cache-Speichereinheit (Data Cache Unit)                                                                                                                                                                                                           |

| DDR:            | doppelte Datenrate (Double Data Rate)                                                                                                                                                                                                                   |

| HSBI:           | Hochgeschwindigkeits-Busschnittstelle, bei der hier allgemein eine Vorrichtung mit Hochgeschwindigkeits-Master-Port auf dem PIC gemeint ist                                                                                                             |

| ICU:            | Befehls-Cache-Speichereinheit (Instruction Cache Unit)                                                                                                                                                                                                  |

| IP:             | Struktur für die Integration in eine integrierte Schaltung, insbesondere ein FPGA                                                                                                                                                                       |

| Little          | Endian: Architektur, bei der, wenn man von einem 16- oder 32-Bit-Datenwort ausgeht, Byte an niedrigeren Adressen geringerwertig sind                                                                                                                    |

| ISA:            | Befehlssatzarchitektur (Instruction Set Architecture)                                                                                                                                                                                                   |

| OPB:            | chipinterner peripherer Bus (On-chip Peripheral Bus)                                                                                                                                                                                                    |

| PIC:            | programmierbarer Schnittstellenkern (Programmable Interface Core), der zwischen einer CPU und programmierbaren Logikvorrichtungsressourcen gemäß der vorliegenden Erfindung bereitgestellt wird                                                         |

| Pipelining:     | Prozeß, in dem eine Master-Vorrichtung mit der Ausführung eines zweiten Buszyklus beginnen kann, bevor der erste Buszyklus abgeschlossen worden ist, d.h. gleichzeitiges Verarbeiten mehrerer Buszyklen, die sich in unterschiedlichen Stadien befinden |

| PLB:            | Prozessor-Local-Bus                                                                                                                                                                                                                                     |

| PowerPC:        | RISC-Mikroprozessor, der einer Norm entspricht, die von IBM, Motorola und Apple Computer gemeinsam entworfen wurde und eine gemeinsame Befehlssatzarchitektur (Instructions Set Architecture = ISA) festlegt                                            |

| Register:       | Hochgeschwindigkeits-Speicherbereich auf dem FPGA                                                                                                                                                                                                       |

| SDRAM:          | synchroner dynamischer RAM (DRAM) der mit höheren Taktgeschwindigkeiten laufen kann als herkömmlicher Speicher und sich selbst mit dem Bus einiger CPUs synchronisieren kann                                                                            |

| Single          | Data Beat: nicht burstartiger Transfer, d.h. ein einziges Datenelement in einem Taktzyklus über den Bus                                                                                                                                                 |

| Datenwort:      | steht für eine Datenmenge von 32 Bit                                                                                                                                                                                                                    |

## B. SIGNALBEZEICHNUNGS- UND NUMMERIERUNGSRICHTLINIEN

**[0057]** Zur Beschreibung von Merkmalen der vorliegenden Erfindung wird auf verschiedene Signale verwiesen. Gemäß der hier verwendeten Richtlinie beginnen die Signalbezeichnungen in den [Fig. 6](#) und [Fig. 8](#) mit einem Präfix, der die Richtung des Signalflusses angibt sowie die übertragende Vorrichtung und die Vorrichtung, die das Signal empfängt. Die Signalbezeichnungen in anderen Figuren können mit einem Präfix beginnen, der nur die übertragende Vorrichtung angibt. Die Bezeichnungen der Vorrichtungen werden der Einfachheit und Übersichtlichkeit halber abgekürzt. Auf den Präfix folgt ein Unterstrich (\_) und dann die Bezeichnung des Signals selbst. Der Suffix „\_n“ bezeichnet ein Active-Low-Signal. Die Signalbezeichnung PIC2M\_foo beschreibt beispielsweise das Signal „foo“, das von dem programmierbaren Schnittstellenkern (PIC) gesteuert und von einer Master-Vorrichtung empfangen wird.

**[0058]** N-Bit-Busbits sind von rechts (0) nach links (N-1) nummeriert. Es sei angemerkt, daß diese Nummerierungsrichtlinie unabhängig von Kompatibilitätsproblemen bei verschiedenen proprietären CPUs nicht die PIC-ISA ändert oder die Software-Kompatibilität der CPU beeinflußt.

## C. TIMING-RICHTLINIEN

**[0059]** Um eine hohe Leistung erzielen zu können, muß das Timing berücksichtigt werden. Fachleute wissen, dass es für eine bestimmte Implementierung einer Struktur häufig ein spezifisches Timing gibt. Daher unterstützen die hier im Sinne von Beispielen angeführten Timing-Bezugswerte zwar das Pipelining der vorliegenden Erfindung, sie betreffen jedoch nicht das Timing aller Strukturen.

**[0060]** Als Timing-Informationen können die Begriffe „frühes“, „mittleres“ und „spätes“ verwendet werden. Bei der hier verwendeten Richtlinie eignet sich frühes Timing am besten und spätes Timing am wenigsten.

**[0061]** Wenn ein Eingangssignal frühes Timing aufweist, dann steht dem Anwender für das Verarbeiten der Daten ein ganzer Taktzyklus zur Verfügung, bevor er sie zwischenspeichert. Ein frühes Timing für Eingangssignale bedeutet, daß das Signal von einem Registerausgang angesteuert wird. Wenn ein Ausgangssignal frühes Timing aufweist, dann kann der Anwender den ganzen Taktzyklus nutzen, bevor er die Daten absendet. Ein frühes Timing für Ausgangssignale bedeutet, daß das Signal den Eingang eines Registers ansteuert.

**[0062]** Wenn ein Eingangssignal mittleres Timing aufweist, dann steht dem Anwender für das Verarbeiten der Daten ungefähr ein halber Taktzyklus zur Verfügung, bevor er sie zwischenspeichert. Ein mittleres Timing für Eingangssignale bedeutet, daß das Signal von einem Registerausgang durch eine geringe Menge Logik oder Leitwege (Routing) zum Anwender angesteuert wird. Wenn ein Ausgangssignal mittleres Timing aufweist, dann kann der Anwender ungefähr den halben Taktzyklus nutzen, bevor er die Daten absendet. Ein mittleres Timing für Ausgangssignale bedeutet, daß das Signal eine geringe Menge Logik oder Leitwege ansteuert, bevor es am Eingang eines Registers eintrifft.

**[0063]** Wenn ein Eingangssignal spätes Timing aufweist, dann steht dem Anwender für das Verarbeiten der Daten ein geringer Bruchteil des Taktzyklus zu Verfügung, bevor er sie zwischenspeichert. Ein spätes Timing für Eingangssignale bedeutet, daß das Signal von einem Registerausgang über eine wesentliche Menge Logik und Leitwege angesteuert wird. Somit steht dem Anwender ein kleines Fenster zur Verfügung, in dem er die Daten vor ihrer Benutzung zwischenspeichern kann. Wenn ein Ausgangssignal spätes Timing aufweist, dann kann der Anwender einen geringen Bruchteil des Taktzyklus nutzen, bevor er die Daten absendet. Ein spätes Timing für Ausgangssignale bedeutet, daß das Signal den Eingang eines Registers über eine wesentliche Menge Logik oder Leitwege ansteuert. Somit sollte der Anwender diesen Ausgangswert direkt von einem Register aus ansteuern.

**[0064]** Angesichts der oben genannten Probleme kann die spezielle Implementierung die Mittel, die jedes Signal bereitstellt, erklären. Einige Signale benötigen mehr Zeit (z.B. späte Signale), und dies kann nachteilige Auswirkungen auf die Schalthäufigkeit des Systems haben. Um diese Probleme anzugehen, kann Pipelining implementiert werden, das das Timing von Signalen abschwächt. Diese Pipeline-Register bieten die Möglichkeit, das Signal neu zu synchronisieren, so daß es, wenn auch mit einer Latenz, früher in der Taktperiode vor kommt.

## II. ERKENNEN DER UNTERSCHIEDE ZWISCHEN RESSOURCEN

**[0065]** Wenn man eine zentrale Verarbeitungseinheit (CPU) statt in einen ASIC in eine programmierbare Logikvorrichtung (z.B. ein FPGA) integrieren will, muß man die Unterschiede zwischen diesen beiden Vorrichtungsarten kennen.

**[0066]** Ein Hauptunterschied zwischen einem FPGA und einem ASIC, der die Leistung beinflussen kann, sind die Logikressourcen. Insbesondere werden die Logikgeneratoren in einem FPGA wie oben beschrieben in der Regel mit Hilfe von Nachschlagetabellen in den CLBs aufgebaut. Somit erfordern eine hohe Eingangsauffächerung oder komplexe kombinatorische logische Funktionen in der Regel mehrere Ebenen von Nachschlagetabellen, wodurch beträchtliche Verzögerungen entstehen. Im Gegensatz dazu kann ein ASIC speziell angepaßte Strukturen für das Ausführen bestimmter logischer Funktionen bieten, wodurch die mehreren Logikelementen eliminiert werden.

**[0067]** Ein weiterer Hauptunterschied zwischen einem FPGA und einem ASIC, der die Leistung beinflussen kann, sind die Leitwegressourcen. Und zwar leitet ein FPGA Signale sowohl über programmierbare als auch über fest zugeordnete (beispielsweise Übertragungskettenlogik) Signalflußkanäle. Im Gegensatz dazu bietet ein ASIC speziell angepaßte Signalwege und eliminiert dadurch die Unkosten für die Programmierbarkeit. Um an Geschwindigkeiten heranzukommen, die einem ASIC entsprechen, bräuchte ein FPGA somit dickere Spu-

ren und größere Puffer als die, die in der Regel in einem FPGA bereitgestellt werden. Ein Vergrößern dieser Leitwegressourcen könnte eine Vergrößerung der Siliziumfläche des FPGA erforderlich machen und dadurch dessen Herstellungskosten auf unerwünschte Weise erhöhen.

**[0068]** Angesichts der oben beschriebenen Unterschiede können FPGA-Ressourcen, die an eine CPU angekoppelt sind, im Hinblick auf das Erzielen von Leistung und Bandbreite bei einer Hochgeschwindigkeitsstruktur beträchtliche Hindernisse darstellen. Gemäß der vorliegenden Erfindung, und wie nachfolgend ausführlich beschrieben wird, kann der Aufbau des FPGA auf vorteilhafte Weise wirksam eingesetzt werden, um sowohl standardmäßige als auch erweiterte Transaktionen, an denen die CPU beteiligt ist, bereitzustellen zu können. Das sich so ergebende System kann derzeitigen ASIC-Systemen nahekommen und sogar über diese hinausgehen, da es statt IC-Technologie Architektur benutzt, um das Problem anzugehen.

## III. EINGRENZEN VON PLB-FUNKTIONEN

**[0069]** Eine typische CPU arbeitet mit einem Satz PLB-Protokolle, wenn sie mit anderen Vorrichtungen kommunizieren will. Ein FPGA mit einem ganzen Satz PLB-Protokolle auszustatten, würde beträchtlich viel Logik erforderlich machen, wodurch sowohl Leistung als auch Fläche negativ beeinflußt werden würden. Deshalb können gemäß eines Merkmals der vorliegenden Erfindung einige der standardmäßigen PLB-Protokolle vorteilhafterweise eliminiert werden, ohne daß die Leistung des FPGA wesentlich beeinflußt wird.

**[0070]** Allgemein gesagt eliminiert die vorliegende Erfindung die PLB-Protokolle, die eine komplexe Datenwegmanipulation erfordern. Eine komplexe Datenwegmanipulation verwendet eine beträchtliche Menge an Logik, die über breite Busse und weite Entfernung verteilt ist. Somit kann eine komplexe Datenwegmanipulation in einem FPGA beträchtliche Ressourcen für sich beanspruchen, während sie nur eine begrenzte Funktionalität für den IP-Anwender hinzufügt.

**[0071]** Die vorliegende Erfindung eliminiert auch die PLB-Protokolle, die ein asynchrones Handshaking erfordern. Bei einem asynchronen Handshaking legt ein Signal in der Regel große Entfernung zurück (d.h. Wege vom Master zum Slave und zurück zum Master) und durchläuft eine beträchtliche Menge Logik, und das alles in einem einzigen Taktzyklus. Somit muß das asynchrone Handshaking, wie auch die komplexe Datenwegmanipulation, beträchtliche Ressourcen für sich in Anspruch nehmen, damit es diese Timing-Aufgabe erfüllen kann.

**[0072]** Durch das fehlende Unterstützen diverser standardmäßiger PLB-Protokolle lassen sich verschiedene Vorteile erzielen. Zum ersten kann die vorliegende Erfindung kritische Wege in der Datenlogik wesentlich vereinfachen. Die Vereinfachung der Datenweglogik ist wichtig, da diese breiten Busse im FPGA weite Entfernung zurücklegen. Anders ausgedrückt läßt sich durch das Verringern der Logik im Datenweg vorteilhaftweise die Signalgeschwindigkeit erhöhen. Zum zweiten kann die vorliegende Erfindung kritische Wege in der Steuerlogik wesentlich vereinfachen, wodurch die Signalgeschwindigkeit weiter erhöht wird. Zum dritten können Transaktionen durch das Entfernen dieser PLB-Protokolle deterministischer werden. Beispielsweise kann Logik in der Regel vereinfacht werden, wenn ein Master für eine bestimmte Transaktion einen kleineren Satz möglicher Antworten von einem Slave erwarten kann. Es ist klar, daß die Logik, je mehr unterschiedliche Antworten oder Aktionen ein Master oder ein Slave aufweisen kann, umso komplexer sein muß, damit sie diese Antworten oder Aktionen unterbringen kann.

**[0073]** Es sei angemerkt, daß das Eliminieren von PLB-Protokollen eine direkte Auswirkung auf die Anzahl der PLB-Funktionen hat, die mit der CPU ausgeführt werden können. Die vorliegende Erfindung behandelt dieses Problem jedoch, wie nachfolgend ausführlich beschrieben wird.

## A. PLB-TEILMENGENFUNKTIONEN

**[0074]** Gemäß der vorliegenden Erfindung konzentriert sich eine Teilmenge der in dem FPGA implementierten PLB-Funktionen auf die Arten der Transaktionen, die die CPU in der Regel durchführt, wodurch die Leistung dieses kritischen Bestandteils optimiert wird. Insbesondere erfolgen die meisten Datentransfers auf dem PLB von Vorrichtung zu Speicher oder von Speicher zu Vorrichtung und nicht von Vorrichtung zu Vorrichtung. Somit ist Speicherleistung am PLB sehr gefragt. Es ist wichtig, daß die meisten FPGA-Anwenderspeicherschnittstellen ähnliche Transaktionen ausführen wie die CPU. Folglich kann eine Teilmenge der PLB-Funktionen vorteilhaftweise die unterschiedlichen Transaktionsarten unterstützen, die am wahrscheinlichsten auf dem FPGA auftreten. Eine Analyse hinsichtlich der Integration verschiedener PLB-Funktionen in ein FPGA folgt anschließend.

## 1. ARBITRIERUNGSSTEUERFUNKTIONEN

**[0075]** Adreßdecodier-Funktion: Das Implementieren einer Adreßdecodierung in Slaves bei einem standardmäßigen PLB erfolgt derzeit über einen gemeinsam genutzten Bus (Shared Bus). Bei einem gemeinsam genutzten Bus wird die von einem Master angeforderte Adresse allen Slaves auf dem Bus zugeführt. Die Slaves decodieren die Adresse, und der ausgewählte Slave leitet dann eine Adreßbestätigung zurück an den anfordernden Master. Dieser Prozeß erzeugt leider eine beträchtliche Verzögerung. Daher wird gemäß der vorliegenden Erfindung das Adreßdecodieren verteilt und in einem programmierbaren Schnittstellenkern (Programmable Interface Core = PIC) durchgeführt (Beschreibung siehe [Fig. 5A–Fig. 5E](#)). Aufgrund des die Transaktion weiterleitenden Charakters dieses Kerns ist dem Slave ein Adreßtreffer (Hit) sicher, wenn ihm eine Transaktion präsentiert wird. Auf diese Weise verringert die vorliegende Erfindung die derzeit in den Slaves bereitgestellte Adreßdecodierlogik beträchtlich, was das Entwickeln und Bauen von Slaves vereinfacht. Es sei angemerkt, daß bei einem Hybridsystem ein zusätzlicher Adreßdecodierer in einem Slave bereitgestellt werden kann, wenn mehrere Slaves einen Bus gemeinsam nutzen. Bei diesem Hybridsystem ist die Anzahl der Slaves, die einen Bus gemeinsam nutzen, relativ gering, wodurch die Adreßdecodierlogik vereinfacht wird.

**[0076]** Busfehler- (Adreß- oder Datenfehler-)Funktion: Die Busfehler-Funktion wird sowohl vom standardmäßigen PLB als auch vom PIC der vorliegenden Erfindung unterstützt.

**[0077]** Abbruch-Funktion: Die Unterstützung einer Abbruch-Funktion bei einem Transaktionen weiterleitenden System ist schwierig, weil die Transaktion zu einem Slave weitergeleitet werden kann, bevor es überhaupt dazu kommt, daß ein Abbruchsignal überprüft wird. Es sei angemerkt, daß bei einem standardmäßigen PLB eine Transaktion nicht mehr abgebrochen werden kann, wenn ein Slave die Anforderung erst einmal bestätigt hat. Darüber hinaus wäre für das Leiten eines Abbruchbefehls in den PIC zusätzliche Logik notwendig, was negative Auswirkungen auf das Timing des Systems hätte. Daher erzeugen Masters bei der vorliegenden Erfindung in der Regel keine Abbruchsignale.

**[0078]** Wenn ein Master ein Abbruchsignal erzeugt, kann er ein Schnittstellenmodul benutzen, das die Anforderung sofort erkennt, sie bestätigt und direkt an den entsprechenden Slave weiterleitet. Dieses Schnittstellenmodul befindet sich auf dem Weg zwischen dem Master und dem Port zum PIC. Somit bleibt die allgemeine Regel, daß Masters keine Abbruchsignale erzeugen, erhalten.

**[0079]** Es sei angemerkt, daß das Unterstützen von Abbruchsignalen bei einem System mit Pipelining zu einer gewissen Leistungssteigerung führen kann, wenn sich der Code des Anwenders verzweigt oder unterbrochen wird. Insbesondere können, wenn Abbrüche unterstützt werden und Masters Zeit zum Überprüfen von Abbrüchen bekommen, unnötige Transaktionen frühzeitig abgebrochen werden, wodurch die Ausnutzung der Datenlogik auf vorteilhafte Weise reduziert wird. Sich verzweigender oder unterbrochener Code beseitigt den Informationsbedarf, der vom Master derzeit eingefordert wird. Wenn der Master Transaktionen abbrechen kann, nachdem er festgestellt hat, daß die Daten nicht gebraucht werden, dann erhöht sich die Leistung. Dieser Nutzen kann jedoch durch die Komplexität und die niedrigere Taktfrequenz für den Rest des Systems wieder aufgehoben werden.

**[0080]** Priorisierte Arbitrierungsfunktion: Der Aufbau kombinatorischer Logik, die auf der Grundlage einer dynamischen Priorität zwischen Masters arbitriert, würde zahlreiche logische Ebenen erfordern, die die Leistung bei einem FPGA beträchtlich verlangsamen könnten. Daher ist bei einer Ausführungsform der vorliegenden Erfindung eine Arbitrierung im Rundlauf (Round-Robin) oder mit fester Priorität vorgesehen. Bei anderen Ausführungsformen kann eine vom Anwender auszuwählende Arbitrierung bereitgestellt werden.

**[0081]** Wiederholungsfunktion: Bei einer Shared-Bus-Architektur wird in der Regel eine Wiederholungsfunktion (manchmal auch als Rearbitrierungsfunktion bezeichnet) benötigt, um zu verhindern, daß sich mehrere Masters gegenseitig blockieren. Gemäß dem PIC der vorliegenden Erfindung können jedoch mehrere Transaktionen gleichzeitig ablaufen, wodurch die Notwendigkeit von Wiederholungen wesentlich verringert oder sogar ganz beseitigt wird. Es sei angemerkt, daß die Implementierung einer Wiederholungsfunktion in einem Transaktionen weiterleitenden System das Leiten von Signalen vom Slave zum Master erforderlich machen würde, was die Komplexität von Logik in dem Arbiter auf unerwünschte Weise erhöht.

**[0082]** Es sei angemerkt, daß eine Wiederholungsfunktion in einem Hybridsystem mit einem gemeinsam genutzten Bus bereitgestellt werden kann. Bei einem Hybridsystem könnte der Zugriffsarbiter so modifiziert werden, daß er eine Wiederholungsfunktion aktiviert, wodurch es nicht mehr notwendig wäre, das Wiederholungs-signal zum Master zurückzuleiten.

**[0083]** Busspen-Funktion: Eine Busspen-Funktion stellt sicher, daß nur ein Master auf einen bestimmten Slave zugreifen kann. Eine Busspen-Funktion kann jedoch die Arbitrierungslogik in dem PIC beeinflussen, die sich auf dem kritischen Timing-Weg befindet. Somit kann die Busspen-Funktion aktiviert werden, wenngleich dies wahrscheinlich auch mit einem gewissen Leistungsverlust einhergeht.

**[0084]** Adressen-Pipelining-Funktion: Eine Adressen-Pipelining-Funktion wird sowohl beim standardmäßigen PLB als auch beim PIC der vorliegenden Erfindung unterstützt. Pipelining kann die Systemleistung beträchtlich verbessern, da es den gleichzeitigen Ablauf mehrerer Transaktionen ermöglicht. Es sei darauf hingewiesen, daß eine Code-Verzweigung die Vorteile des Pipelining untergraben kann.

**[0085]** Transfersart-Funktion: Zu einer Transferart-Funktion bei einem standardmäßigen PLB kann beispielsweise direkter Speicherzugriff (Direct Memory Access = DMA) und Simultanbetrieb gehören. Im allgemeinen erfordert jede Transferart eine Kombination aus verschiedenen Protokollen. Daher kann das Bereitstellen mehrerer Transferarten ein FPGA-System wesentlich komplexer machen. Gemäß der vorliegenden Erfindung sind Übertragungen auf einfache Speichertransfers (Umspeicherungen) beschränkt, was die Logik und die Komplexität des FPGA vereinfacht.

## 2. DATENTRANSFERFUNKTIONEN

**[0086]** Einzeldatenimpulstransferfunktion: Eine Einzeldatenimpulstransferfunktion, d.h. die Übertragung einer einzelnen Dateneinheit, ist eine Grundoperation der CPU und wird daher von der vorliegenden Erfindung unterstützt. Es sei angemerkt, daß es sich bei dieser Transferfunktion um entweder eine Schreib- oder eine Lesoperation handeln und diese ein beliebiges Bytefreigabemuster enthalten kann. Jede Transaktion wird maximal eine Datenmenge übertragen, die der Größe der Busbreite entspricht. Es sei darauf hingewiesen, daß sich diese Funktion vom Burst-Modus unterscheidet.

**[0087]** Burst-von-unbestimmter-Länge-Funktion: Durch das Bereitstellen einer Burst-von-unbestimmter-Länge-Funktion auf Adreß- und Datenwegen mit Pipelining, wie dies bei der vorliegenden Erfindung geschieht, entstehen beträchtliche Leistungsprobleme. Der Master würde beispielsweise einen oder mehrere Zyklen benötigen, um das Ende eines Burst an den angeforderten Slave zu übermitteln. Im Verlauf dieser Zeit könnte der Slave jedoch zu viele Daten senden. Darüber hinaus kann es sich für die Adreßdecodierlogik als schwierig erweisen, rechnerisch zu bestimmen, ob ein Burst von unbestimmter Länge eine Adreßgrenze in dem zugeordneten Zeitraum überschreitet. Deshalb werden Bursts von unbestimmter Länge von der vorliegenden Erfindung nicht unterstützt.

**[0088]** Burst-Beenden-Funktion: Ein standardmäßiger PLB erlaubt dem Slave jederzeit, einen Burst von festgelegter Länge abzubrechen. Der Master kann jedoch wieder einen oder mehrere Zyklen benötigen, um dem Slave ein Beenden-Signal zu übermitteln. Im Verlauf dieses Zeitraums könnte der Slave jedoch zu viele Daten senden. Deshalb unterstützt die vorliegende Erfindung die Burst-Beenden-Funktion bei einer Ausführungsform nicht. Stattdessen erfordert die vorliegende Erfindung deterministisches Verhalten, d.h. der Slave schickt die richtige Anzahl Lesebestätigungs- (RdAck) und Schreibbestätigungssignale (WrAck) zurück. Bei einer weiteren Ausführungsform kann der Slave, wenn ein Burst-Beenden-Signal für die Steuerung des Datenflusses verwendet wird, Wartezustände zwischen RdAck- und WrAck-Signalen einfügen, um mehr Zeit zur Verfügung zu stellen. Alternativ dazu kann der Slave Lesefehler markieren oder Interrupts erzeugen, wenn ein Problem auftritt.

**[0089]** Burst-von-bestimmter-Länge-Funktion: Durch das Bereitstellen eines Burst von bestimmter Länge, d.h. zwischen 2 und 16 Transfers, vereinfacht sich zwar die Struktur des Masters, es ist aber wiederum zusätzliche Logik für den Slave notwendig, damit eine Überschreitung der Adreßgrenze oder Seitengrenze erfaßt werden kann. Deshalb wird diese Funktion bei der vorliegenden Erfindung bei einer Ausführungsform nicht unterstützt, und stattdessen wird für eine Cache-Line-Ausrichtung gesorgt. Bei dieser Ausführungsform kann der PIC Bursts mit festgelegter Länge in Zweierpotenzen durchführen, die auf diese Größe ausgerichtet sind (d.h. einen Cache-Line-Transfer). Bei einer weiteren Ausführungsform wird die Burst-von-bestimmter-Länge-Funktion unterstützt, wobei der Anwender die Adreßkennzeichner definiert und das Master/Slave-IP konstruiert, das diese Kennzeichner unterstützt. Bei einer weiteren Ausführungsform wird die Burst-von-bestimmter-Länge-Funktion forciert als zur Burstlänge ausgerichtete Transfers implementiert, wodurch keine Adreßgrenzenüberprüfungen mehr ausgeführt werden müssen.

**[0090]** Burst-Größe-Funktion: Ein Verändern der Burst-Größe erhöht die Komplexität von Datenwegen im Slave. Der Slave müßte insbesondere Datenwege implementieren, um mit jeder beliebigen Anzahl von Daten-

breiten umgehen zu können. Bei einer Ausführungsform kann die Burst-Größe auf die Datenwegbreite eingestellt werden.

**[0091]** Cache-Line-Transfer-Funktion: Cache-Line-Transfers, d.h. atomare Daten-Bursts von bestimmter Länge und Ausrichtung, vereinfachen die Struktur der Slaves im Hinblick auf Adreß- oder Seitengrenzenausrichtung. Cache-Line-Transfers werden gemäß der vorliegenden Erfindung unterstützt. Bei einer Ausführungsform der vorliegenden Erfindung werden Cache-Line-Transfers von 2, 4, 8, 16 und 32 Datenwörtern bereitgestellt. Es sei darauf hingewiesen, daß diese Größen vorteilhafterweise DDR SDRAM unterstützen.

**[0092]** Dynamische Busabmessungsfunktion: Die dynamische Busabmessungsfunktion erfordert Datenspiegelungs- und -lenkungslogik, was die Komplexität des FPGA beträchtlich erhöhen kann. Darüber hinaus müssen sowohl Masters als auch Slaves die Transferbreiten kennen, damit sie ihre interne Logik für die richtige Anzahl Datentransferzyklen einstellen können. Deshalb unterstützt der PIC gemäß der vorliegenden Erfindung keine Masters und Slaves mit unterschiedlichen Breiten. Stattdessen sind die Transferbreiten über das gesamte System hinweg festgelegt, wodurch sich die Komplexität beim FPGA verringert. Bei einer Ausführungsform kann parametrisiertes IP auf 32- oder 64-Bit-Transfers eingestellt werden. Der Auswirkung der dynamischen Busabmessung lässt sich mit Hilfe von Bytefreigabesignalen und Software-Steuerung Rechnung tragen.

## B. PLB-OBERMENGENFUNKTIONEN

**[0093]** Gemäß der vorliegenden Erfindung stellen eine Anzahl implementierter Funktionen Obermengen der standardmäßigen PLB-Funktionen dar. Die vorliegende Erfindung unterstützt beispielsweise Datenwege mit doppelter Datenrate (DDR), wobei der Datenweg mit der doppelten Taktfrequenz des Adreßweges laufen kann. Zusätzlich dazu enthält die vorliegende Erfindung einen dynamischen Schreib-Bytefreigabemechanismus, damit Schreibtransaktionen in der gesamten Verbindungsstruktur optimiert werden können. Insbesondere kann die vorliegende Erfindung für jedes Byte übertragener Schreibdaten ein zusätzliches Bit bereitstellen, so daß jedes Datenbyte selektiv übersprungen werden kann. So kann der dynamische Schreib-Bytefreigabemechanismus auf effiziente Weise Byte-Muster schreiben, wodurch die Systemleistung bei nicht zusammenhängenden Speicherschreiboperationen verbessert wird. Dies ist besonders vorteilhaft bei Systemen, die DMA verwenden. Insbesondere würde eine DMA-Maschine keine komplexe Logik mehr benötigen, um schlecht ausgerichtete Daten sequentiell zu durchlaufen. Stattdessen kann die DMA-Maschine einfach das richtige Bytefreigabemuster bereitstellen, um den Inhalt des Transfers unterzubringen. Des Weiteren wird die DMA-Maschine nicht mehr so viele Buszyklen für den Transfer ihrer Daten verbrauchen, wodurch dem System mehr verfügbare Leistung zur Verfügung steht. Und schließlich benutzt der PIC der vorliegenden Erfindung eine Transaktionen weiterleitende Architektur, die Pipelining unterstützt und eine höhere Gesamtleistung des Systems ermöglicht. Diese Obermengenfunktionen erhöhen die IP-Leistung bei dem FPGA beträchtlich.

## C. SIGNALE: ABBILDEN (MAPPING) VON PLB AUF PIC

**[0094]** Um die oben beschriebenen PLB-Funktionen bereitstellen zu können, werden verschiedene Signale zwischen dem PLB und den Masters/Slaves des Systems übertragen. Diese PLB-Signale werden nachfolgend aufgeführt, um das Abbilden (Mapping) auf die vorliegende Erfindung zu zeigen. Tabelle 1 führt beispielsweise verschiedene PLB-Signale aus der Perspektive eines Masters auf, und sie gibt an, ob diese Signale bei einer einfachen CPU benötigt werden und bei einem FPGA mit akzeptabler Leistung implementiert werden können.

TABELLE 1

| SIGNALBEZEICHNUNG            | RICHTUNG | VON CPU BENÖTIGT                   | IM FPGA                                                           |

|------------------------------|----------|------------------------------------|-------------------------------------------------------------------|

| PLB-Anforderungskennzeichner |          |                                    |                                                                   |

| SYS_plbClk                   | Eingabe  | Ja                                 | Ja                                                                |

| SYS_plbReset                 | Eingabe  | Ja                                 | Ja                                                                |

| PLB_MnAddrAck                | Eingabe  | Ja                                 | Ja                                                                |

| PLB_MnRearbitrate            | Eingabe  | Nein                               | Ja<br>(gemeinsam genutzter Bus)                                   |

| PLB_MnSSize                  | Eingabe  | Nein                               | Nein                                                              |

| PLB_MnBusy                   | Eingabe  | Ja                                 | Ja                                                                |

| PLB_MnErr                    | Eingabe  | Ja                                 | Ja                                                                |

| PLB_pendReq                  | Eingabe  | Nein                               | Ja<br>(feststehender Wert)                                        |

| PLB_pendPri                  | Eingabe  | Nein                               | Ja                                                                |

| PLB_reqPri                   | Eingabe  | Nein                               | Ja<br>(feststehender Wert)                                        |

| Mn_request                   | Ausgabe  | Ja                                 | Ja                                                                |

| Mn_priority                  | Ausgabe  | Nein                               | Ja                                                                |

| Mn_busLock                   | Ausgabe  | Nein                               | Ja                                                                |

| Mn_RNW                       | Ausgabe  | Ja                                 | Ja                                                                |

| Mn_BE                        | Ausgabe  | Ja<br>(kein Burst)                 | Ja<br>(kein Burst oder Bursts mit festgelegter Länge)             |

| Mn_size                      | Ausgabe  | Ja<br>(kein Burst oder Cache-Line) | Ja<br>(kein Burst, Bursts mit festgelegter Länge oder Cache-Line) |

| Mn_type                      | Ausgabe  | Nein                               | Nein                                                              |

| Mn_Msize                     | Ausgabe  | Nein                               | Nein                                                              |

| Mn_compress                  | Ausgabe  | Ja                                 | Ja                                                                |

| Mn_guarded                   | Ausgabe  | Ja                                 | Ja                                                                |

| Mn_ordered                   | Ausgabe  | Nein                               | Ja                                                                |

| Mn_locker                    | Ausgabe  | Nein                               | Ja                                                                |

| Mn_abort                     | Ausgabe  | Ja                                 | Nein                                                              |

| Mn_Abus                      | Ausgabe  | Ja                                 | Ja                                                                |

| PLB-Schreibdatenbus          |          |                                    |                                                                   |

| PLB_MnWrDAck                 | Eingabe  | Ja                                 | Ja                                                                |

| PLB_MnWrBTerrn               | Eingabe  | Nein                               | Ja                                                                |

| Mn_wrBurst                   | Ausgabe  | Nein                               | Nein                                                              |

| Mn_wDBus                     | Ausgabe  | Ja                                 | Ja                                                                |

| PLB-Lesedatenbus             |          |                                    |                                                                   |

| PLB_MnRdAck                  | Eingabe  | Ja                                 | Ja                                                                |

| PLB_MnRdBTerm                | Eingabe  | Nein                               | Ja                                                                |

| PLB_MnRdWdAddr               | Eingabe  | Ja                                 | Ja                                                                |

| PLB_MnRdDBus                 | Eingabe  | Ja                                 | Ja                                                                |

| Mn_rdBurst                   | Ausgabe  | Nein                               | Nein                                                              |

| Obermengensignale            |          |                                    |                                                                   |

| SYS_plbClk2x                 | Eingabe  | Nein                               | Ja                                                                |

| PLB_MnWrAck                  | Eingabe  | Nein                               | Ja                                                                |

**[0095]** Tabelle 2 führt verschiedene PLB-Signale aus der Perspektive eines Slave auf, und sie gibt an, ob diese Signale bei einer einfachen CPU benötigt werden und bei einem FPGA mit akzeptabler Leistung implementiert werden können.

TABELLE 2

| SIGNALBEZEICHNUNG        | RICHTUNG | IN CPU BENÖTIGT                    | IM FPGA                                                           |

|--------------------------|----------|------------------------------------|-------------------------------------------------------------------|

| PLB-Transferkennzeichner |          |                                    |                                                                   |

| SYS_plbClk               | Eingabe  | Ja                                 | Ja                                                                |

| SYS_plbReset             | Eingabe  | Ja                                 | Ja                                                                |

| PLB_PAValid              | Eingabe  | Ja                                 | Ja                                                                |

| PLB_busLock              | Eingabe  | Nein                               | Ja                                                                |

| PLB_pendReq              | Eingabe  | Nein                               | Ja                                                                |

| PLB_pendPri              | Eingabe  | Nein                               | Ja<br>(feststehender Wert)                                        |

| PLB_reqPri               | Eingabe  | Nein                               | Ja<br>(feststehender Wert)                                        |

| PLB_masterID             | Eingabe  | Nein                               | Ja                                                                |

| PLB_RNW                  | Eingabe  | Ja                                 | Ja                                                                |

| PLB_BE                   | Eingabe  | Ja<br>(kein Burst)                 | Ja<br>(kein Burst oder Bursts mit festgelegter Länge)             |

| PLB_size                 | Eingabe  | Ja<br>(kein Burst oder Cache-Line) | Ja<br>(kein Burst, Bursts mit festgelegter Länge oder Cache-Line) |

| PLB_type                 | Eingabe  | Nein                               | Nein                                                              |

| PLB_Msize                | Eingabe  | Nein                               | Ja<br>(feststehender Wert)                                        |

| PLB_compress             | Eingabe  | Ja                                 | Ja                                                                |

| PLB_guarded              | Eingabe  | Ja                                 | Ja                                                                |

| PLB_ordered              | Eingabe  | Nein                               | Ja                                                                |

| PLB_lockErr              | Eingabe  | Nein                               | Ja                                                                |

| PLB_abort                | Eingabe  | Nein                               | Ja<br>(feststehender Wert)                                        |

| PLB_Abus                 | Eingabe  | Ja                                 | Ja                                                                |

| SI_addrAck               | Ausgabe  | Ja                                 | Ja                                                                |

| SI_wait                  | Ausgabe  | Nein                               | Nein                                                              |

| SI_Ssize                 | Ausgabe  | Nein                               | Nein                                                              |

| SI_rearbitrate           | Ausgabe  | Nein                               | Ja<br>(gemeinsam genutzter Bus)                                   |

| SI_Mbusy                 | Ausgabe  | Ja                                 | Ja                                                                |

| SI_Merr                  | Ausgabe  | Ja                                 | Ja                                                                |

| PLB-Adress-Pipelining    |          |                                    |                                                                   |

| PLB_SAValid              | Eingabe  | Ja<br>(Leistung)                   | Ja                                                                |

| PLB_rdprim               | Eingabe  | Ja<br>(Leistung)                   | Ja                                                                |

| PLB_wrPrim               | Eingabe  | Ja<br>(Leistung)                   | Ja                                                                |

| PLB-Schreibdatenbus      |          |                                    |                                                                   |

| PLB_wrDBus               | Eingabe  | Ja                                 | Ja                                                                |

| PLB_wrBurst              | Eingabe  | Nein                               | Nein                                                              |

| SI_wDAck                 | Ausgabe  | Ja                                 | Ja                                                                |

| SI_wrComp                | Ausgabe  | Ja                                 | Ja                                                                |

| SI_wrBTerm               | Ausgabe  | Nein                               | Ja                                                                |

| PLB-Lesedatenbus         |          |                                    |                                                                   |

| PLB_rdBurst              | Eingabe  | Nein                               | Nein                                                              |

| PLB_SI_rdDBus            | Ausgabe  | Ja                                 | Ja                                                                |

| PLB_rdWdAddr             | Ausgabe  | Ja                                 | Ja                                                                |

## IV. FPGA-IMPLEMENTIERUNG

**[0096]** Gemäß einer Ausführungsform der vorliegenden Erfindung sorgt ein programmierbarer Schnittstellenkern (PIC) für die Kommunikation zwischen einer zentralen Verarbeitungseinheit (CPU) und anderen FPGA-in-

ternen und FPGA-externen Vorrichtungen. Aufgrund der oben beschriebenen, von der vorliegenden Erfindung bestimmten Teilmenge der PLB-Funktionen kann der PIC zum effizienten Implementieren dieser Funktionen vorteilhafterweise standardmäßige FPGA-Ressourcen benutzen, d.h. Nachschlagetabellen, Multiplexer und Flip-Flops. Die vorliegende Erfindung nutzt sowohl das Pipelining als auch logische Funktionen, die sich problemlos in diesen Ressourcen abbilden lassen.

#### A. ZENTRALE VERARBEITUNGSEINHEIT (CPU)