(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4154880号

(P4154880)

(45) 発行日 平成20年9月24日(2008.9.24)

(24) 登録日 平成20年7月18日(2008.7.18)

(51) Int.Cl.

F 1

|      |        |           |      |        |     |

|------|--------|-----------|------|--------|-----|

| GO2F | 1/1335 | (2006.01) | GO2F | 1/1335 | 520 |

| GO2B | 5/02   | (2006.01) | GO2B | 5/02   | B   |

| GO2B | 5/08   | (2006.01) | GO2B | 5/08   | A   |

| GO2F | 1/1343 | (2006.01) | GO2F | 1/1343 |     |

| GO2F | 1/1368 | (2006.01) | GO2F | 1/1368 |     |

請求項の数 5 (全 21 頁) 最終頁に続く

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2001-294719 (P2001-294719)  |

| (22) 出願日  | 平成13年9月26日 (2001.9.26)        |

| (65) 公開番号 | 特開2003-107453 (P2003-107453A) |

| (43) 公開日  | 平成15年4月9日 (2003.4.9)          |

| 審査請求日     | 平成16年12月2日 (2004.12.2)        |

|           |                                               |

|-----------|-----------------------------------------------|

| (73) 特許権者 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号 |

| (74) 代理人  | 100095728<br>弁理士 上柳 雅善                        |

| (74) 代理人  | 100107261<br>弁理士 須澤 修                         |

| (72) 発明者  | 村井 一郎<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内        |

審査官 福島 浩司

最終頁に続く

(54) 【発明の名称】電気光学装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の画素を含んでなる画像表示領域を有し、各前記複数の画素が入射光を反射する反射領域、及び入射光を透過する透過領域を含んでなる電気光学装置において、

前記反射領域には反射性を備えた金属膜が形成されてなり、前記透過領域には透明電極が少なくとも形成されており、

前記反射領域及び前記透過領域の両領域においては前記金属膜及び前記透明電極の上層に配向膜が形成されているとともに、前記金属膜及び前記透明電極の下層に前記金属膜の表面を凹凸形状にする凹凸パターンが形成され、

前記凹凸パターンの凸部分は、前記透過領域と反射領域との境界部分を跨がないように配設され、

前記透明電極の形成領域は、前記金属膜の形成領域よりも広いことを特徴とする電気光学装置。

## 【請求項 2】

前記金属膜は、前記透明電極の表面に形成されていることを特徴とする特徴とする請求項 1 に記載の電気光学装置。

## 【請求項 3】

前記凹凸パターンは、前記凸部分の基礎となる第 1 形成層と、前記第 1 形成層を覆う第 2 形成層とからなり、

前記第 2 形成層は、第 1 形成層におけるエッジが前記凹凸パターンに現れないように形

成されることを特徴とする請求項 1 または 2 に記載の電気光学装置。

【請求項 4】

前記複数の画素は、それぞれがスイッチング用の TFT と、前記画素電極に印加される電圧を保持するための蓄積容量とを有し、

前記 TFT および前記蓄積容量は前記反射領域に形成され、

前記反射領域における前記 TFT および前記蓄積容量が形成された領域には、前記第 2 形成層のみが積層されていることを特徴とする請求項 1 ~ 3 のいずれか一項に記載の電気光学装置。

【請求項 5】

複数の画素を含んでなる画像表示領域を有し、各前記複数の画素が入射光を反射する反射領域、及び入射光を透過する透過領域を含んでなる電気光学装置の製造方法において、

基板の上層に、第 1 形成層を形成する工程と、

前記第 1 形成層におけるエッジが表面に現れないように前記第 1 形成層を覆う第 2 形成層を形成する工程と、

前記第 1 形成層および第 1 形成層からなる凹凸パターン上に透明電極を形成する工程と、

前記透明電極の表面に金属膜を形成する工程と、

前記金属膜のエッチングを含み、前記透明電極を露出させた前記透過領域を有する前記反射電極を形成する工程と、

前記反射領域及び前記透過領域の両領域に配向膜を形成する工程と、を具備してなり、

前記凹凸パターンの凸部分は、前記透過領域と反射領域との境界部分を跨がないように配設することを特徴とする電気光学装置の製造方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、電気光学装置及びその製造方法に関する。さらに詳しくは、携帯電話機、モバイルコンピュータ等に好適に用いられる、透過窓の部分にも配向処理が十分に施され、画素内の透過モード表示におけるコントラストに優れるとともに、反射特性にも優れた電気光学装置及びその製造方法に関する。

【0002】

【従来の技術】

電気光学装置（例えば、液晶表示装置、EL発光表示装置等）は、携帯電話機、モバイルコンピュータ等の各種機器の直視型の表示装置として広く用いられている。このような電気光学装置のうち、例えば、アクティブマトリクス型で、半透過・半反射型の液晶表示装置においては、対向配置された TFT アレイ基板と対向基板とがシール材で貼り合わされているとともに、基板間のシール材で区画された領域内に電気光学物質としての液晶が封入、保持されている。

【0003】

また、TFT アレイ基板の表面に、対向基板の側から入射してきた外光を対向基板の方向に反射するための反射電極が形成されており、対向基板側から入射した光を TFT アレイ基板の反射電極で反射し、対向基板側から出射した光によって画像を表示する（反射モード）。また、反射電極には光を透過する透過窓が形成され、この透過窓を覆うように、反射電極の下層側に透明電極が形成され、バックライトからの光のうち透過窓を透過した光によって画像を表示する（透過モード）。

【0004】

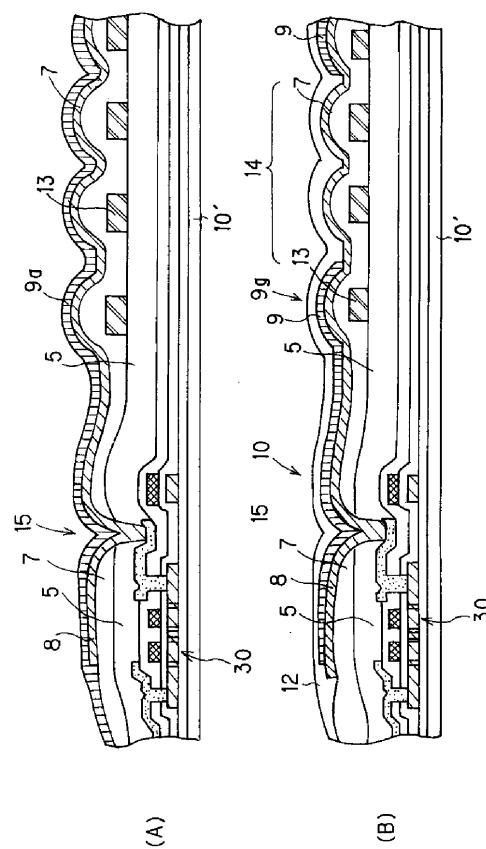

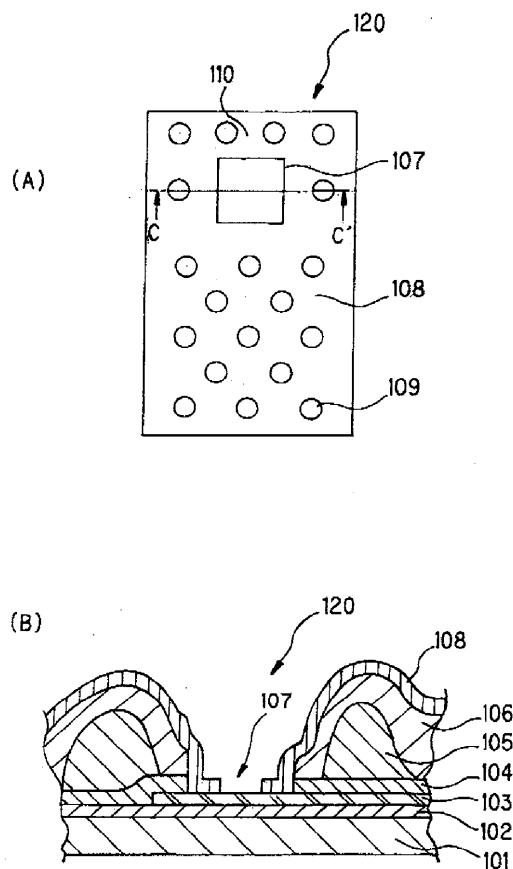

このような液晶表示装置に用いられる TFT アレイ基板 120 としては、例えば、図 14 (A) に示すように、画素 110 の一部に、後述する凹凸層（図示せず）と、この凹凸層上に形成された、外光を反射して画像を表示する反射電極 108（反射電極 108 には、凹凸層の表面凹凸形状に対応した形状の反射用の凹凸 109 が形成されている）と、反射電極 108 を形成しない部分である透過窓 107 と、透過窓 107 に対応した領域を覆う

10

20

30

40

50

ように形成されたITO (Indium Tin Oxide) からなる透明電極 (図示せず) とを備えたものとし、バックライト (図示せず) からの光を、透過窓107から透過させて画像を表示するものが用いられている。このようなTFTアレイ基板120は、図14 (B) に示すように (図14 (B) は図14 (A) のC-C'線における断面図である)、基板101上に、シリコン酸化膜 (SiO<sub>2</sub>膜) 等の下地保護膜102、ITO等からなる透明電極103及びアルミニウムもしくはアルミニウムの合金あるいはアルミニウムの積層膜からなるソース線 (図示せず)、薄膜トランジスタ (図示せず)、シリコン窒化膜 (SiN膜) 等の保護膜104 (この保護膜104は形成しない場合がある)、反射電極108の表面に反射用の凹凸109を形成するためのアクリル樹脂等の有機系の感光性樹脂の2層からなる凹凸形成層105及び凹凸層106、及びアルミニウムや銀、もしくはこれらの合金、又はチタン、窒化チタン、モリブデン、タンタル等との積層膜からなり、透過窓107を有する反射電極108等を積層して形成されている。

#### 【0005】

##### 【発明が解決しようとする課題】

このような構成の反射電極を用いた液晶表示装置は、外光の明るさに影響されず、視認性に優れた液晶表示装置を提供することを可能にしたが、一方、反射電極108の表面に反射用の凹凸109を形成するために用いられるアクリル樹脂等からなる凹凸形成層105及び凹凸層106の膜厚は、2層で最大5μmにも達するほど大きいため、凹凸形成層105及び凹凸層106が存在しない透過窓107の部分においては、画素全体ではかなり薄い構造 (段差を有する構造) になる。このためポリイミド等の配向膜の形成 (塗布) 時、配向膜は、透過窓107の部分には形成 (塗布) されず、また、十分な配向処理を施すことが困難になり、表示特性に悪影響を及ぼすことになる。例えば、ノーマリホワイトの場合、電位を加えても、透過窓107の部分だけ黒くならず、白く見えてしまうという問題があった。

#### 【0006】

本発明は、上述の問題に鑑みてなされたものであって、透過窓の部分にも配向処理が十分に施された、画素内の透過モード表示におけるコントラストに優れるとともに、反射特性にも優れた電気光学装置及びその製造方法を提供することを目的とする。

#### 【0007】

##### 【課題を解決するための手段】

上述の目的を達成するために、本発明の電気光学装置は、複数の画素を含んでなる画像表示領域を有し、各複数の画素が入射光を反射する反射領域、及び入射光を透過する透過領域を含んでなる電気光学装置において、反射領域には反射性を備えた金属膜が形成されてなり、透過領域には透明電極が少なくとも形成されており、反射領域及び透過領域の両領域においては金属膜及び透明電極の上層に配向膜が形成されるとともに、金属膜及び透明電極の下層に金属膜の表面を凹凸形状にする凹凸パターンが形成され、凹凸パターンの凸部分は、透過領域と反射領域との境界部分を跨がないように配設され、透明電極の形成領域は、金属膜の形成領域よりも広いことを特徴とする。

また、金属膜は、透明電極の表面に形成されていることが好ましい。

また、凹凸パターンは、凸部分の基礎となる第1形成層と、第1形成層を覆う第2形成層とからなり、第2形成層は、第1形成層におけるエッジが凹凸パターンに現れないよう形成されることが好ましい。

また、複数の画素は、それぞれがスイッチング用のTFTと、画素電極に印加される電圧を保持するための蓄積容量とを有し、TFTおよび蓄積容量は反射領域に形成され、反射領域におけるTFTおよび蓄積容量が形成された領域には、第2形成層のみが積層されていることが好ましい。

#### 【0008】

このように構成することによって、反射電極の表面に、反射光を適度に散乱させる表面凹凸形状 (反射用の凹凸) を備え、また、透過窓の部分にも配向膜を十分に形成 (塗布) して、配向処理を十分に施すことが可能になり、画素内の透過モード表示におけるコントラ

10

20

30

40

50

ストに優れるとともに、反射特性にも優れた電気光学装置を提供することができる。

【0009】

また、本発明の電気光学装置は、前記凹凸層の凸部分が、前記透過窓に対応した領域とそれ以外の領域との境界部分を跨ることなく前記境界部分の内側又は外側のいずれかに位置するように配設されるものであることが好ましい。

【0010】

このように構成することによって、反射電極にフォトリソグラフィ技術及びエッティング技術を用いて透過窓の形成を行う場合、エッティング剤等が、反射電極と凹凸層の間に侵入するのを有効に防ぐことができる。

【0011】

また、本発明の電気光学装置は、前記凹凸層が、透光性の感光性樹脂から形成されてなるものであることが好ましい。

【0012】

このように構成することによって、製造工程を効率化することができるとともに、透過特性の低減を防止することができる。

【0013】

また、本発明の電気光学装置は、前記凹凸層の下層側に、凹凸形成層がさらに配設されてなるものであることが好ましい。

【0014】

このように構成することによって、エッジや、平坦部分の少ない滑らかな表面凹凸形状を有する凹凸層を容易に形成することができる。

【0015】

また、本発明の電気光学装置は、前記凹凸形成層が、透光性の感光性樹脂から形成されてなるものであることが好ましい。

【0016】

このように構成することによって、所望の位置に、所望の大きさの、表面凹凸形状を有する凹凸層を効率よく形成することができる。

【0017】

また、本発明の電気光学装置は、前記反射電極が、アルミニウムや銀、もしくはこれらの合金、又はチタン、窒化チタン、モリブデン、タンタル等との積層膜から構成されたものであることが好ましい。

【0018】

このように構成することによって、光反射効率を高めることができる。

【0019】

また、本発明の電気光学装置は、前記透明電極が、ITO膜から構成されたものであることが好ましい。

【0020】

このように構成することによって、透過モード表示におけるコントラストを高めることができる。

【0021】

また、本発明の電気光学装置は、前記透明電極の形成領域が、前記反射電極の形成領域よりも広いものであることが好ましい。

【0022】

このように構成することによって、透過モード表示におけるコントラストを高めることができます。

【0023】

また、本発明の電気光学装置は、前記透明電極と前記反射電極とが、電気的に接続されてなるものであることが好ましい。

【0024】

このように構成することによって、消費電力の低減化を図ることができます。

10

20

30

40

50

**【 0 0 2 5 】**

また、本発明の電気光学装置は、前記透明電極が、前記透過窓の外側で電位供給線と電気的に接続されてなるものであることが好ましい。

**【 0 0 2 6 】**

このように構成することによって、消費電力の低減化を図ることができる。

**【 0 0 2 7 】**

また、本発明の電気光学装置の製造方法は、複数の画素を含んでなる画像表示領域を有し、各複数の画素が入射光を反射する反射領域、及び入射光を透過する透過領域を含んでなる電気光学装置の製造方法において、基板の上層に、第1形成層を形成する工程と、第1形成層におけるエッジが表面に現れないように第1形成層を覆う第2形成層を形成する工程と、第1形成層および第1形成層からなる凹凸パターン上に透明電極を形成する工程と、透明電極の表面に金属膜を形成する工程と、金属膜のエッチングを含み、透明電極を露出させた透過領域を有する反射電極を形成する工程と、反射領域及び透過領域の両領域に配向膜を形成する工程と、を具備してなり、凹凸パターンの凸部分は、透過領域と反射領域との境界部分を跨がないように配設されることを特徴とする。

10

**【 0 0 2 8 】**

このように構成することによって、反射電極の表面に、反射光を適度に散乱させる表面凹凸形状（反射用の凹凸）を備え、画素内の透過モード表示におけるコントラストに優れるとともに、反射特性にも優れた電気光学装置を効率よくかつ低コストで提供することができる。

20

**【 0 0 2 9 】**

この場合、前記凹凸層の凸部分を、前記透過窓に対応した領域とそれ以外の領域との境界部分を跨ることなく前記境界部分の内側又は外側のいずれかに位置するように配設することが好ましい。

**【 0 0 3 0 】**

このように構成することによって、反射電極にフォトリソグラフィ技術及びエッチング技術を用いて透過窓の形成を行う場合、エッチング剤等が、反射電極と凹凸層の間に侵入するのを有效地に防ぐことができる。

**【 0 0 3 1 】**

また、本発明の電気光学装置の製造方法は、前記凹凸層を、透光性の感光性樹脂から形成することが好ましい。

30

**【 0 0 3 2 】**

このように構成することによって、製造工程を効率化することができるとともに、透過特性の低減を防止することができる。

**【 0 0 3 3 】**

また、本発明の電気光学装置の製造方法は、前記凹凸層の下層側に、凹凸形成層をさらに配設することが好ましい。

**【 0 0 3 4 】**

このように構成することによって、エッジや、平坦部分の少ない滑らかな表面凹凸形状を有する凹凸層を効率よくかつ低コストで形成することができる。

40

**【 0 0 3 5 】**

また、本発明の電気光学装置の製造方法は、前記凹凸形成層を、透光性の感光性樹脂から形成することが好ましい。

**【 0 0 3 6 】**

このように構成することによって、所望の位置に、所望の大きさの、表面凹凸形状を有する凹凸層を効率よくかつ低コストで形成することができる。

**【 0 0 3 7 】**

また、本発明の電気光学装置の製造方法は、前記反射電極を、アルミニウムや銀、もしくはこれらの合金、又はチタン、窒化チタン、モリブデン、タンタル等との積層膜から構成することが好ましい。

50

## 【0038】

このように構成することによって、光反射効率の高い電気光学装置を効率よくかつ低コストで提供することができる。

## 【0039】

また、本発明の電気光学装置の製造方法は、前記透明電極を、ITO膜から構成することが好ましい。

## 【0040】

このように構成することによって、透過モード表示におけるコントラストの高い電気光学装置を効率よくかつ低コストで提供することができる。

## 【0041】

また、本発明の電気光学装置の製造方法は、前記透明電極の形成領域を、前記反射電極の形成領域よりも広く形成することが好ましい。

10

## 【0042】

このように構成することによって、透過モード表示におけるコントラストの高い電気光学装置を効率よくかつ低コストで提供することができる。

## 【0043】

また、本発明の電気光学装置の製造方法は、前記透明電極と前記反射電極とを、電気的に接続することが好ましい。

## 【0044】

このように構成することによって、消費電力の低減化を図った電気光学装置を効率よくかつ低コストで提供することができる。

20

## 【0045】

また、本発明の電気光学装置の製造方法は、前記透明電極を、前記透過窓の外側で電位供給線と電気的に接続することが好ましい。

## 【0046】

このように構成することによって、消費電力の低減化を図った電気光学装置を効率よくかつ低コストで提供することができる。

## 【0047】

## 【発明の実施の形態】

以下、本発明の電気光学装置及びその製造方法の実施の形態を図面を参照しつつ、具体的に説明する。

30

## 【0048】

## (電気光学装置の基本的な構成)

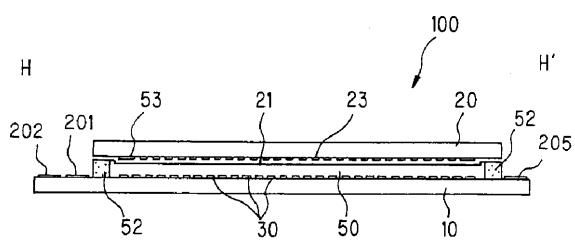

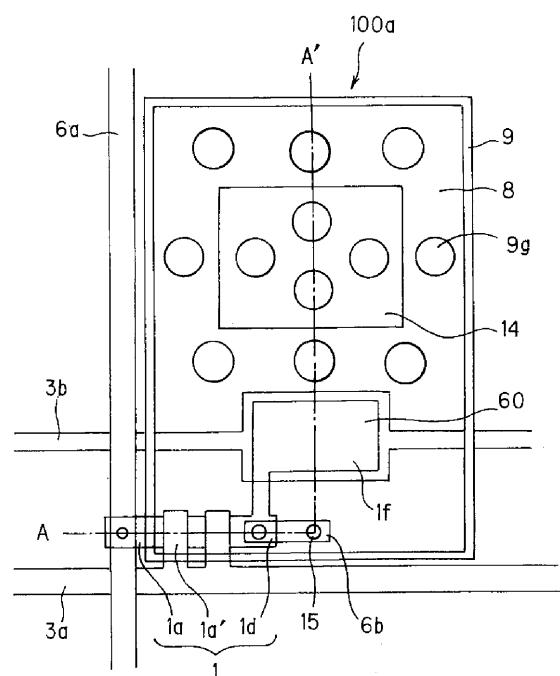

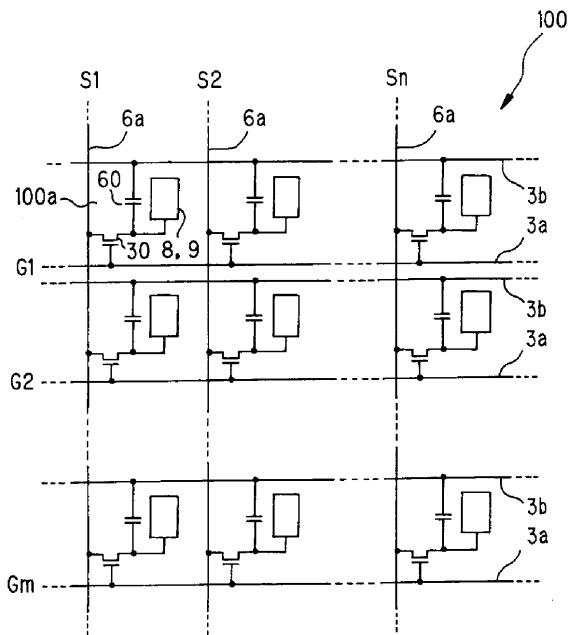

図1は、本発明の電気光学装置の一の実施の形態である液晶表示装置を、各構成要素とともにに対向基板の側から見た平面図であり、図2は、図1のH-H'線における断面図である。図3は、電気光学装置(液晶表示装置)の画像表示領域においてマトリクス状に形成された複数の画素における各種素子、配線等の等価回路図である。なお、本形態の説明に用いた各図においては、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材毎に縮尺を異ならしめてある。

## 【0049】

図1及び図2において、本実施の形態の電気光学装置(液晶表示装置)100は、TFTアレイ基板10(第1の基板)と対向基板20(第2の基板)とがシール材52によって貼り合わされ、このシール材52によって区画された領域(液晶封入領域)内には、電気光学物質としての液晶50が封入、保持されている。シール材52の形成領域の内側の領域には、遮光性材料からなる周辺見切り53が形成されている。シール材52の外側の領域には、データ線駆動回路201、及び実装端子202がTFTアレイ基板10の一辺に沿って形成されており、この一辺に隣接する2辺に沿って走査線駆動回路204が形成されている。TFTアレイ基板10の残る一辺には、画像表示領域の両側に設けられた走査線駆動回路204の間を接続するための複数の配線205が設けられており、さらに、周辺見切り53の下側等を利用して、プリチャージ回路や検査回路が設けられることもある

40

50

。また、対向基板 20 のコーナー部の少なくとも 1 箇所においては、TFT アレイ基板 10 と対向基板 20 との間で電気的導通をとるための基板間導通材 206 が配設されている。

#### 【 0 0 5 0 】

なお、データ線駆動回路 201 及び走査線駆動回路 204 を TFT アレイ基板 10 の上に形成する代わりに、例えば、駆動用 LSI が実装された TAB (テープ オートメイティッド ボンディング) 基板と TFT アレイ基板 10 の周辺部に形成された端子群とを異方性導電膜を介して電気的及び機械的に接続するようにしてもよい。なお、電気光学装置 100 においては、使用する液晶 50 の種類、すなわち、TN (ツイステッドネマティック) モード、STN (スーパー TN) モード等々の動作モードや、ノーマリホワイトモード／ノーマリブラックモードの別に応じて、偏光フィルム、位相差フィルム、偏光板等が所定の向きに配置されるが、ここでは図示を省略している。

#### 【 0 0 5 1 】

また、電気光学装置 100 をカラー表示用として構成する場合には、対向基板 20 において、TFT アレイ基板 10 の後述する各画素電極に対向する領域に、例えば、赤 (R)、緑 (G)、青 (B) のカラーフィルタをその保護膜とともに形成する。

#### 【 0 0 5 2 】

このような構造を有する電気光学装置 100 の画像表示領域においては、図 3 に示すように、複数の画素 100a がマトリクス状に構成されているとともに、これらの画素 100a の各々には、画素スイッチング用の TFT30 が形成されており、画素信号 S1、S2、…、Sn を供給するデータ線 6a が TFT30 のソースに電気的に接続されている。データ線 6a に書き込む画素信号 S1、S2、…、Sn は、この順に線順次で (線番号の順番で) 供給してもよく、相隣接する複数のデータ線 6a 同士に対して、グループ毎に供給するようにしてもよい。また、TFT30 のゲートには走査線 3a が電気的に接続されており、所定のタイミングで、走査線 3a にパルス的に走査信号 G1、G2、…、Gm をこの順に線順次で (線番号の順番で) 印加するように構成されている。反射電極 9 及び透明電極 8 は、TFT30 のドレンに電気的に接続されており、スイッチング素子である TFT30 を一定期間だけオン状態とすることにより、データ線 6a から供給される画素信号 S1、S2、…、Sn を各画素に所定のタイミングで書き込む。このようにして反射電極 9 及び透明電極 8 を介して液晶に書き込まれた所定レベルの画素信号 S1、S2、…、Sn は、図 2 に示す対向基板 20 の対向電極 21 との間で一定期間保持される。

#### 【 0 0 5 3 】

ここで、液晶 50 は、印加される電圧レベルによって分子集合の配向や秩序が変化することにより、光を変調し、階調表示を可能にする。ノーマリホワイトモードであれば、印加された電圧に応じて入射光がこの液晶 50 の部分を通過する光量が低下し、ノーマリブラックモードであれば、印加された電圧に応じて入射光がこの液晶 50 の部分を通過する光量が増大する。その結果、全体として電気光学装置 100 からは画素信号 S1、S2、…、Sn に応じたコントラストを持つ光が出射される。

#### 【 0 0 5 4 】

なお、保持された画素信号 S1、S2、…、Sn がリークするのを防ぐために、反射電極 9 と対向電極との間に形成される液晶容量と並列に蓄積容量 60 (図 3 参照) を附加することがある。例えば、反射電極 9 及び透明電極 8 の電圧は、ソース電圧が印加された時間よりも 3 枝も長い時間だけ蓄積容量 60 により保持される。これにより、電荷の保持特性は改善され、コントラスト比の高い電気光学装置 100 を実現することができる。なお、蓄積容量 60 を形成する方法としては、図 3 に示すように、蓄積容量 60 を形成するための配線である容量線 3b との間に形成する場合、及び前段の走査線 3a との間に形成する場合のいずれであってもよい。

#### 【 0 0 5 5 】

( TFT アレイ基板の構成)

10

20

30

40

50

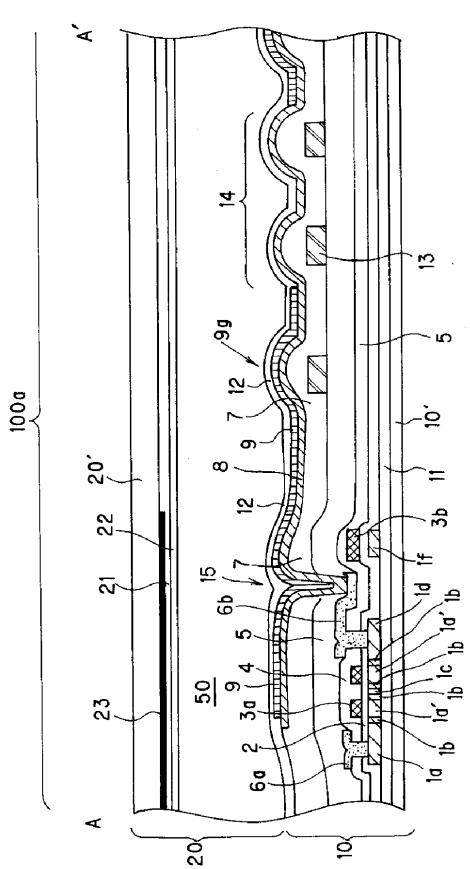

図4は、本実施の形態に用いたTFTアレイ基板の相互に隣接する複数の画素群の平面図である。図5は、図4のA-A'線における画素の断面図である。

#### 【0056】

図4において、TFTアレイ基板上には、アルミニウムや銀、もしくはこれらの合金、又はチタン、窒化チタン、モリブデン、タンタル等との積層膜から構成された反射電極9がマトリクス状に形成されており(図4においては一画素を示す)、これら各反射電極9に対して、画素スイッチング用のTFT30(図3参照)がそれぞれ透明電極8を介して電気的に接続している。また、反射電極9を形成する領域の縦横の境界に沿って、データ線6a、走査線3a及び容量線3bが形成され、TFT30(図3参照)は、データ線6a及び走査線3aに対して接続している。すなわち、データ線6aは、コンタクト孔を介してTFT30(図3参照)の高濃度ソース領域1aに電気的に接続し、透明電極8は、コンタクト孔15及びソース線6bを介してTFT30(図3参照)の高濃度ドレイン領域1dに電気的に接続している。また、TFT30(図3参照)のチャネル形成用領域1a'に対向するように走査線3aが伸びている。なお、蓄積容量60(蓄積容量素子)は、画素スイッチング用のTFT30(図3参照)を形成するための半導体膜1の延設部分1fを導電化したものを下電極とし、この下電極1fに、走査線3aと同層の容量線3bが上電極として重なった構造になっている。

#### 【0057】

図4に示すように、このように構成した各画素100aにおいては、透過窓14を有する反射電極9が形成され、それらの表面には、後述する凹凸層(図示せず)が全面に形成されている。透過窓14に対応する領域は、透明電極8によって覆われ、透過モードで画像表示を行う透過領域であり、その他の領域は、後述する凹凸形成層(図示せず)、凹凸層(図示せず)及び反射電極9を備えた反射領域であり、ここでは反射モードで画像表示を行う。

#### 【0058】

図5に示すように、この反射領域のA-A'線で切断したときの断面は、TFTアレイ基板10の基体としての透明なTFTアレイ基板用のガラス基板10'の表面に、厚さが100nm~500nmのシリコン酸化膜(絶縁膜)からなる下地保護膜11が形成され、この下地保護膜11の表面には、厚さが30nm~100nmの島状の半導体膜1が形成されている。半導体膜1の表面には、厚さが約50~150nmのシリコン酸化膜からなるゲート絶縁膜2が形成され、このゲート絶縁膜2の表面に、厚さが300nm~800nmの走査線3aがゲート電極として通っている。半導体膜1のうち、走査線3aに対してゲート絶縁膜2を介して対向する領域がチャネル形成用領域1a'になっている。このチャネル形成用領域1a'に対して一方側には、低濃度領域1b及び高濃度ソース領域1aを備えるソース領域が形成され、他方側には低濃度領域1b及び高濃度ドレイン領域1dを備えるドレイン領域が形成され、その中間には、ソース、ドレインのどちらの領域にも属さない高濃度領域1cが形成されている。

#### 【0059】

画素スイッチング用のTFT30(図3参照)の表面側には、厚さが300nm~800nmのシリコン酸化膜からなる第1層間絶縁膜4、及び厚さが100nm~800nmのシリコン窒化膜からなる第2層間絶縁膜5(表面保護膜)が形成されている(この第2層間絶縁膜5(表面保護膜)は形成しなくてもよい)。第1層間絶縁膜4の表面には、厚さが300nm~800nmのデータ線6aが形成され、このデータ線6aは、第1層間絶縁膜4に形成されたコンタクト孔を介して高濃度ソース領域1aに電気的に接続している。

#### 【0060】

第2層間絶縁膜(表面保護膜)5の上層には、有機系樹脂等の感光性樹脂からなる凹凸形成層13及び凹凸層7がこの順に形成され、凹凸層7の表面には、ITO膜等からなる透明電極8が形成され、透明電極8の上層には、アルミニウムや銀、もしくはこれらの合金、又はチタン、窒化チタン、モリブデン、タンタル等との積層膜からなる反射電極9が順

10

20

30

40

50

次形成されている。反射電極 9 の表面には、凹凸層 7 の表面凹凸形状に対応した凹凸パターン 9 g が形成されている。

【 0 0 6 1 】

反射電極 9 及び透明電極 8 は、コンタクト孔 15 を介してソース線 6 b と電気的に接続している。

【 0 0 6 2 】

反射電極 9 の表面には、背面光源からの光を透過するための透過窓 14 が形成されている。

【 0 0 6 3 】

反射電極 9 の表面側と、透過窓 14 の形成によって最上層となった透明電極 8 の表面側にはポリイミド膜からなる配向膜 12 が形成されている。この配向膜 12 の表面側には、ラビング処理が施されている。 10

【 0 0 6 4 】

また、高濃度ドレイン領域 1 d からの延設部分 1 f (下電極) に対しては、ゲート絶縁膜 2 と同時形成された絶縁膜 (誘電体膜) を介して、走査線 3 a と同層の容量線 3 b が上電極として対向することにより、蓄積容量 60 (図 3 参照) が構成されている。

【 0 0 6 5 】

なお、TFT 30 (図 3 参照) は、好ましくは上述のように LDD 構造 (ライトナー・ドープト・ドレイン構造) をもつが、低濃度領域 1 b に相当する領域に不純物イオンの打ち込みを行わないオフセット構造を有していてもよい。また、TFT 30 (図 3 参照) は、ゲート電極 (走査線 3 a の一部) をマスクとして高濃度で不純物イオンを打ち込み、自己整合的に高濃度のソース及びドレイン領域を形成したセルファアライン型の TFT であってもよい。 20

【 0 0 6 6 】

また、本実施の形態では、TFT 30 (図 3 参照) のゲート電極 (走査線 3 a) をソース - ドレイン領域の間に 2 個配置したデュアルゲート (ダブルゲート) 構造としたが、1 個配置したシングルゲート構造であってもよく、また、これらの間に 3 個以上のゲート電極を配置したトリプルゲート以上の構造であってもよい。複数個配置した場合、各々のゲート電極には同一の信号が印加されるようにする。このようにデュアルゲート (ダブルゲート)、又はトリプルゲート以上で TFT 30 (図 3 参照) を構成すれば、チャネルとソース - ドレイン領域の接合部でのリーク電流を防止でき、オフ時の電流を低減することができる。これらのゲート電極の少なくとも 1 個を LDD 構造又はオフセット構造にすれば、さらに、オフ電流を低減でき、安定したスイッチング素子を得ることができる。 30

【 0 0 6 7 】

図 4 ~ 図 5 において、TFT アレイ基板 10 では、各画素 100 a の反射領域には、反射電極 9 の表面のうち、TFT 30 (図 3 参照) の形成領域及びコンタクト孔 15 から外れた領域 (凹凸層形成領域) には、前述のように凹凸パターン 9 g が形成されている。

【 0 0 6 8 】

このような凹凸パターン 9 g を構成するにあたって、本実施の形態の TFT アレイ基板 10 では、前述の凹凸層形成領域には、アクリル樹脂等の有機系の透光性の感光性樹脂からなる凹凸形成層 13 が第 2 層間絶縁膜 5 の表面に 1 ~ 3  $\mu\text{m}$  の厚さで例えば、スピンドルコートによって形成され、この凹凸形成層 13 の上層には、アクリル樹脂等の有機系の透光性の感光性樹脂等のような流動性材料から形成された絶縁膜からなる凹凸層 7 が 1 ~ 2  $\mu\text{m}$  の厚さで例えば、スピンドルコートによって積層されている。 40

【 0 0 6 9 】

凹凸形成層 13 には、多数の凹凸が形成されている。このため、図 5 に示すように、反射電極 9 の表面には、凹凸層 7 の表面凹凸形状に対応する凹凸パターン 9 g が形成され、この凹凸パターン 9 g では、凹凸層 7 によって、凹凸形成層 13 のエッジ等が現れないようになっている。なお、凹凸層 7 を形成せずに、凹凸形成層 13 を形成した後、ベーク工程を行うことにより、凹凸形成層 13 の凹凸の縁を滑らかにしてもよい。

10

20

30

40

50

## 【0070】

(対向基板の構成)

図5において、対向基板20では、対向基板側のガラス基板20'上の、TFTアレイ基板10に形成されている反射電極9の縦横の境界領域と対向する領域にブラックマトリクス、又はブラックストライプ等と称せられる遮光膜23が形成され、その上層側には、ITO膜からなる対向電極21が形成されている。また、対向電極21の上層側には、ポリイミド膜からなる配向膜22が形成される。なお、TFTアレイ基板10と対向基板20との間には、液晶50が、保持、封入されている。

## 【0071】

(本形態の電気光学装置の作用)

10

このように構成した電気光学装置100(図1参照)では、アルミニウムや銀、もしくはこれらの合金、又はチタン、窒化チタン、モリブデン、タンタル等との積層膜からなる反射電極9が形成されているため、対向基板20側から入射した光をTFTアレイ基板10側で反射し、対向基板20側から出射することができるので、この間に液晶50によって各画素100a毎で光変調を行えば、外光を利用して所望の画像を表示することができる(反射モード)。

## 【0072】

また、電気光学装置100(図1参照)においては、図4～図5において、反射電極9に設けられた透過窓14を覆うように透明電極8が形成されているため、透過型の液晶表示装置としても機能する。すなわち、TFTアレイ基板10の側に配置されたバックライト装置(図示せず)から出射された光は、TFTアレイ基板10の側に入射した後、各画素100aにおいて反射電極9が形成されている領域のうち、反射電極9が形成されていない透過領域(透明電極8によって覆われた透過窓14)を経由して対向基板20側に透過する。このため、液晶50によって各画素100a毎で光変調を行えば、バックライト装置(図示せず)から出射された光を利用して所望の画像を表示することができる(透過モード)。

20

## 【0073】

また、本実施の形態では、反射電極9の下層側のうち、反射電極9と平面的に重なる領域に凹凸形成層13を形成し、この凹凸形成層13の凹凸を利用して、反射電極9の表面に光散乱用の凹凸パターン9gを形成している。また、凹凸パターン9gでは、凹凸層7によって、凹凸形成層13のエッジ等が現れないようになっている。従って、反射モードで画像を表示したとき、散乱反射光で画像を表示するため、視野角依存性が小さい。

30

## 【0074】

さらに、透過窓14の部分にも配向膜12を十分に形成(塗布)して、かつ配向処理を十分に施すことが可能になり、画素内の透過モード表示におけるコントラストに優れるとともに、反射特性にも優れた電気光学装置を提供することができる。

## 【0075】

[TFTの製造方法]

このような構成のTFTアレイ基板10を製造する方法を、図6～図10を参照しつつ、具体的に説明する。

40

## 【0076】

図6～図10はいずれも、本実施の形態のTFTアレイ基板の製造方法を工程順に示す断面図である。

## 【0077】

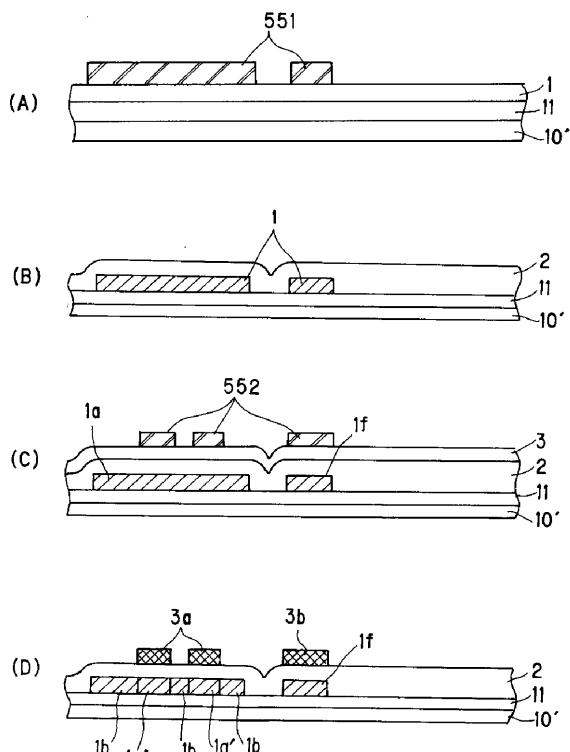

まず、図6(A)に示すように、超音波洗浄等により清浄化したTFTアレイ基板用のガラス基板10'を準備した後、基板温度が150～450の温度条件下で、TFTアレイ基板用のガラス基板10'の全面に、シリコン酸化膜からなる下地保護膜11をプラズマCVD法により100nm～500nmの厚さに形成する。このときの原料ガスとしては、例えば、モノシランと笑気ガス(一酸化二窒素)との混合ガスやTEOS(テトラエトキシシラン:Si(OCH<sub>3</sub>)<sub>4</sub>)と酸素、又はジシランとアンモニアを用いること

50

ができる。

【0078】

次に、基板温度が150～450の温度条件下で、TFTアレイ基板用のガラス基板10'の全面に、非晶質シリコン膜からなる半導体膜1をプラズマCVD法により30nm～100nmの厚さに形成する。このときの原料ガスとしては、例えば、ジシランやモノシランを用いることができる。次に、半導体膜1に対してレーザ光を照射してレーザアニールを施す。その結果、アモルファスの半導体膜1は、一度溶融し、冷却固化過程を経て結晶化する。この際には、各領域へのレーザ光の照射時間が非常に短時間であり、かつ、照射領域も基板全体に対して局所的であるため、基板全体が同時に高温に熱せられることがない。それゆえ、TFTアレイ基板用のガラス基板10'としてガラス基板等を用いても熱による変形や割れ等が生じない。10

【0079】

次に、半導体膜1の表面にフォトリソグラフィ技術を用いてレジストマスク551を介して半導体膜1をエッチングすることにより、図6(B)に示すように、島状の半導体膜1(能動層)を形成するための半導体膜を各々分離した状態に形成する。

【0080】

次に、350以下の温度条件下で、TFTアレイ基板用のガラス基板10'の全面に、CVD法等により半導体膜1の表面に、シリコン酸化膜等からなるゲート絶縁膜2を50nm～150nmの厚さに形成する。このときの原料ガスは、例えば、TEOSと酸素ガスとの混合ガスを用いることができる。ここで形成するゲート絶縁膜2は、シリコン酸化膜に代えてシリコン窒化膜であってもよい。20

【0081】

次に、図示を省略するが、所定のレジストマスクを介して半導体膜1の延設部分1fに不純物イオンを打ち込んで、容量線3bとの間に蓄積容量60を構成するための下電極を形成する(図4及び図5参照)。

【0082】

次に、図6(C)に示すように、スパッタ法等により、TFTアレイ基板用のガラス基板10'の全面に、走査線3a等を形成するためのアルミニウム、タンタル、モリブデン等からなる金属膜、又はこれらの金属のいずれかを主成分とする合金膜からなる導電膜3を300nm～800nmの厚さに形成した後、フォトリソグラフィ技術を用いてレジストマスク552を形成する。30

【0083】

次に、レジストマスクを介して導電膜3をドライエッチングし、図6(D)に示すように、走査線3a(ゲート電極)、容量線3b等を形成する。

【0084】

次に、画素TFT部及び駆動回路のNチャネルTFT部(図示せず)の側には、走査線3aやゲート電極をマスクとして、約 $0.1 \times 10^{13} / \text{cm}^2$ ～約 $10 \times 10^{13} / \text{cm}^2$ のドーズ量で低濃度の不純物イオン(リンイオン)を打ち込んで、走査線3aに対して自己整合的に低濃度領域1bを形成する。ここで、走査線3aの真下に位置しているため、不純物イオンが導入されなかった部分は半導体膜1のままのチャネル形成用領域1a'となる。40

【0085】

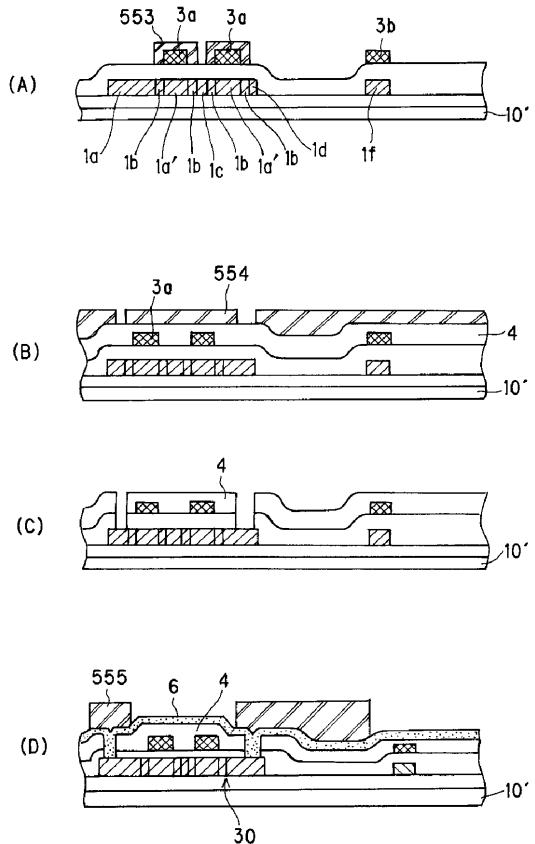

次に、図7(A)に示すように、画素TFT部では、走査線3a(ゲート電極)より幅の広いレジストマスク553を形成して高濃度の不純物イオン(リンイオン)を約 $0.1 \times 10^{15} / \text{cm}^2$ ～約 $10 \times 10^{15} / \text{cm}^2$ のドーズ量で打ち込み、高濃度ソース領域1a、高濃度領域1c及び高濃度ドレイン領域1dを形成する。

【0086】

これらの不純物導入工程に代えて、低濃度の不純物の打ち込みを行わずにゲート電極より幅の広いレジストマスクを形成した状態で高濃度の不純物(リンイオン)を打ち込み、オフセット構造のソース領域及びドレイン領域を形成してもよい。また、走査線3aをマス50

クにして高濃度の不純物を打ち込んで、セルファーライン構造のソース領域及びドレイン領域を形成してもよい。

【0087】

なお、図示を省略するが、このような工程によって、周辺駆動回路部のNチャネルTFT部を形成するが、この際には、PチャネルTFT部をマスクで覆っておく。また、周辺駆動回路のPチャネルTFT部を形成する際には、画素部及びNチャネルTFT部をレジストで被覆保護して、ゲート電極をマスクとして、約 $0.1 \times 10^{15} / \text{cm}^2$ ～約 $10 \times 10^{15} / \text{cm}^2$ のドーズ量でボロンイオンを打ち込むことにより、自己整合的にPチャネルのソース・ドレイン領域を形成する。

【0088】

この際、NチャネルTFT部の形成時と同様、ゲート電極をマスクとして、約 $0.1 \times 10^{13} / \text{cm}^2$ ～約 $10 \times 10^{13} / \text{cm}^2$ のドーズ量で低濃度の不純物（ボロンイオン）を導入して、ポリシリコン膜に低濃度領域を形成した後、ゲート電極より幅の広いマスクを形成して高濃度の不純物（ボロンイオン）を約 $0.1 \times 10^{15} / \text{cm}^2$ ～約 $10 \times 10^{15} / \text{cm}^2$ のドーズ量で打ち込んで、LDD構造のソース領域及びドレイン領域を形成してもよい。また、低濃度の不純物の打ち込みを行わずに、ゲート電極より幅の広いマスクを形成した状態で高濃度の不純物（ボロンイオン）を打ち込み、オフセット構造のソース領域及びドレイン領域を形成してもよい。これらのイオン打ち込み工程によって、CMOS化（相補型化：Complementary MOS化）が可能になり、周辺駆動回路の同一基板内への内蔵が可能になる。

【0089】

次に、図7（B）に示すように、走査線3aの表面側にCVD法等により、シリコン酸化膜等からなる層間絶縁膜4を300nm～800nmの厚さに形成する。このときの原料ガスは、例えば、TEOSと酸素ガスとの混合ガスを用いることができる。

【0090】

次に、フォトリソグラフィ技術を用いてレジストマスク554を形成する。

【0091】

次に、レジストマスク554を介して層間絶縁膜4にドライエッチングを行い、図7（C）に示すように、層間絶縁膜4においてソース領域及びドレイン領域に対応する部分等にコンタクト孔をそれぞれ形成する。

【0092】

次に、図7（D）に示すように、層間絶縁膜4の表面側に、データ線6a（ソース電極）等を構成するためのアルミニウム膜、チタン膜、窒化チタン膜、タンタル膜、モリブデン膜、又はこれらの金属のいずれかを主成分とする合金膜又は積層膜からなる金属膜6をスパッタ法等で400nm～800nmの厚さに形成した後、フォトリソグラフィ技術を用いてレジストマスク555を形成する。

【0093】

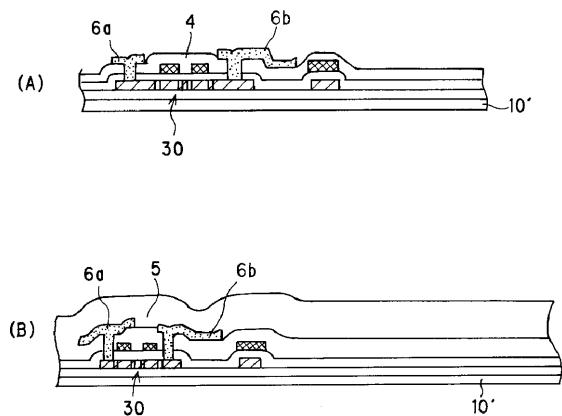

次に、レジストマスク555を介して金属膜6にドライエッチングを行い、図8（A）に示すように、データ線6a、及びソース線6bを形成する。

【0094】

次に、図8（B）に示すように、シリコン窒化膜からなる第2層間絶縁膜5を、データ線6a、及びソース線6bの表面側にCVD法等により、100nm～800nmの膜厚に形成する。

【0095】

次に、図9（A）、（B）に示すように、アクリル樹脂等の有機系の透光性の感光性樹脂13aを1～3μmの厚さにスピンコートで塗布した後、感光性樹脂13aをフォトリソグラフィ技術を用いてパターニングすることによって、厚さが1μm～3μmの凹凸形成層13を形成する。次いで、角をとるためベーク工程を行ってもよい。

【0096】

このようなフォトリソグラフィ技術を利用して凹凸形成層13を形成する際、透光性の感

10

20

30

40

50

光性樹脂 13 a としてはネガタイプ及びポジタイプのいずれを用いてもよいが、図 9 (A) には、感光性樹脂 13 a としてポジタイプを用いた場合を例示してあり、感光性樹脂 13 a を除去したい部分に対して、所定の露光マスクの透光部分を介して紫外線を照射する。

【0097】

次に、図 9 (C) に示すように、透明電極 8 及び凹凸形成層 13 の表面側に、アクリル樹脂等の有機系の透光性の感光性樹脂 7 a をスピンコートで 1 μm ~ 2 μm の厚さに塗布する。

【0098】

次に、図 9 (D) に示すように、フォトリソグラフィ技術を利用して、感光性樹脂 7 a (図 9 (C) 参照) をソース線 6 b の表面に達するまで貫通、開口させて、後述するコンタクト孔 15 を形成することができるよう開口 14 b を形成するとともに、この開口 14 b を備えた厚さが 1 μm ~ 2 μm の凹凸層 7 を形成する。

【0099】

ここで、凹凸層 7 は、流動性を有する材料を塗布したものから形成されるため、凹凸層 7 の表面には、凹凸形成層 13 の凹凸を適度に打ち消して、エッジ等のない、滑らかな形状の凹凸パターンが形成される。

【0100】

なお、凹凸層 7 を形成せずに、滑らかな形状の凹凸パターンを形成する場合には、図 9 (B) に示す状態でベーク工程を行って、凹凸形成層 13 の縁を滑らかな形状にしてもよい。

【0101】

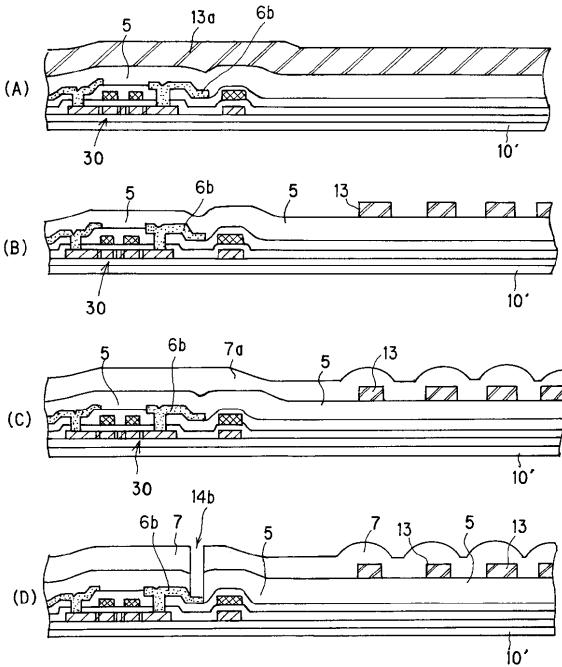

次に、図 10 (A) に示すように、凹凸層 7 及びコンタクト孔 15 の表面に、スパッタリング法等によって、約 50 ~ 200 nm の厚さの ITO からなる透明導電膜を成膜し、フォトリソグラフィ技術及びエッチング技術を用いて、所定のパターンの透明電極 8 を形成する。透明電極 8 の表面に、アルミニウムや銀、もしくはこれらの合金、又はチタン、窒化チタン、モリブデン、タンタル等との積層膜のような反射性を備えた金属膜 9 a を形成する。

【0102】

次に、図 10 (B) に示すように、フォトリソグラフィ技術及びエッチング技術を用いて、透過窓 14 となる部分及び隣接する画素との間を選択的に除去して、透過窓 14 を備えた反射電極 9 を形成する。このようにして形成した反射電極 9 は、透明電極 8 を介してドレイン電極 6 b と電気的に接続している。また、反射電極 9 の表面には、凹凸形成層 13 及び凹凸層 7 からなる凹凸によって 500 nm 以上、さらには 800 nm 以上の凹凸パターン 9 g が形成され、かつ、この凹凸パターン 9 g は、凹凸層 7 によって、エッジ等のない、滑らかな形状になっている。

【0103】

その後、反射電極 9 と、透過窓 14 の形成によって最上層となった透明電極 8 との表面側に配向膜 (ポリイミド膜) 12 を形成する。それには、ブチルセロソルブや n - メチルビロリドン等の溶媒に 5 ~ 10 重量 % のポリイミドやポリアミド酸を溶解させたポリイミド・ワニスをフレキソ印刷した後、加熱・硬化 (焼成) する。そして、ポリイミド膜を形成した基板をレーヨン系纖維からなるパフ布で一定方向に擦り、ポリイミド分子を表面近傍で一定方向に配列させる (ラビング処理を施す)。その結果、後で充填した液晶分子とポリイミド分子との相互作用により液晶分子が一定方向に配列する。

【0104】

以上のようにして、TFT アレイ基板 10 が完成する。

【0105】

上記のいずれの形態も、画素スイッチング素子として TFT を用いたアクティブマトリクス型の液晶表示装置を例に説明したが、画素スイッチング素子として TFD を用いたアクティブマトリクス型の液晶表示装置、又はパッシブマトリクス型の液晶表示装置、さらに

10

20

30

40

50

は液晶以外の電気光学物質（例えば、EL発光素子）を用いた電気光学装置に本発明を適用してもよい。

【0106】

【電気光学装置の電子機器への応用】

このように構成した半反射・半透過型の電気光学装置100は、各種の電子機器の表示部として用いることができるが、その一例を、図11～図13を参照しつつ具体的に説明する。

【0107】

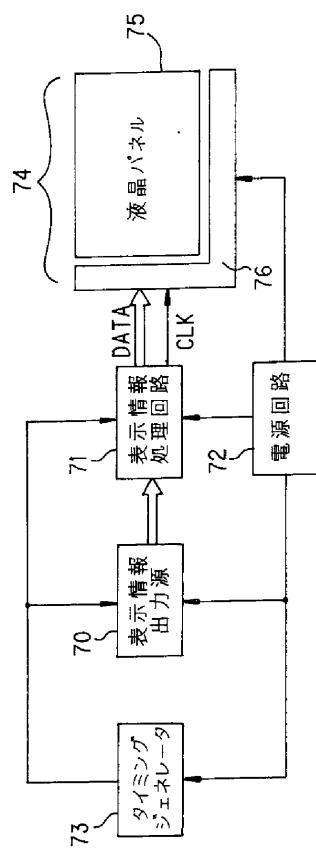

図11は、本発明に係る電気光学装置を表示装置として用いた電子機器の回路構成を示すブロック図である。

10

【0108】

図11において、電子機器は、表示情報出力源70、表示情報処理回路71、電源回路72、タイミングジェネレータ73及び液晶表示装置74を有する。また、液晶表示装置74は、液晶表示パネル75及び駆動回路76を有する。液晶装置74としては、前述した電気光学装置100を用いることができる。

【0109】

表示情報出力源70は、ROM(Read Only Memory)、RAM(Random Access Memory)等のようなメモリ、各種ディスク等のようなストレージユニット、デジタル画像信号を同調出力する同調回路等を備え、タイミングジェネレータ73によって生成された各種のクロック信号に基づいて、所定フォーマットの画像信号等のような表示情報を表示情報処理回路71に供給する。

20

【0110】

表示情報処理回路71は、シリアル-パラレル変換回路や、増幅・反転回路、ローテーション回路、ガンマ補正回路、クランプ回路等のような周知の各種回路を備え、入力した表示情報の処理を実行して、その画像信号をクロック信号CLKとともに駆動回路76へ供給する。電源回路72は、各構成要素に所定の電圧を供給する。

【0111】

図12は、本発明に係る電子機器の一実施形態であるモバイル型のパーソナルコンピュータを示している。ここに示すパーソナルコンピュータ80は、キーボード81を備えた本体部82と、液晶表示ユニット83とを有する。液晶表示ユニット83は、前述した電気光学装置100を含んで構成される。

30

【0112】

図13は、他の電子機器である携帯電話機を示している。ここに示す携帯電話機90は、複数の操作ボタン91と、前述した電気光学装置100からなる表示部とを有している。

【0113】

【発明の効果】

以上、説明したように、本発明によって、携帯電話機、モバイルコンピュータ等に好適に用いられる、透過窓の部分にも配向処理が十分に施された、画素内の透過モード表示におけるコントラストに優れるとともに、反射特性にも優れた電気光学装置及びその製造方法を提供することができる。

40

【図面の簡単な説明】

【図1】本発明の電気光学装置の一の実施の形態を対向基板の側から見たときの平面図である。

【図2】図1のH-H'線における断面図である。

【図3】本発明の電気光学装置の一の実施の形態において、マトリクス状に配置された複数の画素に形成された各種素子、配線等の等価回路図である。

【図4】本発明の電気光学装置の一の実施の形態において、TFTアレイ基板に形成された各画素の構成を示す平面図である。

【図5】図4のA-A'線における画素の断面図である。

【図6】本発明の電気光学装置の製造方法の一の実施の形態において、TFTアレイ基板

50

の製造方法を工程順に示す断面図である。

【図 7】図 6 に示す工程以降の TFT アレイ基板の製造方法を工程順に示す断面図である。

【図 8】図 7 に示す工程以降の TFT アレイ基板の製造方法を工程順に示す断面図である。

【図 9】図 8 に示す工程以降の TFT アレイ基板の製造方法を工程順に示す断面図である。

【図 10】図 9 に示す工程以降の TFT アレイ基板の製造方法を工程順に示す断面図である。

【図 11】本発明に係る電気光学装置を表示装置として用いた電子機器の回路構成を示すブロック図である。 10

【図 12】本発明の電気光学装置を用いた電子機器の一例としてのモバイル型のパーソナルコンピュータを示す説明図である。

【図 13】本発明の電気光学装置を用いた電子機器の他の例としての携帯電話機の説明図である。

【図 14】従来の電気光学装置における画素の一部を模式的に示す説明図であって、( A ) は平面図、( B ) は ( A ) の C - C ' における断面図である。

【符号の説明】

1 ... 半導体膜

1 a ... 高濃度ソース領域

20

1 a ' ... チャネル形成用領域

1 b ... 低濃度領域

1 c ... 高濃度領域

1 d ... 高濃度ドレイン領域

1 f ... 半導体膜の延設部分

2 ... ゲート絶縁膜

3 a ... 走査線

3 b ... 容量線

4 ... 第 1 層間絶縁膜

5 ... 第 2 層間絶縁膜 ( 表面保護膜 )

30

6 ... 金属膜

6 a ... データ線

6 b ... ソース線

7 ... 凹凸層

7 a ... 凹凸層を形成するための感光性樹脂

8 ... 透明電極

9 ... 反射電極

9 a ... 金属膜

9 g ... 凹凸パターン ( 表面凹凸形状 )

10 ... TFT アレイ基板

40

10 ' ... TFT アレイ基板側のガラス基板

11 ... 下地保護膜

12 ... 配向膜

13 ... 凹凸形成層

13 a ... 凹凸形成層を形成するための感光性樹脂

14 ... 透過窓

14 a ... スリット形状の透過窓

14 b ... 凹凸層の開口

15 ... コンタクト孔

20 ... 対向基板

50

|             |                |    |

|-------------|----------------|----|

| 2 0 ' ...   | 対向基板側のガラス基板    |    |

| 2 1 ...     | 対向電極           |    |

| 2 2 ...     | 配向膜            |    |

| 3 0 ...     | 画素スイッチング用の TFT |    |

| 5 0 ...     | 液晶             |    |

| 5 2 ...     | シール材           |    |

| 5 3 ...     | 周辺見切り          |    |

| 6 0 ...     | 蓄積容量           |    |

| 7 0 ...     | 表示情報出力源        | 10 |

| 7 1 ...     | 表示情報処理回路       |    |

| 7 2 ...     | 電源回路           |    |

| 7 3 ...     | タイミングジェネレータ    |    |

| 7 4 ...     | 液晶表示装置         |    |

| 7 5 ...     | 液晶表示パネル        |    |

| 7 6 ...     | 駆動回路           |    |

| 8 0 ...     | パーソナルコンピュータ    |    |

| 8 1 ...     | キーボード          |    |

| 8 2 ...     | 本体部            |    |

| 8 3 ...     | 液晶表示ユニット       |    |

| 9 0 ...     | 携帯電話機          | 20 |

| 9 1 ...     | 操作ボタン          |    |

| 1 0 0 ...   | 電気光学装置         |    |

| 1 0 0 a ... | 画素             |    |

| 1 0 1 ...   | 基板             |    |

| 1 0 2 ...   | 下地保護膜          |    |

| 1 0 3 ...   | 透明電極           |    |

| 1 0 4 ...   | 保護膜            |    |

| 1 0 5 ...   | 凹凸形成層          |    |

| 1 0 6 ...   | 凹凸層            |    |

| 1 0 7 ...   | 透過窓            | 30 |

| 1 0 8 ...   | 反射電極           |    |

| 1 0 9 ...   | 反射用の凹凸         |    |

| 1 1 0 ...   | 画素             |    |

| 1 2 0 ...   | TFTアレイ基板       |    |

| 2 0 1 ...   | データ線駆動回路       |    |

| 2 0 2 ...   | 実装端子           |    |

| 2 0 4 ...   | 走査線駆動回路        |    |

| 2 0 5 ...   | 配線             |    |

| 2 0 6 ...   | 基板間導通材         |    |

【 义 1 】

【 図 2 】

【 四 4 】

【 図 3 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図 10】

【図 11】

【図 12】

【図 13】

【図14】

---

フロントページの続き

| (51)Int.Cl.   |                         | F I           |                      |

|---------------|-------------------------|---------------|----------------------|

| <i>G 09 F</i> | <i>9/30 (2006.01)</i>   | <i>G 09 F</i> | <i>9/30 3 3 8</i>    |

| <i>H 01 L</i> | <i>21/336 (2006.01)</i> | <i>G 09 F</i> | <i>9/30 3 4 9 D</i>  |

| <i>H 01 L</i> | <i>29/786 (2006.01)</i> | <i>H 01 L</i> | <i>29/78 6 1 2 Z</i> |

(56)参考文献 特開2001-075091 (JP, A)

特開2002-202503 (JP, A)

特開2003-050389 (JP, A)

特開2002-357848 (JP, A)

特開2003-015126 (JP, A)

特開2003-057638 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1335

G02F 1/1343

G02F 1/1368