(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6723736号

(P6723736)

(45) 発行日 令和2年7月15日(2020.7.15)

(24) 登録日 令和2年6月26日(2020.6.26)

(51) Int.Cl.

HO4N 5/378 (2011.01)

F 1

HO4N 5/378

請求項の数 13 (全 16 頁)

(21) 出願番号 特願2015-241382 (P2015-241382)

(22) 出願日 平成27年12月10日 (2015.12.10)

(65) 公開番号 特開2017-108317 (P2017-108317A)

(43) 公開日 平成29年6月15日 (2017.6.15)

審査請求日 平成30年12月7日 (2018.12.7)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 小林 秀央

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 山崎 和男

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

最終頁に続く

(54) 【発明の名称】撮像装置、撮像システム、撮像装置の駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

画素信号を各々が出力する複数の画素と、

前記複数の画素の各々から前記画素信号が出力される信号線と、

容量素子と、

信号保持部と、

一方のノードが前記信号線に接続され、他方のノードが前記容量素子と前記信号保持部に接続されたスイッチとを有し、

前記容量素子は、前記スイッチがオンしている場合には、前記信号線に出力されている前記画素信号をサンプリングし、前記スイッチがオンからオフした場合には前記信号線に出力されている前記画素信号を保持する素子であって、

前記複数の画素のうちの第1の画素の前記画素信号が前記信号線に出力され、

前記スイッチをオンすることによって前記容量素子がサンプリングしている前記第1の画素の画素信号に基づく信号が、前記スイッチをオンしたまま、前記信号保持部に保持されることを特徴とする撮像装置。

## 【請求項 2】

前記撮像装置は、第1の動作と第2の動作とで動作し、

前記第1の動作は、前記スイッチをオンしたまま、前記容量素子がサンプリングしている前記第1の画素の画素信号に基づく信号が、前記信号保持部に保持される動作であり、

前記第2の動作は、

前記スイッチがオンからオフすることによって、前記容量素子が前記第1の画素の画素信号を保持し、前記容量素子が保持した前記第1の画素の画素信号に基づく信号を前記信号保持部が保持する動作であることを特徴とする請求項1に記載の撮像装置。

【請求項3】

前記第2の動作において、

前記容量素子が保持した前記第1の画素の画素信号に基づく信号を前記信号保持部が保持する期間であり、前記スイッチがオフしている期間に、前記複数の画素のうちの、前記第1の画素とは別の画素である第2の画素の前記画素信号が前記信号線に出力されることを特徴とする請求項2に記載の撮像装置。

【請求項4】

10

前記複数の画素の各々は、電荷を蓄積する光電変換部と、前記電荷が転送される入力ノードを備える増幅トランジスタとを有し、

前記画素信号は、リセットされた前記入力ノードの電位に基づくノイズ信号と、前記電荷が転送された前記入力ノードの電位に基づく光信号とを含み、

前記第2の動作において、

前記容量素子が保持した前記第1の画素の前記ノイズ信号に基づく信号を前記信号保持部が保持する期間であり、前記スイッチがオフしている期間に、前記第1の画素の前記光信号が前記信号線に出力されることを特徴とする請求項2に記載の撮像装置。

【請求項5】

20

前記撮像装置は、前記容量素子に入力ノードが接続され、出力ノードが前記信号保持部に接続された増幅回路をさらに有し、

前記画素信号に基づく信号が、前記増幅回路によって出力される信号であることを特徴とする請求項1～4のいずれか1項に記載の撮像装置。

【請求項6】

前記撮像装置は、前記信号保持部を備えるA/D変換部を有し、

前記A/D変換部は、前記画素信号に基づく信号をデジタル信号に変換し、

前記信号保持部は前記デジタル信号を保持することを特徴とする請求項1～5のいずれか1項に記載の撮像装置。

【請求項7】

30

前記撮像装置は、前記信号保持部を備えるA/D変換部を有し、

前記A/D変換部は、前記画素信号に基づく信号をデジタル信号に変換し、

前記信号保持部は前記デジタル信号を保持し、

前記第2の動作において、

前記容量素子が保持した前記第1の画素の画素信号に基づく信号を前記A/D変換部がデジタル信号に変換している期間であり、前記スイッチがオフしている期間に、前記複数の画素のうちの、前記第1の画素とは別の画素である第2の画素の前記画素信号が前記信号線に出力されることを特徴とする請求項2に記載の撮像装置。

【請求項8】

40

前記容量素子の一方のノードが、前記スイッチの前記他方のノードに接続され、前記容量素子の他方のノードに、基準電圧が入力されることを特徴とする請求項1～7のいずれか1項に記載の撮像装置。

【請求項9】

請求項1～8のいずれか1項に記載の撮像装置と、

前記撮像装置が出力する信号によって、画像を生成する信号処理部とを有することを特徴とする撮像システム。

【請求項10】

画素信号を各々が output する複数の画素と、

前記複数の画素の各々から前記画素信号が出力される信号線と、

容量素子と、

前記画素信号に基づく信号を保持する信号保持部とを有し、

50

前記容量素子が、前記画素信号のサンプリングと、前記画素信号の保持とが可能な素子である撮像装置の駆動方法であって、

前記複数の画素のうちの第1の画素が前記画素信号を前記信号線に出力し、

前記容量素子が前記第1の画素の画素信号をサンプリングしている期間に、前記第1の画素の画素信号に基づく信号を、前記信号保持部が保持することを特徴とする撮像装置の駆動方法。

#### 【請求項11】

前記撮像装置は第1の動作と第2の動作を行い、

前記第1の動作は、前記容量素子が前記第1の画素の画素信号をサンプリングしている期間に、前記第1の画素の画素信号に基づく信号を、前記信号保持部が保持する動作であり、

前記第2の動作は、前記容量素子が前記第1の画素の画素信号を保持し、前記容量素子が保持した前記第1の画素の画素信号に基づく信号を前記信号保持部が保持する動作であることを特徴とする請求項10に記載の撮像装置の駆動方法。

#### 【請求項12】

前記第2の動作において、

前記容量素子が保持した前記第1の画素の画素信号に基づく信号を前記信号保持部が保持する期間であり、前記容量素子が前記第1の画素の画素信号を保持している期間に、前記複数の画素のうちの、前記第1の画素とは別の画素である第2の画素の前記画素信号が前記信号線に出力されることを特徴とする請求項11に記載の撮像装置の駆動方法。

#### 【請求項13】

前記複数の画素の各々は、電荷を蓄積する光電変換部と、前記電荷が転送される入力ノードを備える増幅トランジスタとを有し、

前記画素信号は、リセットされた前記入力ノードの電位に基づくノイズ信号と、前記電荷が転送された前記入力ノードの電位に基づく光信号とを含み、

前記第2の動作において、

前記容量素子が保持した前記第1の画素の前記ノイズ信号に基づく信号を前記信号保持部が保持する期間であり、前記容量素子が前記第1の画素の前記ノイズ信号を保持している期間に、前記第1の画素の前記光信号が前記信号線に出力されることを特徴とする請求項11に記載の撮像装置の駆動方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、撮像装置、撮像システム、撮像装置の駆動方法に関する。

##### 【背景技術】

##### 【0002】

複数行、複数列に渡って複数の画素が配された撮像装置が知られている。

##### 【0003】

さらに特許文献1のように、画素が出力する信号を保持する信号保持部と、信号保持部に保持された信号をデジタル信号に変換するA/D変換部とを有する撮像装置がある。信号保持部と画素との間の電気的経路にはスイッチが設けられている。このスイッチが導通した後、非導通となることによって、信号保持部は、画素の出力する信号を保持する。

##### 【先行技術文献】

##### 【特許文献】

##### 【0004】

##### 【特許文献1】特開2008-67358号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0005】

特許文献1の撮像装置では、スイッチが導通、非導通の動作を行うことによって生じる

10

20

30

40

50

ノイズが、画素が出力する信号に重畠される。このため、信号保持部が保持する信号に含まれるノイズが増加する課題があった。

【課題を解決するための手段】

【0006】

本発明は上記の課題を鑑みて為されたものであり、一の態様は、画素信号を各々が出力する複数の画素と、前記複数の画素の各々から前記画素信号が出力される信号線と、容量素子と、信号保持部と、一方のノードが前記信号線に接続され、他方のノードが前記容量素子と前記信号保持部に接続されたスイッチとを有し、前記容量素子は、前記スイッチがオンしている場合には、前記信号線に出力されている前記画素信号をサンプリングし、前記スイッチがオンからオフした場合には前記信号線に出力されている前記画素信号を保持する素子であって、前記複数の画素のうちの第1の画素の前記画素信号が前記信号線に出力され、前記スイッチをオンすることによって前記容量素子がサンプリングしている前記第1の画素の画素信号に基づく信号が、前記スイッチをオンしたまま、前記信号保持部に保持されることを特徴とする撮像装置である。

10

【0007】

また、別の一の態様は、画素信号を各々が出力する複数の画素と、前記複数の画素の各々から前記画素信号が出力される信号線と、容量素子と、前記画素信号に基づく信号を保持する信号保持部とを有し、前記容量素子が、前記画素信号のサンプリングと、前記画素信号の保持とが可能な素子である撮像装置の駆動方法であって、前記複数の画素のうちの第1の画素が前記画素信号を前記信号線に出力し、前記容量素子が前記第1の画素の画素信号をサンプリングしている期間に、前記第1の画素の画素信号に基づく信号を、前記信号保持部が保持することを特徴とする撮像装置の駆動方法である。

20

【発明の効果】

【0008】

本発明により、信号保持部が保持する信号のノイズを低減させることができる。

【図面の簡単な説明】

【0009】

【図1】撮像装置の構成の一例を示した図

【図2】撮像装置の動作の一例を示した図

【図3】撮像装置の動作の一例を示した図

30

【図4】撮像装置の動作の一例を示した図

【図5】撮像装置の構成の一例を示した図

【図6】撮像装置の動作の一例を示した図

【図7】撮像装置の構成の一例を示した図

【図8】撮像システムの構成の一例を示した図

【発明を実施するための形態】

【0010】

以下、図面を参照しながら、各実施例を説明する。

【0011】

(実施例1)

40

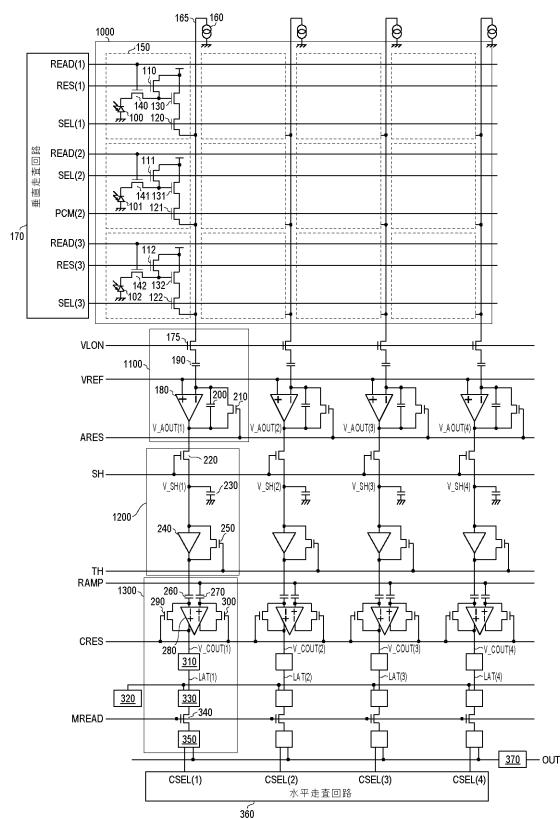

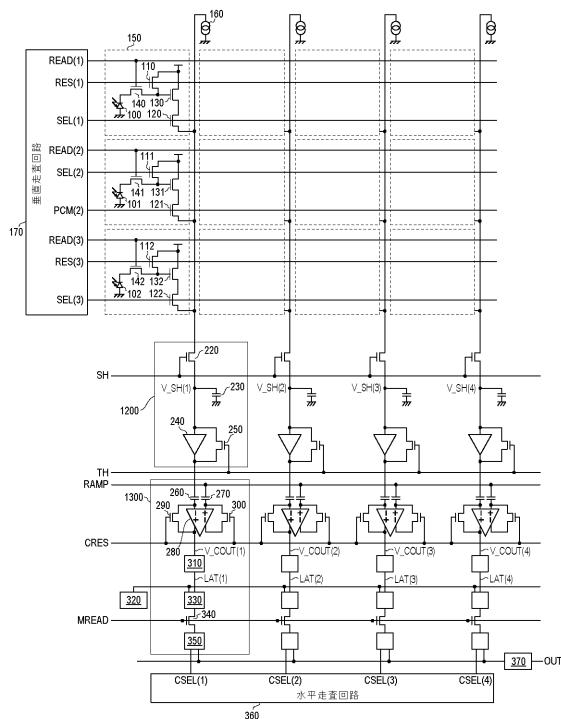

図1は、本実施例の撮像装置の構成を示した図である。撮像装置は、画素アレイ1000、增幅回路1100、サンプルホールド部1200、AD変換部1300を有する。さらに撮像装置は、電流源160、垂直走査回路170、カウンタ320、水平走査回路360を有する。

【0012】

画素アレイ1000は、複数行および複数列に渡って配された画素150を有する。画素150は、フォトダイオード10p、リセットトランジスタ11p、選択トランジスタ12p、増幅トランジスタ13p、転送トランジスタ14pを有する。なお、pには、画素が位置する行の番号から1を引いた数が入る。フォトダイオード10pは、光に基づく電荷を生成する光電変換部である。転送トランジスタ14p、フォトダイオード10pと

50

、増幅トランジスタ 13p の入力ノードに接続されている。また、転送トランジスタ 14p のゲートには、垂直走査回路 170 から信号 R E A D (n) が入力される。なお、(n) は、垂直走査回路 170 が出力する信号について、n 行目の画素 150 に入力されることを示す。リセットトランジスタ 11p は、一方のノードは増幅トランジスタ 13p の入力ノードに接続され、他方のノードは、電源電圧が入力される。リセットトランジスタ 11p のゲートには、垂直走査回路 170 から、信号 R E S (n) が入力される。増幅トランジスタ 13p の一方のノードは、選択トランジスタ 12p に接続され、他方のノードには電源電圧が入力される。選択トランジスタ 12p の一方のノードは増幅トランジスタ 13p に接続され、他方のノードは垂直信号線 165 に接続される。選択トランジスタ 12p のゲートには、垂直走査回路 170 から信号 S E L (n) が入力される。垂直信号線 165 は、電流源 160 と、増幅回路 1100 が有するスイッチ 175 に接続される。信号 P S E L (n) が High となると、選択トランジスタ 12p がオンする。これにより、電流源 160 が供給する電流が、選択トランジスタ 12p を介して、増幅トランジスタ 13p に入力される。増幅トランジスタ 13p は、入力ノードの電位に基づく信号である画素信号を、選択トランジスタ 12p を介して垂直信号線 165 に出力する。増幅トランジスタ 13p は、電源電圧、電流源 160 によってソースフォロワ動作を行う。別の言い方をすれば、電源電圧、電流源 160、増幅トランジスタ 13p は、ソースフォロワ回路を構成する。

#### 【0013】

増幅回路 1100 は、スイッチ 175、容量素子 190、アンプ 180、容量素子 200、スイッチ 210 を有する。スイッチ 175 は、不図示のタイミングジェネレータから入力される信号 V L O N によって制御される。また、スイッチ 210 は、不図示のタイミングジェネレータから入力される信号 A R E S によって制御される。アンプ 180 は、入力される信号を、容量素子 190 の容量値 / 容量素子 200 の容量値で表されるゲインで増幅した信号を、サンプルホールド部 1200 が有するスイッチ 220 に出力する。

#### 【0014】

サンプルホールド部 1200 は、スイッチ 220、容量素子 230、バッファ 240、スイッチ 250 を有する。スイッチ 220 は、不図示のタイミングジェネレータから入力される信号 S H によって制御される。スイッチ 250 は、不図示のタイミングジェネレータから入力される信号 T H によって制御される。容量素子 230 は、スイッチ 220 が導通した後、非導通となることによって、画素 150 が出力する信号に基づく信号を保持する容量素子である。容量素子 230 は、一方のノードがスイッチ 220 に接続されている。また、容量素子 230 の一方のノードは、バッファ 240、容量素子 260、比較器 280、ラッチ 310 を介して、信号保持部である第 1 メモリ 330 に接続されている。容量素子 230 の他方のノードには、基準電圧である、接地電圧が入力される。バッファ 240 は、入力された信号をバッファリングして、A D 変換部 1300 が有する容量素子 260 に出力する。増幅回路 1100 の出力は、出力 V\_A O U T (m) と表す。(m) は、m 列目の増幅回路 1100 であることを示している。

#### 【0015】

A D 変換部 1300 は、容量素子 260、容量素子 270、比較器 280、スイッチ 290、スイッチ 300、ラッチ 310、第 1 メモリ 330、スイッチ 340、第 2 メモリ 350 を有する。

#### 【0016】

比較器 280 の一方の入力ノードは、容量素子 260 に接続されている。比較器 280 の他方の入力ノードは、容量素子 270 を有する。容量素子 270 には、不図示のランプ信号供給部から、ランプ信号 R A M P が入力される。スイッチ 290、スイッチ 300 は、それぞれ、不図示のタイミングジェネレータから出力される信号 C R E S によって制御される。ラッチ 310 には、比較器 280 の出力 V\_C O U N T (m) が入力される。(m) は、m 列目の比較器 280 が出力する信号であることを示している。ラッチ 310 は、比較器 280 の出力 V\_C O U N T (m) を受けて、L A T (m) を第 1 メモリ 330 に

出力する。

【0017】

カウンタ320は、クロック信号を計数することによってカウント信号を生成する。第1メモリ330には、カウンタ320が出力するカウント信号が入力される。

【0018】

スイッチ340は不図示のタイミングジェネレータから入力される信号M R E A Dによって制御される。スイッチ340がオンすると、第2メモリ350は、第1メモリが保持した信号を保持する。

【0019】

水平走査回路360は、各列の第2メモリ350を順次走査することによって、各列の第2メモリ350から、当該第2メモリ350が保持した信号を出力部370に読み出す。

【0020】

出力部370は、第2メモリ350から出力された信号を、撮像装置の外部に出力する。

【0021】

次に、図1の撮像装置の構成を用いた、比較例の動作を説明する。

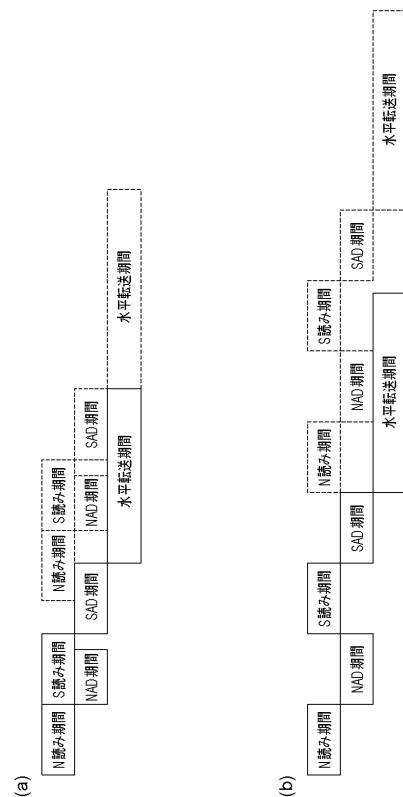

【0022】

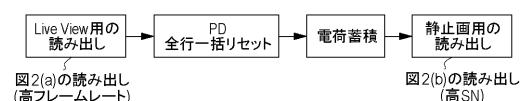

図2(a)は、比較例の動作を示した図である。図2(a)に示した動作では、N A D期間とS読み期間とが重なっている。また、S A D期間と次行の画素150のN読み期間とが重なっている。

【0023】

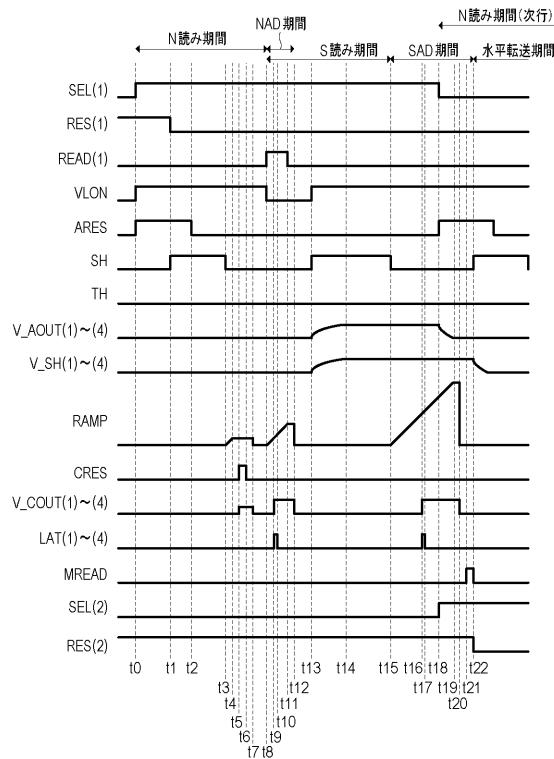

図2(a)に示した動作の詳細の動作を図3に示す。

【0024】

図3に示す時刻t0から時刻t8までの期間が、図2(a)に示したN読み期間である。

【0025】

図3の時刻t0に、垂直走査回路170は、信号S E L(1)をH i g hにする。これにより、1行目の画素150から信号が垂直信号線165に出力される。

【0026】

図3の時刻t1に、垂直走査回路170は、信号R E S(1)をH i g hからL o wにする。これにより、増幅トランジスタ13pの入力ノードは、リセット後の電位となっている。これにより、1行目の画素150の増幅トランジスタ130は、リセットされた入力ノードの電位に基づく信号を、垂直信号線165に出力する。この信号をN信号と表記する。N信号は、画素150が出力する画素信号の1つであり、画素150が出力するノイズ信号である。

【0027】

画素150がN信号を出力している期間である時刻t2に、不図示のタイミングジェネレータは、信号A R E SをH i g hからL o wに遷移させる。これにより、容量素子190には、N信号がクランプされる。

【0028】

時刻t2から、増幅回路1100は、オフセットレベルの信号であるO F F S E T信号を出力する。この信号をオフセット信号と表記する。このO F F S E T信号は、画素信号の一つであるノイズ信号に基づく信号である。不図示のタイミングジェネレータが、信号S HをH i g hとしているので、容量素子230はO F F S E T信号をサンプリングする。

【0029】

その後、時刻t3に、不図示のタイミングジェネレータは、信号S HをL o wにする。これにより、容量素子230は、O F F S E T信号を保持する。

【0030】

10

20

30

40

50

バッファ240には、容量素子230が保持したOFFSET信号が入力される。バッファ240は、このOFFSET信号をバッファリングした信号を、容量素子260を介して比較器280に出力する。

【0031】

この時、ランプ信号RAMPの電位は、ランプ開始電位に設定されている。

【0032】

その後、時刻t3から時刻t4に、ランプ信号供給部はランプ信号RAMPの電位をオフセットさせる。

【0033】

時刻t6に、不図示のタイミングジェネレータは、信号CRESをHighからLowに変化させる。容量素子260は、OFFSET信号をクランプする。また、容量素子270は、ランプ信号RAMPのオフセットされた電位をクランプする。 10

【0034】

N読み期間は、画素150がN信号の出力を開始してから、後述する、ランプ信号RAMPが電位の変化を開始するまでの期間である。

【0035】

次に、NAD期間を説明する。

【0036】

時刻t8では、不図示のランプ信号供給部は、ランプ信号RAMPの電位を、ランプ開始電位に設定している。そして、時刻t8に、ランプ信号供給部は、ランプ信号RAMPの電位の変化を開始する。 20

【0037】

また、カウンタ320は、ランプ信号RAMPの電位の変化の開始に対応して、クロック信号の係数を開始する。これにより、カウント信号のカウントアップが開始される。

【0038】

比較器280は、反転入力ノードと非反転入力ノードとの電位を比較した結果を示す信号V\_COUP(m)を出力する。 30

【0039】

時刻t9に、比較器280の反転入力ノードと非反転入力ノードとの電位の大小関係が逆転すると、信号V\_COUP(m)の信号値が変化する。

【0040】

ラッチ310は、信号V\_COUP(m)の信号値が変化すると、信号LAT(m)をHighにした後、Lowとする。

【0041】

第1メモリ330は、信号LAT(m)がHighからLowとなったタイミングのカウント信号を保持する。このカウント信号は、比較器280のノイズ成分に基づくデジタル信号である。このデジタル信号をデジタルN信号と表記する。このデジタルN信号は、比較器280の列ごとのばらつきの成分を主に含む信号である。

【0042】

その後、時刻t11に、不図示のランプ信号供給部は、ランプ信号RAMPの電位の変化を終了する。また、カウンタ320は、クロック信号の係数を終了する。これにより、カウント信号のカウントアップが終了する。 40

【0043】

NAD期間は、ランプ信号RAMPの電位の変化が開始してから、ランプ信号RAMPの電位の変化が終了するまでの期間である。

【0044】

その後、タイミングジェネレータは、信号READをHighにする。これにより、第1メモリ330が保持したデジタルN信号を、第2メモリ350が保持する。これにより、第1メモリ330の、次のカウント信号の取り込みが可能となる。

【0045】

10

20

30

40

50

図2(a)の比較例の動作では、NAD期間の少なくとも一部の期間が、S読み期間の一部の期間と重なっている。説明する例では、NAD期間の全ての期間が、S読み期間の一部の期間と重なっている。

【0046】

S読み期間を説明する。

【0047】

時刻t7に、垂直走査回路170が、信号PTX(1)をHighとする。これにより、フォトダイオード100が蓄積した電荷が、増幅トランジスタ130に転送される。増幅トランジスタ130は、フォトダイオード100が蓄積した電荷に基づく信号を垂直信号線165に出力する。この信号にはN信号が含まれている。この信号を、S+N信号と表記する。S+N信号は、画素150が出力する画素信号の1つである。また、S+N信号は、画素150が出力する、電荷に基づく光信号である。

10

【0048】

時刻t13に、不図示のタイミングジェネレータは、信号VLONGをHighとする。容量素子190は、N信号をクランプしたままとなっている。よって、アンプ180の入力ノードには、S+N信号からN信号を差し引いたS信号が入力される。

【0049】

アンプ180は、S信号に基づく信号を出力する。この信号にはS信号を増幅した信号と、アンプ180のOFFSET信号とが含まれる。このS信号に基づく信号を、増幅S+OFFSET信号と表記する。

20

【0050】

時刻t13に、不図示のタイミングジェネレータは、信号SHをHighにする。これにより、容量素子230は、増幅S+OFFSET信号をサンプリングする。その後、時刻t15に、不図示のタイミングジェネレータは、信号SHをLowにする。これにより、容量素子230は、増幅S+OFFSET信号を保持する。

【0051】

S読み期間は、画素150がS+N信号の出力を開始してから、後述する、ランプ信号RAMPが電位の変化を開始するまでの期間である。

【0052】

次に、SAD期間について説明する。この期間は、AD変換部1300が、S信号に基づく信号である増幅S信号をデジタル信号に変換する期間である。

30

【0053】

時刻t15において、容量素子230は、増幅S+OFFSET信号を保持している。

【0054】

バッファ240には、容量素子230が保持した増幅S+OFFSET信号が入力される。バッファ240は、この増幅S+OFFSET信号をバッファリングした信号を、容量素子260を介して比較器280に出力する。

【0055】

容量素子260は、先のNAD期間でクランプしたOFFSET信号を引き続きクランプしている。これにより、比較器280の反転入力ノードには、増幅S+OFFSET信号からOFFSET信号を差し引いた増幅S信号が入力される。

40

【0056】

また、容量素子270は、先のNAD期間でクランプしたランプ信号RAMPの初期電位をクランプしている。

【0057】

時刻t15に、ランプ信号供給部は、ランプ信号RAMPの電位の変化を開始する。

【0058】

また、カウンタ320は、ランプ信号RAMPの電位の変化の開始に対応して、クロック信号の係数を開始する。これにより、カウント信号のカウントアップが開始される。

【0059】

50

比較器 280 は、反転入力ノードと非反転入力ノードとの電位を比較した結果を示す信号 V\_COOUT (m) を出力する。

【0060】

時刻 t16 に比較器 280 の反転入力ノードと非反転入力ノードとの電位の大小関係が逆転すると、信号 V\_COOUT (m) の信号値が変化する。

【0061】

ラッチ 310 は、信号 V\_COOUT (m) の信号値が変化すると、信号 LAT (m) を High にした後、時刻 t17 に Low とする。

【0062】

第 1 メモリ 330 は、信号 LAT (m) が High から Low となったタイミングのカウント信号を保持する。このカウント信号は、増幅 S 信号に基づくデジタル信号である。このデジタル信号をデジタル S 信号と表記する。

【0063】

時刻 t19 に、不図示のランプ信号供給部は、ランプ信号 RAMP の電位の変化を終了する。

【0064】

SAD 期間は、ランプ信号 RAMP の電位の変化が開始してから、ランプ信号 RAMP の電位の変化が終了するまでの期間である。

【0065】

その後、時刻 t21 に、不図示のタイミングジェネレータは、信号 READ を High にする。これにより、第 1 メモリ 330 が保持したデジタル S 信号を、第 2 メモリ 350 が保持する。これにより、第 1 メモリ 330 の、次のカウント信号の取り込みが可能となる。

【0066】

その後、水平走査回路 360 は、各列の第 2 メモリ 350 を順次走査することによって、各列の第 2 メモリ 350 から、デジタル S 信号とデジタル N 信号をそれぞれ、出力部 370 に読み出す。

【0067】

図 2 (a) の比較例の動作では、SAD 期間の一部の期間が、次行の画素 150 の N 読み期間の一部の期間と重なっている。

【0068】

比較例の動作では、容量素子 230 が増幅 S + OFFSET 信号を保持するために、スイッチ 220 をオフする駆動を行っていた。この駆動により、スイッチ 220 がオンからオフすることによるスイッチングノイズが増幅 S + OFFSET 信号に重畠される課題があった。

【0069】

図 2 (b) は、本実施例の駆動を示した図である。

【0070】

図 2 (a) の比較例と異なる点は、NAD 期間と S 読み期間とを重ねていない点である。さらに、異なる点として、SAD 期間と N 読み期間とを重ねていない点もある。

【0071】

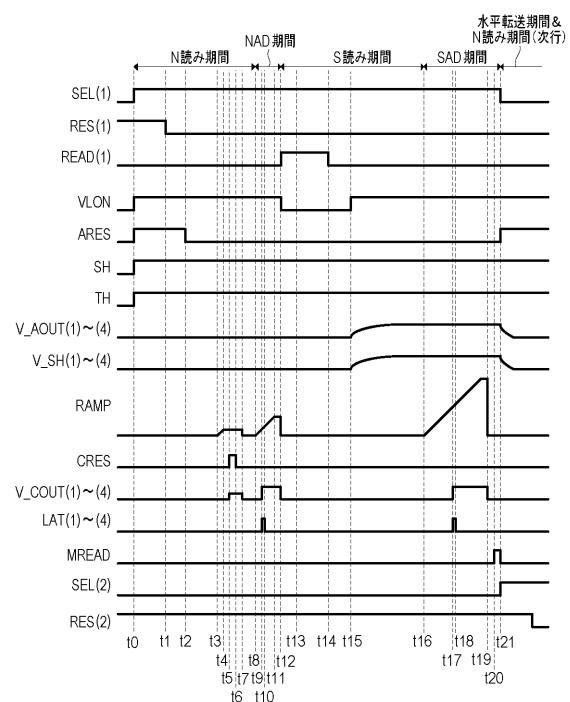

本実施例の N 読み期間について、比較例の N 読み期間とは異なる駆動を説明する。

【0072】

図 4 は、図 2 (b) に示した本実施例の駆動の詳細を示した図である。

【0073】

比較例の N 読み期間では、不図示のタイミングジェネレータが、信号 SH を High から Low にすることによって、容量素子 230 が OFFSET 信号を保持していた。本実施例では、不図示のタイミングジェネレータは、信号 SH を、時刻 t0 から High のままでする。これにより、アンプ 180 がオフセット信号の出力を開始してから NAD 期間の終了まで、アンプ 180 からバッファ 240 を介して比較器 280 に OFFSET 信号

10

20

30

40

50

が入力され続ける。この期間、容量素子 230 は、OFFSET 信号をサンプリングしたままとなる。この容量素子 230 がオフセット信号をサンプリングしている間に、第 1 メモリ 330 は、OFFSET 信号に基づくデジタル信号を保持する。その他の動作については、比較例で述べた N 読み期間の動作と同じである。

【0074】

本実施例の NAD 期間の動作は、比較例の NAD 期間の動作と同じである。

【0075】

本実施例では、NAD 期間が終了してから、S 読み期間が開始される。

【0076】

本実施例の S 読み期間について、比較例の S 読み期間と異なる動作を説明する。比較例の S 読み期間では、不図示のタイミングジェネレータが、信号 SH を High から Low にすることによって、容量素子 230 が増幅 S + OFFSET 信号を保持していた。本実施例では信号 SH は、時刻 t0 から引き続き High のままでする。これにより、アンプ 180 が増幅 S + OFFSET 信号の出力を開始してから SAD 期間の終了まで、アンプ 180 からバッファ 240 を介して比較器 280 に増幅 S + OFFSET 信号が入力され続ける。この期間、容量素子 230 は、増幅 S + OFFSET 信号をサンプリングしたままとなる。この容量素子 230 が増幅 S + OFFSET 信号をサンプリングしている期間に、第 1 メモリ 330 は、増幅 S + OFFSET 信号に基づくデジタル信号を保持する。その他の動作については、比較例で述べた S 読み期間の動作と同じである。

【0077】

SAD 期間の動作は、比較例の SAD 期間の動作と同じである。

【0078】

本実施例では、SAD 期間が終了してから、次行の画素 150 の N 読み期間が開始される。

【0079】

本実施例の動作では、増幅 S + OFFSET 信号の出力を開始してから、SAD 期間が終了するまでの期間、信号保持容量である容量素子 230 に信号を保持させるためのスイッチ 220 をオンのままでする。よって、容量素子 230 は、増幅 S + OFFSET 信号をサンプリングしたままとなる。容量素子 230 が第 1 の画素の S 信号に基づく増幅 S + OFFSET 信号をサンプリングしている期間、第 1 メモリ 330 は、第 1 の画素の S 信号に基づく増幅 S 信号に対応するデジタル信号を保持する。これにより、スイッチ 220 のスイッチングによって生じるノイズが、増幅 S + OFFSET 信号には含まれにくくなる。

【0080】

よって、本実施例の撮像装置では、画素 150 が output する S 信号に基づく信号の S/N (Signal / Noise) 比を向上させることができる。

【0081】

また、オフセット信号の出力を開始してから、NAD 期間が終了するまでの期間、信号保持容量である容量素子 230 に信号を保持させるためのスイッチ 220 をオンのままでする。よって、容量素子 230 は、OFFSET 信号をサンプリングしたままとなる。容量素子 230 が第 1 の画素の N 信号に基づく OFFSET 信号をサンプリングしている期間、第 1 メモリ 330 は、第 1 の画素の N 信号に基づく OFFSET 信号に対応するデジタル信号を保持する。これにより、スイッチ 220 のスイッチングによって生じるノイズが、OFFSET 信号に含まれにくくなる。

【0082】

よって、本実施例の撮像装置では、画素 150 が output する N 信号に基づく信号に含まれるノイズを低減することができる。

【0083】

なお、本実施例では、NAD 期間に先立って、容量素子 260、容量素子 270 がクランプ動作を行う例を説明したが、この動作は必須ではない。本実施例の AD 変換部 130

10

20

30

40

50

0は、容量素子260、容量素子270を有しないようにすることもできる。この場合には、デジタルN信号およびデジタルS信号は、增幅回路1100のOFFSET信号の成分も含むこととなる。この場合であっても、デジタルS信号からデジタルN信号を差し引くことにより、增幅回路1100のオフセット信号の成分を差し引くことができる。

【0084】

なお、本実施例では、ランプ信号の電位の変化の開始から、ランプ信号とアナログ信号との大小関係が逆転するまでの時間を計測することによるA/D変換を説明した。本実施例は、このA/D変換形式に限定されるものではなく、逐次比較型、デルタシグマ型、パイプライン型など、他のA/D変換形式においても適用することができる。

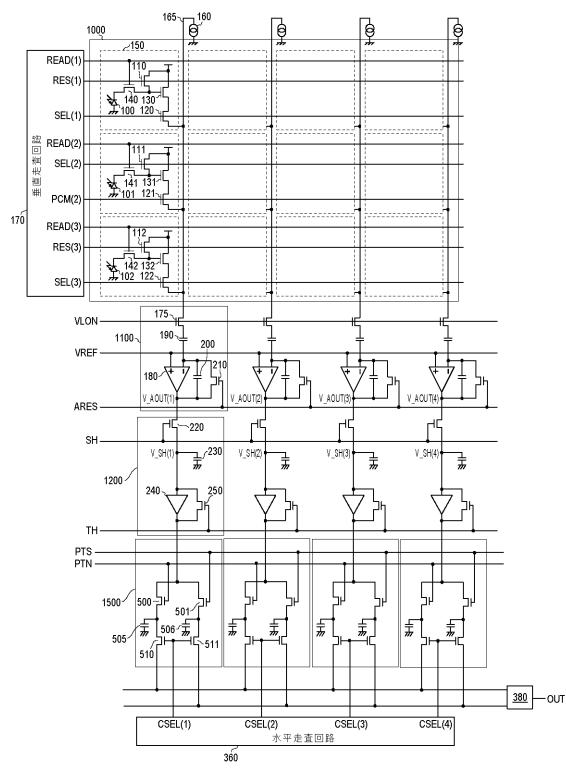

【0085】

なお、本実施例では、各列に增幅回路1100が備えられた例を説明した。他の例を、図5を参照しながら説明する。

【0086】

図5に示した各信号は、図4のタイミング図に示した信号に対応する。つまり、図5の撮像装置においても、N読み期間、NAD期間、S読み期間、SAD期間に渡って、信号SHはHighのままである。

【0087】

図5の撮像装置は、図1に示した撮像装置に対して增幅回路1100を省いた構成を備える。画素150が出力するN信号、S+N信号のそれぞれは、サンプルホールド部1200に出力される。バッファ240は、画素150から出力されたN信号、S+N信号をそれぞれバッファリングした信号を、A/D変換部1300に出力する。容量素子260は、N信号をクランプする。これにより、比較器280の反転入力ノードには、S+N信号からN信号を差し引いた信号が入力される。デジタルN信号は、比較器280の列ごとの特性ばらつきを主とする成分を有する。デジタルS信号は、S信号に基づく信号である。

【0088】

この図5の例においても、他のA/D変換形式を適用することができる。また、容量素子260、容量素子270を省略することができる。

【0089】

なお、本実施例では、撮像装置がA/D変換部1300を備える例を説明した。この例に限定されるものではない。図7は、他の形態の撮像装置を示した図である。図7の撮像装置は、サンプルホールド部1200の出力ノードに接続された、信号読み出し部1500を有する。信号読み出し部1500は、スイッチ500、スイッチ501、容量素子505、容量素子506、スイッチ510、スイッチ511を有する。スイッチ500、スイッチ501は、不図示のタイミングジェネレータから出力される信号PTS、信号PTNによって制御される。スイッチ510、スイッチ511は、水平走査回路360から出力される信号CSEL(m)によって制御される。容量素子505は、バッファ240が出力するOFFSET信号を保持する。容量素子506は、バッファ240が出力する増幅S+OFFSET信号を保持する。

【0090】

出力部380は、各列の信号読み出し部1500から出力される増幅S+OFFSET信号とOFFSET信号とを差し引いた増幅S信号を、出力OUTとして出力する。

【0091】

このような構成においても、本実施例の駆動を適用することができる。つまり、容量素子230が信号をサンプリングしている期間に、信号保持部である、容量素子505あるいは容量素子506が信号を保持するようにすれば良い。

【0092】

(実施例2)

実施例1では、比較例として図2(a)の駆動を説明した。本実施例の撮像装置は、図2(a)の駆動と、図2(b)の駆動とを切り替えて行う。

【0093】

図6は、本実施例の駆動を示した図である。

【0094】

撮像装置は、Live View用の読み出しと、PDの電荷の全行一括リセットと、電荷蓄積と、静止画用の読み出しとを行う。Live Viewでは、1秒あたり数十フレームの画像が生成される。Live Viewの1フレームは、撮像装置の1回の垂直走査に対応する。この1回の垂直走査とは、1行目の画素150から、最終行の画素150までの信号の読み出しに対応する。

【0095】

Live View用の読み出しへは、静止画用の読み出しに比べて、高フレームレートでの信号の読み出しを行う。Live View用の読み出しへは、図2(a)に示した駆動を行う。

10

【0096】

一方、静止画用の読み出しへは、高いS/N比の信号の読み出しへを行う。よって、静止画用の読み出しへは、図2(b)に示した駆動を行う。

【0097】

このように、撮像装置の高速読み出しへを行う場合には、図2(a)に示した駆動を行う。一方、撮像装置の高S/N比の信号の読み出しへを行う場合には、図2(b)に示した駆動を行う。このように、本実施例の撮像装置は、高速読み出しへ、高S/N比の信号の読み出しへを両立することができる効果を有する。

【0098】

20

(実施例3)

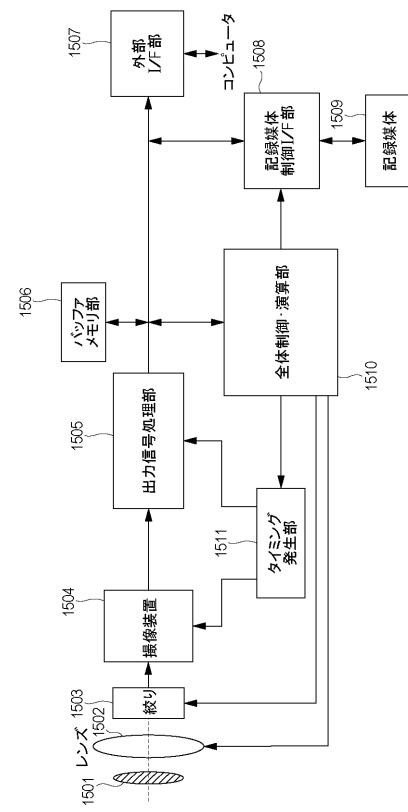

本実施例は、上述した各実施例の撮像装置を有する撮像システムに関する。

【0099】

撮像システムとして、デジタルスチルカメラやデジタルカムコーダーや監視カメラなどがあげられる。図8に、撮像システムの例としてデジタルスチルカメラに撮像装置を適用した場合の模式図を示す。

【0100】

図8に例示した撮像システムは、レンズの保護のためのバリア1501、被写体の光学像を撮像装置1504に結像させるレンズ1502、レンズ1502を通過する光量を可変にするための絞り1503を有する。レンズ1502、絞り1503は撮像装置1504に光を集光する光学系である。また、図8に例示した撮像システムは撮像装置1504より出力される出力信号の処理を行う出力信号処理部1505を有する。出力信号処理部1505は必要に応じて各種の補正、圧縮を行って信号を出力する動作を行う。

30

【0101】

図8に例示した撮像システムはさらに、画像データを一時的に記憶する為のバッファメモリ部1506、外部コンピュータ等と通信する為の外部インターフェース部1507を有する。さらに撮像システムは、撮像データの記録または読み出しへを行う為の半導体メモリ等の着脱可能な記録媒体1509、記録媒体1509に記録または読み出しへを行うための記録媒体制御インターフェース部1508を有する。さらに撮像システムは、各種演算とデジタルスチルカメラ全体を制御する全体制御・演算部1510、撮像装置1504と出力信号処理部1505に各種タイミング信号を出力するタイミング供給部1511を有する。ここで、タイミング信号などは外部から入力されてもよく、撮像システムは少なくとも撮像装置1504と、撮像装置1504から出力された出力信号を処理する出力信号処理部1505とを有すればよい。

40

【0102】

以上のように、本実施例の撮像システムは、撮像装置1504を適用して撮像動作を行うことが可能である。

【0103】

なお、上記実施例は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである

50

。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。また、これまで述べた各実施例を種々組み合わせて実施することができる。

【符号の説明】

【0104】

|      |            |    |

|------|------------|----|

| 100  | フォトダイオード   | 10 |

| 110  | リセットトランジスタ |    |

| 120  | 選択トランジスタ   |    |

| 130  | 増幅トランジスタ   |    |

| 140  | 転送トランジスタ   |    |

| 150  | 画素         |    |

| 160  | 電流源        |    |

| 165  | 垂直信号線      |    |

| 170  | 垂直走査回路     |    |

| 1000 | 画素アレイ      |    |

| 1100 | 増幅回路       |    |

| 1200 | サンプルホールド部  |    |

| 1300 | A/D変換部     |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 落合 慧

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 佐藤 雅紀

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 松永 隆志

(56)参考文献 特開2011-182065(JP,A)

特開2015-032943(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/225-5/378

H04N 9/00-9/11