(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5314891号

(P5314891)

(45) 発行日 平成25年10月16日(2013.10.16)

(24) 登録日 平成25年7月12日(2013.7.12)

(51) Int.Cl.

F 1

H01L 21/20 (2006.01)

H01L 21/20

H01L 21/336 (2006.01)

H01L 29/78 301B

H01L 29/78 (2006.01)

請求項の数 7 (全 9 頁)

(21) 出願番号 特願2007-518341 (P2007-518341)

(86) (22) 出願日 平成17年6月21日 (2005.6.21)

(65) 公表番号 特表2008-504695 (P2008-504695A)

(43) 公表日 平成20年2月14日 (2008.2.14)

(86) 國際出願番号 PCT/US2005/022643

(87) 國際公開番号 WO2006/002410

(87) 國際公開日 平成18年1月5日 (2006.1.5)

審査請求日 平成20年4月24日 (2008.4.24)

(31) 優先権主張番号 10/875,727

(32) 優先日 平成16年6月24日 (2004.6.24)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】 CMOSにおいてキャリア移動度を向上させる方法 (MOSFETデバイスの圧縮SiGe&lt;110&gt;成長および構造)

## (57) 【特許請求の範囲】

## 【請求項1】

キャリアを伝導するための構造であって、

<110>において上面を有するSiまたはSiGeの単結晶基板であって、化学的な処理により当該基板の表面が0.1nmの2乗平均粗さ(RMS)を有する、単結晶基板と、

前記基板の上にSi含有ガスおよびGe含有ガスを用いた急速熱化学的気相堆積(RT CVD)によって形成したSiGeの擬似格子整合層であって、20nm未満の厚さを有し、かつ前記単結晶基板よりも高い22%以上のGe濃度を有し、これによって圧縮性の歪みがかかっている、擬似格子整合層と、を含む構造。

10

## 【請求項2】

前記擬似格子整合層上のゲート誘電体と、前記ゲート誘電体上のゲート電極とを更に含む、請求項1に記載の構造。

## 【請求項3】

前記ゲート誘電体の各側において前記擬似格子整合層に形成されたソースおよびドレイン領域を更に含み、前記ソースおよびドレイン領域間に形成されるチャネルを有する、MOSFETを形成する、請求項2に記載の構造。

## 【請求項4】

前記ゲート電極は、ポリシリコン・ゲート電極、または金属および金属シリサイドのゲート電極からなる、請求項2または3に記載の構造。

20

**【請求項 5】**

前記ゲート誘電体が3.9よりも大きい誘電率を有する、請求項2～4のいずれか1項に記載の構造。

**【請求項 6】**

前記急速熱化学的気相堆積(RT CVD)は、

<110>において上面を有するSiまたはSiGeの単結晶基板を急速化学的気相堆積ツール内に装着するステップと、

前記ツール内の圧力を0.2トール未満に低下させるステップと、

前記ツール内の温度を600まで上昇させるステップと、

Si含有ガスおよびGe含有ガスの双方を導入し、これによって、前記基板の上に、前記基板とは異なるGe濃度を有するSiGeの擬似格子整合層を形成し、これによって前記擬似格子整合層を歪ませるステップと、によりおこなわれる請求項1～5のいずれか1項に記載の構造。10

**【請求項 7】**

前記化学的な処理は、

0.2nm未満の表面粗さを有するSiまたはSiGe基板を選択するステップと、

前記基板を脱イオン化水において23で10PPMオゾンの第1の槽に浸漬するステップと、

前記基板を希薄HF100:1の第2の槽に少なくとも1分間浸漬するステップと、

前記基板を脱イオン化水の第3の槽に少なくとも5分間浸漬するステップと、20

前記基板をHCl酸および脱イオン化水の少なくとも1:100の23の第4の槽に浸漬するステップと、

前記基板を脱イオン化水の第5の槽に少なくとも5分間浸漬するステップと、

前記基板を前記第5の槽から取り出して、窒素を含む雰囲気において少なくとも30の温度で前記基板を乾燥させるステップと、によりおこなわれる請求項1または6に記載の構造。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、特に圧縮歪みSiGe材料に対する高性能相補型金属酸化膜半導体(CMO

S)トランジスタ・デバイス設計および材料プロセスに関する。30

**【背景技術】****【0002】**

CMOSトランジスタ・デバイスが小型化するにつれて、回路性能を向上させる方法がますます重要になっている。これを達成する手法の1つは、チャネル領域においてキャリア移動度を高めること、すなわち、電子およびホールの移動度を高めることである。これは、いくつかの方法によって実行可能である。

**【0003】**

1.シリコン基板上で異なるSi格子寸法を用いて、歪みを得る。一般に、緩和SiGeバッファ上の歪みシリコンまたはSOI上の歪みシリコン(SSDOI)は、高Ge濃度のSiGe合金において、N-FETについて約2倍の電子移動度の向上、およびP-FETについて50%のホール移動度の向上を示している。これは概ね、二軸性引張り歪みのもとにあるシリコンによって得られる。しかしながら、この引張り歪みSiのほとんどは、高い密度の欠陥で構成される。40

**【0004】**

2.Si<110>基板等の異なる表面配向シリコン上にMOSFETを製造すると、P-FETにおいて1.5倍までのホール移動度の向上が示されているが、N-FETからの電子移動度は実質的に劣化する。IEDM2003において、Min Yangによって述べられたハイブリッド配向基板は、Si<110>基板をSi<100>基板と組み合わせ、これによって、Si<110>上にP-FETを形成してホール移動度の向上50

を図り、Si<100>上にN-FETを形成してN-FET性能を維持した。

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0005】**

C MOSにおいて、ホールおよび電子キャリアの双方の向上を得るための解決策が求められている。

**【課題を解決するための手段】**

**【0006】**

本発明は、キャリア移動度が向上した半導体材料を提供する。これは、二軸性圧縮歪みのもとにある<110>表面結晶配向を有するSiGe合金層を含む。二軸性圧縮歪みは、半導体材料の成長中にSiGe合金層の面において誘発される縦方向の圧縮応力および横方向の圧縮応力によって引き起こされる正味(net)応力を表す。10

**【0007】**

SiGe層において二軸性圧縮歪みを形成するには、SiまたはSiGe等、より小さい格子間隔を有するベース層または基板の上に層をエピタキシャル形成すれば良い。ここで、Geの濃度は、上にある圧縮歪み層におけるGeよりも低い。

**【0008】**

SiまたはSiGe層において二軸性引張り歪みを形成するには、SiGe等、より大きい格子間隔を有するベース層または基板の上に層をエピタキシャル形成すれば良い。ここで、Geの濃度は、上にある引張り歪み層におけるGeよりも大きい。20

**【0009】**

本発明の半導体材料は、二軸性圧縮ひずみを有するSiGe合金層の<110>表面配向を含み、N-MOSおよびP-MOS双方の電界効果トランジスタについて移動度の向上が得られる。

**【0010】**

本発明の別の態様は、本発明の半導体材料を形成する方法に関し、本発明の方法は、シリコン-ゲルマニウム合金<110>層を設けるステップを含み、このシリコン-ゲルマニウム合金含有<110>層は二軸性圧縮歪みを有する。

**【0011】**

一実施形態において、<110>表面配向および二軸性圧縮歪みを有するSiGe合金層は、以下のステップを含む方法によって製造される。30

**【0012】**

SiまたはSiGe<110>基板表面を処理するため、DI水(純水)において23で10ppmオゾンの使用、希薄フッ化水素酸100:1の1分間の使用、DI水による5分間の洗浄、DI水において23で1:100の体積比のフッ化水素酸の使用、最後にDI水による5分間の洗浄を行う。次いで、N<sub>2</sub>等の不活性雰囲気において30を超える温度で温め、洗浄および乾燥させる。23

**【0013】**

次に、上述の洗浄プロセスによって処理したSiまたはSiGe<110>基板上でエピタキシャル結晶圧縮歪みSiGe合金層を形成する。シランおよびゲルマン(Germane)ガスを用いて、急速熱化学的気相堆積(RTCVD)システムによって成長させ、温度は600から650の範囲とし、圧力は20トールに等しくする。我々の場合、圧縮歪み22%SiGe合金は厚さを20nm未満とし、100sccmのシラン、40sccmのゲルマン、600の温度、および7トールの圧力を用いて、134秒とした。このSiGe層は、SiまたはSiGe<110>基板上で圧縮歪みまたは擬似格子整合(pseudomorphic)であった。AFMによる表面粗さは0.2nm未満であり、欠陥密度はデバイス品質の範囲内である(5×10<sup>7</sup>欠陥/cm<sup>2</sup>未満)。40

**【0014】**

更に、SiまたはSiGe<110>基板上のエピタキシャル結晶圧縮歪みSiGe合金層は、Applied Material Corporationによって製造された急速熱化学的気相堆積(RT)50

CVD) システム、HTF モデルの Central プラットフォームによって、成長させることができる。このシステムは、6 個のチャンバ、2 個のロードロック、1 個の転送チャンバ、1 個の急速熱アニール ( RTP ) チャンバ、2 個の高温ポリシリコン ( HTP ) チャンバから成る。圧縮歪み SiGe 合金層は、HTP チャンバにおいて、600 から 650 の範囲で成長させる。

#### 【0015】

更に、浅いトレンチ分離を用いて、エピタキシャル結晶圧縮ひずみ SiGe 合金領域上に、CMOS デバイスを形成することができる。

#### 【0016】

更に、浅いトレンチ分離を用いて、エピタキシャル結晶圧縮ひずみ SiGe 合金領域上に、誘電率が 3.9 よりも高い金属酸化物、金属シリケート等の高 K ゲート誘電体を有する CMOS デバイスを形成することができる。 10

#### 【0017】

更に、浅いトレンチ分離を用いて、エピタキシャル圧縮ひずみ SiGe 合金領域上において、ゲート誘電体または高 K 誘電体上に、金属ゲートおよび金属シリケートを有する CMOS デバイスを形成することができる。 15

#### 【0018】

本発明のこれらおよびその他の特徴、目的、および利点は、以下の本発明の詳細な説明を図面と関連付けて読で考察することによって明らかとなろう。

#### 【発明を実施するための最良の形態】

#### 【0019】

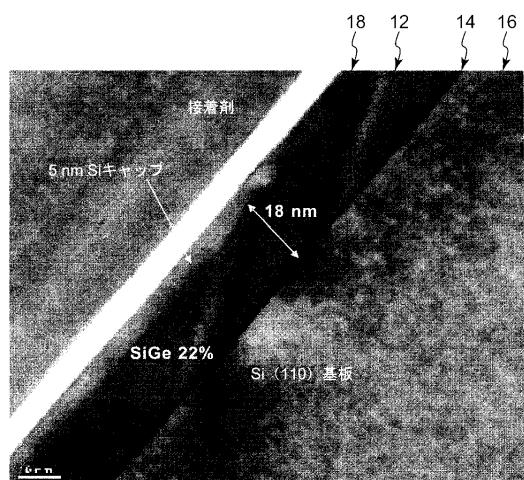

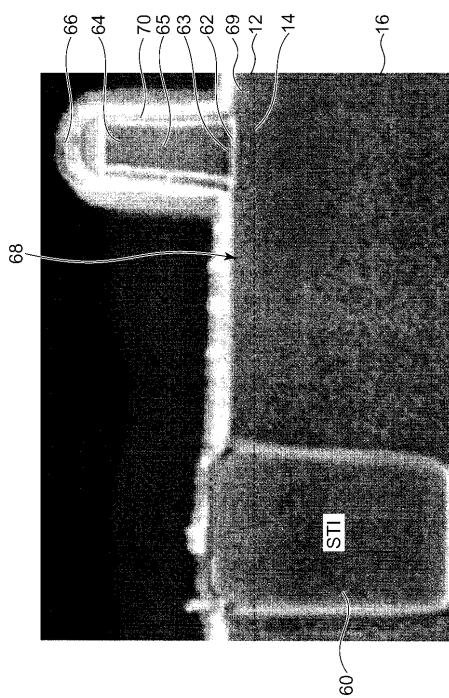

図面、特に図 1 を参照すると、TEM 顕微鏡写真が、単結晶シリコン基板 16 の (110) 表面 14 上の SiGe 合金層 12 を示している。SiGe 合金層 12 における Ge 濃度は 22 % であり、これは、急速熱化学的気相堆積 ( RTCVD ) プロセスによって成長させた。層 12 の厚さは 18 nm である。層 12 の上に、厚さが 5 nm の Si のキャップ層 18 を成長させている。 20

#### 【0020】

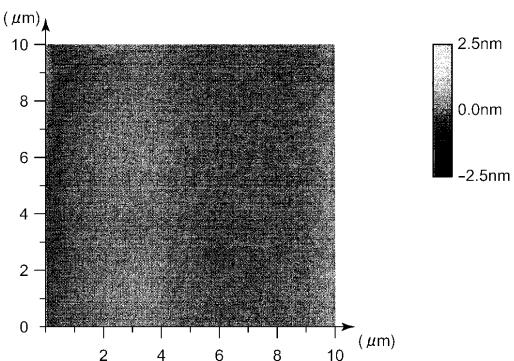

層 12 を堆積する前に、基板 16 の上面 14 を化学的に処理した。図 2 は、化学的処理後の表面 14 の一部の原子間力顕微鏡 ( AFM : Atomic Force Microscope ) 画像を示す。化学的な処理は、0.2 nm 未満の表面粗さを有する Si または SiGe 基板 16 を選択し、基板 16 を脱イオン化水において 23 度 10 PPM オゾンの第 1 の槽に浸漬し、基板 16 を希薄 HF 100 : 1 の第 2 の槽に少なくとも 1 分間浸漬し、基板 16 を脱イオン化水の第 3 の槽に少なくとも 5 分間浸漬し、基板 16 を HCl 酸および脱イオン化水の少なくとも 1 : 100 の約 23 度の第 4 の槽に浸漬し、基板 16 を脱イオン化水の第 5 の槽に少なくとも 5 分間浸漬し、基板 16 を前記第 5 の槽から取り出して、例えば窒素を含む不活性雰囲気において少なくとも 30 度の温度で基板 16 を乾燥することを含む。 RMS による表面粗さは 0.109 nm に等しく、Z 範囲は 1.174 nm に等しかった。これは、最初の Si <110> 表面と同等である。 30

#### 【0021】

SiGe エピタキシャル層 12 を形成することができるが、このためには、<110>において上面を有する Si または SiGe の単結晶基板 16 を選択するステップと、単結晶基板 16 を急速化学的気相堆積ツール内に装着するステップと、ツール内の圧力を 0.2 Torr 未満に低下させるステップと、ツール内の温度を約 600 度まで上昇させるステップと、例えばシランのような Si 含有ガスおよび例えばゲルマンのような Ge 含有ガスの双方を導入し、これによって、基板 16 の上に、前記基板とは異なる Ge 濃度を有する SiGe の擬似格子整合層を形成し、これによって擬似格子整合層 12 を歪ませる、ステップと、を行う。 40

#### 【0022】

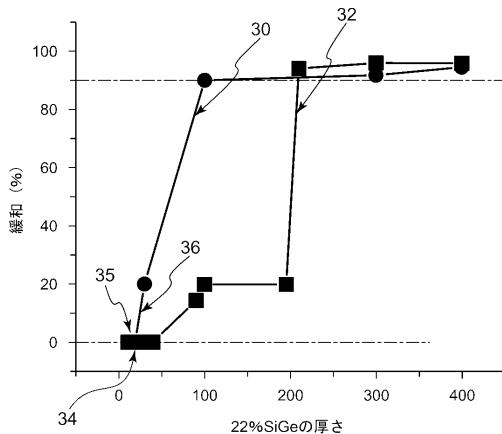

図 3 は、層 12 の RAMAN 分析を、厚さの関数として示す。図 3 において、縦座標は緩和 ( relaxation ) の百分率を表し、横座標は厚さを nm で表す。曲線 30 は曲線部分 3 50

4を有し、ここで層12は擬似格子整合であり、曲線30の点35において、層12の緩和が開始する。曲線部分36は、層12の厚さと共に緩和が急速であることを示す。層12が20nm未満である限り、層12は擬似格子整合であり続ける。擬似格子整合は、表面格子に対してエピタキシャルまたは格子整合あるいは結合している (coherence) またはその両方であることを示す。このため、22%のSiGeの格子間間隔は、Siよりも通常大きく、擬似格子整合であることによって圧縮性の歪みがかかる。<110>についてSiにおける格子間間隔は、xおよびy方向において5.4オングストロームである。Geの格子間間隔は、xおよびy方向において5.6オングストロームであり、Siよりも約4%大きい。SiGeの合金は、SiおよびGeの濃度の線形の関数として格子間間隔を有する。このため、SiGeにおいて22%Ge濃度である結果として、層12が<110>Siについて擬似格子整合である場合、圧縮歪みは約1%になる。圧縮は、<100>Siについて同一である。曲線32は、厚さの関数としてSiGe層<100>の緩和を示す。

#### 【0023】

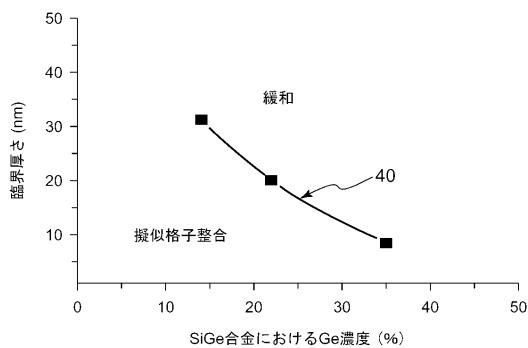

図4の曲線40は、<110>表面配向Si基板上のSiGe合金の臨界(critical)厚さを示す。図4において、縦座標は臨界厚さをnmで表し、横座標はSiGe合金におけるGeの百分率を表す。図4において、曲線40より下の厚さを有するSiGeの層12は擬似格子整合である。

#### 【0024】

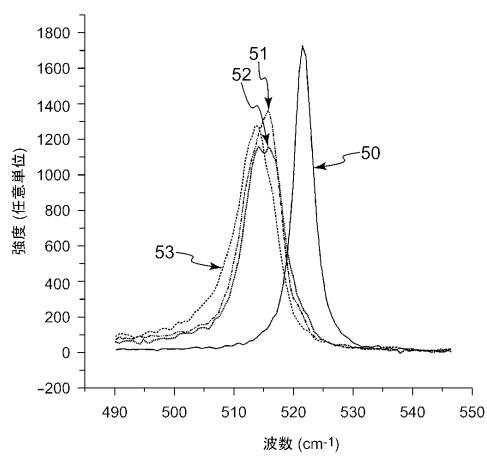

図5の曲線50～53は、MOSFETの製造中のRAMAN分析によるSiGe合金層12の熱安定性を示す。図5において、縦座標は強度を任意単位(a.b.u.)で表し、横座標は波数をcm<sup>-1</sup>(1/cm)で表す。ラムダ(λ)は325nmに等しかった。曲線50は、Si<110>の波数520cm<sup>-1</sup>を示す。曲線51～53は、1000で400秒までの急速熱アニーリング(RTA)による熱サイクルの後の、約514cm<sup>-1</sup>の波数を示す。図5において、曲線51～53は、1000のRTAの間に層12が擬似格子整合のままであったことを示す。RTAの間またはその後に、層12の緩和は観察されなかった。

#### 【0025】

図6は、Si基板16の<110>表面14上の圧縮性歪み22%SiGe合金層12上に形成したMOSFETデバイスの走査顕微鏡画像である。基板16の上面14は、まず化学的に処理した。次いで、基板16上に層12を形成した。次に、基板16に浅いトレンチ分離(STI)領域60を形成して、形成すべきMOSFETの電気的絶縁を設けた。次に、層12の上にゲート誘電体層62を成長させた。ゲート誘電体層62は、約2.5nm厚さのN<sub>2</sub>O酸化物とした。ゲート誘電体層62は、SiGe合金層12まで達する。ゲート誘電体層62の下に、SiGe合金層12上に0.5nm未満のSiのキャップ層18が残されている。これは、N<sub>2</sub>O酸化物がSiGe合金層12に接していることを意味する。次に、ゲート誘電体層62の上にポリシリコン層64を形成した。次に、マスクを形成して反応性イオン・エッチャリング(RIE)によって、層64およびゲート誘電体層62をリソグラフィによってパターニングし、MOSFET66のゲート誘電体63およびゲート電極65を形成した。次に、ゲートのソースおよびドレインに対する自己整合を用いて、イオン注入によってソース68およびドレイン69を形成した。次に、ポリシリコン・ゲート65に隣接して側壁スペーサ70を形成した。

#### 【0026】

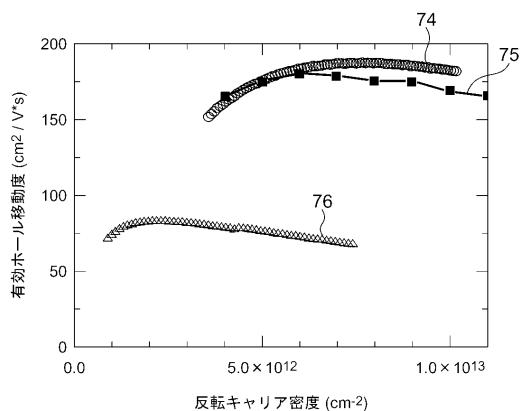

図7は、有効ホール移動度対反転キャリア密度のグラフである。図7において、縦座標は有効ホール移動度をcm<sup>2</sup>/Vsecで表し、横座標は反転キャリア密度を1/cm<sup>2</sup>で表す。曲線74は、層12、図6に示すMOSFET66のチャネルにおける、ホール移動度のプロットである。測定し次いでプロットして曲線74を形成したホール移動度は、曲線75に示すSi<110>のホール移動度よりも約10%高い。曲線75におけるホール移動度は、曲線76においてプロットしたSi<100>のホール移動度よりも約180%高い。

10

20

30

40

50

## 【0027】

これまで説明し例示したのは、

1. Si <110> 基板上に擬似格子整合 SiGe チャネル層を含む MOSFET デバイス、

2. RTCVD によって擬似格子整合 SiGe 層を形成する方法、および、 RTCVD の前にシリコン表面を化学的に処理する方法であるが、当業者には、変更および変形が、添付の特許請求の範囲によってのみ限定される本発明の広範な範囲から逸脱することなく、可能であることは明らかであろう。

## 【図面の簡単な説明】

## 【0028】

10

【図1】(110) 表面配向シリコン基板上の RTCVD 成長 22% SiGe 合金層上の 5 nm Si キャップの TEM 顕微鏡写真を示す。

【図2】Si <110> 表面のための化学的処理(洗浄)シーケンスの後の AFM 画像を示す。

【図3】圧縮歪みまたは擬似格子整合である厚さが 20 nm 未満の(110)表面配向シリコン基板上の SiGe 22% Ge の RAMAN 分析の曲線を示す。

【図4】(110) 表面配向シリコン基板上の SiGe 合金について臨界厚さ曲線を示す。

【図5】RAMAN 分析による(110)表面配向シリコン基板上の 22% SiGe 合金層の熱安定性を示す。

20

【図6】(110) 表面配向シリコン基板上の圧縮歪み 22% SiGe 合金層上に形成した MOSFET を示す。

【図7】ホール移動度対反転電荷のグラフであり、22% SiGe 層 <110> 上のホール移動度が、IEDM、2003において Min Yang によって報告された Si <110> よりも約 10 から 15% 高く、Si 層 <100>、制御層よりも約 180% 高いことを示す。

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

---

フロントページの続き

(72)発明者 チャン、ケヴィン、ケイ

アメリカ合衆国10314 ニューヨーク州スタテン・アイランド スレイトン・アヴェニュー4

1

(72)発明者 グアリニ、キャスリン、ダブリュ

アメリカ合衆国10598 ニューヨーク州ヨークタウン・ハイツ アルデン・ロード290

(72)発明者 ユン、マイケル

アメリカ合衆国12590 ニューヨーク州ワッピンガム・フォールズ サマーリン・コート31

(72)発明者 リム、カーン

アメリカ合衆国10598 ニューヨーク州ヨークタウン・ハイツ ヴァン・コートランド・サー

クル2095

(72)発明者 ヤン、ミン

アメリカ合衆国10598 ニューヨーク州ヨークタウン・ハイツ ゴーマー・ストリート297

0

審査官 太田 一平

(56)参考文献 特開平10-092947(JP,A)

特開2004-014856(JP,A)

特開2002-280384(JP,A)

特開平06-252075(JP,A)

特開平05-109630(JP,A)

特開2002-368230(JP,A)

特開2004-091253(JP,A)

特開2005-019851(JP,A)

特開2002-270834(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/20

H01L 21/336

H01L 29/78

H01L 29/76

H01L 29/772

H01L 29/762

H01L 21/339

H01L 21/205

H01L 21/31

H01L 21/365

H01L 21/469

H01L 21/86

H01L 21/304