(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5684987号

(P5684987)

(45) 発行日 平成27年3月18日(2015.3.18)

(24) 登録日 平成27年1月23日(2015.1.23)

(51) Int.Cl.

H02M 3/155 (2006.01)

F 1

H02M 3/155

H02M 3/155B

P

請求項の数 6 (全 11 頁)

(21) 出願番号 特願2010-13612 (P2010-13612)

(22) 出願日 平成22年1月25日 (2010.1.25)

(65) 公開番号 特開2011-152023 (P2011-152023A)

(43) 公開日 平成23年8月4日 (2011.8.4)

審査請求日 平成24年11月9日 (2012.11.9)

(73) 特許権者 000002325

セイコーインスツル株式会社

千葉県千葉市美浜区中瀬1丁目8番地

(74) 代理人 100154863

弁理士 久原 健太郎

(74) 代理人 100142837

弁理士 内野 則彰

(74) 代理人 100123685

弁理士 木村 信行

(72) 発明者 出口 充康

千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内

審査官 松本 泰典

最終頁に続く

(54) 【発明の名称】スイッチングレギュレータ

## (57) 【特許請求の範囲】

## 【請求項 1】

スイッチングレギュレータの出力電圧が所定の電圧よりも低い時に、スタートアップ用スイッチング信号を出力する第1の発振回路と、

前記スイッチングレギュレータの起動時において、緩やかに上昇する基準電圧を出力する基準電圧回路と、

前記基準電圧と前記スイッチングレギュレータの出力電圧に基づく帰還電圧とを比較する演算增幅器と、

スイッチング信号を出力する第2の発振回路と、

前記演算增幅器の出力信号と前記スイッチング信号を比較するPWMコンパレータと、

前記スイッチングレギュレータの出力電圧によって、前記スタートアップ用スイッチング信号と前記PWMコンパレータの出力信号とを切替えて出力し、前記スイッチングレギュレータの出力電圧を制御する切替え回路と、

を備えたソフトスタート機能を有するスイッチングレギュレータであって、

前記出力電圧が前記所定の電圧を超える時に、前記基準電圧値が前記帰還電圧値と等しくなるように制御する制御回路を備えたことを特徴とするスイッチングレギュレータ。

## 【請求項 2】

前記制御回路は、前記演算增幅器の入力端子間に接続されるゲイン1倍のアンプで構成される、ことを特徴とする請求項1記載のスイッチングレギュレータ。

## 【請求項 3】

10

20

前記制御回路は、ソースフォロアー回路で構成される、ことを特徴とした請求項 1 記載のスイッチングレギュレータ。

【請求項 4】

前記ソースフォロアー回路は、デプレッション型トランジスタを用いることを特徴とした請求項 3 記載のスイッチングレギュレータ。

【請求項 5】

前記制御回路は、前記演算増幅器を含んだ增幅回路で構成される、ことを特徴とした請求項 1 記載のスイッチングレギュレータ。

【請求項 6】

前記制御回路は、前記スイッチングレギュレータの出力電圧を電源とする、ことを特徴とする請求項 1 から 5 のいずれか記載のスイッチングレギュレータ。 10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチングレギュレータに関し、より詳しくはスイッチングレギュレータのソフトスタート機能に関する。

【背景技術】

【0002】

携帯電話、携帯音楽プレーヤー、デジタルカメラ、PDA など電池で駆動される機器は近年ますますの普及をみている。これらの機器の中には、コスト面や外出時の電源確保の容易性などから、乾電池などを電源とするものも多い。さらに中でもランニングコストの低減や、環境意識の高まりなどから乾電池 1 本での動作を要求する機器もある。乾電池の終止電圧は一般に 0.9V 程度とされるため、これらの機器は 0.9V ~ 1.5V 程度の電圧を 3V や 5V などの電圧に、スイッチングレギュレータを用いて昇圧し、機器の電源として供給する事となる。 20

【0003】

しかしながら、0.9V ~ 1.5V の低電圧でスイッチングレギュレータを安定的に動作させる事は非常に困難である。そこで、スイッチングレギュレータを方形波発振器のパルス（数 10KHz ~ 数百KHz）で昇圧動作させ、出力にある程度高い電圧（1.5V ~ 2.0V）を出力した後に、この電圧をスイッチングレギュレータの電源とする技術が用いられている。 30

【0004】

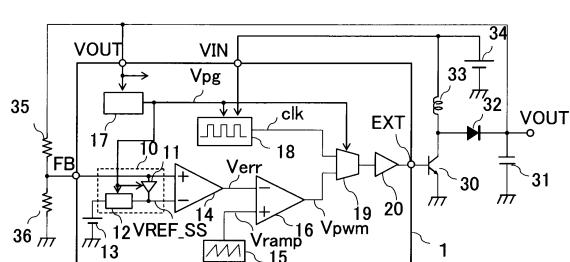

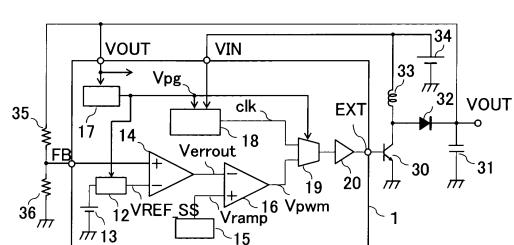

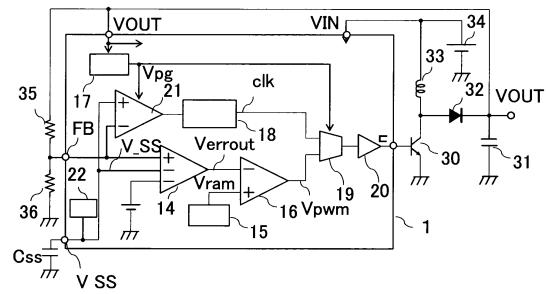

図 4 は、従来のスイッチングレギュレータを示す回路図である。

従来のスイッチングレギュレータは、スイッチングレギュレータ制御回路 1 と周辺回路で構成されている。直流電圧源 34 は、スイッチングレギュレータ制御回路 1 の電源であり、乾電池 1 本を想定し電圧範囲を 0.9V ~ 1.5V とする。方形波発振器 18 は方形波パルス c1k を出力する発振回路である。出力端子 VOUT の電圧は、スイッチングレギュレータ制御回路 1 の電源にもなっている。電圧検出回路 17 は、出力端子 VOUT の電圧を監視する。出力端子 VOUT の電圧がスレッショルド電圧 VTH よりも低ければ、電圧検出回路 17 の検出信号 Vpg は L となる。方形波発振器 18 は、電圧検出回路 17 の検出信号 Vpg が L のとき動作状態となる。マルチプレクサ回路 19 は、電圧検出回路 17 の検出信号 Vpg が L のとき方形波パルス c1k を出力し、電圧検出回路 17 の検出信号 Vpg が H のとき PWM コンパレータ 16 の信号 Vpwm を出力する。バッファ回路 20 は、パワートランジスタ 30 を駆動する。 40

【0005】

スイッチングレギュレータ制御回路 1 が昇圧動作を開始する前、出力端子 VOUT の電圧は直流電圧源 34 の電圧 VIN からダイオード 32 の順方向電圧 Vf を引いた電圧となる。スレッショルド電圧 VTH は、1.5V に設定されたものとする。すなわち、電圧 VIN が 1.5V 以下の時、出力端子 VOUT の出力電圧は 1.5V 以下になるから、電圧検出回路 17 の検出信号 Vpg は L となる。よって、マルチプレクサ回路 19 は方形波発 50

振器 1 8 の方形波パルス c 1 k を出力する。パワートランジスタ 3 0 は、方形波パルス c 1 k で駆動され、スイッチングレギュレータは昇圧動作を開始する。この期間を、スタートアップ期間 T 1 と称する。

【 0 0 0 6 】

スタートアップ期間 T 1 において、検出信号 V p g は L であり、ソフトスタート回路 1 2 の出力 V R E F \_ S S を 0 V に固定する為、スイッチングレギュレータ制御回路 1 は負帰還制御を行なわず、方形波パルス c 1 k による昇圧動作を行なう。

【 0 0 0 7 】

方形波パルス c 1 k による昇圧動作によって、出力端子 V O U T の出力電圧がスレッショルド電圧 V T H を超えると、電圧検出回路 1 7 の検出信号 V p g は H となり、方形波発振器 1 8 は動作を停止する。マルチプレクサ回路 1 9 は、P W M コンパレータ 1 6 の信号 V p w m を出力する。

【 0 0 0 8 】

電圧検出回路 1 7 の検出信号 V p g が H になると、ソフトスタート回路 1 2 が動作を開始し、ソフトスタート期間 T 2 となる。

【 0 0 0 9 】

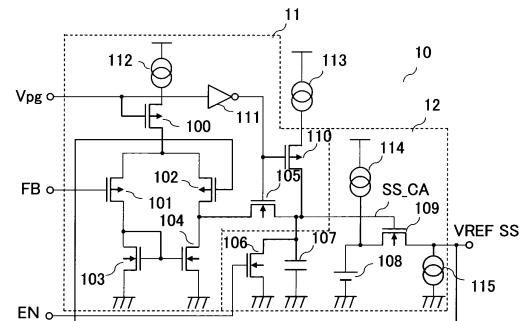

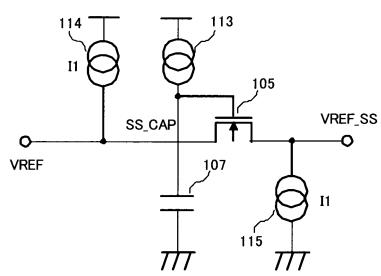

図 5 は、従来のソフトスタート回路 1 2 の一例を示す回路図である。

ソフトスタート回路 1 2 は、以下のように動作をしてソフトスタート用の基準電圧 V R E F \_ S S を出力する。定電流源 1 1 3 がコンデンサ 1 0 7 を充電し、コンデンサ 1 0 7 の電圧は徐々に上昇する。コンデンサ 1 0 7 の電圧は、N 型 M O S トランジスタ 1 0 5 のゲートを制御する。よって、基準電圧源 1 3 の出力する基準電圧 V R E F は、N 型 M O S トランジスタ 1 0 5 から徐々に上昇するソフトスタート用の基準電圧 V R E F \_ S S として出力される。

【 0 0 1 0 】

上述のような構成のスイッチングレギュレータの課題を、図を参照して説明する。

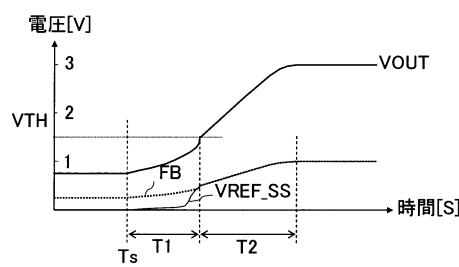

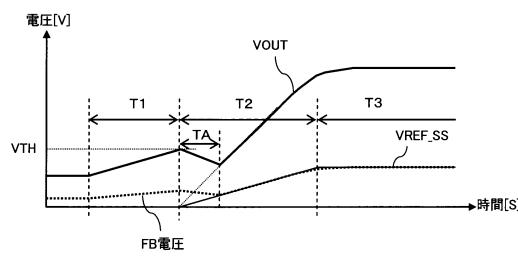

図 6 は、図 4 のスイッチングレギュレータの動作説明のための図である。

【 0 0 1 1 】

スタートアップ期間 T 1 からソフトスタート期間 T 2 に切り替わると、方形波発振器 1 8 は動作を停止し、ソフトスタート回路 1 2 は動作を開始する。出力端子 V O U T の電圧は、スタートアップ期間 T 1 に昇圧されているので、帰還電圧 F B も相当の電圧である。しかし、基準電圧 V R E F \_ S S は、図からわかるように、0 V から徐々に上昇している。ここで、演算増幅器 1 4 は、帰還電圧 F B と基準電圧 V R E F \_ S S の大小関係を等しく保つように、P W M コンパレータ 1 6 に電圧 V e r r o u t を出力する。帰還電圧 F B が基準電圧 V R E F \_ S S に対して大きいので、演算増幅器 1 4 の出力する電圧 V e r r o u t は、ランプ波発振回路 1 5 のランプパルス V r a m p の電圧波形よりも大きい。従って、P W M コンパレータ 1 6 はスイッチングパルスを出力しないので、スイッチングレギュレータは昇圧動作を行わない。よって、出力端子 V O U T の出力電圧は、負荷などによる放電により次第に低下する（期間 T A ）。電圧検出回路 1 7 は、検出電圧にヒステリシスを持っており、ある程度の電圧低下では検出状態を解除しないように設計されている。ここで、負荷が大きいと、出力端子 V O U T の電圧低下が、このヒステリシスを超えてしまい、電圧検出回路 1 7 が検出状態を解除してしまうことがある。この場合、再びスタートアップ期間 T 1 に動作モードが戻り、方形波パルス c 1 k による昇圧動作を開始する。そして、負荷に変化が無ければ、スタートアップ期間 T 1 と期間 T A を繰り返してしまう事となる。

【 0 0 1 2 】

上記課題を解決するために、図 7 に示す回路のスイッチングレギュレータが開示されている（特許文献 1 参照）。方形波発振器 1 8 は、コンパレータ 2 1 によって制御される。コンパレータ 2 1 は、反転端子に入力される帰還電圧 F B が、非反転端子に入力されるソフトスタート用のスロープ電圧 V \_ S S よりも低いときに H レベルを出力し、方形波発振器 1 8 を動作させる。コンデンサ C s s は、起動開始と同時に定電流源 2 2 によって充電

10

20

30

40

50

が開始される。従って、スロープ電圧  $V_{SS}$  は、起動と同時に電圧が上昇する。演算増幅器 14 は反転入力端子が 2 つあり、一方に基準電圧  $V_{ref}$  が入力され、他方にスロープ電圧  $V_{SS}$  が入力されている。二つの反転入力端子は、入力される電圧が低い方の端子のみ機能するよう設計されている。すなわち、スロープ電圧  $V_{SS}$  が上昇を続け、基準電圧  $V_{ref}$  に到達するまではスロープ電圧  $V_{SS}$  が有効となる。そして、スロープ電圧  $V_{SS}$  が基準電圧  $V_{ref}$  を超えると基準電圧  $V_{ref}$  が有効となる。

【0013】

スイッチングレギュレータが起動されると、スロープ電圧  $V_{SS}$  は徐々に上昇する。スロープ電圧  $V_{SS}$  が帰還電圧  $FB$  を超えると、方形波発振器 18 が動作を開始する。そして、スイッチングレギュレータは方形波パルス  $c_{1k}$  による昇圧動作を行なう。また、スロープ電圧  $V_{SS}$  が帰還電圧  $FB$  より低くなると、方形波発振器 18 は動作を停止する。すなわち、一種の周波数変調制御であり、スロープ電圧  $V_{SS}$  の立ち上がりに追従して、出力端子  $VOUT$  の電圧は上昇する。

【0014】

従って、出力端子  $VOUT$  がスレッショルド電圧  $VTH$  を超え、電圧検出回路 17 の検出信号  $V_{pg}$  は  $H$  となったとき、帰還電圧  $FB$  とスロープ電圧  $V_{SS}$  は近い電圧となっているので、図 6 のような期間  $TA$  に相当するタイムラグが無く、円滑にスタートアップから通常制御への移行を実現している。

【先行技術文献】

【特許文献】

【0015】

【特許文献 1】特開 2004-166428 号公報

【発明の概要】

【発明が解決しようとする課題】

【0016】

しかしながら、図 7 のスイッチングレギュレータでは、定電流源 22 がコンデンサ  $C_{ss}$  を充電してスロープ電圧  $V_{SS}$  を作っているので、電源電圧が低いときは、スロープ電圧  $V_{SS}$  の制御が非常に困難である。定電流源 22 に供給される電源電圧が 1V を下回るような場合に、その定電流特性を維持する事は難しく、コンデンサ  $C_{ss}$  に対する充電電流が大きく低下する。この低下の割合は、出力端子  $VOUT$  の出力電圧が高く安定的にソフトスタート回路 12 が動作している時に比べて、1/10 ~ 1/100 以下になる事も有り得る。この場合、スロープ電圧  $V_{SS}$  の立ち上がりの傾きは電流の減少率に等しく減少し、10倍 ~ 100倍以上の時間を要する。すなわち、スイッチングレギュレータの起動時間が大幅に延び、このスイッチングレギュレータを搭載した機器の、電源スイッチ投入から、実際に使用が可能になるまでの時間が長くなるという課題がある。

【0017】

本発明は上記課題を解決するためになされ、電源電圧に依存せず、スタートアップ状態から通常制御への動作状態の移行を円滑に行なうことが可能なスイッチングレギュレータ回路を提供する。

【課題を解決するための手段】

【0018】

本発明のスイッチングレギュレータは、上記課題を解決するために、スイッチングレギュレータの出力電圧が所定の電圧よりも低い時に、スタートアップ用スイッチング信号を出力する第 1 の発振回路と、スイッチングレギュレータの起動時において緩やかに上昇する基準電圧を出力する基準電圧回路と、基準電圧とスイッチングレギュレータの出力電圧に基づく帰還電圧とを比較する演算増幅器と、スイッチング信号を出力する第 2 の発振回路と、演算増幅器の出力信号とスイッチング信号を比較する PWM コンパレータと、スイッチングレギュレータの出力電圧によってスタートアップ用スイッチング信号と PWM コンパレータの出力信号とを切替えて出力する切替え回路と、を備えたソフトスタート機能を有するスイッチングレギュレータであって、出力電圧が所定の電圧を超える時に基準電

10

20

30

40

50

圧値が帰還電圧値と等しくなる、または高くなる、ように制御する制御回路を備えたスイッチングレギュレータ回路を提供する。

【発明の効果】

【0019】

本発明のスイッチングレギュレータによれば、電源電圧に依存せず、スタートアップ状態から通常制御への動作状態の移行を円滑に行うことが可能なスイッチングレギュレータ回路を提供する。

【0020】

また、ソフトスタート時間が極端に長くなることが無いので、本発明のスイッチングレギュレータを搭載した機器は、電源スイッチをオンしてから使用可能になるまでの時間を短縮する事ができる。

10

【図面の簡単な説明】

【0021】

【図1】本実施形態のソフトスタート機能を有するスイッチングレギュレータの回路図である。

【図2】図1のスイッチングレギュレータの動作説明のための図である。

【図3】本実施形態のソフトスタートブロックの一例を示す回路図である。

【図4】従来のスイッチングレギュレータの回路図である。

【図5】従来のソフトスタート回路の一例を示す回路図である。

【図6】図4のスイッチングレギュレータの動作説明のための図である。

20

【図7】従来のスイッチングレギュレータの第二の構成図である。

【図8】図7のスイッチングレギュレータの動作説明のための図である。

【発明を実施するための形態】

【0022】

以下、本発明の実施形態のスイッチングレギュレータを、図面を参照して説明する。

図1は、本実施形態のソフトスタート機能を有したスイッチングレギュレータである。

【0023】

本実施形態のスイッチングレギュレータは、スイッチングレギュレータ制御回路1と周辺回路で構成されている。直流電圧源34は、スイッチングレギュレータ制御回路1の電源であり、乾電池1本を想定し電圧範囲を0.9V~1.5Vとする。直流電圧源34とGNDの間にコイル33とスイッチングトランジスタ30が接続されている。コイル33とパワートランジスタ30の接続点は、ダイオード32を介して出力端子VOUTに接続されている。出力端子VOUTには、出力コンデンサ31と、帰還回路である抵抗35及び抵抗36が接続されている。スイッチングレギュレータ制御回路1は、直流電圧源34と第1電源端子VINを接続し、出力端子VOUTと第2電源端子VOUTを接続し、パワートランジスタ30のベースと出力端子EXTを接続し、帰還回路の出力端子と帰還電圧端子FBを接続する。帰還回路は、スイッチングレギュレータ制御回路1に内蔵されても良い。

30

【0024】

スイッチングレギュレータ制御回路1は、アンプ11と、ソフトスタート回路12と、基準電圧源13と、演算増幅器14と、ランプ波形発信器15と、PWMコンパレータ16と、電圧検出回路17と、方形波発振器18と、マルチプレクサ回路19と、バッファ回路20と、を備える。アンプ11とソフトスタート回路12は、ソフトスタートブロック10を構成する。

40

【0025】

第1電源端子VINの電圧は、方形波発振器18の電源になっている。第2電源端子VOUTの電圧は、スイッチングレギュレータの出力電圧であり、方形波発振器18を除く回路の電源にもなっている。帰還電圧端子FBは、帰還回路の出力が接続されている。

【0026】

電圧検出回路17は、第2電源端子VOUTの電圧を監視する。電圧検出回路17の検

50

出信号  $V_{pg}$  は、第 2 電源端子  $V_{OUT}$  の電圧がスレッショルド電圧  $V_{TH}$  よりも低ければ L となり、高ければ H となる。

【0027】

方形波発振器 18 は、スタートアップ用スイッチング信号である方形波パルス  $c_{1k}$  を出力するスタートアップ用発振回路である。方形波発振器 18 は、電圧検出回路 17 の検出信号  $V_{pg}$  が L のときに方形波パルス  $c_{1k}$  を出力する。方形波発振器 18 は、発振周波数は製造バラツキや温度特性や電源電圧特性などで数 10 KHz ~ 数 100 KHz の範囲でばらついても、昇圧動作には問題無いことから、0.9V といった非常に低い電源電圧で動作が可能な回路で構成することが出来る。

【0028】

演算増幅器 14 は、入力される帰還電圧端子  $FB$  の電圧とソフトスタート回路 12 が出力する基準電圧  $V_{REF\_SS}$  とを比較して、電圧  $V_{errout}$  を出力する。

【0029】

アンプ 11 は、演算増幅器 14 の入力端子間に接続される。アンプ 11 は、ゲイン 1 倍のアンプであり、電圧検出回路 17 の検出信号  $V_{pg}$  が L のときに、演算増幅器 14 の入力端子の電圧が等しくなるように動作する制御回路である。

【0030】

ランプ波発振回路 15 は、スイッチング信号であるランプパルス  $V_{ramp}$  を出力する発振回路である。ランプ波発振回路 15 のランプパルス  $V_{ramp}$  は、三角波やノコギリ波などのある一定の傾きを持った発振波形となっている。

【0031】

PWM コンパレータ 16 は、演算増幅器 14 の電圧  $V_{errout}$  とランプ波発振回路 15 のランプパルス  $V_{ramp}$  とを比較し、信号  $V_{pwm}$  を出力する。

【0032】

マルチブレクサ回路 19 は、方形波発振器 18 の出力信号である方形波パルス  $c_{1k}$  と、PWM コンパレータ 16 の信号  $V_{pwm}$  と、いずれか一方を選択して出力する切替え回路である。マルチブレクサ回路 19 は、電圧検出回路 17 の検出信号  $V_{pg}$  が L の場合は方形波パルス  $c_{1k}$  を出力し、検出信号  $V_{pg}$  が H の場合は信号  $V_{pwm}$  を出力する。

【0033】

バッファ回路 20 は、マルチブレクサ回路 19 の出力する信号に基づいて、スイッチングレギュレータのスイッチング素子であるパワートランジスタ 30 を駆動する。

【0034】

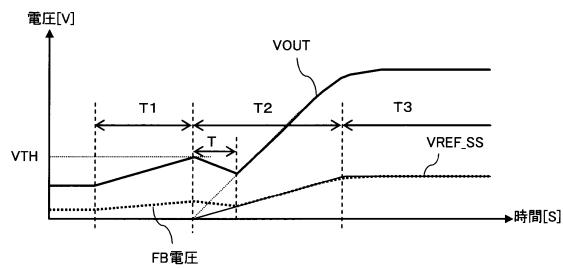

上述のように構成されたスイッチングレギュレータの動作について、図面を元に説明する。図 2 は、図 1 のスイッチングレギュレータの動作を示す図である。

【0035】

スイッチングレギュレータが昇圧動作を開始する前は、パワートランジスタ 30 がオフしているので、出力端子  $V_{OUT}$  の電圧は直流電圧源 34 の電圧  $V_{IN}$  からダイオード 32 の順方向電圧  $V_f$  を減じた電圧である。ショットキーバリアダイオードの場合は、順方向電圧  $V_f$  は 0.2V ~ 0.3V である。マルチブレクサ回路 19 やバッファ回路 20 などのデジタル回路は、電圧  $V_{IN}$  が 0.9V で出力端子  $V_{OUT}$  が更に 0.2V ~ 0.3V 低い状態においても動作は可能である。

【0036】

先ず、起動時  $T_s$  においてスイッチングレギュレータが起動されたときの動作を説明する。

【0037】

ここで、電圧検出回路 17 のスレッショルド電圧  $V_{TH}$  は 1.5V に設定されている。すなわち、電圧  $V_{IN}$  が 0.9V ~ 1.5V の範囲にある時、電圧検出回路 17 の検出信号  $V_{pg}$  は L となる。従って、方形波発振器 18 は動作を開始し方形波パルス  $c_{1k}$  信号を出力する。また、マルチブレクサ回路 19 は方形波発振器 18 の出力を選択する。

【0038】

10

20

30

40

50

よって、マルチプレクサ回路 19 は方形波発振器 18 の方形波パルス c 1 k を出力する。出力端子 E X T に出力された方形波パルス c 1 k によって、パワートランジスタ 30 が駆動され、スイッチングレギュレータが昇圧動作を開始する。

#### 【 0 0 3 9 】

スイッチングレギュレータが方形波パルス c 1 k 信号によって昇圧動作を行なう期間をスタートアップ期間 T 1 と称する。スタートアップ期間 T 1 において、本スイッチングレギュレータは負帰還制御を行なっておらず、出力端子 V O U T の出力電圧がスレッショルド電圧 V T H を超えるまでの間において方形波パルス c 1 k による昇圧動作を行なう。

#### 【 0 0 4 0 】

また、同時にソフトスタートブロック 10 を構成するソフトスタート回路 12 とアンプ 11 も動作を開始する。アンプ 11 は、起動時 T s から帰還電圧 F B に近似する電圧を基準電圧 V R E F \_ S S へ出力するように動作状態が設定される。しかしながら、起動時 T s 直後では出力端子 V O U T の出力電圧が非常に低いためアンプ 11 は正常に動作する事が出来ない。よって、基準電圧 V R E F \_ S S と帰還電圧 F B の電位差は大きい。

10

#### 【 0 0 4 1 】

演算増幅器 14 は、演算増幅器であり、帰還回路を構成する場合、その反転入力と非反転入力の電位差が 0 V となるように帰還制御を行う。すなわち、演算増幅器 14 は、基準電圧 V R E F \_ S S が帰還電圧 F B より高ければ電圧 V e r r o u t を低くし、基準電圧 V R E F \_ S S が帰還電圧 F B より低ければ電圧 V e r r o u t を高くする。すなわち、ソフトスタート期間 T 2 となり、演算増幅器 14 の帰還制御が始まる時点において、演算増幅器 14 の反転入力と非反転入力の電位差がほぼ等しい電位にあれば、大きな変動を伴う帰還制御を行う必要が無く、安定的にスタートアップ期間 T 1 からソフトスタート期間 T 2 へ移行する事ができる。

20

#### 【 0 0 4 2 】

図 3 は、本実施形態のソフトスタートブロック 10 の一例を示す回路図である。

ソフトスタートブロック 10 は、アンプ 11 とソフトスタート回路 12 を備えている。アンプ 11 は、トランジスタ 100 ~ 104 と定電流源 112 からなる差動増幅回路と、トランジスタ 105 及び 110 とインバータ 111 からなる切り替え回路とを備える。ソフトスタート回路 12 は、定電流源 113、114 及び 115 と、直流電圧源 108 と、コンデンサ 107 と、トランジスタ 105 及び 110 とを備えている。差動増幅回路は、入力であるトランジスタ 101 と 102 に帰還電圧 F B とソフトスタート回路 12 の出力である基準電圧 V R E F \_ S S が入力される。また、検出信号 V p g が入力されるトランジスタ 100 によって動作と停止が制御される。さらに、検出信号 V p g がインバータ 111 を介して入力されるトランジスタ 110 と 105 によって、差動増幅回路の出力と定電流源 113 の出力とが切替えて出力される。図示しない起動回路から起動信号 E N がトランジスタ 106 のゲートに入力されることによって、コンデンサ 107 は充放電が制御される。トランジスタ 109 は、ゲート端子をコンデンサ 107 の電圧 S S \_ C A P によって制御される。

30

#### 【 0 0 4 3 】

ソフトスタート回路 12 は、ソフトスタート用の基準電圧 V R E F \_ S S を出力する。アンプ 11 は、検出信号 V p g が H となり昇圧状態が切り替わった時に、基準電圧 V R E F \_ S S 電圧が帰還電圧 F B とほぼ等しくなるように制御する。

40

#### 【 0 0 4 4 】

起動時 T s に検出信号 V p g が L であるから、トランジスタ 100 が導通状態となり、差動増幅回路が動作を開始する。また、トランジスタ 105 は導通状態となり、トランジスタ 110 は非導通状態となるので、差動増幅回路の出力ノードはトランジスタ 105 を介してトランジスタ 109 のゲートに接続される。この時、差動増幅回路とトランジスタ 109 と定電流源 114 及び 115 とは、演算増幅器を構成する。演算増幅器は、トランジスタ 109 のソースが出力、トランジスタ 102 のゲートが反転入力、トランジスタ 101 の入力が非反転入力として機能する。従って、演算増幅器はボルテージフォローアー回

50

路を構成し、帰還電圧 F B に等しい電圧を出力端子に出力する。すなわち、基準電圧 V R E F \_ S S は帰還電圧 F B に等しい電圧となる。

【 0 0 4 5 】

上述のような昇圧動作によって出力端子 V O U T の出力電圧が電圧検出回路 17 のスレッショルド電圧 V T H を超えると、期間 T 2 となる。電圧検出回路 17 の検出信号 V p g が H になると、トランジスタ 100、105 は非導通となり、差動増幅回路はその動作を停止する。トランジスタ 110 が導通状態となるので、定電流源 113 はコンデンサ 107 の充電を開始する。従って、ノード S S \_ C A P の電圧がゆっくり上昇を開始する。この時、定電流源 114 及び 115 は電流を流し続けるので、トランジスタ 109 はソースフォロア回路として動作して、ノード S S \_ C A P の電圧からトランジスタ 109 の電圧 V g s 分下がった電圧を基準電圧 V R E F \_ S S として出力する。以上の事から、基準電圧 V R E F \_ S S は期間 T 1 において帰還電圧 F B に準ずる電圧に到達し、期間 T 2 に入ると直ちに、ノード S S \_ C A P の充電波形に依存した形状で上昇を開始する。トランジスタ 109 は、ドレインに直流電圧源 108 が接続されている為、基準電圧 V R E F \_ S S が直流電圧源 108 の電圧 V R E F まで上昇すると、それ以上は上昇する事が出来ない。従って、電圧 V R E F を安定電位として、ソフトスタート期間 T 2 は終了する。

【 0 0 4 6 】

そして、スタートアップ期間 T 1 において、検出信号 V p g が H となると、方形波発振器 18 は動作を停止し、マルチプレクサ回路 19 は信号 V p w m を出力する。すなわち、スイッチングレギュレータは通常の P W M 制御で昇圧動作を行う。

【 0 0 4 7 】

以上説明したように、本発明のスイッチングレギュレータは、スタートアップ期間 T 1 からソフトスタート期間 T 2 へ切り替わる時に、ソフトスタート用の基準電圧 V R E F \_ S S が帰還電圧 F B と等しくなっている。従って、スタートアップ期間 T 1 からソフトスタート期間 T 2 への移行が安定的に行われる。

【 0 0 4 8 】

なお、本発明のスイッチングレギュレータはスタートアップ期間 T 1 からソフトスタート期間 T 2 へ切り替わる時に、ソフトスタート用の基準電圧 V R E F \_ S S が帰還電圧 F B と等しくなる構成として説明したが、基準電圧 V R E F \_ S S が帰還電圧 F B より高くなるような構成でも良い。例えば、アンプ 11 の増幅率を 1 以上に設定する、すなわちアンプ 11 を非反転増幅回路とし、帰還電圧 F B を所望の倍率で増幅しても良い。このように構成すると、アンプ 11 のオフセット電圧など性能バラツキに対して余裕を持つことが出来て、スタートアップ期間 T 1 からソフトスタート期間 T 2 への移行が安定的に行われる。

【 0 0 4 9 】

また、アンプ 11 を、入力に帰還電圧 V F B を接続し、出力に V R E F \_ S S を接続したソースフォロア回路で構成しても良い。しかしながら、ソースフォロア回路の増幅率は一般に 1 以下であり、概ねソースフォロア回路に用いる M O S トランジスタの閾値電圧を入力電圧から差し引いた値が出力電圧となる。従って、デプレッション型トランジスタなど、閾値電圧が低いトランジスタを用いたソースフォロア回路とすれば、増幅率を 1 に近づける事が可能である。

【 符号の説明 】

【 0 0 5 0 】

- 1 0 ソフトスタートブロック

- 1 1 アンプ

- 1 2 ソフトスタート回路

- 1 3 基準電圧源

- 1 4 演算増幅器

- 1 5 ランプ波発振回路

- 1 6 P W M コンパレータ

10

20

30

40

50

- 1 7 電圧検出回路

1 8 方形波発振器

1 9 マルチプレクサ回路

2 0 バッファ回路

2 1 コンパレータ

3 0 パワートランジスタ

3 4、1 0 8 直流電圧源

2 2、1 1 2、1 1 3、1 1 4、1 1 5 定電流源

【図 1】

【図 3】

【図 2】

【図 4】

【図5】

【図7】

【図6】

【図8】

---

フロントページの続き

(56)参考文献 特開2004-166428(JP, A)

特開平08-186980(JP, A)

特開2009-088587(JP, A)

国際公開第2006/059705(WO, A1)

特開2009-131062(JP, A)

特開2009-130972(JP, A)

特開2007-259515(JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/155