(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4790110号

(P4790110)

(45) 発行日 平成23年10月12日(2011.10.12)

(24) 登録日 平成23年7月29日(2011.7.29)

(51) Int.Cl.

F 1

|              |           |              |         |

|--------------|-----------|--------------|---------|

| G 11 C 29/12 | (2006.01) | G 11 C 29/00 | 6 7 3 V |

| G 11 C 29/02 | (2006.01) | G 11 C 29/00 | 6 7 5 M |

| G 01 R 31/28 | (2006.01) | G 01 R 31/28 | B       |

| G 06 F 12/16 | (2006.01) | G 01 R 31/28 | V       |

| G 11 C 16/02 | (2006.01) | G 06 F 12/16 | 3 3 O A |

請求項の数 5 (全 14 頁) 最終頁に続く

(21) 出願番号

特願2000-350094 (P2000-350094)

(22) 出願日

平成12年11月16日 (2000.11.16)

(65) 公開番号

特開2001-202799 (P2001-202799A)

(43) 公開日

平成13年7月27日 (2001.7.27)

審査請求日 平成19年11月14日 (2007.11.14)

(31) 優先権主張番号 441865

(32) 優先日 平成11年11月17日 (1999.11.17)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 78735 テキサス州

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100116322

弁理士 桑垣 衡

(72) 発明者 リチャード・カズキ・エグチ

アメリカ合衆国テキサス州オースチン、ク

レイア・コーブ 2804(72) 発明者 デビット・ウィリアム・クルディムスキ

アメリカ合衆国テキサス州オースチン、ガ

ントクレスト 8514

最終頁に続く

(54) 【発明の名称】回路内メモリ・アレイ・ビット・セル・スレシホールド電圧分布測定

## (57) 【特許請求の範囲】

## 【請求項 1】

オン・チップ・プログラマブル回路を用いてウェハ上で複数の素子を一括検査する方法であって、各々の素子はビット・セル・アレイを有する不揮発性メモリを含み、前記方法は：

前記不揮発性メモリの行デコーダに対して、前記不揮発性メモリを通常モードで動作させるための動作電源の電源電圧と異なり、かつ所定の電圧範囲を有する検査電源の電源電圧を供給し、前記行デコーダによりワード・ラインを前記検査電源の前記電源電圧としてのワード・ライン電圧で駆動する段階であって、前記検査電源はチップ上でプログラム可能である、前記駆動する段階であって、前記動作電源の電源電圧と前記検査電源の電源電圧との間で前記ワード・ライン電圧を切り替えるための、前記チップ内の制御レジスタの第1のフィールドに記憶された指示データを読み出すこと、前記制御レジスタの第2のフィールドに記憶された前記検査電源の電源電圧のデータを読み出すことを含む、前記駆動する段階；

前記ワード・ライン電圧を前記所定の電圧範囲内の複数の電圧値の内の第1電圧値に設定する段階であって、前記複数の電圧値は前記第1電圧値、最終電圧値、および前記第1および最終電圧値の間の複数の電圧値からなる、段階；

前記不揮発性メモリ内において前記ビット・セル・アレイを読み取る段階；

ビット・セルが導通状態にあるか否かを判定する段階；

前記ワード・ライン電圧が最終電圧値であるか否かについて判定を行なう段階；

10

20

前記ワード・ライン電圧が前記最終電圧値でない場合、前記最終電圧値への方向における次の電圧値である前記複数の電圧値の内の選択された1つの電圧値へと前記検査電源の電圧値の分圧値だけ前記ワード・ライン電圧を変化させる段階；および

前記ワード・ライン電圧が前記最終電圧値を有するまで、前記ビット・セル・アレイを読み取る前記段階、前記ビット・セルが導通状態にあるか否かを判定する前記段階、前記ワード・ライン電圧が最終電圧値であるか否かについて判定を行なう前記段階、および前記ワード・ライン電圧を変化させる前記段階を繰り返す段階；

を具備し、前記不揮発性メモリにおけるスレシホールド電圧分布が前記第1電圧値から前記最終電圧値までの範囲にわたり測定されることを特徴とする方法。

【請求項2】

10

ビット・セル・アレイを含む不揮発性メモリを動作させる方法であって：

動作電源および前記動作電源と異なり、かつ所定の電圧範囲を有する検査電源間で選択を行なう段階であって、前記検査電源がチップ上でプログラム可能である、前記選択を行う段階であって、前記動作電源の電源電圧と前記検査電源の電源電圧との間で選択を行うための、前記チップ内の制御レジスタの第1のフィールドに記憶された指示データを読み出すこと、前記制御レジスタの第2のフィールドに記憶された前記検査電源の電源電圧のデータを読み出すことを含む、前記選択を行う段階；

前記動作電源が選択された場合、前記不揮発性メモリを動作モードで動作させる段階；および

前記検査電源が選択された場合、前記不揮発性メモリを検査モードで動作させる段階；を具備し、

20

前記検査モードにおいて、第1電圧値から最終電圧値までの前記所定の電圧範囲にわたりて、前記不揮発性メモリにおける前記ビット・セル・アレイのスレシホールド電圧分布を測定し、前記電圧値は前記第1電圧値、前記最終電圧値および前記第1電圧値と前記最終電圧値との間の複数の電圧値を有し、前記不揮発性メモリを検査モードで動作させる段階は：

前記不揮発性メモリの行デコーダに対して、検査電源を選択して前記検査電源の電源電圧を供給し、前記行デコーダによりワード・ラインを前記検査電源の前記電源電圧としてのワード・ライン電圧で駆動する段階；

前記ワード・ライン電圧を前記第1電圧値に設定する段階；

30

前記不揮発性メモリ内において前記ビット・セル・アレイを読み取る段階；

ビット・セルが導通状態にあるか否かについて判定する段階；

前記ワード・ライン電圧が最終電圧値であるか否かについて判定を行なう段階；

前記ワード・ライン電圧が前記最終電圧値でない場合、前記最終電圧値の方向に前記検査電源の分圧値だけ、前記ワード・ライン電圧を変化させる段階；および

前記ワード・ライン電圧が前記最終電圧値を有するまで、前記ビット・セル・アレイを読み取る前記段階、前記ビット・セルが導通状態にあるか否かについて判定する前記段階、前記ワード・ライン電圧が最終電圧値であるか否かについて判定を行なう前記段階、および前記ワード・ライン電圧を変化させる前記段階を繰り返す段階；

を具備することを特徴とする方法。

40

【請求項3】

ビット・セル・アレイを含む不揮発性メモリを動作させる方法であって：

動作電源および前記動作電源と異なり、かつ所定の電圧範囲を有する検査電源間で選択を行なう段階であって、前記検査電源がチップ上でプログラム可能である、前記選択を行う段階であって、前記動作電源の電源電圧と前記検査電源の電源電圧との間で選択を行うための、前記チップ内の制御レジスタの第1のフィールドに記憶された指示データを読み出すこと、前記制御レジスタの第2のフィールドに記憶された前記検査電源の電源電圧のデータを読み出すことを含む、前記選択を行う段階；

前記動作電源が選択された場合、前記不揮発性メモリを動作モードで動作させる段階；および

50

前記検査電源が選択された場合、前記不揮発性メモリを検査モードで動作させる段階；を具備し、

前記検査モードにおいて、前記不揮発性メモリの切迫不良を検出し、前記不揮発性メモリを検査モードで動作させる前記段階は：

動作電源を選択して前記不揮発性メモリの行デコーダに前記動作電源の電源電圧を供給し、前記行デコーダによりワード・ラインを前記動作電源の前記電源電圧としてのワード・ライン電圧で駆動する段階；

前記動作電源を前記不揮発性メモリに印加した後、前記ビット・セル・アレイから第1データ・セットを読み取る段階；

前記検査電源を選択して前記不揮発性メモリの前記行デコーダに前記検査電源の電源電圧を供給し、前記行デコーダによりワード・ラインを前記検査電源の前記電源電圧としてのワード・ライン電圧で駆動する段階；

前記ワード・ライン電圧を所定の電圧範囲内の切迫不良電圧値に設定する段階；

前記ワード・ライン電圧を前記切迫不良電圧値に設定した後、前記ビット・セル・アレイから第2データ・セットを読み取る段階；

前記第1データ・セットを前記第2データ・セットと比較する段階；および

前記第1データ・セットの前記第2データ・セットに対する比較に基づいて、切迫不良が示されたか否かについて判定を行なう段階；

を具備することを特徴とする方法。

#### 【請求項4】

ビット・セル・アレイを含む不揮発性メモリを動作させる方法であって：

動作電源および前記動作電源と異なり、かつ所定の電圧範囲を有する検査電源間で選択を行なう段階であって、前記検査電源がチップ上でプログラム可能である、前記選択を行う段階であって、前記動作電源の電源電圧と前記検査電源の電源電圧との間で選択を行うための、前記チップ内の制御レジスタの第1のフィールドに記憶された指示データを読み出すこと、前記制御レジスタの第2のフィールドに記憶された前記検査電源の電源電圧のデータを読み出すことを含む、前記選択を行う段階；

前記動作電源が選択された場合、前記不揮発性メモリを動作モードで動作させる段階；および

前記検査電源が選択された場合、前記不揮発性メモリを検査モードで動作させる段階；を具備し、

前記検査モードにおいて、前記不揮発性メモリの応力検査を行い、前記不揮発性メモリを検査モードで動作させる前記段階は：

前記ビット・セル・アレイを第1数値セットに初期化する段階；

ストレスを印加する段階；

前記検査電源を選択して前記不揮発性メモリの行デコーダに前記検査電源の電源電圧を供給し、前記行デコーダによりワード・ラインを前記検査電源の前記電源電圧としてのワード・ライン電圧で駆動する段階；

前記ワード・ライン電圧を所定の電圧範囲内のストレス・マージン電圧値に設定する段階；

前記ワード・ライン電圧を前記ストレス・マージン電圧値に設定した後、前記ビット・セル・アレイから第2数値セットを読み取る段階；

前記第1数値セットを前記第2数値セットと比較する段階；および

前記第1数値セットの前記第2数値セットに対する比較に基づいて、ストレス不良が発生したか否かについて判定を行なう段階；

を具備することを特徴とする方法。

#### 【請求項5】

マイクロコントローラであって：

不揮発性メモリ・ビット・セル・アレイであって、ワード・ラインを電源電圧で駆動する行デコーダを有する、前記不揮発性メモリ・ビット・セル・アレイ；

10

20

30

40

50

前記行デコーダに前記電源電圧を供給するように結合された出力を有する電力スイッチ；

前記電力スイッチの第1入力に動作電源の電源電圧と異なり、かつ所定の電圧範囲を有する検査電源の電源電圧を供給するように結合された出力を有するプログラマブル電圧発生器；

前記電力スイッチの第2入力に結合された出力を有する前記動作電源；および

前記電力スイッチの制御入力に結合された第1出力を有し、前記プログラマブル電圧発生器に結合された第2出力を有し、前記プログラマブル電圧発生器によって出力される前記検査電源の電源電圧を決定する制御回路；

を具備し、

10

前記制御回路は、

前記不揮発性メモリが動作モードで動作する場合に前記電力スイッチに前記動作電源の電源電圧を供給させ、前記不揮発性メモリが検査モードで動作する場合に前記電力スイッチに前記検査電源の電源電圧を供給させ、

前記動作電源の電源電圧と前記検査電源の電源電圧との間で選択を行うための指示データを記憶する第1のフィールドと、前記検査電源の電源電圧のデータを記憶する第2のフィールドとを有する制御レジスタを含むことを特徴とするマイクロコントローラ。

【発明の詳細な説明】

【0001】

20

【発明の属する技術分野】

本発明は、不揮発性メモリ・システムに関し、更に特定すれば、当該不揮発性メモリ・システム内においてビット・セルのスレシホールド電圧を測定する回路内技法即ちオン・チップ技術を含むメモリ・システムに関する。

【0002】

【従来の技術】

NVMシステムにおけるビット・セルのスレシホールド電圧測定は、典型的に、外部の製品検査プラットフォーム(plat form)を使用し、例えば、入力電圧を掃引しピン上のビット・セル電圧を測定することによって、フラッシュ・メモリ内のビット・セルの電流／電圧特性を測定する。NVMシステムにおける別のビット・セルのスレシホールド電圧測定方法に、外部の製品検査プラットフォームを使用し、例えば、入力電圧を掃引しデジタル・データ出力を読み取ることによって、ビット・セルの電流／電圧特性を測定し、更に内部基準に対してビット・セル電流／電圧特性を比較するものがある。これら従来の方法双方には、検査プラットフォームが正確に制御された入力電圧を掃引することができなければならず、しかも最初の方法の場合、小さなビット・セル電流を測定できなければならないという欠点がある。

30

【0003】

現在のフラッシュEEPROMアレイのスレシホールド電圧分布の典型的な測定は、既存の製品検査プラットフォームを用いてデータ収集するために、複雑な外部電圧およびタイミング制御を必要とする。例えば、既存の製品検査プラットフォームは、被検査素子の同期、複雑な制御コード、およびインテリジェント検査プラットフォームを必要とし、その結果検査時間が長くなり、被検査素子のピン数が多いために、並列度が高い検査環境には適していなかった。また、既存の製品検査プラットフォームは、高精度の電源を必要とする。単一の現場テスター(site tester)上で埋め込み型不揮発性メモリ(NVM)を有するマイクロコントローラを検査する際に考慮すべき別の問題点には、プログラム／消去サイクルの後に生ずるデータ保持力の低下およびゲート／ドレイン・ストレスの悪化、ならびに高耐久性仕様の部品に対する潜伏性プログラム／消去耐久性欠損の識別が含まれる。

40

【0004】

【発明が解決しようとする課題】

従来の单一現場テスター上における埋め込みNVMを有するマイクロコントローラの検査では、全検査コストの90%までがフラッシュ・モジュールだけに用いられていることが示

50

されている。500Kバイト更に1Mバイトにも達するサイズの埋め込みNVMメモリでは、品質および信頼性を維持しつつ、サイクル時間を短縮しコストを削減するために、フラッシュを検査する方法の改良および高コスト効率化が求められている。

【0005】

本発明は、ピット・セル・アレイの制御ゲートを掃引し、ピット・セル電流／電圧特性を内部基準と比較するための、オン・チップ・ディジタル可制御精密電圧源を提供する。本発明は、内蔵型であり、並列性が高い環境における自己検査に適しており、検査工程におけるプラットフォーム・テスタ／素子のオーバーヘッドを解消することによって、スループットを向上させる。

【0006】

10

【課題を解決するための手段】

先に述べたのは概要であり、したがって、必然的に、簡略化、一般化および詳細の省略がある。つまり、この概要は例示に過ぎず、全く限定を意図していないことを当業者は認めよう。本発明の他の態様、発明的特徴、および利点は、以下の詳細な説明において明白となろう。

【0007】

本発明によれば、ピット・セル・アレイを含む不揮発性メモリを動作させる装置および方法が記載される。動作電源および検査電源間で選択が行われ、検査電源はチップ上でプログラム可能である。不揮発性メモリは、動作電源が選択された場合には、動作モードで動作し、検査電源が選択された場合には検査モードで動作する。

20

【0008】

本発明の第1実施例では、不揮発性メモリを検査モードで動作させ、不揮発性メモリ内におけるスレシホールド電圧分布を第1電圧値から最終電圧値までの電圧値範囲において測定する。本発明の別の実施例では、検査モードにおける不揮発性メモリの動作は、不揮発性メモリの切迫不良(imminent failure)の早期検出を含む。本発明の更に別の実施例では、検査モードにおける不揮発性メモリの動作は、不揮発性メモリの応力検査を含む。

【0009】

本発明の特性および利点の更なる理解は、本明細書の残りの部分および図面を参考することによって実現されよう。

【0010】

30

【発明の実施の形態】

添付図面を参照することによって、本発明のより良い理解が得られ、その多数の目的、特徴、および利点は当業者には明白となろう。異なる図面における同一参照符号の使用は、同様または同一の部分を示すこととする。

【0011】

特に指示しない限り、多数の図に同じ参照番号で現れる構造は同一である。

【0012】

以下の記載は、本発明の一例の詳細な説明を行なうことを意図するのであり、発明自体を限定するものとは見なしてはならない。逆に、特許請求の範囲に規定した本発明の範囲内には、多数の変形が該当する可能性がある。

40

【0013】

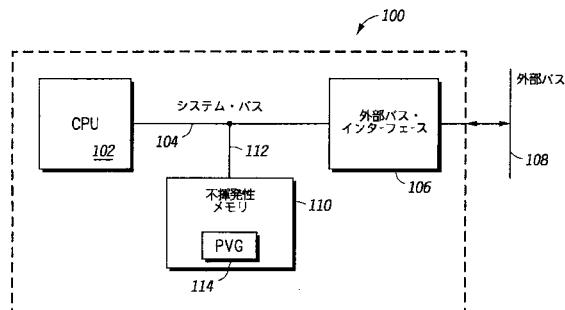

図1は、埋め込み不揮発性メモリ(NVM)110モジュールを含むマイクロコントローラ100の機能ブロック図であり、NVM110モジュールは、更に、オン・チップ・プログラマブル電圧発生器(PVG)114を含む。更に、マイクロコントローラ100は、システム・バス104を通じてNVM110に接続された中央演算装置(CPU)102を含む。外部バス・インターフェース106がシステム・バス104を通じてNVM110およびCPU102に接続されており、外部バス108を通じて、例えば、I/O素子(図示せず)のような外部素子に接続するために利用される。

【0014】

前述の部品および素子は、ここでは、概念を明確にするための例として用いている。例え

50

ば、CPU102は、マイクロプロセッサ・ユニットを含みこれには限定されないあらゆる汎用演算装置の一例として利用され、システム・バス104および外部バス108は、マルチプロセッサ・バスおよびI/Oバスを含みこれらには限定されないあらゆる処理バスの例として利用され、外部バス・インターフェース106は、外部バスとインターフェースするために利用されるあらゆる種類のインターフェースの一例として利用される。したがって、ここで用いる場合、これらの具体的な例は、その更に一般的なクラスを代表することを意図するものとする。更に、総じて、ここで具体的な例の使用は、そのクラスを代表することも意図しており、かかる具体的な素子が前述のリストに含まれないことは、限定が望ましいことを示すとして解釈してはならない。

## 【0015】

10

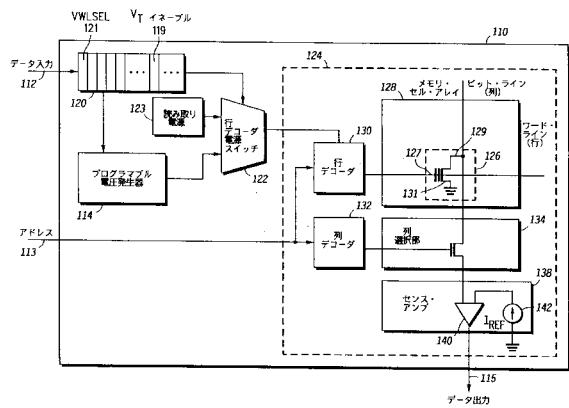

図2は、本発明によるNVM110モジュールの機能ブロック図である。NVM110モジュールは、図1に示すように、マイクロコントローラ100内に埋め込むことができ、あるいは単体のメモリ・モジュールとすることも可能である。NVM110のコアは、メモリ・セルまたはビット・セル、例えば、ビット・セル126のアレイ128である。アレイ128は、好ましくは、フローティング・ゲート・トランジスタ・セル・アレイであり、各ビット・セル126は、フローティング・ゲート・トランジスタを含み、制御ゲート端子127がワード・ラインに接続され、ドレイン端子129がビット・ラインに接続され、ソース端子131がアースに接続されている。アレイ128内の個々のビット・セル126は、行および列に配列されており、例えば、合計128Kの32ビット・ワードがアレイ128に格納される。行デコーダ130は、アドレス・ライン113からのアドレス入力をデコードし、所望のメモリ・ビット・セル126が位置するアレイ128内の行を選択する。列デコーダ132はアドレス・ライン113からのアドレス入力をデコードし、列選択部134をイネーブルして、所望のメモリ・ビット・セル126が位置するアレイ128内の列を選択する。列選択部134は、ビット・セル126を、複数のセンス・アンプ、例えば、センス・アンプ140を含むセンス・アンプ・モジュール138に接続する。センス・アンプ140は、読み取り動作の間、またはビット・セルの状態が、例えば、プログラミングまたは消去動作の後に判定されるデータ検証ステップの間に、メモリ・ビット・セル内に含まれているデータを読み取るために用いられる。例えば、センス・アンプ140は、ビット・セル126の電流値を含む、ビット・セル126内に含まれるデータを判定する際、ビット・セル126の電流値を電流基準142と比較する。ビット・セル126の電流が電流基準142よりも大きい場合、センス・アンプ140は、ビット・セル126を、データ出力ライン115上において1の論理値として読み取る。ビット・セル126の電流が電流基準142未満である場合、センス・アンプ140は、ビット・セル126を、データ出力ライン115上において0の論理値として読み取る。

20

## 【0016】

30

アレイ128内のメモリ・セルのプログラミングまたは消去は、適切な時間期間にわたり適切な電圧をセルのソース、ドレインおよび制御ゲートに印加することによって行われる。これによって、電子はチャネル領域からフローティング・ゲートに潜入する、即ち、注入される。フローティング・ゲート上にある電荷量は、素子にソースおよびドレイン領域間に電流を導通させるために制御ゲート上に必要な電圧を決定する。これをビット・セルのスレシホールド電圧または $V_T$ と呼ぶ。導通は素子の「オン」または消去状態を表し、1の論理値に対応する。プログラム状態の「オフ」は、ソースおよびドレイン領域間に電流が導通していない状態であり、ゼロの論理値に対応する。ビット・セルの $V_T$ を適切な値に設定することにより、1組の所与の印加電圧に対して、ビット・セルに電流を導通させるかまたは導通させないようにすることができる。このように、1組の所与の印加電圧においてビット・セルが電流を導通させるか否かについて決定することにより、ビット・セルの状態（プログラムまたは消去）を求めることができる。

40

## 【0017】

NVM110モジュールは、アレイ128内のビット・セルに対するプログラミングまたは消去動作を行なった後、当該ビット・セルのステータスを検証する。検証を行なうには

50

、各ビット・セルにアクセスし、動作後にビット・セルが有するマージン（ビット・セルのV<sub>T</sub>およびアース・レベル間の電圧差）を評価する。

【0018】

NVM110モジュールは、制御レジスタ120、行デコーダ電源スイッチ122、動作読み取り電源123、およびプログラマブル電圧発生器（PVG）114を含む。PVG114は、例えば、分圧器を含む。本発明によれば、PVG114即ち検査電源は、チップ上または回路内にあり、制御レジスタ120を用いてプログラム可能である。ライン112におけるデータは、制御レジスタ120に入力値を与える。制御レジスタ120は、種々のビット・フィールドを含み、メモリ・アレイ128の読み取り動作の間に用いられるワード・ライン電源電圧を制御する。例えば、1ビット・フィールドのV<sub>T</sub>イネーブル・フィールド119は、行デコーダ電源スイッチ122をイネーブルし、読み取り電源123またはPVG114からの出力を選択するために用いられる。行デコーダ電源スイッチ122からの出力は、行デコーダ130の電源となる。行デコーダ電源スイッチ122から行デコーダ130への電源は、選択されたワード・ライン上に駆動される電圧である。

【0019】

本発明による不揮発性メモリを動作させる方法は、動作電源および検査電源の間で選択を行なうことを含み、検査電源は、チップ上でプログラム可能である。不揮発性メモリは、動作電源ノードが選択された場合動作モードで動作し、検査電源が選択された場合検査モードで動作する。例えば、通常の読み取り動作では、V<sub>T</sub>イネーブル・フィールド119は読み取り電源123の電圧出力即ち動作電源を選択し、行デコーダ130の電源電圧として用いる。検査モード動作では、V<sub>T</sub>イネーブル・フィールド119はPVG114の電圧出力即ち検査電源を選択し、行デコーダ130の電源電圧として用いる。

【0020】

別のビット・フィールド、例えば、ワード・ライン電圧（V<sub>WL</sub>）選択フィールド121は、プログラマブル電圧発生器114の出力電圧を選択するために用いられる。V<sub>WL</sub>選択フィールド121を変更することにより、プログラマブル電圧発生器114の出力電圧を変化させる。検査モード動作では、プログラマブル電圧発生器114の出力電圧を変化させると、ビット・セル126の制御ゲート端子127に供給される電圧も変化する。

【0021】

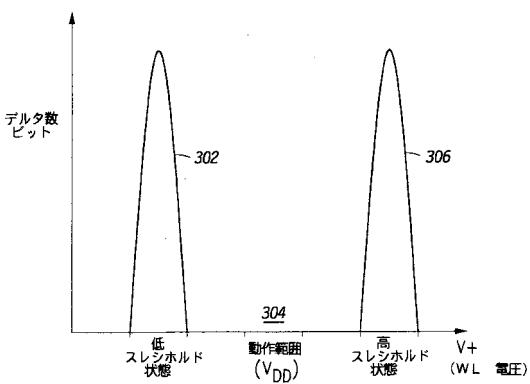

図3は、ワード・ライン電圧に対するビット・セルV<sub>T</sub>の所望の分布曲線300を示す図である。動作範囲304は、通常の読み取り動作の間にビット・セル制御ゲート127に印加される電圧である。高スレシホールド状態即ちプログラム状態にあるビット・セルは曲線306の分布内に位置し、低スレシホールド状態即ち消去状態にあるビット・セルは曲線302の分布内に位置する。高スレシホールド状態の最小値を動作範囲304の最大値から分離し、高スレシホールド状態におけるビット・セルからの信頼性の高い読み取りを保証する。低スレシホールド状態の最小値を動作範囲304の最大値から分離し、低スレシホールド状態におけるビット・セルからの信頼性のある読み取りを保証する。

【0022】

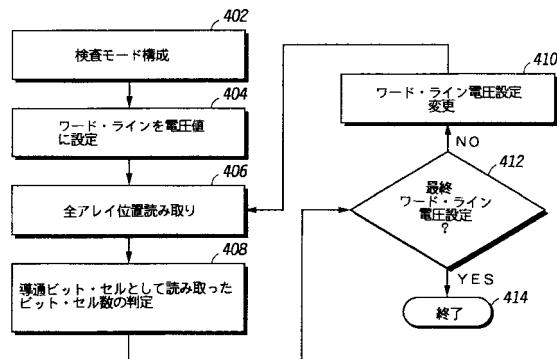

図4は、本発明の一実施例による、メモリ・アレイ内のビット・セルのV<sub>T</sub>分布を判定する方法を示すフロー・チャートである。ここでは、不揮発性メモリ110は検査モードで動作しており、V<sub>T</sub>分布は、例えば、第1電圧値から最終電圧値までの電圧値範囲にわたって測定される。ブロック402において、NVM110は検査モードに構成され、図2においてPVG114として示される検査電源をNVM110に印加し、NVMを検査モードで動作するように構成することを含む。ブロック404において、ワード・ライン電圧を第1電圧値に設定する。メモリ・セル・アレイ128内のビット・セル位置は全て、ブロック406において読み出される。ブロック408において、どのビット・セルが導通状態にあるかについて判定し、更に導通ビット・セルとして読み出すビット・セルの数を判定する。判断ブロック412において、ワード・ライン電圧が最終電圧値にセットされているか否かについて判定を行なう。ワード・ライン電圧が未だ最終電圧値ではない場

10

20

30

40

50

合、フローはブロック410に進み、最終電圧値の方向に検査電源の値の分数だけ、ワード・ライン電圧設定を変化させる。NVM110内のビット・セル・アレイでは、ブロック406において再度読み取りが行われる。ブロック408において、導通ビット・セルとして読み取ったビット・セルの数を判定し、ブロック412においてワード・ライン電圧が最終電圧値に設定されたと判定されるまで、このプロセスを繰り返し、ブロック412においてワード・ライン電圧が最終電圧値に設定されたと判定された場合、プロセスは414において終了する。ワード・ライン電圧を連続的に読み取って変化させ、更に導通状態のビット・セルを判定することにより、またはデータ出力115が状態を変化させたときを判定することにより、データ出力115が状態を変化させた時点において各ビット・セルの $V_T$ を判定することができ、したがって、メモリ・セル128内のビット・セルの $V_T$ の分布を判定することができる。このビット・セルの $V_T$ の分布を判定する方法は、本発明のオン・チップ・プログラマブル回路を用いてウエハ上で多数の素子を一括検査(gang testing)する場合にも適用可能である。

#### 【0023】

ブロック404において、ワード・ライン電圧を第1電圧値に設定するには、更に、制御レジスタ120に第1電圧値を示す第1デジタル値をプログラムすることを含む。ブロック410において、ワード・ライン電圧を変化させるには、更に、制御レジスタ120を次のデジタル値に変更することを含み、これは制御レジスタ120のフィールドを増分することまたは制御レジスタ120のフィールドを減分することを含む可能性がある。ブロック408において、ビット・セルが導通状態にあるか否かについての判定は、更に、どのデータ・セルが導通状態として読み取り、ビット・セルが最初に導通したワード・ライン電圧値を格納したかについて判定すること即ち、導通状態として読み取った各ビット・セル毎に状態の変化を判定することを含む。

#### 【0024】

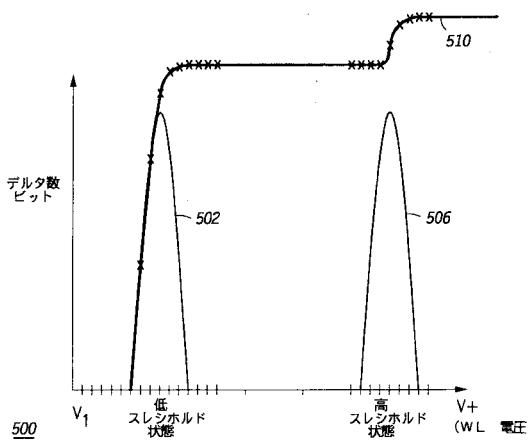

図5は、ワード・ライン電圧に対するビット・セル $V_T$ の分布、および蓄積 $V_T$ 分布を示す図である。高スレシホールド状態即ちプログラム状態にあるビット・セルは、曲線506の分布内に位置し、低スレシホールド状態即ち消去状態にあるビット・セルは曲線502の分布内に位置する。曲線510は、チック・マーク(tic mark)で示される $V_T$ レベルを超過するビット・セルの蓄積数である。

#### 【0025】

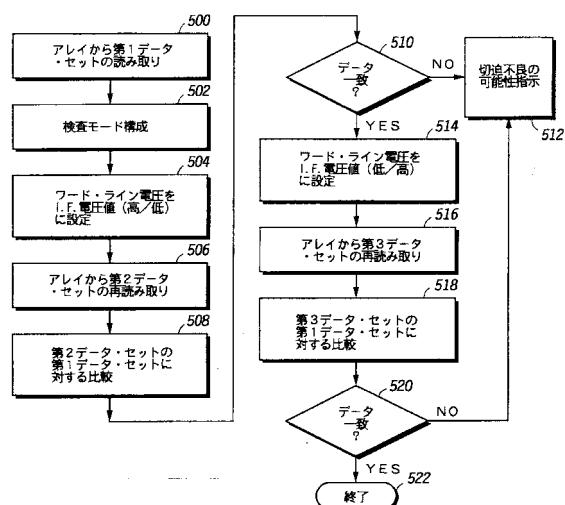

図6は、本発明の別の実施例による切迫不良検出方法を示すフロー・チャートである。本発明の利点の1つは、メモリ・セル・アレイの切迫不良を簡単に、例えば、外部検査プラットフォームを用いることなく、顧客によって検出可能なことにある。本発明による不揮発性メモリ集積回路および動作方法は、並列性が高い環境における自己検査に適しており、容易に切迫不良検出が行なえる。図6は、検査モードにおいて、NVM110の切迫不良を検出する実施例を示す。読み取り電源123として示す動作電源を選択してNVM110に印加し、ブロック500において、動作電源をNVM110に印加した後、ビット・セル・アレイから第1データ・セットを読み取る。ブロック502において、NVM110に対して検査モードを構成する。これは、検査電源を選択しNVM110に印加することを含む。ブロック504において、ワード・ライン電圧を切迫不良電圧値に設定し、次いでブロック506において、ビット・セル・アレイを再度読み取り、ビット・セル・アレイから第2データ・セットを与える。ブロック508において、第1データ・セットを第2データ・セットと比較する。判断ブロック510において判断を行い、第1データ・セットの第2データ・セットに対する比較に基づいて、切迫不良が示されたか否かについて判定する。例えば、第1データ・セットおよび第2データ・セットの比較により、データが一致しないことが示された場合、ブロック512における切迫不良の可能性を示す。

#### 【0026】

第1データ・セットおよび第2データ・セットが一致した場合、切迫不良は示されない。ブロック504において設定された切迫不良電圧値が高電圧値である場合、ブロック510

10

20

30

40

50

4において、ワード・ライン電圧を切迫不良低電圧値に設定する。しかしながら、ブロック504において設定した切迫不良電圧値が切迫不良低電圧値である場合、ブロック514において設定した切迫不良電圧値は高電圧値となる。ブロック516において、第3データ・セットをビット・セル・アレイから読み取る。ブロック518において、第1データ・セットの第3データ・セットと比較し、ブロック520において、第1データ・セットが一致しない場合、ブロック512において切迫不良の可能性が示される。しかしながら、判断ブロック520において、第1データ・セットおよび第3データ・セットが一致した場合、プロセスはブロック522において終了する。第1データ・セット、第2データ・セットおよび第3データ・セットは、動作電源をNVM110に印加した後にビット・セル・アレイから読み取った第1の値、ワード・ライン電圧を切迫不良電圧値に設定した後にビット・セル・アレイから読み取った第2の値、およびワード・ライン電圧を切迫不良電圧値に設定した後にビット・セル・アレイから読み取った第3の値をそれぞれ含むことができる。第1データ・セット、第2データ・セットおよび第3データ・セットは、第1の値のチェックサム、第2の値のチェックサム、および第3の値のチェックサムをそれぞれ含むことも可能である。

10

#### 【0027】

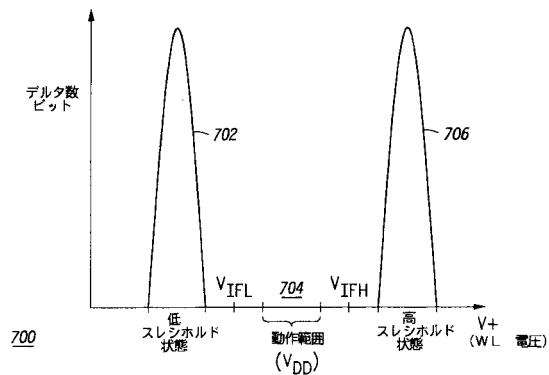

図7は、ワード・ライン電圧に対するビット・セル $V_T$ の分布を示し、更に動作範囲および検出スレシホールド双方を示す図である。動作範囲704は、通常動作の間ビット・セル制御ゲート127に印加される電圧である。高スレシホールド状態即ちプログラム状態のビット・セルは、曲線706の分布内に位置し、低スレシホールド状態即ち消去状態のビット・セルは、曲線702の分布内に位置する。切迫不良低電圧値は、 $V_{IFL}$ として示し、切迫不良高電圧値は $V_{IFH}$ として示す。高電圧または定電圧いずれでも、切迫不良電圧が動作範囲704に近づく程、切迫不良の可能性に対して反応するために許される時間は少なくなる。逆に、切迫不良電圧が動作範囲704から遠ざかる程、切迫不良の可能性に対して反応するために許される時間は長くなる。 $V_{IFL}$ に対する許容範囲は、低スレシホールド状態702の最大値から704の動作範囲の最小値までであり、 $V_{IFH}$ に対する許容範囲は、高スレシホールド状態706の最小値から動作範囲704の最大値までである。

20

#### 【0028】

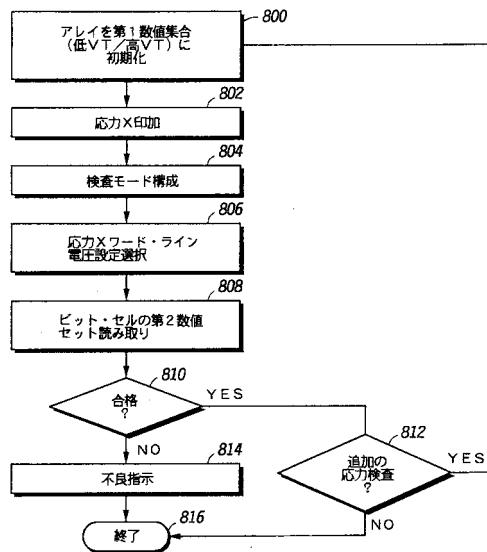

図8は、本発明にしたがって、不揮発性メモリ・アレイ内に含まれるビット・セルの選択応力検査による合格不合格基準を判定する方法を示すフローである。ブロック800において、ビット・セル・アレイを第1数値セットに初期化する。これは、例えば、低 $V_T$ および高 $V_T$ を含む。次にNVM110のビット・セル・アレイに応力を印加する。応力は、例えば、温度加速応力および電圧加速応力、またはこれらの応力の組み合わせを含む。ブロック804において、検査電源を選択し、これをNVM110に印加することによって、NVM110を検査モードに構成する。ブロック806において、ワード・ライン電圧を応力マージン電圧値に設定する。次に、ブロック808において、ワード・ライン電圧を応力マージン電圧値に設定した後に、ビット・セル・アレイから第2数値セットを読み取る。応力マージン電圧値は、通常電圧値と低スレシホールド状態または高スレシホールド状態のいずれかのスレシホールド状態との間の範囲において選択する。判断ブロック810において、第1数値セットを第2数値セットと比較し、第1数値セットの第2数値セットに対する比較に基づいて、応力不良が示されているか否かについて判定を行い、合格／不合格基準を与える。NVM110が応力検査に合格しなかった場合、ブロック814において不良を示し、プロセスはブロック816において終了する。NVM110が応力検査に合格した場合、判断ブロック812において追加の応力検査を選択することができ、その場合プロセスはブロック800に戻り、NVM110アレイを初期化し、ブロック802において新たな応力を加える。ブロック810において、例えば、第1数値セットおよび第2数値セットの比較により、第1数値セットおよび第2数値セットが一致しないことが示された場合、ブロック814において、例えば、応力不良が示される。応力不良を判

40

50

定するステップは、本発明のオン・チップ・プログラマブル回路を用いて、ウェハ上における多数の素子の一括検査にも適用することができる。

【0029】

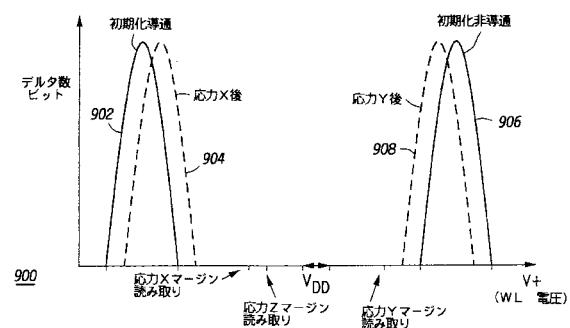

図9は、ワード・ライン電圧に対するビット・セル $V_T$ の分布を示し、選択した応力検査に対する不良レベルを示す図である。初期化導通状態におけるビット・セルは、曲線902の分布内に位置することが示されている。応力X、応力Yおよび応力Zに対する応力マージンの読み取りは、ワード・ライン電圧値上にも示されている。応力XをNVM110のビット・セルに印加した後、ビット・セルは曲線904の分布内に位置することが示されている。ビット・セルのデータ値は、分布曲線904によって予期されかつ図示されたように移動しなければならない。さもないと、応力Xに対する不良が示される。非導通即ち高 $V_T$ 状態に初期化されたビット・セルは、曲線906の分布内に位置し、応力Yを加えた後、曲線908の分布内に位置しなければならない。さもないと、応力Yに対する応力不良が示される。

10

【0030】

図4、図6および図8は、本発明の一実施例によるモジュールの動作、ならびに不揮発性メモリ・モジュールの動作および検査方法のフロー・チャートを示す。ここで論ずる動作は、コンピュータ・システムのユーザによって、または特定用途ハードウェア・モジュールによって実行されるステップによって直接入力されるコマンドで構成することができるが、好適実施例はソフトウェア・モジュールによって実行されるステップを含むことは認められよう。ここで言及するステップの機能性は、モジュールまたはモジュールの一部の機能性に対応する。

20

【0031】

ここで言及する動作は、モジュールまたはモジュールの一部（例えば、ソフトウェア、ファームウェアまたはハードウェア・モジュール）とすることも可能である。例えば、ここに記載する実施例はソフトウェア・モジュールおよび/または手作業で入力するユーザ・コマンドを含むが、種々のモジュール例としては、特定用途ハードウェア・モジュールも可能である。ここで論ずるソフトウェア・モジュールは、スクリプト、バッチまたはその他の実行可能ファイル、あるいはかかるファイルの組み合わせおよび/または一部を含むことも可能である。ソフトウェア・モジュールは、コンピュータ読み取り可能媒体上にエンコードされたプログラム、またはそのサブルーチンを含むことができる。例えば、本発明は、不揮発性メモリへのアクセスを制御する、コンピュータ・プログラム生産物をエンコードしたコンピュータ読み取り可能媒体を含むことができる。コンピュータ・プログラム生産物は、第1データ処理システム上で実行可能であり、動作電源ノードおよび検査電源ノード間で選択するための第1命令を含み、検査電源ノードは、チップ上でプログラム可能である。第2命令は、第1データ処理システム上で実行可能であり、動作電源ノードが選択された場合、不揮発性メモリを動作モードで動作させる。第3命令は、第1データ処理システム上で実行可能であり、検査電源ノードが選択された場合、不揮発性メモリを検査モードで動作させる。

30

【0032】

加えて、モジュール間の境界は単に例示に過ぎず、代替実施例では、モジュールの併合や、あるいは代わりにモジュールの機能性の分解も可能であることを当業者は認めよう。更に、代替実施例では、特定のモジュールまたはサブモジュールの多数のインスタンスを組み合わせることも可能である。更に又、代表的な実施例に記載した動作は例示のために過ぎないことも当業者は認めよう。本発明にしたがって、動作を組み合わせたり、あるいは動作の機能性を追加の動作内に分散することも可能である。更に、回路図内の回路要素および論理ブロック間の境界は単に例示に過ぎないこと、および代替実施例では、論理回路または回路要素の併合、あるいは代わりに種々の論理ブロックまたは回路要素上における機能性の分解も可能であることを当業者は認めよう。

40

【0033】

前述の説明は、本発明の実施例を余すことなく網羅したリストを提示することを意図した

50

ものではない。代表的な実施例の一部およびその代表的な変形について概要を説明しようとしたのであるが、他の実施例および／または変形も、特許請求の範囲内に規定した本発明の範囲に含まれることとする。

【図面の簡単な説明】

【図1】埋め込み不揮発性メモリ・モジュールを含むマイクロコントローラの機能ブロック図。

【図2】本発明による不揮発性メモリ・モジュールの機能ブロック図。

【図3】ピット・セルのスレシホールド電圧( $V_T$ )のワード・ライン電圧に対する分布を示す図。

【図4】本発明によるメモリ・アレイ内におけるピット・セルの $V_T$ 分布を判定する方法を示すフロー・チャート。 10

【図5】ワード・ライン電圧に対するピット・セルのスレシホールド電圧( $V_T$ )の分布、および蓄積 $V_T$ 分布を示す図。

【図6】本発明による切迫不良検出方法を示すフロー・チャート。

【図7】ワード・ライン電圧に対するピット・セルの $V_T$ の分布を示し、動作範囲および検出スレシホールド双方を示す図。

【図8】本発明にしたがってメモリ・セル内に含まれるピット・セルの選択応力検査による合格／不合格基準を決定する方法を示すフロー・チャート。

【図9】ワード・ライン電圧に対するピット・セル $V_T$ の分布を示し、選択応力検査に対する不良レベルを示す図。 20

【符号の説明】

|       |                          |    |

|-------|--------------------------|----|

| 1 0 0 | マイクロコントローラ               |    |

| 1 0 2 | 中央演算装置(CPU)              |    |

| 1 0 4 | システム・バス                  |    |

| 1 0 6 | 外部バス・インターフェース            |    |

| 1 0 8 | 外部バス                     |    |

| 1 1 0 | 埋め込み不揮発性メモリ(NVM)         |    |

| 1 1 2 | データ入力ライン                 |    |

| 1 1 3 | アドレス・ライン                 |    |

| 1 1 4 | オン・チップ・プログラマブル電圧発生器(PVG) | 30 |

| 1 1 5 | データ出力ライン                 |    |

| 1 1 9 | $V_T$ イネーブル・フィールド        |    |

| 1 2 0 | 制御レジスタ                   |    |

| 1 2 1 | $V_{WL}$ 選択フィールド         |    |

| 1 2 2 | 行デコーダ電源スイッチ              |    |

| 1 2 3 | 動作読み取り電源                 |    |

| 1 2 6 | ピット・セル                   |    |

| 1 2 7 | 制御ゲート端子                  |    |

| 1 2 8 | アレイ                      |    |

| 1 2 9 | ドレイン端子                   | 40 |

| 1 3 0 | 行デコーダ                    |    |

| 1 3 1 | ソース端子                    |    |

| 1 3 2 | 列デコーダ                    |    |

| 1 3 4 | 列選択部                     |    |

| 1 3 8 | センス・アンプ・モジュール            |    |

| 1 4 0 | センス・アンプ                  |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(51)Int.Cl. F I

**G 1 1 C 16/06 (2006.01)** G 1 1 C 17/00 6 0 1 Z

G 1 1 C 17/00 6 3 2 C

G 1 1 C 17/00 6 3 3 B

(72)発明者 トーマス・ジュー

アメリカ合衆国テキサス州オースチン、アイダリア・ドライブ4020

審査官 小林 紀和

(56)参考文献 特開平06-012900 (JP, A)

特開昭63-229700 (JP, A)

特開平09-320300 (JP, A)

特開平06-176585 (JP, A)

特開平08-297987 (JP, A)

特開平08-077785 (JP, A)

特開平08-315598 (JP, A)

特開2001-167588 (JP, A)

特開2001-266599 (JP, A)

特開2000-215700 (JP, A)

特開平01-116999 (JP, A)

特開2000-173300 (JP, A)

特開平10-241400 (JP, A)

特開2000-90675 (JP, A)

特開昭62-1194 (JP, A)

特開平11-134317 (JP, A)

特開平11-134884 (JP, A)

特開平11-175501 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 29/12

G01R 31/28

G06F 12/16

G11C 16/02

G11C 16/06

G11C 29/02