(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6740986号

(P6740986)

(45) 発行日 令和2年8月19日(2020.8.19)

(24) 登録日 令和2年7月29日(2020.7.29)

|               |           |        |       |         |

|---------------|-----------|--------|-------|---------|

| (51) Int.Cl.  | F 1       |        |       |         |

| HO 1 L 29/78  | (2006.01) | HO 1 L | 29/78 | 6 5 2 B |

| HO 1 L 29/12  | (2006.01) | HO 1 L | 29/78 | 6 5 3 C |

| HO 1 L 21/336 | (2006.01) | HO 1 L | 29/78 | 6 5 2 T |

| HO 1 L 21/205 | (2006.01) | HO 1 L | 29/78 | 6 5 2 H |

|               |           | HO 1 L | 29/78 | 6 5 8 E |

請求項の数 9 (全 21 頁) 最終頁に続く

|           |                              |                 |           |

|-----------|------------------------------|-----------------|-----------|

| (21) 出願番号 | 特願2017-166883 (P2017-166883) | (73) 特許権者       | 000004260 |

| (22) 出願日  | 平成29年8月31日 (2017.8.31)       | 株式会社デンソー        |           |

| (65) 公開番号 | 特開2019-46909 (P2019-46909A)  | 愛知県刈谷市昭和町1丁目1番地 |           |

| (43) 公開日  | 平成31年3月22日 (2019.3.22)       | (73) 特許権者       | 000003207 |

| 審査請求日     | 令和1年10月29日 (2019.10.29)      | トヨタ自動車株式会社      |           |

|           |                              | 愛知県豊田市トヨタ町1番地   |           |

|           |                              | (73) 特許権者       | 000003609 |

|           |                              | 株式会社豊田中央研究所     |           |

|           |                              | 愛知県長久手市横道41番地の1 |           |

|           |                              | (74) 代理人        | 110001128 |

|           |                              | 特許業務法人ゆうあい特許事務所 |           |

|           |                              | (72) 発明者        | 梶 愛子      |

|           |                              | 愛知県刈谷市昭和町1丁目1番地 | 株式会社デンソー内 |

最終頁に続く

(54) 【発明の名称】炭化珪素半導体装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

反転型の半導体素子を備えている炭化珪素半導体装置であって、炭化珪素で構成された第1または第2導電型の基板(1)と、前記基板の上に形成され、前記基板よりも低不純物濃度とされた第1導電型の炭化珪素からなるドリフト層(2、3、5)と、

前記ドリフト層の上に形成された第2導電型の炭化珪素からなるベース領域(6)と、前記ベース領域の上に形成され、前記ドリフト層よりも第1導電型不純物濃度が高くされた第1導電型の炭化珪素からなるソース領域(8)と、

前記ソース領域の表面から前記ベース領域よりも深く形成されたゲートトレンチ(11)内に、該ゲートトレンチの内壁面を覆うゲート絶縁膜(12)と該ゲート絶縁膜の上に配置されたゲート電極(13)とを備えて構成され、一方向を長手方向として複数本がストライプ状に並べられたトレンチゲート構造と、

前記ゲート電極および前記ゲート絶縁膜を覆うと共にコンタクトホールが形成された層間絶縁膜(14)と、

前記コンタクトホールを通じて、前記ソース領域にオーミック接触させられたソース電極(15)と、

前記基板の裏面側に形成されたドレイン電極(16)と、を含む前記半導体素子を備え、

前記ソース領域は、前記ベース領域側の方が前記ソース電極にオーミック接触させられ

10

20

る表面側よりも低不純物濃度で構成されており、

前記ベース領域と前記ソース領域との間には、キャリア濃度が  $5.0 \times 10^{15} / \text{cm}^3$  以下とされたノンドープ層(7)が備えられている炭化珪素半導体装置。

【請求項 2】

前記ソース領域は、前記ベース領域側に位置する第1ソース領域(8a)と前記ソース電極にオーミック接触させられる第2ソース領域(8b)とを有した構成とされている請求項1に記載の炭化珪素半導体装置。

【請求項 3】

前記第2ソース領域は、厚さが  $0.1 \mu\text{m}$  以上とされていると共に、第2導電型不純物濃度が  $1.0 \times 10^{18} \sim 5.0 \times 10^{19} / \text{cm}^3$  とされている請求項2に記載の炭化珪素半導体装置。

10

【請求項 4】

前記第1ソース領域は、厚さが  $0.2 \sim 0.5 \mu\text{m}$  とされ、不純物濃度が  $2.0 \times 10^{16} \sim 1.0 \times 10^{17} / \text{cm}^3$  とされている請求項2または3に記載の炭化珪素半導体装置。

【請求項 5】

前記ノンドープ層は、厚さが  $0.05 \sim 0.2 \mu\text{m}$  とされている請求項1ないし4のいずれか1つに記載の炭化珪素半導体装置。

【請求項 6】

前記ノンドープ層および前記ソース領域の合計膜厚が  $0.8 \mu\text{m}$  以下とされている請求項1ないし5のいずれか1つに記載の炭化珪素半導体装置。

20

【請求項 7】

反転型の半導体素子を備えた炭化珪素半導体装置の製造方法であって、

炭化珪素で構成された第1または第2導電型の基板(1)を用意することと、

前記基板の上に、前記基板よりも低不純物濃度の第1導電型の炭化珪素からなるドリフト層(2、3、5)を形成することと、

前記ドリフト層の上に、第2導電型の炭化珪素からなるベース領域(6)を形成することと、

前記ベース領域の上に、前記ドリフト層よりも第1導電型不純物濃度が高くされた第1導電型の炭化珪素からなるソース領域(8)を形成することと、

30

前記ソース領域の表面から前記ベース領域よりも深いゲートトレンチ(11)を、一方を長手方向としてストライプ状に複数本形成したのち、前記ゲートトレンチの内壁面にゲート絶縁膜(12)を形成すると共に、前記ゲート絶縁膜の上にゲート電極(13)を形成することでトレンチゲート構造を形成することと、

前記ソース領域に電気的に接続されるソース電極(15)を形成することと、

前記基板の裏面側にドレイン電極(16)を形成することと、を含み、

前記ベース領域を形成すること、および、前記ソース領域を形成することでは、前記ベース領域および前記ソース領域をエピタキシャル成長によって形成し、

前記ソース領域を形成することでは、前記ベース領域側より第1導電型不純物濃度が異なる第1ソース領域(8a)と前記ソース電極にオーミック接触させられる第2ソース領域(8b)とを順にエピタキシャル成長によって形成し、前記第1ソース領域を前記第2ソース領域よりも低不純物濃度で形成する炭化珪素半導体装置の製造方法。

40

【請求項 8】

前記ベース領域を形成すること、および、前記ソース領域を形成することとの間に、炭化珪素で構成されるノンドープ層(7)を形成することを含み、

前記ベース領域を形成することと前記ノンドープ層を形成すること、および、前記ソース領域を形成することを連続的にエピタキシャル成長によって行い、

前記ノンドープ層を形成することでは、第1導電型ドーパントおよび第2導電型ドーパントのガス導入を停止した状態で前記エピタキシャル成長を行うことで、前記ノンドープ層を厚さ  $0.05 \sim 0.2 \mu\text{m}$  で形成する請求項7に記載の炭化珪素半導体装置の製造方

50

法。

【請求項 9】

前記ノンドープ層を形成すること、および、前記ソース領域を形成することのち、前記ソース領域の表面側から第2導電型不純物をイオン注入することで、前記ベース領域に達して、該ベース領域と前記ソース電極とを連結する第2導電型の連結層(10)を形成することを含み、

前記連結層を形成することでは、前記連結層のうち前記第1ソース領域に対して前記第2導電型不純物をイオン注入する部分を第1領域(10a)とし、前記第2ソース領域に対して前記第2導電型不純物をイオン注入する部分を第2領域(10b)として、前記第2ソース領域の第1導電型不純物濃度の2~10倍のドーズ量で前記第2導電型不純物をイオン注入したのち、1500以上<sup>10</sup>の熱処理によって活性化することで前記第2領域を形成することを含んでいる請求項8に記載の炭化珪素半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、炭化珪素(以下、SiCという)にて構成されるMOS構造の半導体素子を有したSiC半導体装置およびその製造方法に関する。

【背景技術】

【0002】

従来より、大電流が流せるようにチャネル密度を高くした構造として、トレンチゲート構造を有するSiC半導体装置がある。このSiC半導体装置は、n型ドリフト層の上にp型ベース領域とn<sup>+</sup>型ソース領域とが順に形成され、n<sup>+</sup>型ソース領域の表面からp型ベース領域を貫通してn<sup>+</sup>型ドリフト層に達するようにトレンチゲートが形成された構造とされる。具体的には、n型ドリフト層の上にp型ベース領域をエピタキシャル成長させたのち、p型ベース領域に対してn型不純物をイオン注入で打ち返すことでp型ベース領域の一部をn型に反転させ、n<sup>+</sup>型ソース領域を形成している(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】国際公開第2016/063644号パンフレット

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、n<sup>+</sup>型ソース領域の全域を高濃度のn型不純物層によって形成しているため、負荷短絡時の飽和電流値が大きくなり、SiC半導体装置の短絡耐量を得ることができない。

【0005】

本発明は上記点に鑑みて、短絡耐量を向上することが可能なSiC半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

上記目的を達成するため、請求項1に記載のSiC半導体装置は、SiCで構成された第1または第2導電型の基板(1)と、基板の上に形成され、基板よりも低不純物濃度とされた第1導電型のSiCからなるドリフト層(2、3、5)と、ドリフト層の上に形成された第2導電型のSiCからなるベース領域(6)と、ベース領域の上に形成され、ドリフト層よりも第1導電型不純物濃度が高くされた第1導電型のSiCからなるソース領域(8)と、ソース領域の表面からベース領域よりも深く形成されたゲートトレンチ(11)内に、該ゲートトレンチの内壁面を覆うゲート絶縁膜(12)と該ゲート絶縁膜の上に配置されたゲート電極(13)とを備えて構成され、一方向を長手方向として複数本が

10

20

30

40

50

ストライプ状に並べられたトレンチゲート構造と、ゲート電極およびゲート絶縁膜を覆うと共にコンタクトホールが形成された層間絶縁膜(14)と、コンタクトホールを通じて、ソース領域にオーミック接触させられたソース電極(15)と、基板の裏面側に形成されたドレイン電極(16)と、を含む半導体素子を備えている。そして、ソース領域は、ベース領域側の方がソース電極にオーミック接触させられる表面側よりも低不純物濃度で構成されている。

【0007】

このように、ソース領域のうちのベース領域側を低濃度とし、ソース電極側をそれよりも高濃度とている。このように、ソース領域のうちのベース領域側に低濃度となる領域を備えることで、負荷短絡時の飽和電流値を小さくすることが可能となり、SiC半導体装置の短絡耐量を向上させることが可能となる。

10

【0008】

なお、上記各手段の括弧内の符号は、後述する実施形態に記載の具体的手段との対応関係の一例を示すものである。

【図面の簡単な説明】

【0009】

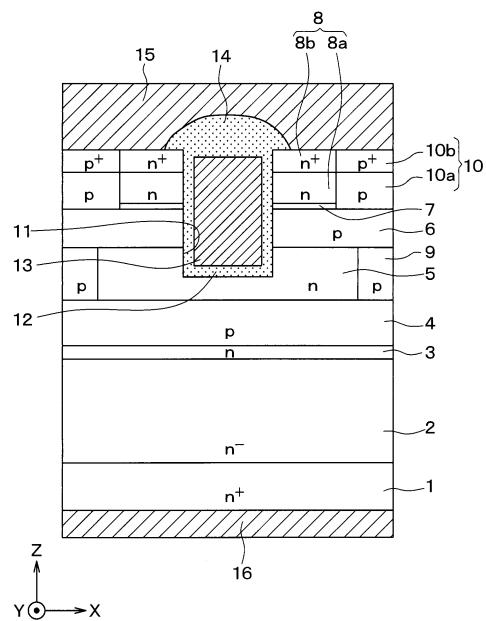

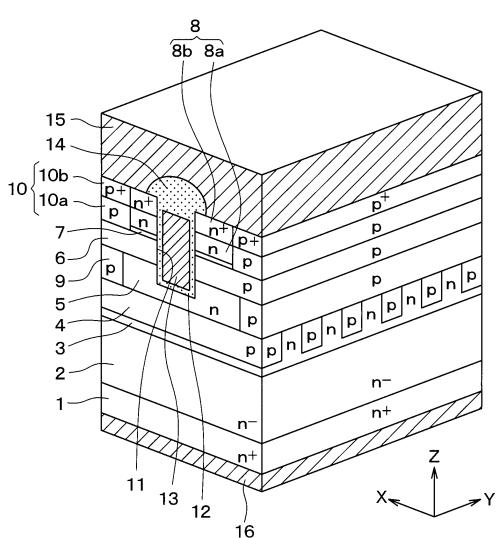

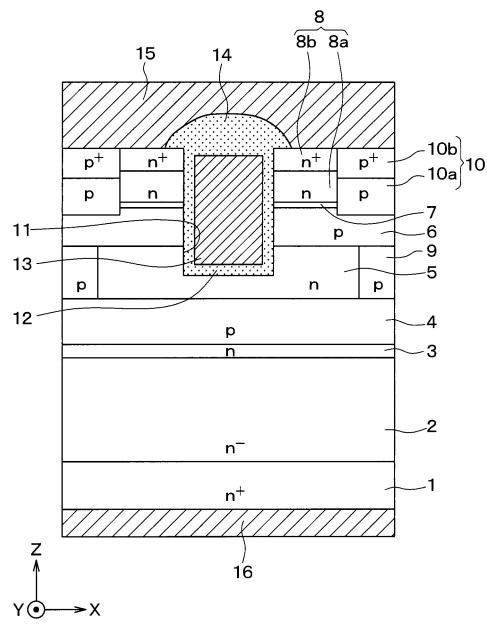

【図1】第1実施形態にかかるSiC半導体装置の上面レイアウト図である。

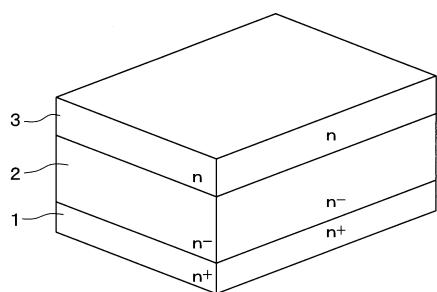

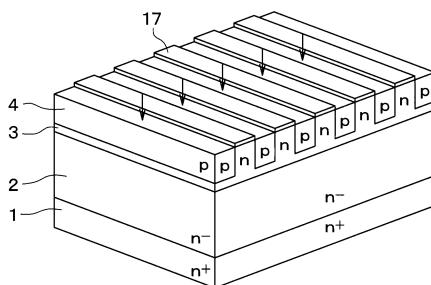

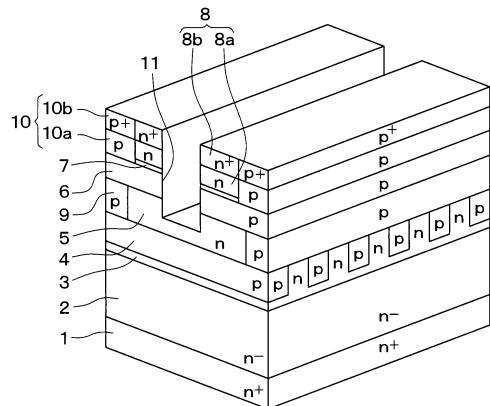

【図2】図1に示すSiC半導体装置の斜視断面図である。

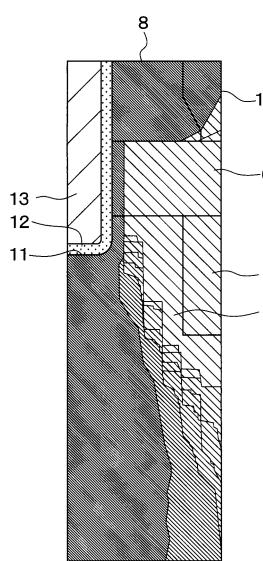

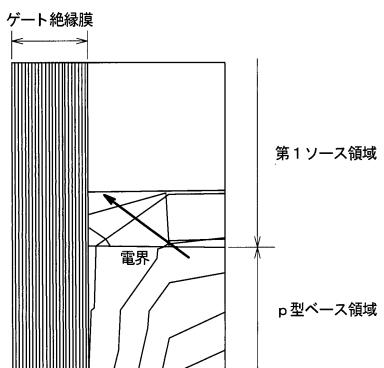

【図3】n型ソース領域の全域を高濃度とした場合の電子電流密度をシミュレーションにより調べた結果を示す図である。

20

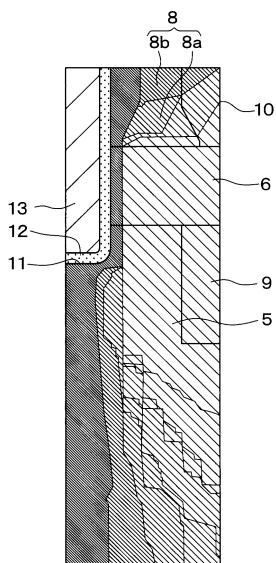

【図4】n型ソース領域を第1ソース領域および第2ソース領域で構成した場合の電子電流密度をシミュレーションにより調べた結果を示す図である。

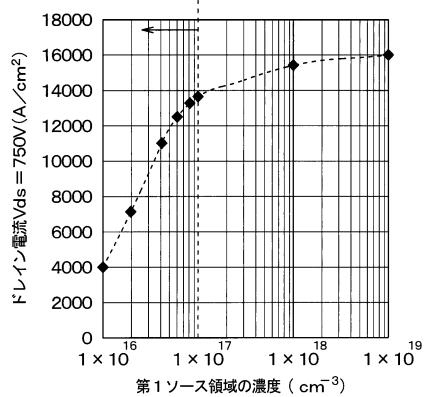

【図5】第1ソース領域の不純物濃度を変化させて、ドレイン電流の変化をシミュレーションにより調べた結果を示す図である。

【図6】第1ソース領域のn型不純物濃度とオン抵抗との関係についてシミュレーションにより調べた結果を示す図である。

【図7】n型ソース領域の全域を高不純物濃度とした場合について、逆導通時の電圧分布を調べた結果を示した図である。

【図8】第1ソース領域をp型ベース領域に接するように形成した場合について、逆導通時の電圧分布を調べた結果を示した図である。

30

【図9】ノンドープ層を備えた場合について、逆導通時の電圧分布を調べた結果を示した図である。

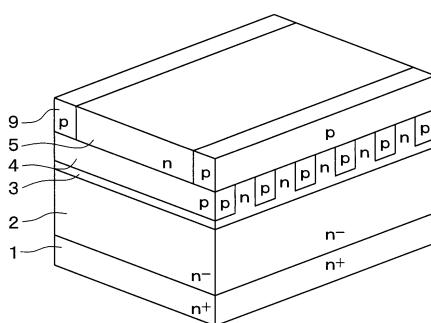

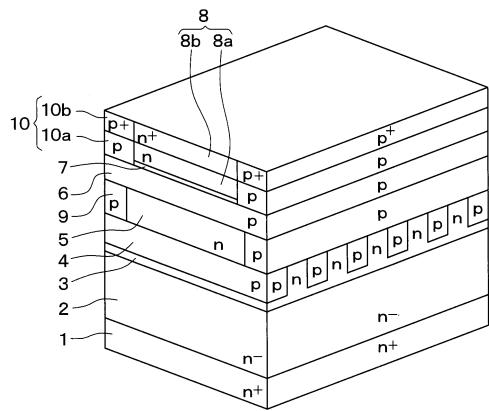

【図10A】図1に示すSiC半導体装置の製造工程を示した斜視断面図である。

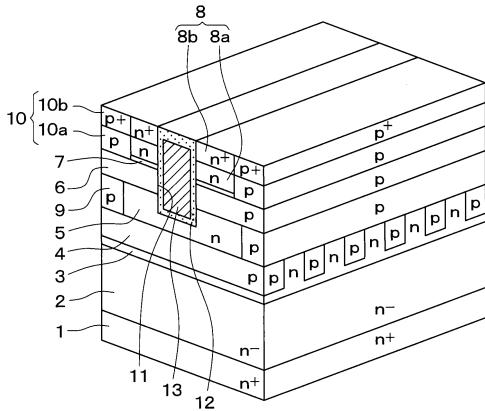

【図10B】図10Aに続くSiC半導体装置の製造工程を示した斜視断面図である。

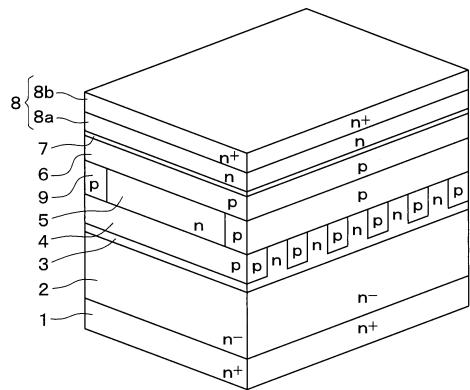

【図10C】図10Bに続くSiC半導体装置の製造工程を示した斜視断面図である。

【図10D】図10Cに続くSiC半導体装置の製造工程を示した斜視断面図である。

【図10E】図10Dに続くSiC半導体装置の製造工程を示した斜視断面図である。

【図10F】図10Eに続くSiC半導体装置の製造工程を示した斜視断面図である。

【図10G】図10Fに続くSiC半導体装置の製造工程を示した斜視断面図である。

【図11】他の実施形態で説明するSiC半導体装置の断面図である。

40

【発明を実施するための形態】

【0010】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、同一符号を付して説明を行う。

【0011】

(第1実施形態)

第1実施形態について説明する。本実施形態にかかるSiC半導体装置は、半導体素子として、図1および図2に示すトレンチゲート構造の反転型の縦型MOSFETが形成されたものである。これらの図に示す縦型MOSFETは、SiC半導体装置のうちのセル領域に形成されており、そのセル領域を囲むように外周耐圧構造が形成されることでSi

50

C 半導体装置が構成されているが、ここでは縦型MOSFETのみ図示してある。なお、以下では、図1および図2に示すように、縦型MOSFETの幅方向をX方向、X方向に對して交差する縦型MOSFETの奥行方向をY方向、縦型MOSFETの厚み方向もしくは深さ方向、つまりXY平面に対する法線方向をZ方向として説明する。

【0012】

図1および図2に示されるように、SiC半導体装置には、SiCからなるn<sup>+</sup>型基板1が半導体基板として用いられている。n<sup>+</sup>型基板1の主表面上にSiCからなるn<sup>-</sup>型層2が形成されている。n<sup>+</sup>型基板1は、表面が(0001)Si面とされ、例えばn型不純物濃度が $5.9 \times 10^{18} / \text{cm}^3$ とされ、厚さが $100 \mu\text{m}$ とされている。n<sup>-</sup>型層2は、例えばn型不純物濃度が $7.0 \times 10^{15} \sim 1.0 \times 10^{16} / \text{cm}^3$ とされ、厚さが $8.0 \mu\text{m}$ とされている。

10

【0013】

n<sup>-</sup>型層2の上には、SiCからなるJFET部3と電界ブロック層4が形成されており、n<sup>-</sup>型層2は、n<sup>+</sup>型基板1から離れた位置においてJFET部3と連結されている。

【0014】

JFET部3と電界ブロック層4は、飽和電流抑制層を構成するものであり、共に、X方向に延設され、Y方向において交互に繰り返し並べられて配置されている。つまり、n<sup>+</sup>型基板1の主表面に対する法線方向から見て、JFET部3の少なくとも一部と電界ブロック層4は、それぞれ複数の短冊状、つまりストライプ状とされ、それが交互に並べられたレイアウトとされている。

20

【0015】

なお、本実施形態の場合、JFET部3が電界ブロック層4よりも下方まで形成されたものとされている。このため、JFET部3のうちストライプ状とされている部分は電界ブロック層4の下方において連結した状態になっているが、ストライプ状とされている各部はそれぞれ複数の電界ブロック層4の間に配置された状態となっている。

【0016】

JFET部3のうちストライプ状とされている部分の各部、つまり各短冊状の部分は、幅が例えば $0.25 \mu\text{m}$ 、形成間隔となるピッチが例えば $0.6 \sim 2.0 \mu\text{m}$ とされている。また、JFET部3の厚みは、例えば $1.5 \mu\text{m}$ とされており、n型不純物濃度は、n<sup>-</sup>型層2よりも高くされていて、例えば $5.0 \times 10^{17} \sim 2.0 \times 10^{18} / \text{cm}^3$ とされている。

30

【0017】

電界ブロック層4は、p型不純物層によって構成されている。上記したように、電界ブロック層4は、ストライプ状とされており、ストライプ状とされた電界ブロック層4の各短冊状の部分は、幅が例えば $0.15 \mu\text{m}$ 、厚みが例えば $1.4 \mu\text{m}$ とされている。また、電界ブロック層4は、例えばp型不純物濃度が $3.0 \times 10^{17} \sim 1.0 \times 10^{18} / \text{cm}^3$ とされている。本実施形態の場合、電界ブロック層4は、深さ方向においてp型不純物濃度が一定とされている。また、電界ブロック層4は、n<sup>-</sup>型層2と反対側の表面がJFET部3の表面と同一平面とされている。

40

【0018】

さらに、JFET部3および電界ブロック層4の上には、SiCからなるn型電流分散層5が形成されている。n型電流分散層5は、後述するようにチャネルを通じて流れる電流がX方向に拡散できるようにする層であり、例えば、n<sup>-</sup>型層2よりもn型不純物濃度が高くされている。本実施形態では、n型電流分散層5は、Y方向に向けて延設されており、n型不純物濃度がJFET部3と同じかそれよりも高くされ、例えば厚みが $0.5 \mu\text{m}$ とされている。

【0019】

なお、ここでは、ドリフト層を、便宜的にn<sup>-</sup>型層2、JFET部3およびn型電流分散層5に分けて説明しているが、これらは共にドリフト層を構成する部分であり、互いに

50

連結されている。

【0020】

n型電流分散層5の上にはSiCからなるp型ベース領域6が形成されている。また、p型ベース領域6の上には、SiCからなるノンドープ層7が形成され、さらにその上にはn型ソース領域8が形成されている。n型ソース領域8は、p型ベース領域6のうちn型電流分散層5と対応する部分の上に形成されている。

【0021】

p型ベース領域6は、電界ブロック層4よりも厚みが薄く、かつ、p型不純物濃度が低くされており、例えばp型不純物濃度が $3 \times 10^{17} / \text{cm}^3$ とされ、厚さが $0.4 \sim 0.6 \mu\text{m}$ とされている。

10

【0022】

ノンドープ層7は、不純物をドープしていない層、もしくは、n型不純物およびp型不純物を共にドープすることでキャリア濃度を低くした層である。ノンドープ層7の厚みは、 $0.05 \sim 0.2 \mu\text{m}$ とされている。ノンドープ層7は、n型不純物およびp型不純物が共にドープされていないのが好ましいが、ドープされていたとしても、キャリア濃度が $5.0 \times 10^{15} / \text{cm}^3$ 以下とされていれば良い。例えば、ノンドープ層7は、窒素(N)などのn型不純物が $1.0 \times 10^{16} / \text{cm}^3$ 以下、好ましくは $1.0 \times 10^{15} / \text{cm}^3$ 以下とされ、アルミニウム(Al)などのp型不純物が $1.0 \times 10^{16} / \text{cm}^3$ 以下、好ましくは $1.0 \times 10^{15} / \text{cm}^3$ 以下とされている。そして、p型不純物とn型不純物の一方のみがドープされている場合には、不純物濃度が $5.0 \times 10^{15} / \text{cm}^3$ 以下とされ、両方がドープされている場合には、互いに打ち消しあうことでキャリア濃度が $5.0 \times 10^{15} / \text{cm}^3$ 以下となっている。

20

【0023】

n型ソース領域8は、ノンドープ層7およびp型ベース領域6側とこれらとは反対側、つまり素子表面側とでn型不純物濃度が異なった構造とされている。具体的には、n型ソース領域8は、ノンドープ層7やp型ベース領域6側に配置された第1ソース領域8aと、素子表面側に配置された第2ソース領域8bとを有した構成とされている。

【0024】

第1ソース領域8aは、第2ソース領域8bよりもn型不純物濃度が低くされており、本実施形態の場合はノンドープ層7と接している。第1ソース領域8aは、例えばn型不純物濃度が $2.0 \times 10^{16} \sim 1.0 \times 10^{17} / \text{cm}^3$ 以下とされ、厚みが $0.2 \sim 0.5 \mu\text{m}$ 、好ましくは $0.3 \mu\text{m}$ 以上とされている。

30

【0025】

第2ソース領域8bは、後述するソース電極15とのコンタクトを取るための領域であり、n型不純物が高濃度とされている。第2ソース領域8bは、例えばn型不純物濃度が $1.0 \times 10^{18} \sim 5.0 \times 10^{19} / \text{cm}^3$ とされ、厚みが $0.1 \sim 0.2 \mu\text{m}$ とされている。

【0026】

また、p型ベース領域6から下方に向けて、具体的にはJFET部3と電界ブロック層4の表面からp型ベース領域6の間であって、n型電流分散層5が形成されていない部分に、p型ディープ層9が形成されている。本実施形態では、p型ディープ層9は、JFET部3のうちのストライプ状の部分や電界ブロック層4の長手方向に対して交差する方向、ここではY方向を長手方向とした短冊状とされ、X方向に複数本並べられることでストライプ状にレイアウトされている。このp型ディープ層9を通じて、p型ベース領域6や電界ブロック層4が電気的に接続されている。p型ディープ層9の形成ピッチは、後述するトレンチゲート構造の形成間隔となるセルピッチと合わせてあり、隣り合うトレンチゲート構造の間にp型ディープ層9が配置されるようにしてある。

40

【0027】

さらに、p型ベース領域6上のうちp型ディープ層9と対応する位置、換言すればn型ソース領域8と異なる位置であってn型ソース領域8を挟んでトレンチゲート構造と反対

50

側の位置に、p型連結層10が形成されている。p型連結層10は、p型ベース領域6と後述するソース電極15とを連結することで電気的に接続するための層である。本実施形態では、p型連結層10は、p型ベース領域6側とその反対側、つまり素子表面側とでp型不純物濃度が異なった構造とされている。具体的には、p型連結層10は、p型ベース領域6側に配置された第1領域10aと、素子表面側に配置された第2領域10bとを有した構成とされている。

#### 【0028】

第1領域10aは、第1ソース領域8aと同程度もしくは、より深く構成され、第2領域10bよりもp型不純物濃度が低くされていて、p型ベース領域6と接した構造とされている。第1領域10aは、例えばp型不純物濃度が $2.0 \times 10^{17} \sim 1.0 \times 10^{19} / \text{cm}^3$ とされ、厚みが $0.2 \sim 0.5 \mu\text{m}$ 、好ましくは $0.3 \mu\text{m}$ 以上とされている。ただし、本実施形態の場合、第1領域10aを第1ソース領域8aへのイオン注入によって形成していることから、キャリア濃度、つまりキャリアとして機能する分のp型不純物濃度が $2.0 \times 10^{17} \sim 1.0 \times 10^{19} / \text{cm}^3$ となるようにしている。

#### 【0029】

第2領域10bは、第2ソース領域8bと同程度の深さで構成され、後述するソース電極15とのコンタクトを取るための領域であり、p型不純物が高濃度とされている。第2領域10bは、例えばp型不純物濃度が $2.0 \times 10^{18} \sim 1.0 \times 10^{20} / \text{cm}^3$ とされ、厚みが $0.2 \sim 0.3 \mu\text{m}$ とされている。ただし、本実施形態の場合、第2領域10bを第2ソース領域8bへのイオン注入によって形成していることから、キャリア濃度、つまりキャリアとして機能する分のp型不純物濃度が $2.0 \times 10^{18} \sim 1.0 \times 10^{20} / \text{cm}^3$ となるようにしている。

#### 【0030】

なお、後述するように、本実施形態では、n型ソース領域8へのp型不純物のイオン注入によってp型連結層10を形成している。その場合、第1領域10aや第2領域10bのp型不純物濃度は、p型不純物のうちキャリアとして機能する分の濃度のことを意味する。p型不純物のうち、打ち込み前の第1ソース領域8aに含まれているn型不純物とキャンセルされて、キャリアとしては機能しない。このため、イオン注入によってp型連結層10を形成する場合、活性化率を加味して、例えば第1ソース領域8aや第2ソース領域8bのn型不純物濃度の2~10倍のドーズ量でp型不純物を注入すれば、上記したp型不純物濃度が得られる。

#### 【0031】

さらに、n型ソース領域8およびp型ベース領域6を貫通してn型電流分散層5に達するように、例えば幅が $0.4 \mu\text{m}$ 、深さがp型ベース領域6とn型ソース領域8の合計膜厚よりも $0.2 \sim 0.4 \mu\text{m}$ 深くされたゲートトレンチ11が形成されている。このゲートトレンチ11の側面と接するように上述したp型ベース領域6やノンドープ層7およびn型ソース領域8が配置されている。ゲートトレンチ11は、図2のX方向を幅方向、J F E T部3や電界ブロック層4の長手方向と交差する方向、ここではY方向を長手方向、Z方向を深さ方向とする短冊状のレイアウトで形成されている。そして、図1および図2には示していないが、ゲートトレンチ11は、複数本がX方向に等間隔に配置されたストライプ状とされており、それぞれの間にp型ベース領域6やノンドープ層7およびn型ソース領域8が配置されている。また、各ゲートトレンチ11の中間位置に、p型ディープ層9やp型連結層10が配置されている。

#### 【0032】

このゲートトレンチ11の側面の位置において、p型ベース領域6およびノンドープ層7は、縦型MOSFETの作動時にn型ソース領域8とn型電流分散層5との間を繋ぐチャネル領域を形成する。このチャネル領域を含むゲートトレンチ11の内壁面は、ゲート絶縁膜12で覆われている。ゲート絶縁膜12の表面にはドープドPoly-Siにて構成されたゲート電極13が形成されており、これらゲート絶縁膜12およびゲート電極13によってゲートトレンチ11内が埋め尽くされ、トレンチゲート構造が構成されている

10

20

30

40

50

。

## 【0033】

また、n型ソース領域8の表面やゲート電極13の表面には、層間絶縁膜14を介してソース電極15や図示しないゲート配線層などが形成されている。ソース電極15やゲート配線層は、複数の金属、例えばN<sub>i</sub> / A<sub>1</sub>等にて構成されている。そして、複数の金属のうち少なくともn型SiC、具体的にはn型ソース領域8は、n型SiCとオーミック接触可能な金属で構成されている。また、複数の金属のうち少なくともp型SiC、具体的には第2領域10bと接触する部分は、p型SiCとオーミック接触可能な金属で構成されている。なお、ソース電極15は、層間絶縁膜14上に形成されることでSiC部分と電気的に絶縁されているが、層間絶縁膜14に形成されたコンタクトホールを通じて、n型ソース領域8およびp型ディープ層9と電気的に接触させられている。10

## 【0034】

一方、n<sup>+</sup>型基板1の裏面側にはn<sup>+</sup>型基板1と電気的に接続されたドレイン電極16が形成されている。このような構造により、nチャネルタイプの反転型のトレンチゲート構造の縦型MOSFETが構成されている。このような縦型MOSFETが複数セル配置されることでセル領域が構成されている。そして、このような縦型MOSFETが形成されたセル領域を囲むように図示しないガードリングなどによる外周耐圧構造が構成されることでSiC半導体装置が構成されている。

## 【0035】

このように構成される縦型MOSFETを有するSiC半導体装置は、例えば、ソース電圧V<sub>s</sub>を0V、ドレイン電圧V<sub>d</sub>を1~1.5Vとした状態で、ゲート電極13に対して20Vのゲート電圧V<sub>g</sub>を印加することで動作させられる。すなわち、縦型MOSFETは、ゲート電圧V<sub>g</sub>が印加されることにより、ゲートトレンチ11に接する部分のp型ベース領域6およびノンドープ層7にチャネル領域を形成する。これにより、n型ソース領域8とn型電流分散層5との間が導通する。したがって、縦型MOSFETは、n<sup>+</sup>型基板1より、n<sup>-</sup>型層2とJFET部3およびn型電流分散層5にて構成されるドリフト層を通じ、さらにチャネル領域からn型ソース領域8を通じて、ドレイン-ソース間に電流を流すという動作を行う。20

## 【0036】

また、このような半導体装置における縦型MOSFETを上アームと下アームそれぞれに配置したインバータ回路等に適用すると、縦型MOSFETに内蔵される寄生ダイオードが還流ダイオードとして働く。具体的には、n<sup>-</sup>型層2などドリフト層を構成するn型層と電界ブロック層4やp型ベース領域6もしくはp型ディープ層9を含むp型層によるPN接合によって寄生ダイオードが構成され、これが還流ダイオードとして働く。30

## 【0037】

インバータ回路等は、直流電源を用いつつ交流モータ等の負荷に対して交流電流を供給する際に用いられる。例えば、インバータ回路等は、直流電源に対して上アームと下アームを直列接続したブリッジ回路を複数個並列接続し、各ブリッジ回路の上アームと下アームを交互に繰り返しオンオフすることで、負荷に対して交流電流を供給する。

## 【0038】

具体的には、インバータ回路等の各ブリッジ回路では、上アームの縦型MOSFETをオン、下アームの縦型MOSFETをオフすることで負荷に対して電流供給を行った後、上アームの縦型MOSFETをオフ、下アームの縦型MOSFETをオンして電流供給を停止する。また、各アームの縦型MOSFETのオンオフの切り替えの際には、オフされる側の縦型MOSFETに備えられる寄生ダイオードが還流ダイオードとして働き、還流電流をソース-ドレイン間に流すという逆導通時の動作を行う。このようにして、インバータ回路等による負荷の交流駆動が行われる。40

## 【0039】

このような動作を行うに当たり、負荷短絡が発生すると、例えば600~1200Vもしくはそれ以上の電圧がドレイン-ソース間電圧V<sub>ds</sub>としてドレインに印加されること50

になる。このとき、n型ソース領域8の全域が高濃度のn型不純物層によって構成されていると、負荷短絡時の飽和電流値が大きくなり、SiC半導体装置の短絡耐量を得ることができなくなる。しかしながら、本実施形態のSiC半導体装置では、n型ソース領域8を比較的低濃度とされた第1ソース領域8aとそれよりも高濃度とされた第2ソース領域8bとによって構成していることから、負荷短絡時の飽和電流値を小さくすることが可能となる。これにより、SiC半導体装置の短絡耐量を向上させることが可能となる。

#### 【0040】

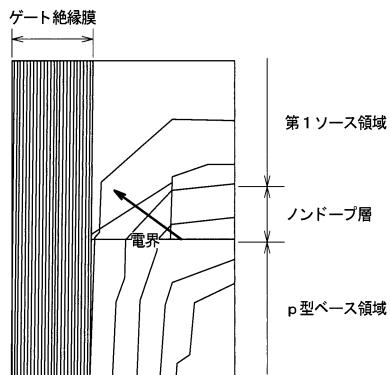

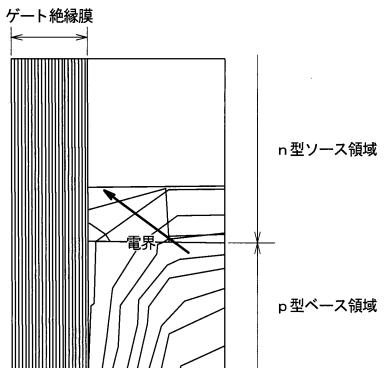

ここで、シミュレーションにより、n型ソース領域8の全域を高濃度とした場合と、本実施形態のように第1ソース領域8aおよび第2ソース領域8bで構成した場合、それについて、電子電流密度を調べた。図3および図4は、それぞれの結果を示した図である。図中ハッチングの間隔が狭い部分ほど、電子電流密度が高いことを示している。また、第1ソース領域8aの不純物濃度を変化させて、ドレイン電流の変化を調べた。図5は、その結果を示している。

#### 【0041】

なお、図3～図5のシミュレーションでは、ソース電圧Vsを0V、ゲート電圧Vgを20V、ドレイン電圧Vdを750Vとしている。また、図3のシミュレーションでは、n型ソース領域8の全域のn型不純物濃度を $1.0 \times 10^{19} / \text{cm}^3$ としている。同様に、図4のシミュレーションでは、n型ソース領域8を第1ソース領域8aと第2ソース領域8bで構成しつつ、第1ソース領域8aのn型不純物濃度を $1.0 \times 10^{16} / \text{cm}^3$ とし、第2ソース領域8bのn型不純物濃度を $1.0 \times 10^{19} / \text{cm}^3$ としている。図5のシミュレーションでは、n型ソース領域8を第1ソース領域8aと第2ソース領域8bで構成しつつ、第2ソース領域8bのn型不純物濃度を $1.0 \times 10^{19} / \text{cm}^3$ とし、第1ソース領域8aのn型不純物濃度を変化させている。

#### 【0042】

図3に示すように、n型ソース領域8の全域のn型不純物濃度を高濃度とした場合、n型ソース領域8の全域において電子電流密度が高くなっていることが判る。これは、n型ソース領域8が高濃度とされていることから、殆ど空乏化する領域が発生せず、n型ソース領域8の全域において電流が流れているためと考えられる。

#### 【0043】

一方、図4に示すように、n型ソース領域8を第1ソース領域8aおよび第2ソース領域8bで構成した場合、第1ソース領域8aにおいて、電子電流密度が小さくなっていることが判る。これは、第1ソース領域8aが低濃度とされていることから、第1ソース領域8aの広範囲に入り込むように空乏化が生じ、空乏化した部分において電流が流れなくなるためと考えられる。

#### 【0044】

このシミュレーション結果からも、n型ソース領域8を第1ソース領域8aおよび第2ソース領域8bによって構成することで、負荷短絡時における飽和電流値を低減できると言える。したがって、本実施形態の構造とすることで、SiC半導体装置の短絡耐量を向上させることが可能になることが判る。

#### 【0045】

また、第1ソース領域8aについては、第2ソース領域8bよりもn型不純物濃度が低ければ良いものの、ある程度の濃度でないと飽和電流値を所望値まで低下させることができない。具体的には、負荷短絡時のドレイン電流が $14000 \text{ A} / \text{cm}^2$ 以下となるようには、所望の短絡耐量を得ることができる。そして、図5に示されるように、負荷短絡時のドレイン電流が $14000 \text{ A} / \text{cm}^2$ 以下となるのは、第1ソース領域8aのn型不純物濃度が $1.0 \times 10^{17} / \text{cm}^3$ 以下となる場合である。したがって、本実施形態のSiC半導体装置のように、第1ソース領域8aのn型不純物濃度を $1.0 \times 10^{17} / \text{cm}^3$ 以下とすることで、短絡耐量を向上させることが可能となる。

#### 【0046】

ただし、第1ソース領域8aのn型不純物濃度が低すぎると、第1ソース領域8aの抵

10

20

30

40

50

抗値が大きくなり過ぎ、オン抵抗  $R_{on}$  を増大させることになる。第 1 ソース領域 8 a の n 型不純物濃度とオン抵抗  $R_{on}$  との関係について調べたところ、図 6 に示す結果となつた。SiC 半導体装置の高速スイッチング動作を鑑みると、オン抵抗  $R_{on}$  については  $1.2 \text{ m} \text{ cm}^2$  以下であることが好ましい。図 6 の結果によれば、第 1 ソース領域 8 a の n 型不純物濃度が  $2.0 \times 10^{16} / \text{cm}^3$  未満になると急激にオン抵抗  $R_{on}$  が上昇するが、n 型不純物濃度がそれ以上であれば、オン抵抗  $R_{on}$  を  $1.2 \text{ m} \text{ cm}^2$  以下にできていた。したがつて、本実施形態の SiC 半導体装置のように、第 1 ソース領域 8 a の n 型不純物濃度を  $2.0 \times 10^{16} / \text{cm}^3$  以上とすることで、オン抵抗  $R_{on}$  の劣化を抑制することが可能となる。

## 【0047】

10

このように、第 1 ソース領域 8 a の n 型不純物濃度を  $2.0 \times 10^{16} \sim 1.0 \times 10^{17} / \text{cm}^3$  とすることで、短絡耐量を向上させつつ、オン抵抗  $R_{on}$  の劣化を抑制することが可能となる。

## 【0048】

20

さらに、本実施形態の SiC 半導体装置では、p 型ベース領域 6 と第 1 ソース領域 8 a との間にノンドープ層 7 を備えるようにしている。このため、ゲート絶縁膜 12 へのダメージを抑制できるという効果が得られる。この効果について、図 7 ~ 図 9 を参照して説明する。なお、図 7 ~ 図 9 は、それぞれ、n 型ソース領域 8 の全域を高不純物濃度とした場合、第 1 ソース領域 8 a を p 型ベース領域 6 に接するように形成した場合、ノンドープ層 7 を備えた本実施形態の構造の場合について、逆導通時の電圧分布を調べた結果を示している。逆導通時の条件としては、ゲート電圧  $V_g$  を 20 V、ドレイン - ソース間電圧  $V_{ds}$  を -5 V としている。

## 【0049】

30

逆通電時には、基本的には、縦型 MOSFET に形成される寄生ダイオードが還流ダイオードとして働き、寄生ダイオードを通じて還流電流が流れる。そして、寄生ダイオードを構成する PN 接合の p 型層側から n 型層側に拡散した正孔と n 型層中の電子が再結合する。このとき、再結合エネルギーが大きいために、エピタキシャル膜で構成された n 型層中の基底面転位（以下、BPD という）が拡張してシングルショックレースタッキングフォルト（以下、SSSF という）という積層欠陥になる。BPD は線状欠陥であるために、SiC 半導体装置のセル領域内における占有面積が狭く、素子動作に及ぼす影響が殆ど無いが、SSSF になると、積層欠陥となるためにセル領域内における占有面積が広くなり、素子動作に及ぼす影響が大きくなる。このため、逆導通時にも積極的にゲート電圧  $V_g$  を印加してチャネル領域を形成し、チャネル領域を通じても還流電流が流れるようすれば、還流電流を分散して再結合エネルギーを低減できるため、SSSF の発生を抑制することが可能となる。ただし、チャネル領域を通じての還流電流の流れが発生することから、p 型ベース領域 6 と n 型ソース領域 8 の間ににおいて、高い電界が掛かることになり、ホットエレクトロンを生じさせ、ゲート絶縁膜 12 にダメージを与えるという現象が発生する。

## 【0050】

40

具体的には、図 7 に示すように、p 型ベース領域 6 に接するように全域高濃度とした n 型ソース領域 8 を形成する場合、逆導通時に、PN 接合箇所において電位分布が生じ、n 型ソース領域 8 に高い電界が掛かる状態となる。p 型ベース領域 6 に接するように n 型ソース領域 8 を形成する場合、n 型ソース領域 8 に掛けられる電界によって、n 型ソース領域 8 のうち p 型ベース領域 6 と接する部分に存在するキャリアが電界によって加速され、ホットエレクトロンとなる。これがゲート絶縁膜 12 に衝突し、ゲート絶縁膜 12 にダメージを与えるという課題を発生させる。特に、n 型ソース領域 8 の全域において n 型不純物濃度を高くすると、この課題が顕著になる。

## 【0051】

50

一方、ノンドープ層 7 を備えていなくても、n 型ソース領域 8 に第 1 ソース領域 8 a を備える場合、p 型ベース領域 6 と第 1 ソース領域 8 a とによって PN 接合が構成されるこ

となる。このように、第1ソース領域8aを備える場合、ノンドープ層7を備えていなくても、第1ソース領域8aのn型不純物濃度が比較的低くされていることから、PN接合部に掛かる電界をある程度抑制できる。すなわち、図8に示されるように、図7の場合よりもPN接合部での等電位線の間隔が広くなり、第1ソース領域8aを備えた構造の方が電界をある程度抑制できる。

#### 【0052】

しかしながら、ノンドープ層7を形成しない場合には、p型ベース領域6と第1ソース領域8aとによるPN接合部が構成されることから、図7の場合よりも軽減されるものの、ホットエレクトロンが生成されることで、上記課題を発生させ得る。

#### 【0053】

これに対して、本実施形態のように、p型ベース領域6と第1ソース領域8aとの間にノンドープ層7を備えると、図9に示すように、ノンドープ層7によって等電位線を受けることができ、n型ソース領域8中の電界を弱めることができるとなる。そして、ノンドープ層7中に電界が発生するものの、ノンドープ層7中に殆どキャリアが存在しない。したがって、ノンドープ層7を備えることにより、逆導通時のホットエレクトロンによるゲート絶縁膜12のダメージを抑制することができる。

#### 【0054】

よって、逆導通時に、寄生ダイオードだけでなく積極的にチャネル領域を通じても還流電流が流れるようにすることでSSSFの発生を抑制しつつ、ホットエレクトロンの生成も抑制でき、ゲート絶縁膜12にダメージを与えることを抑制できる。

#### 【0055】

さらに、本実施形態のSiC半導体装置には、JFET部3および電界ブロック層4を備えてある、このため、縦型MOSFETの動作時には、JFET部3および電界ブロック層4が飽和電流抑制層として機能し、飽和電流抑制効果を発揮することで低オン抵抗を図りつつ、低飽和電流を維持できる構造とすることが可能となる。具体的には、JFET部3のうちストライプ状とされた部分と電界ブロック層4とが交互に繰り返し形成された構造とされていることから、次に示すような作動を行う。

#### 【0056】

まず、ドレイン電圧Vdが例えば1~1.5Vのように通常作動時に印加される電圧である場合には、電界ブロック層4側からJFET部3へ伸びる空乏層は、JFET部3のうちストライプ状とされた部分の幅よりも小さい幅しか伸びない。このため、JFET部3内へ空乏層が伸びても電流経路が確保される。そして、JFET部3のn型不純物濃度がn-型層2よりも高くされていて、電流経路を低抵抗に構成できるため、低オン抵抗を図ることが可能となる。

#### 【0057】

また、負荷短絡などによってドレイン電圧Vdが通常作動時の電圧よりも高くなると、電界ブロック層4側からJFET部3へ伸びる空乏層がJFET部3のうちストライプ状とされた部分の幅よりも伸びる。そして、n型電流分散層5よりも先にJFET部3が即座にピンチオフされる。このとき、JFET部3のうちストライプ状とされた部分の幅およびn型不純物濃度に基づいてドレイン電圧Vdと空乏層の幅との関係が決まる。このため、通常作動時のドレイン電圧Vdよりも少し高い電圧となつたときにJFET部3がピンチオフされるように、JFET部3のうちストライプ状とされた部分の幅およびn型不純物濃度を設定することで、低いドレイン電圧VdでもJFET部3をピンチオフすることができる。このように、ドレイン電圧Vdが通常作動時の電圧よりも高くなつたときにJFET部3が即座にピンチオフされるようにすることで、低飽和電流を維持することができ、更に負荷短絡等によるSiC半導体装置の耐量を向上することが可能となる。

#### 【0058】

このように、JFET部3および電界ブロック層4が飽和電流抑制層として機能し、飽和電流抑制効果を発揮することで、更に低オン抵抗と低飽和電流を両立することができるSiC半導体装置とすることが可能となる。

10

20

30

40

50

## 【0059】

さらに、J F E T 部 3 を挟み込むように電界ブロック層 4 を備えることで、J F E T 部 3 のうちストライプ状とされた部分と電界ブロック層 4 とが交互に繰り返し形成された構造とされている。このため、ドレイン電圧  $V_d$  が高電圧になったとしても、下方から  $n^-$  型層 2 に伸びてくる空乏層の伸びが電界ブロック層 4 によって抑えられ、トレンチゲート構造に延伸することを防ぐことができる。したがって、ゲート絶縁膜 1 2 に掛かる電界を低下させる電界抑制効果を発揮させられ、ゲート絶縁膜 1 2 が破壊されることを抑制できるため、高耐圧化で信頼性の高い素子とすることが可能となる。そして、このようにトレンチゲート構造への空乏層の延伸を防げるため、ドリフト層の一部を構成する  $n^-$  型層 2 や J F E T 部 3 の  $n$  型不純物濃度を比較的濃くすることができ、低オン抵抗化を図ることが可能となる。 10

## 【0060】

よって、低オン抵抗かつ高信頼性の縦型M O S F E T を有する S i C 半導体装置とすることが可能となる。

## 【0061】

次に、本実施形態にかかる  $n$  チャネルタイプの反転型のトレンチゲート構造の縦型M O S F E T を備えた S i C 半導体装置の製造方法について、図 10 A ~ 図 10 H に示す製造工程中の断面図を参照して説明する。

## 【0062】

## 〔図 10 A に示す工程〕

20

まず、半導体基板として、 $n^+$  型基板 1 を用意する。そして、図示しない C V D (chemical vapor deposition) 装置を用いたエピタキシャル成長により、 $n^+$  型基板 1 の主表面上に S i C からなる  $n^-$  型層 2 を形成する。このとき、 $n^+$  型基板 1 の主表面上に予め  $n^-$  型層 2 を成長させてある所謂エピ基板を用いても良い。そして、 $n^-$  型層 2 の上に S i C からなる J F E T 部 3 をエピタキシャル成長させる。

## 【0063】

なお、エピタキシャル成長については、S i C の原料ガスとなるシランやプロパンに加えて、 $n$  型ドーパントとなるガス、例えば窒素ガスを導入することで行っている。

## 【0064】

## 〔図 10 B に示す工程〕

30

J F E T 部 3 の表面に、マスク 1 7 を配置したのち、マスク 1 7 をパターニングして電界ブロック層 4 の形成予定領域を開口させる。そして、 $p$  型不純物をイオン注入することで、電界ブロック層 4 を形成する。その後、マスク 1 7 を除去する。

## 【0065】

なお、ここでは、電界ブロック層 4 をイオン注入によって形成しているが、イオン注入以外の方法によって電界ブロック層 4 を形成しても良い。例えば、J F E T 部 3 を選択的に異方性エッチングすることで電界ブロック層 4 と対応する位置に凹部を形成し、この上に  $p$  型不純物層をエピタキシャル成長させたのち、J F E T 部 3 の上に位置する部分において  $p$  型不純物層を平坦化して電界ブロック層 4 を形成する。このように、電界ブロック層 4 をエピタキシャル成長によって形成することもできる。 $p$  型 S i C をエピタキシャル成長させる場合、S i C の原料ガスに加えて、 $p$  型ドーパントとなるガス、例えばトリメチルアルミニウム（以下、T M A という）を導入すれば良い。 40

## 【0066】

## 〔図 10 C に示す工程〕

引き続き、J F E T 部 3 および電界ブロック層 4 の上に  $n$  型 S i C をエピタキシャル成長させることで、 $n$  型電流分散層 5 を形成する。そして、 $n$  型電流分散層 5 の上に、 $p$  型ディープ層 9 の形成予定領域が開口する図示しないマスクを配置する。その後、マスクの上から  $p$  型不純物をイオン注入することで  $p$  型ディープ層 9 を形成する。なお、 $p$  型ディープ層 9 についてもイオン注入によって形成する例を示したが、イオン注入以外の方法によって形成することもできる。例えば、電界ブロック層 4 と同様に、 $n$  型電流分散層 5 に 50

対して凹部を形成したのち、p型不純物層をエピタキシャル成長させ、さらにp型不純物層の平坦化を行うことで、p型ディープ層9を形成するようにも良い。

【0067】

【図10Dに示す工程】

図示しないCVD装置を用いて、n型電流分散層5およびp型ディープ層9の上にp型ベース領域6とノンドープ層7およびn型ソース領域8を順にエピタキシャル成長させる。例えば、同じCVD装置内において、まずはp型ドーパントとなるガスを導入したエピタキシャル成長によってp型ディープ層9を形成する。続いて、p型ドーパントとn型ドーパントの両方のドーパントガスの導入を停止した状態でエピタキシャル成長を連続して行うことでノンドープ層7を形成する。そして、ノンドープ層7が所定膜厚に達したら、今度はn型ドーパントとなるガスを導入したエピタキシャル成長によってn型ソース領域8を形成する。このとき、n型ドーパントの導入量を調整することで、第1ソース領域8aと第2ソース領域8bのn型不純物濃度が所望の値となるように調整する。

【0068】

このようにして、p型ベース領域6とノンドープ層7およびn型ソース領域8を上記した不純物濃度および膜厚で形成することができる。ここで、各部の膜厚や不純物濃度については次のように決めている。

【0069】

まず、p型ベース領域6については、チャネル領域が設定される部分となることから、ゲート電圧Vgの印加時に反転型チャネルを構成する不純物濃度に設定しつつ、チャネル長を規定する膜厚となるようにしている。このため、p型ベース領域6については、例えばp型不純物濃度を $3 \times 10^{17} / \text{cm}^3$ 、厚さを $0.4 \sim 0.6 \mu\text{m}$ としている。

【0070】

ノンドープ層7については、任意に膜厚を設定できるが、厚すぎるとオン抵抗Ronが高くなる。このため、 $0.05 \sim 0.2 \mu\text{m}$ の厚みとしている。また、ノンドープ層7については、基本的には不純物が存在しないようにするのが好ましいが、キャリア濃度が低くなつていれば良い。特に、p型ベース領域6の形成後に連続してノンドープ層7を形成しようとすると、雰囲気中に残留しているp型不純物が導入されたり、大気中に存在している窒素がn型不純物として導入されることもあり得る。このような場合であっても不純物濃度が低ければ良いし、一方の導電型の不純物が導入され得ることが想定される場合、他方の導電型の不純物を意図的に導入して、両方がドープされるようにすることで互いに打ち消しあってキャリア濃度が低くなるようにすればよい。例えば、p型不純物とn型不純物の一方のみがドープされている場合には、不純物濃度が $5.0 \times 10^{15} / \text{cm}^3$ 以下とされ、両方がドープされている場合には、互いに打ち消しあうことでキャリア濃度が $5.0 \times 10^{15} / \text{cm}^3$ 以下となるようにしている。

【0071】

n型ソース領域8のうちの第1ソース領域8aについては、負荷短絡時に高いドレン電圧Vdが印加された場合でも飽和電流値を小さくしつつ、オン抵抗Ronが高くなることを抑制できるように膜厚およびn型不純物濃度を設定している。このため、第1ソース領域8aについては、例えばn型不純物濃度を $2.0 \times 10^{16} \sim 1.0 \times 10^{17} / \text{cm}^3$ とし、厚みを $0.2 \mu\text{m}$ 以上としている。

【0072】

n型ソース領域8のうちの第2ソース領域8bについては、ソース電極15とオーミック接触させられる不純物濃度となるようにしつつ、ソース電極15との化学反応によって全域が消失してしまわない程度の膜厚に設定してある。第2ソース領域8bのn型不純物濃度については高いほどオーミック接触させ易くなる。しかしながら、本実施形態のようにn型ソース領域8をエピタキシャル成長させたのちp型不純物をイオン注入してp型連結層10を形成することもあり、その場合には、n型ソース領域8のn型不純物濃度が高すぎると、p型連結層10を所望の濃度にできない。このため、本実施形態の場合は、第2ソース領域8bのn型不純物濃度を例えば $1.0 \times 10^{18} \sim 5.0 \times 10^{19} / \text{cm}^3$

10

20

30

40

50

<sup>3</sup> としてある。

【0073】

また、上記したように、ソース電極15は、複数の金属によって構成されており、第2ソース領域8bとオーミック接触させられる部分は、例えばN<sub>i</sub>によって構成される。その場合、第2ソース領域8bのうちN<sub>i</sub>と接触させられる部分はN<sub>i</sub>シリサイドとなることでオーミック接触となるが、シリサイド化される分、第2ソース領域8bが消失することになる。そして、シリサイド化反応によってN<sub>i</sub>シリサイドとなるのが0.1μm程度の厚さであることから、シリサイド化反応によって第2ソース領域8bが全域消失しないように、第2ソース領域8bの厚みを0.1μm以上としている。

【0074】

ただし、第1ソース領域8aや第2ソース領域8bを厚くすると、その分、トレンチゲート構造を深くまで形成することが必要になる。このため、第1ソース領域8aの膜厚を0.5μm以下としており、第2ソース領域8bの膜厚を0.2μm以下としている。

【0075】

また、p型ベース領域6とノンドープ層7およびn型ソース領域8をエピタキシャル成長によって形成する場合、各部の膜厚のバラツキを小さくできる。そして、チャネル領域の形成に用いられるp型ベース領域6については、膜厚バラツキを小さくできることにより、チャネル長を精度良く作りこむことが可能となる。これにより、縦型MOSFETの閾値V<sub>th</sub>のバラツキを低減することが可能となる。

【0076】

例えば、p型ベース領域6をエピタキシャル成長させたのち、p型ベース領域6に対してn型不純物を打ち返すことでノンドープ層7やn型ソース領域8を形成することも可能である。しかしながら、この場合、エピタキシャル成長させるときのp型ベース領域6の膜厚について、イオン注入によって形成するノンドープ層7およびn型ソース領域8の分の厚みを見込んで厚くする必要がある。エピタキシャル成長させるときの膜厚バラツキは、成長させる膜厚が厚いほど大きくなるが、イオン注入の飛程のバラツキはあまり大きくないため、イオン注入後のp型ベース領域6の膜厚バラツキは、エピタキシャル成長させた膜厚に対応するバラツキとなる。このため、例えばp型ベース領域6を1.4μmの厚みとした場合の膜厚バラツキが±0.21μmであったとすると、イオン注入によってノンドープ層7およびn型ソース領域8を形成した後でも、p型ベース領域6の膜厚バラツキは±0.21μmとなる。

【0077】

これに対して、本実施形態のように、各部をエピタキシャル成長によって形成する場合、p型ベース領域6の膜厚バラツキは、ノンドープ層7およびn型ソース領域8の膜厚分を含んだバラツキにはならず、p型ベース領域6のみの厚みに対応したバラツキとなる。例えば、p型ベース領域6の膜厚を0.4~0.6μmとする場合、膜厚バラツキが±0.06~0.09μmとなる。このため、各部をエピタキシャル成長によって形成することで、p型ベース領域6の膜厚バラツキを抑制でき、チャネル長を精度良く作りこむことができる。

【0078】

また、エピタキシャル成長によって各部を連続的に形成する場合、格子定数に不純物種・不純物濃度依存性があることから、不純物種および不純物濃度が急激に変化しないことが好ましい。これに対して、本実施形態のように、p型ベース領域6の上にノンドープ層7を介してn型ソース領域8を形成する場合、不純物種がp型からすぐにn型に変化しないことから、不純物種が急激に変化しないようにできる。また、n型ソース領域8を形成する際にも、比較的低濃度の第1ソース領域8aを形成してから、比較的高濃度の第2ソース領域8bを形成することになるため、不純物濃度が急激に変化しないようにできる。

【0079】

したがって、不純物種や不純物濃度が急激に変化する場合に生じる結晶欠陥を抑制することが可能となる。

10

20

30

40

50

## 【0080】

## 〔図10Eに示す工程〕

n型ソース領域8の上にp型連結層10の形成予定位置を開口させた図示しないマスクを配置する。そして、マスクの上からp型不純物をイオン注入したのち、活性化のために1500以上熱処理を行う。イオン注入する元素としては、ボロン(B)とアルミニウム(A1)のいずれか一方もしくは両方を用いている。これにより、n型ソース領域8をp型不純物のイオン注入によって打ち返してp型連結層10を形成することができる。また、p型連結層10については、p型ベース領域6に接続されるようにする必要があるため、ノンドープ層7にもp型不純物が打ち込まれるようにし、この部分もp型連結層10となるようにする。

10

## 【0081】

このとき、p型連結層10のうちの第2領域10bについては、ソース電極15とオーミック接触が取れるようにする必要がある。このため、第2ソース領域8bのn型不純物濃度の2~10倍のドーズ量でイオン注入を行っている。ドーズ量については、第2ソース領域8bのn型不純物濃度の2倍あれば、ソース電極15とオーミック接触させられる程度のキャリア濃度にできると考えられるが、活性化率を考慮して、2~10倍とするのが好ましい。

## 【0082】

これにより、第2領域10bのキャリア濃度、つまり第2ソース領域8bとの間でキャンセルされる分や活性化していない分を除いたキャリアとして機能する分のp型不純物濃度が例えば $2.0 \times 10^{18} \sim 1.0 \times 10^{20} / \text{cm}^3$ となるようにできる。第2領域10bの不純物濃度が高いほどソース電極15とのオーミック接触が取り易くなるが、第2領域10bを形成する前の第2ソース領域8bについても、ソース電極15とオーミック接触させなければならない。また、ドーズ量が多いとイオン注入による結晶欠陥の生成の原因となることから、ある程度の量に抑える必要がある。これらを加味して、第2ソース領域8bのn型不純物濃度と第2領域10bのp型不純物濃度を設定する必要がある。このため、第2ソース領域8bのn型不純物濃度や第2領域10bのうちp型不純物濃度を例えば $1.0 \times 10^{18} \sim 5.0 \times 10^{19} / \text{cm}^3$ としている。

20

## 【0083】

一方、第1領域10aについては、ソース電極15とオーミック接触させられる部分ではないため、第2領域10bよりもp型不純物濃度が低くて良い。ただし、ここでは、活性化率を考慮して、第1ソース領域8aの2~10倍のドーズ量のp型不純物をイオン注入するようにしている。

30

## 【0084】

なお、p型連結層10をイオン注入によって形成する場合、イオン注入装置の出力の観点より、p型不純物が注入されるノンドープ層7およびn型ソース領域8の合計膜厚が0.8μm以下となるようにすると好ましい。このようにすれば、汎用されているイオン注入装置の出力でもp型連結層10をp型ベース領域6に達するように形成することができ、量産性を担保することが可能となる。

## 【0085】

40

## 〔図10Fに示す工程〕

n型ソース領域8などの上に図示しないマスクを形成したのち、マスクのうちのゲートトレンチ11の形成予定領域を開口させる。そして、マスクを用いてRIE(Reactive Ion Etching)等の異方性エッティングを行うことで、ゲートトレンチ11を形成する。

## 【0086】

## 〔図10Gに示す工程〕

その後、マスクを除去してから例えば熱酸化を行うことによって、ゲート絶縁膜12を形成し、ゲート絶縁膜12によってゲートトレンチ11の内壁面上およびn型ソース領域8の表面上を覆う。そして、p型不純物もしくはn型不純物がドープされたPoly-Siをデポジションした後、これをエッチバックし、少なくともゲートトレンチ11内にP

50

o 1 y - S i を残すことでゲート電極 1 3 を形成する。これにより、トレンチゲート構造が完成する。

【 0 0 8 7 】

この後の工程については図示しないが、以下のような工程を行う。すなわち、ゲート電極 1 3 およびゲート絶縁膜 1 2 の表面を覆うように、例えば酸化膜などによって構成される層間絶縁膜 1 4 を形成する。また、図示しないマスクを用いて層間絶縁膜 1 4 に n 型ソース領域 8 および p 型ディープ層 9 を露出させるコンタクトホールを形成する。そして、層間絶縁膜 1 4 の表面上に例えば複数の金属の積層構造により構成される電極材料を形成したのち、電極材料をパターニングすることでソース電極 1 5 やゲート配線層を形成する。さらに、n<sup>+</sup> 型基板 1 の裏面側にドレイン電極 1 6 を形成する。このようにして、本実施形態にかかる S i C 半導体装置が完成する。

【 0 0 8 8 】

以上説明したように、本実施形態の S i C 半導体装置では、n 型ソース領域 8 を比較的低濃度とされた第 1 ソース領域 8 a とそれよりも高濃度とされた第 2 ソース領域 8 b とによって構成している。このため、負荷短絡時の飽和電流値を小さくすることが可能となり、S i C 半導体装置の短絡耐量を向上させることが可能となる。

【 0 0 8 9 】

さらに、本実施形態の S i C 半導体装置では、p 型ベース領域 6 と第 1 ソース領域 8 a との間にノンドープ層 7 を備えるようにしている。このため、ホットエレクトロンの生成を抑制でき、ゲート絶縁膜 1 2 へのダメージを抑制できるという効果が得られる。

【 0 0 9 0 】

( 他 の 実 施 形 態 )

本発明は上記した実施形態に限定されるものではなく、特許請求の範囲に記載した範囲内において適宜変更が可能である。

【 0 0 9 1 】

( 1 ) 例えば、上記実施形態において、J F E T 部 3 および電界ブロック層 4 を備えると共に n 型電流分散層 5 を備え、J F E T 部 3 や n 型電流分散層 5 がドリフト層の一部を構成する構造としている。しかしながら、これは縦型M O S F E T の構成の一例を挙げたに過ぎず、J F E T 部 3 および電界ブロック層 4 を備えない構造、n 型電流分散層 5 を備えない構造、もしくは、これら両方を備えない構造としても良い。

【 0 0 9 2 】

( 2 ) また、上記実施形態では、p 型ベース領域 6 とノンドープ層 7 および n 型ソース領域 8 をエピタキシャル成長によって形成する場合について説明したが、他の手法で形成しても良い。例えば、上記実施形態と比較すると、チャネル長のバラツキが大きくなり得るが、p 型ベース領域 6 に対して n 型不純物をイオン注入してノンドープ層 7 や n 型ソース領域 8 を形成するようにしても良い。また、p 型ベース領域 6 の上に n 型ソース領域 8 の厚み分を加えてノンドープ層 7 をエピタキシャル成長させ、ノンドープ層 7 に対して n 型不純物をイオン注入することで n 型ソース領域 8 を形成しても良い。

【 0 0 9 3 】

ただし、ノンドープ層 7 や n 型ソース領域 8 をイオン注入によって形成する場合、ゲートトレンチ 1 1 の側面が n 型ソース領域 8 の表面に対して垂直にならない部分が生じる。具体的には、ゲートトレンチ 1 1 を形成したときには、必要に応じて、犠牲酸化やケミカルドライエッティングを行うことで、内壁面の欠陥除去などを行うが、イオン注入ダメージがあると、その部分がダメージを受けていない部分よりも除去され易くなる。このため、ゲートトレンチ 1 1 の入り口側において開口幅が広がり、ゲートトレンチ 1 1 の側面が n 型ソース領域 8 の表面に対して垂直にならなくなる。この点からもノンドープ層 7 や n 型ソース領域 8 をエピタキシャル成長によって形成するのが好ましい。

【 0 0 9 4 】

( 3 ) また、上記実施形態で示した S i C 半導体装置を構成する各部の不純物濃度や厚み、幅等の各種寸法については一例を示したに過ぎない。

10

20

30

40

50

## 【0095】

(4) また、上記実施形態では、p型ディープ層9とp型連結層10を別々に構成したが、これらを同じp型層によって構成しても良い。例えば、n型ソース領域8の表面からノンドープ層7やp型ベース領域6およびn型電流分散層5を貫通して電界ブロック層4に達するディープトレンチを形成し、このディープトレンチ内に埋め込まれるようにp型層を形成する。このようにすれば、p型層によってp型ディープ層9とp型連結層10を構成することが可能となる。

## 【0096】

(5) また、上記実施形態では、n型ソース領域8を不純物濃度が異なる2つの領域、つまり第1ソース領域8aと第2ソース領域8bとに区画する構造について説明したが、これらが明確に区画された構造でなくても良い。すなわち、n型ソース領域8のうちのp型ベース領域6側がソース電極15に接触させられる表面側よりも低不純物濃度で、かつ、表面側がソース電極15に対してオーミック接触させられる高不純物濃度とされれば良い。

10

## 【0097】

(6) また、上記実施形態において、各不純物層の深さなどについては適宜変更可能である。例えば、図11に示すように、第1領域10aが第1ソース領域8aよりも深い位置まで形成されていたり、第2領域10bが第2ソース領域8bおよびノンドープ層7よりも深い位置まで形成されていても良い。

## 【0098】

20

(7) また、上記実施形態では、第1導電型をn型、第2導電型をp型としたnチャネルタイプの縦型MOSFETを例に挙げて説明したが、各構成要素の導電型を反転させたpチャネルタイプの縦型MOSFETとしても良い。また、上記説明では、半導体素子として縦型MOSFETを例に挙げて説明したが、同様の構造のIGBTに対しても本発明を適用することができる。nチャネルタイプのIGBTの場合、上記各実施形態に対してn<sup>+</sup>型基板1の導電型をn型からp型に変更するだけであり、その他の構造や製造方法に関しては上記各実施形態と同様である。

## 【符号の説明】

## 【0099】

- 6 p型ベース領域

- 7 ノンドープ層

- 8 n型ソース領域

- 8a 第1ソース領域

- 8b 第2ソース領域

- 10 p型連結層

- 11 ゲートトレンチ

- 13 ゲート電極

- 15 ソース電極

- 16 ドレイン電極

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図9】

【図10A】

【図7】

【図8】

【図10B】

【図10C】

【図10D】

【図10F】

【図10E】

【図10G】

【図11】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/205

(72)発明者 竹内 有一

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 箕谷 周平

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

(72)発明者 鈴木 龍太

愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内

(72)発明者 山下 侑佑

愛知県長久手市横道41番地の1 株式会社豊田中央研究所内

審査官 杉山 芳弘

(56)参考文献 特開2010-021175 (JP, A)

米国特許第9123800 (US, B2)

特開2011-044688 (JP, A)

特開2014-239146 (JP, A)

特開2007-134469 (JP, A)

特開2002-190595 (JP, A)

特表2011-503871 (JP, A)

国際公開第2011/027831 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29/78

H 01 L 29/12

H 01 L 21/336

H 01 L 21/205