(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년10월19일

(11) 등록번호 10-1667770

(24) 등록일자 2016년10월13일

- (51) 국제특허분류(Int. Cl.)

*H01J 37/244* (2006.01) *H01J 37/304* (2006.01)

*H01J 37/317* (2006.01)

- (21) 출원번호 10-2012-7027493

- (22) 출원일자(국제) 2011년03월22일

심사청구일자 2016년03월21일

- (85) 번역문제출일자 2012년10월22일

- (65) 공개번호 10-2013-0067252

- (43) 공개일자 2013년06월21일

- (86) 국제출원번호 PCT/EP2011/054372

- (87) 국제공개번호 WO 2011/117253

국제공개일자 2011년09월29일

- (30) 우선권주장

1037820 2010년03월22일 네덜란드(NL)

## (56) 선행기술조사문현

- JP2000315785 A

JP평성11246300 A

WO2007032670 A1

US20070057204 A1

전체 청구항 수 : 총 17 항

심사관 : 임은정

## (54) 발명의 명칭 리소그래피 시스템, 센서, 변환기 엘리먼트 및 제조 방법

**(57) 요약**

하나 이상의 하전 입자 빔릿들의 하나 이상의 특징들을 결정하기 위한 센서를 포함하는, 패턴을 타겟의 표면으로 전사하기 위한 하전 입자 빔릿 리소그래피 시스템이 개시된다. 센서는 하전 입자들(22)을 수용하고 이에 응답하여 광자들(photon)을 생성하기 위한 변환기 엘리먼트(1)를 포함한다. 변환기 엘리먼트는 하나 이상의 하전 입

(뒷면에 계속)

**대표도** - 도2a

자 빔릿들을 수용하기 위한 표면을 포함하고, 표면에는 하나 이상의 개별적인 빔릿들을 평가하기 위한 하나 이상의 셀들이 제공된다. 각각의 셀은 변환기 엘리먼트 표면에 걸쳐 미리결정된 빔릿 스캔 궤적을 따라 차단 및 비 차단 영역들 사이의 전이들(transitions)에서 다수의 나이프 에지들(knife edges)을 형성하는 미리결정된 차단 패턴(18)의 하나 이상의 하전 입자 차단 구조들을 포함한다. 변환기 엘리먼트 표면은 하전 입자들에 대해 실질적으로 침투 가능하고 주변 광(ambient light)에 대해 실질적으로 침투 불가한 코팅층(20)으로 코팅된다. 전기 적으로 도전성 층(21)은 코팅층 및 차단 구조들 사이에 위치된다.

---

## 명세서

### 청구범위

#### 청구항 1

변환기(converter) 엘리먼트로서,

상기 변환기 엘리먼트는 복수의 하전 입자 빔릿들의 특징을 감지하기 위한 센서에서의 사용에 응답하여 하전 입자들을 수용하고 그리고 광자(photon)들을 생성하기 위한 것이며, 상기 변환기 엘리먼트는 하나 또는 그 초과의 하전 입자 빔릿들을 수용하기 위한 표면을 포함하고,

상기 표면에는 하나 또는 그 초과의 개별적인 빔릿들을 평가하기 위한 하나 또는 그 초과의 셀들이 제공되고,

각각의 셀은 상기 변환기 엘리먼트의 표면에 걸쳐 미리결정된 빔릿 스캔 궤적을 따라 차단(block) 및 비차단 영역들 사이의 전이(transition)들에서 다수의 나이프 에지(knife edge)들을 형성하는 하나 또는 그 초과의 하전 입자 차단 구조들의 미리결정된 차단 패턴을 포함하고,

상기 변환기 엘리먼트의 표면은, 하전 입자들에 대하여는 침투가능(permeable)하고 주변 광(ambient light)에 대하여는 침투불가능한 코팅층으로 커버되고, 그리고

전기적 도전성 층이 상기 코팅층과 상기 차단 구조들 사이에 위치되는,

변환기 엘리먼트.

#### 청구항 2

제 1 항에 있어서,

상기 도전성 층은 상기 변환기 엘리먼트의 표면과 평행인 평면 내의 상기 차단 구조들의 치수들과 형상 및 크기 면에서 유사한,

변환기 엘리먼트.

#### 청구항 3

제 1 항 또는 제 2 항에 있어서,

상기 도전성 층은 크롬을 포함하는,

변환기 엘리먼트.

#### 청구항 4

제 1 항 또는 제 2 항에 있어서,

상기 차단 구조들은 텅스텐을 포함하는,

변환기 엘리먼트.

#### 청구항 5

제 1 항 또는 제 2 항에 있어서,

상기 변환기 엘리먼트는 섬광 재료(scintillating material)를 포함하는,

변환기 엘리먼트.

#### 청구항 6

제 5 항에 있어서,

상기 섬광 재료는 이트륨 알루미늄 석류석(yttrium aluminum garnet)을 포함하는,

변환기 엘리먼트.

#### 청구항 7

제 1 항 또는 제 2 항에 있어서,

상기 코팅층은 티타늄 또는 알루미늄을 포함하는,

변환기 엘리먼트.

#### 청구항 8

하전 입자 빔에 의한 센서의 노출에 응답하여 신호를 생성하기 위한 센서로서,

제 1 항 또는 제 2 항에 따른 변환기 엘리먼트, 및

상기 변환기 엘리먼트에 의해 생성되는 광자들에 기초하여 신호를 생성하기 위한 상기 변환기 엘리먼트와 연관된 광자 수용기

를 포함하는,

센서.

#### 청구항 9

제 8 항에 있어서,

상기 광자 수용기는 상기 변환기 엘리먼트에 의해 생성되는 광자들에 기초하여 수용 정보를 형성하도록 구성되고, 상기 센서는 상기 광자 수용기로부터 상기 수용 정보를 수용하고 그리고 상기 수용 정보에 기초하여 상기 복수의 하전 입자 빔들의 특징을 결정하기 위한 제어 유닛을 더 포함하는,

센서.

#### 청구항 10

패턴을 타겟의 표면에 전사하기 위한 하전 입자 빔릿 리소그래피 시스템으로서,

제 8 항에 따른 센서를 포함하는,

시스템.

#### 청구항 11

제 10 항에 있어서,

상기 센서는, 상기 복수의 하전 입자 빔릿들 각각을 수용하는 것에 응답하여 동시에 신호를 생성함으로써 동시에 상기 빔릿들 각각에 대해 복수의 하전 입자 빔릿들의 하나 또는 그 초과의 특징들을 결정하도록 적응되는,

시스템.

#### 청구항 12

제 10 항에 있어서,

- 복수의 하전 입자 빔릿들을 생성하기 위한 빔릿 생성기;

- 전사될 패턴에 따라 상기 하전 입자 빔릿들을 변조하기 위한 변조 시스템;

- 상기 변조된 빔릿들을 상기 타겟의 표면 상으로 포커싱하기 위한 전자-광학 시스템;

- 상기 타겟 또는 상기 센서 중 어느 하나의 표면에 걸쳐 상기 포커싱된 빔릿들을 굴절시키기 위한 굴절 시스템을 더 포함하는,

시스템.

#### 청구항 13

충돌하는 하전 입자들을 광자들로 선택적으로 변환하도록 배열된 변환기 엘리먼트를 제조하는 방법으로서,

- 하전 입자들을 광자들로 변환하기 위한 변환 재료를 포함하는 기판을 제공하는 단계;

- 전기적 도전성 재료를 포함하는 제 1 층, 예칭 정지 재료(etch stop material)를 포함하는 제 2 층 및 제 3 재료를 포함하는 제 3 층으로 상기 기판을 후속으로 코팅하는 단계;

- 상기 제 3 층의 상부 상에 레지스트층을 제공하는 단계;

- 제 1 미리결정된 패턴을 형성하기 위해 상기 레지스트층을 패터닝, 및 현상하고, 상기 제 3 층이 노출될 때까지 상기 현상된 레지스트층을 예칭하는 단계;

- 추가적인 예칭 정지 재료를 포함하는 제 4 층으로 상기 노출된 제 3 층을 코팅하는 단계;

- 상기 제 3 층이 제 2 미리결정된 패턴에 따라 노출되도록 상기 현상된 레지스트층을 리프팅하는 단계 – 상기 제 2 미리결정된 패턴은 상기 제 1 미리결정된 패턴의 반전임 – ;

- 상기 제 2 층이 노출될 때까지 상기 제 2 미리결정된 패턴에 따라 상기 제 3 층을 예칭하는 단계; 및

- 상기 제 1 층이 노출될 때까지 상기 제 2 미리결정된 패턴에 따라 상기 제 2 층 및 상기 제 4 층을 예칭하는 단계를 포함하는,

변환기 엘리먼트 제조 방법.

#### 청구항 14

제 13 항에 있어서,

상기 예칭 정지 재료 및 상기 추가적인 예칭 정지 재료 중 적어도 하나는 크롬을 포함하는,

변환기 엘리먼트 제조 방법.

#### 청구항 15

제 13 항 또는 제 14 항에 있어서,

상기 제 1 층의 전기적 도전성 재료는 티타늄 및 알루미늄 중 적어도 하나를 포함하는,

변환기 엘리먼트 제조 방법.

#### 청구항 16

제 13 항 또는 제 14 항에 있어서,

상기 제 3 재료는 텅스텐을 포함하는,

변환기 엘리먼트 제조 방법.

#### 청구항 17

제 13 항 또는 제 14 항에 있어서,

상기 기판의 변환 재료는 섬광 재료를 포함하는,

변환기 엘리먼트 제조 방법.

#### 청구항 18

삭제

#### 청구항 19

삭제

#### 청구항 20

삭제

청구항 21

삭제

청구항 22

삭제

청구항 23

삭제

## 발명의 설명

### 기술 분야

[0001] 본 발명은 하전 입자 리소그래피 시스템(charged particle lithography system), 특히, 무마스크(maskless) 하전 입자 시스템, 센서, 특히 하전 입자 빔 속성들을 결정하기 위한 센서, 변환기 엘리먼트뿐만 아니라 이들의 제조 방법에 관한 것이다.

### 배경 기술

[0002] 하전-입자 빔릿 리소그래피 시스템(charged particle beamlet lithography system)은 패턴을 타겟의 표면으로 전사하기 위해 복수의 하전 입자 빔릿들을 사용한다. 빔릿들은, 턴 온 또는 오프될 수 있는 빔릿을 생성하기 위해 그들의 궤적이 제어 가능하게 차단될 수 있으면서 타겟 표면에 걸쳐 스캐닝됨으로써 패턴을 기록할 수 있다. 차단은 차단 표면 상의 빔릿들의 정전기 굴절에 의해 설정될 수 있다. 부가적으로, 또는 대안적으로, 빔릿들의 크기 및 형태는 궤적에 따라 적응될 수 있다. 굴절, 형상화 및/또는 크기 적응은, 예를 들면, 개구 어레이, 정전기 굴절기들의 어레이 및/또는 빔릿 블랭커들(blankers)과 같은 하나 이상의 전자 광학 컴포넌트들에 의해 실행될 수 있다. 패턴을 타겟 표면으로 전사하기 위해, 타겟 표면에 걸친 빔릿들의 이동과 조합하여 빔릿들의 제어 가능한 차단은 변조 정보에 따라 수행된다. 다수의 하전 입자 빔릿 리소그래피 시스템의 예는, 인용에 의해 전체 내용이 본원에 통합되는 미국 특허 제 6,958,804 호에 기재되어 있다.

[0003] 그러한 리소그래피 시스템들은 매우 많은 수, 즉, 10,000 개 정도 또는 그 이상, 예를 들면, 13,000 개의 빔릿들을 가질 수 있다. 미래의 설계들은 심지어 1,000,000 개 정도의 빔릿들의 수를 예상한다. 현재 전자 빔 리소그래피 시스템들은 일반적으로 고해상도로 타겟 표면을 패터닝할 수 있는 것을 목표로 하고, 일부 애플리케이션들은 100 nm 피처 크기들 미만의 우물(well)의 임계 치수를 갖는 패턴들을 이미징할 수 있다.

[0004] 상업적으로 실행 가능한 그러한 다수의 빔릿, 고해상도 리소그래피 시스템에 대해, 하전 입자 빔릿들 각각의 위치가 정밀하게 알려지고 제어되는 것이 중요하다. 부가적으로, 타겟 표면에서 빔릿들의 스팟 크기 및 형상 및 강도의 지식 및 제어가 또한 중요하다. 그러나, 제조 허용 오차들 및 열적 드리프트와 같은 다양한 상황들로 인해, 그러한 빔릿 특성들은 그들의 예상되고 원하는 특성들로부터 벗어나고, 이것은 이러한 일탈한 빔릿들이 정확한 패터닝에 대해 무효하게 할 수 있다.

[0005] 그러한 일탈들은, 다른 것들 중에서도, 위치에서의 일탈, 타겟 표면 상에서 노출되는 스팟 크기에서의 일탈 및/또는 빔릿 강도에서의 일탈을 포함할 수 있다. 빔릿 일탈은 기록될 패턴의 품질에 심각하게 악영향을 줄 수 있다. 따라서, 정확한 측정들이 취해질 수 있도록 이러한 일탈을 검출하는 것이 바람직하다.

[0006] 종래의 리소그래피 시스템들에서, 각각의 빔릿의 위치는 빔릿 위치의 빈번한 측정에 의해 결정된다. 빔릿 위치의 지식을 통해, 빔릿은 정확한 위치로 시프트될 수 있다. 정확한 기록을 위해, 몇 나노미터 정도의 거리 내에서 빔릿 위치를 결정하는 것이 이롭다.

[0007] 알려진 빔릿 위치 교정 방법들은 일반적으로 적어도 3 개의 단계들: 빔릿의 위치가 측정되는 측정 단계, 빔릿의 측정된 위치가 그 빔릿의 원하는 예상된 위치와 비교되는 계산 단계, 및 측정된 위치 및 원하는 위치 사이의 차이가 보상되는 보상 단계를 포함한다. 보상은 리소그래피 시스템의 소프트웨어 또는 하드웨어 중 어느 하나에서 수행될 수 있다.

[0008] 진보된 하전 입자 빔릿 리소그래피 시스템들에서, 위치 제어 이외에, 빔릿 스팟 크기 제어가 동일하게 중요할

수 있다. 스팟 크기 측정들에 대한 원하는 규격들은 30 nm 내지 150 nm 범위의 빔릿 스팟 크기들; 5 nm보다 작은 3 시그마 값을 갖는 스팟 크기 측정들의 정확성; 및 5 nm보다 작은 3 시그마 값을 갖는 단일 센서 내의 그러한 스팟 크기 측정들의 재생 가능성의 결정을 포함한다.

[0009] 타겟 표면 패터닝 정확성을 개선하도록 초기 위치 및/또는 스팟 크기 교정을 허용하기 위해, 리소그래피 시스템의 동작 동안에 빔릿 위치 및/또는 빔릿 스팟 크기와 같은 특성을 결정하는 것이 바람직하다. 스루풋, 즉, 미리결정된 시간의 기간 내에 패터닝될 수 있는 타겟 표면들의 수에 대한 부정적인 효과들을 제한하기 위해, 하전 입자 빔릿들의 특성들을 측정하는 방법이 정확성을 희생하지 않고 제한된 시간 기간 내에 수행될 수 있는 것이 바람직하다.

[0010] 매우 많은 하전 입자 빔릿들의 속성들을 측정하고, 특히 리소그래피 시스템에서 사용되는 하전 입자 빔릿들에 대한 센서는, 본 출원인에게 양도된 미국 공개 특허 출원 제 2007/057204 호에 기재되어 있고, 그로 인해 그 특허 출원의 내용은 인용에 의해 전체가 본원에 통합된다.

[0011] US 제 2007/057204 호는, 하전 입자 빔릿들이 형광 스크린 또는 도핑된 YAG 재료와 같은 변환기 엘리먼트를 사용하여 광 빔들로 변환되는 방법 및 센서를 기재하고 있다. 후속으로, 광 빔들은 다이오드들, CCD 또는 CMOS 디바이스들과 같은 광 감지 검출기들의 어레이에 의해 검출된다. 단일 동작으로 매우 많은 광 감지 검출기들을 판독함으로써 비교적 빠른 측정이 성취될 수 있다. 부가적으로, 센서 구조, 특히, 광 검출기들의 어레이에는, 리소그래피 시스템의 스테이지 부분의 영역에서 과도하게 큰 구조적 측정들을 필요로 하지 않고, 다수의 빔들의 매우 작은 피치들이 측정되는 것을 가능하게 한다.

[0012] 그러나, 스루풋의 손실 없이, 작은 치수들에 관한 산업의 계속해서 증가하는 요구들을 고려하여, 리소그래피 시스템들, 특히, 높은 스루풋을 제공하도록 설계된 매우 많은 하전 입자 빔릿들을 포함하는 리소그래피 기계들에서 빔릿 속성들의 측정을 위한 훨씬 더 정확한 디바이스들 및 기술들을 제공할 필요성이 존재한다.

### 발명의 내용

[0013] 본 발명의 목적은 개선된 해상도 성능을 갖는 하전 입자 리소그래피 시스템에서 사용하기에 적절한 더 정확한 센서를 제공하는 것이다. 이러한 목적을 위해, 본 발명은 하나 이상의 하전 입자 빔릿들의 하나 이상의 특징들을 결정하기 위한 센서를 포함하는, 패턴을 타겟의 표면으로 전사하기 위한 하전 입자 빔릿 리소그래피 시스템을 제공하고, 상기 센서는 하전 입자들을 수용하고 이에 응답하여 광자들(photons)을 생성하기 위한 변환기 엘리먼트를 포함하고, 상기 변환기 엘리먼트는 하나 이상의 하전 입자 빔릿들을 수용하기 위한 표면을 포함하고, 상기 표면에는 하나 이상의 개별적인 빔릿들을 평가하기 위한 하나 이상의 셀들이 제공되고, 각각의 셀은 상기 변환기 엘리먼트 표면에 걸쳐 미리결정된 빔릿 스캔 궤적을 따라 차단 및 비차단 영역들 사이의 전이들(transitions)에서 다수의 나이프 에지들(knife edges)을 형성하는 미리결정된 차단 패턴의 하나 이상의 하전 입자 차단 구조들을 포함하고, 상기 변환기 엘리먼트 표면은 상기 하전 입자들에 대해 실질적으로 침투 가능하고 주변 광(ambient light)에 대해 실질적으로 침투 불가한 코팅층으로 커버되고, 상기 센서는 상기 코팅층 및 상기 차단 구조들 사이의 전기적으로 도전성 층을 더 포함한다.

[0014] 코팅층은 센서가 변환기 엘리먼트 표면의 상당한 영역, 예를 들면, 약  $3 \times 3 \text{ mm}^2$ 의 영역에 걸쳐 하전 입자들의 수신에 더 균일한 방식으로 응답하도록 허용한다. 코팅층은 주변 광, 예를 들면, 배경 방사 등으로부터의 로컬 영향들을 제거한다. 결과적으로, 복수의 빔릿들은 고해상도로 동시에 감지될 수 있다. 코팅층에서 사용하기 위한 적절한 재료들은 티타늄(Ti) 및 알루미늄(Al)을 포함한다.

[0015] 차단 구조들은 일반적으로 텅스텐(W)과 같은 중금속을 포함하고, 기판의 상부 상에 그러한 구조들을 제공하는 것은 일반적으로 하나 이상의 에칭 단계들을 포함한다. 전기적으로 도전성 층에서 사용되는 재료는 그러한 에칭 단계들에 대해 높은 선택성을 갖는 것이 바람직하다. 전기적으로 도전성 층을 형성하는 재료에 포함될 수 있는 적절한 재료는 크롬(Cr)이다. Cr을 사용하는 이점은, Cr이 Ti와 동일한 방식으로 증착될 수 있어서, 상당한 양의 부가적인 노력 또는 어려움 없이 이것이 적용될 수 있다는 것이다.

[0016] 실시예에서, 본 발명은 충돌하는 하전 입자들을 광자들로 선택적으로 변환하도록 구성된 변환기 엘리먼트를 제조하는 방법에 관한 것이다. 상기 방법은: 하전 입자들을 광자들로 변환하기 위한 변환 재료를 포함하는 기판을 제공하는 단계; 전기적으로 도전성 재료를 포함하는 제 1 층, 에칭 정지 재료(etch stop material)를 포함하는 제 2 층 및 제 3 재료를 포함하는 제 3 층으로 상기 기판을 후속으로 코팅하는 단계; 상기 제 3 층의 상부 상에 레지스트층을 제공하는 단계; 제 1 미리결정된 패턴을 형성하기 위해 상기 레지스트층을 패터닝, 및 현상

하고, 상기 제 3 층이 노출될 때까지 상기 현상된 레지스트층을 에칭하는 단계; 추가적인 에칭 정지 재료를 포함하는 제 4 층으로 상기 노출된 제 3 층을 코팅하는 단계; 상기 제 3 층이 제 2 미리결정된 패턴에 따라 노출되도록 상기 현상된 레지스트층을 리프팅하는 단계 – 상기 제 2 미리결정된 패턴은 상기 제 1 미리결정된 패턴의 반전임 – ; 상기 제 2 층이 노출될 때까지 상기 제 2 미리결정된 패턴에 따라 상기 제 3 층을 에칭하는 단계; 및 상기 제 1 층이 노출될 때까지 상기 제 2 미리결정된 패턴에 따라 상기 제 4 층 및 상기 제 2 층을 에칭하는 단계를 포함한다.

[0017] 본 발명의 특징들 및 이점들은 다음의 도면들을 참조하여 인식될 것이다.

### 도면의 간단한 설명

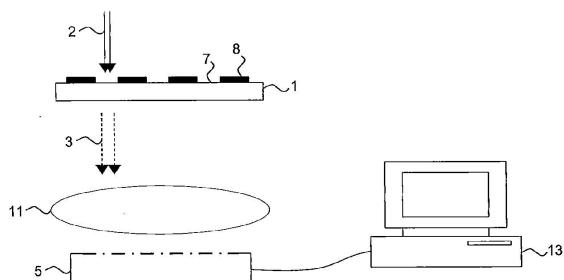

[0018] 도 1은 하전 입자들을 광자들로 변환하는 기판을 사용하는 센서의 개념을 간략히 도시한 도면.

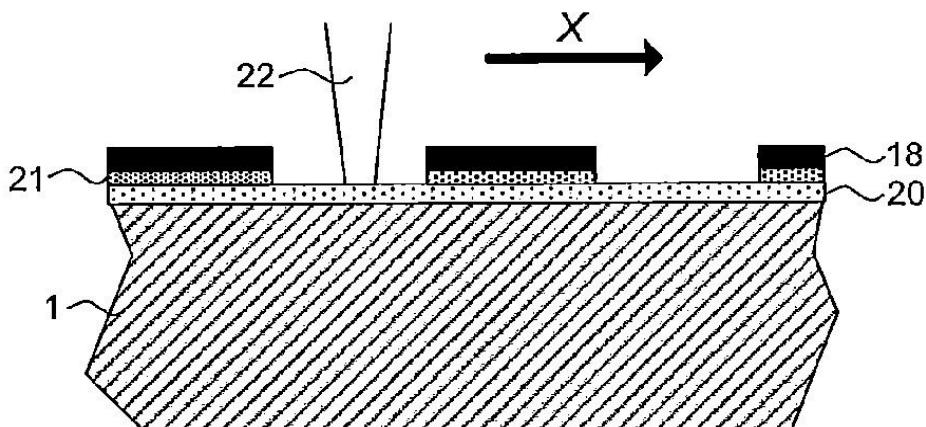

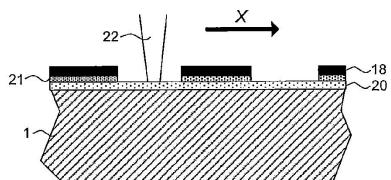

도 2a는 차단 구조가 제공된 변환기 엘리먼트의 단면을 간략히 도시한 도면.

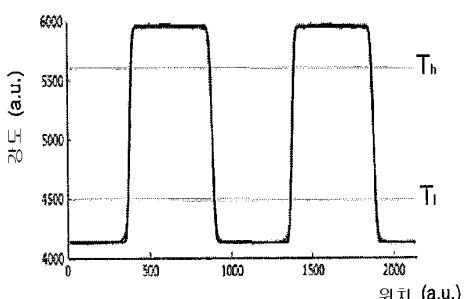

도 2b는 도 2a의 차단 구조에 대한 위치의 함수로서 전사된 강도를 도시한 그래프.

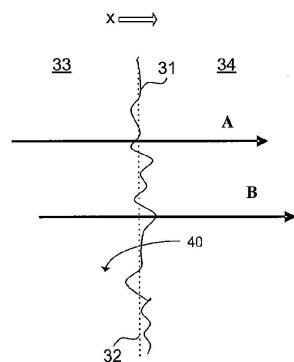

도 2c는 라인 예지 거칠기에 관련된 문제점을 간략히 도시한 도면.

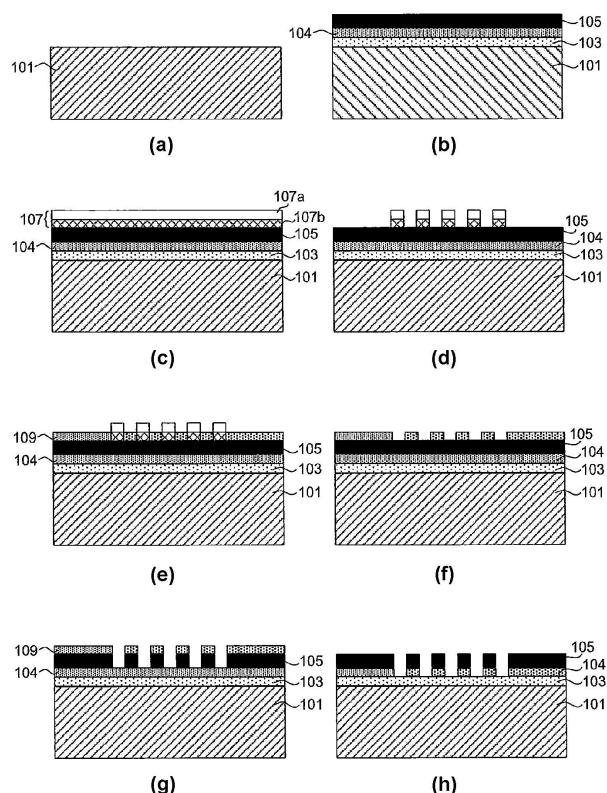

도 3a-도 3h는 변환기 엘리먼트를 제조하는 방법의 상이한 스테이지들을 간략히 도시한 도면.

### 발명을 실시하기 위한 구체적인 내용

[0019] 다음은 도면들을 참조하여 단지 예로서 주어진 본 발명의 특정 실시예들의 설명이다.

[0020] 도 1은 입자 빔들의 하나 이상의 특징들, 특히, 하전 입자 빔럿들의 하나 이상의 특징들을 결정하기 위한 센서의 동작을 간략히 도시한다. 센서는 변환기 엘리먼트(1) 및 광자 수용기(5)를 포함한다. 변환기 엘리먼트에는 하전 입자 차단 영역들(8) 및 비차단 영역들로서 또한 지칭되는 하전 입자 전사 영역들(7)을 포함하는 패턴이 제공된다. 변환기 엘리먼트(1)는 하전 입자들(2)을 수신하고 응답하여 광자들(3)을 생성하도록 구성된다. 광자들(3)은 광학 시스템(11)에 의해 광자 수용기(5)를 향해 지시될 수 있다. 광자 수용기(5)는 하전 입자들(2)의 하나 이상의 특징들을 결정하기 위해 제어 유닛, 예를 들면, 컴퓨터(13)에 통신 가능하게 연결된다.

[0021] 변환기 엘리먼트(1)는 형광 엘리먼트, 예를 들면, 형광 스크린, 또는 섬광 엘리먼트, 예를 들면, 도핑된 YAG(yttrium aluminum garnet) 재료의 기판의 형태를 취할 수 있다. 이후에, 본 발명의 실시예들은 변환기 엘리먼트(1)로서 사용되는 YAG-스크린과 함께 설명될 것이고, 여기서 YAG-스크린은 YAG(1)로서 지칭될 수 있다.

[0022] 광자 수용기(5)는 복수의 다이오드들, CCD(charged coupled device) 카메라들 또는 CMOS(complementary metal-oxide semiconductor) 카메라들과 같은 임의의 적절한 광 감지 검출기를 포함할 수 있다. 이후에, 광자 수용기(5)는 카메라(5)로서 지칭될 수 있다.

[0023] 부가적으로, 본 발명의 실시예들이 임의의 형태의 (하전) 입자들 또는 광 빔들(2)에 대해 사용될 수 있지만, 이후에, 본 발명의 실시예들은 전자들을 참조하여 논의될 것이다.

[0024] 빔럿 크기가 나노미터 범위 내에 있는 전자 빔럿 디바이스들, 예를 들면, 전자 현미경들, 전자 빔 리소그래피 장치, 및 전자 빔 패턴 생성기들에서, 변환기 엘리먼트(1)에 의한 변환에 의해 생성된 광자들의 직접적인 관찰은, 해상도가 변환기 엘리먼트(1)의 파장에 의해 제한되기 때문에 전자 빔럿의 위치와 같은 특성들의 결정을 가능하게 하기에 불충분하다.

[0025] 정확성을 개선하기 위해, 전자 빔럿은 나이프 에지들(knife edges)로서 또한 지칭되는 날카로운 에지들이 제공된 전자 차단 구조에 걸쳐 스캐닝될 수 있다. 나이프 에지가 제공된 변환기 엘리먼트를 사용하는 센서의 예는 미국 특허 출원 제 2007/057204 호에 기재되어 있다.

[0026] 도 2a는, 전자 차단 구조가 제공된 전자 빔럿 수용 표면을 포함하는 YAG(1)의 단면을 간략히 도시한다. 전자 차단 구조는 전자들을 차단할 수 있는 층(18)이 제공된 전자 차단 영역들을 포함한다. 차단층(18)은 금속층일 수 있다. 전자들을 차단하기 위한 적절한 재료는 텅스텐이다. 차단 영역들 사이에는 비차단 영역들이 존재한다. 전자 차단 구조의 비차단 영역에 충돌하는 전자 빔(22)은 실제로 YAG(1)의 표면 또는 YAG의 표면 상의 코딩에 충돌한다.

[0027] 전자들을 차단하기 위한 부분들 내에서, 차단층(18) 이외에, 부가적인 층(21)이 존재한다. 부가적인 층(21)은

차단층(18)의 균일성을 증가시킬 목적으로 기능한다. 부가적인 층(21)은 금속층일 수 있다. 부가적인 층(21)에서 사용하기 위한 특히 적절한 재료의 예는 크롬이다.

[0028] YAG(1)는 코팅층(20)으로 코팅될 수 있다. 코팅층(20)은 배경 방사(background radiation)를 차단하기 위한 금속층일 수 있다. 한편 코팅층(20)은 실질적으로 하천 입자들에 대해 침투 가능하지만, 반면에 실질적으로 주변 광(ambient light)에 대해 침투 불가하다. 이러한 이유로, 코팅층(20)의 두께는 양자의 기능들을 설정하기에 충분하다. 코팅층(20)에 대한 적절한 재료들은 알루미늄 및 티타늄을 포함한다.

[0029] 상술된 바와 같이, 전자 빔(22)의 하나 이상의 특징들을 결정하기 위해, 전자 빔(22)은 YAG(1) 상에 제공된 차단 구조에 걸쳐 (도 2a에서 X-방향으로 표기된 방향으로) 스캐닝될 수 있다. 이에 응답하여, YAG(1) 내에서 생성된 광자들은 카메라에 의해 검출될 수 있다. 그러한 스캐닝 및 검출 동작의 예시적인 결과는 도 2b에 간략히 도시된다.

[0030] 도 2b는 변환기 엘리먼트(1)의 표면에 걸쳐 전자 빔(22)의 x-위치의 함수로서 변환기 엘리먼트(1)에 의해 방출된 광의 강도를 나타내는 그래프를 도시한다. 전자 빔(22)이 비차단 영역에 전체적으로 위치될 때, 최대 응답은 관찰되고, 전자 빔(22)이 차단 영역의 상부 상에 전체적으로 위치되는 경우에, 최소 광이 생성된다. 나이프 에지의 교차는 광 강도의 급격한 변화를 발생시킨다.

[0031] 일부 실시예들에서, 측정 결과들의 강건한 프로세싱을 제공하기 위해, 더 높은 임계값  $T_h$ 을 초과하는 강도 레벨들은 고레벨의 신호 값들로서 프로세서에 제공된다. 마찬가지로, 더 낮은 임계값  $T_l$  아래의 검출된 강도 레벨들은 저레벨의 신호 값들로서 제공될 수 있다. 임계값들  $T_h$ ,  $T_l$ 의 사용은 디지털 프로세싱의 사용을 가능하게 할 수 있다.

[0032] 미리결정된 방향으로 전자 빔을 스캐닝할 때, 전자 빔럿은 나이프 에지를 교차하는 동안에 2 개의 형태들의 상황들을 접할 수 있다. 제 1 상황에서, 빔럿은 차단 영역으로부터 비차단 영역으로의 전이(transition)를 경험한다. 제 2 상황에서, 빔럿은 비차단 영역으로부터 차단 영역으로의 전이를 경험한다.

[0033] 제 1 상황에 대응하는 전이 동안에 접하게 되는 나이프 에지들은 제 1 형태의 나이프 에지들로서 지칭될 수 있다. 마찬가지로, 제 2 상황에 대응하는 전이 동안에 접하게 되는 나이프 에지들은 제 2 형태의 나이프 에지들로서 지칭될 수 있다. 따라서, 나이프 에지의 형태는 측정될 빔럿의 스캐닝 방향에 의존한다. "유사한 형태의 나이프 에지들"에 대해 참조가 이루어지면, 이것은 수반된 모든 나이프 에지들이 제 1 형태의 나이프 에지들에 관련되거나 제 2 형태의 나이프 에지들에 관련된다는 것을 의미한다.

[0034] 변환기 엘리먼트 표면의 전자-수용 표면 상에 제공된 나이프 에지 패턴의 지식은 빔럿의 하나 이상의 특징들의 결정을 허용한다. 도 1을 참조하여 설명된 바와 같은 센서, 및 도 2a를 참조하여 설명된 바와 같은 나이프 에지 패턴을 사용함으로써 측정될 수 있는 특징들은 빔럿 위치 및 빔럿 스팟 크기를 포함하고, 여기서 스팟 크기는 변환기 엘리먼트(1)의 표면 상의 전자 빔럿의 크기에 관련된다.

[0035] 예를 들면, 빔럿 위치는, 도 2b에 도시된 바와 같이, 변환기 엘리먼트의 표면에 걸쳐 빔럿을 x-방향으로 스캐닝하고, 변환기 엘리먼트에 의해 방출된 광의 강도가 최대치로부터 최소치로 또는 최소치로부터 최대치로 변하는 위치를 측정함으로써 측정될 수 있다. 예를 들면, 강도가 최대치로부터 최소치로 변할 때, 이것은 빔럿이 비차단 영역으로부터 차단 영역으로 전이하는 나이프 에지에 걸쳐 x 방향으로 스캐닝된다는 것을 나타낸다. 그러나, 빔럿이 어떠한 나이프 에지에 위치되는지에 관하여 불확실성이 존재할 수 있다.

[0036] 빔럿의 크기는, 예를 들면, 빔럿이 나이프 에지에 걸쳐 스캐닝됨에 따라 강도가 최대치로부터 감소하기 시작하는 지점 및 강도가 최소치에 도달하는 지점 사이의 거리를 측정함으로써 결정될 수 있다. 이것은 빔럿이 부분적으로 차단되고 부분적으로 차단되지 않는 거리를 나타낸다. 마찬가지로, 빔럿 크기는, 빔럿이 나이프 에지에 걸쳐 스캐닝됨에 따라 최대 강도를 감지한 것 및 최소 강도를 감지한 것 사이의 시간을 측정하고, 빔럿의 스캐닝 속도를 곱셈함으로써 결정될 수 있다. 이러한 측정들은 또한 빔럿이 최소 강도로부터 최대 강도로 이동하는 반대 나이프 에지 상에서 수행될 수 있다.

[0037] 도 2b에 도시된 측정, 및 빔럿 위치 및 빔럿 크기 측정들의 논의가 수반되는 차단 및 비차단 영역들의 폭보다 작은 치수들을 갖는 빔럿에 관련된다는 것을 유의하라. 이러한 치수들 및 폭들은 사용되는 스캔 방향에 평행인 방향을 따라 취해지는 것이 바람직하다.

[0038] 많은 애플리케이션들에서, 단일 나이프 에지는 충분한 정확성으로 빔럿 특징들을 획득하기에 적절하지 않다.

특히, 나이프 에지의 소위 라인 에지 거칠기(LER)는 범럿 측정들의 정확성을 제한할 수 있다. 도 2d는 LER에 관련된 문제점을 간략히 예시한다. 도 2d에서, 센서는 전자 차단 영역(33) 및 전자 비차단 영역(34)을 분리하는 나이프 에지(31)에 걸쳐 이동되는 범럿의 강도를 검출하도록 구성된다. 나이프 에지(31)는 점선(32)에 의해 표시된 바와 같은 배향 및 형상을 갖도록 설계된다.

[0039] 실제로 궤적 B가 뒤따르지만, 범럿이 나이프 에지(31)에 걸쳐 차단 영역(33)으로부터 비차단 영역(34)을 향한 궤적 A을 따른다는 가정 하에서 범럿의 x-위치가 검출되면, 스캐닝 방향에서 범럿 위치는 양자의 궤적들에 대해 동일해야 한다. 결국에는, 양자의 궤적들이 동일한 x-위치에서 점선(32)과 교차한다. 그러나, 도 2d에서 용이하게 보여질 수 있듯이, 나이프 에지(31)의 라인 에지 거칠기로 인해, 궤적 A에 대한 범럿의 측정된 x-위치는 궤적 B에 대한 측정된 x-위치와 상이할 것이다. 이러한 예에서, 단일의 나이프 에지(31)의 교차에 기초하여 x-위치를 결정하는 것은 부정확한 결과를 제공한다.

[0040] 도 3a 내지 도 3h는 변환기 엘리먼트, 예를 들면, 도 2a를 참조하여 논의된 바와 같은 변환기 엘리먼트를 제조하는 방법의 상이한 스테이지들을 간략히 도시한다. 변환기 엘리먼트는 충돌하는 하전 입자들을 광자들로 선택적으로 변환하도록 구성된다.

[0041] 먼저, 도 3a에 도시된 바와 같이, 센서의 부가적인 층들을 지지하기 위한 기판(101)이 제공된다. 본 명세서에 걸쳐, 기판(101) 및 그 위에 도포된 구조들의 조합은 변환기 엘리먼트로서 지칭된다. 기판(101)은 하전 입자들을 광자들로 변환하기 위한 변환 재료를 포함한다. 그러한 변환 재료는 섬광 재료일 수 있다. 특히, 전자들이 하전 입자들로서 사용되는 애플리케이션들에 대해, 적절한 섬광 재료는 YAG(yttrium aluminum garnet)를 포함하는 재료일 수 있다.

[0042] 후속으로, 도 3b에 도시된 바와 같이, 하전 입자들의 수용을 위해 구성된 기판(101)의 표면 측면은, 통상적으로 금속층들인 하나 이상의 층들로 코팅된다. 그 층들은 전기적으로 도전성 재료를 포함하는 제 1 층(103)을 포함한다. 제 1 층(103)은 실질적으로 주변 광에 대해 실질적으로 침투 불가하고, 즉, 그 층은 배경 방사를 차단하도록 구성된다. 그러한 배경 광 차단층은 배경광이 변환기 엘리먼트에 의해 생성된 광과 간섭하는 것을 방지함으로써 센서의 품질을 개선한다. 제 1 층(103)은 또한 하전 입자 범럿들에 대해 실질적으로 침투 가능하다. 이러한 이유로, 제 1 층(103)은 일반적으로 약 30 내지 약 80 nm 범위의 두께를 갖는다. 제 1 금속에 대해 적절한 재료들은 티타늄 및 알루미늄을 포함하고, Ti는 시간에 걸쳐 덜 산화되고, 따라서 상기 층의 지속적인 표면 균일성을 유지하기 더 좋은 것으로서 바람직하다.

[0043] 부가적으로, 그 층들은 제 2 재료를 포함하는 제 2 층(104)을 포함한다. 제 2 재료는 바람직하게는 습식 애칭 및 건식 애칭 프로세스들 양자에 대해 애칭 프로세스를 정지할 목적으로 기능하는 애칭 정지 재료이다. 제 2 층의 사용은, 특히 재료가 높은 애칭 민감도를 갖는 경우에 애칭 품질을 개선시킬 수 있다. 제 2 층은 더 날카로운 에지들의 실현에서 특히 유용할 수 있다. 제 2 재료에 대해 적절한 재료는 크롬이다.

[0044] 그 층들은 제 3 재료를 포함하는 제 3 층(105)을 더 포함한다. 제 3 재료는 하전 입자 범럿들을 차단할 목적으로 기능한다. 제 3 층에 대해 적절한 재료는, 제한된 두께의 층을 가지면서 하전 입자들 및 주변광을 차단하는 재료이다. 적절한 재료는 텅스텐이고, 이러한 경우에 적절한 두께는 50 내지 500 nm의 범위 내에 있을 것이다. 그러한 두께는 인입하는 하전 입자들을 충분히 차단하기에 충분한 두께이다. 반면에, 그러한 두께는 디포커스 및 에지 거칠기와 같은 효과들에 대해 무시할만한 영향력을 갖는다.

[0045] 다수의 층들(103, 104, 105)의 상부 상에, 레지스트층(107)이 제공된다. 도 3c에 간략히 도시된 바와 같이, 레지스트층(107)은 단일 레지스트층일 수 있거나, 대안적으로, 상부층(107a), 하부층(107b) 각각을 포함하는 이중 레지스트층일 수 있다. 단일 레지스트층(107)에 대해 추가적인 참조가 이루어질 것이다.

[0046] 그후, 레지스트층(107)은 제 1 미리결정된 패턴에 대응하여 패터닝된다. 패터닝 후에, 레지스트층(107)은 일반적으로 당분야에 알려진 방식으로 현상 및 애칭 단계들을 겪는다. 애칭은, 제 3 층(105)이 노출될 때까지 수행된다. 레지스트층(107)을 패터닝, 현상 및 애칭한 예시적인 최종 결과가 도 3d에 간략히 도시된다.

[0047] 애칭 후에, 도 3e에 간략히 도시된 바와 같이, 노출된 제 3 층(105)은, 예를 들면, 증발에 의해 제 4 층(109)으로 코팅된다. 일반적으로, 제 4 층(109)은 금속층이다. 제 4 층(109)은 애칭 정지 층으로서 기능할 수 있고, 애칭 품질을 개선할 수 있다. 층(109)은 제 2 층(104)에서 사용된 것과 동일한 재료, 예를 들면, 크롬을 포함할 수 있다.

[0048] 제 4 층(109)의 증착 후에, 도 3f에 간략히 도시된 바와 같이, 현상된 레지스트는 제 3 층(105)이 제 2 미리결정된 패턴에 따라 노출되도록 리프트 오프(lift off)에 의해 제거된다. 제 2 미리결정된 패턴은 제 1 미리결정

된 패턴의 반전이다.

[0049] 후속으로, 노출된 제3층은 제2층(104)이 노출될 때까지 제2미리결정된 패턴에 따라 에칭된다. 제조 프로세서의 이러한 스테이지에서 변환기 엘리먼트의 간략한 모면이 도3g에 도시된다.

[0050] 마지막으로, 도3h에 간략히 도시된 바와 같이, 제2미리결정된 패턴에 따른 제4층(109) 및 제2층(104)이 제거되고, 제2층(104)은 제1층(103)이 노출될 때까지 제거된다. 제거는 당분야에 알려진 기술들, 예를 들면, 에칭에 의해 수행될 수 있다.

[0051] 결과적인 변환기 엘리먼트는 도2a를 참조하여 설명된 변환기 엘리먼트와 유사하다. 도3a 내지 도3h의 방법이 도2a의 변환기 엘리먼트를 제조하는데 사용될 때, 도2a에서 기판(1) 및 층들(18, 20 및 21)은 기판(101) 및 층들(105, 103 및 104)에 각각 대응한다.

[0052] 본 발명은 위에 논의된 특정 실시예들을 참조하여 기재되었다. 이러한 실시예들이 당업자에게 잘 알려진 다양한 수정들 및 대안적인 형태들로 가능하다는 것이 인식될 것이다. 상술된 것 이외에, 본 발명의 사상 및 범위로부터 벗어나지 않고 본원에 기재된 구조들 및 기술들에 대해 추가적인 수정이 이루어질 수 있다. 따라서, 특정 실시예들이 기재되었지만, 이들은 단지 예들이고 본 발명의 범위를 제한하지 않으며, 본 발명의 범위는 첨부된 청구항들에 규정된다.

## 도면

### 도면1

### 도면2a

### 도면2b

## 도면2c

## 도면3