(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2010-508167

(P2010-508167A)

(43) 公表日 平成22年3月18日(2010.3.18)

(51) Int.Cl.

**B81C 1/00**

F 1

B81C 1/00

テーマコード(参考)

3C081

審査請求 未請求 予備審査請求 未請求 (全 25 頁)

(21) 出願番号 特願2009-535072 (P2009-535072)

(86) (22) 出願日 平成19年10月31日 (2007.10.31)

(85) 翻訳文提出日 平成21年6月30日 (2009.6.30)

(86) 國際出願番号 PCT/EP2007/061731

(87) 國際公開番号 WO2008/053008

(87) 國際公開日 平成20年5月8日 (2008.5.8)

(31) 優先権主張番号 60/863,679

(32) 優先日 平成18年10月31日 (2006.10.31)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 PCT/EP2007/061558

(32) 優先日 平成19年10月26日 (2007.10.26)

(33) 優先権主張国 歐州特許庁(EP)

(71) 出願人 591060898

アイメック

1 M E C

ベルギー、ペー・3001ルーヴァン、カ

ペルドリーフ75番

(71) 出願人 306025156

アースエムエル・ネザーランズ・ベスロ

テン・フェンノートシャップ

A S M L N e t h e r l a n d s B.

V.

オランダ5504デール・フェルトホー

フェン、デ・ルン6501番

(74) 代理人 100101454

弁理士 山田 順二

最終頁に続く

(54) 【発明の名称】マイクロマシンデバイスの製造方法

## (57) 【要約】

本発明は、電気回路を含む基板(10)の上に、少なくとも1つのマイクロマシン構造を含むマイクロマシンデバイスを、下方の電気回路に影響を与えることなく作製する方法を提供する。この方法は、電気回路を含む基板(10)の上に、保護層(15)を形成する工程と、少なくとも1つのマイクロマシン構造を形成するための複数のパターニングされた層を保護層(15)の上に形成する工程であって、複数のパターニングされた層は、少なくとも1つの犠牲層(18)を含む工程と、その後に、犠牲層(18)の少なくとも一部を除去して、少なくとも1つのマイクロマシン構造を開放する工程とを含む。この方法は、更に、保護層(15)を形成する前に、マイクロマシンデバイスの製造中に使用される最高温度より高い温度で基板(10)をアニールする工程を含み、アニールは、その後の製造工程中に、保護層(15)の下での気体の形成を防止する。本発明は、また、本発明の具体例にかかる方法で得られたマイクロマシンデバイスを提供する。

**【特許請求の範囲】****【請求項 1】**

電気回路を含む基板(10)に、少なくとも1つのマイクロマシン構造を含むマイクロマシンデバイスを作製する方法であって、

電気回路を含む基板(10)の上に、保護層(15)を形成する工程と、

少なくとも1つのマイクロマシン構造を形成するための複数のパターニングされた層を保護層(15)の上に形成する工程であって、複数のパターニングされた層は、少なくとも1つの犠牲層(18)を含む工程と、

その後に、犠牲層(18)の少なくとも一部を除去して、少なくとも1つのマイクロマシン構造を開放する工程と、を含み、

更に、保護層(15)を形成する前に、マイクロマシンデバイスの製造中に使用される最高温度より高い温度で基板(10)をアニールする工程を含み、アニールは、その後の製造工程中に、保護層(15)の下での気体の形成を防止する方法。

**【請求項 2】**

更に、保護層(15)の形成前に、 $1 / \text{cm}^2$ より少ない欠陥数を有する誘電体上部層(14)を、基板(10)の上に形成する工程を含む請求項1にかかる方法。

**【請求項 3】**

誘電体上部層(14)を形成する工程は、

基板(10)の上に誘電体層(14)を形成する工程と、

誘電体層(14)を平坦化する工程と、

誘電体層(14)中の欠陥数を、 $1 / \text{cm}^2$ より少なく減らすために基板(10)をアニールする工程と、を含む請求項2の記載の方法。

**【請求項 4】**

実質的に平坦な誘電体上部層(14)を形成する工程は、

基板(10)の上に第1誘電体層(13)を形成する工程と、

第1誘電体層(13)を平坦化する工程と、

下方の層から欠陥や形状を写し取らない堆積技術を用いて、第1誘電体層(13)の上に第2誘電体層を形成し、これにより $1 / \text{cm}^2$ より少ない欠陥数を含む誘電体層(14)を形成する工程と、を含む請求項2に記載の方法。

**【請求項 5】**

第2誘電体層を形成する工程は、高密度プラズマ気相成長により行われる請求項4に記載の方法。

**【請求項 6】**

基板(10)の上に保護層(15)を形成する工程は、実質的に平坦な保護層(15)を形成する工程で行われる請求項1～5のいずれか1項に記載の方法。

**【請求項 7】**

その後の製造工程中に保護層(15)の下での気体の形成を防止するための基板(10)のアニール工程は、マイクロマシンデバイスの製造中に使用される最高温度より、1から10だけ高い温度で行われる請求項1～6のいずれか1項に記載の方法。

**【請求項 8】**

本方法のプロセスパラメータは、マイクロマシンデバイスの製造中および製造後において、保護層(15)が $1 / \text{cm}^2$ より少ない欠陥数を有するように定められる請求項1～7のいずれか1項に記載の方法。

**【請求項 9】**

複数のパターニングされた層を保護層(15)の上に形成する工程は、少なくとも1つの電極を形成するために、電極材料の層を堆積する工程を含む請求項1～8のいずれか1項に記載の方法。

**【請求項 10】**

電極材料の層は、 $\text{Si}_{1-x}\text{Ge}_x$ ( $0.5 < x < 0.65$ )を含む請求項9に記載の方法。

10

20

30

40

50

**【請求項 1 1】**

電極材料の層の堆積は、プラズマエンハンス化学気相成長またはプラズマアシスト化学気相成長で行われる請求項 9 または 10 に記載の方法。

**【請求項 1 2】**

電極材料の層の堆積は、電極材料の層中の応力が、10 MPa より低い引っ張り応力となる堆積温度、堆積圧力、および堆積電力で行われる請求項 9 ~ 11 のいずれか 1 項に記載の方法。

**【請求項 1 3】**

少なくとも 1 つの電極 (17) を形成する工程は、更に、電極材料の層をパターニングする工程を含む請求項 9 ~ 12 のいずれか 1 項に記載の方法。 10

**【請求項 1 4】**

電極材料の層のエッチング工程は、HBr 系反応性イオンエッチングプロセスにより行われる請求項 13 に記載の方法。

**【請求項 1 5】**

電気回路は、少なくとも 1 つの電気接続パッド (12) を含み、この方法は、更に、保護層 (15) の形成後、および複数のパターニングされた層の形成前に、少なくとも 1 つの電気的な導電構造を、下にある電気回路の電気接続パッド (12) が配置される場所に形成する工程を含む請求項 1 ~ 12 のいずれか 1 項に記載の方法。

**【請求項 1 6】**

少なくとも 1 つの電気的な導電構造を形成する工程は、 20

少なくとも 1 つの電気接続パッド (12) から保護層 (15) を通って延びる少なくとも 1 つのビアを形成する工程と、

電気的な導電材料 (16) で、少なくとも 1 つのビアを満たす工程と、

平坦化を行う工程と、を含む請求項 15 に記載の方法。

**【請求項 1 7】**

更に、複数のパターニングされた層を形成した後、および犠牲層 (18) を少なくとも部分的に除去した後に、電気的な導電構造が配置された場所に、犠牲層 (18) を通って少なくとも 1 つの開口部を形成する工程と、

少なくとも 1 つの開口部中に電気的な導電層を形成し、これにより少なくとも 1 つのボンドパッド (20) を形成する工程と、を含む請求項 15 または 16 に記載の方法。 30

**【請求項 1 8】**

請求項 1 ~ 17 のいずれかの製造方法で製造されたマイクロマシンデバイス。

**【請求項 1 9】**

電気回路を含む基板 (10) の上のマイクロマシンデバイスであって、マイクロマシンデバイスは少なくとも 1 つのマイクロマシン構造を含み、電気回路と少なくとも 1 つのマイクロマシン構造との間に、 $1 / \text{cm}^2$  より少ない欠陥数を含む保護層 (15) を含むマイクロマシンデバイス。

**【請求項 2 0】**

更に、電気回路と少なくとも 1 つのマイクロマシン構造との間に、 $1 / \text{cm}^2$  より少ない欠陥密度を有する誘電体層 (14) を含む請求項 19 に記載のマイクロマシンデバイス。 40

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、例えば MEMS (micro-electromechanical system : 微小電気機械システム) デバイスのようなマイクロマシンデバイスに関する。更に、本発明は、例えば CMOS 回路を含む基板のような電気回路を含む基板上に、例えば MEMS のような少なくとも 1 つのマイクロマシン構造を含む、例えば MEMS のようなマイクロマシンデバイスの製造方法、および、それにより得られた、例えば MEMS のようなマイクロマシンデバイスに関する。本方法では、例えば CMOS 回路のような下方の回路に影響を与えることなく、 50

例えばC M O Sのような電気回路を含む基板上にマイクロマシンデバイスを形成することができる。

#### 【背景技術】

##### 【0 0 0 2】

例えば加速度計、ジャイロスコープ、インクジェットプリンタのヘッドのようなマイクロマシンシステム（M E M S）は、使用が増加している。将来の傾向は、高性能でより小型のシステムに向かっている。より小型のシステムと高性能との双方を得る方法は、ドライブ、制御、及び信号処理の電子器機を含むC M O S基板上に、M E M Sのモノリシック集積化を行うことである。これは、例えば容量検出の寄生を減らすことで、M E M Sの性能を改良できる。更に、このアプローチは非常にコンパクトな集積解であり、パッケージを小型化できる。

10

##### 【0 0 0 3】

M E M Sデバイスと埋め込まれた電子器機のモノリシック集積化を得ることは簡単ではない。なぜなら、異なる材料と処理技術が同じ基板上で組み合わせなければならないからである。近年、M E M Sと埋め込まれた電子器機のモノリシック集積化を達成するためには、以下の3つのアプローチがある。（1）最初にM E M Sデバイスを処理し、次に例えばM E M Sデバイスの隣に集積回路を形成する。（2）M E M Sデバイスと集積回路の双方を混合して形成する。（3）最初に集積回路を処理し、次に例えば集積回路の上にM E M Sデバイスを形成する（ポスト処理とも呼ばれる）。

20

##### 【0 0 0 4】

第3のアプローチは、下方の回路技術の深い知識の必要無しに、下方の信号処理回路上でモジュール式にデバイスを処理し相互接続する可能性を提供する。しかしながら、ポスト処理は、許容されるM E M Sプロセスと材料に、非常に厳しい要求を課す。下方の回路のダメージおよび／または下方の回路の性能の低下を避けるために、M E M S作製温度は、450より低くしなければならず、M E M S処理中に使用される化学剤の制限も考慮しなければならない。例えば多結晶のシリコンゲルマニウム（多結晶S i G e）は、M E M Sのポスト処理にとって魅力的な材料である。多結晶S i G eは、S iに似た特性を有するが、多結晶S iで必要とされるより実質的に低い温度で処理できる半導体合金材料である。このため、多結晶S i G eは、好ましい温度で、所望の電気的、機械的特性を有するM E M Sデバイスを作製できる。M E M Sのポスト処理で使用される化学剤に対する下方のC M O S回路を保護するための最新の解決法では、保護層が用いられ、またはC M O S回路に影響する化学剤の使用が避けられる。

30

##### 【0 0 0 5】

米国特許第6,210,988では、電気回路を含む基板上にM E M S構造を作製する方法が記載され、かかる方法では、M E M Sデバイスのグランド面層と構造層が、S i G e層により形成される。一の具体例では、高いG e含有量のS i G e層または純粋のG e層が、M E M S構造の製造プロセスで、犠牲層として使用される。このタイプの犠牲層は、下方の電気回路に影響しない、過酸化水素のような化学剤により除去できる。米国特許第6,210,988の他の具体例では、犠牲層としてシリコン酸化物が使用される。M E M S構造の開放中にH Fによる攻撃からM E M Sデバイスの下方の電気回路を保護するために、犠牲層の形成前に保護層が形成される。この文献で示されるように、アモルファスS iが、この保護層にとって有用な材料であることが見出された。

40

##### 【0 0 0 6】

米国特許第6,917,459では、電気回路を含む基板上に、M E M Sデバイスを形成する方法が記載されている。この方法では、誘電体層が基板上に形成され、この誘電体層は平坦化されて実質的に平坦な面を形成し、誘電体層の平坦化後に保護層が形成される。この保護層は、例えば炭化シリコンのような、続くM E M S処理に使用されるエッティング液に耐性のある材料から形成される。

##### 【0 0 0 7】

しかしながら、上述の方法では、保護層を形成した場合に、下方にある欠陥を複製する

50

ことで、保護層中に欠陥が形成されうる。例えばMEMS層の形成および／またはそれらの層をパターニングするためのエッチングプロセスのような、例えばMEMSデバイスの作成中に保護層の下部に気体が形成された結果、またはMEMS作製中に使用されるプロセスの結果による。保護層中のこのような欠陥の存在は、エッチング液が保護層を突き抜けて、CMOS回路のような下方の電気回路にダメージを与えることとなる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】米国特許第6,210,988号

10

【特許文献2】米国特許第6,917,459号

【発明の概要】

【0009】

本発明の具体例の目的は、電気回路を含む基板にマイクロマシンデバイスを形成する方法、およびそれにより得られたマイクロマシンデバイスを提供することである。

【0010】

第1の形態では、例えばマイクロ電気機械システム(micro-electromechanical: MEMS)デバイスのようなマイクロマシンデバイスを、例えばCMOSのような電気回路を含む基板上に作製する方法であって、MEMSのようなマイクロマシンデバイスは少なくとも1つの例えばMEMSのようなマイクロマシン構造を含む方法を提供する。

20

この方法は、

基板の上に、保護層を形成する工程と、

少なくとも1つの、例えばMEMSのようなマイクロマシン構造を形成するための複数のパターニングされた層を保護層の上に形成する工程であって、複数のパターニングされた層は、少なくとも1つの犠牲層を含む工程と、

その後に、犠牲層の少なくとも一部を除去して、少なくとも1つの、例えばMEMSのようなマイクロマシン構造を開放(release)する工程と、を含む。

【0011】

この方法は、更に、保護層を形成する前に、例えばMEMSのようなマイクロマシンデバイスの製造中に使用される最高温度より高い温度で基板をアニールする工程を含み、アニールは、その後の製造工程中に、保護層の下での気体の形成を防止する。

30

【0012】

マイクロマシンデバイスの製造中に使用される最高温度より高い温度で基板をアニールする工程は、基板の加熱が必要な製造プロセスの工程中に、下方の層からの気体の形成による保護層の損傷を防止する。

【0013】

本発明の具体例にかかる方法は、マイクロマシンデバイスの製造中に、下方の回路の良好な保護を提供する。これは、保護層中の欠陥数を低く保たれることを確認することで行われ、これにより例えば保護層を通る化学剤の貫通のような問題を避ける。

【0014】

保護層は、例えばSiCを含む。本発明の他の具体例では、他の好適な材料を、保護層の形成に使用しても構わない。

40

【0015】

本発明の具体例にかかる方法の長所は、シリコン酸化物(SiO<sub>2</sub>)のような安価で標準的な材料を使用できることであり、例えばGe犠牲層に比較して、これらは容易に平坦化でき、例えば吸着の無い気相HF開放のような標準的な方法により除去できる。

【0016】

本発明の具体例にかかる方法は、更に、保護層の形成前に、1/cm<sup>2</sup>より少ない欠陥数、例えば0.1/cm<sup>2</sup>より少ない、または0.011/cm<sup>2</sup>より少ない欠陥数を有する例えば実質的に平坦な誘電体上部層のような誘電体上部層を基板上に形成する工程を含む。

50

## 【0017】

本発明の具体例では、例えば実質的に平坦な誘電体上部層のような誘電体上部層を形成する工程は、

基板の上に誘電体層を形成する工程と、

誘電体層を平坦化する工程と、

誘電体層中の欠陥数を、 $1 / \text{cm}^2$  より少なく、例えば $0.1 / \text{cm}^2$  より少なく、または $0.01 / \text{cm}^2$  より少なく減らすために基板をアニールする工程と、を含んでも良い。

## 【0018】

本発明の他の具体例では、例えば実質的に平坦な誘電体上部層のような誘電体上部層を形成する工程は、

10

基板の上に第1誘電体層を形成する工程と、

第1誘電体層を平坦化する工程と、

下方の層から欠陥や形状を写し取らない堆積技術を用いて、第1誘電体層の上に第2誘電体層を形成し、これにより $1 / \text{cm}^2$  より少ない、例えば $0.1 / \text{cm}^2$  より少ない、または $0.01 / \text{cm}^2$  より少ない欠陥数を含む誘電体層を形成する工程と、を含んでも良い。

## 【0019】

第2誘電体層を形成する工程は、高密度プラズマ気相成長により行われても良い。

## 【0020】

その後の製造工程中に保護層の下での気体の形成を防止するための基板のアニール工程は、例えばMEMSのようなマイクロマシンデバイスの製造中に使用される最高温度より、1から10だけ高い温度で行われても良い。本発明の具体例で、例えばMEMSのようなマイクロマシンデバイスの製造中に使用される最高温度は450である。他の具体例では、例えばMEMSのようなマイクロマシンデバイスの製造中に使用される最高温度は、450より低く、または400より低い。

20

## 【0021】

本発明の具体例では、基板上に保護層を形成する工程は、実質的に平坦な保護層を形成する工程で行われても良い。

30

## 【0022】

本発明の具体例では、例えばMEMSのようなマイクロマシンデバイスの製造プロセスの材料とプロセスパラメータは、高品質の保護層に影響ないように選択される。高品質とは、保護層が低欠陥密度を有し、製造プロセス中に使用される化学剤に対して低い浸透性を示すことを意味する。換言すれば、例えばMEMSのようなマイクロマシンデバイスの製造プロセスの材料とプロセスパラメータは、例えばMEMSのようなマイクロマシンデバイスの製造中および製造後において、保護層が、 $1 / \text{cm}^2$  より少ない、例えば $0.1 / \text{cm}^2$  より少ない、または $0.01 / \text{cm}^2$  より少ない欠陥数を有し、保護層は、基板と、より重要な基板上の電気回路を、例えば複数のパターニングされた層を形成する処理工程のような更なる処理工程から保護し、犠牲層を部分的に除去する処理工程の影響から保護する。本発明の具体例では、高品質の保護層を得るために、保護層はより平坦に形成され、保護層中の欠陥数が減らされることが好ましい。更には、例えばピンホール、マイクロクラック、または密度変化のような保護層を通じて延びる欠陥の数を実質的にゼロまで減らす。保護層を通じて延びる欠陥を除去または少なくとも低減すると、ポストプロセス（例えばMEMS犠牲層エッチング）中に使用された化学剤が保護層を貫通するのを避けて、下方の電気回路の良好な保護を得ることができる。

40

## 【0023】

本発明の具体例では、プロセスパラメータは、例えば、使用される材料、異なる層を形成するのに使用される堆積方法、堆積温度、および／または異なる層の堆積中に使用される堆積圧力、堆積電力、エッチング技術、および／またはエッチング化学剤である。

## 【0024】

50

複数のパターニングされた層を保護層の上に形成する工程は、少なくとも1つの電極を形成するために、電極材料の層を堆積する工程を含んでも良い。少なくとも1つの電極を形成する工程は、例えば電極材料の層のエッティングのようなパターニングにより行われても良い。

【0025】

電極材料の層は、例えば、 $\text{Si}_{1-x}\text{Ge}_x$  ( $0.5 < x < 0.65$ ) を含んでも良い。電極材料の層は、例えば、プラズマエンハンス化学気相成長またはプラズマアシスト化学気相成長で行われても良い。

【0026】

電極材料の層の堆積は、電極材料の層中の応力が最小になるような、堆積温度、堆積圧力、および堆積電力で行われても良い。電極材料の層中の応力が最小になるとは、電極材料の層中の応力が  $100\text{ MPa}$  より低く、例えば  $50\text{ MPa}$  より低く、または  $10\text{ MPa}$  より低いことを意味する。電極材料の層中の応力は、引っ張りでも良く、残留引っ張り応力と呼ばれるものでも良い。

【0027】

電極材料の層のエッティング工程は、例えば、HBr系反応性イオンエッティングプロセスにより行われても良い。

【0028】

本発明の具体例では、電気回路は、少なくとも1つの電気接続パッドを含む。本発明にかかるこの方法は、それらの具体例では、更に、保護層の形成後、および複数のパターニングされた層の形成前に、少なくとも1つの電気的な導電構造を、下方にある電気回路の電気接続パッドが配置される場所に形成する工程を含んでも良い。

【0029】

少なくとも1つの電気的な導電構造を形成する工程は、

少なくとも1つの電気接続パッドから保護層を通って延びる少なくとも1つのビアを形成する工程と、

電気的な導電材料で、少なくとも1つのビアを満たす工程と、

平坦化を行う工程と、を含んでも良い。

【0030】

本発明の具体例では、少なくとも1つの電気的な導電構造は、電気接続パッドと、例えばMEMSのようなマイクロマシンデバイスの電極との間に、電気接続を形成するものであっても良い。

【0031】

電気接続は、下方の電気回路を、MEMS電極のようなマイクロマシンデバイスの電極と電気的に接続するためと、下方の電気回路を、外部世界（ボンドパッド）と電気的に接続するための、双方に使用されても良い。

【0032】

本発明の具体例では、例えばMEMSのようなマイクロマシンデバイスの処理後に保護層を通る電気接続を形成することにより、MEMS処理後に保護層を通るエッティングの必要性が避けられる。

【0033】

複数のパターニングされた層を形成した後、および犠牲層を少なくとも部分的に除去した後に、この方法は更に、

電気的な導電構造が配置された場所に、犠牲層を通って少なくとも1つの開口部を形成する工程と、

少なくとも1つの開口部中に電気的な導電層を形成し、これにより少なくとも1つのボンドパッドを形成する工程とを含んでも良い。

【0034】

電気的な導電層は、例えばAlおよび/またはTaNを含んでも良い。他の具体例では、電気的な導電層は、当業者に知られた他の適当な材料を含んでも良い。本発明の具体例

10

20

30

40

50

では、少なくとも 1 つの電気的な導電構造は、電気接続パッドとボンドパッドとの間の電気接続を形成しても良い。

【0035】

第 2 の形態では、本発明は、本発明の具体例を用いた製造方法の手段により得られたマイクロマシンデバイスを提供する。

【0036】

第 3 の形態では、本発明は、電気回路を含む基板の上のマイクロマシンデバイスを提供し、このマイクロマシンデバイスは少なくとも 1 つのマイクロマシン構造を含み、電気回路と少なくとも 1 つのマイクロマシン構造との間に、 $1 / \text{cm}^2$  より少ない、例えば $0 . 1 / \text{cm}^2$  より少ない、または $0 . 01 / \text{cm}^2$  より少ない欠陥密度を有する保護層を含む。 10

【0037】

本発明の具体例では、マイクロマシンデバイスは、更に、電気回路と少なくとも 1 つのマイクロマシン構造との間に、 $1 / \text{cm}^2$  より少ない、例えば $0 . 1 / \text{cm}^2$  より少ない、または $0 . 01 / \text{cm}^2$  より少ない欠陥密度を有する誘電体層を含んでも良い。

【0038】

本発明の特定の好ましい形態は、独立請求項と従属請求項に示される。従属請求項の特徴は、独立請求項の特徴や、他の独立請求項との組み合わせても良い。

【0039】

本発明の特徴、長所、および優位点は、図面と組み合わせた詳細な説明中で明らかになるなり、これらは本発明の原理を示す、この記載は、例としてのみ与えられ、本発明の範囲を限定するものでは無い。 20

【図面の簡単な説明】

【0040】

【図 1】本発明の具体例にかかるマイクロマシンデバイスの製造方法の、連続した工程を示す。

【図 2】本発明の具体例にかかるマイクロマシンデバイスの製造方法の、連続した工程を示す。 30

【図 3】本発明の具体例にかかるマイクロマシンデバイスの製造方法の、連続した工程を示す。

【図 4】本発明の具体例にかかるマイクロマシンデバイスの製造方法の、連続した工程を示す。

【図 5】本発明の具体例にかかるマイクロマシンデバイスの製造方法の、連続した工程を示す。

【図 6】本発明の具体例にかかるマイクロマシンデバイスの製造方法の、連続した工程を示す。

【図 7】本発明の具体例にかかるマイクロマシンデバイスの製造方法の、連続した工程を示す。

【図 8】本発明の具体例にかかるマイクロマシンデバイスの製造方法の、連続した工程を示す。

【図 9】本発明の具体例にかかるマイクロマシンデバイスの製造方法の、連続した工程を示す。 40

【図 10】異なる電極材料を用いる実験で使用された試料の概略図を示す。

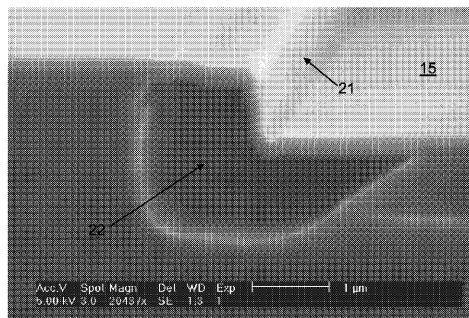

【図 11】気体の HF を用いてエッティングした後の小さな段差を覆う、 $800 \text{ nm}$  膜厚の酸化層と $300 \text{ nm}$  膜厚の SiC 層を有するウエハの SEM 像を示す。

【発明を実施するための形態】

【0041】

本発明は、特定の具体例について、添付図面を参照しながら詳細に説明するが、本発明はこれらにより限定されるものではなく、請求の範囲によってのみ限定されるものである。記載された図面は、単に概略であり、限定するものではない。図面において、図示目的 50

で、いくつかの要素の大きさは拡張され、縮尺通りに記載されていない。寸法と相対寸法は、本発明の実施の実際の縮小には対応していない。

#### 【0042】

更に、明細書や請求の範囲中の、第1、第2等の用語は、類似の要素の間で区別するために使用され、順序や他の方法において、時間的、空間的順序を表す必要はない。そのように使用される用語は、適当な状況下で入替え可能であり、ここに記載された発明の具体例は、ここに記載や図示されたものと異なる順序によつても操作できることを理解すべきである。

#### 【0043】

また、明細書や請求の範囲中の、上、上に、等の用語は、記載目的のために使用され、相対的な位置を示すものではない。そのように使用される用語は、適当な状況下で入替え可能であり、ここに記載された発明は、ここに記載や図示されたものと異なる位置でも操作できることを理解すべきである。

#### 【0044】

また、請求の範囲で使用される「含む (comprising)」の用語は、それ以降に示される要素に限定して解釈されること排除するものであり、他の要素や工程を排除しない。このように、言及された特徴、数字、工程、または成分は、その通りに解釈され、1またはそれ以上の他の特徴、数字、工程、または成分、またはこれらの組み合わせの存在または追加を排除してはならない。このように、「手段AおよびBを含むデバイス」の表現の範囲は、構成要素AとBのみを含むデバイスに限定されるべきではない。本発明では、単にデバイスに関連した構成要素がAとBであることを意味する。

#### 【0045】

この明細書を通じて参照される「一の具体例 (one embodiment)」または「具体例 (an embodiment)」は、この具体例に関係して記載された特定の長所、構造、または特徴は、本発明の少なくとも1つの具体例に含まれることを意味する。このように、この明細書を通して多くの場所の「一の具体例 (one embodiment)」または「具体例 (an embodiment)」の語句の表現は、同じ具体例を表す必要はなく、表しても構わない。更に、特定の長所、構造、または特徴は、この記載から当業者に明らかのように、1またはそれ以上の具体例中で適当な方法で組み合わせることができる。

#### 【0046】

同様に、本発明の例示の記載中において、能率的に開示し、多くの発明の形態の1またはそれ以上の理解を助ける目的で、本発明の多くの長所は、時には1つの具体例、図面、またはその記載中にまとめられることを評価すべきである。しかしながら、この開示の方法は、請求される発明がそれぞれの請求項に記載されたものより多くの特徴を必要とすることを意図して表されていると解釈すべきではない。むしろ、以下の請求項が表すように、発明の態様は、1つの記載された具体例の全ての長所より少なくなる。このように詳細な説明に続く請求の範囲は、これにより詳細な説明中に明確に含まれ、それぞれの請求項は、この発明の別々の具体例としてそれ自身で成立する。

#### 【0047】

更に、ここで記載された幾つかの具体例は幾つかの特徴で、他の具体例に含まれる以外の特徴を含み、異なった具体例の長所の組み合わせは、本発明の範囲に入ることを意味し、当業者に理解されるように異なった具体例を形成する。例えば、以下の請求の範囲では、請求された具体例のいくつかは、他の組み合わせにおいても使用することができる。

#### 【0048】

ここで与えられる明細書において、多くの特別な細部が示される。しかしながら、本発明の具体例はそれらの特別な細部無しに実施できることを理解すべきである。他の例では、公知の方法、構造、および技術は、この記載の理解をわかりにくくしないために、詳細には示されていない。

#### 【0049】

明細書および請求の範囲で使用される「基板 (substrate)」の用語は、使用される下

10

20

30

40

50

方の材料を含み、または材料からなり、または、その上にMEMSデバイス、機械的、電子的、電気的、気体、流体、または半導体成分等、回路、またはエピタキシャル層を形成することができる。本発明の多くの具体例では、基板は、例えばドープされたシリコン基板、ガリウムアーセナイト(GaAs)基板、ガリウムアーセナイトフォスファイト(GaAsP)基板、インジウムフォスファイト(InP)基板、ゲルマニウム(Ge)基板、またはシリコングルマニウム(SiGe)基板のような半導体基板を含んでも良い。基板は、半導体基板部分に加えて、例えばシリコン酸化物層、またはシリコン窒化層のような絶縁層を含んでも良い。

#### 【0050】

「基板」の用語は、またシリコン・オン・ガラスやシリコン・オン・サファイアのような基板を含む。「基板」の用語は、このように、興味のある層や部分の下にある層のための要素を一般に規定するのに使用される。基板は、例えばガラス基板やガラスまたは金属層のような、その上に層が形成される他の基礎でも良い。以下において、処理について、主としてシリコン基板の処理を参照しながら説明するが、当業者は、他の半導体材料系、ガラス、または重合材料のような材料に基づいて好適な具体例を実効することができ、当業者により同等のものとして適當な材料が選択できることを認めるであろう。

#### 【0051】

本発明は、本発明の多くの具体例の詳細な記載によって記載される。本発明の他の具体例が、本発明の真実の精神や技術的示唆から離れることなく、当業者の知識により形成できることができ、本発明は、添付された請求の範囲の文言によってのみ限定されることは明らかである。

#### 【0052】

本発明は、ポスト処理による、例えばCMOS回路のような電気回路を含む基板上への、例えばMEMSデバイスのようなマイクロマシンデバイスのモノリシック集積化、およびそれにより得られたMEMSのようなマイクロマシンデバイスに関する。

#### 【0053】

「ポスト処理」は、電気回路が形成された後に、例えばMEMSデバイスのようなマイクロマシンデバイスが、基板上に形成されることを意味する。換言すれば、例えばMEMSデバイスのようなマイクロマシンデバイスが、電気回路が既に存在する基板に形成される。それゆえに、MEMSデバイスのようなマイクロマシンデバイスの処理中に電気回路が影響、損傷、および/または破壊されないように注意を払う必要がある。

#### 【0054】

ポスト処理は、例えばMEMSデバイスのようなマイクロマシンデバイスの形成に許容される技術や使用される材料に対して厳しい要求を課す。基板の電気回路の特性の、損傷や劣化を避けるために、例えばMEMSのようなマイクロマシンデバイスの製造中に使用される最高温度が、例えば450℃以下、例えば400℃以下に制限される。更に、例えばMEMS構造のようなマイクロマシンの形成に使用される犠牲層を除去するエッチングのような、製造プロセス中に使用される化学剤が制限される。

#### 【0055】

本発明は、それゆえに、電気回路を含む基板に、MEMSのようなマイクロマシン構造を少なくとも1つ含む、MEMSのようなマイクロマシンデバイスを製造する方法を提供する。この方法は、

電気回路を有する基板の上に保護膜を形成する工程と、

保護膜の上に、少なくとも1つのマイクロマシンデバイスを形成するための、複数のパターニングされた層を形成する工程であって、複数のパターニングされた層は少なくとも1つの犠牲層を含む工程と、

その後に、少なくとも犠牲層の一部を除去し、少なくとも1つのマイクロマシン構造を開放する工程と、を含む。

#### 【0056】

この方法は、更に、保護層を形成する前に、マイクロマシンデバイスの製造中に使用さ

10

20

30

40

50

れる最高温度より高い温度で基板をアニールする工程を含み、アニール工程は、連続する製造工程中に、保護層の下に気体が形成されるのを防止するものである。

#### 【0057】

本発明の具体例にかかる方法は、例えば基板上に存在する電気回路の性能の損傷や劣化のような、下層の電気回路に影響を与える前に、電気回路を含む基板の上にMEMSのようなマイクロマシンデバイスを形成できる。

#### 【0058】

本発明の具体例では、マイクロマシンデバイスの製造中に、下層にある電気回路が、例えばSiCを含む保護層の手段により保護される。この保護層を形成する前に、マイクロマシンデバイスを製造する工程で使用される最高温度より高い温度で基板を最初にアニールすることにより、基板と基板上にある層は、保護層の形成前に、脱ガスされる。「脱ガス」は、保護層を形成する前に、基板を加熱することにより、吸収された気体が基板や基板上の層から除去されることを意味する。

10

#### 【0059】

これにより、保護層の供給後にマイクロマシンデバイスの製造中に気体が形成されるのを防止する。なぜなら、気体の形成は、保護層の中に形成される欠陥の原因となるからである。これにより、本発明の具体例にかかる方法を用いて、このガスの形成と保護層中の欠陥の形成を防止し、例えば欠陥密度が $1 / \text{cm}^2$ より低い、 $0.1 / \text{cm}^2$ より低い、または $0.01 / \text{cm}^2$ より低いような、低い欠陥密度が得られる。これは、ポスト処理中に使用される化学剤が、保護層を貫通するのを防止し、これにより例えばCMOS回路のような下方の電気回路の損傷を避けることができる。

20

#### 【0060】

このように、高品質で低欠陥密度の保護層が得られ、ポスト処理中にこの高品質で低欠陥密度が維持されることが、本発明の具体例の特徴である。高品質を有するとは、マイクロマシンデバイスがその上に形成される基板上の電気回路に対して保護層が良好な保護を与えることを意味する。ここで保護は、例えばMEMSのようなマイクロマシンデバイスの製造プロセス中に使用される化学剤に対する保護である。低欠陥密度を有するとは、例えばピンホール、マイクロクラック、または密度変化のような保護層を通じて延びる欠陥の数が、例えば $1 / \text{cm}^2$ より低い、 $0.1 / \text{cm}^2$ より低い、または $0.01 / \text{cm}^2$ より低いような、実質的に0まで低減されることをいう。

30

#### 【0061】

本発明の具体例にかかる方法の他の特徴は、コンパクトの集積化の解を与えることや、基板上に例えばCMOS回路のような電気回路の製造プロセス中に変更を導入することなく、例えばMEMSのようなマイクロマシンデバイスの集積化を可能とすることである。

#### 【0062】

これ以降、本発明の具体例にかかる方法の連続した工程について説明する。この記載は例示するものであり、これ以降に記載される処理工程と一連の処理工程は、本発明をこれに限定することを意図するものではない。更に、本方法は、CMOS回路である電気回路の手段により述べられる。これは、単に説明を容易にするためであり、本発明を如何なる方法においても限定することを意図しない。本発明の他の具体例では、電気回路はマイクロマシンデバイスと組み合わせることが他の電気回路であっても良い。

40

#### 【0063】

更に、この方法は、少なくとも1つのMEMS構造を含むMEMSデバイスのようなマイクロマシンデバイスの手段により説明される。これは単に説明を容易にするためであり、如何なる方法によっても本発明を限定することを意図するものではない。マイクロマシンデバイスは、その製造に犠牲層を必要とするマイクロマシンデバイスでもよい

#### 【0064】

本発明の具体例にかかる方法を用いて作製可能なMEMSデバイスの例は、例えば、マイクロミラー、加速度計、ジャイロスコープ、インクジェットプリントヘッド、およびアクチュエータである。MEMSデバイスの下方の基板の電気回路は、MEMSデバイスの

50

駆動回路の例である。

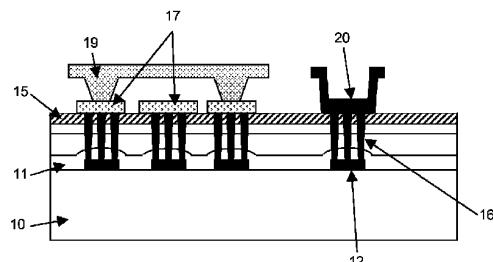

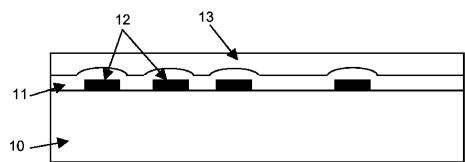

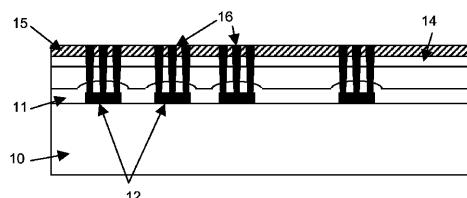

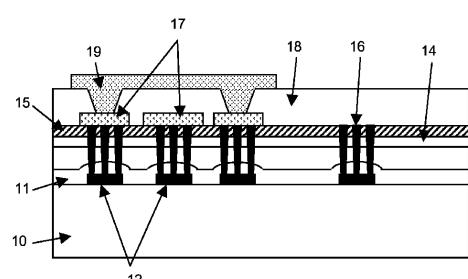

**【 0 0 6 5 】**

本発明の具体例にかかるCMOS基板10上での、MEMSポスト処理の一連の工程が、図1から図9に示される。主表面にCMOS回路を含む基板10が提供される。CMOS回路は、好適な方法で作製され、例えばA1、Cu、Ti、Ta、TaNまたはそれらの組み合わせのような当業者に知られた好適な導電性材料を含む少なくとも1つの電気コンタクトパッド12を含んでも良い。当業者に知られたように、CMOS回路を含む基板10上に標準のCMOSパッシベーション層11を堆積させた後、例えば化学気相成長(CVD)、プラズマ強化CVDまたはプラズマアシストCVD(PECVD/PACVD)、又は高密度プラズマ(HDP)CVDの手段により、標準のCMOSパッシベーション層11の上に、第1誘電体層13が堆積される。10

**【 0 0 6 6 】**

本発明の具体例では、第1誘電体層13は、シリコン酸化層またはシリコン窒化層である。しかしながら、他の具体例では、第1誘電体層13の形成に、他の好適な誘電体材料が用いられても構わない。例えば、CMPによる平坦化と、ポストCMPクリーニングのような洗浄の後、第1誘電体層13は、平坦化工程により部分的に導入された多くの欠陥を含む。例えば、ポストCMP洗浄後に残された汚染が存在するかもしれない、また、平坦化された第1誘電体層13中に気体や液体がトラップや吸収されるかもしれない。上述の工程後に得られる構造が、図1に示される。20

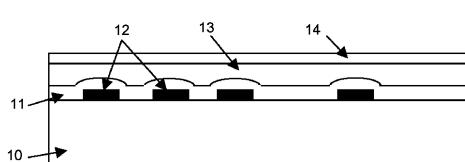

**【 0 0 6 7 】**

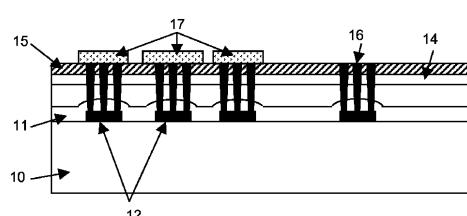

本発明の具体例では、方法は、次の工程に、例えば $1 / \text{cm}^2$ より低い、 $0.1 / \text{cm}^2$ より低い、または $0.01 / \text{cm}^2$ より低いような、低欠陥密度の、実質的に平坦な誘電体上部層14を形成する工程を含む。低欠陥密度の誘電体上部層14の形成は、異なる方法で行うことができる。20

**【 0 0 6 8 】**

低欠陥密度の誘電体上部層14を得るための1つの方法は、例えば続いてCMPによる平坦化が行われる好適な堆積技術により基板上に実質的に平坦な誘電体層13を形成し、アニール工程を行うことによる。アニール工程は、例えばCMP平坦化工程のより導入された欠陥や、有機物または無機物の汚染による欠陥、または例えば $1 / \text{cm}^2$ より低い、 $0.1 / \text{cm}^2$ より低い、または $0.01 / \text{cm}^2$ より低いようなトラップされた気体や液体による欠陥のような、第1誘電体層13中の欠陥を低減することができる。本発明の具体例では、アニール工程は、ポスト処理中に使用される最も高い処理温度より、例えば1から10だけ高い温度、例えば5高い温度のような数高い温度で行われる。これじゃ、基板10の脱ガスのためのアニール工程と同時にあっても良い。例えば、ポスト処理温度が450の場合、アニールは、例えば455で行われる。30

**【 0 0 6 9 】**

これにより、これらの具体例では、アニール工程は、誘電体層13中の欠陥を減らすと共に、基板10と、基板10の上に存在する層の材料の脱ガスの追加の効果を有する。しかしながら、本発明の具体例では、誘電体層13中の欠陥の数を減らすための基板10のアニールと、基板10と基板10の上に存在する層の材料の脱ガスのためのアニールは、異なった工程で行われても良い。40

**【 0 0 7 0 】**

低欠陥密度の誘電体上部層14を得るための第2の方法は、例えば、HDP-CVD(高密度プラズマ化学気相成長)やスピノンのような、下方の層から欠陥や形状を写しとらない堆積技術のような適当な堆積技術を用いて、第1の平坦化された誘電体層13の上に第2の誘電体層14を堆積する。第2の誘電体層14は、例えばHDP(高堆積温度)のシリコン酸化物、HDPシリコン窒化物、またはスピノンガラスでも良い。例えば、下方の層から欠陥を写しとらない堆積技術のような適当な堆積技術を選択することにより、例えば $1 / \text{cm}^2$ より低い、 $0.1 / \text{cm}^2$ より低い、または $0.01 / \text{cm}^2$ より低いような欠陥の数が得られる。50

## 【0071】

低欠陥密度の誘電体上部層14を得るための他の方法は、第1の方法と第2の方法との組み合わせであり、例えば、少なくとも1つのアニール工程と、加えて上述の適当な堆積技術を用いた第1誘電体層13の上への第2誘電体層14の堆積工程により行われる。

## 【0072】

図1、2に示される例では、最初に、第1誘電体層13が基板10の上に形成される(図1参照)。選択的に、第1誘電体層13がアニールされ、この層13中に存在する欠陥数が低減される。次に、第2誘電体層14が、例えば第1誘電体層13のような下方の層から欠陥を写しとらない堆積技術を用いて堆積される(図2参照)。

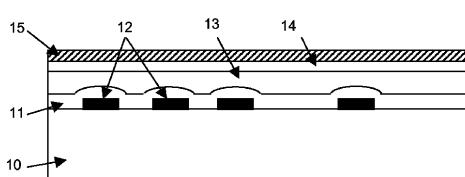

## 【0073】

本発明の具体例にかかる低欠陥密度の実質的に平坦な誘電体上部層14を得ることの重要性は、連続した工程で保護層15が形成された場合(図3参照)、下方の層から欠陥および/または形状を引き継ぎ、保護層中の欠陥数が、例えば $1/cm^2$ より低く、 $0.1/cm^2$ より低く、または $0.01/cm^2$ より低くなることがある。このように、低欠陥密度の実質的に平坦な誘電体上部層14の存在は、例え下方の層から欠陥および/または形状が写し取られおよび/または増幅される堆積技術が用いられてても、例えば $1/cm^2$ より低い、 $0.1/cm^2$ より低い、または $0.01/cm^2$ より低いような欠陥の数を有する低欠陥密度の実質的に平坦な保護層15の形成を可能とする。更に、特に、ピンホール、マイクロクラック、または密度変化のような保護層15を通って延びる欠陥の数は、例えば $1/cm^2$ より低い、 $0.1/cm^2$ より低い、または $0.01/cm^2$ より低い、実質的にゼロまで低減できる。

10

20

## 【0074】

本発明の具体例では、保護層15は例えればSiC層であり、CMOSと互換性のある温度、例えば450より低い温度、更には400より低い温度で、SiCの標準的な堆積技術として知られているPECVD(プラズマエンハンスドCVD)やPACVD(プラズマアシストCVD)の手段で堆積される。PECVDやPACVDで堆積されたそのようなSiC層は、下方の層中に存在する欠陥を写し取り、下方の層中に存在する形状を平坦化しない。この方法で堆積されたSiC層は、下方の層から写し取られた欠陥を有し、下方の層の残る形状の上に形成されるホールやクラックのような欠陥を有する。これゆえに、上述のように、下方の層の欠陥を写し取る技術を用いる場合、上述のように、保護層15を形成する前に、低欠陥密度の実質的に平坦な上部層14の形成が必要となるであろう。

30

## 【0075】

本発明の他の具体例では、しかしながら、低欠陥密度の平坦な誘電体上部層14の形成は省略される。この場合、例えば $1/cm^2$ より低い、 $0.1/cm^2$ より低い、または $0.01/cm^2$ より低い欠陥数のような、低い欠陥数の保護層15を形成するために、下層の標準的なCMOSパッシベーション層の具体例で、下方の層から欠陥を写し取らない堆積技術が使用される。この方法では、低欠陥密度の保護層15が得られる。

## 【0076】

40

保護層15を堆積する前に、基板10は、MEMSデバイスの製造中に使用される最高温度より高い温度でアニールされる。これは、続く製造工程で、保護層15の下方での気体の形成を防止するために行われる。換言すれば、保護層15の形成前に、アニール工程は、基板10と基板10の上に存在する層の材料の脱ガスのために行われる。本発明の具体例では、第2誘電体層14が形成された場合、アニール工程は、電気回路、標準CMOSパッシベーション層11、第1の平坦化誘電体層13、および第2に誘電体層14を含む基板10の上で行われる。

## 【0077】

50

本発明の他の具体例では、第1の平坦な誘電体層13と保護層15との間に第2誘電体層14は形成されず、アニール工程は、誘電体層13中の欠陥数を低減するためにも行われる。アニール工程は、例えば少なくとも20分のような適当な時間、ポスト処理中に使

用される最高温度より高い温度、例えば455で、不活性雰囲気、例えば形成ガス( $N_2/H_2$ )雰囲気中で行われる。更なる具体例では、保護層15が形成される前に誘電体層は形成されず、アニールは、電気回路と標準CMOSパッシベーション層11を含む基板に行われる。

#### 【0078】

製造プロセスで使用される最も高いポスト処理温度より、例えば1と10の間のような僅かに高くなるように、アニール温度が選択される理由は、ポスト処理中に、保護層15の下方に気体が形成されるのを避けるためである。保護層15の下での気体の形成は避けなければならない。なぜならば、これにより、保護層15の損傷が形成され、例えば、ポスト処理中に使用される化学剤が損傷した保護層15を貫通し、下方の電気回路を損傷および/または劣化させるからである。

10

#### 【0079】

多くの実験が行われ、例えば誘電体上部層14中の欠陥の存在と数の、欠陥の無いSiC保護層15の品質への影響が研究された。1つの実験は、誘電体上部層14としての平坦な800nm膜厚の酸化層と、誘電体上部層14の上の保護層15としての300nm膜厚のPECVD層とを有するシリコンウエハ上で行われた。この実験では、第1ウエハは300nmSiC層を有し、下方の酸化層のCMP処理の無い第1ウエハが用いられた。即ち、SiC層が堆積される前に、参照ウエハ上の酸化層はCMPの手段により平坦化されない。このウエハでは、気相HFエッティング後に、下方の酸化層の劣化は発生しなかった。

20

#### 【0080】

第2ウエハ上には、下方の酸化層のCMP処理を行うことなく300nmSiC層が堆積されたが、SiCの堆積後にCMP平坦化が行われた。このウエハもまた、気相HFエッティング後に劣化を示さなかった。第3のウエハでは、標準的な酸化物CMP平坦化が、SiCの堆積前に行われた。このウエハでは、20分間、35で気相HFエッティングを行った後でさえ、下方の酸化層の明確な攻撃が見られた。このウエハの劣化は、1分間のウエットHFエッティング(49%)の後にも見られる。これは、この場合、SiC層15が、この層15を通る化学剤の貫通を避けるのに十分な程度まで欠陥が無くなっていることを示す。これは、CMP手段による下方の酸化層14の平坦化が、酸化層14と保護SiC層15との間に残渣を残し、または欠陥を導入し、これが、例えば $1/cm^2$ より低い、 $0.1/cm^2$ より低い、または $0.01/cm^2$ より低い欠陥密度のSiC保護層15のような、実質的に欠陥の無いPECVD-SiC保護層15の成長を妨げるからである。

30

#### 【0081】

上述の実験は、保護層15の下に誘電体上部層14が存在する場合、この誘電体上部層14は、例えばPECVD-SiC保護層のような保護層15の形成前に、好適には、例えば $1/cm^2$ より低い、 $0.1/cm^2$ より低い、または $0.01/cm^2$ より低いような低欠陥密度を有すべきであることを示す。実験は、更に、下方の誘電体層14の平坦化が、良好なSiC保護層15を得るために必要であることを示す。形状を有するウエハまたは層の上に堆積されたSiC保護層15では、上述のような下方の層から欠陥を写し取る堆積技術が用いられた場合、保護としては不十分であることが示された。例えば、小さなステップ21を覆う300nm膜厚のSiC層15を有するウエハで実験が行われた。気相HFを用いたエッティング後に、SEM写真(図11参照)は、SiC層15の側壁のカバーは良好に見えるにもかかわらずステップ21の位置で酸化層14が攻撃されている(図11中に矢印22で示される)。

40

#### 【0082】

表1は、SiC層15の下に存在する、異なった処理が行われた誘電体層14についてのPECVD-SiC層15の保護品質が調査された実験の概略を示す。全てのウエハに対して、800nm膜厚の誘電体層13が、基板10の上に堆積された。誘電体層13は、続いて420でアニールされ、CMP手段で平坦化された。このアニール工程は、本

50

発明のアニール工程には対応しない。この後、異なる試料について、表1にまとめたような異なった処理が行われた。最後に、300 nm 膜厚のPECVD-SiC層15が全ての試料上に堆積され、続いて420°でアニール工程が行われる。SiC層15の品質が、続いて、気相HFエッティングを行い、SiC層15の下方の誘電体層14の欠陥を検査することで評価された

## 【0083】

|             | D03 | D04 | D05 | D07 | D09 | D13 |

|-------------|-----|-----|-----|-----|-----|-----|

| 20 nm DXZ   | X   |     |     |     |     |     |

| 200 nm IMD  |     | X   | X   |     |     |     |

| HF洗浄        |     |     |     | X   |     |     |

| シンター 420° C | X   |     | X   | X   | X   |     |

| 300 nm SiC  | X   | X   | X   | X   | X   | X   |

| シンター 420° C | X   | X   | X   | X   | X   | X   |

| 20' vHF テスト | bad |     | OK  | OK  | OK  |     |

| 60' vHF テスト |     | OK  |     | OK  | OK  | Bad |

10

20

表1：PECVD-SiC層の保護特性と調査を行う実験の概略

## 【0084】

低欠陥密度の酸化層14を得るために基板のアニール無しで、酸化物CMPの直後にSiC堆積が行われた試料D13を参照すると、60分の気相HFエッティング後に、保護層15の下方の誘電体層14の損傷が明らかに示される。

## 【0085】

高密度プラズマ酸化物で下方の層からの欠陥を写し取らない新しいIMD（中間金属誘電体）酸化物14の堆積後（試料D04）、または欠陥密度を例えば1/cm<sup>2</sup>より低い、0.1/cm<sup>2</sup>より低い、または0.01/cm<sup>2</sup>より低く減らすためのシンター工程やアニール工程後（試料D07およびD09）、のいずれにおいても、またはIMD酸化物堆積とアニール工程との組み合わせにより（試料D05）、SiC層15の保護特性が満足された。しかしながら、全ての酸化物の堆積が有用なわけでは無い。20 nm DXZ酸化物（PECVD酸化物）の堆積は、良好な保護特性を示さず（試料D03）、これは欠陥がこの層中で増殖し、ステップカバレジが悪いためであろう。第2誘電体層14の膜厚は、例えば50 nmと800 nmの間の範囲、100 nmと500 nmの間の範囲、100 nmと300 nmの間の範囲である。

30

## 【0086】

本発明の他の具体例では、上述のように、例えばSiC保護層のような保護層が、HDPE-CVDまたはスピノンの手段により形成される。それらの技術を用いると、保護層15を形成する前に、低欠陥密度の実質的に平坦な誘電体上部層14を形成する必要が無い。これらの具体例では、保護層15を形成する前に、基板10がマイクロマシンデバイスの製造中に使用される最高温度より高い温度でアニールされ、続く製造工程で保護層の下に気体が形成されるのを防止する。

40

## 【0087】

例えば、アルミニウム酸化物、ポリイミド、エポキシ、BCB、アモルファスシリコン、アモルファスゲルマニウム、またはアモルファスシリコンゲルマニウムのような、SiC以外の材料が、保護層15の形成に使用されても良い。堆積は、300と450の

50

間の範囲、例えば300と400の間の範囲、例えば350で行われても良い。保護層15は、100nmより薄く、例えば100nmと500nmの間の範囲、例えば300nmである。保護層15は、CMOS回路のような電気回路を含む基板上でMEMSデバイスのポスト処理中に使用される例えば化学剤の影響から、例えばCMOS回路のような下方の電気回路を保護する機能を有しても良い。特に、保護層15は、例えば犠牲層のエッティング中のこのようなポスト処理中に、下方の回路を保護しても良い(以下参照)。それゆえに、保護層15は、可能な限り少ない欠陥を有し、例えば欠陥の数は $1/cm^2$ より低く、 $0.1/cm^2$ より低く、または $0.01/cm^2$ より低い。

#### 【0088】

本発明の具体例にかかる方法は、更に、保護層15を通り、下方のCMOS電気回路の電気接続パッドから伸びた電気接続を形成する工程を含んでも良い。これらの電気接続は、下方の電気回路をMEMSデバイスの電極(以下参照)に電気的に接続するためと、下方の電気回路を外部世界(ボンドパッド)に電気的に接続するための、双方に使用できる。それゆえに、保護層15を形成した後、本発明の具体例にかかる方法の次の工程(図4に示す)で、誘電体層11、13、14により形成されたスタックや保護層15中に、例えばエッティングによりビア(via)が、例えば下方の電気回路の電気的な接続パッド12が配置される位置に形成されてもよい。

#### 【0089】

これは、当業者に知られた好適な技術により行われても良い。例えばSiC保護層の場合、保護層15は、米国特許6,599,814も記載された方法により例えば部分的に除去されても良い。この方法は、酸素含有プラズマを照射し酸化シリコン層を除去することにより、SiC層15の露出した部分を少なくとも部分的に酸化シリコン層中に転写する工程を含み、転写工程と除去工程は、誘電体層14が露出するまで繰り返される。SiC層15は、純粋のシリコン酸化層に転写されず、少なくともSiとOを含み、選択的にCおよび/またはNおよび/またはHを含み、C/N/Hの部分はOの部分より小さい層に転写される。それゆえに、形成された層は、ここでは酸化シリコン層と呼ばれる。CMOS回路の上部層は、例えばCMOS回路のCMOS構造の上部金属スタック(例えば電気コンタクトパッド)のTiN層は、ビアを形成するための、誘電体層11、13、14および保護層15のエッティング中に、エッティングストップとして使用されても良い。

#### 【0090】

次の工程では、導電性プラグ16が、例えばCVD、PECVD、または物理気相成長(PVD)の手段によりビアの中に堆積される(図4参照)。このアプローチは、少なくとも1つのCMOS電気コンタクトパッド12から、保護層15を通って伸びる電気接続の形成を可能とする。導電性プラグ16は、例えばTi/TiN/W金属スタックのような金属や金属スタック、または田度江波ドープされたSiGeのようなドープされた半導体を含む。例えば、Ti/TiN/Wプラグの場合、最初に薄いTi/TiNビアライナーがビア中に堆積され、このビアライナーは数nmから数10nmの膜厚を有し、ビア金属(例えばW)が隣接する層中に拡散するのを防止する拡散バリアとして働く。ビアライナーを形成した後、ビアはビア金属(例えばW)で満たされ、その後、CMP平坦化工程のような平坦化工程が行われる。プロセスのこの段階では、構造の表面は実質的に平坦であり、例えばSiC保護層のような保護層15、例えばWプラグのような金属プラグ16のような導電体により形成される(図4参照)。

#### 【0091】

次の工程では、少なくとも1つのMEMS構造を形成するために、複数のパターニングされた層が保護層15の上に形成される。複数のパターニングされた層は、当業者に知られた適当な技術により行われる。複数のパターニングされた層は、いくつかのパターニングされた層と、例えば所定のMEMS構造中で要求されるマイクロマシン構造を形成するのに必要ないずれかの材料を含む。堆積技術、エッティング技術、複数のパターニングされた層に使用される材料は、保護層15に追加の損傷や欠陥を与えないように行われる。このため、堆積技術、エッティング技術、複数のパターニングされた層に使用される材料は、

10

20

30

40

50

MEMSデバイスの製造中および製造後の保護層15中の欠陥の数が、常に $1 / \text{cm}^2$ より低く、例えば $0.1 / \text{cm}^2$ より低く、または $0.01 / \text{cm}^2$ より低くなるよう行われる。

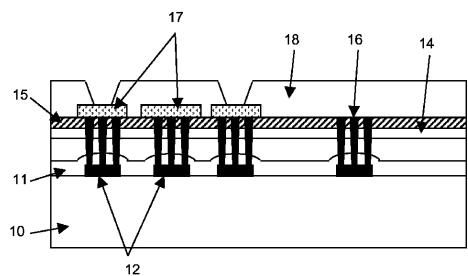

#### 【0092】

本発明の具体例では、他の中で複数のパターニングされた層を形成は、MEMSデバイスのための少なくとも1つの電極17を形成するために、電極材料の層を形成しパターニングする工程を含む(図5参照)。この電極材料の層は、保護層15の上に堆積される。電極材料の層のパターニングは、例えば、保護層15および導電性プラグ16に対して良好な選択性で電極材料の層を部分的にエッチングする工程を含む。本発明の具体例では、電極材料、電極材料を堆積させるのに使用される技術、および電極材料の層のパターニングのためのエッチングプロセスは、保護層15中に欠陥を導入せず。導電性プラグ16を攻撃しないものである。本発明の具体例では、電極材料の層は、 $\text{Si}_{1-x}\text{Ge}_x$ ( $0.5 < x < 0.65$ )を含む。しかしながら、本発明の具体例では、他の材料を使用しても良く、電極材料の層の定積やパターニングは、下方の保護層15中に欠陥を導入しない。

10

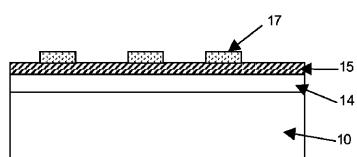

#### 【0093】

少なくとも1つのMEMS電極17を形成するために、異なった材料を用いて実験が行われた。それらの実験に使用された試料の例を図10に示す。シリコンウエハ10上に、シリコン酸化層が堆積され、平坦化され、アニールされて、 $1 / \text{cm}^2$ より低く、例えば $0.1 / \text{cm}^2$ より低く、または $0.01 / \text{cm}^2$ より低い欠陥数を有する誘電体上部層14が形成される。シリコン酸化物層14の上に $\text{SiC}$ 層15が堆積され、続いて電極材料の層を堆積しパターニングして少なくとも1つの電極17を形成する。第1の試料では、少なくとも1つの電極の形成に700nmのAl層が使用され、第2の試料では、少なくとも1つの電極の形成に100nmのTiN層が使用され、第3の試料では、少なくとも1つの電極の形成に300nmのSiGe層が使用された。

20

#### 【0094】

電極材料の層を堆積した後、電極材料の層のパターニングのために、エッチング工程が行われた。700nm Al層を含む試料と、100nm TiN層を含む試料のために、 $\text{BCl}_3$ 系のエッチング化学剤が使用された。 $\text{SiGe}$ 層を含む試料のためには、 $\text{HBr}$ 系のエッチング化学剤が使用された。次の工程では、試料が気体のHFに晒され、加熱されたウエハステージを有するジメティック(Gemtec)のパッドヒュームシステム(Pad Fume system)中で、35で60分間エッチングされた。700nm Alスタックと、100nm TiN電極の双方で、 $\text{SiC}$ 層15の下方の酸化層14が攻撃され、 $\text{SiC}$ 層15の完全な層間剥離が観察された。300nm SiGe電極17では、酸化層14は攻撃されず、 $\text{SiC}$ 層15が良好な保護層として残ることを示した。試料間で観察されたこの違いは、電極材料の層のパターニングに使用されたエッチング化学剤によるものである。これらの結果は、電極材料の層のエッチングの結果として、 $\text{SiC}$ 層15の劣化は、最小にすべきであることを示している。電極材料の層のエッチング中に、保護層15中に欠陥が形成されることとは、適当なエッチング化学剤の選択により避けられる。例えば、SiGe電極17の場合、HBr系のエッチング化学種が用いられる。

30

#### 【0095】

更に、電極材料だけでなく、電極の機械的性質(例えば応力)は、保護層15への損傷を避ける役割を果たす。例えば、電極材料の層17と保護層15との間の堆積中または熱サイクル中の応力の不整合は、保護層15中の欠陥を生じることになる。応力の不整合は、内在的な材料特性の結果や、使用した堆積技術に関係する。たとえば、PECVDの手段で電極材料の層が堆積されて形成され、残留引っ張り応力を有する350nmの膜厚のSiGe電極17では、下方のSiC保護層15の劣化はなく、一方、CVDの手段で電極材料の層が堆積されて形成され、残留圧縮応力を有する350nmの膜厚のSiGe電極17では、SiC保護層15は明らかに劣化している。

40

#### 【0096】

本発明の具体例では、 $\text{Si}_{1-x}\text{Ge}_x$ 層は、PECVDまたはPACVDの手段によ

50

り堆積される。100 MPaより低いような、例えば50 MPaの引っ張りより低い、または10 MPaの引っ張りより低いような、低い残留引っ張り応力を有するSi<sub>1-x</sub>Ge<sub>x</sub>電極層は、残留圧縮応力を有する電極材料の層より好ましい。SiGe層中の応力を制御する方法は、例えば、U.S.2000-0166467やEP1801067に記載されている。

#### 【0097】

MEMSデバイスの少なくとも1つの電極17が、導電性プラグ16と電気的に接続された場所では、電気接続は、MEMSデバイスの電極17とCMOS電気接続パッド12との間に形成されても良い。

#### 【0098】

保護層15の上に形成された複数のパターニングされた層は、少なくとも1つの犠牲層18を含み(図6参照)、犠牲層18は、以下に記載するように、連続する処理中に少なくとも部分的に除去される。犠牲層18は、例えばシリコン酸化物を含むが、他の具体例では、当業者に知られた他の適当な材料が使用されても良い。犠牲層18を堆積させた後、この層は例えばCMPにより平坦化され、例えばローカルエッティングによりパターニングされる。犠牲層18のローカルエッティングは、例えばウエットエッティングや当業者に知られた他の適当な方法で行われ、MEMS電極17の少なくとも1つは、エッティングストップとして働く。

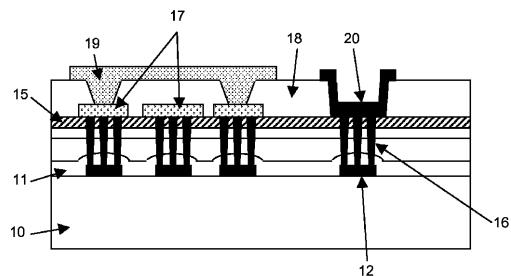

#### 【0099】

次の工程では、図7に示すように、例えばSi<sub>1-x</sub>Ge<sub>x</sub>(0.5 < x < 0.8)のようなMEMS構造層19が堆積されパターニングされる。他の具体例では、当業者に知られた他の適当な材料が、構造層を形成するたまに使用される。構造層19の膜厚は、例えば50 nmと30 μmの間の範囲である。構造層19は、例えば、CVD、PECVD、PVDまたは蒸着の手段で堆積される。必要であれば、例えば光学の応用において、例えばマイクロミラーを形成するために、例えばA1層のような少なくとも1つの追加の層が構造層19の上に形成されても良い(図示せず)。

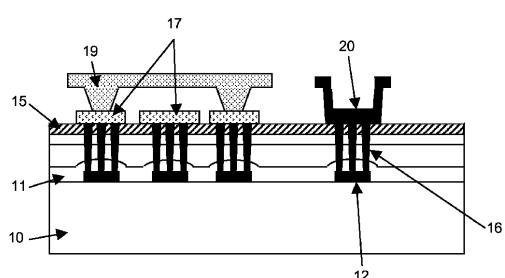

#### 【0100】

本発明の具体例では、次の工程で、例えばプラズマエッティングやウエットエッティングの手段により、例えば犠牲層18を通るエッティングにより少なくとも1つの開口部が形成されても良い。少なくとも1つの開口部は、(上述の)先の工程で、例えば金属プラグ16のような導電体が形成され、MEMS電極17とは接続されていない場所をエッティングして形成される(図8参照)。保護層15と導電性プラグ16は、犠牲層18中に開口部をエッティングする間、エッティングストップ層として働く。犠牲層18を通る少なくとも1つの開口部のエッティング後、少なくとも1つのボンドパッド20が、保護層15の上に形成され、ボンドパッドの少なくとも1つが導電性プラグ16に電気的に接続される。これは、例えば、導電層の堆積とパターニングにより行われる(図8参照)。この方法では、電気接続が、下方のCMOS回路の電気接続パッド12と、外部世界(ボンドパッド20)との間を接続する。本発明の具体例では、少なくとも1つのボンドパッド20は、例えば、Alおよび/またはTiNおよび/またはTaNを含む。

#### 【0101】

上述のように、図8に示すようなMEMSデバイスと電気接続を形成するために、SiC層15を通るエッティングによりビアが形成される必要があり、スタックが誘電体層11、13、14から形成され、それらのビアは、金属プラグ16により埋められる(図4参照)。MEMS電極17を形成するために電極材料の層をエッティングする間、それらのプラグ16は、ボンドパッド20が形成される領域で保護されていない。電極材料の層のエッティングの、ビアと金属プラグ16の整合についての影響を調査する実験が行われた。SiGe電極層をHBr系化学剤を用いてプラズマエッティングし、O<sub>2</sub>アッシングに基づくレジスト剥離やウエットポリマー洗浄(3分間のH<sub>2</sub>SO<sub>4</sub>/H<sub>2</sub>O<sub>2</sub>/H<sub>2</sub>Oおよび2分間のHF/H<sub>2</sub>O)を行った後、金属プラグ16の電気的特性の大きな劣化は見られなかった。

10

20

30

40

50

## 【0102】

また、ビアライナー（WビアについてのTiNライナー対Ti/TiNライナー）とビアエッチング時間の、少なくとも1つのボンドパッド20と、下方の電気接続パッド12への電気接続の、電気特性に対する影響が評価された。実験は、ビア（金属プラグ16）を介して下方の電気接続パッド12に接続された、2つのボンドパッド20の直列な抵抗が測定されて行われた。表2に示す実験結果から、Ti/TiNライナーは、TiNライナーより低い抵抗となるが、TiNライナーでも良好な結果が得られることがわかる。更に、ボンドパッド20と電気接続パッド12との間で良好なコンタクトを得るには、十分に長いビアのエッチング時間が必要なこともわかった。

## 【0103】

10

| ビアエッチング時間 | Ti/TiNライナー | TiNライナー     |

|-----------|------------|-------------|

| 160"      | -          | 312-450 mΩ  |

| 170"      | 250 mΩ     | 312-1100 mΩ |

| 180"      | 250 mΩ     | 330-400 mΩ  |

表2：直列な2つのボンドパッドの抵抗（ビアと下方の金属を介して接続）

20

## 【0104】

少なくとも1つのボンドパッド20を形成した後、次の工程で、犠牲層18が少なくとも部分的に除去され、これにより、MEMS構造が開放される（図9）。これは、例えばウェットエッチングや当業者に知られた他の好適な方法により行われても良い。犠牲層18がシリコン酸化物18を含む本発明の具体例では、犠牲層18は、気相HFエッチングにより除去される。気相HFを用いる長所は、吸着のないエッチングであり、金属ベースの膜に対して高い選択性を有し、保護層15以外に、MEMSの開放中に少なくとも1つのボンドパッド20の保護を行う必要が無いことである。たとえば少なくとも1つのボンドパッド20の金属のような導電性材料に対する、気相HFエッチングの選択性や、気相HFエッチング後の少なくとも1つのボンドパッドの整合が、実験的に検討された。それゆえに、A1ボンドパッド20が、A1の下方のバリア層とともに形成された。TiNバリア層がA1ボンドパッド20の下方に使用された場合、ボンドパッド20は、気相HFエッチング後に剥離した。A1ボンドパッド20の下方のTaNバリア層の場合、気相HFエッチング後に、下方の誘電体層の攻撃は見られず、ボンドパッド20の電気的特性（例えば、ボンドパッド20と下方の電気接続パッド12との間の電気抵抗）の大きな劣化は見られなかった。

30

## 【0105】

本発明の具体例にかかる方法により得られたMEMSデバイスは、1/cm<sup>2</sup>より低いような、例えば0.1/cm<sup>2</sup>より低く、または0.01/cm<sup>2</sup>より低いような、十分に低い欠陥密度を含み、例えばMEMSのようなマイクロマシンデバイスのポスト処理中に、保護層15を通じて化学剤が貫通するのを避けることができ、マイクロマシンデバイスの製造中に使用される最高温度は、例えば400より低いような、450より低いことが、本発明の特徴である。このため、マイクロマシンデバイスがその上に形成される基板上に存在するCMOS電気回路は、マイクロマシンデバイスの製造中に損傷を受けず、これにより、良好で、信頼性があり、適当な機能を示す。本発明の具体例にかかる方法のさらなる特徴は、標準的で安価な材料が犠牲層18に使用できることであり、基板10上のCMOSデバイスへの影響および/または損傷無しに、この犠牲層18は容易に平坦化でき、MEMSデバイスの吸着の無い気相HFでの開放が可能となる。

40

## 【0106】

好適な具体例、構造、および外形は、材料とともに、本発明のデバイスについてここで

50

検討されたが、本発明の範囲や精神から離れることなく、形状や細部について多くの変形や修正を行うことができる。本発明の範囲内で、記載された方法について、工程を追加または削除することができる。

【図 1】

FIG. 1

【図 2】

FIG. 2

【図 3】

FIG. 3

【図 4】

FIG. 4

【図 5】

FIG. 5

【図 6】

FIG. 6

【図 8】

FIG. 8

【図 7】

FIG. 7

【図 9】

FIG. 9

【図 10】

FIG. 10

【図 11】

FIG. 11

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/EP2007/061731

**A. CLASSIFICATION OF SUBJECT MATTER**

INV. B81C1/00

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

B81C

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data, INSPEC, IBM-TDB

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                           | Relevant to claim No. |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | EP 1 484 281 A (HEWLETT PACKARD DEVELOPMENT CO [US])<br>8 December 2004 (2004-12-08)<br>figures 3a-3h<br>paragraphs [0029] - [0031]<br>----- | 19,20                 |

| X         | US 2006/166467 A1 (WITVROUW ANN [BE] ET AL) 27 July 2006 (2006-07-27)<br>cited in the application<br>figures 3a-4b<br>-----                  | 19,20                 |

| A         | US 6 822 304 B1 (HONER KENNETH A [US])<br>23 November 2004 (2004-11-23)<br>figures 5-9<br>paragraph [0024]<br>-----<br>-/-                   | 1-20                  |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

- \*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- \*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- \*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- \*&\* document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

18 April 2008

25/04/2008

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

Fax: (+31-70) 340-3016

Authorized officer

McGinley, Colm

**INTERNATIONAL SEARCH REPORT**

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/EP2007/061731 |

|---------------------------------------------------|

| C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                           |                       |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category*                                            | Citation of document, with indication, where appropriate, of the relevant passages                                                        | Relevant to claim No. |

| A                                                    | US 2005/073011 A1 (TAGUWA TETSUYA [US]<br>TAGUWA TETSUYA [JP])<br>7 April 2005 (2005-04-07)<br>figures 2a-3g<br>paragraphs [0042], [0043] | 1                     |

| A                                                    | EP 1 452 481 A (DALSA SEMICONDUCTOR INC<br>[CA]) 1 September 2004 (2004-09-01)<br>figure 11                                               | 1-20                  |

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/EP2007/061731 |

|---------------------------------------------------|

| Patent document cited in search report | Publication date | Patent family member(s) |  | Publication date |

|----------------------------------------|------------------|-------------------------|--|------------------|

| EP 1484281                             | A 08-12-2004     | CN 1572719 A            |  | 02-02-2005       |

|                                        |                  | JP 3980571 B2           |  | 26-09-2007       |

|                                        |                  | JP 2004358654 A         |  | 24-12-2004       |

|                                        |                  | KR 20040104408 A        |  | 10-12-2004       |

|                                        |                  | SG 115612 A1            |  | 28-10-2005       |

|                                        |                  | TW 225845 B             |  | 01-01-2005       |

|                                        |                  | US 2004245588 A1        |  | 09-12-2004       |

| US 2006166467                          | A1 27-07-2006    | NONE                    |  |                  |

| US 6822304                             | B1 23-11-2004    | NONE                    |  |                  |

| US 2005073011                          | A1 07-04-2005    | CN 1610115 A            |  | 27-04-2005       |

|                                        |                  | JP 2005116693 A         |  | 28-04-2005       |

|                                        |                  | KR 20050033494 A        |  | 12-04-2005       |

|                                        |                  | TW 242802 B             |  | 01-11-2005       |

| EP 1452481                             | A 01-09-2004     | US 2006166403 A1        |  | 27-07-2006       |

|                                        |                  | US 2004157426 A1        |  | 12-08-2004       |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IS,IT,LT,LU,LV,MC,MT,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BH,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IS,JP,KE,KG,KM,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RS,RU,SC,SD,SE,SG,SK,SL,SM,SV,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,ZA,ZM,ZW

(74)代理人 100081422

弁理士 田中 光雄

(74)代理人 100112911

弁理士 中野 晴夫

(72)発明者 アン・ウィトフルーウ

ベルギー、ベー - 3 0 2 0 ヘレント、フルールストラート 4 8 番

(72)発明者 リュック・ハスペスラーフフ

ベルギー、ベー - 3 2 1 0 リュベーク - リンデン、パストレイストラート 7 番

F ターム(参考) 3C081 AA01 AA18 BA22 BA32 BA44 BA48 CA03 CA14 CA20 CA27

CA29 CA40 DA02 DA27 DA29 DA30 DA31 EA02 EA35 EA41