(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294486

(P2005-294486A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

H01F 17/00

H03H 7/09

F 1

H01F 17/00

H03H 7/09

テーマコード(参考)

5 E 0 7 0

5 J 0 2 4

審査請求 未請求 請求項の数 12 O L (全 14 頁)

(21) 出願番号

特願2004-106689 (P2004-106689)

(22) 出願日

平成16年3月31日 (2004.3.31)

(71) 出願人 000003067

TDK株式会社

東京都中央区日本橋1丁目13番1号

(74) 代理人 100088155

弁理士 長谷川 芳樹

(74) 代理人 100092657

弁理士 寺崎 史朗

(74) 代理人 100108213

弁理士 阿部 豊隆

(72) 発明者 渡邊 邦保

東京都中央区日本橋一丁目13番1号 T

DK株式会社内

(72) 発明者 阿部 裕

東京都中央区日本橋一丁目13番1号 T

DK株式会社内

最終頁に続く

(54) 【発明の名称】 積層型電子部品

## (57) 【要約】

【課題】 焼成が施された際のデラミネーション及びクラックの発生を抑制できる積層型電子部品を提供すること。

【解決手段】 積層型電子部品1は、絶縁材料によって形成された本体部2と、この本体部2の内部に形成されたコイル軸方向Zに並列する2つのコイル部5a, 5bとを備えている。コイル部5a(5b)は、仮想の平面S上に導体パターン7が巻回された巻回部8a(8c)と、平面Sと平行に導体パターン7が巻回され、コイル軸方向Zに巻回部8a(8c)と並列された巻回部8b(8d)とを有している。この巻回部8a(8c), 8b(8c, 8d)は、導体パターン7の巻回の間隔が互いに等しい部分を有しており、この部分は、巻回部8a(8c)と巻回部8b(8d)とがコイル軸方向Zに並列して接続されたとき、平面Sと平行な方向にずれた状態となっている。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

絶縁材料によって形成された本体部と、

前記本体部内に形成され、コイル軸方向に並列された第1及び第2のコイル部とを備え、

前記第1及び第2のコイル部の各々は、導体パターンが仮想の平面上に巻回された第1の巻回部と、前記平面と平行に導体パターンが巻回され前記コイル軸方向に前記第1の巻回部と並列されると共に、前記第1の巻回部とスルーホールを介して電気的に接続された第2の巻回部とを有し、

前記第1及び第2のコイル部の少なくとも一方において、前記第1及び第2の巻回部は、前記導体パターンの巻回の間隔が互いに等しい部分を有し、この部分は前記平面と平行な方向にずれていることを特徴とする積層型電子部品。 10

**【請求項 2】**

前記第1のコイル部の前記第2のコイル部側に配置された前記巻回部と、前記第2のコイル部の前記第1のコイル部側に配置された前記巻回部とは、前記導体パターンの巻回の間隔が互いに等しい部分を有し、この部分は前記平面と平行な方向にずれていることを特徴とする請求項1記載の積層型電子部品。 20

**【請求項 3】**

前記平面と平行な方向にずれた部分は、前記スルーホールを挟んだ両側に位置していることを特徴とする請求項1又は2記載の積層型電子部品。 20

**【請求項 4】**

絶縁材料によって形成された本体部と、

前記本体部内に形成され、コイル軸方向に並列された第1及び第2のコイル部とを備え、

前記第1及び第2のコイル部の各々は、導体パターンが仮想の平面上に矩形状に巻回された第1の巻回部と、前記平面と平行に導体パターンが矩形状に巻回され前記コイル軸方向に前記第1の巻回部と並列されると共に、前記第1の巻回部とスルーホールを介して電気的に接続された第2の巻回部とを有し、

前記第1及び第2の巻回部は、一方に延びる直線状の第1ライン部と、前記第1ライン部に略直交する方向に延びる直線状の第2ライン部とを有し、 30

前記第1及び第2のコイル部の少なくとも一方において、前記第1及び第2の巻回部の前記第1ライン部同士及び第2ライン部同士が互いに前記平面と平行な方向にずれていることを特徴とする積層型電子部品。 30

**【請求項 5】**

前記第1のコイル部の前記第2のコイル部側に配置された前記巻回部と、前記第2のコイル部の前記第1のコイル部側に配置された前記巻回部とは、前記第1ライン部及び第2ライン部が互いに前記平面と平行な方向にずれていることを特徴とする請求項4記載の積層型電子部品。 40

**【請求項 6】**

前記第1及び第2のコイル部の前記スルーホールは、前記平面に平行な方向に互いにずれていることを特徴とする請求項1～5いずれか一項記載の積層型電子部品。 40

**【請求項 7】**

絶縁材料によって形成された本体部と、

前記本体部内に形成され、コイル軸方向に並列された第1及び第2のコイル部とを備え、

前記第1及び第2のコイル部の各々は、導体パターンが仮想の平面上に巻回された第1の巻回部と、前記平面と平行に導体パターンが巻回され前記コイル軸方向に前記第1の巻回部と並列されると共に、前記第1の巻回部とスルーホールを介して電気的に接続された第2の巻回部とを有し、

前記第1及び第2のコイル部の少なくとも一方における前記導体パターンは、前記本体 50

部の前記コイル軸方向に沿った断面において千鳥状に配置されていることを特徴とする積層型電子部品。

【請求項 8】

前記第1のコイル部の前記第2のコイル部側に配置された前記導体パターンと、前記第2のコイル部の前記第1のコイル部側に配置された前記導体パターンとは、前記コイル軸方向に沿った断面において千鳥状に配置されていることを特徴とする請求項7記載の積層型電子部品。

【請求項 9】

前記第1及び第2のコイル部の前記スルーホールは、前記コイル軸方向に沿った断面において千鳥状に配置されていることを特徴とする請求項7又は8記載の積層型電子部品。

10

【請求項 10】

前記本体部は磁性体で形成されていることを特徴とする請求項1~9いずれか一項記載の積層型電子部品。

【請求項 11】

前記本体部は、前記コイル軸方向に沿って前記本体部の端面から前記導体パターンまでの連続した領域が磁性体で形成され、それ以外の領域は非磁性体で形成されていることを特徴とする請求項1~9いずれか一項記載の積層型電子部品。

【請求項 12】

前記本体部は、前記コイル軸方向に沿って連続した、前記第1及び第2のコイル部を囲む領域は非磁性体で形成され、それ以外の領域は磁性体で形成されていることを特徴とする請求項1~9いずれか一項記載の積層型電子部品。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、コモンモードチョークコイルやL C フィルタ等の積層型電子部品に関する。

【背景技術】

【0002】

この種の積層型電子部品としては、絶縁材料によって形成された本体部内に、コイル軸方向に並列した第1及び第2のコイル部を有する積層型電子部品（コモンモードチョークコイル）が知られている（例えば、特許文献1参照）。このような積層型電子部品は、第1及び第2のコイル部を構成する導体パターンが形成されたものを含む複数の絶縁体層を積層し、積層方向に加圧して圧着させた後、焼成を施して製造される。

30

【特許文献1】特開平11-54327号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

上記特許文献1に記載されたものを始めとする従来の積層型電子部品では、第1及び第2のコイル部の導体パターンの大部分が本体部の積層方向に重なり合って形成されている。したがって、第1のコイル部と第2のコイル部とによって積層方向に挟まれた部分は、絶縁体層の圧着に際し積層方向に加圧されると、絶縁体層よりも高密度である第1及び第2のコイル部から圧力が加わり、第1及び第2のコイル部に挟まれていない部分よりも絶縁体層を構成する粒子間の隙間が小さくなる。

40

【0004】

このため、第1及び第2のコイル部に挟まれていない部分では、第1のコイル部と第2のコイル部とに挟まれた部分よりも絶縁体層が十分に圧着されず、焼成が施されたとき、デラミネーション（層間剥離）及び/又はクラックが生じる可能性がある。デラミネーションやクラックが生じると、その部分に水分が滞留し、絶縁抵抗が低下したりショートが発生するおそれがある。

【0005】

また、積層型電子部品の中には、絶縁体層に導体パターンが平面状に巻回された巻回部

50

が連結されることにより第1及び第2のコイル部が構成されているものもある。このような積層型電子部品にあっても、導体パターンに挟まれていない部分での絶縁体層が十分に圧着されず、その部分においてデラミネーションやクラックが生じるおそれがある。

#### 【0006】

本発明は、上記従来技術の有する問題に鑑みてなされたものであり、焼成が施された際のデラミネーション及びクラックの発生を抑制できる積層型電子部品を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0007】

本発明の積層型電子部品は、絶縁材料によって形成された本体部と、本体部内に形成され、コイル軸方向に並列された第1及び第2のコイル部とを備え、第1及び第2のコイル部の各々は、導体パターンが仮想の平面上に巻回された第1の巻回部と、平面と平行に導体パターンが巻回されコイル軸方向に第1の巻回部と並列されると共に、第1の巻回部とスルーホールを介して電気的に接続された第2の巻回部とを有し、第1及び第2のコイル部の少なくとも一方において、第1及び第2の巻回部は、導体パターンの巻回の間隔が互いに等しい部分を有し、この部分は平面と平行な方向にずれていることを特徴とするものである。

#### 【0008】

本発明によれば、第1及び第2の巻回部における導体パターンの巻回の間隔が互いに等しい部分が、第1の巻回部が巻回されている仮想の平面と平行な方向にずれているため、未焼成の本体部を構成する絶縁体層を積層して圧着する際、導体パターンから絶縁体層に加わる積層方向（コイル軸方向）の圧力の偏りが低減される。このため、絶縁体層には積層方向にほぼ均等に圧力が加わる。したがって、絶縁体層が圧着された後において、絶縁体層を構成する粒子間の隙間の差が小さくなるため、焼成が施された際の本体部にデラミネーション及びクラックの発生が抑制される。

#### 【0009】

この場合、第1のコイル部の第2のコイル部側に配置された巻回部と、第2のコイル部の第1のコイル部側に配置された巻回部とは、導体パターンの巻回の間隔が互いに等しい部分を有し、この部分は平面と平行な方向にずれていることが好ましい。これにより、第1のコイル部に対して第2のコイル部がずれた状態となるため、圧着時に上記の絶縁体層が受ける積層方向の圧力の偏りがより低減される。したがって、圧着された後の絶縁体層を構成する粒子間の隙間の差をより小さくすることができる。

#### 【0010】

平面と平行な方向にずれた部分は、スルーホールを挟んだ両側に位置していることが好ましい。これにより、第1及び／又は第2のコイル部から上記の絶縁体層に加わる積層方向の圧力の偏りがより低減される。

#### 【0011】

本発明の積層型電子部品は、絶縁材料によって形成された本体部と、本体部内に形成され、コイル軸方向に並列された第1及び第2のコイル部とを備え、第1及び第2のコイル部の各々は、導体パターンが仮想の平面上に矩形状に巻回された第1の巻回部と、平面と平行に導体パターンが矩形状に巻回されコイル軸方向に第1の巻回部と並列されると共に、第1の巻回部とスルーホールを介して電気的に接続された第2の巻回部とを有し、第1及び第2の巻回部は、一方向に延びる直線状の第1ライン部と、第1ライン部に略直交する方向に延びる直線状の第2ライン部とを有し、第1及び第2のコイル部の少なくとも一方において、第1及び第2の巻回部の第1ライン部同士及び第2ライン部同士が互いに平面と平行な方向にずれていることを特徴とするものである。

#### 【0012】

本発明によれば、第1及び第2の巻回部における第1及び第2ライン部が互いに、第1の巻回部が巻回されている仮想の平面と平行な方向にずれているため、未焼成の本体部を構成する絶縁体層を積層して圧着する際、第1及び／又は第2のコイル部から絶縁体層に

10

20

30

40

50

加わる積層方向の圧力の偏りが低減される。このため、絶縁体層には積層方向にほぼ均等に圧力が加わる。したがって、絶縁体層が圧着された後において、絶縁体層を構成する粒子間の隙間の差が小さくなるため、焼成が施された際の本体部にデラミネーション及びクラックの発生が抑制される。

#### 【 0 0 1 3 】

この場合、第1のコイル部の第2のコイル部側に配置された巻回部と、第2のコイル部の第1のコイル部側に配置された巻回部とは、第1ライン部及び第2ライン部が互いに平面と平行な方向にずれていることが好ましい。これにより、第1のコイル部に対して第2のコイル部がずれた状態となる。このため、圧着時に上記の絶縁体層が受ける積層方向の圧力の偏りがより低減され、圧着された後の絶縁体層を構成する粒子間の隙間の差がより小さくなる。

#### 【 0 0 1 4 】

また、第1及び第2のコイル部のスルーホールは、平面に平行な方向に互いにずれていることが好ましい。これにより、スルーホールから上記の絶縁体層に加わる積層方向の圧力も分散させることができるために、圧着された後の絶縁体層を構成する粒子間の隙間の差をさらに小さくすることができる。

#### 【 0 0 1 5 】

本発明の積層型電子部品は、絶縁材料によって形成された本体部と、本体部内に形成され、コイル軸方向に並列された第1及び第2のコイル部とを備え、第1及び第2のコイル部の各々は、導体パターンが仮想の平面上に巻回された第1の巻回部と、平面と平行に導体パターンが巻回されコイル軸方向に第1の巻回部と並列されると共に、第1の巻回部とスルーホールを介して電気的に接続された第2の巻回部とを有し、第1及び第2のコイル部の少なくとも一方における導体パターンは、本体部のコイル軸方向に沿った断面において千鳥状に配置されていることを特徴とするものである。

#### 【 0 0 1 6 】

本発明によれば、本体部のコイル軸方向に沿った断面において導体パターンが千鳥状に配置されているため、未焼成の本体部を構成する絶縁体層の圧着に際して積層方向に加圧されたとき、第1及び/又は第2のコイル部から絶縁体層に加わる積層方向の圧力の偏りが低減される。このため、絶縁層には積層方向にほぼ均等に圧力が加わり、圧着された後において、絶縁体層を構成する粒子間の隙間の差が小さくなる。したがって、焼成して得られた本体部に対するデラミネーション及びクラックの発生を抑制することができる。

#### 【 0 0 1 7 】

この場合、第1のコイル部の第2のコイル部側に配置された導体パターンと、第2のコイル部の第1のコイル部側に配置された導体パターンとは、コイル軸方向に沿った断面において千鳥状に配置されていることが好ましい。これにより、第1のコイル部に対して第2のコイル部がずれた状態となるため、圧着時に上記の絶縁体層が受ける積層方向の圧力の偏りがより低減される。したがって、圧着された後の絶縁体層を構成する粒子間の隙間の差をより小さくすることができる。

#### 【 0 0 1 8 】

また、第1及び第2のコイル部のスルーホールは、コイル軸方向に沿った断面において千鳥状に配置されていることが好ましい。これにより、スルーホールから上記の絶縁体層に加わる積層方向の圧力も分散させることができるために、圧着された後の絶縁体層を構成する粒子間の隙間の差をさらに小さくすることができる。

#### 【 0 0 1 9 】

本体部は磁性体で形成されていてもよい。これにより、周波数帯域が1.0(MHz)～1.0(GHz)程度であるコモンモードノイズを除去できるコモンモードチョークコイルを実現することができる。

#### 【 0 0 2 0 】

本体部は、コイル軸方向に沿って本体部の端面から導体パターンまでの連続した領域が磁性体で形成され、それ以外の領域は非磁性体で形成されていることが好ましい。これに

10

20

30

40

50

より、導体パターン間の浮遊容量が低減され、10 (MHz) ~ 3.0 (GHz) 程度の高周波帯域のコモンモードノイズを除去できるコモンモードチョークコイルを実現することができる。

【0021】

本体部は、コイル軸方向に沿って連続した、第1及び第2のコイル部を囲む領域は非磁性体で形成され、それ以外の領域は磁性体で形成されていることが好ましい。これにより、導体パターン間の浮遊容量がさらに低減され、10 (MHz) ~ 6.0 (GHz) 程度の高周波帯域のコモンモードノイズを除去できるコモンモードチョークコイルを実現することができる。

【発明の効果】

10

【0022】

本発明によれば、焼成が施された際のデラミネーション及びクラックの発生を抑制できる積層型電子部品を提供することができる。

【発明を実施するための最良の形態】

【0023】

以下、添付図面を参照しながら、本発明の好適な実施形態について詳細に説明する。なお、図面の説明において、同一または相当要素には同一の符号を付し、重複する説明は省略する。

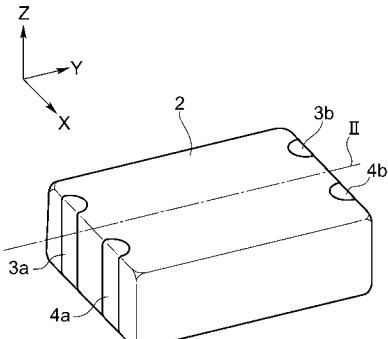

【0024】

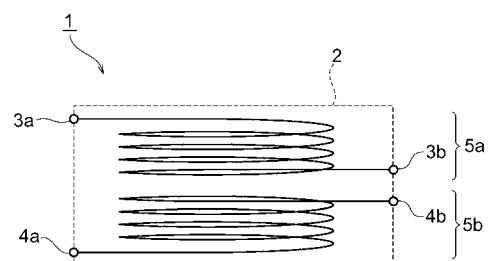

図1は、本実施形態に係る積層型電子部品を示す斜視図であり、図2は、図1に示す積層型電子部品をII線でコイル軸方向Zに切断した断面を示す図である。なお、本実施形態における積層型電子部品1は、本発明をコモンモードチョークコイルに適用したものである。積層型電子部品1は、絶縁材料によって形成された直方体形状の本体部2と、この本体部2の内部に形成されコイル軸方向Zに並列する2つのコイル部5a, 5bと、本体部2の長手方向の一組の端面に形成された2対の外部電極3a, 3b, 4a, 4bとを備えている。この外部電極3a, 3b, 4a, 4bは、例えば、銀を主成分とする図示しない端子電極と、この端子電極の表面を覆うように形成され、Cu、Ni及びSn等からなる図示しないめっき膜とによって構成されている。このような積層型電子部品1の等価回路図を図3に示す。

【0025】

20

本体部2は、詳細は後述するが、絶縁性のグリーンシート6がコイル軸方向Zに積層された積層体を焼成することによって形成されている。

【0026】

30

コイル部5a, 5bの各々は、グリーンシート6上に形成された導体パターン7によって構成されている。コイル部5a (5b)は、図2に示す積層型電子部品1において、仮想の平面S上に導体パターン7が矩形状に巻回された巻回部8a (8c)を有している。また、この巻回部8a (8c)には、平面Sと平行に導体パターン7が矩形状に巻回された巻回部8b (8d)がコイル軸方向Zに並列されている。そして、巻回部8a (8c)と巻回部8b (8d)とはスルーホール9を介して電気的に接続されている。

【0027】

40

なお、積層された導体パターン7付きグリーンシート6の積層方向の少なくとも上部には、導体パターン7が形成されていない1又は複数のグリーンシート6が積層されている。

【0028】

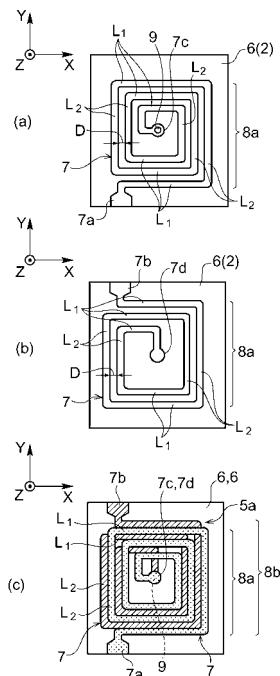

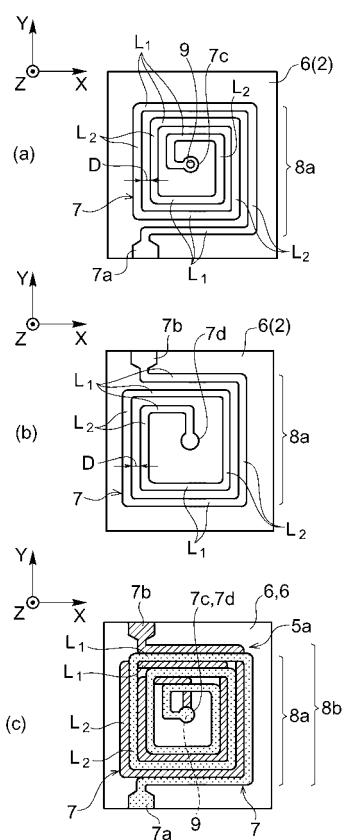

図4は、コイル部5aを構成する導体パターン7が形成されたグリーンシート6を示す図である。同図において、(a)は、巻回部8aを有するグリーンシート6をコイル軸方向Zから見た図であり、(b)は、巻回部8bを有するグリーンシート6をコイル軸方向Zから見た図である。また、図4(c)は、図4(b)に示すグリーンシート6の上に図4(a)に示すグリーンシート6が積層され、巻回部8a, 8bがスルーホール9を介して接続されたコイル部5aを示している。

50

## 【0029】

グリーンシート6は、上記平面Sに相当する、あるいは平面Sと平行になっている薄板であり、その表面には、導体パターン7が巻回されることによって構成された巻回部8a又は巻回部8bが形成されている。この巻回部8a, 8bの巻回方向は、互いが接続されたとき、コイル部5aが同一方向に巻回されたものとなるようになっている。

## 【0030】

導体パターン7の一方の端部7a, 7bは、グリーンシート6の縁部まで引き出されており、それぞれ外部電極3a, 3b又は4a, 4bに接続されている。そして、巻回部8a, 8bは、図4(c)に示すように、巻回部8bの上に巻回部8aが配置された際、導体パターン7の他方の端部7c, 7dが、グリーンシート6を貫通するスルーホールを介して接続される。

## 【0031】

そして、巻回部8a, 8bは、導体パターン7の巻回の間隔が互いに等しい部分を有しており、この部分は、図4(c)に示すように、巻回部8aと巻回部8bとがコイル軸方向Zに並列して接続されたとき、スルーホール9を挟んだ両側に位置し、平面Sと平行な方向にずれた状態となっている。ここでいう「巻回の間隔」とは、巻回された導体パターン7において、ある領域とその外側に巻回されている領域との間隔のことである(例えば、図4(a), (b)に示す間隔D)。

## 【0032】

これをより具体的に説明すると、本実施形態に係る巻回部8a, 8bは矩形状に巻回されているため、一方向(ここではX方向)に延びる直線状のライン部L<sub>1</sub>と、このライン部L<sub>1</sub>に直交する方向(ここではY方向)に延びる直線状のライン部L<sub>2</sub>とをそれぞれ有している。そして、巻回部8a, 8bのライン部L<sub>1</sub>, L<sub>1</sub>同士及びライン部L<sub>2</sub>, L<sub>2</sub>同士が、平面Sと平行な方向にずれた状態となる(図4(c)参照)。そのため、本体部2をコイル軸方向Zに沿った断面で見ると、図2に示すように、導体パターン7は千鳥状に配置されている。

## 【0033】

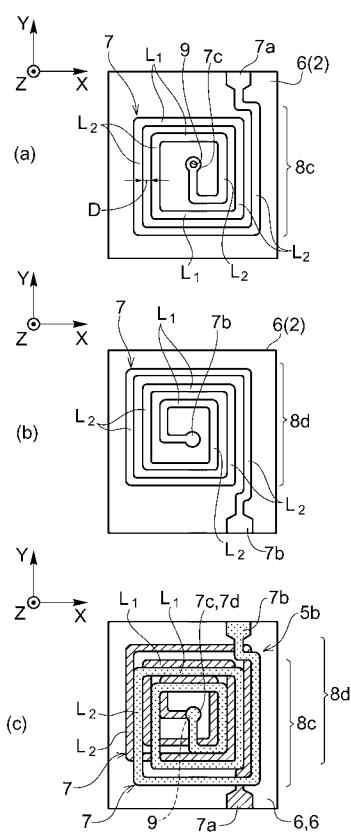

図5は、コイル部5bを構成する導体パターン7が形成されたグリーンシート6を示す図である。同図において、(a)は、巻回部8cを有するグリーンシート6をコイル軸方向Zから見た図であり、(b)は、巻回部8dを有するグリーンシート6をコイル軸方向Zから見た図である。また、図5(c)は、図5(b)に示すグリーンシート6の上に図5(a)に示すグリーンシート6が積層され、巻回部8c, 8dがスルーホール9を介して接続されたコイル部5bを示している。

## 【0034】

図5(c)に示すコイル部5bにおいても上記コイル部5aと同様に、巻回部8c, 8dが、導体パターン7の巻回の間隔が互いに等しい部分を有していると共に、この部分が、図5(c)に示すように、巻回部8cと巻回部8dとがコイル軸方向Zに並列して接続されたとき、平面Sと平行な方向にずれた状態となっている。つまり、矩形状に巻回された巻回部8c, 8dにおいて、一方向に延びる直線状のライン部L<sub>1</sub>, L<sub>1</sub>同士及びこのライン部L<sub>1</sub>, L<sub>1</sub>に直交する方向に延びる直線状のライン部L<sub>2</sub>, L<sub>2</sub>同士が、平面Sと平行な方向にずれた状態となっている(図5(c)参照)。そのため、本体部2をコイル軸方向Zに沿った断面で見ると、図2に示すように、導体パターン7は千鳥状に配置されている。

## 【0035】

また、コイル部5a及びコイル部5bにおける隣り合った巻回部8b, 8cも、互いのライン部L<sub>1</sub>, L<sub>1</sub>同士及びライン部L<sub>2</sub>, L<sub>2</sub>同士が平面Sと平行な方向にずれた状態となっている。このため、本体部2をコイル軸方向Zに沿った断面で見ると、図2に示すように、巻回部8a~8dを通して導体パターン7が千鳥状に配置された状態となっている。

## 【0036】

10

20

30

40

50

図5(c)に示すコイル部5bを構成するグリーンシート6,6の上には、図4(c)に示すコイル部5bを構成するグリーンシート6,6が積層される。その後、後述する、圧着、切断、焼成、外部電極形成等の工程を経ることにより、図1に示す積層型電子部品1が得られる。

【0037】

以下、上記積層型電子部品1の製造方法について説明する。

【0038】

まず、Ni-Cu-Zn系フェライト、Ni-Cu-Zn-Mg系フェライト、Cu-Zn系フェライト、Ni-Cu系フェライト等の磁性体を用いて得られるスラリーを、ドクターブレード法等によりベースフィルム上に所定の厚みで塗布して切断し、複数枚の磁性体のグリーンシート(絶縁体層)6を作製する。なお、後述する積層型電子部品30,40では、その一部に非磁性体のグリーンシート6が用いられている。このような非磁性体のグリーンシートを作製する場合は、 $Fe_2O_3$ ,  $ZnO$ ,  $CuO$ の混合物を原料としたスラリーをドクターブレード法等によりベースフィルム上に塗布して切断する。そして、グリーンシート6の所定の位置に、レーザー加工等によってスルーホール9を形成する。

10

【0039】

次に、Agを主成分とした導体ペーストを用いて、例えばスクリーン印刷により、グリーンシート6上に導体パターン7を形成し、その後乾燥させる。このとき、上記巻回部8a~8dがそれぞれ一枚のグリーンシート6の表面に設けられるように導体パターン7を形成する。

20

【0040】

次に、グリーンシート6と、導体パターン7付きグリーンシート6とを積層・圧着する。この場合、4枚の導体パターン7付きグリーンシート6を積層し、その導体パターン7付きグリーンシート6の上に1又は複数のグリーンシート6を積層する。これにより、グリーンシート6上の導体パターン7が保護される。なお、1又は複数のグリーンシート6を積層し、その上に4枚の導体パターン7付きグリーンシート6を積層するようにしてもよい。また、圧着の際に加える圧力は、例えば、65~100 MPa程度とするのが好ましい。

30

【0041】

グリーンシート6のスルーホール9は、コイル軸方向Zに隣り合う巻回部8a,8b及び巻回部8c,8dの導体パターン7の端部同士が重なる部位に形成されており、巻回部8a,8bの導体パターン7及び巻回部8c,8dの導体パターン7がグリーンシート6の積層によりスルーホール9を介してそれぞれ接続されるようになっている。

30

【0042】

通常、グリーンシート6が積層された段階では、コイル軸方向Zに並列したコイル部の組がコイル軸方向Zと直交する方向に複数配列されたウェハ状となっているため、このウェハを所定の形状・大きさに切断することによって、複数の未焼成状態の本体部2を得る。その後、この未焼成状態の本体部2を所定の温度で焼成して図2に示す本体部2を得る。

40

【0043】

本体部2は、一般に外部電極3a,3b,4a,4bの形成された位置が特定しやすいように直方体とし、例えば、焼成後に、長手方向(Y方向)の長さが1.2mm、幅方向(X方向)の長さが1.0mm、高さ方向(Z方向)の長さが0.7mm程度(いわゆる1210形状)となるように切断して作製する。この場合、導体パターン7の端部7a,7bが、本体部2の長手方向の端面に位置するように切断する。また、焼成の温度は、例えば、870程度とする。

【0044】

次に、導体パターン7の端部7a,7bが露出した本体部2の端面に、銀を主成分とする導体ペーストを塗布した後、700度程度で焼き付け、その表面に電気めっきを施し

50

て外部電極 3 a , 3 b , 4 a , 4 b を形成する。なお、電気めっきは、例えば、Cu、Ni および Sn、または Ni および Sn を用いて行う。以上により、本実施形態に係る積層型電子部品 1 が完成する。

#### 【 0 0 4 5 】

以上のような積層型電子部品 1 では、グリーンシート 6 を積層して圧着する際、導体パターン 7 からグリーンシート 6 に加わるコイル軸方向 Z の圧力が、平面 S の面方向にほぼ均等になる。このため、グリーンシート 6 が圧着された後において、グリーンシート 6 を構成する粒子間の隙間の差が小さくなり、焼成が施された際のデラミネーション及びクラックの発生が抑制される。

#### 【 0 0 4 6 】

また、コイル部 5 a 及びコイル部 5 b の隣り合う巻回部 8 b , 8 c についても、互いのライン部 L<sub>1</sub> , L<sub>1</sub> 同士及びライン部 L<sub>2</sub> , L<sub>2</sub> 同士が平面 S と平行な方向にずれた状態とすることにより、圧着時にグリーンシート 6 が受けるコイル軸方向 Z の圧力の偏りがより低減される。したがって、圧着された後の本体部を構成する粒子間の隙間の差をより小さくすることができる。

#### 【 0 0 4 7 】

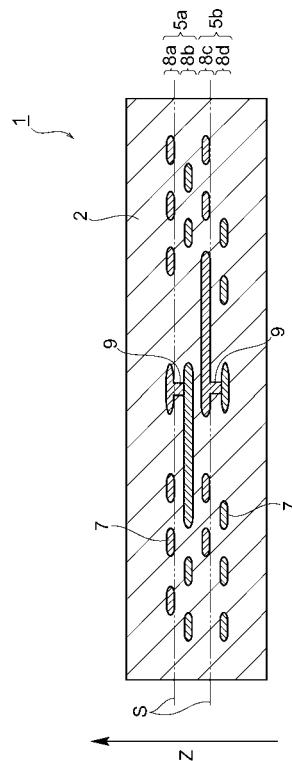

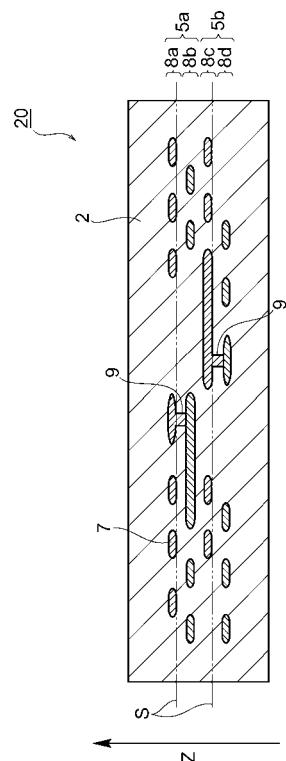

図 6 は、本発明に係る積層型電子部品の他の形態を示し、コイル軸方向 Z に切断した断面を示す図であり、図 7 は、図 6 に示す積層型電子部品 20 のコイル部 5 a , 5 b を示す図である。積層型電子部品 20 は、図 7 に示すように、スルーホール 9 が平面 S に平行な方向に互いにずれている点で、上記積層型電子部品 1 と異なっている。この積層型電子部品 20 をコイル軸方向 Z に沿った断面で見た場合、図 6 に示すように、スルーホール 9 が千鳥状に配置されている。

#### 【 0 0 4 8 】

このような積層型電子部品 20 では、グリーンシート 6 を積層して圧着する際、スルーホール 9 からグリーンシート 6 に加わるコイル軸方向 Z の圧力も平面 S の面方向に分散される。このため、グリーンシート 6 を圧着して得られた本体部 2 を構成する粒子間の隙間の差がさらに小さくなり、焼成が施された際に、スルーホール 9 付近でデラミネーションやクラックが発生する可能性が低減される。

#### 【 0 0 4 9 】

ここで、上記積層型電子部品 1 , 20 では本体部 2 がすべて磁性体から形成されているが、本体部 2 におけるコイル軸方向 Z の上下に非磁性体のグリーンシートから形成された非磁性体部を備えてよい。以下、非磁性体部を備えた積層型電子部品について説明する。

#### 【 0 0 5 0 】

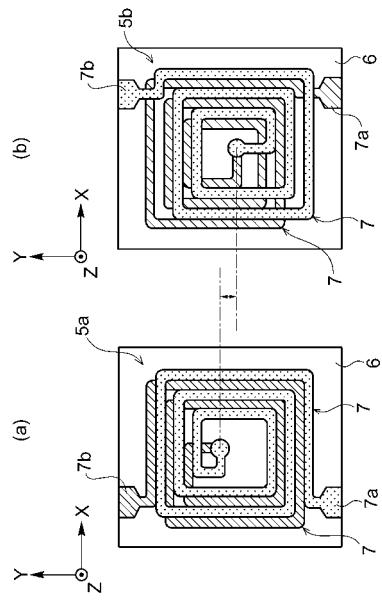

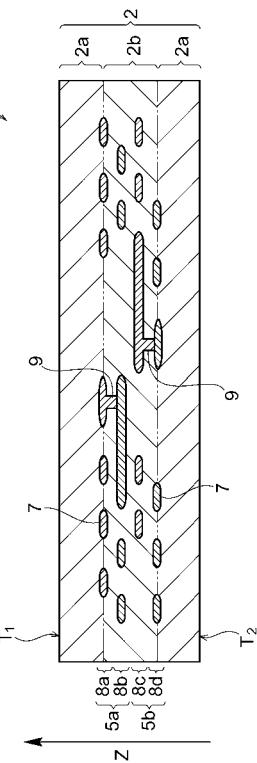

図 8 、 9 は、本実施形態に係る積層型電子部品の他の形態を示す図である。図 8 に示す積層型電子部品 30 では、本体部 2 において、本体部 2 の上面 T<sub>1</sub> 及び底面 T<sub>2</sub> のそれから導体パターン 7 までコイル軸方向 Z に沿って連続した領域が磁性体部 2 a , 2 a となっており、それ以外の領域は非磁性体部 2 b となっている。つまり、本体部 2 は、導体パターン 7 を境に磁性体部 2 a と非磁性体部 2 b とに分けられている（図中、境界線を二点鎖線で示す。）。

#### 【 0 0 5 1 】

図 8 に示す積層型電子部品 30 では、本体部 2 内の上側に位置するコイル部 5 a において、上側の巻回部 8 a を構成する導体パターン 7 が非磁性体のグリーンシート 6 に形成され、本体部 2 内の下側に位置するコイル部 5 b において、下側の巻回部 8 d を構成する導体パターン 7 が磁性体のグリーンシート 6 に形成され、また、その間の導体パターン 7 が非磁性体のグリーンシート 6 に形成されている。これにより、コイル部 5 a の上側に位置する巻回部 8 a を構成する導体パターン 7 を境に、上側が磁性体部 2 a 、下側が非磁性体部 2 b となっており、コイル部 5 b の上側に位置する巻回部 8 d を構成する導体パターン 7 を境に、上側が非磁性体部 2 b 、下側が磁性体部 2 a となっている。

#### 【 0 0 5 2 】

10

20

30

40

50

上記の積層型電子部品 1, 2 0 のように本体部 2 がすべて磁性体で形成された場合は、周波数帯域が 1.0 (MHz) ~ 1.0 (GHz) 程度であるコモンモードノイズを除去できるのに対し、図 8 に示す積層型電子部品 3 0 では、導体パターン間の浮遊容量が低減されるため、1.0 (MHz) ~ 3.0 (GHz) 程度の高周波帯域のコモンモードノイズを除去することができる。

#### 【0053】

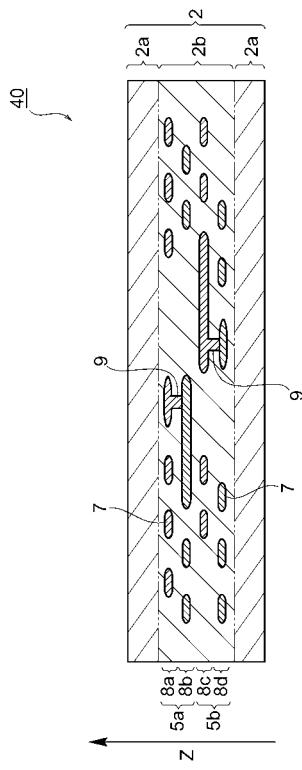

図 9 に示す積層型電子部品 4 0 では、本体部 2 において、コイル部 5 a, 5 b を囲むコイル軸方向 Z に沿って連続した領域が非磁性体部 2 b となっており、それ以外の領域は磁性体部 2 a となっている（図中、境界線を二点鎖線で示す。）。

#### 【0054】

図 9 に示す積層型電子部品 4 0 では、本体部 2 内の上側に位置するコイル部 5 a において、上側の巻回部 8 a を構成する導体パターン 7 の上に非磁性体のグリーンシート 6 が積層され、本体部 2 内の下側に位置するコイル部 5 b において、下側の巻回部 8 d を構成する導体パターン 7 が非磁性体のグリーンシート 6 に形成され、また、その間の導体パターン 7 が非磁性体のグリーンシート 6 に形成されている。これにより、巻回部 8 a ~ 8 d が非磁性体部 2 b 内に形成され、非磁性体部 2 b の上下には磁性体部 2 a, 2 a が形成される。

#### 【0055】

このような積層型電子部品 4 0 では、導体パターン間の浮遊容量がさらに低減されるため、1.0 (MHz) ~ 6.0 (GHz) 程度の高周波帯域までのコモンモードノイズを除去することができる。

#### 【0056】

以上、本発明の好適な実施形態について詳細に説明したが、本発明は上記実施形態に限定されるものではない。例えば、上記実施形態では、コイル部 5 a, 5 b の両方において、互いの導体パターン 7 がずれた状態となっているが、コイル部 5 a, 5 b のいずれか一方がずれた状態であってもよい。また、本発明は、コイル部 5 a, 5 b のいずれか一方にコンデンサ回路を附加することによって構成された L C フィルタにも適用することができる。

#### 【実施例】

#### 【0057】

以下、実施例及び比較例を挙げ、本発明の積層型電子部品の内容をさらに詳しく説明するが、本発明はこれらの実施例に何ら限定されるものではない。

#### 【0058】

実施例として、本発明に係る積層型電子部品を用い、比較例として、巻回部における導体パターンの大部分がコイル軸方向に重なり合っている従来の積層型電子部品を用いて、それぞれのデラミネーション及びクラックの発生数を調べた。

#### 【0059】

実施例及び比較例に係る積層型電子部品は、上述した製造方法において、非磁性体のグリーンシートの厚みを 1.8  $\mu\text{m}$  とし、磁性体のグリーンシートの厚みを 2.0  $\mu\text{m}$  となるようにした。また、焼成後の導体パターンは、幅 5.0  $\mu\text{m}$ 、厚み 1.4  $\mu\text{m}$  となるようにし、導体パターンの巻回の間隔（図 4 における間隔 D）は 8.0  $\mu\text{m}$  となるようにした。

#### 【0060】

このような実施例及び比較例に係る積層型電子部品をそれぞれ約 60000 (個/ロット) 製造し、その中から抜き取り検査を行ってデラミネーション及びクラックの発生状況を調べた。まず、それぞれ 600 個の抜き取り検査を行ってクラックの発生数を調べたところ、比較例に係る積層型電子部品の発生率が 0.5 % であったのに対し、実施例に係る積層型電子部品の発生率は 0 % であった。また、60 個を抜き取り、断面検査を行った結果、ショートに至る可能性があるデラミネーションが生じていたものが、比較例に係る積層型電子部品では 3 個確認されたが、実施例に係る積層型電子部品では 0 個であった。

#### 【0061】

10

20

30

40

50

以上により、本発明に係る積層型電子部品は、デラミネーション及びクラックの発生を確実に抑制することができるため信頼性が高く、量産性にも優れたものであることが確認された。

【図面の簡単な説明】

【0062】

【図1】本発明の実施形態に係る積層型電子部品を示す斜視図である。

【図2】図1に示す積層型電子部品をII-I線でコイル軸方向Zに切断した断面を示す図である。

【図3】図1に示す積層型電子部品の等価回路図を示す図である。

【図4】コイル部5aを構成する導体パターンが形成されたグリーンシートを示す図である。 10

【図5】コイル部5bを構成する導体パターンが形成されたグリーンシートを示す図である。

【図6】上記積層型電子部品の他の形態を示し、コイル軸方向Zに切断した断面を示す図であり。

【図7】図6に示す積層型電子部品のコイル部を示す図である。

【図8】本発明の実施形態に係る積層型電子部品の他の形態を示す図である。

【図9】本実施形態に係る積層型電子部品の他の形態を示す図である。

【符号の説明】

【0063】

1...積層型電子部品、2...本体部、2a...磁性体部、2b...非磁性体部、5a,5b...コイル部、7...導体パターン、8a~8d...巻回部、9...スルーホール、20,30,40...積層型電子部品、L<sub>1</sub>,L<sub>2</sub>...ライン部、S...平面(仮想の平面)、Z...コイル軸方向。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 佐藤 善光

東京都中央区日本橋一丁目13番1号 TDK株式会社内

(72)発明者 熊谷 修美

東京都中央区日本橋一丁目13番1号 TDK株式会社内

F ターム(参考) 5E070 AA05 AB01 BA01 CB02 CB13

5J024 AA01 CA06 DA01 DA29 DA35 EA08

【要約の続き】