## SCHWEIZERISCHE EIDGENOSSENSCHAFT

EIDGENÖSSISCHES INSTITUT FÜR GEISTIGES EIGENTUM

(11) CH 702 971 A2

(51) Int. Cl.: **H03K 17/10** (2006.01) **H03K 17/56** (2006.01)

## Patentanmeldung für die Schweiz und Liechtenstein

Schweizerisch-liechtensteinischer Patentschutzvertrag vom 22. Dezember 1978

## (12) PATENTANMELDUNG

(21) Anmeldenummer: 00500/10

(71) Anmelder:

ETH Zürich ETH Transfer, HG E 47-49 Rämistrasse 101 8092 Zürich ETH-Zentrum (CH)

(22) Anmeldedatum: 07.04.2010

(43) Anmeldung veröffentlicht:

(72) Erfinder: Daniel Aggeler, 8044 Zürich (CH) Jürgen Biela, 8004 Zürich (CH) Johann Kolar, 8044 Zürich (CH)

(74) Vertreter:

Frei Patentanwaltsbüro AG, Postfach 1771

8032 Zürich (CH)

# (54) SCHALTEINRICHTUNG MIT JFET-SERIESCHALTUNG.

14.10.2011

(57) Eine Schalteinrichtung zum Schalten eines Stromes zwischen einem ersten Anschluss (1) und einem zweiten Anschluss (2) weist eine Serieschaltung von mindestens zwei JFETs  $(J_1-J_n)$  auf, mit weiteren JFETs  $(J_2-J_n)$ , die zu einem untersten JFET  $(J_1)$  in Serie geschaltet sind, und wobei ein Beschaltungsnetzwerk zur Stabilisierung der Gatespannungen der JFETs  $(J_1-J_n)$ , zwischen dem zweiten Anschluss (2) und dem ersten Anschluss (1) geschaltet ist.

Dabei ist zwischen Gateanschlüssen (G<sub>12</sub>, G<sub>13</sub>, ..., G<sub>Jn</sub>) der weiteren JFETs (J<sub>2</sub>-J<sub>n</sub>) und dazugehörigen Kathodenanschlüssen des Beschaltungsnetzwerkes jeweils eine Zusatzschaltung (5) bzw. eine Ansteuerschaltung geschaltet, welche beim Einschalten und im eingeschalteten Zustand das Potential des jeweiligen Gateanschlusses höher hält als jenes des dazugehörigen Sourceanschlusses.

## Beschreibung

[0001] Die Erfindung bezieht sich auf das Gebiet der elektronischen Schaltungstechnik und insbesondere auf eine Schalteinrichtung mit einer Serieschaltung von Sperrschicht-FETs (JFET oder Junction Field Effect Transistor) gemäss dem Oberbegriff von Patentanspruch 1 respektive Anspruch 9.

### STAND DER TECHNIK

[0002] Leistungsschalter oder Schalteinrichtungen zum Schalten bei hohen Betriebsspannungen können in leistungselektronischen Schaltungen durch Kaskadierung oder in Serie angeordnete Transistoren realisiert werden. Dabei werden nach US 6 822 842 oder DE 19 926 109 A1 solche Schalteinrichtungen beispielsweise als Kaskode-Schaltung bezeichnet, welche auf der speziellen Zusammenschaltung eines MOSFET M und mindestens einem JFET J1 basieren, illustriert durch die Fig. 1. Die Schalter sind zwischen einem ersten Anschluss 1 und einem zweiten Anschluss 2 angeordnet und durch einen Steueranschluss 3 des MOSFET M gesteuert. Diese bekannte Schalteinrichtung für hohe Betriebsspannungen basierend auf der Kaskoden-Topologie sieht vor, mehrere JFETs J2 ... Jn in Serie zu schalten und damit eine hohe Sperrspannung zu erreichen. Zur passiven Steuerung der dynamischen Sperrspannungsaufteilung des mit seriellen angeordneten Transistoren aufgebauten Leistungsschalters wird ein Beschaltungsnetzwerk 4 zwischen dem ersten Anschluss 1 und dem zweiten Anschluss 2 angeschlossen, wobei Avalanche-Dioden DAV.1- 1 und dem zweiten Anschluss 2 angeschlossen, wobei Avalanche-Dioden DAV.1- DAV,n des Beschaltungsnetzwerkes 4 zwischen den Gate-Anschlüssen der JFETs angeschlossen sind. Die Funktionsweise des Beschaltungsnetzwerkes 4 zur symmetrischen Sperrspannungsaufteilung der JFETs ist in der Publikation «Balancing Circuit for a 5kV/50ns Pulsed Power Switch Based on SiC-JFET Super Cascode» (J. Biela, D. Aggeier, J.W. Kolar, Proceedings of the 17<sup>th</sup> IEEE Pulsed Power Conference (PPC'09)) beschrieben.

[0003] Aufgrund der Durchlasswiderstände der einzelnen Halbleiterschalter M, J<sub>1</sub> ... J<sub>n</sub> in der Serieschaltung entsteht im eingeschalteten Zustand ein Spannungsabfall über jedem Element. Dabei bewirkt die Summe aller Spannungsabfälle speziell beim obersten JFET J<sub>n</sub> der Fig. 1, eine andere Gate-Source Spannung als bei den unteren JFETs. Diese unterschiedliche Gate-Source Spannung kann dazu führen, dass der oberste Transistor ausgeschaltet und dabei hochohmig wird und eine hohe Vorwärtsspannung im eingeschalteten Zustand erfährt, was im schlimmsten Fall zu seiner Zerstörung führt.

#### DARSTELLUNG DER ERFINDUNG

[0004] Es ist deshalb die Aufgabe der Erfindung, eine Schalteinrichtung mit einer Serieschaltung von Sperrschicht-FETs der eingangs genannten Art zu schaffen welche die oben genannten Nachteile behebt.

[0005] Diese Aufgabe löst eine Schalteinrichtung mit einer Serieschaltung von Sperrschicht-FETs mit den Merkmalen des Patentanspruches 1.

[0006] Die Schalteinrichtung zum Schalten eines Stromes zwischen einem ersten Anschluss und einem zweiten Anschluss weist also eine Serieschaltung von mindestens zwei JFETs auf, von denen ein unterster JFET mit dem ersten Anschluss verbunden ist oder über einen in Serie angeordneten Steuerschalter mit dem ersten Anschluss verbunden ist. Es liegt mindestens ein weiterer JFET vor, der zu dem untersten JFET in Serie geschaltet ist, wobei der am weitesten vom untersten JFET entfernte JFET als oberster JFET bezeichnet wird und mit seinem Drainanschluss mit dem zweiten Anschluss verbunden ist. Die vom untersten oder ersten JFET verschiedenen JFET werden zusammenfassend auch als obere JFET bezeichnet. Es ist ein Beschaltungsnetzwerk zur dynamischen Sperrspannungsaufteilung und zur Stabilisierung der Gatespannungen der JFETs zwischen dem ersten Anschluss und dem zweiten Anschluss geschaltet. Das Beschaltungsnetzwerk weist beispielsweise jeweils zwischen den Gates zweier aufeinanderfolgender JFETs in Sperrrichtung betriebene Dioden auf. Dabei ist jeweils zwischen den Gateanschlüssen der oberen JFETs und der Kathode der jeweiligen Diode eine Zusatzschaltung geschaltet, welche im eingeschalteten Zustand der Schaltung das Potential am Gateanschluss der oberen JFETs hoch hält, und ein unerwünschtes Ausschalten der oberen JFETs verhindert.

[0007] Dadurch werden bei eingeschalteten oberen JFETs abhängig vom Laststrom die Spannungen an den oberen Gates geringfügig über, vorzugsweise aber gleich bzw. geringfügig unter der Spannung am jeweiligen Sourceanschluss gehalten. Vorzugsweise resultiert eine Gate-Sourcespannung, welche mindestens zweimal, vorzugsweise fünfmal oder zehnmal kleiner ist als ohne die Zusatzschaltung. Dadurch bleiben beim Einschalten die oberen JFETs eher eingeschaltet als ohne die Zusatzschaltung. Dadurch wiederum wird verhindert, dass insbesondere der oberste JFET zwischen dem ersten und dem zweiten Anschluss hochohmig wird und die gesamte Spannung aufnimmt.

[0008] Die Zusatzschaltung bewirkt, dass beim Einschalten die parasitären Kapazitäten des Beschaltungsnetzwerkes sich jeweils über die Diode der Zusatzschaltung entladen können und gleichzeitig die jeweiligen Gates der JFETs über eine Kapazität parallel zur Diode der Zusatzschaltung hoch gehalten wird.

[0009] Dadurch wird die dynamische Einschaltung des mit seriell angeordneten Transistoren aufgebauten Leistungsschalters durch die gesamte Zusatzschaltung balanciert wie auch synchronisiert.

[0010] Die Zusatzschaltung für sich alleine gesehen vermag, allgemein gesprochen, für jeden der JFETs eine vorgebbare Spannung zwischen dessen Gateanschluss und Sourceanschluss anzulegen. Diese Zusatzschaltung bewirkt eine symmetrische Spannungsbelastung der Gate Sourceanschlüsse der seriell geschalteten JFETs.

[0011] In weiteren bevorzugten Ausführungsformen der Erfindung ist die Zusatzschaltung nicht bei jedem der oberen JFET angeschlossen, sondern nur bei einem oder mehreren, vorzugsweise bei weiter oben liegenden JFETs.

[0012] In einer weiteren Ausführungsform der Erfindung wird in mindestens einer der Zusatzschaltungen eine weitere Diode antiparallel zur bestehenden Diode und in Serie zum Kondensator der Zusatzschaltung geschaltet. Diese resultierende Ansteuerschaltung bewirkt, dass sich die Kondensatoren der Zusatzschaltung während des dynamischen Einschaltens und des statischen Einschaltzustandes nicht entladen und somit die Gatepotentiale der oberen JFETs auf einem definierten Potential bleiben.

[0013] In einer weiteren Ausführungsform der Erfindung ist die Folge von Diode und Zusatzschaltung in der Serieschaltung umgekehrt: die Zusatzschaltung ist nicht zwischen Gateanschluss und Kathodenanschluss, sondern zwischen Gateanschluss des jeweils unteren JFETs und dem Anodenanschluss der jeweiligen Diode angeschlossen.

[0014] Grundsätzlich gilt, dass die Schaltung sinngemäss modifiziert auch für p-Kanal JFETs anstelle der hier gezeichneten n-Kanal JFETs einsetzbar ist. Dabei entspricht komplementär der Drainanschluss dem Sourceanschluss und der Sourceanschluss dem Drainanschluss.

[0015] Weitere bevorzugte Ausführungsformen gehen aus den abhängigen Patentansprüchen hervor.

#### KURZE BESCHREIBUNG DER ZEICHNUNGEN

[0016] Im Folgenden wird der Erfindungsgegenstand anhand von bevorzugten Ausführungsbeispielen, welche in den beiliegenden Zeichnungen dargestellt sind, näher erläutert. Es zeigen jeweils schematisch:

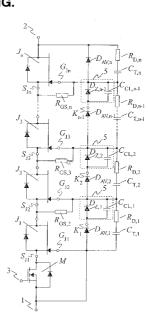

- Fig. 1 eine Serieschaltung von Sperrschicht-FETs gemäss dem Stand der Technik; und

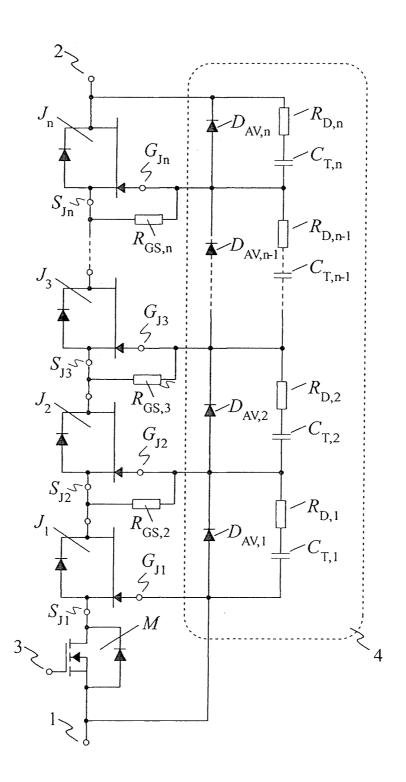

- Fig. 2 eine erste Ausführungsform der Erfindung, und

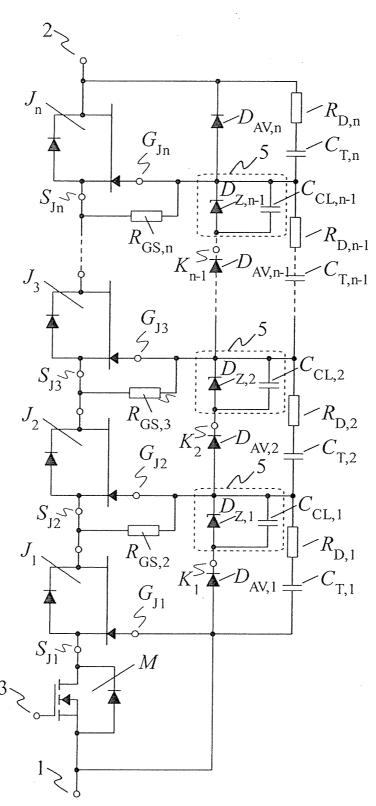

- Fig. 3 eine zweite Ausführungsform der Erfindung.

[0017] Grundsätzlich sind in den Figuren gleiche Teile mit gleichen Bezugszeichen versehen.

#### WEGE ZUR AUSFÜHRUNG DER ERFINDUNG

[0018] In Fig. 1 ist die Erfindung für eine Schalteinrichtung hoher Betriebsspannung dargestellt. Die Schaltung weist eine Kaskodenschaltung eines MOSFET M mit einem ersten oder untersten JFET  $J_1$  und mindestens einem in Serie zu diesem ersten JFET  $J_1$  geschalteten weiteren oder oberen JFET  $J_2$ - $J_n$  auf. Der unterste oder erste JFET ist also in der Kaskodenschaltung von einem als Steuerschalter wirkenden MOSFET angesteuert. Der letzte, am weitesten vom ersten JFET entfernte JFET der in Serie geschalteten JFETs wird auch als oberster JFET  $J_n$  bezeichnet. Zur Stabilisierung der Gatespannungen der JFETs und zur Vergleichmässigung der Spannungsbelastung der JFETs ist ein Beschaltungsnetzwerk 4 angeordnet. Dieses weist jeweils zwischen den Gates zweier aufeinanderfolgender JFETs eine Parallelschaltung von in Sperrrichtung betriebenen Diode  $D_{AV,1}$ ,  $D_{AV,2}$ , ...  $D_{AV,n}$  und einer RC-Schaltung  $R_{D,1}$   $C_{T,1}$ ,  $R_{D,2}$   $C_{T,2}$ ,  $R_{D,n}$   $C_{T,n}$  auf.

[0019] Jeweils zwischen Gate und Source der oberen JFETs J<sub>2</sub>-J<sub>n</sub> (also nicht des ersten JFET) sind Widerstände (in Fig. 1: R<sub>GS.2</sub> - R<sub>GS.n</sub>) geschaltet. Anstelle der Widerstände können auch Zenerdioden verwendet werden.

[0020] Zur dynamischen und auch statischen Kontrolle der Gatespannungen zwischen dem Gate  $(G_{12}, G_{13}, ..., G_{1n})$  und dem Kathodenanschluss  $(K_1, K_2...K_{n-1})$  der Diode des Beschaltungsnetzwerkes ist jeweils eine Zusatzschaltung 5 geschaltet. Diese weist gemäss der Fig. 2 eine Parallelschaltung aus einer Zenerdiode Dz,1, Dz,2, ... Dz,n-I und eines Kondensators  $C_{CL,1}$ ,  $C_{CL,2}$ , ...  $C_{CL,n-1}$  auf. Diese bewirken, dass das Potential am Gateanschluss der oberen JFETs hochgehalten wird und damit einerseits die Vorwärtsspannung der Dioden, andererseits der Spannungsabfall resultierend wegen dem Durchlasswiderstand kompensiert und die anliegende Spannung zwischen dem Gateanschluss und dem Sourceanschluss vorzugsweise gleich null oder gering positiv gehalten wird.

[0021] Der Kondensator der Zusatzschaltung ist, verglichen mit der Sperrschichtkapazität der in Sperrrichtung betriebenen Dioden und der Drain-Sourcekapazität des jeweiligen JFETs, um ein Vielfaches grösser und bewirkt dadurch beim Einschalten, dass die gespeicherte Energie nicht vollständig entzogen werden kann und eine resultierende Spannung über dem Kondensator der Zusatzschaltung verbleibt, welche die Spannung des jeweiligen Gates hochhält.

[0022] Das Beschaltungsnetzwerk leitet von den Gateanschlüssen der JFETs (J<sub>1</sub>-J<sub>n</sub>) einen Ladestrom in die jeweils zugeordneten Speicherelemente (Sperrschichtkapazität der in Sperrrichtung betriebenen Diode und Kapazität des RC-Elementes des Beschaltungsnetzwerkes mit der Zusatzschaltung) ab und bewirkt damit eine dynamische Stabilisierung der in Serie geschalteten JFETs.

[0023] Anstelle der Zenerdiode und des Kondensators können in der Zusatzschaltung andere Schaltungselemente vorliegen, welche den gleichen Effekt bewirken, z.B. nur eine oder zwei oder mehr in Serie geschaltete Zenerdioden, bzw. nur eine oder zwei oder mehrere parallel geschaltete Kondensatoren.

[0024] In einer bevorzugten Ausführungsform der Erfindung ist die Zusatzschaltung nicht bei jedem der oberen JFET angeschlossen, sondern nur bei einem oder mehreren, vorzugsweise bei weiter oben liegenden JFETs.

[0025] Fig. 3 zeigt eine alternative bevorzugte Ausführungsform der Erfindung, in welcher weitere Dioden  $D_{ZR,1}$ ,  $D_{ZR,2}$ ,... $D_{ZR,n-1}$  jeweils seriell zum Kondensator und antiparallel zur Diode der Zusatzschaltung geschaltet sind.

[0026] Für die Erfindung als Ganzes gilt grundsätzlich, dass die Schaltung, sinngemäss modifiziert auch für p-Kanal JFETs anstelle der hier gezeichneten n-Kanal JFETs, einsetzbar ist.

## Patentansprüche

- Schalteinrichtung zum Schalten eines Stromes zwischen einem ersten Anschluss (1) und einem zweiten Anschluss (2), aufweisend eine Serieschaltung von mindestens zwei JFETs (J<sub>1</sub>-J<sub>n</sub>), von denen ein unterster JFET (J<sub>1</sub>) mit dem ersten Anschluss (1) verbunden ist oder der unterste JFET (J<sub>1</sub>) in einer Kaskodeschaltung über einen Steuerschalter (M) mit dem ersten Anschluss (1) verbunden ist, und einem oder mehreren weiteren, oberen JFET (J<sub>2</sub>-J<sub>n</sub>), der oder die zu dem untersten JFET (J<sub>1</sub>) in Serie geschaltet ist/sind, wobei der am weitesten vom untersten JFET (J<sub>1</sub>) entfernte JFET (J<sub>n</sub>) als oberster JFET (J<sub>n</sub>) bezeichnet wird und mit seinem Drainanschluss mit dem zweiten Anschluss (2) verbunden ist, und wobei ein passives Beschaltungsnetzwerk (4) zur dynamischen Ansteuerung der Gatespannungen der JFETs (J<sub>1</sub>-J<sub>n</sub>) zwischen Gateanschlüsse der JFETs (J<sub>1</sub>-J<sub>n</sub>) und dem ersten Anschluss (1) geschaltet ist, wobei das Beschaltungsnetzwerk (4) jeweils zwischen den Gates zweier aufeinanderfolgender JFETs in Sperrrichtung betriebene Dioden (D<sub>AV,1</sub>, D<sub>AV,2</sub>, ... D<sub>AV,n</sub>) aufweist, dadurch gekennzeichnet, dass zwischen den Gateanschlüssen (G<sub>J2</sub>, G<sub>J3</sub>, ... G<sub>Jn</sub>) der oberen JFETs (J<sub>2</sub>, J<sub>3</sub>, ... J<sub>n</sub>) und Kathodenanschlüssen (K<sub>DAV,2</sub>, K<sub>DAV,3</sub>, ... K<sub>DAV,n-1</sub>) der Dioden des Beschaltungsnetzwerks (4), oder zwischen Anodenanschlüssen der Dioden des Beschaltungsnetzwerks (4) und den Gateanschlüssen (G<sub>J2</sub>, G<sub>J3</sub>,...G<sub>Jn</sub>) von zugeordneten JFETs (J<sub>1</sub>, J<sub>3</sub>, ..., J<sub>n-1</sub>), jeweils eine Zusatzschaltung (5) geschaltet ist welche das Potential des jeweiligen Gateanschlusses im dynamischen Einschalten wie im stationären Einschaltzustand gegenüber dem dazugehörigen Sourceanschlusse (S<sub>J2</sub>, S<sub>J3</sub>, ..., S<sub>Jn</sub>) hoch hält.

- Schalteinrichtung gemäss Anspruch 1, wobei das Beschaltungsnetzwerk (4) mit der Zusatzschaltung (5) von den Gateanschlüssen der JFETs (J<sub>1</sub>-J<sub>n</sub>) einen Ladestrom in jeweils zugeordnete Speicherelemente des Beschaltungsnetzwerks (4) mit der Zusatzschaltung (5) ableitet und damit eine dynamische Stabilisierung der in Serie geschalteten JFETs bewirkt.

- 3. Schalteinrichtung gemäss Anspruch 1 oder 2, wobei die Zusatzschaltung (5) zusammen mit dem Beschaltungsnetzwerk (4) eine symmetrische Spannungsbelastung der Gateanschlüsse der JFETs (J<sub>1</sub>-J<sub>n</sub>) und zusätzlich ein sauberes Einschaltverhalten der oberen JFETs (J<sub>2</sub>-J<sub>n</sub>) bewirkt, indem beim Einschalten und im eingeschalteten Zustand der jeweilige Gateanschluss durch die Zusatzschaltung auf einem höheren Potential als ohne Zusatzschaltung gehalten wird.

- Schalteinrichtung gemäss einem der bisherigen Ansprüche, wobei die Zusatzschaltung (5) eine oder mehrere in Serie

und in Sperrrichtung zwischen den Gateanschlüssen (G<sub>J2</sub>, G<sub>J3</sub>, ..., G<sub>Jn</sub>) und den Kathodenanschlüssen (K<sub>1</sub>, K<sub>2</sub>, ...,

K<sub>n-1</sub>) betriebene Dioden (D<sub>Z,1</sub>, D<sub>Z,2</sub>,...D<sub>Z,n-1</sub>) aufweist.

- Schalteinrichtung gemäss einem der bisherigen Ansprüche, wobei die Zusatzschaltung (5) einen oder mehrere jeweils parallel zu den in Sperrrichtung betriebenen Dioden (D<sub>Z,1</sub>, D<sub>Z,2</sub>, ... D<sub>Z,n-1</sub>), Kondensatoren (C<sub>CL,1</sub>, C<sub>CL,2</sub>, ... C<sub>CL,n-1</sub>) aufweist.

- 6. Schalteinrichtung gemäss einem der bisherigen Ansprüche, wobei mindestens eine Ansteuerschaltung (6) aus einer Zusatzschaltung und einer weiteren Diode (D<sub>ZR.1</sub>, D<sub>ZR.2</sub>, ..., D<sub>ZR.n-1</sub>) vorliegt.

- Schalteinrichtung gemäss Anspruch 6, in welcher in mindestens einer der Zusatzschaltungen (6) eine weitere Diode (D<sub>ZR.1</sub>, D<sub>ZR.2</sub>, ..., D<sub>ZR.n-1</sub>) in Serie zum Kondensator der Zusatzschaltung und antiparallel zur Diode (D<sub>Z.1</sub>, D<sub>Z.2</sub>, ... D<sub>Z,n-1</sub>) der Zusatzschaltung geschaltet ist.

- 8. Schalteinrichtung gemäss einem der bisherigen Ansprüche, wobei die Zusatzschaltung (5) und die Ansteuerschaltung (6) so ausgelegt sind, dass bei einem Einschaltvorgang und im eingeschaltenen Zustand auftretende Spannungsabfälle an den oberen JFETs wie auch die Vorwärtsspannung der in Sperrrichtung betriebenen Dioden des Beschaltungsnetzwerkes (4) reduziert sind und im Vergleich mit der Schalteinrichtung ohne Zusatzschaltung (5) bzw. Ansteuerschaltung (6) eine Gate-Sourcespannung resultiert welche mindestens zweimal, vorzugsweise fünfmal oder zehnmal kleiner ist, oder, kein Spannungsabfall resultiert, oder die Gate-Sourcespannung geringfügig positiv ist.

- 9. Schalteinrichtung zum Schalten eines Stromes zwischen einem ersten Anschluss und einem zweiten Anschluss, aufweisend eine Serieschaltung von mindestens zwei p-Kanal JFETs, von denen ein unterster JFET mit dem ersten Anschluss verbunden ist oder der unterste JFET in einer Kaskodeschaltung über einen Steuerschalter mit dem ersten Anschluss verbunden ist, und einem oder mehreren weiteren, oberen JFET, der oder die zu dem untersten JFET in Serie geschaltet ist/sind, wobei der am weitesten vom untersten JFET entfernte JFET als oberster JFET bezeichnet wird und mit seinem Sourceanschluss mit dem zweiten Anschluss verbunden ist, und wobei ein passives Beschaltungsnetzwerk zur dynamischen Ansteuerung der Gatespannungen der JFETs zwischen Gateanschlüsse der JFETs und dem ersten Anschluss geschaltet ist, wobei das Beschaltungsnetzwerk jeweils zwischen den Gates zweier

- aufeinanderfolgender JFETs in Sperrrichtung betriebene Dioden aufweist, dadurch gekennzeichnet, dass zwischen den Gateanschlüssen der oberen JFETs und Kathodenanschlüssen der Dioden des Beschaltungsnetzwerks, oder zwischen Anodenanschlüssen der Dioden des Beschaltungsnetzwerks und den Gateanschlüssen von zugeordneten JFETs, jeweils eine Zusatzschaltung geschaltet ist welche das Potential des jeweiligen Gateanschlusses im dynamischen Einschalten wie im stationären Einschaltzustand gegenüber dem dazugehörigen Drainanschluss hoch hält.

- 10. Schalteinrichtung gemäss Anspruch 9, wobei das Beschaltungsnetzwerk mit der Zusatzschaltung von den Gateanschlüssen der JFETs einen Ladestrom in jeweils zugeordnete Speicherelemente des Beschaltungsnetzwerks mit der Zusatzschaltung ableitet und damit eine dynamische Stabilisierung der in Serie geschalteten p-Kanal JFETs bewirkt.

Fig. 1

Fig. 2

Fig. 3