(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-49561

(P2011-49561A)

(43) 公開日 平成23年3月10日(2011.3.10)

| (51) Int.Cl.             | F 1                   | テーマコード (参考) |

|--------------------------|-----------------------|-------------|

| HO 1 L 27/115 (2006.01)  | HO 1 L 27/10 4 3 4    | 5 B 1 2 5   |

| HO 1 L 21/8247 (2006.01) | HO 1 L 29/78 3 7 1    | 5 F 0 8 3   |

| HO 1 L 29/792 (2006.01)  | HO 1 L 27/10 4 5 1    | 5 F 1 0 1   |

| HO 1 L 29/788 (2006.01)  | HO 1 L 27/10 4 8 1    |             |

| HO 1 L 27/10 (2006.01)   | G 1 1 C 17/00 6 2 2 E |             |

審査請求 未請求 請求項の数 43 O L (全 70 頁) 最終頁に続く

|                    |                              |          |                                                                                                                                                        |

|--------------------|------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号          | 特願2010-189800 (P2010-189800) | (71) 出願人 | 390019839<br>三星電子株式会社<br>SAMSUNG ELECTRONICS CO., LTD.<br>大韓民国京畿道水原市靈通区梅灘洞416<br>416, Maetan-dong, Yeongtong-gu, Suwon-si,<br>Gyeonggi-do 442-742 (KR) |

| (22) 出願日           | 平成22年8月26日 (2010.8.26)       | (74) 代理人 | 110000051<br>特許業務法人共生国際特許事務所                                                                                                                           |

| (31) 優先権主張番号       | 10-2009-0079243              | (72) 発明者 | 孫炳根<br>大韓民国 京畿道 水原市 灵通区 灵通洞 404 棟2004号                                                                                                                 |

| (32) 優先日           | 平成21年8月26日 (2009.8.26)       |          |                                                                                                                                                        |

| (33) 優先権主張国        | 韓国 (KR)                      |          |                                                                                                                                                        |

| (31) 優先権主張番号       | 12/752,485                   |          |                                                                                                                                                        |

| (32) 優先日           | 平成22年4月1日 (2010.4.1)         |          |                                                                                                                                                        |

| (33) 優先権主張国        | 米国 (US)                      |          |                                                                                                                                                        |

| (特許庁注: 以下のものは登録商標) |                              |          |                                                                                                                                                        |

| 1. R R A M         |                              |          |                                                                                                                                                        |

最終頁に続く

(54) 【発明の名称】 3次元メモリセルアレイを含む半導体メモリ素子及びその製造方法

## (57) 【要約】

【課題】高密度、且つ工程マージンの確保された3次元メモリセルアレイを含む半導体メモリ素子を提供する。

【解決手段】平坦な基板と、基板に対して垂直に形成され且つ各々複数の貯蔵セルを含む複数のメモリストリングからなるメモリストリングアレイと水平方向に互いに重畠した複数のワードラインを含み、ワードラインは各々基板に平行で且つメモリストリングに接続された第1部分及び第1部分から延伸され基板に対して上方に傾斜する第2部分を含み、メモリストリングアレイは複数のワードラインの各々の第1部分の中間部分に配置され、ワードラインの各々に接続されて各々対応する貯蔵セルを形成し、複数のワードラインの第1、第2グループは各々、メモリストリングアレイの第1、第2の側方に配置された第1、第2導電ラインのグループの各々と電気的に接続される。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

平坦な基板と、

前記基板に対して垂直（Z方向とする）に形成され、且つ、各々複数の貯蔵セル（メモリセル）を含む複数のメモリストリングからなるメモリストリングアレイ（X、Y方向に整列しているとする）と、

Z方向に互いに離隔して重畠した複数のワードラインとを含み、

前記ワードラインは各々前記基板に平行に形成され、前記メモリストリングに接続された第1部分、及び前記第1部分から延伸され前記基板に対して上方（Z方向に）に傾斜する第2部分を含み、

前記メモリストリングアレイは前記複数のワードラインの各々の第1部分に配置され、前記ワードラインの各々に接続されて各々対応する前記貯蔵セルを形成し、

前記複数のワードラインの第1グループは前記メモリストリングアレイの第1の側方に配置された第1導電ラインのグループの各々と電気的に接続され、前記複数のワードラインの第2グループは前記メモリストリングアレイの第2の側方に配置された第2導電ラインのグループの各々と電気的に接続されることを特徴とする半導体メモリ素子。

**【請求項 2】**

前記ワードラインのうち、前記第1グループのワードライン及び前記第2グループのワードラインは、前記メモリストリングの上部から底部まで延伸された垂直方向（Z方向）に沿って交互に位置することを特徴とする請求項1に記載の半導体メモリ素子。

**【請求項 3】**

前記メモリストリングの延伸方向は、前記基板と90°に交差し、前記メモリストリングアレイの前記第1の側方は、前記メモリストリングアレイの前記第2の側方と、前記メモリストリングアレイを挟んで対向することを特徴とする請求項1に記載の半導体メモリ素子。

**【請求項 4】**

前記複数のワードラインの各々の第1部分は互いに平行であることを特徴とする請求項1に記載の半導体メモリ素子。

**【請求項 5】**

前記メモリストリングアレイの前記第1の側方に位置する前記複数のワードラインの各々の前記第2部分は、互いに平行であり、前記メモリストリングアレイの前記第2の側方に位置する前記複数のワードラインの各々の前記第2部分は、互いに平行であることを特徴とする請求項1に記載の半導体メモリ素子。

**【請求項 6】**

前記第1グループのワードラインは前記メモリストリングの上部から底部に向かってカウンティングし、奇数番目の貯蔵セルに各々接続するよう配置され、前記第2グループのワードラインは前記メモリストリングの上部から底部に向かってカウンティングし、偶数番目の貯蔵セルに各々接続するよう配置されることを特徴とする請求項1に記載の半導体メモリ素子。

**【請求項 7】**

前記メモリストリングアレイの前記第1の側方に位置する、偶数番目の前記ワードラインの第2部分の上方に傾斜して延伸された端部、及び前記メモリストリングアレイの前記第2の側方に位置する、奇数番目の前記ワードラインの第2部分の上方に傾斜して延伸された端部に各々配置された絶縁キャップをさらに含むことを特徴とする請求項1に記載の半導体メモリ素子。

**【請求項 8】**

第3導電ラインと接続され、前記メモリストリングアレイの第3の側方に配置されたワードラインの第3グループをさらに含み、

前記ワードラインの第1グループは前記メモリストリングの上部から底部に向かってカウンティングしてモジュロ（m o d u l o ）3で第1番目の貯蔵セルと各々接続され、

10

20

30

40

50

前記ワードラインの第2グループは前記メモリストリングアレイの上部から底部に向かってカウンティングしてモジュロ3で第2番目の貯蔵セルと各々接続され、

前記ワードラインの第3グループは前記メモリストリングアレイの上部から底部に向かってカウンティングしてモジュロ3で第0番目の貯蔵セルと各々接続されることを特徴とする請求項1に記載の半導体メモリ素子。

【請求項9】

前記複数の貯蔵セルの各々及び対応するワードラインは前記基板の平坦面に平行に配置された他の平面に配置されることを特徴とする請求項1に記載の半導体メモリ素子。

【請求項10】

前記メモリストリングアレイの他の側方の同一の平面内に配置されたワードラインの連続する部分は1つのワードラインに電気的に接続されることを特徴とする請求項9に記載の半導体メモリ素子。

【請求項11】

前記基板は水平であり、前記メモリストリングは垂直であり、

前記基板上に配置された周辺領域をさらに含むことを特徴とする請求項1に記載の半導体メモリ素子。

【請求項12】

前記第1グループのワードラインと第1導電ラインとの間、及び前記第2グループのワードラインと前記第2導電ラインとの間に、各々コンタクトパッドとして配置された複数の導電パターンをさらに含むことを特徴とする請求項1に記載の半導体メモリ素子。

【請求項13】

前記平坦な基板上に配置された周辺領域をさらに含むことを特徴とする請求項12に記載の半導体メモリ素子。

【請求項14】

前記周辺領域は、前記導電パターンの下部面と同一のレベルに配置されることを特徴とする請求項13に記載の半導体メモリ素子。

【請求項15】

前記ワードラインの前記上方に傾斜する第2部分は、前記基板と50°乃至90°の角度を有することを特徴とする請求項1に記載の半導体メモリ素子。

【請求項16】

前記上方に傾斜する第2部分は、各ワードラインの前記第1部分の両端から延伸され、前記第2部分の各対の1方は絶縁キャップで覆われることを特徴とする請求項1に記載の半導体メモリ素子。

【請求項17】

前記ワードライン及び前記メモリストリング( Z方向 )の各々と直交するように配置された複数のビットライン( Y方向 )をさらに含み、前記複数のビットラインの各々は、該ビットラインに沿って配置された前記複数のメモリストリングの上端で該メモリストリングに接続されることを特徴とする請求項1に記載の半導体メモリ素子。

【請求項18】

前記平坦な基板上にチャンバ( 凹部 )をさらに含み、

前記チャンバは、前記基板内のシリコンリセスを含み、前記メモリストリング、ビットライン、及びワードラインの各々の延長部は前記シリコンリセス内に配置されることを特徴とする請求項1に記載の半導体メモリ素子。

【請求項19】

前記平坦な基板上にチャンバをさらに含み、

前記チャンバは前記基板の上部面上の絶縁壁を含み、前記メモリストリング、ビットライン、及びワードラインの延長部は前記絶縁壁の周りに配置されることを特徴とする請求項1に記載の半導体メモリ素子。

【請求項20】

前記ワードラインの延長部は金属またはシリサイドを含むことを特徴とする請求項1に

10

20

30

40

50

記載の半導体メモリ素子。

**【請求項 2 1】**

前記複数の貯蔵セルを含む前記メモリストリングは柱、管、またはバーサイド形状を有することを特徴とする請求項 1 に記載の半導体メモリ素子。

**【請求項 2 2】**

少なくとも 2 つのロウデコーダをさらに含み、

1 つのロウデコーダは前記第 1 グループのワードラインの側方に配置され、他のロウデコーダは前記第 2 グループのワードラインの側方に配置されることを特徴とする請求項 6 に記載の半導体メモリ素子。

**【請求項 2 3】**

さらに、各々、X 方向に整列した複数のメモリストリングに接続され、離隔して互いに平行に Y 方向に整列した複数のストリング選択ラインを備え、

前記 2 つのロウデコーダの中の第 1 ロウデコーダは、Y 方向に沿ってカウントして偶数番目、または奇数番目からなる前記ストリング選択ラインのグループのいずれか 1 つと接続され、

前記 2 つのロウデコーダの中の第 2 ロウデコーダは、前記ストリング選択ラインのグループの他の 1 つと各々接続されることを特徴とする請求項 2 2 に記載の半導体メモリ素子。

**【請求項 2 4】**

前記 2 つのロウデコーダの中の第 1 ロウデコーダは、すべてのストリング選択ライン、及び Z 方向に沿ってカウントして偶数番目または奇数番目のワードラインのグループのいずれか 1 つと接続され、

前記 2 つのロウデコーダの中の第 2 ロウデコーダは、すべてのストリング選択ライン、及び前記ワードラインのグループの他の 1 つと各々接続されることを特徴とする請求項 2 2 に記載の半導体メモリ素子。

**【請求項 2 5】**

前記基板はシリコンを含み、前記絶縁膜はシリコン酸化膜を含み、前記ワードラインは金属を含むことを特徴とする請求項 1 に記載の半導体メモリ素子。

**【請求項 2 6】**

前記貯蔵セルは制御ゲート、第 1 絶縁領域、電荷貯蔵領域、及び第 2 絶縁領域を含むことを特徴とする請求項 1 に記載の半導体メモリ素子。

**【請求項 2 7】**

前記貯蔵セルは、制御ゲートとして金属ゲート、ブロッキング膜として h i g h - K 領域、電荷貯蔵膜として窒化領域、及びトンネル膜として酸化領域を含むことを特徴とする請求項 1 に記載の半導体メモリ素子。

**【請求項 2 8】**

平坦な基板を提供し、

前記基板上にチャンバ(凹部)を形成し、

絶縁膜及び犠牲膜を前記チャンバ内に交互に蒸着し、各膜は、水平な第 1 部分、及び前記基板に対して上方に傾斜する少なくとも 1 つの第 2 部分を含み、

前記基板に垂直であり、前記重疊した膜を貫通して基板に到達するホール(貫通孔)を形成し、

前記ホール内に前記基板と垂直にメモリストリングを蒸着してメモリストリングアレイを形成し、

前記メモリストリングは複数の貯蔵セルを含み、

犠牲膜を導電膜に各々取り替え、複数の延伸されたワードラインを形成し、

前記離隔して重疊した複数のワードラインのうち、奇数番目のワードラインを、前記メモリストリングアレイの第 1 の側方に配置した導電ラインと接続し、偶数番目のワードラインを前記メモリストリングアレイの第 2 の側方に配置した導電ラインと各々接続することを含むことを特徴とする半導体メモリ素子の製造方法。

10

20

30

40

50

**【請求項 29】**

前記メモリストーリングの最上部レベルの表面上に周辺領域を形成することをさらに含むことを特徴とする請求項28に記載の半導体メモリ素子の製造方法。

**【請求項 30】**

前記垂直メモリストーリングはバーサイド形であり、

X-cutのためにトレンチを形成し、メモリストーリングを2つの平行なストーリングに分けることをさらに含むことを特徴とする請求項28に記載の半導体メモリ素子の製造方法。

**【請求項 31】**

前記基板はシリコンを含み、前記絶縁膜はシリコン酸化膜を含み、前記ワードラインは金属を含むことを特徴とする請求項28に記載の半導体メモリ素子の製造方法。 10

**【請求項 32】**

前記チャンバは前記基板を直接リセスして形成されることを特徴とする請求項28に記載の半導体メモリ素子の製造方法。

**【請求項 33】**

前記チャンバは前記基板上に絶縁側壁を形成して前記基板上に形成されることを特徴とする請求項28に記載の半導体メモリ素子の製造方法。

**【請求項 34】**

前記貯蔵セルは、前記メモリストーリングとして形成された、ワードラインに接続された制御ゲート、第1絶縁領域、電荷貯蔵領域、第2絶縁領域、及びチャネルが形成される活性領域を含むことを特徴とする請求項28に記載の半導体メモリ素子の製造方法。 20

**【請求項 35】**

前記貯蔵セルは、制御ゲートとして金属ゲート膜、ブロッキング領域(第2絶縁領域)としてhigh-K膜、電荷貯蔵領域として窒化膜、及びトンネル領域(第1絶縁領域)として酸化膜を含むことを特徴とする請求項28に記載の半導体メモリ素子の製造方法。

**【請求項 36】**

基板と、

前記基板に対して垂直(Z方向とする)に形成された複数のメモリストーリングからなるメモリストーリングアレイ(X、Y方向に整列しているとする)と、

前記メモリストーリングは複数の貯蔵セル(メモリセル)を含み、

Z方向に互いに離隔して重畳した複数のワードラインとを含み、

前記ワードラインは各々前記基板に平行に形成され、前記メモリストーリングに結合された第1部分、及び前記第1部分から延伸され前記基板に対して上方(Z方向に)に傾斜する第2部分を含み、

前記メモリストーリングのアレイは前記複数のワードラインの各々の第1部分に配置され、前記ワードラインの各々に結合されて各々対応する前記貯蔵セルを形成し、

前記Z方向に重畳した複数のワードラインのうち、奇数番目のワードラインは前記メモリストーリングアレイの第1の側方に配置された第1導電ラインのグループ内の各々の導電ラインと電気的に接続され、

偶数番目のワードラインは前記メモリストーリングアレイの第2の側方に配置された第2導電ラインのグループ内の各々の導電ラインと電気的に接続されることを特徴とする半導体メモリ素子。 40

**【請求項 37】**

基板と、

前記基板に対して垂直(Z方向とする)に形成された複数のメモリストーリングからなるメモリストーリングアレイ(X、Y方向に整列しているとする)と、

前記メモリストーリングは複数の貯蔵セル(メモリセル)を含み、

Z方向に互いに離隔して重畳した複数のワードラインとを含み、

前記ワードラインは各々前記基板に平行に形成され、前記メモリストーリングに結合された第1部分、及び前記第1部分から延伸され前記基板に対して上方(Z方向に)に傾斜す 50

る第2部分を含み、

前記メモリストリングのアレイは前記複数のワードラインの各々の第1部分に配置され、前記ワードラインの各々に結合されて各々対応する前記貯蔵セルを形成し、

前記ワードラインは前記メモリストリングアレイの第1の側方に配置された第1導電ラインと選択的に接続された第1ワードライン、及び前記メモリストリングアレイの第2の側方に配置された第2導電ラインと選択的に接続された第2ワードラインを含むことを特徴とする半導体メモリ素子。

#### 【請求項38】

前記ワードラインは少なくとも1つのダミーワードラインを含むことを特徴とする請求項37に記載の半導体メモリ素子。

10

#### 【請求項39】

前記第1の側方には第1ロウデコーダを有し、前記第2の側方には第2ロウデコーダを有することを特徴とする請求項37に記載の半導体メモリ素子。

#### 【請求項40】

基板と、

前記基板に対して垂直(Z方向とする)に形成された複数のメモリストリングからなるメモリストリングアレイ(X、Y方向に整列しているとする)と、

前記メモリストリングは複数の貯蔵セル(メモリセル)を含み、

Z方向に互いに離隔して重畳した複数のワードラインと、

少なくとも2つのロウデコーダとを含み、

20

前記複数のワードラインは、前記メモリストリングアレイの第1の側方に配置された1つのロウデコーダと電気的に接続されたワードラインの第1グループと、前記メモリストリングアレイの第2の側方に配置された他のロウデコーダと電気的に接続されたワードラインの第2グループとを含むことを特徴とする半導体メモリ素子。

#### 【請求項41】

さらに、各々、X方向に整列した複数のメモリストリングに接続され、離隔して互いに平行にY方向に整列した複数のストリング選択ラインを備え、

前記第1ロウデコーダは、前記メモリストリングアレイの第1の側方に配置した導電ラインを介して前記ストリング選択ラインの第1のグループと接続され、

30

前記第2ロウデコーダは、前記メモリストリングアレイの第2の側方に配置した導電ラインを介して前記ストリング選択ラインの残りからなるグループと接続されることを特徴とする請求項40に記載の半導体メモリ素子。

#### 【請求項42】

前記2つのロウデコーダの中のいずれか1つは前記ストリング選択ラインの全体と接続されることを特徴とする請求項40に記載の半導体メモリ素子。

#### 【請求項43】

平坦な基板を提供し、

前記基板上にチャンバ(凹部)を形成し、

前記チャンバ内に絶縁膜及び導電膜を交互に蒸着し、

前記導電膜は複数のワードラインを形成し、

40

各膜は、水平な第1部分、及び前記基板に対して上方に傾斜する少なくとも1つの第2部分を含み、

前記基板に垂直であり、前記重畳した膜を貫通して前記基板に到達するホール(貫通孔)を形成し、

前記ホール内に前記基板と垂直にメモリストリングを形成してメモリストリングアレイを形成し、

前記メモリストリングは複数の貯蔵セルを含み、

前記離隔して重畳した複数のワードラインのうち、奇数番目のワードラインを前記メモリストリングアレイの第1の側方に配置したコンタクトパッドに接続し、偶数番目のワードラインを前記メモリストリングアレイの第2の側方に配置したコンタクトパッドに接続

50

することを特徴とする半導体メモリ素子の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体素子に係り、より具体的には、分散した(distributed)コンタクトパッドを有する改善した3次元構造を有する半導体メモリ素子に関する。 10

【背景技術】

【0002】

半導体産業の高度発展によって、半導体素子の高集積化、低消費電力化及び／または高速化などが深化している。特に、半導体素子の高集積化は多様な電子機器の仕様を増加させることができ、且つ製品の価格を決める重要な要因であるので、最近になって重要性が大きくなっている。かくして、高集積化された半導体素子を実現するため、半導体技術は既存の平板型素子から脱して多様な構造を含む半導体素子を製造するように発展した。 20

【0003】

半導体素子の高集積化及び構造の多様化によって、半導体素子に存在する多様で複雑なパターンを導電ライン及び他のパターンと接続する工程のマージン確保がますます難しくなっている。半導体素子の工程で不良が発生した場合、半導体素子の信頼性が低下し、これは半導体素子を含む電子器機性能の低下に直結する。これによって、複雑なパターンを有する半導体素子において工程マージンを確保し、高集積化された半導体素子で信頼性向上させるための多様な研究が進められている。 20

【先行技術文献】

【特許文献】

【0004】

【特許文献1】日本特許出願公開第2008-263029号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の目的は、メモリセルアレイ、及びメモリセルアレイとその外部電気回路網との間の電気的な接続を含めた構成に係り、高密度、且つ工程マージンの確保された3次元構造のメモリ素子を提供することにある。 30

したがって、垂直NAND、V NANDに限定されず、RRAM、MRAM及びPRAMのような3次元構造のメモリ素子に適用できる。

【0006】

本発明の他の目的は、メモリセルアレイ、及びメモリセルアレイとその外部電気回路網との間の電気的接続を含めた構成に係り、高密度、且つ工程マージンの確保された3次元構造のメモリ素子の製造方法を提供することにある。

したがって、垂直NANDまたはV NANDに限定されず、PRAM、MRAM、RRAMなどのような3次元構造のメモリ素子の製造に適用できる。

【課題を解決するための手段】

【0007】

本発明の一実施形態によると、半導体メモリ素子は平坦な基板と、前記基板に垂直であり、複数の貯蔵セルを含むメモリストリングと、複数のワードラインとを含み、各ワードラインは前記基板に平行であり、前記メモリストリングに接続された第1部分及び前記基板と交差する第2部分を含み、前記複数のワードラインの第1グループは前記メモリストリングの第1側の第1導電ラインと電気的に接続され、前記複数のワードラインの第2グループは前記メモリストリングの第2側の第2導電ラインと電気的に接続される。 40

【0008】

ワードラインの第1グループのワードライン及びワードラインの第2グループのワードラインは、前記メモリストリングの上部から底まで延長する方向に交互に位置する。延長するメモリストリングは前記基板と90°に交差し、前記メモリストリングの前記第1側

10

20

30

40

50

は前記メモリストリングの前記第2側と対向する。

【0009】

前記複数のワードラインの各々の第1部分は各々互いに平行である。前記メモリストリングの前記第1側の前記複数のワードラインの各々の前記第2部分は各々互いに平行である。

【0010】

前記第1交互(*alternating*)ワードラインは前記メモリストリングの上部から底にカウンティング(*counting*)して、奇数番目の貯蔵セルに各々配置され、前記第2交互(*alternating*)ワードラインは前記メモリストリングの上部から底にカウンティング(*counting*)して、偶数番目の貯蔵セルに各々配置される。10

【0011】

前記半導体メモリ素子はメモリストリングの前記第1側の偶数番目のワードラインの前記第2部分の前記延長された一端、及び前記メモリストリングの前記第2側の奇数番目のワードラインの前記第2部分の前記延長された一端に配置された絶縁キャップ(*insulating caps*)をさらに含む。

【0012】

前記半導体メモリ素子は第2導電ラインと接続され、前記メモリストリングの第3側上に配置されたワードラインの第3グループをさらに含み、前記ワードラインの第1グループは前記メモリストリングの上部から下にカウンティング(*counting*)して、モジュロ(*modulus*)3で一番目の貯蔵セルと各々接続され、前記ワードラインの第2グループは前記メモリストリングの上部から下にカウンティングして、モジュロ(*modulus*)3で二番目の貯蔵セルと各々接続され、前記ワードラインの第3グループは前記メモリストリングの上部から下にカウンティングして、モジュロ(*modulus*)3で0番目の貯蔵セルと各々接続される。20

【0013】

前記複数の貯蔵セルの各々及び対応するワードラインは前記基板の平面に平行に配置された他の平面に配置される。メモリストリングの他の側上の同一の平面内に配置されたワードラインの連続する部分は1つのワードラインに電気的に接続される。前記基板は水平であり、前記メモリストリングは垂直であり、前記半導体メモリ素子は前記基板上に配置されるか、または前記垂直メモリストリング上に配置される周辺領域をさらに含む。30

【0014】

前記半導体メモリ素子は前記複数のワードラインの前記第1交互(*alternating*)ワードラインと第1導電ラインとの間、及び前記複数のワードラインの前記第2交互(*alternating*)ワードラインと前記第2導電ラインとの間にコンタクトパッドに配置された複数の導電パターンをさらに含む。前記半導体メモリ素子は前記平坦な基板上に配置された周辺領域をさらに含む。

【0015】

前記周辺領域は導電パターンの下部面と同一のレベルに配置されるか、または前記チャンバの上部上に配置される。前記ワードラインの前記交差する第2延長部は前記基板と50°乃至90°の角度を有する。前記交差する第2延長部は各ワードラインの前記第1部分の両端から延長され、各ワードラインから交差する第2部分の各対の1つは絶縁キャップ(*insulating cap*)で覆われる。40

【0016】

前記半導体メモリ素子は前記ワードライン及び前記メモリストリングの各々と垂直に(*perpendicular*)配置された複数のピットラインをさらに含む。前記平坦な基板上にチャンバ(*chamber*)をさらに含み、前記チャンバは前記基板内のシリコンリセスを含み、前記延長するメモリストリング及び延長するワードラインは前記シリコンリセス内に配置される。

【0017】

10

20

30

40

50

前記平坦な基板上にチャンバをさらに含み、前記チャンバは前記基板の上部面上の絶縁壁（insulating wall）を含み、前記延長するメモリストリング及び延長するワードラインは前記絶縁壁の周りに配置される。前記延長するワードラインは金属またはシリサイドを含む。前記複数の貯蔵セルを含む前記メモリストリングは柱（columnar）、管（tubular）、またはバーサイド（bar-sided）形である。

#### 【0018】

前記半導体メモリ素子は少なくとも2つのロウ（row）デコーダをさらに含み、1つのロウデコーダは奇数番目の貯蔵セルの側面に配置され、他のロウデコーダは偶数番目の貯蔵セルの側面に配置される。前記2つのロウデコーダの中の第1ロウデコーダは偶数または奇数ストリング選択ラインの中のいずれか1つと接続され、前記2つのロウデコーダの中の第2ロウデコーダは偶数または奇数ストリング選択ラインの中の他の1つと各々接続される。前記2つのロウデコーダの中で第1ロウデコーダはすべてのストリング選択ライン、及び偶数または奇数ワードラインの中のいずれか1つと接続され、前記2つのロウデコーダの中で第2ロウデコーダは奇数または偶数ワードラインの中の他の1つと各々接続される。

10

#### 【0019】

前記基板はシリコンを含み、前記絶縁膜はシリコン酸化膜を含み、前記ワードラインは金属を含む。前記貯蔵セルは制御ゲート、第1絶縁領域、電荷貯蔵領域、及び第2絶縁領域を含む。前記貯蔵セルは制御ゲートとして金属ゲート、プロッキング膜としてhigh-K領域、電荷貯蔵膜として窒化領域、及びトンネル膜として酸化領域を含む。

20

#### 【0020】

本発明の一実施形態によれば、半導体メモリ素子の製造方法は、基板を提供し、前記基板上にチャンバを形成し、絶縁膜及び犠牲膜を前記チャンバ内に交互に蒸着し、各膜は水平な第1部分、及び少なくとも1つの前記基板と交差する第2部分を含み、前記基板に垂直であり、前記膜を貫通して基板に延長するホールを形成し、前記ホール内に前記基板と垂直なメモリストリングを蒸着し、前記メモリストリングは複数の貯蔵セルを含み、犠牲膜を導電膜に各々取り替えて、複数の延長するワードラインを形成し、前記複数のワードラインの第1交互（alternating）ワードラインを前記メモリストリングの第1側の導電ラインと接続し、複数のワードラインの第2交互（alternating）ワードラインを前記メモリストリングの第2側の導電ラインと各々接続することを含む。

30

#### 【0021】

前記半導体メモリ素子の製造方法は前記メモリストリングの最上部レベルの表面上に周辺領域を形成することをさらに含む。前記垂直メモリストリングはバーサイド（bar-sided）形であり、前記半導体メモリ素子の製造方法はX-cutのためにトレンチを形成してメモリストリングを2つの平行なストリングに分けることをさらに含む。前記基板はシリコンを含み、前記絶縁膜はシリコン酸化膜を含み、前記ワードラインは金属を含む。前記チャンバは前記基板を直接リセスする。

#### 【0022】

前記チャンバは前記基板上に絶縁側壁を形成して前記基板上に形成される。各貯蔵セルは制御ゲート、第1絶縁領域、電荷貯蔵領域、及び絶縁領域を含む。各貯蔵セルは制御ゲートとして金属ゲート、プロッキング膜としてhigh-K領域、電荷貯蔵膜として窒化領域、及びトンネル膜として酸化領域を含む。

40

#### 【0023】

本発明の実施形態によると、半導体メモリ素子は、基板と、前記基板に垂直なメモリストリングと、前記メモリストリングは複数の貯蔵セルとを含み、複数のワードラインを含み、各ワードラインは前記基板に平行な前記メモリストリングに結合された第1部分、及び前記基板と交差し、上に延長する第2部分を含み、複数のワードラインの第1交互（alternating）ワードラインは前記メモリストリングの第1側の第1導電ラインと電気的に接続され、複数のワードラインの第2交互（alternating）ワード

50

ラインは前記メモリストリングの第2側の第2導電ラインと電気的に接続される。

**【0024】**

本発明の実施形態によれば、半導体メモリ素子は基板と、前記基板に垂直なメモリストリングと、前記メモリストリングは複数の貯蔵セルとを含み、複数のワードラインを含み、各ワードラインは前記基板に平行であり、前記メモリストリングに結合された第1部分、及び前記基板と交差し、上に延長する第2部分を含み、前記ワードラインは前記メモリストリングの第1側の第1導電ラインと選択的に接続された第1ワードライン及び前記メモリストリングの第2側の第2導電ラインと選択的に接続された第2導電ラインを含む。

**【0025】**

前記ワードラインは少なくとも1つのダミーワードラインを含む。前記第1側は第1口ウ(row)デコーダを有し、前記第2側は第2口ウデコーダを有する。

本発明の実施形態によれば、半導体メモリ素子は基板と、前記基板に垂直なメモリストリングと、前記メモリストリングは複数の貯蔵セルとを含み、複数のワードライン及び少なくとも2つのロウ(row)デコーダを含み、複数のワードラインは前記メモリストリングの第1側の1つのロウデコーダと電気的に接続されたワードラインの第1グループ、及び前記メモリストリングの第2側の他のロウデコーダと電気的に接続されたワードラインの第2グループを含む。前記第1口ウデコーダは前記メモリストリングの第1側のストリング選択ラインの一グループと接続され、前記第2口ウデコーダは前記メモリストリングの第2側のストリング選択ラインの他のグループと接続される。前記2つのロウデコードの中のいずれか1つは前記ストリング選択ラインの全体と接続される。

**【0026】**

本発明の実施形態によれば、半導体メモリ素子の製造方法は、基板を提供し、前記基板上にチャンバを形成し、前記チャンバ内に絶縁膜及び導電膜を交互に蒸着し、前記導電膜は複数のワードラインを形成し、各膜は水平な第1部分及び前記基板と交差する少なくとも1つの第2部分を含し、前記基板に垂直であり、前記膜を貫通して前記基板に延長するホールを形成し、前記ホール内に前記基板と垂直なメモリストリングを形成し、前記メモリストリングは複数の貯蔵セルを含み、前記複数のワードラインの第1交互(alternating)ワードラインと前記メモリストリングの一側のコンタクトパッドとを接続し、前記複数のワードラインの第2交互(alternating)ワードラインと前記メモリストリングの第2側のコンタクトパッドとを接続することを含む。

**【発明の効果】**

**【0027】**

本発明によれば、平坦な基板上に上下方向に重畠した面状のワードラインと、これを垂直に貫通する孔に設けたメモリストリングにより、ワードラインとメモリストリングの接続はセルフアラインに達成でき、ワードラインから外部導電ラインへのコンタクトの工程マージンは実質的に無制限になるので、十分余裕のある工程マージンを持つ高密度の3次元メモリ素子を提供できる。

本発明の実施形態によれば、少なくとも2つの活性バー(active bars)が電気的な接続の失敗なしに半導体基板上にユニホームに(uniformly)積層される。したがって、このような構造内に形成された複数セルの分散は改善することができる。言い替えれば、高集積化が最適化されて電気的特性が改善した不揮発性メモリ素子を実現することができる。

**【図面の簡単な説明】**

**【0028】**

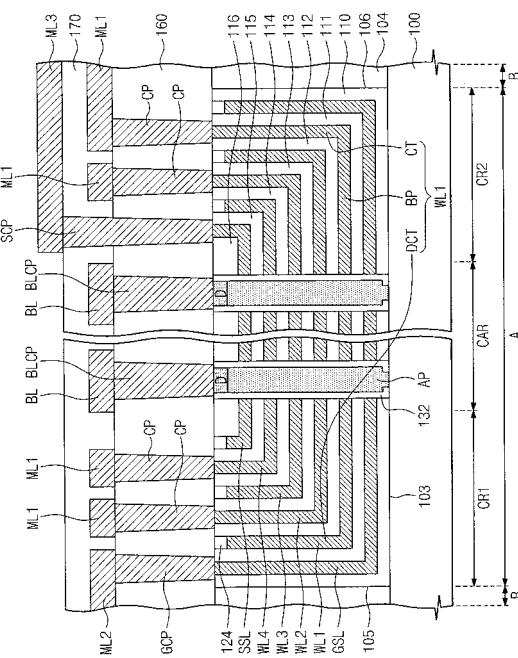

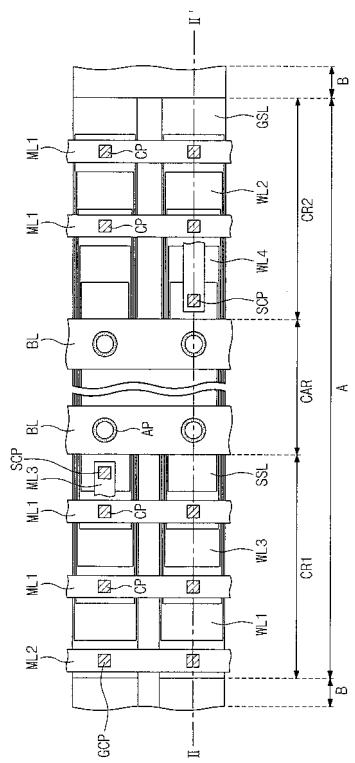

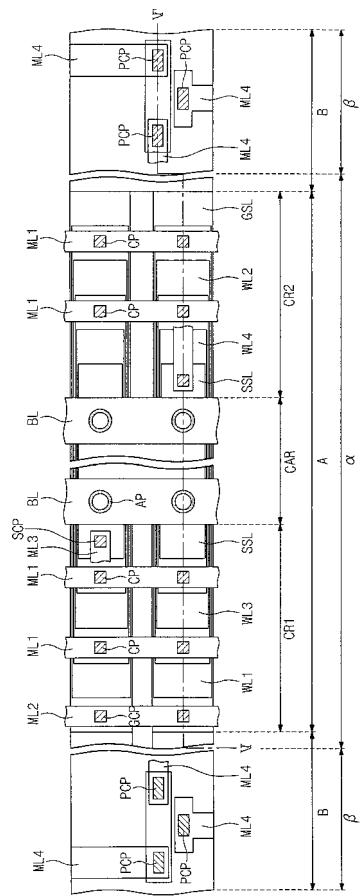

【図1】本発明の一実施形態に係る半導体素子を説明するための図式的な平面図である。

【図2】本発明の一実施形態に係る半導体素子を説明するための図式的な平面図である。

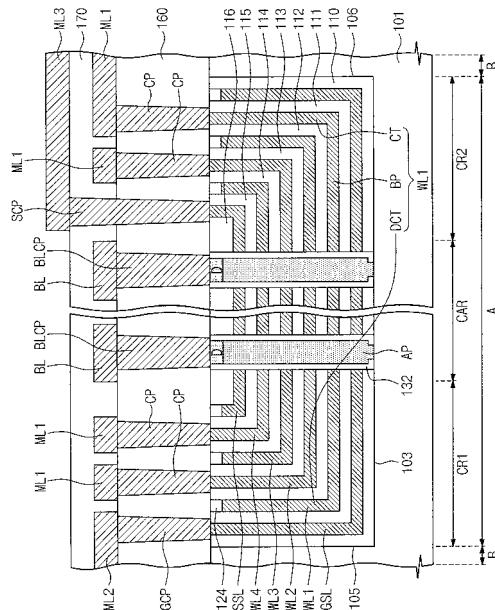

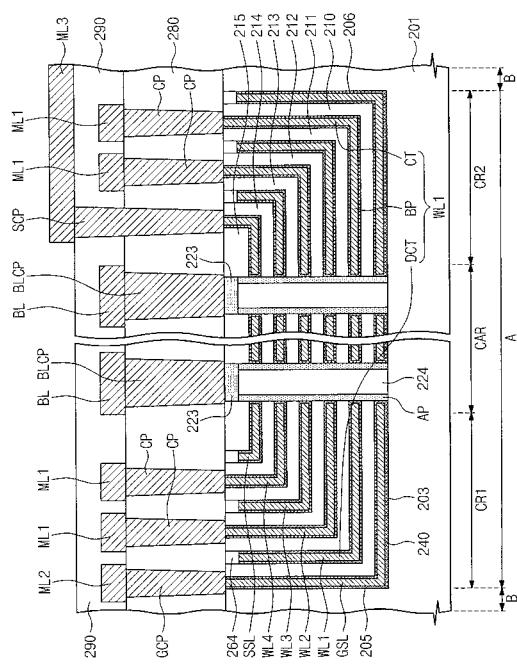

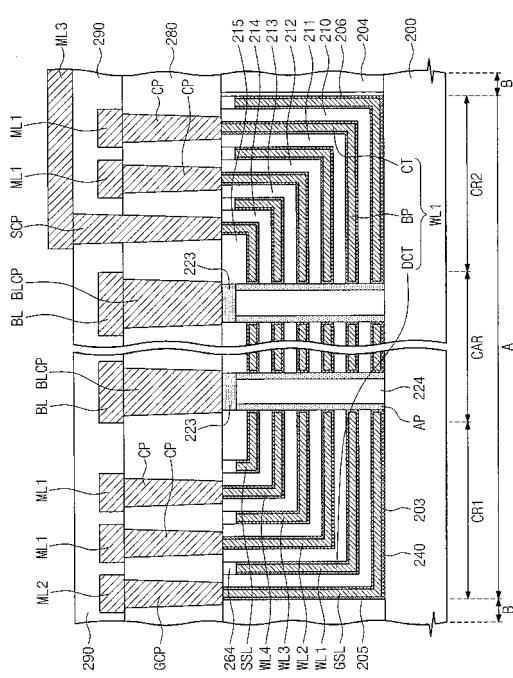

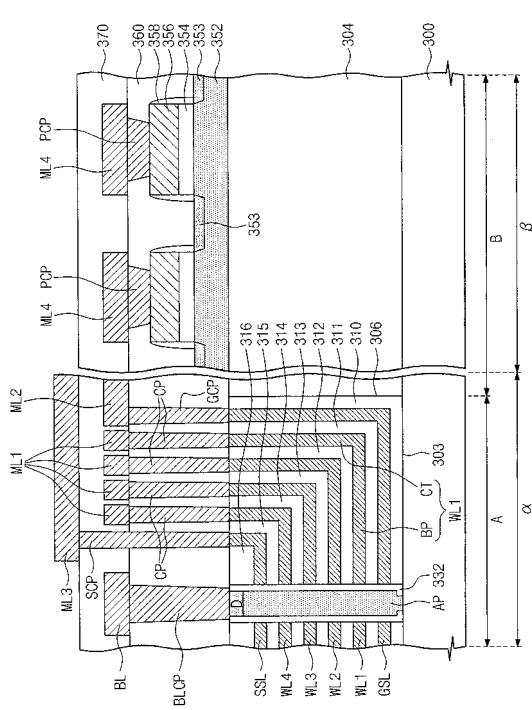

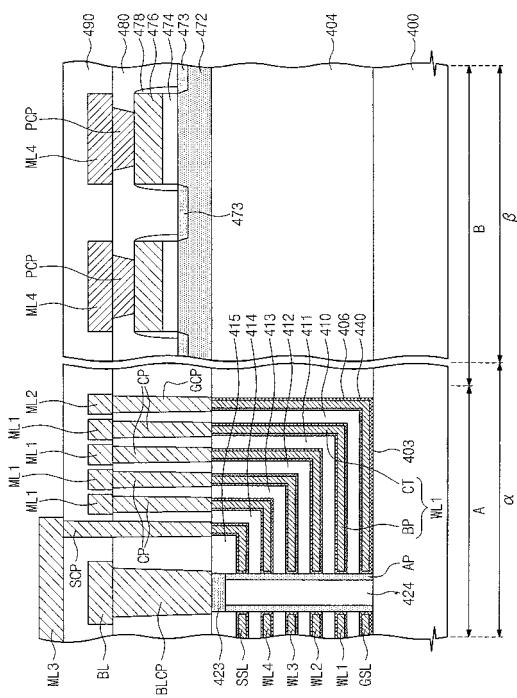

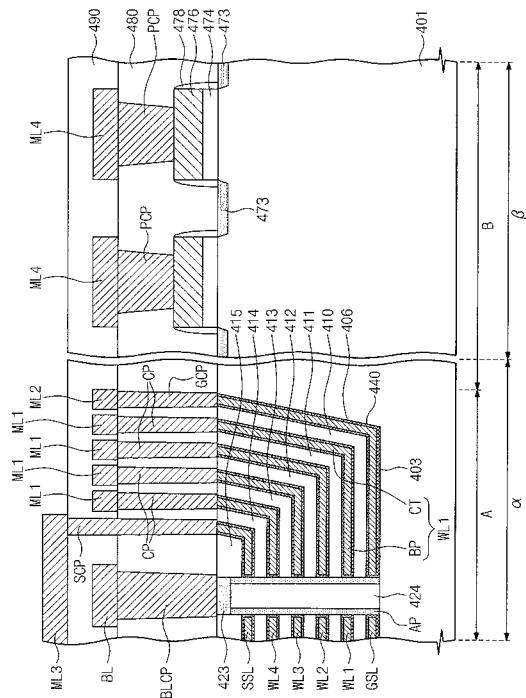

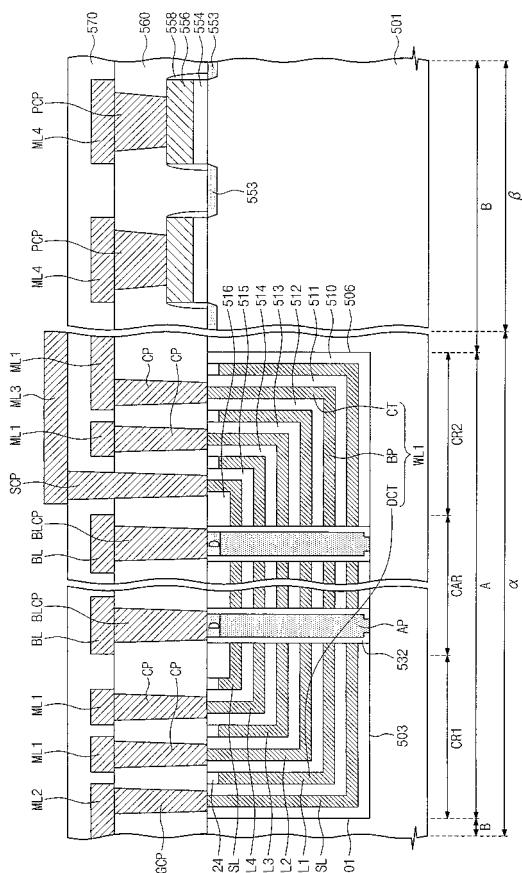

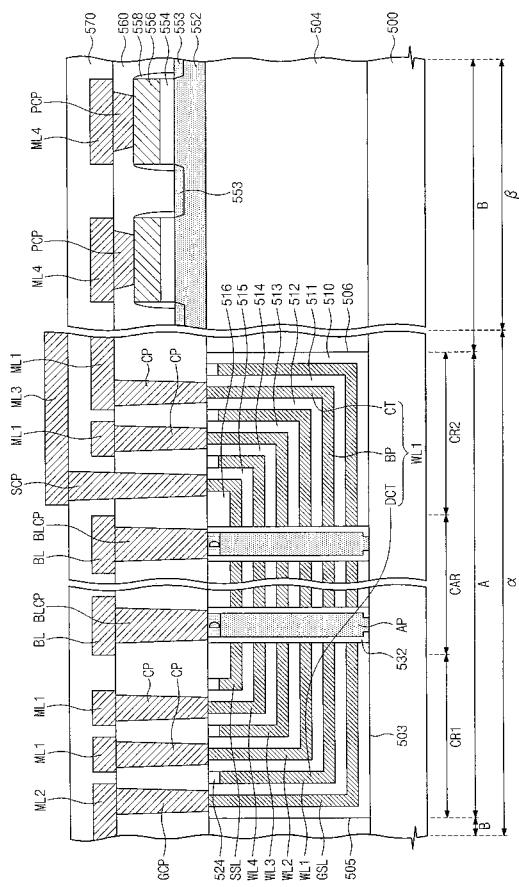

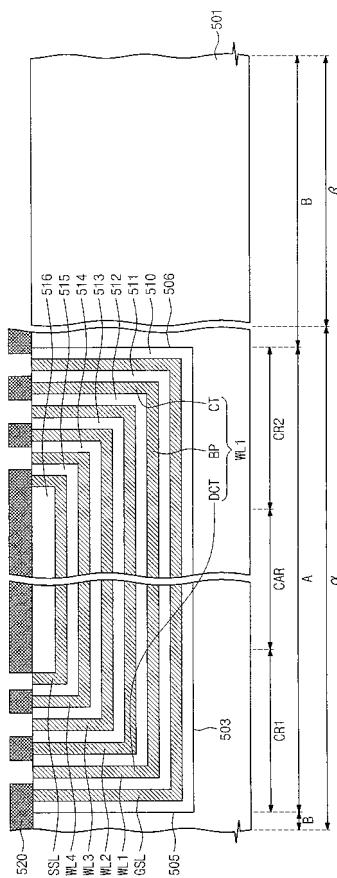

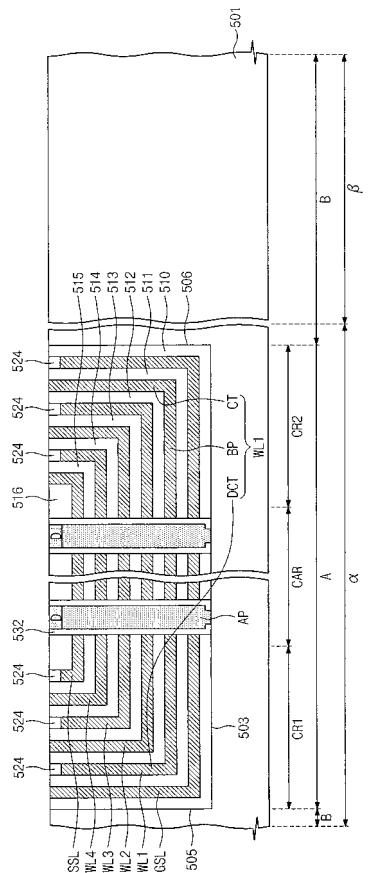

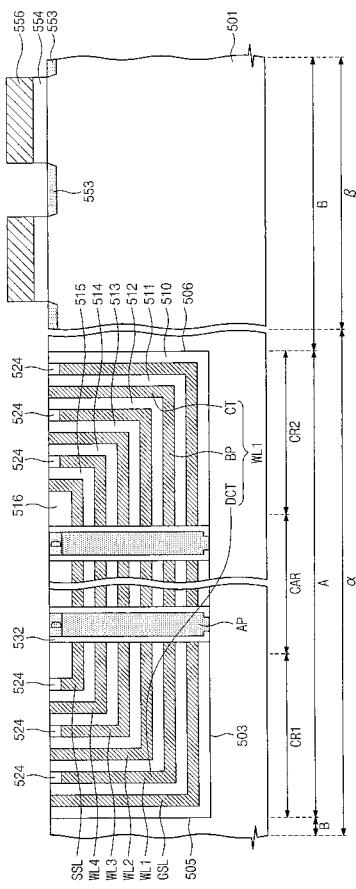

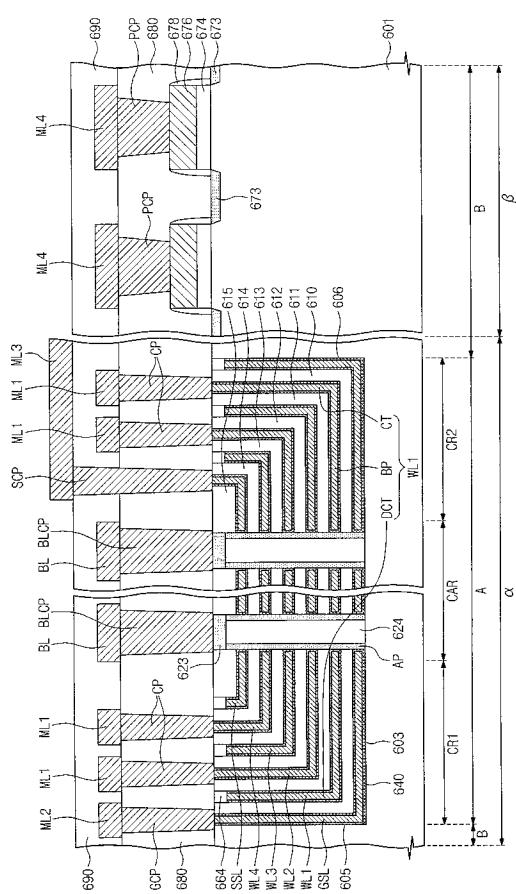

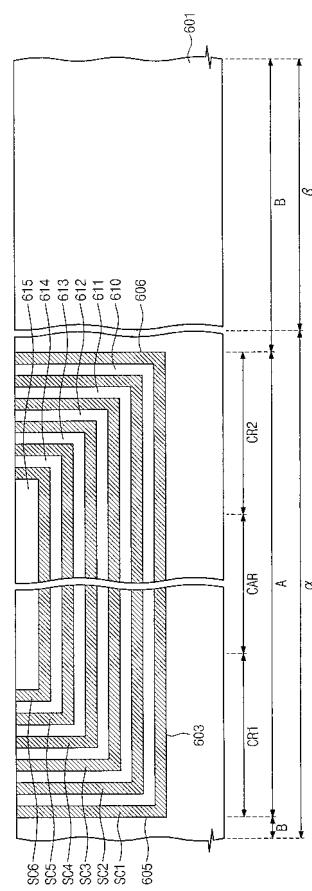

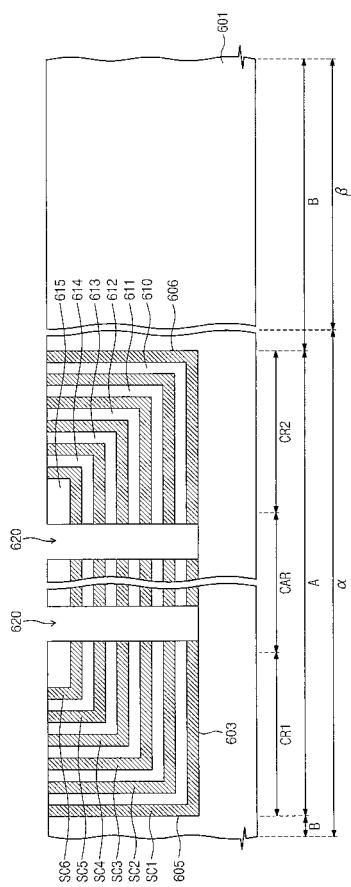

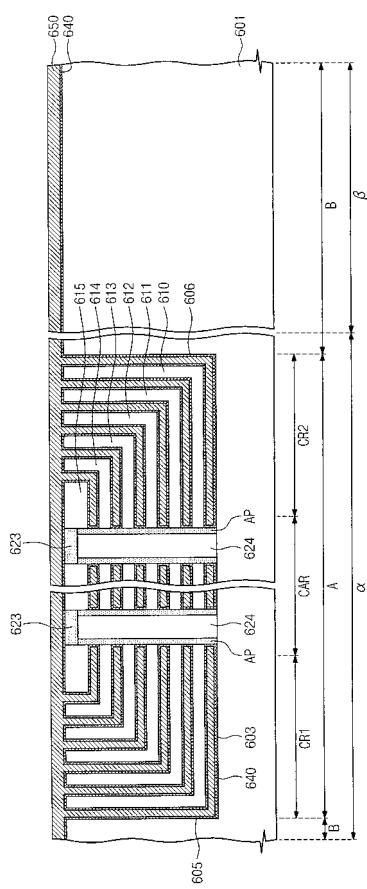

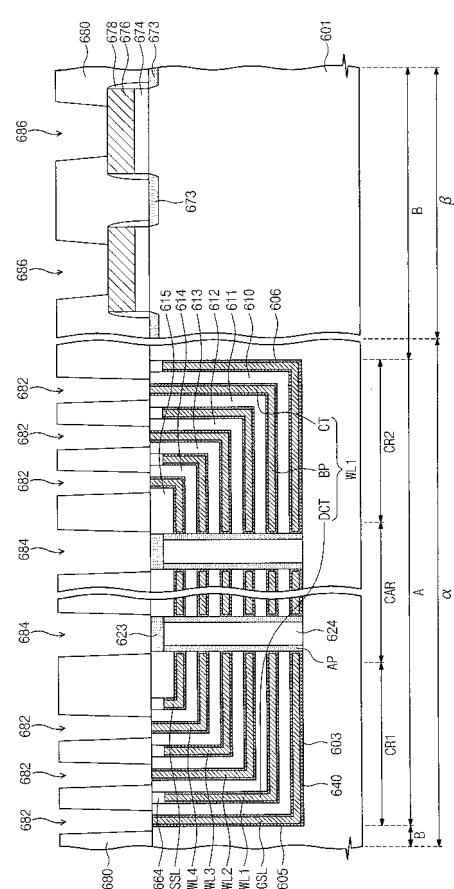

【図3】本発明の一実施形態によって図1及び図2のI-I'に沿って切断した図式的な断面図である。

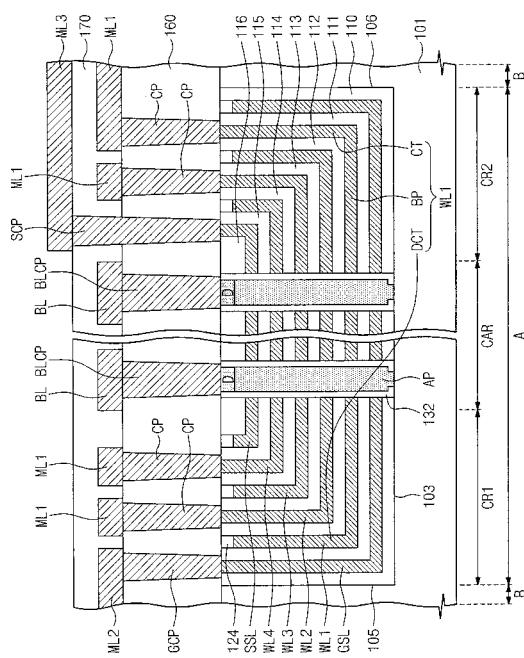

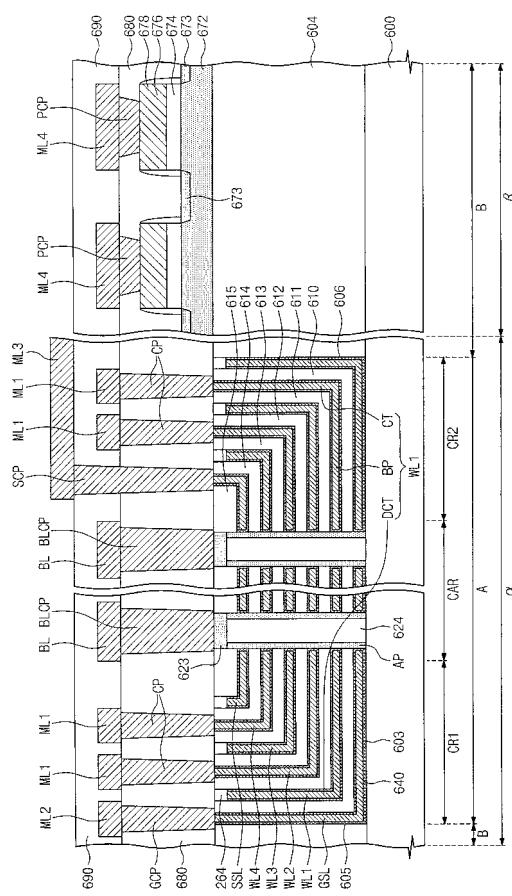

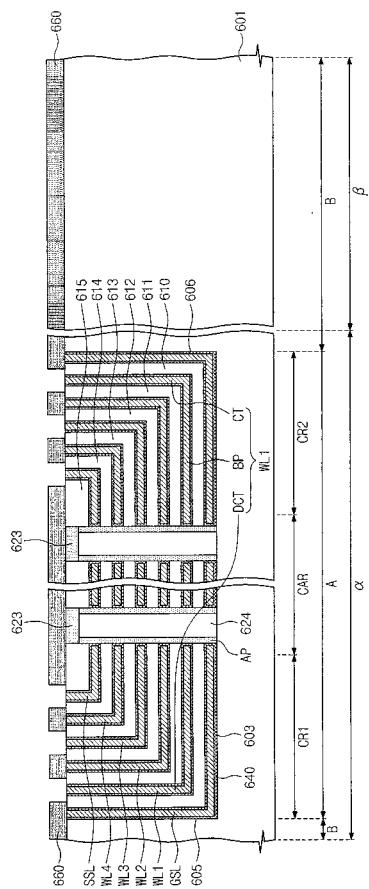

【図4】本発明の一実施形態によって図1及び図2のI-I'に沿って切断した図式的な断面図である。

10

20

30

40

50

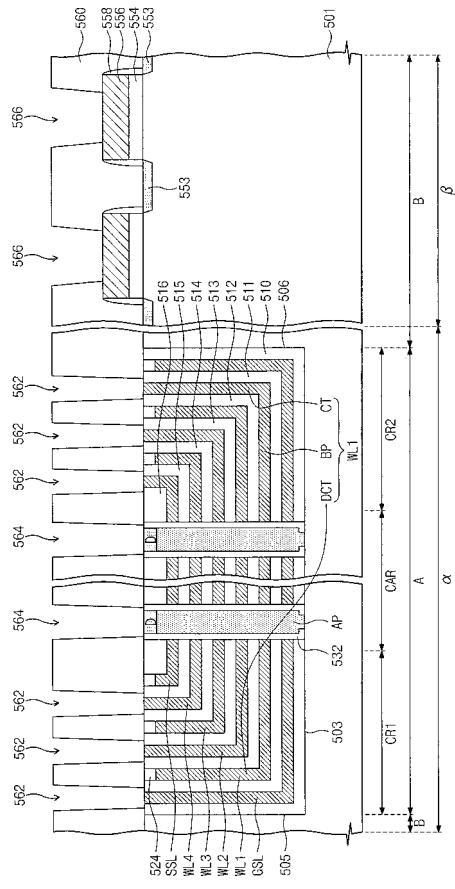

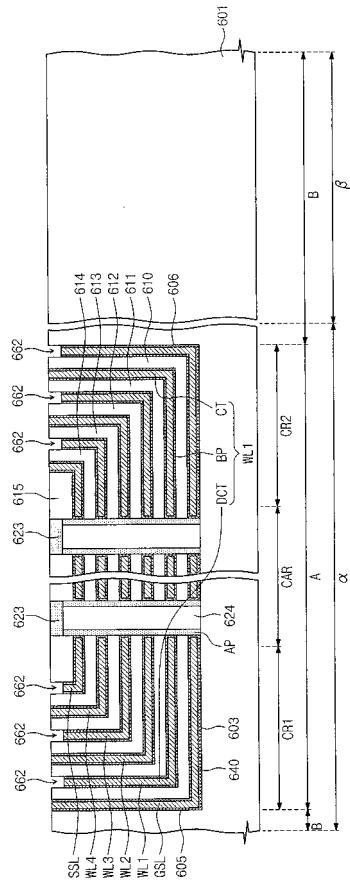

【図 5】本発明の一実施形態によって図 1 及び図 2 の I - I' に沿って切断した図式的な断面図である。

【図 6】本発明の一実施形態に係る情報貯蔵膜（例えば、電荷貯蔵膜）を説明するための図式図である。

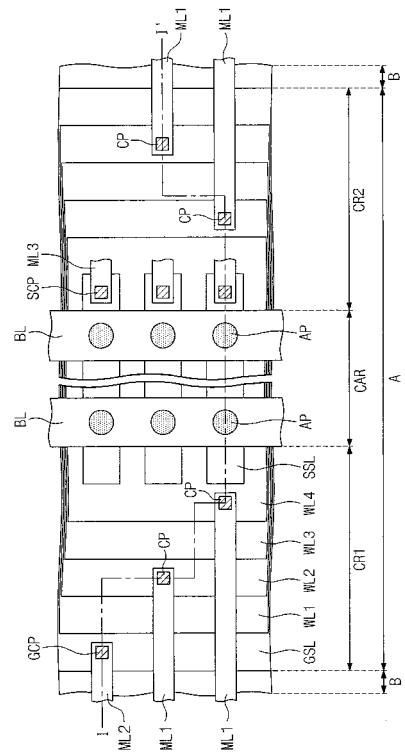

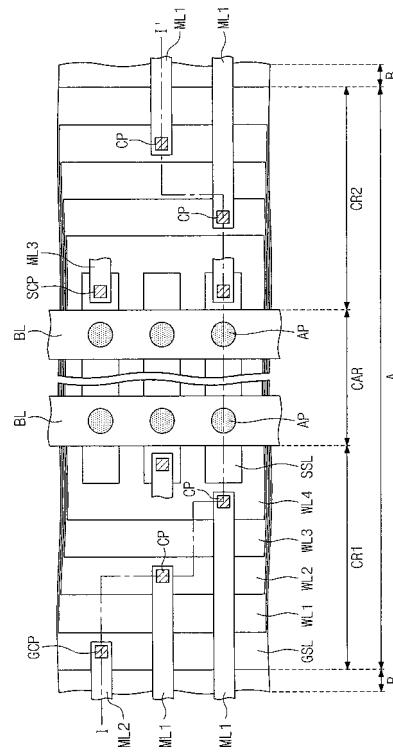

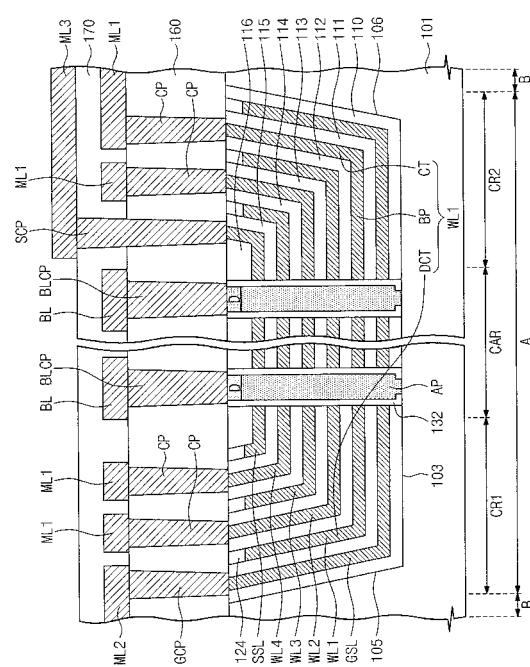

【図 7】本発明の他の実施形態に係る半導体素子を説明するための図式的な平面図である。

【図 8】本発明の他の実施形態に係る半導体素子を説明するための図式的な平面図である。

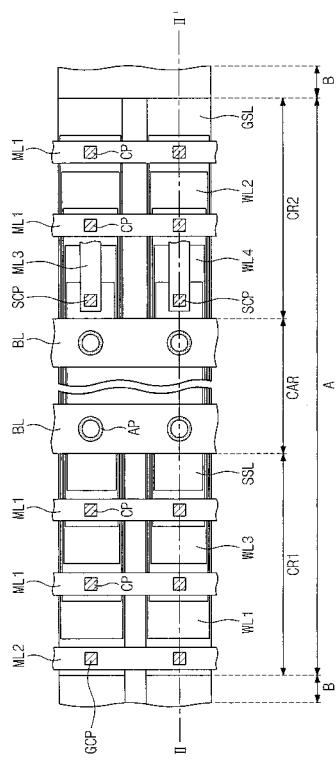

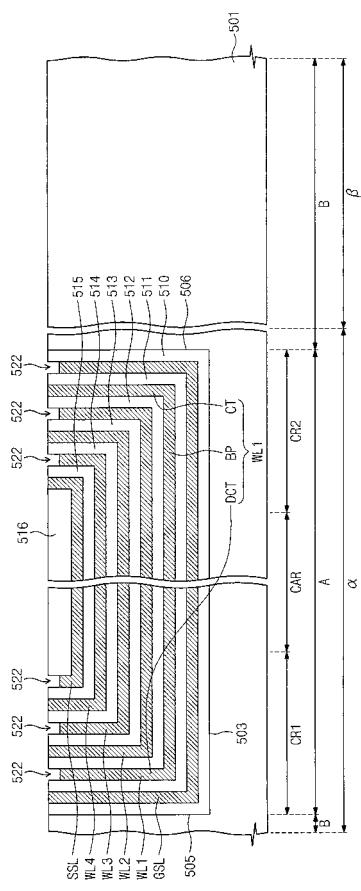

【図 9】本発明の一実施形態によって図 7 及び図 8 の II - II' に沿って切断した図式的な断面図である。

10

【図 10】本発明の一実施形態によって図 7 及び図 8 の II - II' に沿って切断した図式的な断面図である。

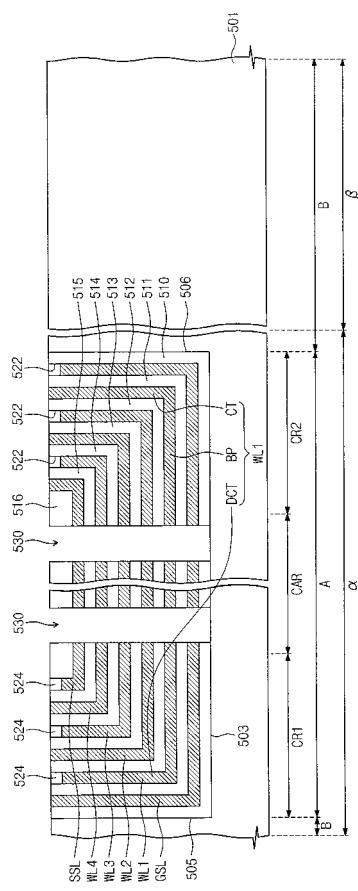

【図 11】本発明の一実施形態によって図 7 及び図 8 の II - II' に沿って切断した図式的な断面図である。

【図 12】本発明の一実施形態に係る情報貯蔵膜を説明するための図式図である。

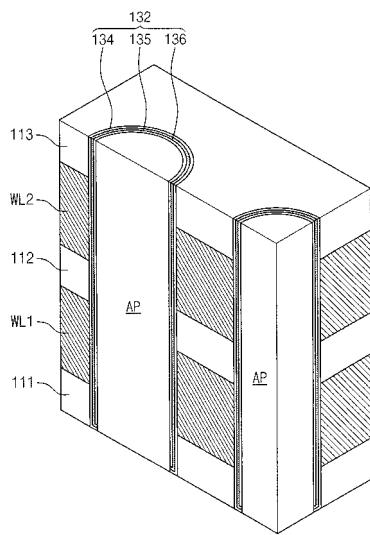

【図 13】本発明の一実施形態に係る活性部を部分的に示す図である。

【図 14】本発明の一実施形態に係る半導体素子を説明するための図式的な平面図である。

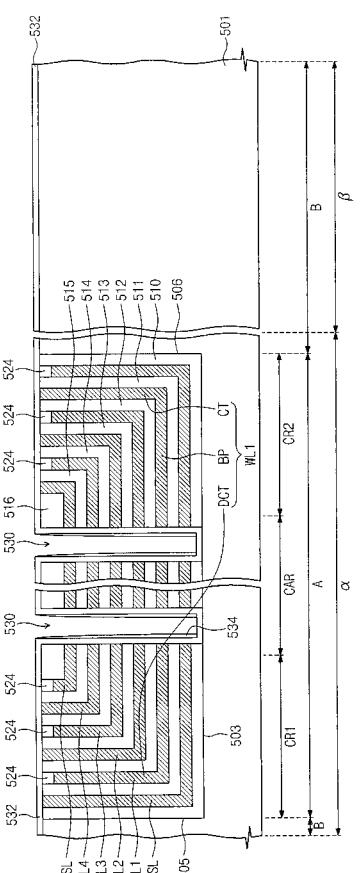

【図 15】本発明の一実施形態によって、図 14 の III - III' に沿って切断した図式的な断面図である。

20

【図 16】本発明の一実施形態によって、図 14 の III - III' に沿って切断した図式的な断面図である。

【図 17】本発明の一実施形態によって、図 14 の III - III' に沿って切断した図式的な断面図である。

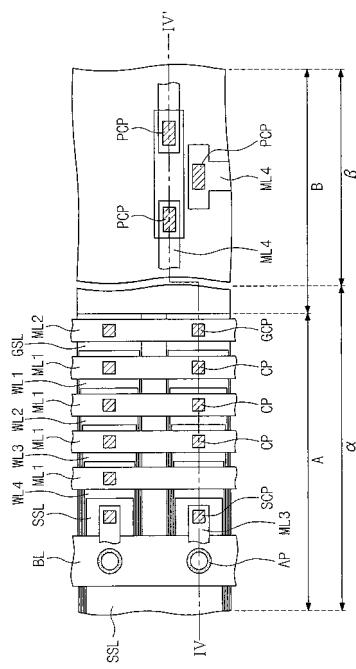

【図 18】本発明の一実施形態に係る半導体素子を説明するための図式的な平面図である。

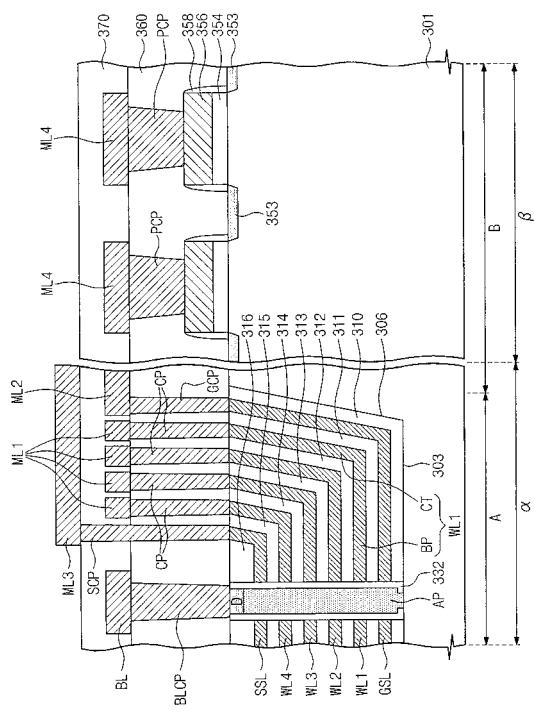

【図 19】本発明の一実施形態によって、図 18 の IV - IV' に沿って切断した図式的な断面図である。

【図 20】本発明の一実施形態によって、図 18 の IV - IV' に沿って切断した図式的な断面図である。

30

【図 21】本発明の一実施形態によって、図 18 の IV - IV' に沿って切断した図式的な断面図である。

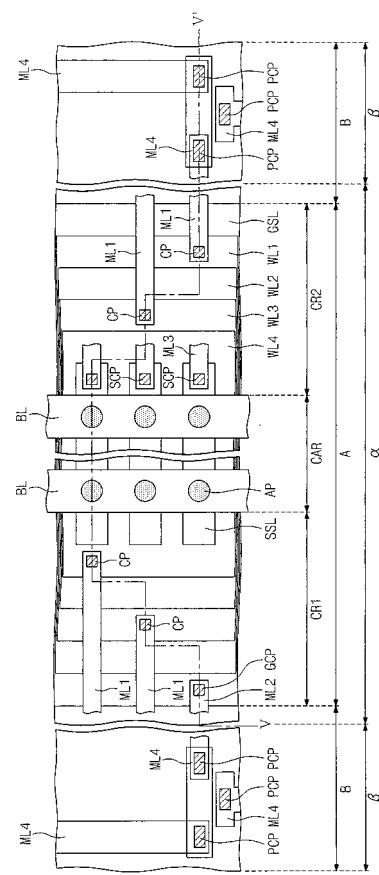

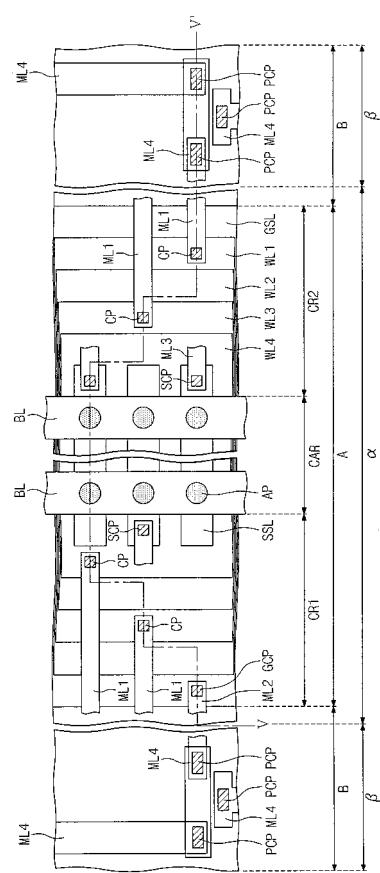

【図 22】本発明の一実施形態に係る半導体素子を説明するための図式的な平面図である。

【図 23】本発明の一実施形態に係る半導体素子を説明するための図式的な平面図である。

【図 24】本発明の一実施形態によって、図 22 及び図 23 の V - V' に沿って切断した図式的な断面図である。

【図 25】本発明の一実施形態によって、図 22 及び図 23 の V - V' に沿って切断した図式的な断面図である。

40

【図 26】本発明の一実施形態によって、図 22 及び図 23 の V - V' に沿って切断した図式的な断面図である。

【図 27】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

【図 28】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

【図 29】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

【図 30】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

50

【図31】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

【図32】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

【図33】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

【図34】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

【図35】本発明の一実施形態に係る半導体素子を説明するための図式的な平面図である。

【図36】本発明の一実施形態に係る半導体素子を説明するための図式的な平面図である。

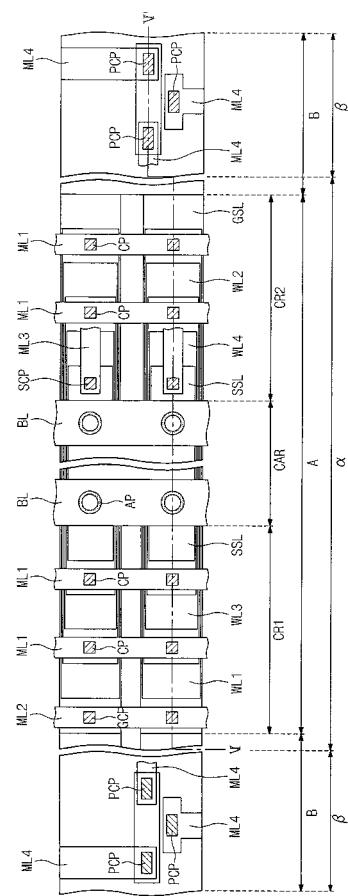

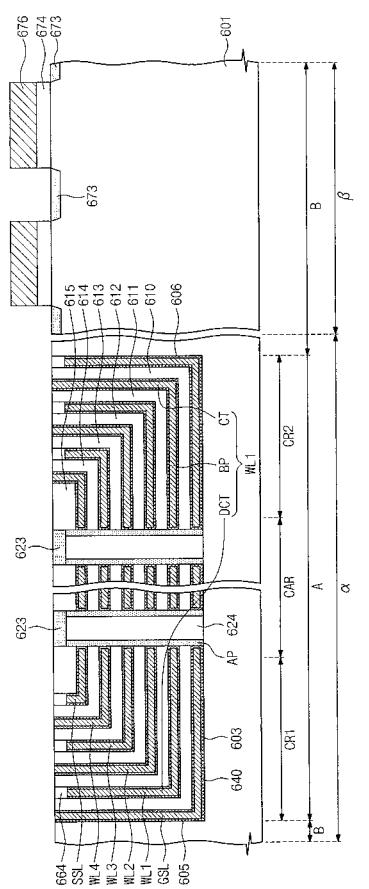

【図37】本発明の一実施形態によって、図35及び図36のV I - V I'に沿って切斷した図式的な断面図である。

【図38】本発明の一実施形態によって、図35及び図36のV I - V I'に沿って切斷した図式的な断面図である。

【図39】本発明の一実施形態によって、図35及び図36のV I - V I'に沿って切斷した図式的な断面図である。

【図40】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

【図41】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

【図42】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

【図43】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

【図44】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

【図45】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

【図46】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

【図47】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

【図48】本発明の一実施形態に係る半導体素子の形成方法を説明するための図式的な断面図である。

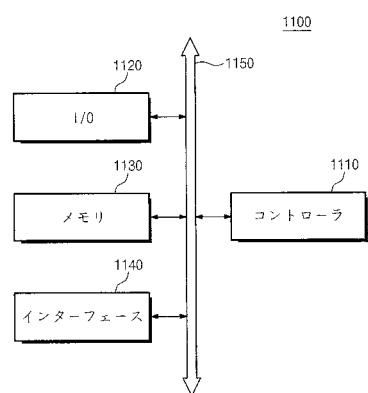

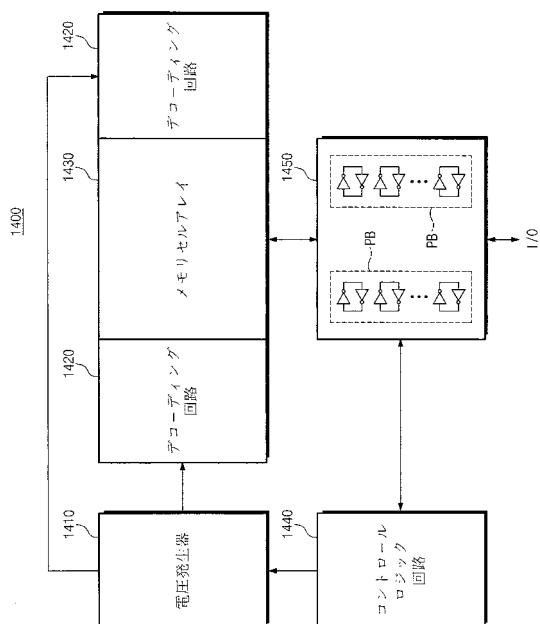

【図49】本発明の一実施形態に係る半導体素子を含むメモリシステムのブロック図である。

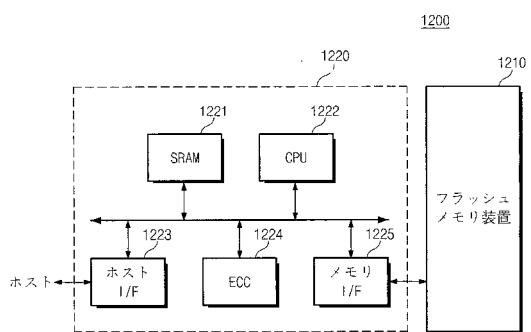

【図50】本発明の一実施形態に係る半導体素子を含むメモリカードのブロック図である。

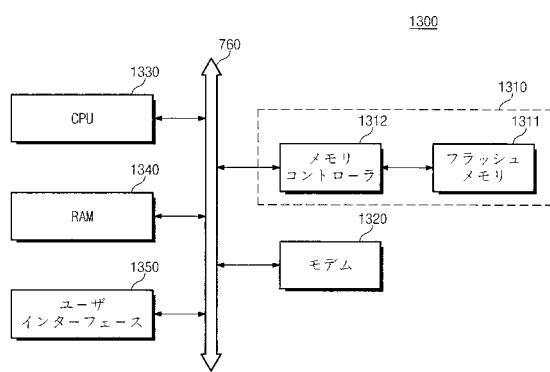

【図51】本発明の一実施形態に係る半導体素子が装着された情報処理システムのブロック図である。

【図52】本発明の一実施形態に係る半導体素子を含む不揮発性メモリ素子のブロック図である。

#### 【発明を実施するための形態】

##### 【0029】

本発明の実施形態は分散したコンタクトパッドを有する改善した3次元構造の半導体メモリ構造を提供する。望ましい実施形態は高信頼性を確保することができる改善したコンタクト面積のマージンを提供する。また、本発明はワードラインまたはワードラインとメモリストリング（以下、単に「ストリング」ともいう）選択ラインとの間の接続、及び少

10

20

30

40

50

なくとも 2 つのロウデコーダのレイアウトを提供する。

### 【 0 0 3 0 】

以下、添付の図を参照して本発明の望ましい実施形態をさらに詳細に説明する。しかしながら、本発明はここで説明する実施形態に限定されず、他の形態への具体化も可能である。さらにここで紹介する実施形態は開示された内容が徹底且つ完全になれるよう、そして当業者に本発明の思想を十分に伝達するために提供される。また、望ましい実施形態によることから、説明の手順によって提示される参照符号はその手順に必ず限定されない。図において、膜及び領域の厚さは明確性のために誇張されている。また、膜が他の膜または基板上にあると言及される場合に、それは他の膜または基板上に直接形成され、またはそれらの間に第 3 の膜を介在することができる。本明細書において、「及び／または」という表現は前後に羅列された構成要素のうちの少なくとも 1 つを含む意味として用いられる。10

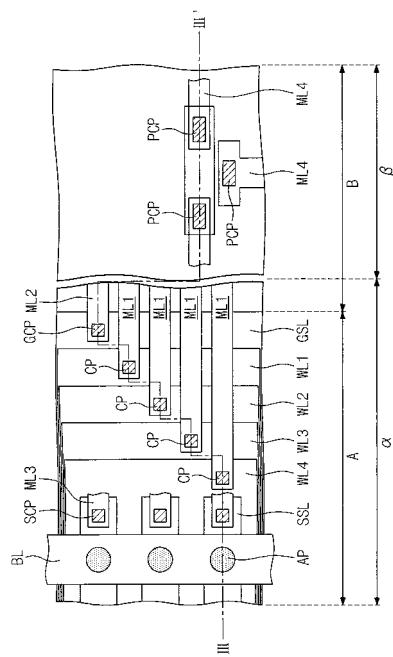

### 【 0 0 3 1 】

本発明の第 1 実施形態に係る半導体素子を説明する。図 1 及び図 2 は、本発明の実施形態に係る平面図を示し、図 3 は、図 1 及び図 2 の I - I' に沿って切断した断面図である。10

### 【 0 0 3 2 】

本発明に係る半導体素子はメモリセルアレイ領域、ロウ (row) デコーダ、コラム (column) デコーダ、メモリセルアレイと半導体素子の外部の素子とを接続する配線（例えば、電圧発生器）、及びコントロールユニットを含む。配線は、他の層、パターンまたはラインに垂直に延長する導電ビア (via)、プラグ、またはパッドと接続される。20

### 【 0 0 3 3 】

本発明に係る半導体メモリ素子のメモリセルアレイは、3 次元構造の複数のメモリセルを含む。本発明の一実施形態によれば、前記メモリセルアレイは、平坦な基板上で垂直に形成され、各々複数個のメモリセルを含む複数個のメモリストリングのアレイからなる。前記メモリストリングは各々、制御ゲート、第 1 絶縁膜、電荷貯蔵膜、第 2 絶縁膜、及び、チャンネルが形成される活性部を含む。電荷貯蔵膜は絶縁膜またはナノドット (nanodots) などのように電荷が貯蔵される膜を含む。電荷貯蔵のための前記絶縁膜はシリコン窒化膜、または酸素より窒素が十分に多いシリコン酸窒化膜を含む。第 1 絶縁膜は活性部と電荷貯蔵膜との間に位置する。前記第 1 絶縁膜はシリコン酸化膜、またはシリコン酸化膜、シリコン酸窒化膜、及びシリコン窒化膜の中のいずれを含む薄い（約 50 ~ 150 nm）複層膜を含む。前記第 2 絶縁膜は前記電荷貯蔵膜と前記制御ゲートとの間に位置する。前記第 2 絶縁膜はシリコン酸化膜、high-K 物質、アルミニウム酸化膜及びまたはこれらの組み合わせであり得る。30

### 【 0 0 3 4 】

活性部の形状は多様なタイプであり得る。例えば、柱 (pillar)、円周 (circular)、管 (tubular) またはバーサイド (bar-sided) 形状であり得る。前記管活性部は内部の絶縁性物質を取り囲んでいる。

### 【 0 0 3 5 】

図 1、図 2、及び図 3 を参照すると、基板 101 が提供される。前記基板 101 は半導体ベースの半導体基板であり、実質的に平坦である。前記基板はシリコン、好ましくは、単結晶シリコンを含む。前記基板 101 は第 1 導電型のドーパントでドーピングされたウェル (well) のようなドーピング領域を含む。前記基板 101 内に共通ソース領域（図示しない）が配置される。前記複数個のメモリストリングは 1 つのソース領域を、共通ソースラインとして共有する。前記共通ソース領域は前記基板 101 の、メモリセルが形成される領域（後述の凹部 A）内に平板形態 (plateform) に配置される。前記共通ソース領域は高濃度のドーパントを含むことができる。前記共通ソース領域に含まれたドーパントは前記ウェルに含まれたドーパントと異なる導電型の第 2 導電型であり得る。例えば、前記ウェルが p 型ドーパントを含む場合、前記共通ソース領域は高濃度の n 型ドーパントを含む。4050

## 【0036】

図4を参照すると、前記基板100は平坦である。突出部104が基板100上に形成される。前記突出部104は基板100上に蒸着される。突出部104の物質はシリコンまたは絶縁膜であり得る。その結果として生じた表面は平坦な基板100における、凹部A及び、突出部104による隆起部Bを含む。前記凹部Aは底面103と、互いに対向する第1側壁105及び第2側壁106を含む。これによる基板101は前記第1側壁105及び第2側壁106から延長された隆起部Bを含む。前記隆起部Bの上部面は前記凹部Aの前記底面103と平行であり得る。

これと異なり、再び図3を参照すると、前記凹部A及び前記隆起部Bは、半導体基板101の凹部Aが配置される部分をエッチングして、隆起部Bが配置される部分を残して形成される。この場合、前記基板101は一体の基板であり得る。前記凹部Aにメモリセルが配置される。もし、突出部が絶縁膜で形成され、周辺回路が突出部上に形成される場合、シリコン膜が突出部上にさらに形成される(Silicon on Insulator type、SOI)。

以下、この凹部Aと隆起部Bが形成された基板100、101を、基板101で代表する。

## 【0037】

前記半導体メモリ素子を説明する。

## 【0038】

前記凹部Aは前記第1側壁105と隣接した第1コンタクト領域CR1及び前記第2側壁106と隣接した第2コンタクト領域CR2を含む。前記第1コンタクト領域CR1と前記第2コンタクト領域CR2との間にセルアレイ領域CARが配置される。前記第1コンタクト領域CR1及び第2コンタクト領域CR2は、前記セルアレイ領域CARを挟んで互いに離隔されている。

前記メモリストリングのアレイは、このセルアレイ領域CARに形成される。

## 【0039】

前記基板101上に互いに離隔された導電パターンGSL、WL1～WL4、SSLが配置される。前記導電パターンGSL、WL1～WL4、SSLは前記基板101の前記凹部A上に順に積層された接地選択ラインGSL、ワードラインWL1～WL4、及びストリング選択ラインSSLを含む。

## 【0040】

そして、隣接した導電体の間の所望しないショート(short)を防止するため、層間絶縁膜が隣接したワードラインの間に配置される。本発明に係る前記メモリ素子は、接地選択ラインGSL及び／またはストリング選択ラインSSLの近傍の、またはワードラインの間のダミーワードラインを含む。前記ワードラインWL、接地選択ラインGSL及びストリング選択ラインSSLは導電膜と層間絶縁膜が積層されて形成される。他の実施形態によれば、積層されたワードラインWL、接地選択ラインGSL及びストリング選択ラインSSL、と層間絶縁膜の積層は複数回に分けて実行される。

## 【0041】

前記メモリセルアレイは平坦な基板上に配置された情報貯蔵が可能な複数のメモリセルの3次元構造であり得る。メモリセルの活性化のためのスイッチング素子はトランジスタまたはダイオードタイプであり得る。メモリセルのタイプは揮発性または不揮発性タイプであり得る。例えば、本発明に係るメモリ素子はフラッシュメモリ素子である。

## 【0042】

3次元メモリ素子の活性部は平坦な基板101と垂直または平行である。望ましくは、前記活性部は基板上の垂直活性部である。前記活性部はシリコンで形成される。前記活性部は柱(pillar)、管(tubular)またはバーサイド(bar-sided)タイプであり得る。前記活性部は単結晶シリコンまたは多結晶シリコンで形成される。前記活性部は非晶質シリコンで形成され、多結晶シリコンに結晶化される。

## 【0043】

10

20

30

40

50

制御ゲート、第1絶縁膜、電荷貯蔵膜、第2絶縁膜及び活性部を含むメモリストリントは平坦な( planar)基板に対して垂直に形成される。電荷貯蔵のための前記絶縁膜はシリコン窒化膜、または酸素より窒素が十分に多いシリコン酸窒化膜を含むことができる。第1絶縁膜は活性部と電荷貯蔵膜との間に位置する。前記第1絶縁膜はシリコン酸化膜、またはシリコン酸化膜、シリコン酸窒化膜、及びシリコン窒化膜の中のいずれを含む薄い(約50~150)複層膜を含むことができる。前記第2絶縁膜は前記電荷貯蔵膜と前記制御ゲートとの間に位置する。前記第2絶縁膜はシリコン酸化膜、high-K物質、アルミニウム酸化膜及びまたはこれらの組み合わせであり得る。

## 【0044】

一方、前記導電パターンGSL、WL1~WL4、SSLは、ゲート間絶縁膜111~115を挟んで互いに離隔されて配置される。例えば、前記接地選択ラインGSL、第1ゲート間絶縁膜111、第1ワードラインWL1、第2ゲート間絶縁膜112、第2ワードラインWL2、第3ゲート間絶縁膜113、第3ワードラインWL3、第4ゲート間絶縁膜114、第4ワードラインWL4、第5ゲート間絶縁膜115、及びストリング選択ラインSSLが順に積層されている。

## 【0045】

前記凹部Aの前記底面103、第1及び第2側壁105、106と前記接地選択ラインGSLとの間に接地選択絶縁膜110が配置される。前記ストリング選択ラインSSL上にストリング選択絶縁膜116が配置される。前記絶縁膜110~116は合わせて前記層間絶縁膜を形成し、各々、前記凹部Aの前記底面103上にあって前記底面103に平行に配置された底部と、前記底部から前記第1側壁105及び前記第2側壁106に沿って延長される側壁部を含む。

## 【0046】

前記導電パターンGSL、WL1~WL4、SSLは前記凹部Aの前記底面103上に配置された底部BPを含む。前記底部BPは前記底面103と平行である。

前記メモリストリントは、前記セルアレイ領域において、前記導電パターンGSL、WL1~WL4、SSLと前記層間絶縁膜とを貫通して形成され、これらの導電パターン及び層間絶縁膜の貫通孔壁は、前記メモリストリントの第2絶縁膜と接触する。

前記メモリセルの活性部は、前記メモリストリントのうち、前記ワードラインWL1~WL4との貫通孔壁に対応する部分からなる。

## 【0047】

前記導電パターンGSL、WL1~WL4、SSLは上側延長部(上方傾斜部)を含む。前記上側延長部はコンタクト延長部CTを含む。前記コンタクト延長部CTは前記底部BPの一端から前記第1側壁105または前記第2側壁106の中の1つの側壁上に延長する。前記導電パターンGSL、WL1~WL4、SSLの中のいずれか1つの導電パターンのコンタクト延長部が配置されるコンタクト領域と、前記いずれか1つの導電パターンと隣接した導電パターンのコンタクト延長部が配置されるコンタクト領域は異なることができる。例えば、前記接地選択ラインGSLのコンタクト延長部CTが前記第1コンタクト領域CR1に配置される場合、前記接地選択ゲート膜GSLと隣接した第1ワードラインWL1のコンタクト延長部CTは前記第2コンタクト領域CR2に配置される。

## 【0048】

前記コンタクト延長部CTは前記底面103に対して傾斜する。例えば、前記コンタクト延長部CTは前記底面103に対して直角に傾斜することができる。本発明の一実施形態において、前記コンタクト延長部CTの上部面は前記隆起部Bの上部面と同一平面にある(planar)。前記コンタクト延長部CTが前記底部BPとなす角度は50°~90°であり得る。

## 【0049】

前記導電パターンGSL、WL1~WL4、SSLは前記底面103上の前記底部BPの他端から前記第1側面105及び前記第2側面106の中の他の1つの側面上に延長された(extended over)ダミー延長部DCTを含む。前記導電パターンGS

10

20

30

40

50

L、WL1～WL4、SSLの中のいずれか1つの導電パターンのダミー延長部が配置されるコンタクト領域と、前記いずれか1つの導電パターンと隣接した他の導電パターンのダミー延長部が配置されるコンタクト領域は異なることができる。例えば、前記ストリング選択ラインSSLのダミー延長部DCTが前記第1コンタクト領域CR1に配置される場合、前記ストリング選択ラインSSLと隣接した前記第4ワードラインWL4のダミー延長部DCTは前記第2コンタクト領域CR2に配置される。

#### 【0050】

前記導電パターンGSL、WL1～WL4、SSLの各々は1つのコンタクト延長部CTと1つのダミー延長部DCTとを含む。前記導電パターンGSL、WL1～WL4、SSLの中の1つの導電パターンにおいて、前記ダミー延長部DCTの長さは前記コンタクト延長部CTの長さより短いことがある。前記コンタクト延長部CTは互いに隣接したダミー延長部DCTの間に配置される。ダミー延長部DCTと隣接したコンタクト延長部CTはその間に介在された絶縁膜の側壁部によって離隔される。言い換えれば、ワードラインの一部はメモリストリングの第1側(図1、図2で左側、即ち、前記第1コンタクト領域CR1にある)導電ラインと接続でき(後述)、ワードラインの残りはメモリストリングの第2側(図1、図2で右側、即ち、前記第2コンタクト領域CR2にある)導電ラインと接続できる(後述)ので、接続コンタクトマージンを改善することができる。10

#### 【0051】

前記ダミー延長部DCT上にダミー絶縁パターン124が配置される。前記ダミー絶縁パターン124の上部面は前記隆起部Bの上部面と同一平面にある。前記ダミー絶縁パターン124の上部面は前記ストリング選択絶縁膜116の上部面と同一平面にある。前記ダミー絶縁パターン124の側壁は前記ダミー延長部DCTの側壁と同一平面にある。前記ダミー絶縁パターン124は前記絶縁膜110～116と同一の物質を含むことができる20ことができる。

#### 【0052】

前記ワードラインWL1～WL4のコンタクト延長部CT上に導電プラグが各々配置される。前記導電プラグはワードラインコンタクトプラグCPであり得る。前記ワードラインWL1～WL4の各々は前記ワードラインコンタクトプラグCPと電気的に接続される。前記ワードラインコンタクトプラグCPの幅は前記ワードラインWL1～WL4のコンタクト延長部CTの上部面の幅より広いことがある。前記ワードラインコンタクトプラグCPは前記ワードラインWL1～WL4のコンタクト延長部CTと隣接したダミー延長部DCTの間の幅より広いことがある。前記ワードラインコンタクトプラグCPは第1層間絶縁膜160を貫通する。前記ワードラインコンタクトプラグCP及び前記第1層間絶縁膜160上に第1導電ラインML1が配置される。前記ワードラインコンタクトプラグCPは前記第1導電ラインML1と電気的に接続される。前記第1導電ラインML1の一部は第1方向(図1、図2で左方向)に延長される。前記第1導電ラインML1の残りの一部は前記第1方向の反対になる第2方向(図1、図2で右方向)に延長される。例えば、前記基板101から奇数層に配置されたワードラインWL2、WL4と接続された第1導電ラインML1は前記第1方向に延長され、前記基板101から偶数層に配置されたワードラインWL1、WL3と接続された第1導電ラインML1は前記第2方向に延長される。前記第1導電ラインML1は前記ワードラインコンタクトプラグCPを通じて前記ワードラインWL1～WL4と電気的に接続される。これと異なり、前記ワードラインWL1～WL4と前記導電ラインML1は直接接続され得る。前記第1導電ラインML1を覆う第2層間絶縁膜170が配置される。前記第1層間絶縁膜160及び前記第2層間絶縁膜170は同一の物質を含むことができる。3040

#### 【0053】

前記接地選択ラインGSLのコンタクト延長部CT上に導電プラグが配置される。前記導電プラグは接地選択コンタクトプラグGCPであり得る。前記接地選択ラインGSLは前記接地選択コンタクトプラグGCPと電気的に接続される。前記接地選択コンタクトプラグGCPの幅は前記接地選択ラインGSLのコンタクト延長部CTの上部面の幅より広50

いことがある。前記接地選択コンタクトプラグ G C P は第 1 層間絶縁膜 1 6 0 を貫通する。前記接地選択コンタクトプラグ G C P 及び前記第 1 層間絶縁膜 1 6 0 上に第 2 導電ライン M L 2 が配置される。前記接地選択コンタクトプラグ G C P は前記第 2 導電ライン M L 2 と電気的に接続される。前記第 2 導電ライン M L 2 は前記第 1 方向に延長される。前記第 2 導電ライン M L 2 は前記接地選択コンタクトプラグ G C P を通じて前記接地選択ライン G S L と電気的に接続される。これと異なり、前記接地選択ライン G S L と前記第 2 導電ライン M L 2 は直接接続され得る。前記第 2 層間絶縁膜 1 7 0 は前記第 2 導電ライン M L 2 を覆う。

#### 【 0 0 5 4 】

前記ストリング選択ライン S S L のコンタクト延長部 C T 上に導電プラグが配置される。前記導電プラグはストリング選択コンタクトプラグ S C P であり得る。前記ストリング選択ライン S S L は前記ストリング選択コンタクトプラグ S C P と電気的に接続される。前記ストリング選択コンタクトプラグ S C P の幅は前記ストリング選択ライン S S L のコンタクト延長部 C T の上部面の幅より広いことがある。前記ストリング選択コンタクトプラグ S C P は第 1 層間絶縁膜 1 6 0 を貫通する。前記ストリング選択コンタクトプラグ S C P 及び前記第 1 層間絶縁膜 1 6 0 上に第 3 導電ライン M L 3 が配置される。前記ストリング選択コンタクトプラグ S S L は前記第 3 導電ライン M L 3 と電気的に接続される。図 1、図 2 を参照すると、複数のストリング選択ライン S S L が前記凹部 A 内に提供される。そして、互いに隣接したストリング選択ライン S S L の前記第 3 導電ライン M L 3 は図 1 の場合は同一方向に、図 2 の場合は互いに異なる方向に延長する。本発明の他の実施形態において、導電パッドはコンタクトパッドとコンタクト延長部 C Tとの間に介在される。

#### 【 0 0 5 5 】

前記導電ライン M L 1 ~ M L 3 は前記セルアレイ領域 C A R を挟んで前記第 1 方向及び前記第 2 方向に分けて延長される。例えば、コンタクト延長部 C T が前記第 1 コンタクト領域 C R 1 に配置される導電パターン G S L 、 W L 2 、 W L 4 と接続された導電ライン M L 1 、 M L 2 は前記第 1 方向に延長され、コンタクト延長部 C T が前記第 2 コンタクト領域 C R 2 に配置される導電パターン W L 1 、 W L 3 、 S S L と接続された導電ライン M L 1 、 M L 3 は前記第 2 方向に延長される。

#### 【 0 0 5 6 】

前記凹部 A の前記底面 1 0 3 から上部に延長される活性部 A P が配置される。前記活性部 A P は前記基板 1 0 1 に垂直に延長される。前記活性部 A P は前記導電パターン G S L 、 W L 1 ~ W L 4 、 S S L を貫通し、前記活性部 A P の一端が前記共通ソース領域 1 0 2 に電気的に接続される。前記活性部 A P の他端にドレイン領域 D が配置される。前記ドレイン領域 D は高濃度のドーパントでドーピングされた領域であり得る。例えば、前記活性部 A P は単結晶半導体を含む。

#### 【 0 0 5 7 】

本発明の一実施形態において、前記活性部 A P の前記ドレイン領域 D 上にビットラインコンタクトプラグ B L C P が配置される。前記ビットラインコンタクトプラグ B L C P は前記ドレイン領域 D と電気的に接続されており、前記第 1 層間絶縁膜 1 6 0 を貫通する。前記ビットラインコンタクトプラグ B L C P の上部にビットライン B L が配置される。前記ビットライン B L は前記ビットラインコンタクトプラグ B L C P を通じて前記活性部 A P の前記ドレイン領域 D と接続される。これと異なり、前記ビットライン B L はドレイン領域 D に直接接続され得る。前記ビットライン B L は前記第 1 方向及び前記第 2 方向と交差する第 3 方向に延長される。前記第 3 方向は前記第 1 及び第 2 方向と直角に交差でき、その場合は第 1 、第 2 側壁 1 0 5 、 1 0 6 の水平方向に平行になる。

前記ビットライン B L は複数本配置され、各々のビットライン B L は、前記メモリストリングのアレイのうち前記第 3 方向に沿って整列する複数のメモリストリングの前記ドレイン領域 D に前記ビットラインコンタクトプラグ B L C P を介して接続される。従って前記ビットライン B L は前記ストリング選択ライン S S L とも交差する。

10

20

30

40

50

## 【0058】

前記活性部APの側壁と前記導電パターンGSL、WL1～WL4、SSLとの間に情報貯蔵膜132が介在される。前記情報貯蔵膜132は前記導電パターンGSL、WL1～WL4、SSLを貫通するシリンドータイプに配置されている。前記情報貯蔵膜132は前記活性部APをとり囲むように配置される。前記情報貯蔵膜132は前記活性部APの側壁と前記導電パターンGSL、WL1～WL4、SSL及び前記絶縁膜110～116との間に配置される。

## 【0059】

本発明の第1実施形態に係る活性部、情報貯蔵膜、及び導電パターンを具体的に説明する。図6は、本発明の第1実施形態に係る情報貯蔵膜を説明するための図である。

10

## 【0060】

図6を参照すると、前記情報貯蔵膜132は第1絶縁膜（以下、「トンネル誘電膜」ともいう）136と、電荷貯蔵膜135と、第2絶縁膜（以下、「プロッキング膜」ともいう）134とを含む。

## 【0061】

図1及び図2を参照すると、前記セルアレイ部の一端の外部に延長する一配線は前記一侧のワードラインのコンタクト延長部と電気的に接続される一方、前記セルアレイ部の他端の外部に延長する他の配線は前記他側のワードラインのコンタクト延長部と電気的に接続される。

20

図1に示すように、すべてのストリング選択ラインSSLは一侧で配線と接続される一方、図2に示すように、ストリング選択ラインの一部は一侧の配線と接続され、残りのストリング選択ラインは他側の配線と接続される。前記ワードラインは交互に選択される。すなわち、例えば、ストリングの底から上に向かって奇数番目のワードライン（第1、第3、第5ワードライン）はストリングの一側（図1、図2で右側）の配線と接続され、偶数番目のワードライン（第2、第4、第6ワードライン）はストリングの他側（図1、図2で左側）の配線と接続される。

## 【0062】

前記トンネル誘電膜136は前記活性部APの側壁を覆う。前記トンネル誘電膜136は単一層または多層であり得る。例えば、前記トンネル誘電膜136はシリコン酸窒化膜、シリコン窒化膜、シリコン酸化膜、及び金属酸化膜の中で選択された少なくともいずれか1つを含む。

30

## 【0063】

前記電荷貯蔵膜135は前記トンネル誘電膜136を覆う。前記電荷貯蔵膜135は前記トンネル誘電膜136によって前記活性部APと離隔される。前記電荷貯蔵膜135は電荷を貯蔵することができる電荷トラップサイト（site）を含むことができる。例えば、前記電荷貯蔵膜135はシリコン窒化膜、金属窒化膜、金属酸窒化膜、金属シリコン酸化膜、金属シリコン酸窒化膜、及びナノドット（nanodots）の中の少なくともいずれか1つを含む。

## 【0064】

前記電荷貯蔵膜135と前記導電パターンGSL、WL1～WL4、SSLとの間にプロッキング膜134が介在される。前記電荷貯蔵膜135と前記絶縁膜110～116との間にプロッキング膜134が介在される。前記プロッキング膜134は前記電荷貯蔵膜135を覆う。前記プロッキング膜134はシリコン酸化膜、シリコン窒化膜、シリコン酸窒化膜、及び高誘電膜の中で選択された少なくともいずれか1つを含む。前記高誘電膜は金属酸化膜、金属窒化膜、及び金属酸窒化膜の中で選択された少なくともいずれか1つを含む。前記高誘電膜はハフニウム（Hf）、ジルコニア（Zr）、アルミニウム（Al）、タンタル（Ta）、ランタン（La）、セリウム（Ce）、プラセオジム（Pr）などを含む。前記プロッキング膜134の誘電率は前記トンネル絶縁膜136の誘電率より大きいことがある。

40

50

## 【0065】

本発明の第1実施形態の変形例を説明する。図5は、本発明の第1実施形態の変形例を説明するための図であり、図1及び図2のI-I'に沿って切断した断面図である。

## 【0066】

図1、図2、及び図5を参照すると、基板101が提供される。前記基板101内に共通ソース領域が配置される。前記基板101は凹部Aを含む。前記凹部Aは底面103と互いに対向する第1側壁105及び第2側壁106を含む。前記基板101は前記第1側壁105及び第2側壁106から延長された隆起部Bを含む。前記隆起部Bの上部面は前記凹部Aの前記底面103と平行である。前記隆起部Bは前記基板101上に配置された突出部104によって定義される。

10

## 【0067】

前記凹部Aにはメモリセルが配置される。前記凹部Aは第1側壁105に隣接した第1コンタクト領域CR1、及び第2側壁106に隣接した第2コンタクト領域CR2を含む。前記メモリセルは図3を参照して説明したメモリセルであり得る。

## 【0068】

本発明の第1実施形態の他の変形例に係る半導体素子を説明する。図5は、本発明の第1実施形態の他の変形例を説明するための図であり、図1のI-I'に沿って切断した断面図である。

## 【0069】

図1、2、及び図5を参照すると、基板101が提供される。前記基板101内に共通ソース領域が配置される。前記基板101は凹部Aを含む。前記凹部Aは底面103と互いに対向する第1側壁105及び第2側壁106を含む。前記第1側壁105及び前記第2側壁106の中のいずれか1つの側壁は前記凹部Aの前記底面103に傾いている。例えば、前記第1側壁105及び前記第2側壁106は前記底面103に対して50°であるか、または90°より小さいことがある。前記第1側壁105が前記底面103に対して有する勾配と前記第2側壁106が前記底面103に対して有する勾配は同一であり得る。これと異なり、前記第1側壁105が前記底面103に対して有する勾配と前記第2側壁106が前記底面103に対して有する勾配は異なることができる。前記基板101は前記第1側壁105及び第2側壁106から延長された隆起部Bを含む。前記隆起部Bの上部面は前記凹部Aの前記底面103と平行である。前記基板101において前記凹部A及び前記隆起部Bはエッティング工程を通じて定義される。これと異なり、図4を参照して説明したように、前記隆起部Bは前記基板101上に選択的蒸着により形成された突出部104によって定義される。

20

## 【0070】

前記凹部Aにはメモリセルが配置される。前記メモリセルを説明する。前記凹部Aの前記第1側壁105と隣接した第1コンタクト領域CR1及び前記第2側壁106と隣接した第2コンタクト領域CR2を含む。図3を参照して説明したメモリセルが配置される。前記導電パターンGSL、WL1～WL4、SSLの中の1つの導電パターンで、コンタクト延長部CT及びダミー延長部DCTは底部BPに対して傾いた勾配を有する。

30

## 【0071】

前記コンタクト延長部CTが配置されたコンタクト領域と隣接した側壁が前記底面103となす角度は、前記コンタクト延長部CTが底部BPとなす角度と同一であり得る。第1ワードラインWL1を例にとって、コンタクト延長部CTが前記底部BPに対して有する勾配は前記第2側壁106が前記底面103に対して有する勾配と同一であり得る。前記第1側壁105及び前記第2側壁106が前記底面103に対して有する勾配が各々異なる場合、1つの導電パターンで、コンタクト延長部CTが底部BPに対して有する勾配は、ダミー延長部DCTが底部BPに対して有する勾配と異なることができる。

40

## 【0072】

図1はセルアレイに割り当てられた少なくとも2つのロウ(row)デコーダを含み、すべての前記ストリング選択ラインSSLが1側のロウデコーダと結合されたメモリ素子

50

を示す一方、図2は奇数のストリング選択ラインは一側のロウデコーダと結合し、偶数のストリング選択ラインは他側のロウデコーダと結合するメモリ素子を示す。

### 【0073】

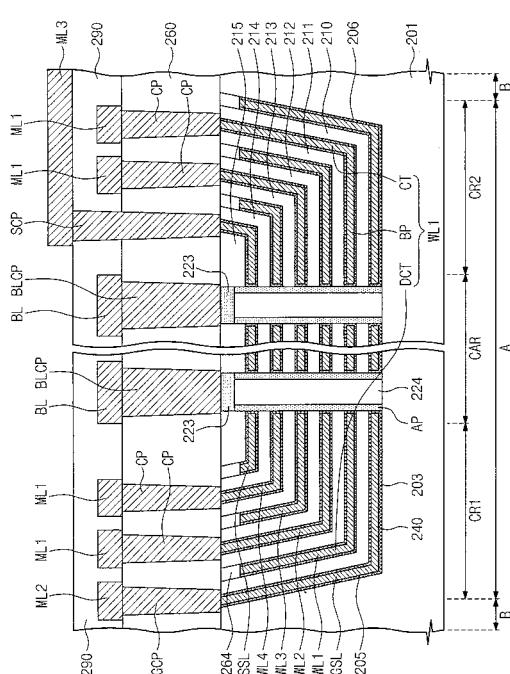

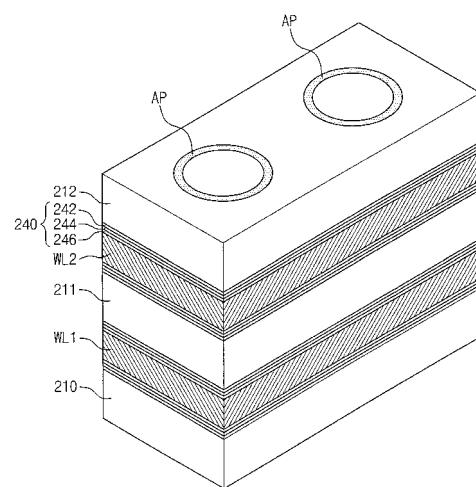

本発明の第2実施形態に係る半導体素子を説明する。図7乃至図8は、本発明の第2実施形態に係る半導体素子を説明するための平面図であり、図9は、図7及び図8のI-I'に沿って切断した断面図である。

### 【0074】

図7、図8、及び図9を参照すると、基板201が提供される。前記基板201は半導体基盤の半導体基板である。前記基板201はウェル(well)を含む。前記ウェルは第1導電型のドーパントを含む。前記基板201内に共通ソース領域202が配置される。前記共通ソース領域202は前記基板201のセル領域内に平板形態(plate form)に配置される。前記共通ソース領域202は高濃度のドーパントを含むことができる。前記共通ソース領域202に含まれたドーパントは前記ウェルに含まれたドーパントと異なる導電型の第2導電型であり得る。例えば、前記ウェルがp型ドーパントを含む場合、前記共通ソース領域202は高濃度のn型ドーパントを含む。

10

### 【0075】

前記基板201は凹部Aを含む。前記凹部Aは底面203と互いに対向する第1側壁205及び第2側壁206を含む。前記基板201は前記第1側壁205及び第2側壁206から延長された隆起部Bを含む。前記隆起部Bの上部面は前記凹部Aの前記底面203と平行である。前記凹部A及び前記隆起部Bは、半導体基板の凹部Aが配置される部分をエッチングして、隆起部Bが配置される部分を残して形成される。この場合、前記基板201は一体の基板であり得る。前記凹部Aにメモリセルが配置される。

20

### 【0076】

前記凹部Aの前記第1側壁205と隣接した第1コンタクト領域CR1、及び前記第2側壁206と隣接した第2コンタクト領域CR2を含む。前記第1コンタクト領域CR1と前記第2コンタクト領域CR2との間にセルアレイ領域CARが配置される。前記第1コンタクト領域CR1及び第2コンタクト領域CR2は、前記セルアレイ領域CARを挟んで互いに離隔されている。

30

### 【0077】

前記基板201上に互いに離隔された導電パターンGSL、WL1～WL4、SSLが配置される。前記導電パターンGSL、WL1～WL4、SSLは前記基板201の前記凹部A上に順に積層された接地選択ラインGSL、ワードラインWL1～WL4、及びストリング選択ラインSSLを含む。前記導電パターンGSL、WL1～WL4、SSLはゲート間絶縁膜210～214を挟んで互いに離隔されて配置される。例えば、前記接地選択ラインGSL、第1ゲート間絶縁膜210、第1ワードラインWL1、第2ゲート間絶縁膜211、第2ワードラインWL2、第3ゲート間絶縁膜212、第3ワードラインWL3、第4ゲート間絶縁膜213、第4ワードラインWL4、第5ゲート間絶縁膜214、及びストリング選択ラインSSLが順に積層されている。前記絶縁膜210～214は前記基板201の前記凹部Aの前記底面203上の底部、前記底部から前記第1側壁205及び前記第2側壁206上に延長される側壁部を含む。前記ストリング選択ラインSSL上にストリング選択絶縁膜215が配置されている。前記導電パターンGSL、WL1～WL4、SSLは第1方向に延長されるライン形態であり得る。前記第1方向はI-I'の方向である。すなわち、本実施形態のメモリ素子はセルアレイメモリでワードライン平面を分離するX-cutトレニチを含む素子である。実質的に同一のレベルの前記分離したワードラインは電気的に互いに接続されており、1つのワードライン平面として作用する。

40

### 【0078】

前記導電パターンGSL、WL1～WL4、SSLは前記凹部Aの前記底面203上に配置された底部BPを含む。前記底部BPの長さは前記基板201の前記凹部Aから遠く

50

なるほど長さが短くなる。前記底部B Pは前記底面203と平行である。前記底部B Pは前記隆起部Bの上部面と平行である。

#### 【0079】

前記導電パターンG S L、W L 1 ~ W L 4、S S Lは前記底部B Pの一端から前記第1側壁205または前記第2側壁206の中の1つの側壁上に延長される(ex tended over)コンタクト延長部C Tを含む。前記導電パターンG S L、W L 1 ~ W L 4、S S Lの中のいずれか1つの導電パターンのコンタクト延長部が配置されるコンタクト領域と、前記いずれか1つの導電パターンと隣接した他の導電パターンのコンタクト延長部が配置されるコンタクト領域は異なることができる。例えば、前記接地選択ラインG S Lのコンタクト延長部C Tが前記第1コンタクト領域C R 1に配置される場合、前記接地選択ラインG S Lと隣接した第1ワードラインW L 1のコンタクト延長部C Tは前記第2コンタクト領域C R 2に配置される。

10

#### 【0080】

前記コンタクト延長部C Tは前記底面203に対して傾斜する。前記コンタクト延長部C Tは前記底面203に対して直角に傾斜することができる。前記コンタクト延長部C Tは前記基板201の前記凹部Aから距離が遠くなるほど長さが減少される。前記コンタクト延長部C Tの上部面は前記隆起部Bの上部面と同一平面にある。前記コンタクト延長部C Tが前記底部B Pとなす角度は90°であり得る。

20

#### 【0081】

前記導電パターンG S L、W L 1 ~ W L 4、S S Lは前記底面203上の前記底部B Pの他端から前記第1側面205及び前記第2側面206の中の他の1つの側面上に延長される(ex tended over)ダミー延長部D C Tを含む。前記導電パターンG S L、W L 1 ~ W L 4、S S Lの中のいずれか1つの導電パターンのダミー延長部が配置されるコンタクト領域と、前記いずれか1つの導電パターンと隣接した他の導電パターンのダミー延長部が配置されるコンタクト領域は異なることができる。例えば、前記ストリング選択ラインS S Lのダミー延長部D C Tが前記第1コンタクト領域C R 1に配置される場合、前記ストリング選択ラインS S Lと隣接した前記第4ワードラインW L 4のダミー延長部D C Tは前記第2コンタクト領域C R 2に配置される。

20

#### 【0082】

前記導電パターンG S L、W L 1 ~ W L 4、S S Lの各々は1つのコンタクト延長部C Tと、1つのダミー延長部D C Tとを含む。前記導電パターンG S L、W L 1 ~ W L 4、S S Lの中の1つの導電パターンで、前記ダミー延長部D C Tの長さは前記コンタクト延長部C Tの長さより短いことがある。前記コンタクト延長部C Tは互いに隣接したダミー延長部D C Tの間に配置される。ダミー延長部D C Tと隣接したコンタクト延長部C Tはその間に介在された絶縁膜の側壁部によって離隔される。

30

#### 【0083】

前記ダミー延長部D C T上にダミー絶縁パターン264が配置される。前記ダミー絶縁パターン264の上部面は前記隆起部Bの上部面と同一平面にある。前記ダミー絶縁パターン264の上部面は前記ストリング選択絶縁膜215の上部面と同一平面にある。前記ダミー絶縁パターン264の側壁は前記ダミー延長部D C Tの側壁と同一平面にある。前記ダミー絶縁パターン264は前記絶縁膜210~215と同一の物質を含むことができる。

40

#### 【0084】

前記ワードラインW L 1 ~ W L 4のコンタクト延長部C T上に導電プラグが配置される。前記導電プラグはワードラインコンタクトプラグC Pであり得る。前記ワードラインW L 1 ~ W L 4の各々は前記ワードラインコンタクトプラグC Pと電気的に接続される。前記ワードラインコンタクトプラグC Pの幅は前記ワードラインW L 1 ~ W L 4のコンタクト延長部C Tの上部面の幅より広いことがある。前記ワードラインコンタクトプラグC Pは前記ワードラインW L 1 ~ W L 4のコンタクト延長部C Tと隣接したダミー延長部D C Tの間の幅より広いことがある。前記ワードラインコンタクトプラグC Pは第1層間絶縁

50

膜 280 を貫通する。前記ワードラインコンタクトプラグ C P 及び前記第 1 層間絶縁膜 280 上に第 1 導電ライン M L 1 が配置される。前記ワードラインコンタクトプラグ C P は前記第 1 導電ライン M L 1 と電気的に接続される。前記第 1 導電ライン M L 1 は前記第 1 方向と交差する第 2 方向に延長される。前記第 1 導電ライン M L 1 は前記ワードラインコンタクトプラグ C P を通じて前記ワードライン W L 1 ~ W L 4 と電気的に接続される。これと異なり、前記第 1 導電ライン M L 1 及び前記ワードライン W L 1 ~ W L 4 は直接接続され得る。前記第 1 導電ライン M L 1 を覆う第 2 層間絶縁膜 290 が配置される。前記第 1 層間絶縁膜 280 及び前記第 2 層間絶縁膜 290 は同一の物質を含むことができる。

#### 【 0085 】

前記接地選択ライン G S L のコンタクト延長部 C T 上に導電プラグが配置される。10 前記導電プラグは接地選択コンタクトプラグ G C P であり得る。前記接地選択ライン G S L は前記接地選択コンタクトプラグ G C P と電気的に接続される。前記接地選択コンタクトプラグ G C P の幅は前記接地選択ライン G S L のコンタクト延長部 C T の上部面の幅より広いことがある。前記接地選択コンタクトプラグ G C P は第 1 層間絶縁膜 280 を貫通する。前記接地選択コンタクトプラグ G C P 及び前記第 1 層間絶縁膜 280 上に第 2 導電ライン M L 2 が配置される。前記接地選択コンタクトプラグ G S P は前記第 2 導電ライン M L 2 と電気的に接続される。前記第 2 導電ライン M L 2 は前記第 2 方向に延長される。前記第 2 導電ライン M L 2 は前記接地選択コンタクトプラグ G C P を通じて接地選択ライン G S L と電気的に接続される。これと異なり、前記第 2 導電ライン M L 2 は前記接地選択ライン G S L と直接接続され得る。20 前記第 2 層間絶縁膜 290 は前記第 2 導電ライン M L 2 を覆う。

#### 【 0086 】

前記ストリング選択ライン S S L のコンタクト延長部 C T 上に導電プラグが配置される。30 前記導電プラグはストリング選択コンタクトプラグ S C P であり得る。前記ストリング選択ライン S S L は前記ストリング選択コンタクトプラグ S C P と電気的に接続される。前記ストリング選択コンタクトプラグ S C P の幅は前記ストリング選択ライン S S L のコンタクト延長部 C T の上部面の幅より広いことがある。前記ストリング選択コンタクトプラグ S C P は第 1 層間絶縁膜 280 及び前記第 2 層間絶縁膜 290 を貫通する。前記ストリング選択コンタクトプラグ S C P 及び前記第 2 層間絶縁膜 280 上に第 3 導電ライン M L 3 が配置される。前記ストリング選択コンタクトプラグ S S L は前記第 3 導電ライン M L 3 と電気的に接続される。前記第 3 導電ライン M L 3 は前記第 1 方向に延長される。図 8 を参照すると、複数のストリング選択ライン S S L が前記凹部 A 内に配置される。そして、互いに隣接したストリング選択ライン S S L の第 3 導電ライン M L 3 は他の方向に延長される。

#### 【 0087 】

前記導電ライン M L 1 、 M L 2 は前記セルアレイ領域 C A R の両側に分けられて配置される。導電パターン G S L 、 W L 1 ~ W L の中のいずれか 1 つの導電パターンと接続された導電ラインは、前記いずれか 1 つの導電パターンと隣接した他の導電パターンと接続された導電ラインと異なるコンタクト領域に配置される。例えば、前記第 1 ワードライン W L 1 と接続された第 1 導電ライン M L 1 は前記第 2 コンタクト領域 C R 2 に配置されており、前記第 1 ワードライン W L 1 と隣接した前記接地選択ライン G S L 及び前記第 2 ワードライン W L 2 と各々接続された第 2 導電ライン M L 2 及び第 1 導電ライン M L 1 は前記第 1 コンタクト領域 C R 1 に配置されている。40

#### 【 0088 】

前記基板 201 の前記凹部 A の前記底面 203 から上部に延長される活性部 A P が配置される。前記活性部 A P は前記基板 201 に垂直に延長される。前記活性部 A P は前記導電パターン G S L 、 W L 1 ~ W L 4 、 S S L を貫通する。これと異なり、前記活性部 A P は前記導電パターン G S L 、 W L 1 ~ W L 4 、 S S L の側面と対向することができる。前記活性部 A P の一端が前記共通ソース領域 202 に電気的に接続される。前記活性部 A P の他端にドレイン領域 223 が配置される。前記ドレイン領域 D は高濃度のドーパントで50

ドーピングされた領域であり得る。前記活性部 A P は単結晶半導体を含む。

#### 【 0 0 8 9 】

前記活性部 A P の前記ドレイン領域 D 上にビットラインコンタクトプラグ B L C P が配置される。前記ビットラインコンタクトプラグ B L C P は前記ドレイン領域 2 2 3 と電気的に接続され、前記第 1 層間絶縁膜 2 8 0 及び第 2 層間絶縁膜 2 9 0 を貫通する。前記ビットラインコンタクトプラグ B L C P の上部にビットライン B L が配置される。前記ビットライン B L は前記ビットラインコンタクトプラグ B L C P を通じて前記活性部 A P の前記ドレイン領域 2 2 3 と接続される。これと異なり、前記ビットライン B L はドレイン領域 D に直接接続され得る。前記ビットライン B L は前記第 2 方向に延長される。前記ビットライン B L は前記第 3 導電ライン M L 3 と交差する。

10

#### 【 0 0 9 0 】

前記活性部 A P の側壁と前記導電パターン G S L 、 W L 1 ~ W L 4 、 S S L との間に情報貯蔵膜 2 4 0 が介在される。前記情報貯蔵膜 2 4 0 は前記導電パターン G S L 、 W L 1 ~ W L 4 、 S S L と前記活性部 A P の側壁との間に配置される。前記情報貯蔵膜 2 4 0 は前記導電パターン G S L 、 W L 1 ~ W L 4 、 S S L と前記絶縁膜 2 1 0 ~ 2 1 5 との間に配置される。

#### 【 0 0 9 1 】

本発明の第 2 実施形態に係る活性部、情報貯蔵膜及び導電パターンを具体的に説明する。図 1 2 は、本発明の第 2 実施形態に係る情報貯蔵膜を説明するための図である。

20

#### 【 0 0 9 2 】

図 7 はセルアレイに割り当てられた少なくとも 2 つのロウ ( r o w ) デコーダを含み、すべての前記ストリング選択ライン S S L が 1 つのロウデコーダと結合されたメモリ素子を示す一方、図 8 は奇数のストリング選択ラインは一口ウデコーダと結合し、偶数のストリング選択ラインは他のロウデコーダと結合するメモリ素子を示す。

#### 【 0 0 9 3 】

図 1 2 を参照すると、前記情報貯蔵膜 2 4 0 はトンネル誘電膜 2 4 2 と、電荷貯蔵膜 2 4 4 と、プロッキング膜 2 4 6 とを含む。

#### 【 0 0 9 4 】

前記トンネル誘電膜 2 4 2 は前記活性部 A P の側壁を覆う。前記トンネル誘電膜 2 4 2 は単一層または多層であり得る。例えば、前記トンネル誘電膜 2 4 2 はシリコン酸窒化膜、シリコン窒化膜、シリコン酸化膜及び金属酸化膜の中で選択された少なくともいずれか 1 つを含む。

30

#### 【 0 0 9 5 】

前記電荷貯蔵膜 2 4 4 は前記トンネル誘電膜 2 4 2 を覆う。前記電荷貯蔵膜 2 4 4 は前記トンネル誘電膜 2 4 2 によって前記活性部 A P と離隔される。前記電荷貯蔵膜 2 4 4 は電荷を貯蔵することができる電荷トラップサイト ( s i t e ) を含むことができる。例えば、前記電荷貯蔵膜 2 4 4 はシリコン窒化膜、金属窒化膜、金属酸窒化膜、金属シリコン酸化膜、金属シリコン酸窒化膜及びナノドット ( n a n o d o t ) の中の少なくともいずれか 1 つを含む。

#### 【 0 0 9 6 】

前記電荷貯蔵膜 2 4 4 と前記導電パターン G S L 、 W L 1 ~ W L 4 、 S S L との間にプロッキング膜 2 4 6 が介在される。前記電荷貯蔵膜 2 4 4 と前記絶縁膜 1 1 0 ~ 1 1 6 との間にプロッキング膜 2 4 6 が介在される。前記プロッキング膜 2 4 6 は前記電荷貯蔵膜 2 4 4 を覆う。前記プロッキング膜 2 4 6 はシリコン酸化膜、シリコン窒化膜、シリコン酸窒化膜及び高誘電膜の中で選択された少なくともいずれか 1 つを含む。前記高誘電膜は金属酸化膜、金属窒化膜及び金属酸窒化膜の中で選択された少なくともいずれか 1 つを含む。前記高誘電膜はハフニウム ( H f ) 、ジルコニア ( Z r ) 、アルミニウム ( A l ) 、タンタル ( T a ) 、ランタン ( P a ) 、セリウム ( C e ) 、プラセオジム ( P r ) などを含む。前記プロッキング膜 2 4 6 の誘電率は前記トンネル絶縁膜 2 4 2 の誘電率より大きいことがある。

40

50

本発明の第2実施形態の活性部の変形例を説明する。図13は、本発明の第2実施形態の変形例に係る活性部を説明するための図である。

#### 【0097】

図13を参照すると、図12を参照して説明したトンネル誘電膜242、電荷貯蔵膜244及びブロッキング膜246を含む情報貯蔵膜240が導電パターンWL1、GSLと前記活性部APとの間に配置される。前記活性部APは前記導電パターンGSL、WL1の前記底部BPの側面と対向する。

#### 【0098】

本発明の第2実施形態の変形例を説明する。図10は、本発明の第2実施形態の変形例を説明するための図であり、図7及び図8のII-II'に沿って切断した断面図である。

10

#### 【0099】

図7、図8、及び図10を参照すると、基板200が提供される。前記基板200内に共通ソース領域202が配置される。前記基板200は凹部Aを含む。前記凹部Aは底面203と互いに対向する第1側壁205及び第2側壁206を含む。前記基板200は前記第1側壁205及び第2側壁206から延長された隆起部Bを含む。前記隆起部Bの上部面は前記凹部Aの前記底面203と平行である。前記隆起部Bは前記基板201上に配置された絶縁膜204によって定義される。

#### 【0100】

前記凹部Aにメモリセルが配置される。前記凹部Aの前記第1側壁205と隣接した第1コンタクト領域CR1、及び前記第2側壁206と隣接した第2コンタクト領域CR2を含む。前記基板200の凹部Aには図9を参照して説明したメモリセルが配置される。

20

#### 【0101】

本発明の第2実施形態の他の変形例に係る半導体素子を説明する。図11は、本発明の第2実施形態の他の変形例を説明するための図であり、図7及び図8のII-II'に沿って切断した断面図である。

#### 【0102】

図7、図8、及び図11を参照すると、基板201が提供される。前記基板201内に共通ソース領域102が配置される。前記基板201は凹部Aを含む。前記凹部Aは底面203と互いに対向する第1側壁205及び第2側壁206を含む。前記第1側壁205及び前記第2側壁206の中のいずれか1つの側壁は前記凹部Aの前記底面203に傾いている。例えば、前記第1側壁205及び前記第2側壁206は前記底面203に対して50°であるか、または90°より小さいことがある。前記第1側壁205が前記底面203に対して有する勾配と前記第2側壁206が前記底面203に対して有する勾配は同一であり得る。これと異なり、前記第1側壁205が前記底面203に対して有する勾配と前記第2側壁206が前記底面203に対して有する勾配は異なることができる。前記基板201は前記第1側壁205及び第2側壁206から延長された隆起部Bを含む。前記隆起部Bの上部面は前記凹部Aの前記底面203と平行である。基板の凹部及び隆起部はエッチング工程を通じて定義される。これと異なり、図10を参照して説明したように、前記隆起部Bは前記基板201上に配置された絶縁膜104によって定義される。

30

#### 【0103】

前記凹部Aにメモリセルが配置される。前記凹部Aの前記第1側壁205に隣接した第1コンタクト領域CR1、及び前記第2側壁206に隣接した第2コンタクト領域CR2とを含む。図9を参照して説明したメモリセルが配置される。前記導電パターンGSL、WL1～WL4、SSLの中の1つの導電パターンで、コンタクト延長部CT及びダミー延長部DCTは底部BPに対して傾いた勾配を有する。

40

#### 【0104】

前記コンタクト延長部CTが配置されたコンタクト領域に隣接した側壁が前記底面203となす角度は、前記コンタクト延長部CTが底部BPとなす角度と同一であり得る。第1ワードラインWL1を例にとって、コンタクト延長部CTが前記底部BPに対して有す

50

る勾配は、前記第2側壁206が前記底面203に対して有する勾配と同一であり得る。前記第1側壁205及び前記第2側壁206が前記底面203に対して有する勾配が各々異なる場合、1つの導電パターンで、コンタクト延長部C Tが底部B Pに対して有する勾配は、ダミー延長部D C Tが底部B Pに対して有する勾配と異なることができる。

#### 【0105】

図12及び図13を参照すると、前記活性部はシリコンで形成される。前記活性部は柱(pillar)、管(tubular)またはバーサイド(bar-sided)形であり得る。前記活性部は単結晶シリコンまたは多結晶シリコンで形成される。前記活性部は非晶質シリコンで形成され、多結晶シリコンに結晶化される。図13はバーサイド形の垂直な活性部を示す。本発明によれば、活性部の形は制限されない。したがって、管または柱形の活性部を図1、図2、及び図7、図8に適用することができる。10

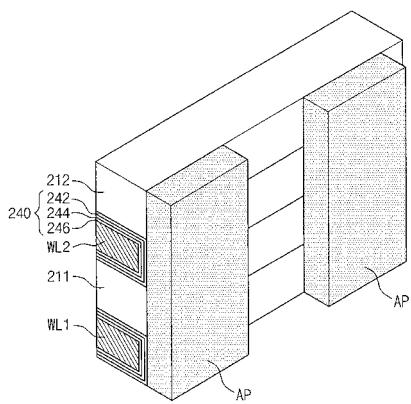

#### 【0106】

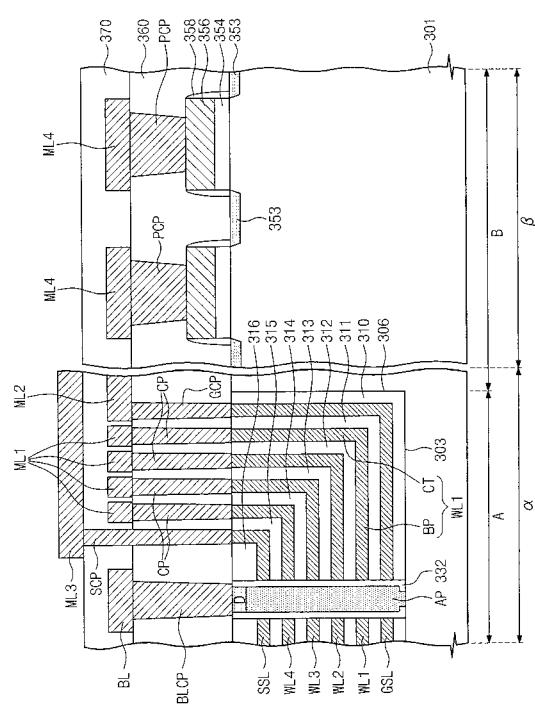

本発明の第3実施形態に係る半導体素子を説明する。図14は、本発明の第3実施形態に係る半導体素子を説明するための平面図であり、図15は、図14のI—I—I’に沿って切断した断面図である。

#### 【0107】

図14及び図15を参照すると、基板301が提供される。前記基板301は半導体基盤の半導体基板である。前記基板301はウェル(well)を含む。前記ウェルは第1導電型のドーパントを含む。前記基板301内に共通ソース領域302が配置される。前記共通ソース領域302は前記基板301のセル領域内に平板形態(plate form)に配置される。前記共通ソース領域302は高濃度のドーパントを含むことができる。前記共通ソース領域302に含まれたドーパントは前記ウェルに含まれたドーパントと異なる導電型の第2導電型であり得る。例えば、前記ウェルがp型ドーパントを含む場合、前記共通ソース領域302は高濃度のn型ドーパントを含む。20

#### 【0108】

前記基板301は凹部Aを含む。前記凹部Aは底面303と第1側壁306とを含む。前記基板301は前記第1側壁306から延長された隆起部Bを含む。前記隆起部Bの上部面は前記凹部Aの前記底面303と平行である。前記凹部A及び前記隆起部Bは、半導体基板の凹部Aが配置される部分をエッチングして、隆起部Bが配置される部分を残して形成される。この場合、前記基板301は一体の基板である。30

#### 【0109】

前記基板301はセル領域と周辺回路領域とを含む。前記セル領域にはメモリセルが配置される。前記セル領域は前記凹部A及び前記隆起部Bを含む。前記周辺回路領域には周辺回路が配置される。前記周辺回路領域は前記隆起部Bを含む。

#### 【0110】

前記基板301のセル領域に対して説明する。

#### 【0111】

前記基板301の前記凹部A上に互いに離隔された導電パターンG S L、W L 1 ~ W L 4、S S Lが配置される。前記導電パターンG S L、W L 1 ~ W L 4、S S Lは前記基板301の前記凹部A上に順に積層された接地選択ラインG S L、ワードラインW L 1 ~ W L 4、及びストリング選択ラインS S Lを含む。前記導電パターンG S L、W L 1 ~ W L 4、S S Lはゲート間絶縁膜311 ~ 315を挟んで互いに離隔されて配置される。例えば、前記接地選択ラインG S L、第1ゲート間絶縁膜311、第1ワードラインW L 1、第2ゲート間絶縁膜312、第2ワードラインW L 2、第3ゲート間絶縁膜313、第3ワードラインW L 3、第4ゲート間絶縁膜314、第4ワードラインW L 4、第5ゲート間絶縁膜315、及びストリング選択ラインS S Lが順に積層されている。40

#### 【0112】

前記基板301の前記凹部Aの前記底面303及び第1側壁306と前記接地選択ラインG S Lとの間に接地選択絶縁膜310が配置される。前記ストリング選択ラインS S L上にストリング選択絶縁膜316が配置される。前記絶縁膜310 ~ 116は前記基板3

10

20

30

40

50

01の前記凹部Aの前記底面303上の底部と、前記底部から前記第1側壁306上に延長される側壁部とを含む。

【0113】

前記導電パターンGSL、WL1～WL4、SSLは前記凹部Aの前記底面303上に配置された底部BPを含む。前記底部BPの長さは前記基板301の前記凹部Aから遠くなるほど長さが短くなることができる。前記底部BPは前記底面303と平行である。前記底部BPは前記隆起部Bの上部面と平行である。

【0114】

前記導電パターンGSL、WL1～WL4、SSLは前記底部BPの一端から前記第1側壁206上に延長される(extended over)コンタクト延長部CTを含む。前記コンタクト延長部CTの延長線は前記底面303と交差することができる。前記コンタクト延長部CTの延長線は前記底面303と直角に交差することができる。前記コンタクト延長部CTは前記基板301の前記凹部Aから距離が遠くなるほど長さが減少される。前記コンタクト延長部CTの上部面は前記隆起部Bの上部面と同一平面にある。前記コンタクト延長部CTが前記底部BPとなす角度は90°であり得る。

10

【0115】

前記ワードラインWL1～WL4のコンタクト延長部CT上に導電プラグが配置される。前記導電プラグはワードラインコンタクトプラグCPであり得る。前記ワードラインWL1～WL4の各々は前記ワードラインコンタクトプラグCPと電気的に接続される。前記ワードラインコンタクトプラグCPは第1層間絶縁膜360を貫通する。前記ワードラインコンタクトプラグCP及び前記第1層間絶縁膜360上に第1導電ラインML1が配置される。前記ワードラインコンタクトプラグCPは前記第1導電ラインML1と電気的に接続される。前記第1導電ラインML1は第1方向に延長される。前記第1導電ラインML1は前記ワードラインコンタクトプラグCPを通じて前記ワードラインWL1～WL4と電気的に接続される。これと異なり、前記第1導電ラインML1は前記ワードラインWL1～WL4と直接接続され得る。前記第1導電ラインML1覆う第2層間絶縁膜370が配置される。前記第1層間絶縁膜360及び前記第2層間絶縁膜360は同一の物質を含むことができる。

20

【0116】

前記接地選択ラインGSLのコンタクト延長部CT上に導電プラグが配置される。前記導電プラグは接地選択コンタクトプラグGCPであり得る。前記接地選択ラインGSLは前記接地選択コンタクトプラグGCPと電気的に接続される。前記接地選択コンタクトプラグGCPは第1層間絶縁膜360を貫通する。前記接地選択コンタクトプラグGCP及び前記第1層間絶縁膜360上に第2導電ラインML2が配置される。前記接地選択コンタクトプラグGCPは前記第2導電ラインML2と電気的に接続される。前記第2導電ラインML2は前記第1方向に延長される。前記第1方向はI I I - I I I'方向である。前記第2導電ラインML2は前記接地選択コンタクトプラグGCPを通じて前記接地選択ラインGSLと電気的に接続される。これと異なり、前記第2導電ラインML2は前記接地選択ラインGSLと直接接続され得る。前記第2層間絶縁膜370は前記第2導電ラインML2を覆う。

30

【0117】

前記ストリング選択ラインSSLのコンタクト延長部CT上に導電プラグが配置される。前記導電プラグはストリング選択コンタクトプラグSCPであり得る。前記ストリング選択ラインSSLは前記ストリング選択コンタクトプラグSCPと電気的に接続される。前記ストリング選択コンタクトプラグSCPは第1層間絶縁膜360及び第2層間絶縁膜370を貫通する。前記ストリング選択コンタクトプラグSCP及び前記第1層間絶縁膜360上に第3導電ラインML3が配置される。前記ストリング選択コンタクトプラグSSLは前記第3導電ラインML3と電気的に接続される。前記第3導電ラインML3は前記第1方向に延長される。

40

【0118】

50

前記凹部Aの前記底面303から上部に延長される活性部APが配置される。前記活性部APは前記基板301に垂直に延長される。前記活性部APは前記導電パターンGSL、WL1～WL4、SSLを貫通して前記活性部APの一端が前記共通ソース領域302に電気的に接続される。前記活性部APの他端にドレイン領域Dが配置される。前記ドレイン領域Dは高濃度のドーパントでドーピングされた領域であり得る。前記活性部APは単結晶半導体を含む。

#### 【0119】

前記活性部APの前記ドレイン領域D上にピットラインコンタクトプラグBLCPが配置される。前記ピットラインコンタクトプラグBLCPは前記ドレイン領域Dと電気的に接続され、前記第1層間絶縁膜360を貫通する。前記ピットラインコンタクトプラグBLCPの上部にピットラインBLが配置される。前記ピットラインBLは前記ピットラインコンタクトプラグBLCPを通じて前記活性部APの前記ドレイン領域Dと接続される。これと異なり、前記ピットラインBLはドレイン領域Dに直接接続され得る。前記ピットラインBLは前記第1方向と交差する第2方向に延長される。前記ピットラインBLは前記第3導電ラインML3と交差する。

10

#### 【0120】

前記活性部APの側壁と前記導電パターンGSL、WL1～WL4、SSLとの間に情報貯蔵膜332が介在される。前記情報貯蔵膜332は前記導電パターンGSL、WL1～WL4、SSLを貫通するシリンドータイプに配置される。前記情報貯蔵膜332は前記活性部APを取り囲むように配置される。前記情報貯蔵膜332は前記活性部APの側壁と前記導電パターンGSL、WL1～WL4、SSL及び前記絶縁膜310～116との間に配置される。

20

#### 【0121】

本発明の第3実施形態に係る情報貯蔵膜332は図6を参照して説明した情報貯蔵膜である。

#### 【0122】

前記基板301の周辺回路領域に対して説明する。

#### 【0123】

前記周辺回路領域の前記隆起部Bの上部面上に周辺回路が配置される。前記隆起部Bの上部面上にゲート絶縁膜354が配置される。前記ゲート絶縁膜354はシリコン酸化膜を含む。前記ゲート絶縁膜354は前記隆起部Bの上部面を熱酸化して形成されたことを含む。前記ゲート絶縁膜354上にゲート電極356が配置される。前記ゲート電極356はドーピングされたポリシリコン、金属及び金属シリサイドの中のいずれか1つを含む。前記ゲート電極356の両側壁上にスペーサ358が配置される。前記ゲート電極356の両側壁の前記隆起部Bにソースドレイン領域353が配置される。前記ソースドレイン領域353は高濃度のドーパントでドーピングされた領域である。

30

#### 【0124】

前記ゲート電極356及びソースドレイン領域353上に第1層間絶縁膜360を貫通する周辺回路コンタクトプラグPCPが配置される。前記周辺回路コンタクトプラグPCP上に第4導電ラインML4が配置される。前記第4導電ラインML4上に第2層間絶縁膜370が配置される。

40

#### 【0125】

本発明の第3実施形態の変形例を説明する。図16は、本発明の第3実施形態の変形例を説明するための図であり、図14のIII-III'に沿って切断した断面図である。

#### 【0126】

図14及び図16を参照すると、基板300が提供される。前記基板300内に共通ソース領域302が配置される。前記基板300は凹部Aを含む。前記凹部Aは底面303と第1側壁306とを含む。前記基板300は前記第1側壁306から延長された隆起部Bを含む。前記隆起部Bの上部面は前記凹部Aの前記底面303と平行である。前記隆起部Bは前記基板300上に配置された絶縁膜304によって定義される。

50

## 【0127】

前記基板300はセル領域 及び周辺回路領域 を含む。前記セル領域 にはメモリセルが配置される。前記周辺回路領域 に周辺回路が配置される。

## 【0128】

前記基板300のセル領域 に対して説明する。

## 【0129】

前記基板300のセル領域 には図15を参照して説明したメモリセルが配置される。

## 【0130】

前記基板300の周辺回路領域 に対して説明する。

## 【0131】

前記周辺回路領域 の前記隆起部Bの上部面上に周辺回路が配置される。前記絶縁膜304の上部面上に半導体膜352が配置される。前記半導体膜352はポリシリコン、結晶質シリコン、及び単結晶シリコンを含むその他半導体物質を含む。前記半導体膜352上にゲート絶縁膜354が配置される。前記ゲート絶縁膜354はシリコン酸化膜を含む。前記ゲート絶縁膜354は前記半導体膜352を熱酸化して形成されたことを含む。前記ゲート絶縁膜354上にゲート電極356が配置される。前記ゲート電極356はドーピングされたポリシリコン、金属、及び金属シリサイドの中のいずれか1つを含む。前記ゲート電極356の両側壁上にスペーサ358が配置される。前記ゲート電極356の両側壁の前記半導体膜352にソースドレイン領域353が配置される。前記ソースドレイン領域353は高濃度のドーパントでドーピングされた領域であり得る。

10

20

## 【0132】

前記ゲート電極356及びソースドレイン領域353上に第1層間絶縁膜360を貫通する周辺回路コンタクトプラグPCPが配置される。前記周辺回路コンタクトプラグPCP上に第4導電ラインML4が配置される。前記第4導電ラインML4上に第2層間絶縁膜370が配置される。

## 【0133】

本発明の第3実施形態の他の変形例に係る半導体素子を説明する。図17は、本発明の第3実施形態の他の変形例を説明するための図であり、図14のI—I—I—I—I’に沿って切断した断面図である。

## 【0134】

30

図14及び図17を参照すると、基板301が提供される。前記基板301内に共通ソース領域302が配置される。前記基板301は凹部Aを含む。前記凹部Aは底面303と第1側壁306とを含む。前記第1側壁306は前記凹部Aの前記底面303に傾いている。例えば、前記第1側壁305は前記底面303に対して90°超過130°以下の角度を有することができる。前記前記基板301は前記第1側壁306から延長された隆起部Bを含む。前記隆起部Bの上部面は前記凹部Aの前記底面303と平行である。基板の凹部及び隆起部はエッチング工程を通じて定義される。これと異なり、図16を参照して説明したように、前記隆起部Bは前記基板301上に配置された絶縁膜304によって定義される。

## 【0135】

40

前記基板301はセル領域 及び周辺回路領域 を含む。前記セル領域 にはメモリセルが配置される。前記周辺回路領域 は周辺回路を含む。

## 【0136】

前記基板301のセル領域 に対して説明する。

## 【0137】

前記セル領域 の前記凹部Aに図15を参照して説明したメモリセルが配置される。前記導電パターンGSL、WL1～WL4、SSLのコンタクト延長部CTは前記底面303に対して傾いた勾配を有する。導電パターンGSL、WL1～WL4、SSLのコンタクト延長部CTが前記底面303となす角度は前記第1側壁306が前記底面303に対してなす角度と同一であり得る。

50

## 【0138】

前記基板301の周辺回路領域 に対して説明する。

## 【0139】

前記基板301の周辺回路領域 には図15を参照して説明した周辺回路が配置される。これと異なり、上述のように、基板が図16を参照して説明した基板の場合、半導体膜352が追加される。

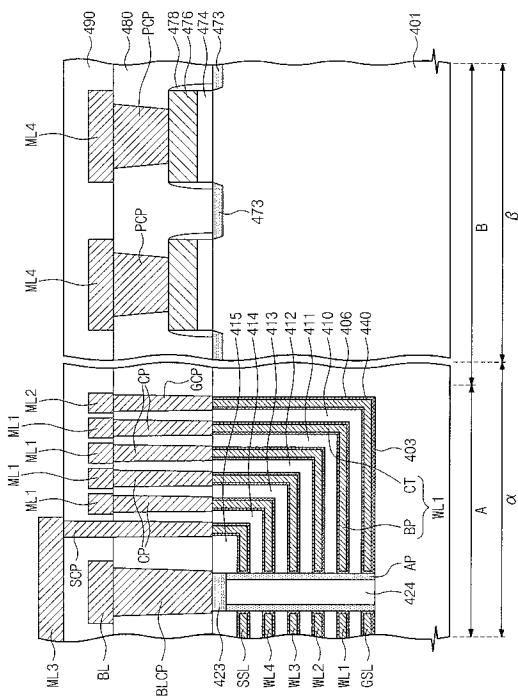

## 【0140】

本発明の第4実施形態に係る半導体素子を説明する。図18は、本発明の第4実施形態に係る半導体素子を説明するための平面図であり、図19は、図18のIV-IV'に沿って切断した断面図である。

10

## 【0141】

図18及び図19を参照すると、基板401が提供される。前記基板401は半導体基盤の半導体基板である。前記基板401はウェル(well)を含む。前記ウェルは第1導電型のドーパントを含む。前記基板401内に共通ソース領域402が配置される。前記共通ソース領域402は前記基板401のセル領域内に平板形態(plate form)に配置される。前記共通ソース領域402は高濃度のドーパントを含むことができる。前記共通ソース領域402に含まれたドーパントは前記ウェルに含まれたドーパントと異なる導電型の第2導電型であり得る。例えば、前記ウェルがp型ドーパントを含む場合、前記共通ソース領域402は高濃度のn型ドーパントを含む。

## 【0142】

前記基板401は凹部Aを含む。前記凹部Aは底面403と第1側壁406とを含む。前記基板401は前記第1側壁406から延長された隆起部Bを含む。前記隆起部Bの上部面は前記凹部Aの前記底面403と平行である。前記凹部A及び前記隆起部Bは、半導体基板の凹部Aが配置される部分をエッチングして、隆起部Bが配置される部分を残して形成される。この場合、前記基板401は一体の基板である。

20

## 【0143】

前記基板401はセル領域 及び周辺回路領域 を含む。前記セル領域 にはメモリセルが配置される。前記セル領域 は前記凹部A及び前記隆起部Bを含む。前記周辺回路領域 には周辺回路が配置される。前記周辺回路領域 は前記隆起部Bを含む。

## 【0144】

前記基板401のセル領域 に対して説明する。

30

## 【0145】

前記基板401の前記セル領域 の前記凹部A上に互いに離隔された導電パターンGSL、WL1～WL4、SSLが配置される。前記導電パターンGSL、WL1～WL4、SSLは前記基板401の前記凹部A上に順に積層された接地選択ラインGSL、ワードラインWL1～WL4、及びストリング選択ラインSSLを含む。前記導電パターンGSL、WL1～WL4、SSLはゲート間絶縁膜410～414を挟んで互いに離隔されて配置される。例えば、前記接地選択ラインGSL、第1ゲート間絶縁膜410、第1ワードラインWL1、第2ゲート間絶縁膜411、第2ワードラインWL2、第3ゲート間絶縁膜412、第3ワードラインWL3、第4ゲート間絶縁膜413、第4ワードラインWL4、第5ゲート間絶縁膜414、及びストリング選択ラインSSLが順に積層されている。

40

## 【0146】

前記ストリング選択ラインSSL上にストリング選択絶縁膜415が配置される。前記絶縁膜410～414は前記基板401の前記凹部Aの前記底面403上の底部と、前記底部から前記第1側壁405上に延長される側壁部とを含む。前記導電パターンGSL、WL1～WL4、SSLは第1方向に延長されるライン形態であり得る。前記第1方向はIV-IV'の方向である。

## 【0147】

前記導電パターンGSL、WL1～WL4、SSLは前記凹部Aの前記底面403上に

50

配置された底部 B P を含む。前記底部 B P の長さは前記基板 4 0 1 の前記凹部 A から遠くなるほど短くなる。前記底部 B P は前記底面 4 0 3 と平行である。前記底部 B P は前記隆起部 B の上部面と平行である。

#### 【 0 1 4 8 】

前記導電パターン G S L 、 W L 1 ~ W L 4 、 S S L は前記底部 B P の一端から前記第 1 側壁 4 0 6 上に延長される (e x t e n d e d o v e r) コンタクト延長部 C T を含む。前記コンタクト延長部 C T の延長線は前記底面 4 0 3 と交差する。前記コンタクト延長部 C T の延長線は前記底面 4 0 3 と直角に交差することができる。前記コンタクト延長部 C T は前記基板 4 0 1 の前記凹部 A から距離が遠くなるほど長さが減少される。前記コンタクト延長部 C T の上部面は前記隆起部 B の上部面と同一平面にある。前記コンタクト延長部 C T が前記底部 B P となす角度は 9 0 ° であり得る。10

#### 【 0 1 4 9 】

前記ワードライン W L 1 ~ W L 4 のコンタクト延長部 C T 上に導電プラグが配置される。前記導電プラグはワードラインコンタクトプラグ C P であり得る。前記ワードライン W L 1 ~ W L 4 の各々は前記ワードラインコンタクトプラグ C P と電気的に接続される。前記ワードラインコンタクトプラグ C P は第 1 層間絶縁膜 4 8 0 を貫通する。前記ワードラインコンタクトプラグ C P 及び前記第 1 層間絶縁膜 4 8 0 上に第 1 導電ライン M L 1 が配置される。前記ワードラインコンタクトプラグ C P は前記第 1 導電ライン M L 1 と電気的に接続される。前記第 1 導電ライン M L 1 は前記第 1 方向と交差する第 2 方向に延長される。前記第 1 導電ライン M L 1 は前記ワードラインコンタクトプラグ C P を通じて前記ワードライン W L 1 ~ W L 4 と電気的に接続される。これと異なり、前記第 1 導電ライン M L 1 は前記ワードライン W L 1 ~ W L 4 と直接接続され得る。前記第 1 導電ライン M L 1 を覆う第 2 層間絶縁膜 4 9 0 が配置される。前記第 1 層間絶縁膜 4 8 0 及び前記第 2 層間絶縁膜 4 9 0 は同一の物質を含むことができる。20

#### 【 0 1 5 0 】

前記接地選択ライン G S L のコンタクト延長部 C T 上に導電プラグが配置される。前記導電プラグは接地選択コンタクトプラグ G C P であり得る。前記接地選択ライン G S L は前記接地選択コンタクトプラグ G C P と電気的に接続される。前記接地選択コンタクトプラグ G C P は第 1 層間絶縁膜 4 8 0 を貫通する。前記接地選択コンタクトプラグ G C P 及び前記第 1 層間絶縁膜 4 8 0 上に第 2 導電ライン M L 2 が配置される。前記接地選択コンタクトプラグ G C P は前記第 2 導電ライン M L 2 と電気的に接続される。前記第 2 導電ライン M L 2 は前記第 2 方向に延長される。前記第 2 導電ライン M L 2 は前記接地選択コンタクトプラグ G C P を通じて前記接地選択ライン G S L と電気的に接続される。これと異なり、前記第 2 導電ライン M L 2 は前記接地選択ライン G S L と直接接続され得る。前記第 2 層間絶縁膜 4 9 0 は前記第 2 導電ライン M L 2 を覆う。30

#### 【 0 1 5 1 】

前記ストリング選択ライン S S L のコンタクト延長部 C T 上に導電プラグが配置される。前記導電プラグはストリング選択コンタクトプラグ S C P であり得る。前記ストリング選択ライン S S L は前記ストリング選択コンタクトプラグ S C P と電気的に接続される。前記ストリング選択コンタクトプラグ S C P は第 1 層間絶縁膜 4 8 0 及び第 2 層間絶縁膜 4 9 0 を貫通する。前記ストリング選択コンタクトプラグ S C P 及び前記第 1 層間絶縁膜 4 8 0 上に第 3 導電ライン M L 3 が配置される。前記ストリング選択コンタクトプラグ S S L は前記第 3 導電ライン M L 3 と電気的に接続される。前記第 3 導電ライン M L 3 は前記第 1 方向に延長される。40

#### 【 0 1 5 2 】

前記基板 4 0 1 の前記凹部 A の前記底面 4 0 3 から上部に延長される活性部 A P が配置される。前記活性部 A P は前記基板 4 0 1 に垂直に延長される。前記活性部 A P は前記導電パターン G S L 、 W L 1 ~ W L 4 、 S S L を貫通する。これと異なり、図 13 を参照して説明したように、前記活性部 A P は前記導電パターン G S L 、 W L 1 ~ W L 4 、 S S L の側面と対向する。前記活性部 A P の一端が前記共通ソース領域 4 0 2 に電気的に接続さ50

れる。前記活性部 A P の他端にドレイン領域 4 2 3 が配置される。前記ドレイン領域 D は高濃度のドーパントでドーピングされた領域であり得る。前記活性部 A P は単結晶半導体を含む。

#### 【 0 1 5 3 】

前記活性部 A P の前記ドレイン領域 D 上にビットライインコンタクトプラグ B L C P が配置される。前記ビットライインコンタクトプラグ B L C P は前記ドレイン領域 4 2 3 と電気的に接続され、前記第 1 層間絶縁膜 4 8 0 及び第 2 層間絶縁膜 4 9 0 を貫通する。前記ビットライインコンタクトプラグ B L C P の上部にビットライイン B L が配置される。前記ビットライイン B L は前記ビットライインコンタクトプラグ B L C P を通じて前記活性部 A P の前記ドレイン領域 4 2 3 と接続される。これと異なり、前記ビットライイン B L は前記ドレイン領域 4 2 3 と直接接続され得る。前記ビットライイン B L は前記第 2 方向に延長される。前記ビットライイン B L は前記ストリング選択ライン S S L と交差する。

#### 【 0 1 5 4 】

前記活性部 A P の側壁と前記導電パターン G S L 、 W L 1 ~ W L 4 、 S S L との間に情報貯蔵膜 4 4 0 が介在される。前記情報貯蔵膜 4 4 0 は前記導電パターン G S L 、 W L 1 ~ W L 4 、 S S L と前記活性部 A P の側壁との間に配置される。前記情報貯蔵膜 4 4 0 は前記導電パターン G S L 、 W L 1 ~ W L 4 、 S S L と前記絶縁膜 4 1 0 ~ 4 1 5 との間に配置される。

#### 【 0 1 5 5 】

本発明の第 4 実施形態に係る情報貯蔵膜 4 2 0 は図 1 2 または図 1 3 を参照して説明した情報貯蔵膜であり得る。

#### 【 0 1 5 6 】

前記周辺回路領域 に対して説明する。

#### 【 0 1 5 7 】

前記周辺回路領域 の前記隆起部 B の上部面上に周辺回路が配置される。前記隆起部 B の上部面上にゲート絶縁膜 4 7 4 が配置される。前記ゲート絶縁膜 4 7 4 はシリコン酸化膜を含む。前記ゲート絶縁膜 4 7 4 は前記半導体基板 4 0 1 を熱酸化して形成されたことを含む。前記ゲート絶縁膜 4 7 4 上にゲート電極 4 7 6 が配置される。前記ゲート電極 4 7 6 はドーピングされたポリシリコン、金属及び金属シリサイドの中のいずれか 1 つを含む。前記ゲート電極 4 7 6 の両側壁上にゲートスペーサ 4 7 8 が配置される。前記ゲート電極 4 7 6 の両側壁の前記隆起部 B にソースドレイン領域 4 7 3 が配置される。前記ソースドレイン領域 4 7 3 は高濃度のドーパントでドーピングされた領域であり得る。

#### 【 0 1 5 8 】

前記ゲート電極 4 7 6 及びソースドレイン領域 4 7 3 上に第 1 層間絶縁膜 4 8 0 を貫通する周辺回路コンタクトプラグ P C P が配置される。前記周辺回路コンタクトプラグ P C P 上に第 4 導電ライン M L 4 が配置される。前記第 4 導電ライン M L 4 上に第 2 層間絶縁膜 4 9 0 が配置される。

#### 【 0 1 5 9 】

本発明の第 4 実施形態の変形例を説明する。図 2 0 は、本発明の第 4 実施形態の変形例を説明するための図であり、図 1 8 の I V - I V ' に沿って切断した断面図である。

#### 【 0 1 6 0 】

図 1 8 及び図 2 0 を参照すると、基板 4 0 0 が提供される。前記基板 4 0 0 内に共通ソース領域 4 0 2 が配置される。前記基板 4 0 0 は凹部 A を含む。前記凹部 A は底面 4 0 3 と第 1 側壁 4 0 5 とを含む。前記基板 4 0 0 は前記第 1 側壁 4 0 5 から延長された隆起部 B を含む。前記隆起部 B の上部面は前記凹部 A の前記底面 4 0 3 と平行である。前記隆起部 B は前記基板 4 0 0 上に配置された絶縁膜 4 0 4 によって定義される。

#### 【 0 1 6 1 】

前記基板 4 0 0 はセル領域 及び周辺回路領域 を含む。前記セル領域 にはメモリセルが配置される。前記周辺回路領域 には周辺回路が配置される。

#### 【 0 1 6 2 】

10

20

30

40

50

前記基板 400 のセル領域 に対して説明する。

【0163】

前記セル領域 の前記凹部Aには図19を参照して説明したメモリセルが配置される。

【0164】

前記基板 400 の周辺回路領域 に対して説明する。

【0165】

前記周辺回路領域 の前記隆起部Bの上部面上に周辺回路が配置される。前記絶縁膜404の上部面上に半導体膜472が配置される。前記半導体膜472はポリシリコン、結晶質シリコン、及び単結晶シリコンを含むその他半導体物質であり得る。前記半導体膜472上にゲート絶縁膜474が配置される。前記ゲート絶縁膜474はシリコン酸化膜を含む。前記ゲート絶縁膜474は前記半導体膜472を熱酸化して形成されたことを含む。前記ゲート絶縁膜474上にゲート電極476が配置される。前記ゲート電極476はドーピングされたポリシリコン、金属、及び金属シリサイドの中のいずれか1つを含む。前記ゲート電極476の両側壁上にスペーサ478が配置される。前記ゲート電極476の両側壁の前記半導体膜472にソースドレイン領域473が配置される。前記ソースドレイン領域473は高濃度のドーパントでドーピングされた領域であり得る。

10

【0166】

前記ゲート電極476及びソースドレイン領域473上に第1層間絶縁膜480を貫通する周辺回路コンタクトプラグPCPが配置される。前記周辺回路コンタクトプラグPCP上に第4導電ラインML4が配置される。前記第4導電ラインML4上に第2層間絶縁膜490が配置される。

20

【0167】

本発明の第4実施形態の他の変形例に係る半導体素子を説明する。図21は、本発明の第4実施形態の他の変形例を説明するための図であり、図18のI-V - I-V'に沿って切断した断面図である。

【0168】

図18及び図21を参照すると、基板401が提供される。前記基板401内に共通ソース領域402が配置される。前記基板401は凹部Aを含む。前記凹部Aは底面403と第1側壁405とを含む。前記第1側壁405は前記凹部Aの前記底面403に傾いている。例えば、前記第1側壁405は前記底面403に対して90°超過130°以下の角度を有することができる。前記前記基板401は前記第1側壁405から延長された隆起部Bを含む。前記隆起部Bの上部面は前記凹部Aの前記底面403と平行である。基板の凹部及び隆起部はエッチング工程を通じて定義される。これと異なり、図20を参照して説明したように、前記隆起部Bは前記基板401上に配置された絶縁膜404によって定義される。

30

【0169】

前記基板401はセル領域 及び周辺回路領域 を含む。前記セル領域 にはメモリセルが配置される。前記周辺回路領域 は周辺回路を含む。

【0170】

前記基板401のセル領域 に対して説明する。

40

【0171】

前記セル領域 には図19を参照して説明したメモリセルが配置される。前記導電パターンGSL、WL1 ~ WL4、SSLのコンタクト延長部CTは前記底面403に対して傾いた勾配を有する。導電パターンGSL、WL1 ~ WL4、SSLのコンタクト延長部CTが前記底面403となす角度は前記第1側壁406が前記底面403となす角度と同一であり得る。

【0172】

前記基板401の周辺回路領域 に対して説明する。

【0173】

前記基板401の周辺回路領域 には図19を参照して説明した周辺回路が配置される

50

。これと異なり、上述ように、基板が図20を参照して説明した基板の場合、半導体膜472が追加される。

#### 【0174】

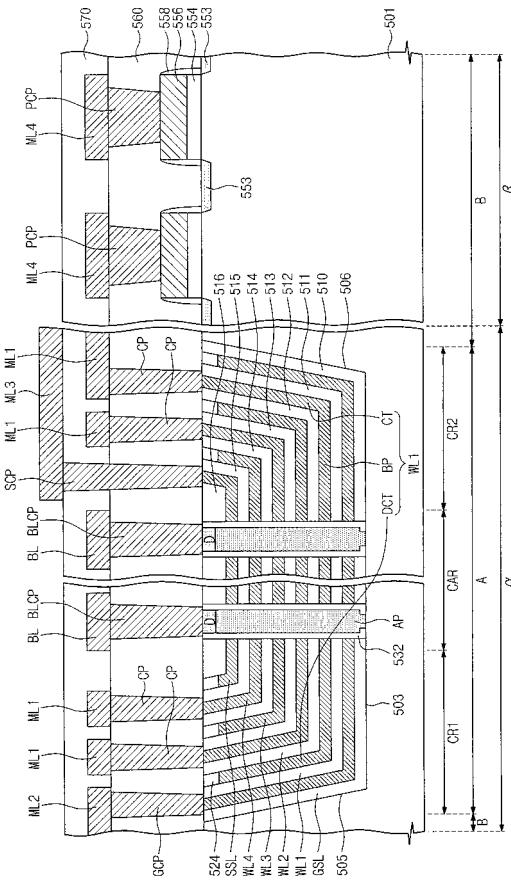

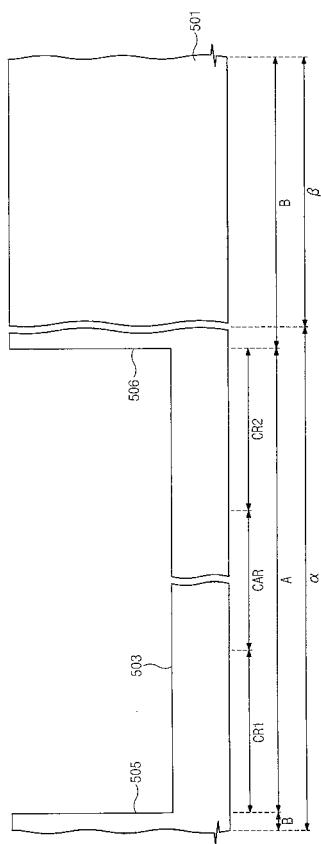

本発明の第5実施形態に係る半導体素子を説明される。図22及び図23は本発明の第5実施形態に係る半導体素子を説明するための平面図であり、図24は、図22及び図23のV-V'に沿って切断した断面図である。

#### 【0175】

図22、図23、及び図24を参照すると、基板501が提供される。前記基板501は半導体基盤の半導体基板である。前記基板501はウェル(well)を含む。前記ウェルは第1導電型のドーパントを含む。前記基板501内に共通ソース領域502が配置される。前記共通ソース領域502は前記基板501のセル領域内に平板形態(plate form)に配置される。前記共通ソース領域502は高濃度のドーパントを含むことができる。前記共通ソース領域502に含まれたドーパントは前記ウェルに含まれたドーパントと異なる導電型の第2導電型であり得る。例えば、前記ウェルがp型ドーパントを含む場合、前記共通ソース領域502は高濃度のn型ドーパントを含む。

10

#### 【0176】

前記基板501は凹部Aを含む。前記凹部Aは底面503と互いに対向する第1側壁505及び第2側壁506を含む。前記基板501は前記第1側壁505及び第2側壁506から延長された隆起部Bを含む。前記隆起部Bの上部面は前記凹部Aの前記底面503と平行である。前記凹部A及び前記隆起部Bは、半導体基板の凹部Aが配置される部分をエッチングして、隆起部Bが配置される部分を残して形成される。この場合、前記基板501は一体の基板である。

20

#### 【0177】

前記基板501はセル領域及び周辺回路領域を含む。前記セル領域にはメモリセルが配置される。前記セル領域は前記凹部A及び前記隆起部Bを含む。前記周辺回路領域には周辺回路が配置される。前記周辺回路領域は前記隆起部Bを含む。

20

#### 【0178】

前記基板501のセル領域に対して説明する。

前記セル領域は前記凹部Aの前記第1側壁505と隣接した第1コンタクト領域CR1、及び前記第2側壁506と隣接した第2コンタクト領域CR2を含む。前記第1コンタクト領域CR1と前記第2コンタクト領域CR2との間にセルアレイ領域CARが配置される。前記第1コンタクト領域CR1及び第2コンタクト領域CR2は、前記セルアレイ領域CARを挟んで互いに離隔されている。

30

#### 【0179】

前記基板501上に互いに離隔された導電パターンGSL、WL1~WL4、SSLが配置される。前記導電パターンGSL、WL1~WL4、SSLは前記基板501の前記凹部A上に順に積層された接地選択ラインGSL、ワードラインWL1~WL4、及びストリング選択ラインSSLを含む。前記導電パターンGSL、WL1~WL4、SSLはゲート間絶縁膜511~515を挟んで互いに離隔されて配置される。例えば、前記接地選択ラインGSL、第1ゲート間絶縁膜511、第1ワードラインWL1、第2ゲート間絶縁膜512、第2ワードラインWL2、第3ゲート間絶縁膜513、第3ワードラインWL3、第4ゲート間絶縁膜514、第4ワードラインWL4、第5ゲート間絶縁膜515、及びストリング選択ラインSSLが順に積層されている。前記絶縁膜510~516は前記基板501の前記凹部Aの前記底面503上の底部と、前記底部から前記第1側壁505及び前記第2側壁506上に延長される側壁部とを含む。

40

#### 【0180】

前記基板501の前記凹部Aの前記底面503、第1及び第2側壁505、506と前記接地選択ラインGSLとの間に接地選択絶縁膜510が配置される。前記ストリング選択ラインSSL上にストリング選択絶縁膜516が配置される。前記ワードラインWL1~WL4は前記凹部Aと平行な平板形態であり得る。

50

**【 0 1 8 1 】**

前記導電パターン G S L、W L 1 ~ W L 4、S S L は前記凹部 A の前記底面 5 0 3 上に配置された底部 B P を含む。前記底部 B P の長さは前記基板 5 0 1 の前記凹部 A から遠くなるほど短くなる。前記底部 B P は前記底面 5 0 3 と平行である。前記底部 B P は前記隆起部 B の上部面と平行である。

**【 0 1 8 2 】**

前記導電パターン G S L、W L 1 ~ W L 4、S S L は前記底部 B P の一端から前記第 1 側壁 5 0 5 または前記第 2 側壁 5 0 6 の中の 1 つの側壁上に延長される (e x t e n d e d o v e r) コンタクト延長部 C T を含む。前記導電パターン G S L、W L 1 ~ W L 4、S S L の中のいずれか 1 つの導電パターンのコンタクト延長部が配置されるコンタクト領域と、前記いずれか 1 つの導電パターンと隣接した他の導電パターンのコンタクト延長部が配置されるコンタクト領域は異なることができる。例えば、前記接地選択ライン G S L のコンタクト延長部 C T が前記第 1 コンタクト領域 C R 1 に配置される場合、前記接地選択ライン G S L と隣接した第 1 ワードライン W L 1 のコンタクト延長部 C T は前記第 2 コンタクト領域 C R 2 に配置される。前記コンタクト延長部 C T の延長線は前記底面 5 0 3 と交差する。前記コンタクト延長部 C T の延長線は前記底面 5 0 3 と直角に交差することができる。前記コンタクト延長部 C T は前記基板 5 0 1 の前記凹部 A から距離が遠くなるほど長さが減少される。前記コンタクト延長部 C T の上部面は前記隆起部 B の上部面と同一平面にある。前記コンタクト延長部 C T が前記底部 B P となす角度は 9 0 ° であり得る。

10

20

**【 0 1 8 3 】**

前記導電パターン G S L、W L 1 ~ W L 4、S S L は前記底面 5 0 3 上の前記底部 B P の他端から前記第 1 側面 5 0 5 及び前記第 2 側面 5 0 6 の中の他の 1 つの側面上に延長される (e x t e n d e d o v e r) ダミー延長部 D C T を含む。前記導電パターン G S L、W L 1 ~ W L 4、S S L の中のいずれか 1 つの導電パターンのダミー延長部が配置されるコンタクト領域と、前記いずれか 1 つの導電パターンと隣接した他の導電パターンのダミー延長部が配置されるコンタクト領域は異なることができる。例えば、前記ストリング選択ライン S S L のダミー延長部 D C T が前記第 1 コンタクト領域 C R 1 に配置される場合、前記ストリング選択ライン S S L と隣接した前記第 4 ワードライン W L 4 のダミー延長部 D C T は前記第 2 コンタクト領域 C R 2 に配置される。前記導電パターン G S L、W L 1 ~ W L 4、S S L の各々は 1 つのコンタクト延長部 C T と 1 つのダミー延長部 D C T を含む。前記導電パターン G S L、W L 1 ~ W L 4、S S L の中の 1 つの導電パターンで、前記ダミー延長部 D C T の長さは前記コンタクト延長部 C T の長さより短いことがある。前記コンタクト延長部 C T は互いに隣接したダミー延長部 D C T の間に配置される。ダミー延長部 D C T と隣接したコンタクト延長部 C T はその間に介在された絶縁膜の側壁部によって離隔される。

30

**【 0 1 8 4 】**

前記ダミー延長部 D C T 上にダミー絶縁パターン 5 2 4 が配置される。前記ダミー絶縁パターン 5 2 4 の上部面は前記隆起部 B の上部面と同一平面にある。前記ダミー絶縁パターン 5 2 4 の上部面は前記ストリング選択絶縁膜 5 1 6 の上部面と同一平面にある。前記ダミー絶縁パターン 5 2 4 の側壁は前記ダミー延長部 D C T の側壁と同一平面にある。前記ダミー絶縁パターン 5 2 4 は前記絶縁膜 5 1 0 ~ 5 1 6 と同一の物質を含むことができる。

40

**【 0 1 8 5 】**

前記ワードライン W L 1 ~ W L 4 のコンタクト延長部 C T 上に導電プラグが配置される。前記導電プラグはワードラインコンタクトプラグ C P であり得る。前記ワードライン W L 1 ~ W L 4 の各々は前記ワードラインコンタクトプラグ C P と電気的に接続される。前記ワードラインコンタクトプラグ C P の幅は前記ワードライン W L 1 ~ W L 4 のコンタクト延長部 C T の上部面の幅より広いことがある。前記ワードラインコンタクトプラグ C P は前記ワードライン W L 1 ~ W L 4 のコンタクト延長部 C T と隣接したダミー延長部 D C

50

Tの間の幅より広いことがある。前記ワードラインコンタクトプラグC Pは第1層間絶縁膜5 6 0を貫通する。前記ワードラインコンタクトプラグC P及び前記第1層間絶縁膜5 6 0上に第1導電ラインM L 1が配置される。前記ワードラインコンタクトプラグC Pは前記第1導電ラインM L 1と電気的に接続される。前記第1導電ラインM L 1の一部は第1方向に延長される。前記第1導電ラインM L 1の残りの一部は前記第1方向の反対になる第2方向に延長される。例えば、前記基板5 0 1から奇数層に配置されたワードラインW L 2、W L 4と接続された第1導電ラインM L 1は前記第1方向に延長され、前記基板5 0 1から偶数層に配置されたワードラインW L 1、W L 3と接続された第1導電ラインM L 1は前記第2方向に延長される。前記第1方向はV - V'方向である。前記第1導電ラインM L 1は前記ワードラインコンタクトプラグC Pを通じて前記ワードラインW L 1 ~ W L 4と電気的に接続される。これと異なり、前記第1導電ラインM L 1は前記ワードラインW L 1 ~ W L 4と直接接続され得る。前記第1導電ラインM L 1を覆う第2層間絶縁膜5 7 0が配置される。前記第1層間絶縁膜5 6 0及び前記第2層間絶縁膜5 7 0は同一の物質を含むことができる。

10

## 【0186】

前記接地選択ラインG S Lのコンタクト延長部C T上に導電プラグが配置される。前記導電プラグは接地選択コンタクトプラグG C Pであり得る。前記接地選択ラインG S Lは前記接地選択コンタクトプラグG C Pと電気的に接続される。前記接地選択コンタクトプラグG C Pの幅は前記接地選択ラインG S Lのコンタクト延長部C Tの上部面の幅より広いことがある。前記接地選択コンタクトプラグG C Pは第1層間絶縁膜5 6 0を貫通する。前記接地選択コンタクトプラグG C P及び前記第1層間絶縁膜5 6 0上に第2導電ラインM L 2が配置される。前記接地選択コンタクトプラグG C Pは前記第2導電ラインM L 2と電気的に接続される。前記第2導電ラインM L 2は前記第1方向に延長される。前記第2導電ラインM L 2は前記接地選択コンタクトプラグG C Pを通じて前記接地選択ラインG S Lと電気的に接続される。これと異なり、前記第2導電ラインM L 2は前記接地選択ラインG S Lと直接接続され得る。前記第2層間絶縁膜5 7 0は前記第2導電ラインM L 2を覆う。

20

## 【0187】

前記ストリング選択ラインS S Lのコンタクト延長部C T上に導電プラグが配置される。前記導電プラグはストリング選択コンタクトプラグS C Pであり得る。前記ストリング選択ラインS S Lは前記ストリング選択コンタクトプラグS C Pと電気的に接続される。前記ストリング選択コンタクトプラグS C Pの幅は前記ストリング選択ラインS S Lのコンタクト延長部C Tの上部面の幅より広いことがある。前記ストリング選択コンタクトプラグS C Pは第1層間絶縁膜5 6 0及び第2層間絶縁膜5 7 0を貫通する。前記ストリング選択コンタクトプラグS C P及び前記第1層間絶縁膜5 6 0上に第3導電ラインM L 3が配置される。前記ストリング選択コンタクトプラグS S Lは前記第3導電ラインM L 3と電気的に接続される。前記第3導電ラインM L 3は前記第2方向に延長される。前記第2層間絶縁膜5 7 0は前記第3導電ラインM L 3を覆う。図20を参照すると、複数のストリング選択ラインS S Lが前記凹部A内に配置される。そして、互いに隣接したストリング選択ラインS S Lの第3導電ラインM L 3は他の方向に延長される。

30

## 【0188】

前記導電ラインM L 2、M L 1、M L 3は前記セルアレイ領域C A Rを挟んで前記第1方向及び前記第2方向に分けて延長される。例えば、コンタクト延長部C Tが前記第1コンタクト領域C R 1に配置される導電パターンG S L、W L 2、W L 4と接続された導電ラインM L 2、M L 1は前記第1方向に延長され、コンタクト延長部C Tが前記第2コンタクト領域C R 2に配置される導電パターンW L 1、W L 3、S S Lと接続された導電ラインM L 1、M L 3は前記第2方向に延長される。

40

## 【0189】

前記凹部Aの前記底面5 0 3から上部に延長される活性部A Pが配置される。前記活性部A Pは前記基板5 0 1に垂直に延長される。前記活性部A Pは前記導電パターンG S L

50

、WL1～WL4、SSLを貫通して前記活性部APの一端が前記共通ソース領域502に電気的に接続される。前記活性部APの他端にドレイン領域Dが配置される。前記ドレイン領域Dは高濃度のドーパントでドーピングされた領域であり得る。前記活性部APは単結晶半導体を含む。

#### 【0190】

前記活性部APの前記ドレイン領域D上にビットラインコンタクトプラグBLCPが配置される。前記ビットラインコンタクトプラグBLCPは前記ドレイン領域Dと電気的に接続され、前記第1層間絶縁膜560を貫通する。前記ビットラインコンタクトプラグBLCPの上部にビットラインBLが配置される。前記ビットラインBLは前記ビットラインコンタクトプラグBLCPを通じて前記活性部APの前記ドレイン領域Dと接続される。これと異なり、前記ビットラインBLは前記ドレイン領域Dに直接接続され得る。前記ビットラインBLは前記第1方向及び前記第2方向と交差する第3方向に延長される。前記第3方向は前記第1及び第2方向と直角に交差することができる。前記ビットラインBLは前記ストリング選択ラインSSLと交差する。

#### 【0191】

前記活性部APの側壁と前記導電パターンGSL、WL1～WL4、SSLとの間に情報貯蔵膜532が介在される。前記情報貯蔵膜532は前記導電パターンGSL、WL1～WL4、SSLを貫通するシリンドータイプに配置される。前記情報貯蔵膜532は前記活性部APを取り囲むように配置される。前記情報貯蔵膜532は前記活性部APの側壁と前記導電パターンGSL、WL1～WL4、SSL及び前記絶縁膜510～516との間に配置される。

本発明の第5実施形態に係る情報貯蔵膜532は図6を参照して説明した情報貯蔵膜であり得る。

#### 【0192】

前記基板501の周辺回路領域に対して説明する。

#### 【0193】

前記周辺回路領域の前記隆起部Bの上部面上に周辺回路が配置される。前記隆起部Bの上部面上にゲート絶縁膜554が配置される。前記ゲート絶縁膜554はシリコン酸化膜を含む。前記ゲート絶縁膜554は前記隆起部Bの上部面を熱酸化して形成されたことを含む。前記ゲート絶縁膜554上にゲート電極556が配置される。前記ゲート電極556はドーピングされたポリシリコン、金属、及び金属シリサイドの中のいずれか1つを含む。前記ゲート電極556の両側壁上にスペーサ558が配置される。前記ゲート電極556の両側壁の前記隆起部Bにソースドレイン領域553が配置される。前記ソースドレイン領域553は高濃度のドーパントでドーピングされた領域であり得る。

#### 【0194】

前記ゲート電極556及びソースドレイン領域553上に第1層間絶縁膜560を貫通する周辺回路コンタクトプラグPCPが配置される。前記周辺回路コンタクトプラグPCP上に第4導電ラインML4が配置される。前記第4導電ラインML4上に第2層間絶縁膜570が配置される。

#### 【0195】

本発明の第5実施形態の変形例を説明する。図25は、本発明の第5実施形態の変形例を説明するための図であり、図22及び図23のV-V'に沿って切断した断面図である。

#### 【0196】

図25、図22、及び図23を参照すると、基板500が提供される。前記基板500内に共通ソース領域502が配置される。前記基板500は凹部Aを含む。前記凹部Aは底面503と互いに対向する第1側壁505及び第2側壁506を含む。前記基板500は前記第1側壁505及び第2側壁506から延長された隆起部Bを含む。前記隆起部Bの上部面は前記凹部Aの前記底面503と平行である。前記隆起部Bは前記基板500上に配置された絶縁膜504によって定義される。

10

20

30

40

50

## 【0197】

前記基板 501 はセル領域 及び周辺回路領域 を含む。前記セル領域 にはメモリセルが配置される。前記周辺回路領域 に周辺回路が配置される。

## 【0198】

前記基板 500 のセル領域 に対して説明する。

## 【0199】

前記セル領域 は前記凹部 A の前記第 1 側壁 505 と隣接した第 1 コンタクト領域 C R 1、及び前記第 2 側壁 506 と隣接した第 2 コンタクト領域 C R 2 を含む。前記基板 500 のセル領域 には図 24 を参照して説明したメモリセルが配置される。

## 【0200】

前記基板 500 の周辺回路領域 に対して説明する。

## 【0201】

前記周辺回路領域 の前記隆起部 B の上部面上に周辺回路が配置される。前記絶縁膜 504 の上部面上に半導体膜 552 が配置される。前記半導体膜 552 はポリシリコン、結晶質シリコン及び単結晶シリコンを含むその他半導体物質であり得る。前記半導体膜 552 上にゲート絶縁膜 554 が配置される。前記ゲート絶縁膜 554 はシリコン酸化膜を含む。前記ゲート絶縁膜 554 は前記半導体膜 552 を熱酸化して形成されたことを含む。前記ゲート絶縁膜 554 上にゲート電極 556 が配置される。前記ゲート電極 556 はドーピングされたポリシリコン、金属、及び金属シリサイドの中のいずれか 1 つを含む。前記ゲート電極 556 の両側壁上にスペーサ 558 が配置される。前記ゲート電極 556 の両側壁の前記半導体膜 552 にソースドレイン領域 553 が配置される。前記ソースドレイン領域 553 は高濃度のドーパントでドーピングされた領域であり得る。

10

20

## 【0202】

前記ゲート電極 556 及びソースドレイン領域 553 上に第 1 層間絶縁膜 560 を貫通する周辺回路コンタクトプラグ P C P が配置される。前記周辺回路コンタクトプラグ P C P 上に第 4 導電ライン M L 4 が配置される。前記第 4 導電ライン M L 4 上に第 2 層間絶縁膜 570 が配置される。

30

## 【0203】

本発明の第 5 実施形態の他の変形例に係る半導体素子を説明する。図 26 は、本発明の第 5 実施形態の他の変形例を説明するための図であり、図 22 及び図 23 の V - V' に沿って切断した断面図である。

## 【0204】

図 22、図 23、及び図 26 を参照すると、基板 501 が提供される。前記基板 501 内に共通ソース領域 502 が配置される。前記基板 501 は凹部 A を含む。前記凹部 A は底面 503 と互いに対向する第 1 側壁 505 及び第 2 側壁 506 を含む。前記第 1 側壁 505 及び前記第 2 側壁 506 の中のいずれか 1 つの側壁は前記凹部 A の前記底面 503 に傾いている。例えば、前記第 1 側壁 505 及び前記第 2 側壁 506 は前記底面 503 に対して 50° から 90° の角度を有することができる。前記第 1 側壁 505 が前記底面 503 に対して有する勾配と前記第 2 側壁 506 が前記底面 503 に対して有する勾配は同一であり得る。これと異なり、前記第 1 側壁 505 が前記底面 503 に対して有する勾配と前記第 2 側壁 506 が前記底面 503 に対して有する勾配は異なることができる。前記基板 501 は前記第 1 側壁 505 及び第 2 側壁 506 から延長された隆起部 B を含む。前記隆起部 B の上部面は前記凹部 A の前記底面 503 と平行である。基板の凹部 A 及び隆起部 B はエッチング工程を通じて定義される。これと異なり、図 25 を参照して説明したように、前記隆起部 B は前記基板 500 上に配置された絶縁膜 504 によって定義される。

40

## 【0205】

前記基板 501 はセル領域 及び周辺回路領域 を含む。前記セル領域 にはメモリセルが配置される。前記周辺回路領域 は周辺回路を含む。

## 【0206】

前記基板 501 のセル領域 に対して説明する。

50

## 【0207】

前記セル領域 は前記凹部 A の前記第 1 側壁 505 と隣接した第 1 コンタクト領域 C R 1 、及び前記第 2 側壁 506 と隣接した第 2 コンタクト領域 C R 2 を含む。図 24 を参照して説明したメモリセルが配置される。前記導電パターン G S L 、 W L 1 ~ W L 4 、 S S L の中の 1 つの導電パターンで、コンタクト延長部 C T 及びダミー延長部 D C T は底部 B P に対して傾いた勾配を有する。

## 【0208】

前記コンタクト延長部 C T が配置されたコンタクト領域と隣接した側壁が前記底面 503 となす角度は、前記コンタクト延長部 C T が底部 B P となす角度と同一であり得る。第 1 ワードライン W L 1 を例にとって、コンタクト延長部 C T が前記底部 B P に対して有する勾配は、前記第 2 側壁 506 が前記底面 503 に対して有する勾配と同一であり得る。前記第 1 側壁 505 及び前記第 2 側壁 506 が前記底面 503 に対して有する勾配が各々異なる場合、1 つの導電パターンで、コンタクト延長部 C T が底部 B P に対して有する勾配は、ダミー延長部 D C T が底部 B P に対して有する勾配と異なることができる。

10

## 【0209】

前記基板 501 の周辺回路領域 に対して説明する。

## 【0210】

前記基板 501 の周辺回路領域 には図 24 を参照して説明した周辺回路が配置される。これと異なり、上述のように、基板が図 25 を参照して説明した基板の場合、半導体膜 552 が追加される。

20

## 【0211】

本発明の第 5 実施形態の形成方法を説明する。図 27 ~ 図 34 は、本発明の第 5 実施形態の形成方法を説明するための断面図である。

## 【0212】

図 27 を参照すると、基板 501 が提供される。前記基板 501 は凹部 A を含む。前記凹部 A は底面 503 と、互いに対向する第 1 側壁 505 と、第 2 側壁 506 とを含む。前記基板 501 は前記第 1 側壁 505 及び第 2 側壁 506 から延長された隆起部 B を含む。前記隆起部 B の上部面は前記凹部 A の前記底面 503 と平行である。前記基板 501 の前記凹部 A 及び前記隆起部 B を形成することは、凹部 A が形成される部分の半導体基板をエッチングして、隆起部 B が形成される部分の半導体基板を残すことを含む。

30

## 【0213】

前記基板 501 はセル領域 及び周辺回路領域 を含む。前記セル領域 にはメモリセルが配置される。前記セル領域 は前記凹部 A 及び前記隆起部 B を含む。前記周辺回路領域 は周辺回路を含む。前記周辺回路領域 は前記隆起部 B を含む。

## 【0214】

前記セル領域 は前記凹部 A の前記第 1 側壁 505 と隣接した第 1 コンタクト領域 C R 1 、及び前記第 2 側壁 506 と隣接した第 2 コンタクト領域 C R 2 を含む。前記第 1 コンタクト領域 C R 1 と前記第 2 コンタクト領域 C R 2 との間にセルアレイ領域 C A R が配置される。前記第 1 コンタクト領域 C R 1 及び第 2 コンタクト領域 C R 2 は、前記セルアレイ領域 C A R を挟んで互いに離隔されている。

40

## 【0215】

前記基板 501 は単結晶構造の半導体（例えば、P 型シリコンウェーハ）であり得る。前記基板 501 はウェルを含む。前記ウェルは前記基板 501 内にドーパントを注入させて形成される。前記ドーパントはイオン注入またはプラズマ注入を含むドーピング工程によって前記基板 501 内に注入される。前記基板 501 の上部面に共通ソース領域 502 が提供される。前記共通ソース領域 502 は前記ウェル内にドーパントをドーピングすることによって形成される。前記共通ソース領域 502 は前記ウェルと異なる導電型のドーパントを含むことができる。例えば、前記ウェルは p 型ドーパントを含み、前記共通ソース領域 502 は n 型ドーパントを含む。

## 【0216】

50

図28を参照すると、前記基板501の前記凹部A上に導電パターンGSL、WL1～WL4、SSL及び絶縁膜510～516が交互に形成される。例えば、前記基板501上に接地選択絶縁膜510、接地選択ラインGSL、第1ゲート間絶縁膜511、第1ワードラインWL1、第2ゲート間絶縁膜512、第2ワードラインWL2、第3ゲート間絶縁膜513、第3ワードラインWL3、第4ゲート間絶縁膜514、第4ワードラインWL4、第5ゲート間絶縁膜515、ストリング選択ラインSSL、及びストリング選択絶縁膜516が順に蒸着される。前記導電パターンGSL、WL1～WL4、SSL及び前記絶縁膜510～516は前記隆起部Bの上部面上にも形成される。前記導電パターンGSL、WL1～WL4、SSLは金属または多結晶半導体物質を含む。前記絶縁膜510～516はシリコン酸化膜を含む。

10

## 【0217】

前記隆起部Bの上部面をエッチング停止膜としてエッチング工程が実行される。前記平坦化工程はエッチバックまたは化学機械的研磨(CMP)の中のいずれか1つの方法によって実行される。前記エッチング工程によって、前記隆起部Bの上部面上に形成された導電パターンGSL、WL1～WL4、SSL及び絶縁膜510～516が除去される。

## 【0218】

前記導電パターンGSL、WL1～WL4、SSLは前記凹部Aの前記底面503上に配置された底部BPを含む。前記導電パターンGSL、WL1～WL4、SSLは前記底部BPの一端から前記第1側壁505または前記第2側壁506の中の1つの側壁上に延長される(extended over)コンタクト延長部CTを含む。前記導電パターンGSL、WL1～WL4、SSLの中のいずれか1つの導電パターンのコンタクト延長部が配置されるコンタクト領域と、前記いずれか1つの導電パターンと隣接した他の導電パターンのコンタクト延長部が配置されるコンタクト領域は異なることができる。前記コンタクト延長部CTの露出された上部面は前記隆起部Bの上部面と同一平面にある。

20

## 【0219】

前記導電パターンGSL、WL1～WL4、SSLは前記底面503上の前記底部BPの他端から前記第1側面505及び前記第2側面506の中の他の1つの側面上に延長される(extended over)ダミー延長部DCTを含む。前記導電パターンGSL、WL1～WL4、SSLの中のいずれか1つの導電パターンのダミー延長部が配置されるコンタクト領域と、前記いずれか1つの導電パターンと隣接した導電パターンのダミー延長部が配置されるコンタクト領域は異なることができる。前記導電パターンGSL、WL1～WL4、SSLの各々は1つのコンタクト延長部CTと1つのダミー延長部DCTとを含む。

30

## 【0220】

露出された前記コンタクト延長部CTの上部面を覆うマスクパターン520が形成される。前記マスクパターン520はダミー延長部DCTを露出させる。前記マスクパターン520を形成することは、前記基板501上にマスク膜を形成し、前記マスク膜をパテニングすることを含む。前記マスクパターン520は前記導電パターンGSL、WL1～WL4、SSL及び前記絶縁膜510～516に対してエッチング選択比を有する物質を含む。例えば、前記マスクパターン520はシリコン窒化膜またはフォトレジストパターンを含む。

40

## 【0221】

図29を参照すると、前記マスクパターン520をエッチングマスクとして用いて、前記マスクパターン520によって露出されたダミー延長部DCTの一部がエッチングされる。前記ダミー延長部DCTの一部がエッチングされ、ダミーリセス部522が形成される。前記ダミー延長部DCTの長さは前記コンタクト延長部CTの長さより短いことがある。前記ダミーリセス部522によって前記絶縁膜510～516の側壁部の一部が露出される。前記ダミー延長部DCTをエッチングすることは、前記導電パターンGSL、WL1～WL4、SSLに対するエッチング率が前記マスクパターン520及び前記絶縁膜510～516より高いエッチングレシピを利用することができる。前記マスクパターン

50

520が除去される。

【0222】

前記ストリング選択ラインSSLがパターニングされ、第1方向に延長されるライン形態で形成される。前記第1方向はV-V'方向である。

【0223】

図30を参照すると、前記ダミーリセス部522を埋め込むダミー絶縁パターン524が形成される。前記ダミー絶縁パターン524を形成することは、前記基板501上にダミー絶縁膜を形成し、前記隆起部Bの上部面または前記ストリング選択絶縁膜516の上部面をエッチング停止膜として平坦化工程を実行することを含む。前記ダミー絶縁パターン524の上部面は前記隆起部Bの上部面と同一平面にある。前記ダミー絶縁パターン524の上部面は前記ストリング選択絶縁膜516の上部面と同一平面にある。前記ダミー絶縁パターン524の側壁は前記絶縁膜510～516の側壁と同一平面にある。

10

【0224】

前記導電パターンGSL、WL1～WL4、SSL及び前記絶縁膜510～516をエッチングして、前記凹部Aの前記底面503の前記共通ソース領域502を露出する活性開口部530が形成される。前記活性開口部530は前記導電パターンGSL、WL1～WL4、SSLの側壁及び前記絶縁膜510～516の側壁を露出する。前記導電パターンGSL、WL1～WL4、SSL及び前記絶縁膜510～516をエッチングすることは異方性エッチング工程を利用することができます。

20

【0225】

図31を参照すると、前記活性開口部530によって露出された前記導電パターンGSL、WL1～WL4、SSLの側壁及び前記絶縁膜510～516の側壁を覆う情報貯蔵膜532が形成される。前記情報貯蔵膜532は前記活性開口部530によって露出された前記共通ソース領域502を覆う。前記情報貯蔵膜532は前記隆起部Bの上部面、ストリング選択絶縁膜516の上部面、絶縁膜510～515の側壁部、ダミー絶縁パターン524の上部面、及びコンタクト延長部CTの上部面上に形成される。

20

【0226】

再び図6を参照して、前記情報貯蔵膜532の形成方法を説明する。前記情報貯蔵膜532を形成することは、前記活性開口部530内にブロッキング膜134を形成し、前記ブロッキング膜134を覆う電荷貯蔵膜135を形成し、前記電荷貯蔵膜135を覆うトンネル絶縁膜136を形成することを含む。

30

【0227】

再び図31を参照すると、前記活性開口部530内にスペーサ534が形成される。前記スペーサ534は前記活性開口部530の側壁上に形成された情報貯蔵膜532と前記活性開口部530の底面上に形成された情報貯蔵膜532の一部を覆う。前記スペーサ534を形成することは、前記基板501上にスペーサ膜を形成し、異方性で底部をエッチングすることを含む。前記スペーサ534はシリコンを含む。前記スペーサ534は前記情報貯蔵膜532に対してエッチング選択比を有する物質を含む。

【0228】

図32を参照すると、前記スペーサ534をエッチングマスクとして用いて、前記スペーサ534によって露出された情報貯蔵膜532がエッチングされる。前記情報貯蔵膜532がエッチングされ、前記基板503の表面が露出される。前記隆起部Bの上部面、ストリング選択絶縁膜516の上部面、絶縁膜510～515の側壁部、ダミー絶縁パターン524の上部面、及びコンタクト延長部CTの上部面上に形成された情報貯蔵膜532が除去される。前記スペーサ534は除去されるか、または除去されず、活性部として用いることができる。前記スペーサ534がポリシリコンを含む場合、前記スペーサ534は除去されず、活性部として用いることができる。これと異なり、前記スペーサ534が絶縁物質の場合、前記スペーサ534は除去され、活性部を形成するための半導体物質が開口部の底及び側壁上に形成される。

40

【0229】

50

前記活性開口部 530 を満たす活性部 A P が形成される。前記活性部 A P は単結晶半導体を含むが、これによって限定されない。前記活性部 A P が単結晶半導体を含む場合、前記活性部 A P は前記基板 501 のシード層 (seed layer) として用いたエピタキシャル成長 (epitaxial growth) によって形成される。これと異なり、前記活性部 A P は、前記活性開口部 530 を満たす多結晶または非晶質の半導体膜を形成した後、熱及び／またはレーザを提供して前記多結晶または非晶質半導体膜を相転移することによって形成されることもできる。前記スペーサ 534 が除去されない場合、前記活性部 A P は前記スペーサ 534 と同一の物質を含むことができる。前記活性部 A P は前記活性開口部 530 を満たすように形成されるか、前記活性開口部 530 を満たす活性部 A P の一部を除去してシリンドータイプに形成することもできる。

10

## 【0230】

前記活性部 A P の上部にドレイン領域 D が形成される。前記ドレイン領域 D は前記活性部 A P の上部をドーピングさせて形成される。前記ドレイン領域 D は前記ウェルと異なる導電型のドーパントが高濃度で含まれた領域であり得る。例えば、前記ドレイン領域 D は高濃度の n 型ドーパントを含む。前記ドレイン領域 D は管 (tubular) 状のパッド形であり得る。

## 【0231】

図 33 を参照すると、前記隆起部 B の上部面上にゲート絶縁膜 554 が形成される。前記ゲート絶縁膜 554 を形成することは、前記半導体基板 501 を熱酸化することを含む。前記ゲート絶縁膜 554 が熱酸化工程によって形成される場合、前記コンタクト延長部 C T の上部面上に酸化膜が形成されるので、前記ゲート絶縁膜 554 を形成する前に、前記凹部 A を覆い、前記隆起部 B を露出するマスク層が追加で形成される。前記マスク層は絶縁膜であり得る。

20

## 【0232】

前記ゲート絶縁膜 554 はシリコン酸化膜を含む。前記ゲート絶縁膜 554 上にゲート電極 556 が形成される。前記ゲート電極 556 の両側の半導体膜 552 にソースドレイン領域 553 が形成される。前記ソースドレイン領域 553 は前記半導体膜 552 に不純物を注入して形成される。

## 【0233】

図 34 を参照すると、前記ゲート電極 556 の両側壁上にゲートスペーサ 558 が形成される。前記基板 501 上に第 1 層間絶縁膜 560 が形成される。前記第 1 層間絶縁膜 560 は前記隆起部 B 上の周辺回路を覆う。前記第 1 層間絶縁膜 560 はシリコン酸化膜を含む。

30

## 【0234】

前記第 1 層間絶縁膜 560 をエッチングして、前記導電パターン G S L、W L 1 ~ W L 4 のコンタクト延長部 C T、前記活性部 A P の前記ドレイン領域 D、及び前記周辺回路の前記ゲート電極 556 の上部面を各々露出するコンタクト開口部 562、ビットライン開口部 564、及び周辺回路開口部 566 が各々形成される。この時、周辺回路領域 のソースドレイン領域を露出する開口部が形成される。前記第 1 層間絶縁膜 560 のエッチングは異方性エッチング工程を利用することができる。

40

## 【0235】

上述のように、前記ゲート絶縁膜 554 が熱酸化工程で形成されて、前記セル領域 の前記導電パターン G S L、W L 1 ~ W L 4、S S L のコンタクト延長部 C T の上部面に酸化膜が形成された場合、前記第 1 層間絶縁膜 560 をエッチングする過程で前記マスク層はエッチングされ、前記コンタクト延長部 C T が露出される。これと異なり、前記ゲート絶縁膜 554 が熱酸化工程で形成されたが、前記導電パターン G S L、W L 1 ~ W L 4、S S L のコンタクト延長部 C T の上部にマスク層を形成しないので、酸化膜が形成された場合、前記第 1 層間絶縁膜 560 をエッチングする過程で、前記酸化膜はエッチングされることがある。

## 【0236】

50

再び図24を参照すると、前記コンタクト開口部562、前記ビットライン開口部564及び前記周辺回路開口部566を各々埋め込むコンタクトプラグGCP、CP、ビットラインコンタクトプラグBLCP、及び周辺回路コンタクトプラグPCPが形成される。

#### 【0237】

接地選択コンタクトプラグGCPは前記接地選択ラインGSLのコンタクト延長部CTと電気的に接続される。前記ワードラインコンタクトプラグCPは前記ワードラインWL1～WL4と電気的に接続される。前記コンタクトプラグGCP、CPは各々前記導電バターンGSL、WL1～WL4より高い伝導性を有する物質を含む。前記周辺回路コンタクトプラグPCPは前記ゲート電極556と電気的に接続される。前記周辺回路コンタクトプラグPCPは前記ゲート電極556より高い伝導性を有する物質を含む。例えば、前記コンタクトプラグGCP、CP、ビットラインコンタクトプラグBLCP、及び周辺回路コンタクトプラグPCPはタンゲステンを含む。

#### 【0238】

前記接地選択コンタクトプラグGCP上に第2導電ラインML2が形成される。前記ワードラインコンタクトプラグCP上に第1導電ラインML1が形成される。前記ビットラインコンタクトプラグBLCP上にビットラインBLが形成される。前記周辺回路コンタクトプラグPCP上に第4導電ラインML4が形成される。前記第2導電ラインML2、第1導電ラインML1、ビットラインBL、及び第4導電ラインML4が形成されることは、前記第1層間絶縁膜560上に導電膜を形成し、パターニングすることを含む。

#### 【0239】

前記第2導電ラインML2、第1導電ラインML1、及び第4導電ラインML4を覆う第2層間絶縁膜570が形成される。前記第2層間絶縁膜570は前記第1層間絶縁膜560と同一の物質を含むことができる。前記第2層間絶縁膜570を貫通し、ストリング選択ラインSSLのコンタクト延長部CTを露出する開口部を埋め込むストリング選択コンタクトプラグSCPが形成される。前記ストリング選択コンタクトプラグSCPは前記ストリング選択ラインSSLより伝導性が高い物質を含む。前記ストリング選択コンタクトプラグSCP上に第3導電ラインML3が形成される。前記第3導電ラインML3を形成することは、第2層間絶縁膜570上に導電膜を形成し、パターニングすることを含む。これによって、図24を参照して説明した半導体素子が提供される。

#### 【0240】

図25を参照して説明した本発明の第5実施形態の変形例に係る半導体素子の形成方法を説明する。

#### 【0241】

図25を参照すると、図27～図34、及び図24を参照して説明した半導体素子の形成方法において、凹部A及び隆起部Bは基板500上に絶縁膜504を形成し、凹部Aが配置される基板500の部分上の絶縁膜をエッチングし、隆起部Bが配置される基板500の部分上の絶縁膜504を残して定義される。

#### 【0242】

前記周辺回路領域の前記隆起部B上に半導体膜552が形成される。前記半導体膜552を形成することは、前記隆起部Bの上部面上に半導体膜552をポンディングすること、または前記半導体膜552を成長させることを含む。前記半導体膜552はシリコンを含むことができる。前記半導体膜552上にゲート絶縁膜554が形成される。以後、図33及び図34を参照して説明した周辺回路の形成方法によって周辺回路が形成される。

#### 【0243】

図26を参照して説明した本発明の第5実施形態の他の変形例に係る半導体素子の形成方法を説明する。

#### 【0244】

図26を参照すると、図27～図34、及び図24を参照して説明した半導体素子の形成方法において、前記第1側壁505及び前記第2側壁506の中の少なくとも1つの側

10

20

30

40

50

壁は、前記底面 503 に傾くように形成される。この場合、前記コンタクト延長部 C T 及び前記ダミー延長部 D C T は前記底面 503 及び前記底部 B P に傾くように形成される。前記絶縁膜 510 ~ 516 の側壁部は前記底面 503 に傾くように形成される。

#### 【0245】

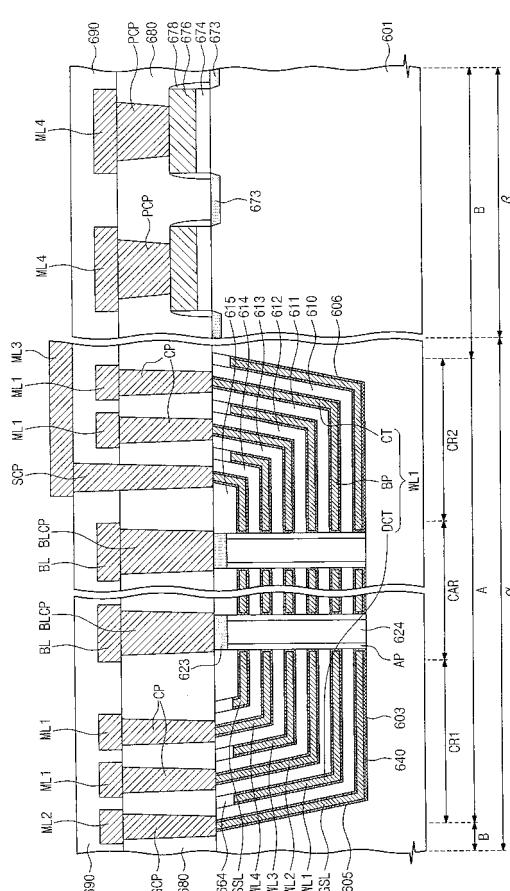

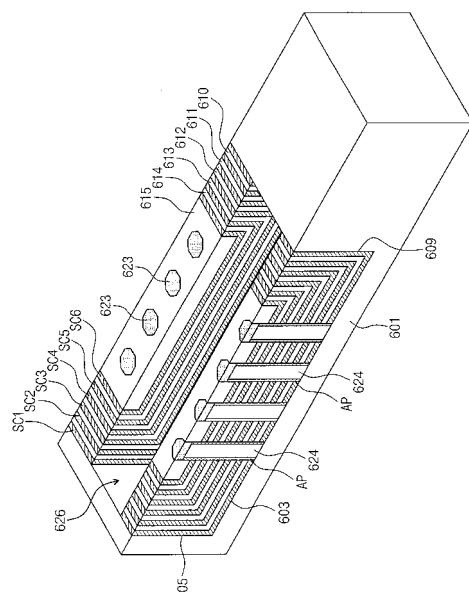

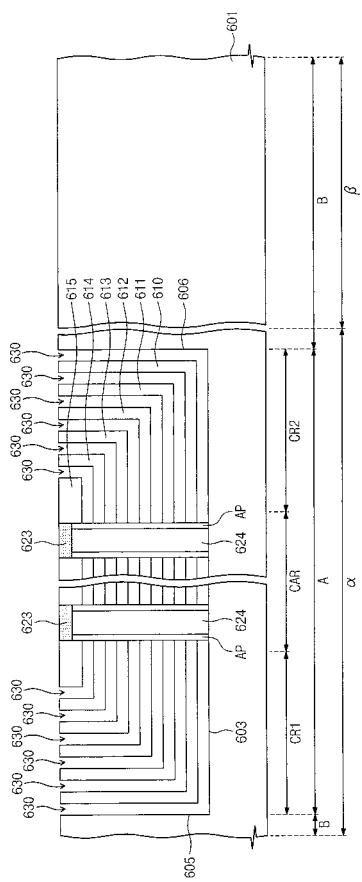

本発明の第 6 実施形態に係る半導体素子を説明する。図 35 及び図 36 は、本発明の第 6 実施形態に係る半導体素子を説明するための平面図であり、図 37 は、図 35 及び図 36 の V I - V I' に沿って切断した断面図である。

#### 【0246】

図 35 乃至図 36、及び図 37 を参照すると、基板 601 が提供される。前記基板 601 は半導体基盤の半導体基板である。前記基板 601 はウェル (w e l l) を含む。前記ウェルは第 1 導電型のドーパントを含む。前記基板 601 内に共通ソース領域 202 が配置される。前記共通ソース領域 602 は前記基板 601 のセル領域内に平板形態 (p l a t e f o r m) に配置される。これと異なり、共通ソース領域は基板上にライン形態であり得る。例えば、前記共通ソース領域はゲート代替工程で形成されたトレンチを実現して形成される。

10

#### 【0247】

前記共通ソース領域 602 は高濃度のドーパントを含むことができる。前記共通ソース領域 202 に含まれたドーパントは前記ウェルに含まれたドーパントと異なる導電型の第 2 導電型であり得る。例えば、前記ウェルが p 型ドーパントを含む場合、前記共通ソース領域 202 は高濃度の n 型ドーパントを含む。

20

#### 【0248】

前記基板 601 は凹部 A を含む。前記凹部 A は底面 603 と互いに対向する第 1 側壁 605 及び第 2 側壁 606 を含む。前記基板 601 は前記第 1 側壁 605 及び第 2 側壁 606 から延長された隆起部 B を含む。前記隆起部 B の上部面は前記凹部 A の前記底面 603 と平行である。前記凹部 A 及び前記隆起部 B は半導体基板の凹部 A が配置される部分をエッチングして、隆起部 B が配置される部分を残して形成される。この場合、前記基板 601 は一体の基板である。

#### 【0249】

前記基板 601 はセル領域 及び周辺回路領域 を含む。前記セル領域 にはメモリセルが配置される。前記セル領域 は前記凹部 A 及び前記隆起部 B を含む。前記周辺回路領域 には周辺回路が配置される。前記周辺回路領域 は前記隆起部 B を含む。

30