(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-143087

(P2005-143087A)

(43) 公開日 平成17年6月2日(2005.6.2)

(51) Int.Cl.<sup>7</sup>

**H04N 5/00**

**G09G 3/20**

**G09G 3/36**

**G09G 5/00**

**H04N 5/44**

F 1

H04N 5/00

G09G 3/20

G09G 3/20

G09G 3/20

G09G 3/20

テーマコード(参考)

5C006

5C025

5C056

5C058

5C064

審査請求 未請求 請求項の数 10 O L 外国語出願 (全 20 頁) 最終頁に続く

(21) 出願番号 特願2004-271125 (P2004-271125)

(22) 出願日 平成16年9月17日 (2004.9.17)

(31) 優先権主張番号 60/504060

(32) 優先日 平成15年9月18日 (2003.9.18)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 60/562737

(32) 優先日 平成16年4月15日 (2004.4.15)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 10/909027

(32) 優先日 平成16年7月29日 (2004.7.29)

(33) 優先権主張国 米国(US)

(71) 出願人 502359574

ジェネシス・マイクロチップ・インコーポ

レーテッド

GENESIS MICROCHIP, I

N.C.

アメリカ合衆国 95002 カリフォル

ニア、アルビソ、ゴールド・ストリート

2150

2150 Gold Street, Al

viso, CA 95002 U. S. A

.

(74) 代理人 110000028

特許業務法人明成国際特許事務所

最終頁に続く

(54) 【発明の名称】画像制御集積回路におけるピクセルクロック生成回路およびCRT制御回路のバイパス技術

## (57) 【要約】

【課題】 ビデオ処理装置において、ピクセルクロック速度に無関係なクロック速度でビデオデータストリームを提供する方法を開示する。

【解決手段】 この方法は、固有ビデオデータを固有クロック速度でビデオソースから受信し、ビデオデータを記憶装置に格納し、ビデオデータの選択部分をメモリクロック速度で読み出し、ビデオデータの選択部分をラスタライズし、ラスタライズされたビデオデータをパケット化し、パケット化されたビデオデータを、メモリクロック速度を基調とするリンク速度によって、リンクを介して表示装置に送信する。

【選択図】 図2

Fig. 2

**【特許請求の範囲】****【請求項 1】**

ビデオ処理装置において、ピクセルクロック速度に無関係なクロック速度でビデオデータストリームを提供する方法であって、

ビデオソースからの固有ビデオデータを固有クロック速度で受信し、

前記ビデオデータを記憶装置に格納し、

前記記憶装置に格納された前記ビデオデータの選択部分をメモリクロック速度で読み出し、

前記ビデオデータの選択部分をラスタライズし、

前記ラスタライズされたビデオデータを複数のビデオデータパケットにパケット化し、 10

前記パケット化されたビデオデータを、メモリクロック速度を基調とするリンク速度のリンクを介して表示装置に送信する

方法。

**【請求項 2】**

前記記憶装置は、前記ビデオデータの少なくとも1つのフレームラインを格納可能な記憶容量を有するラインバッファである請求項1記載の方法。

**【請求項 3】**

請求項1記載の方法であって、

前記ビデオデータパケットの各々は、パケットヘッダおよびパケットペイロードを含み 20

、前記パケットヘッダは、パケットIDを含み、

前記パケットペイロードは、対応する画素の駆動に適するビデオデータを含む方法。

**【請求項 4】**

前記ラスタライザは、カラー参照テーブルに接続されている請求項1記載の方法。

**【請求項 5】**

リンクを介して接続された非CRT形式の表示装置にビデオデータを表示させるためのビデオプロセッサであって、

メモリクロック速度で動作するビデオ記憶装置と、

当該ビデオプロセッサがCRT制御装置を必要としないように、メモリクロック速度 30

memoryを基調とするリンク速度で、前記ビデオデータをビデオデータパケット形式で前記非CRT形式の表示装置へと伝送するためのビデオパケット伝送装置と

を備えるビデオプロセッサ。

**【請求項 6】**

前記非CRT形式の表示装置は、LCD形式の表示装置である請求項5記載のビデオプロセッサ。

**【請求項 7】**

請求項5記載のビデオプロセッサであって、更に、

固有クロック速度 nativeおよび固有ビデオフォーマットでビデオ信号V<sub>1</sub>を提供するビデオソースに接続されたインタフェースと、

前記インタフェースおよび前記ビデオ記憶装置に接続され、前記ビデオデータを受信し、該受信したビデオデータを、表示中のビデオ画面に対応する前記ビデオ記憶装置の記憶領域に格納するための書き込み・変更動作を実行するメモリ制御装置と、

前記メモリ制御装置に接続されたラスタエンジンと

を備え、

前記メモリ制御装置は、前記ビデオ記憶装置に格納された前記ビデオデータを表示するために、前記格納されたビデオデータの選択部分を、前記ビデオ記憶装置から前記メモリクロック速度 memoryで読み出し、該読み出されたビデオデータの選択部分を前記ラスタエンジンに引き渡す読み出し動作を実行し、

前記ラスタエンジンは、前記固有ビデオフォーマット nativeのビデオ信号V<sub>1</sub>を、前 50

記表示装置の特性に基づく表示フォーマットのビデオ信号  $V_2$  へと変換するビデオプロセッサ。

【請求項 8】

請求項 7 記載のビデオプロセッサであって、更に、

前記ラスタエンジンに接続され、前記ビデオ信号  $V_2$  を前記ビデオデータパケットにパケット化するパケタイザと、

前記パケタイザを前記リンクへと接続し、前記ビデオデータパケットをビデオデータストリームとして整列させるリンクインターフェースと

を備え、

前記ビデオデータストリームは、前記メモリクロック速度  $memory$  を基調とし固有ストリーム速度  $native$  に無関係なリンク速度  $L_R$  で、前記リンクを介して前記表示装置に伝送される

ビデオプロセッサ。

【請求項 9】

前記リンクは、該リンクの状態を協調して維持可能な複数の論理データチャネルによって構成可能である請求項 8 記載のビデオプロセッサ。

【請求項 10】

接続された表示装置に対して表示用ビデオデータを提供するための設定変更が可能なビデオプロセッサであって、

C R T C 回路と、

前記 C R T C 回路に接続された選択式 C R T 制御回路と、

前記選択式 C R T 制御回路に接続されたラスタエンジンと、

前記表示装置および前記選択式 C R T 制御回路に接続され、前記表示装置に対応する表示形式を判別する表示判別装置と

を備え、

前記表示判別装置は、

前記表示装置が非 C R T 形式であると判別した場合には、前記表示用ビデオデータが前記ラスタエンジンから前記表示装置へと直接的に送信されるように、前記 C R T C 回路の機能を無効化する第 1 の信号を前記選択式 C R T 制御回路に送信し、

前記表示装置が C R T タイプであると判別した場合には、前記表示用ビデオデータが前記リンクによって前記表示装置に送信される前に前記 C R T C 回路によって処理されるように、前記 C R T C 回路の機能を有効化する第 2 の信号を前記選択式 C R T 制御回路に送信する

ビデオプロセッサ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、表示装置に関する。本発明は、より具体的には、L C D パネルを駆動する駆動用電子機器を使用するための方法および装置に関する。

【背景技術】

【0002】

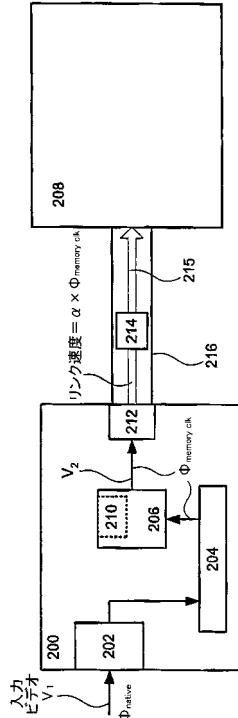

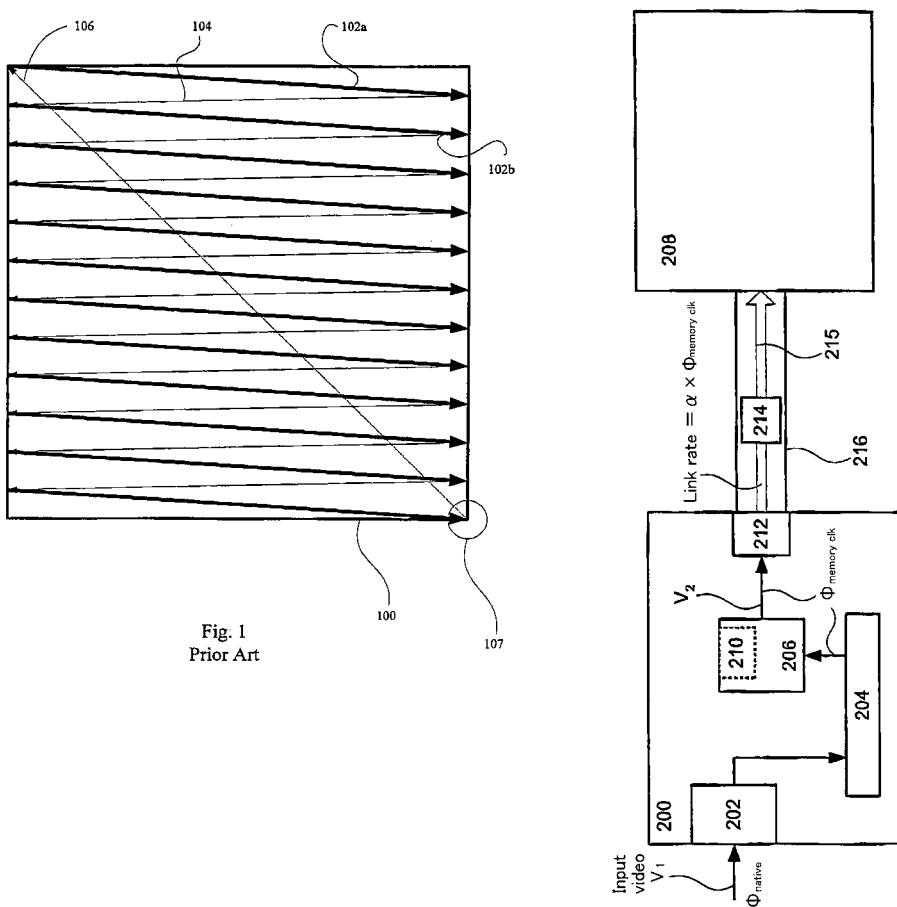

ごく最近まで、今日使用されているテレビのほぼ全ては、ブラウン管すなわち C R T として知られる装置を用いて画像表示を行っていた。画面全体に画像を表示するために、テレビ内蔵の電子回路は、磁界偏向コイル（電子ビームを左右に移動させる水平偏向コイル、および電子ビームを上下に移動させる垂直偏向コイル）を用いて、画面上を横切り下方へと走査する「ラスタ走査」パターンで電子ビームを移動させる。図 1 は、従来のブラウン管上のラスタ 100 を示す説明図である。図 1 に示すラスタ 100 における電子ビームは、徐々に下方へと移動しながら、画面の左端から右端へと横切る一本のライン 102a を描いた後、素早く左端へ戻り（104）、別の水平ライン 102b を描く。電子ビームは、ボトムライン 107 の右端に到達すると、ライン 106 で表されるように画面の左上

10

20

30

40

50

角へ戻る。電子ビームは、ライン102上の「描線」中にはオン状態であり、ライン104上の「帰線」中には、帰線中に画面上に跡を残さないようにオフ状態である。「水平帰線」は、電子ビームが各ラインの終端から左端に戻る軌跡を意味し、「垂直帰線」は、電子ビームがラスタ106の底部から頂部に戻る軌跡を意味する。

#### 【0003】

CRT表示画面に画像を表示するために、画像の各々は、複数の水平走査ラインから構成されるフレームの連続したものとして伝送される。ビデオ信号を水平走査ライン毎およびフレーム毎に区切るために、通常、時間基準信号が与えられる。これらの基準信号は、フレームの開始を示すVSYNC信号と、次回の走査ラインの開始を示すHSYNC信号とを含む。このように、画像は、画素として表示される複数の点毎に区切られ、各画素は、画素が生成される速度（画素／秒）を定めるピクセルクロックを基調とする。したがって、CPUやDVDプレーヤ等のビデオソースからのビデオデータを表示するために、ビデオデータは、ビデオ処理装置（VPU）によって処理される。従来のビデオ処理装置（VPU）は、入力されたビデオデータを、ビデオデータを一時的に格納するメモリによって決定されるクロック速度で、（固有のフォーマットから）ビデオ表示用フォーマットに変換する。

#### 【0004】

その後、ブラウン管（CRT）制御装置は、表示装置がCRT方式またはLCDのような固定ピクセル方式であるか否かに関係なく、タイミング信号および制御信号（例えば、HSYNCおよびVSYNC）を与えることによって、表示用フォーマット変換されたビデオデータを、CRT用表示タイミングに変換する。このように、CRT制御装置は、表示装置がCRT用の信号を必要とするという想定だけに基づいて、ビデオソースから読み出されたビデオデータを、ピクセルクロック速度<sub>pixel</sub>に変換する。そのため、CRTの古い設計思想に厳密に基づくと、入力されたビデオ信号は、固有ビデオクロック<sub>native</sub>からピクセルクロック<sub>pixel</sub>に変換された後、ピクセルクロック<sub>pixel</sub>よりも高速なリンク速度LRで表示装置に送信される。その結果、表示の際には、ビデオデータを正確に表示するために、ビデオ信号をピクセルクロック再生回路によって再び処理する必要がある。

#### 【0005】

したがって、ピクセルクロック速度が重要でない場合（例えば、LCDのような固定ピクセル方式の表示装置である場合）であっても、従来のビデオプロセッサは、CRT方式の表示装置で表示されることのないビデオ信号を、CRT制御装置によってCRTの古い仕様に従わせる必要がある。

#### 【0006】

それ故に、表示装置がCRT方式でない場合には、CRTの古い仕様を強要することのないビデオプロセッサが望まれる。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0007】

液晶表示装置（LCD）のようなデジタル表示装置での使用に適した方法、装置、システムとして具体化されるビデオプロセッサ技術であって、ピクセル速度に依存することなくメモリクロック速度を基調とするビデオ信号を提供するビデオプロセッサ技術が提供される。

#### 【課題を解決するための手段】

#### 【0008】

ビデオ処理装置において、ピクセルクロック速度に無関係なクロック速度でビデオデータストリームを提供する方法を開示する。この方法は、固有ビデオデータを固有クロック速度でビデオソースから受信し、ビデオデータを記憶装置に格納し、ビデオデータのうちの選択部分をメモリクロック速度で読み出し、選択されたビデオデータをラスタライズし、ラスタライズされたビデオデータをパケット化し、パケット化されたビデオデータを、

メモリクロック速度を基調とするリンク速度によって、リンクを介して表示装置に送信する。

【0009】

他の実施形態として、リンクによって接続された非CRT形式の表示装置にビデオデータを表示させるためのビデオプロセッサを開示する。このビデオプロセッサは、メモリクロック速度で動作するビデオ記憶装置と、メモリクロック速度 *memory*を基調とするリンク速度で、ビデオデータをビデオデータパケット形式で非CRT形式の表示装置へと伝送するためのビデオパケット伝送装置とを備える。これによって、ビデオプロセッサはCRT制御装置を必要としない。

【0010】

また、他の実施形態として、接続された表示装置に対して表示用ビデオデータを提供するための設定変更が可能なビデオプロセッサを開示する。このビデオプロセッサは、CRT回路と、CRT回路に接続された選択式CRT制御回路と、選択式CRT制御回路に接続されたラスタエンジンとを備える。ビデオプロセッサは、更に、表示装置および選択式CRT制御回路に接続され、表示装置に対応する表示形式を判別する表示判別装置を備える。前記表示判別装置は、前記表示装置が非CRT形式であると判別した場合には、前記表示用ビデオデータが前記ラスタエンジンから前記表示装置へと直接的に送信されるように、前記CRT回路の機能を無効化する第1の信号を前記選択式CRT制御回路に送信し、前記表示装置がCRTタイプであると判別した場合には、前記表示用ビデオデータが前記リンクによって前記表示装置に送信される前に前記CRT回路によって処理されるように、前記CRT回路の機能を有効化する第2の信号を前記選択式CRT制御回路に送信する。

【発明を実施するための最良の形態】

【0011】

次に、添付の図面に一例を示された本発明の特定の一実施形態を詳細に説明する。以下では、特定の一実施形態との関連のもとで本発明を説明するが、これは、本発明をその実施形態に限定することを意図しているのではない。逆に、代替形態、変更形態、等価形態は、特許請求の範囲に記載された発明の趣旨および範囲に含まれるものとする。

【0012】

ごく最近まで、今日使用されているテレビのほぼ全ては、ブラウン管すなわちCRTとして知られる装置を用いて画像表示を行っていた。画面全体に画像を表示するために、テレビ内蔵の電子回路は、磁界偏向コイル（電子ビームを左右に移動させる水平偏向コイル、および電子ビームを上下に移動させる垂直偏向コイル）を用いて、画面上を横切り下方へと走査する「ラスタ走査」パターンで電子ビームを移動させる。CPUやDVDプレーヤ等のビデオソースからのビデオデータを表示するために、ビデオソースから固有クロック速度 *native*で与えられたビデオデータは、従来のビデオ処理装置（VPU）やラスタエンジンによって処理される。従来のビデオ処理装置（VPU）は、ビデオデータをビデオ記憶装置に格納し、ビデオデータは、メモリクロック速度 *memory*で読み出される。ラスタエンジンは、画像を表示するための表示装置の特性に基づいて、ビデオデータを固有フォーマットから表示用フォーマットに変換する。

【0013】

その後、ブラウン管（CRT）制御装置は、表示装置がCRT方式またはLCDのような固定ピクセル方式であるか否かに關係なく、タイミング信号および制御信号（例えば、HSYNCおよびVSYNC）を与えることによって、表示タイミングを用いてビデオ信号を変換する。このように、CRT制御装置は、表示装置がCRT方式の信号を必要とするという想定だけに基づいて、記憶装置からメモリクロック速度 *memory*で読み出されたビデオデータを、ピクセルクロック速度 *pixel*に変換する。CRT制御装置がCRT方式の制御信号およびタイミング信号を与えた後、ビデオデータは、リンクを介してリンク速度LRで表示装置に引き渡される。したがって、ピクセルクロック速度が重要でない場合（例えば、LCDのような固定ピクセル方式の表示装置である場合）であっても、従来

10

20

30

40

50

のビデオプロセッサは、C R Tの古い仕様に従うために、C R T方式の表示装置で表示されることのないビデオ信号の生成をC R T制御装置によって実行させる必要がある。

【0014】

しかるべき、本発明は、L C Dのような非C R T方式の表示装置にビデオが表示される場合には、C R Tの古い仕様を強要することのない方法、システム、装置を開示する。より具体的には、本発明のビデオプロセッサは、ピクセルクロックに無関係なメモリクロック速度を基調とするリンク速度で、ビデオデータをビデオデータパケットとして伝送することによってメモリクロック速度を維持する。よって、本発明のビデオプロセッサは、接続される表示装置がC R T方式でない場合には、C R T制御装置を必要としない。本発明のビデオプロセッサは、実施形態によっては、固定ピクセル方式の表示装置に専用であり、C R T制御装置や関連の回路を完全に排除しても良いし、可能性のある全ての表示環境に対応するように、選択的に動作するC R T制御回路を組み込むこととしても良い。C R T制御装置や関連の回路の動作は、初期設定処理においてビデオプロセッサが表示装置に対してC R T方式であるか否かを照会する表示装置属性の照会に基づいて選択される。

【0015】

以下では、代表的なL C Dパネルの観点から本発明を説明する。しかしながら、本発明は、L C D方式、プラズマ方式、D L P方式を含むあらゆるデジタル固定ピクセル方式の表示装置に適用可能であり、以下の説明におけるL C Dパネルの使用は、本発明の範囲および意図のいずれをも限定するものではない。本発明は、パケットベースのビデオ表示インターフェースとの併用に適する。パケットベースのビデオ表示インターフェースについては、例えば、2003年12月3日付けで出願された小林による同時係属出願である米国特許出願第10/726,794号「パケットベースのビデオ表示インターフェースおよびその使用方法」や、この出願と同時に出願された小林による米国特許出願第10/909,103号「L C Dパネル駆動装置におけるパケット伝送の使用技術」に開示されている。上記の出願のいずれも、引用によって本明細書に組み込まれるものとする。

【0016】

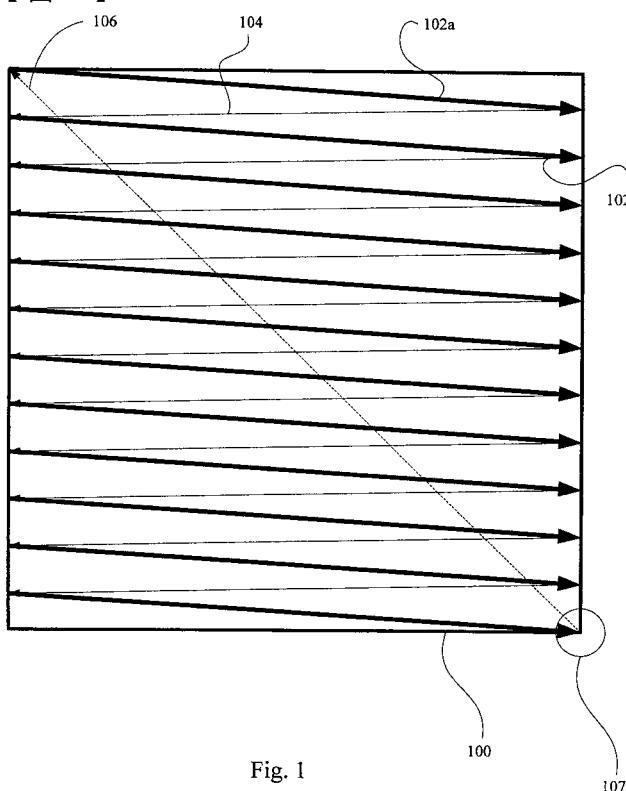

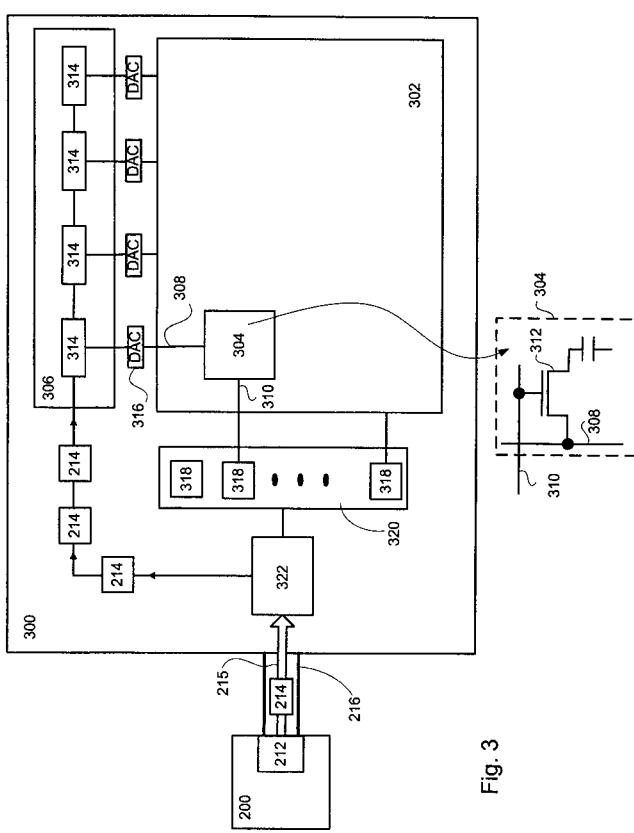

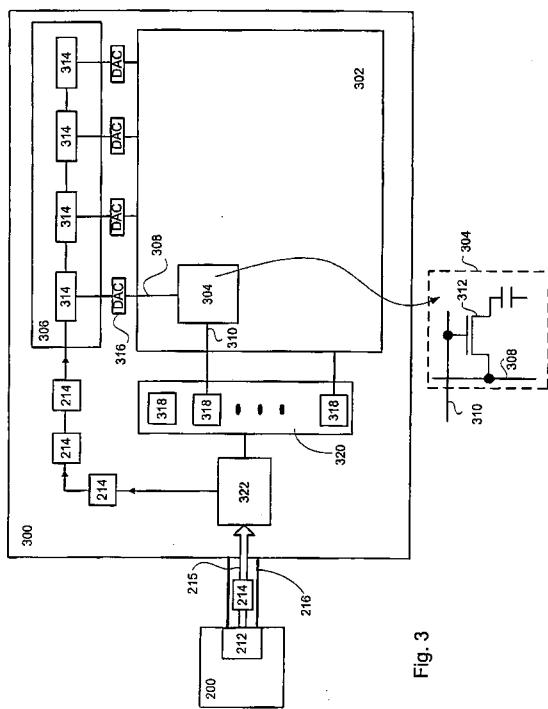

それに応じて、図2は、本発明の一実施形態におけるビデオ処理装置(V P U)200の一例を示す説明図である。V P U200は、固有クロック速度nativeおよび固有ビデオフォーマットでビデオ信号V<sub>1</sub>を提供可能なC P UやD V Dプレーヤ等のビデオソース(図示しない)に接続されたインターフェース202を備える。ビデオソースは、デジタル画像(すなわちデジタル静止画像、若しくはデジタルビデオ)ソース、アナログ画像(すなわちアナログ静止画像、若しくはアナログビデオ)ソースの少なくともいずれかであることとしても良い。よって、ビデオソースによって提供される種々のビデオ信号には、合成ビデオや、シリアルデジタル、パラレルデジタル、R G B、民生デジタルビデオ等の種々の周知のフォーマットが含まれることとしても良い。ビデオ信号は、何らかのアナログビデオソースの形態を備えたソースから提供されるアナログビデオ信号であっても良く、アナログビデオソースとしては、例えば、アナログテレビ、スチルカメラ、アナログV C R、D V Dプレーヤ、ビデオカメラ、レーザディスクプレーヤ、テレビチューナ、セットトップボックス(衛生D S Sやケーブル信号を用いるもの)等がある。また、ソースは、例えば、デジタルテレビ(D T V)やデジタルスチルカメラ等のデジタル画像ソースを備えることとしても良い。デジタルビデオ信号は、種々のデジタルフォーマットであることとしても良く、デジタルフォーマットとしては、例えば、S M P T E 274 M - 1995(解像度:1920×1080、順次走査または飛び越し走査)や、S M P T E 296 M - 1997(解像度:1280×720、順次走査)，標準的な480順次走査ビデオ等がある。

【0017】

ビデオデータV<sub>1</sub>は、受信された後、インターフェース202に接続されたビデオ記憶装置204の記憶領域のうち、表示されているビデオ画面に対応する記憶領域に(書き込み・変更の動作によって)格納される。ほとんどの場合、記憶装置204は、少なくともビデオデータのフレームの全てを格納するのに十分な記憶容量を有する。記憶装置204に

10

20

30

30

40

50

格納されたビデオデータを表示するためには、ビデオデータ  $V_1$  の一部が、メモリクロック速度  $memory$  で記憶装置 204 から読み出された後、固有フォーマットのビデオデータは、ラスタエンジン 206 によって、表示装置 208 の特性に基づいた表示用フォーマットのビデオ信号  $V_2$  に変換される。例えば、固有フォーマットが 8 ビットのビデオデータであり、表示装置 208 が 24 ビットのビデオデータを必要とする場合には、ラスタエンジン 206 は、カラー参照テーブル (CLUT) 210 を用いて変換を実行しても良い。

#### 【0018】

ビデオ信号  $V_2$  が、表示装置 208 による表示に適したフォーマットに変換された後、パケタイザ 212 は、ビデオ信号  $V_2$  を、データストリーム 215 の様で複数のデータパケット 214 へとパケット化する。データストリーム 215 は、リンク 216 によって、リンク速度  $LR$  と称される伝送速度で表示装置 208 に伝送される。リンク速度  $LR$  は、ビデオデータの固有ストリーム速度  $native$  を基調とせず、メモリクロック速度  $memory$  を基調とする（すなわち、 $LR = \times memory$ ）。本実施例では、リンクの状態を協調して維持可能な複数の論理データチャネル（図示しない）によってリンク 216 のリンク速度を実現するように設定することができる。例えば、チャネル毎の速度が 2.5 G bps である場合は、リンク 216 は、チャネル毎に 18 ビット / ピクセルの色階調で 60 Hz の SXGA に対応することができる。なお、チャネル数の削減は、相互接続コストを低減させるだけでなく、携帯機器のような機器に求められる省電力化を図ることもできる。しかしながら、チャネル数を 4 つに増やすことによって、リンク 216 は、24 ビット / ピクセルの色階調で 60 Hz の WQSXGA（画像解像度： $3200 \times 2048$ ）や、18 ビット / ピクセルの色階調で 60 Hz の QSXGA（ $2560 \times 2048$ ）を、データ圧縮を行うことなく対応することができる。チャネル毎の速度が 1.0 Gbps の最低速度の場合であっても、たった 2 つのチャネル数で、非圧縮 HDTV（すなわち、1080i または 720p）データストリームに対応することができる。

#### 【0019】

しかしながら、リンク 216 の帯域は、リンク 216 を介して伝送されるデータストリームの全ての帯域の合計よりも大きくなければならない。このように、データパケット 214 は、VPU 200 や表示装置 208 のいずれかにおけるピクセルクロックの生成を必要とすることなく、後述するように適切に構成された表示装置 208 によって受信され適切に処理される。一実施形態では、VPU 200 は、表示装置が古い CRT 方式である場合に必要な CRT 制御信号およびタイミングを与える CRT 制御装置に接続されたスイッチを仕様に応じて備えることとしても良い。その結果、種々の表示装置に対して VPU を用いることができる。

#### 【0020】

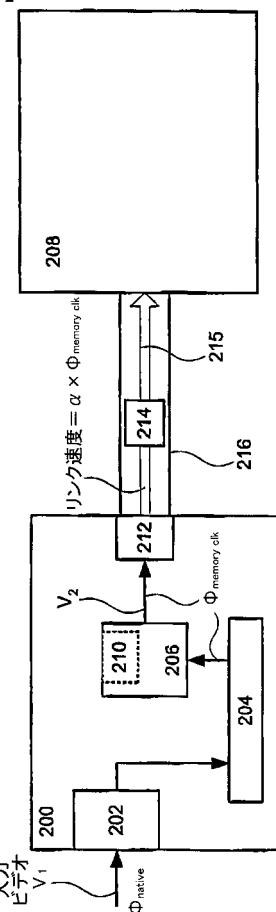

図 3 は、VPU 200 に適応する LCD 表示装置 300 の一例を示す説明図である。ここで、LCD 表示装置 300 は、複数のデータ線 308 および複数のゲート線 310 によってマトリクス状に配置されデータドライバ 306 に接続される複数の画像素子 304（ピクセル）を有する LCD パネル 302 を備える。本実施例では、これらの画像素子 304 は、データ線 308 とゲート線 310 との間に接続された複数の薄膜トランジスタ（TFT）312 である。動作の際には、ビデオデータが格納された複数のデータラッチ 314 の各々は、データ線 308 を介して接続されたデジタル / アナログ変換器（DAC）316 に、デジタルデータ信号を出力する。同時に、ゲートドライバ 320 が備える複数の論理回路 318 の各々は、水平同期信号と同期した一連のタイミングで、所定の走査信号をゲート線 310 に出力する。これによって、TFT 312 は、DAC 316 から供給されたアナログデータ信号を、画像素子 304 のうち選択された画素を最終的に駆動するデータ線 308 を介して伝送するために、所定の走査信号がゲート線 310 に供給された際に、ターンオンする。

#### 【0021】

ビデオデータを伝送するために、VPU 200 は、表示インタフェース 322 による受信および処理を経ることになる複数のデータパケット 214 を含むデータストリーム 21

10

20

30

40

50

5を生成する。本実施例では、その後、データパケット214は、カラムドライバ306が備えるデータラッチ314に直接的に転送される。この際、ビデオフレームの所定のフレームラインnの表示に用いられる(ピクセルデータ形式の)ビデオデータの全てが、ライン期間内にデータラッチ314に提供される。したがって、各データラッチ314に適切なピクセルデータが格納されると、データドライバ306は、LCDアレイ302の適切なTFT312を駆動する。

#### 【0022】

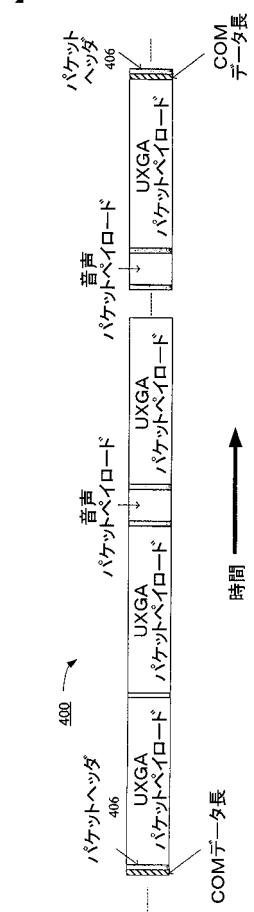

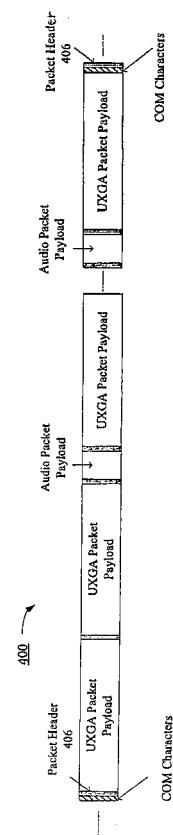

図4は、リンク216上で伝送されるデータストリーム400の詳細図である。1つのデータストリーム400は、複数のビデオデータパケット402および複数の音声データパケット404を多重化したものである。本実施例では、ビデオデータパケット402は、音声データパケット404(ストリームID=2)形式の音声に関連付けられたUXGA画像の1280×720ピクセルのビデオ(ストリームID=1)である。本実施例では、各フレームラインは、少なくとも1280ピクセル(すなわち3840サブピクセル)から成ることから、ビデオデータの1つのフレームラインをライン期間内に格納するためには3840回のデータラッチが必要である。例えば、一実施形態では、データストリーム400が表示インターフェース322によって受信されると、フレームバッファまたはラインバッファの態様を採用するメモリに、(対応するパケットヘッダ406によって定義される)3840個のデータパケットの集まりが格納される。ただし、厳密なパイプライン方式が望ましい場合には、メモリを迂回することとしても良いし、メモリを全く無くすこととしても良い。

#### 【0023】

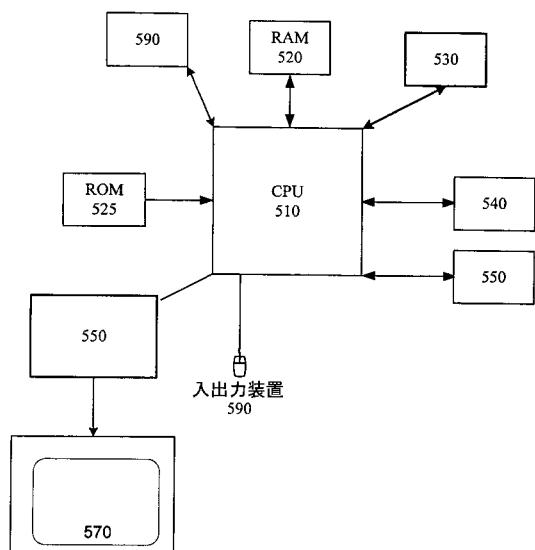

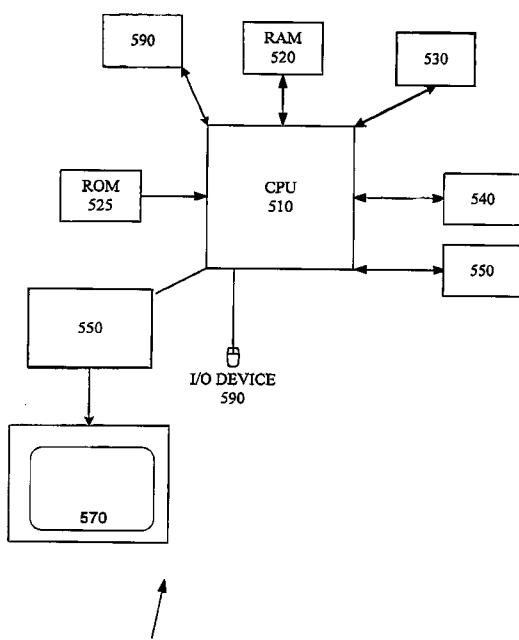

図5は、本発明を適用した画像システム500を示す説明図である。システム500は、本発明を適用した画像システムの一例に過ぎない。システム500は、中央演算処理装置(CPU)510と、ランダムアクセスメモリ(RAM)520と、読み出し専用メモリ(ROM)525と、1つ以上の周辺機器530と、画像コントローラ560と、一次記憶装置540, 550と、デジタル表示装置570とを備える。CPU510は、1つ以上の入出力装置590にも接続されている。画像コントローラ560は、画像データおよびそれに対応する参照信号を生成し、両信号をデジタル表示装置570に提供する。画像データは、例えば、CPU510または外付けの回路から受信されたピクセルデータに基づいて生成することができる。

#### 【0024】

以上では、本発明の実施形態をいくつか説明したが、本発明は、本発明の範囲および趣旨から逸脱することなしに、様々な形態で実現することが可能である。上述した実施形態は、例示を目的としたものであって限定を目的としたものではなく、したがって、本発明は、上述の詳細に限定されることはなく、添付した特許請求の範囲およびそれらのあらゆる等価形態の範囲で変更することが可能である。

#### 【0025】

以上では、本発明の好ましい実施形態を取り上げて説明したが、そのほかにも、本発明の範囲内で各種の代替形態、置換形態、等価形態が可能である。なお、本発明のプロセスおよび装置は、多くの方法によって具体化することができる。したがって、本発明は、本発明の真の趣旨および範囲に含まれる。このようなあらゆる代替形態、置換形態、等価形態を含むものと解釈される。

#### 【図面の簡単な説明】

#### 【0026】

【図1】従来のブラウン管上のラスタ100を示す説明図である。

【図2】本発明の一実施形態におけるビデオ処理装置(VPU)200の一例を示す説明図である。

#### 【図3】VPU200に適応するLCD表示装置300の一例を示す説明図である。

#### 【図4】リンク216上で伝送されるデータストリーム400の詳細図である。

#### 【図5】本発明を適用した画像システム500を示す説明図である。

10

20

30

40

50

【 図 1 】

Fig. 1

従来技術

【 図 2 】

Fig. 2

( 3 )

Fig. 3

( 义 4 )

Fig. 4 リンクトラフィックの詳細例

【図5】

500

Fig. 5

## フロントページの続き

| (51)Int.Cl. <sup>7</sup> | F I           | テーマコード(参考)        |

|--------------------------|---------------|-------------------|

| H 0 4 N 5/66             | G 0 9 G 3/20  | 6 3 3 P 5 C 0 8 0 |

| H 0 4 N 7/173            | G 0 9 G 3/20  | 6 5 0 L 5 C 0 8 2 |

|                          | G 0 9 G 3/36  |                   |

|                          | H 0 4 N 5/44  | A                 |

|                          | H 0 4 N 5/66  | 1 0 2 Z           |

|                          | H 0 4 N 7/173 | 6 3 0             |

|                          | G 0 9 G 5/00  | 5 5 5 D           |

(72)発明者 小林 修

アメリカ合衆国 カリフォルニア州 9 4 0 2 4 ロス・アルトス, フォーレン・リーフ・レーン,

1 4 6 4

F ターム(参考) 5C006 AA01 AF03 AF04 AF44 AF45 AF51 AF53 AF61 AF72 BB16

BC03 BC11 BC16 BF14 BF16 BF24 FA41 FA51

5C025 AA30 BA27 DA10

5C056 FA05 HA01 HA04

5C058 AA05 AB02 BA04 BB11

5C064 BC20 BC23 BD07 BD08 BD09 BD13

5C080 AA10 BB05 DD22 DD27 DD28 EE19 FF11 GG07 GG08 JJ02

JJ05

5C082 BB01 BD02 MM05

## 【外国語明細書】

## 1. TITLE OF THE INVENTION

BYPASSING PIXEL CLOCK GENERATION AND CRTC CIRCUITS IN A GRAPHICS CONTROLLER CHIP

## 2. DETAILED DESCRIPTION OF THE INVENTION

## Field of the Invention

[0001] The invention relates to display devices. More specifically, the invention describes a method and apparatus for using driving LCD panel drive electronics.

## Background of the Invention

[0002] Until most recently, almost all TVs in use today rely on a device known as the cathode ray tube, or CRT, to display their images. In order to display an image on the entire screen, electronic circuits inside the TV use magnetic deflection coils (a horizontal deflection coil to move the beam from left to right and a vertical deflection coil to move the beam up and down) to move the electron beam in a "raster scan" pattern across and down the screen. Fig. 1 illustrates a raster 100 on a conventional cathode ray tube where an electron beam paints one line across the screen from left to right 102a and then quickly moves back to the left side 104, and paints another horizontal line 102b, while continuously moving down slightly. When the beam reaches the right side of the bottom line 107, it is moved back to the upper left corner of the screen, as represented by line 106. When the beam is "painting" lines 102 it is on, and when it is "retracing" lines 104, it is off so that it does not leave a trail on the screen. The term horizontal retrace is used to refer to the beam moving back to the left at the end of each line, while the term vertical retrace refers to its movement from the bottom to the top of the raster 106.

[0003] In order to display an image on a CRT display screen, each image is transmitted as a sequence of frames each of which includes a number of horizontal scan lines. Typically, time reference signals are provided in order to divide the video signal into horizontal scan lines and frames. These reference signals include a VSYNC signal that indicates the beginning of a frame and an HSYNC signal that indicates the beginning of a next source scan line. In this way, the image is divided into a number of points where each point is displayed as a pixel having a corresponding pixel clock that specifies the rate at which pixels are generated (in pixels per second). Therefore, in order to display video data from a video source, such as a CPU, DVD player, etc., the video data is processed by a conventional video processor unit (VPU) that converts the incoming video data (at a native format) to a video data at a video display format at a clock rate determined by a memory unit into which the data is temporarily stored.

[0004] A cathode ray tube (CRT) controller unit then converts the display formatted video data to CRT compatible display timing by adding timing and control signals (such Hsync and Vsync) regardless of the whether or not the display unit is a cathode ray tube based display or a fixed pixel display such as an LCD. In this way, the CRT controller unit converts the video data that is read from the video source to a pixel clock rate <sub>pixel</sub> based solely upon the assumption that the display requires CRT type signals. It should be noted therefore, that strictly based upon CRT legacy considerations, the incoming video signal has been converted from a native video clock <sub>native</sub> to a pixel clock <sub>pixel</sub> and then sent to the display unit at a link rate LR that must be faster than the pixel clock <sub>pixel</sub>. At the display, the video signal must then be processed again by a pixel clock regenerator circuit in order for the video data to be properly dis-

played.

[0005] Therefore, even in those situations where a pixel clock rate is not meaningful (such as with fixed pixel displays, such as LCDs), conventional video processors require that a CRT controller unit force a video signal that will not be displayed on a CRT type display to conform to legacy CRT requirements.

[0006] Therefore, in those cases where a display is not CRT based, a video processor that does not enforce CRT legacy requirements is desirable.

#### SUMMARY OF THE INVENTION

[0007] What is provided is a video processor architecture embodied as a method, apparatus, and system suitable for implementation with digital displays, such as liquid crystal displays (LCDs), that provides a video signal that is directly related to a memory clock rate and independent of a pixel rate.

[0008] In a video processor unit, a method of providing a video data stream at a clock rate that is independent of a pixel clock rate. Receiving native video data from a video source at a native clock rate, storing the video data in a memory unit, reading selected portions of the video data at a memory clock rate, rasterizing the selected video data, packetizing the rasterized video data, sending the packetized video data to a display unit by way of a link at a link rate, wherein the link rate is directly related to the memory clock rate.

[0009] In another embodiment, a video processor for displaying video data on a non-CRT type display unit coupled thereto by way of a link is disclosed that includes a video memory unit having an associated memory clock rate and a video packet transmitter unit for transmitting the video data to the non-CRT type display in the form of video data packets at a link rate that is directly related to the memory clock rate <sup>memory</sup> such that the video processor does not require a CRT controller unit.

[0010] In still another embodiment, a configurable video processor for providing displayable video data to a display unit coupled thereto is disclosed. The video processor includes a CRTC circuit, a selectable CRT controller circuit coupled to the CRTC circuit and a raster engine coupled to the selectable CRT controller circuit. The processor also includes a display interrogator unit coupled to the display unit and the selectable CRT controller circuit for determining a display type corresponding to the display unit, wherein when the display type is a non-CRT type display, the display interrogator unit sends a first signal to the selectable CRT controller circuit that disables (if enabled) the CRTC circuit such that the displayable video data is sent directly to the display unit from the raster engine and wherein when the display interrogator determines that the display is a CRT type display, then the display interrogator sends a second signal to the selectable CRT controller circuit that enables the CRTC circuit (if disabled) such that the displayable video data is processed by the CRTC circuit prior to being sent to the display unit by way of the link.

#### DETAILED DESCRIPTION OF SELECTED EMBODIMENTS

[0011] Reference will now be made in detail to a particular embodiment of the invention an example of which is illustrated in the accompanying drawings. While the invention will be described in conjunction with the particular embodiment, it will be understood that it is not intended to limit the invention to the described embodiment. To the contrary, it is intended to cover alternatives, modifications, and equivalents as may be included within the spirit and scope of the

invention as defined by the appended claims.

[0012] Until most recently, almost all TVs in use today rely on a device known as the cathode ray tube, or CRT, to display their images. In order to display an image on the entire screen, electronic circuits inside the TV use magnetic deflection coils (a horizontal deflection coil to move the beam from left to right and a vertical deflection coil to move the beam up and down) to move the electron beam in a "raster scan" pattern across and down the screen. In order to display video data from a video source, such as a CPU, DVD player, etc., the video data provided by a video source at a native clock rate <sub>native</sub> is processed by a conventional video processor unit (VPU) by storing the video data in a video memory unit until such time as it is read from the memory at a memory clock rate <sub>memory</sub> and processed by a raster engine that converts the video data native format to a video signal having a displayable format based upon the characteristics of the display unit for which the image will be displayed..

[0013] A cathode ray tube (CRT) controller unit then converts the video signal using display timing by adding timing and control signals (such Hsync and Vsync) regardless of the whether or not the display unit is a cathode ray tube based display or a fixed pixel display such as an LCD. In this way, the CRT controller unit converts the video data that is read from the memory unit at the memory clock rate <sub>memory</sub> to a pixel clock rate <sub>pixel</sub> based solely upon the assumption that the display requires CRT type signals. Once the CRT controller unit has added the CRT based control and timing signals, the video signal is then passed by way of a link to the display unit at a link rate LR. Therefore, even in those situations where a pixel clock rate is not meaningful (such as with fixed pixel displays, such as LCDs), conventional video processors require that a CRT controller unit force a video signal that will not be displayed on a CRT type display to conform to legacy CRT requirements.

[0014] Accordingly, the invention describes a method, system, and apparatus that does not enforce CRT legacy requirements for those situations where a video is to be displayed on a non-CRT type display unit, such as an LCD. More specifically, the inventive video processor does not force the video signal to conform to a pixel clock but preserves the memory clock rate by transmitting the video data in video data packets at a link rate that is directly related to the memory clock rate. In this way, the inventive video processor does not require a CRT controller unit for those situations where a display unit so connected is not a CRT type display. In some embodiments, the inventive processor is dedicated to a fixed pixel display and therefore does away with the CRT controller and associated circuitry entirely whereas in other embodiments, in order to maintain compatibility with all possible display environments, a selectable CRT controller circuit is included. The selection (or de-selection) of the CRT controller and associated circuitry is based upon a query of the display attributes during an initialization process whereby the video processor queries the display whether or not it is a CRT type display.

[0015] The invention will now be described in terms of a representative LCD panel. However, it should be noted that any digital fixed pixel display, be it LCD, plasma, DLP based, is also suitable and therefore the use of an LCD panel in the following description should not be considered to limit either the scope or the intent of the invention. It should be noted that the invention is also well suited to be used in conjunction with any packet based video display interface such as described in copending U.S. Patent Application Serial No.10/726,794 ent

itled "Packet Based Video Display Interface and methods of use thereof" by Koba yashi filed December 3, 2003 and U.S. Patent Application Serial No.10/909,103 en titled "USING PACKET TRANSFER FOR DRIVING LCD PANEL DRIVER ELECTRONICS" by Kobay ashi filed concurrently with this application each of which are incorporated her ein by reference for all purposes.

[0016] Accordingly, FIG. 2 shows an exemplary video processor unit (VPU) 200 in accordance with an embodiment of the invention. The VPU 200 includes an interface 202 coupled to a video source (not shown) such as a CPU, DVD player, etc. capable of providing a video signal  $V_1$  at a native clock rate  $\text{native}$  and a native video format. It should be noted that the video source can include either or both a digital image (i.e. still or digital video) source and/or an analog image (i.e., still or analog video) source. Accordingly, the video source provides various video signals that can have any number and type of well-known formats, such as composite video, serial digital, parallel digital, RGB, or consumer digital video. The video signal can be an analog video signal provided the source includes some form of an analog video source such as for example, an analog television, still camera, analog VCR, DVD player, camcorder, laser disk player, TV tuner, set top box (with satellite DSS or cable signal) and the like. The source can also include a digital image source such as for example a digital television (DTV), digital still camera, and the like. The digital video signal can be any number and type of well known digital formats such as, SMPTE 274M-1995 (1920 x 1080 resolution, progressive or interlaced scan), SMPTE 296M-1997 (1280 x 720 resolution, progressive scan), as well as standard 480 progressive scan video.

[0017] Once received, the video data  $V_1$  is then stored (by way of a write/modify operation) in a video memory unit 204 coupled to the interface 202 at a memory space location corresponding to the video window being displayed. In most cases, the memory unit 204 is of a size sufficient to store at least a full frame of video data. In order to display the video data stored in the memory unit 204, selected portions of the video data  $V_1$  are read from the memory 204 at a memory clock rate  $\text{memory}$  and processed by a raster engine 206 that converts the video data native format to a video signal  $V_2$  having a displayable format based up on the characteristics of a display unit 208. For example, if the native format is 8 bit video data and the display unit 208 requires 24 bit video data, then the raster engine 206 has the option of utilizing a color look up table (CLUT) 210 in the conversion process.

[0018] Once the video signal  $V_2$  has been properly formatted for display on the display unit 208, a packetizer 212 packetizes the video signal  $V_2$  into a number of data packets 214 in the form of a data stream 215. The data stream 215 is transmitted to the display 208 by way of a link 216 at a transmission rate referred to as a link rate LR that is independent of the native stream rate  $\text{native}$  of the video data but is, however, directly related to the memory clock rate  $\text{memory}$  (i.e.,  $LR = \text{native} \times \text{memory}$ ). In the described embodiment, the speed, or link rate, of the link 216 can be configured to include a number of logical data channels (not shown) that can be adjusted to compensate for link conditions. For example, at 2.5 Gbps per channel, the link 216 can support SXGA 60Hz with a color depth of 18 bits per pixel over a single channel. It should be noted that a reduction in the number of channels reduces not only the cost of interconnect, but also reduces the power consumption which is an important consideration (and desirable) for power sensitive applications such as portable devices and the like. However, by increasing the number of channels to four, the link 216 can suppo

rt WQSXGA (3200 x 2048 image resolution) with a color depth of 24-bits per pixel at 60Hz. or QSXGA (2560 x 2048) with a color depth of 18-bits per pixel at 60Hz, without data compression. Even at the lowest rate of 1.0 Gbps per channel, only two channels are required to support an uncompressed HDTV (i.e., 1080i or 720p) data stream.

[0019] It should be noted, however, that the bandwidth of the link 216 must be greater than the aggregate bandwidth of all data stream(s) being transmitted over the link 216. In this way, the data packets 214 are received by and appropriately processed by a properly configured display 208 an example of which is described below without the need to generate a pixel clock at either the VPU 200 or the display 208. In one embodiment, the VPU 200 can optionally include a switch coupled to a CRT controller unit that provides the necessary CRT control signals and timing only in those cases where the display is a legacy CRT type display. In this way, the VPU can be used for any type display.

[0020] Fig. 3 shows an exemplary LCD display 300 suitable for use with the VPU 200. Accordingly, the LCD display 300 includes an LCD panel 302 having a number of picture elements 304 (pixels) that are arranged in a matrix connected to a data driver 306 by way of a plurality of data lines 308 and a plurality of gate lines 310. In the described embodiment, these picture elements 304 take the form of a plurality of thin film transistors (TFTs) 312 that are connected between the data lines 308 and the gate lines 310. During operation, each of a number of data latches 314 into which video data is stored, outputs digital data signals to an associated digital to analog converter (DAC) 316 by way of the data lines 308. Concurrently, each of a number of logic circuits 318 included in a gate driver 320 outputs a predetermined scanning signal to the gate lines 310 in sequence at timings that are in sync with a horizontal synchronizing signal. In this way, the TFTs 312 are turned ON when the predetermined scanning signal is supplied to the gate lines 310 to transmit the analog data signals supplied by the DACs 316 by way of the data lines 408 that ultimately drive selected ones of the picture elements 304.

[0021] In order to transmit the video data, the VPU 200 forms the data stream 215 that includes a number of the data packets 214 which are then received and processed by a display interface 322. In the described embodiment, the data packets 214 are then forwarded to directly to the data latches 314 included in the column driver 306 in such a way that all the video data (in the form of pixel data) used for the display of a particular frame line  $n$  of the video frame is provided to the data latches 314 within a line period. Therefore, once each data latch 314 has appropriate pixel data stored therein, the data driver 306 drive appropriate ones of the TFTs 312 in the LCD array 302.

[0022] Fig. 4 shows a high-level diagram of a data stream 400 for transmission over the link 216 formed of a number of video data packets 402 and audio data packets 404 multiplexed into the single data stream 400. In this example the video data packets 402 are consistent with UXGA graphics 1280x720p video (Stream 1 D = 1) having an associated audio in the form of the audio packets 504 (Stream 1 D = 2). In this example, each frame line is formed of at least 1280 pixels (or 3840 sub-pixels) therefore requiring 3840 data latches be used to store a single frame line of video data within the line period. For example, in one embodiment, when the data stream 400 is received at the display interface 322, a group of 3840 data packets (as defined by corresponding packet headers 406) are stored in a memory that takes the form of a frame buffer or a line buffer. It should

also be noted, however, that the memory can be bypassed or be absent altogether if a strictly pipelined architecture is desired.

[0023] FIG. 5 illustrates a system 500 that can be used to implement the invention. The system 500 is only an example of a graphics system in which the present invention can be implemented. System 500 includes central processing unit (CPU) 510, random access memory (RAM) 520, read only memory (ROM) 525, one or more peripherals 530, graphics controller 560, primary storage devices 540 and 550, and digital display unit 570. CPU 510 is also coupled to one or more input/output devices 590. Graphics controller 560 generates image data and corresponding reference signals, and provides both to digital display unit 570. The image data can be generated, for example, based on pixel data received from CPU 510 or from an external circuitry.

[0024] Although only a few embodiments of the present invention have been described, it should be understood that the present invention may be embodied in many other specific forms without departing from the spirit or the scope of the present invention. The present examples are to be considered as illustrative and not restrictive, and the invention is not to be limited to the details given herein, but may be modified within the scope of the appended claims along with their full scope of equivalents.

[0025] While this invention has been described in terms of a preferred embodiment, there are alterations, permutations, and equivalents that fall within the scope of this invention. It should also be noted that there are many alternative ways of implementing both the process and apparatus of the present invention.

It is therefore intended that the invention be interpreted as including all such alterations, permutations, and equivalents as fall within the true spirit and scope of the present invention.

### 3. BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 illustrates a raster on a conventional cathode ray tube.

FIG. 2 shows an exemplary video processor unit (VPU) in accordance with an embodiment of the invention.

FIG. 3 shows an exemplary LCD display suitable for use with the VPU shown in FIG. 2.

FIG. 4 shows a high-level diagram of a data stream for transmission over the link in accordance with an embodiment of the invention.

FIG. 5 illustrates a system that can be used to implement the invention.

1. In a video processor unit, a method of providing a video data stream at a clock rate that is independent of a pixel clock rate, comprising:

receiving native video data from a video source at a native clock rate;

storing the video data in a memory unit;

reading selected portions of the video data in a memory unit at a memory clock rate;

rasterizing the selected video data;

packetizing the rasterized video data into a number of video data packets;

sending the packetized video data to a display unit by way of a link at a link rate that is directly related to the memory clock rate.

2. A method as recited in claim 1 wherein the memory device is a line buffer arranged to store at least a quantity of video data consistent with a single frame line.

3. A method as recited in claim 1, wherein each of the video data packets includes a packet header and a packet payload, wherein the packet header includes a packet ID and wherein the packet payload includes video data suitable for driving a corresponding pixel.

4. A method as recited in claim 1, wherein the rasterizer is coupled to a color look up table.

5. A video processor for displaying video data on a non-CRT type display unit coupled thereto by way of a link, comprising:

a video memory unit having an associated memory clock rate;

a video packet transmitter unit for transmitting the video data to the non-CRT type display in the form of video data packets at a link rate that is directly related to the memory clock rate <sub>memory</sub> such that the video processor does not require a CRT controller unit.

6. A video processor as recited in claim 5, wherein the non-CRT type display is an LCD type display.

7. A video processor as recited in claim 5, further comprising:

an interface coupled to a video source arranged to provide a video signal  $V_1$  at a native clock rate <sub>native</sub> and a native video format;

a memory controller unit coupled to the interface and the video memory unit arranged to receive and then store the video data is then stored by way of a write/modify operation in the video memory unit at a memory space location corresponding to a video window being displayed; and

a raster engine coupled to the memory controller wherein in order to display the video data stored in the memory unit, selected portions of the stored video data are read from the video memory by the memory controller by way of a read operation at the memory clock rate <sub>memory</sub> and passed to the raster engine that converts video signal  $V_1$  at the native video format <sub>native</sub> to a video signal  $V_2$  having a displayable format based upon the characteristics of the display unit.

8. A video processor as recited in claim 7, further comprising:

a packetizer coupled to the raster engine arranged to packetize the video signal  $V_2$  into the video data packets;

a link interface coupling the packetizer to the link arranged to form the video data packets into a video data stream that is transmitted to the display by way of the link at a link rate LR that is independent of the native stream rate <sub>native</sub> wherein the link rate LR is directly related to the memory clock rate <sub>memory</sub>.

9. A video processor as recited in claim 8 wherein the link is configurable to include a number of adjustable logical data channels that can be adjusted to compensate for any of a number of link conditions.

10. A configurable video processor for providing displayable video data to a display unit coupled thereto, comprising:

a CRTC circuit;

a selectable CRT controller circuit coupled to the CRTC circuit;

a raster engine coupled to the selectable CRT controller circuit; a display interrogator unit coupled to the display unit and the selectable CRT controller circuit for determining a display type corresponding to the display unit, wherein when the display type is a non-CRT type display, the display interrogator unit sends a first signal to the selectable CRT controller circuit that disables (if enabled) the CRTC circuit such that the displayable video data is sent directly to the display unit from the raster engine and wherein when the display interrogator determines that the display is a CRT type display, then the display interrogator sends a second signal to the selectable CRT controller circuit that enables the CRTC circuit (if disabled) such that the displayable video data is processed by the CRTC circuit prior to being sent to the display unit by way of the link.

## 1. ABSTRACT

In a video processor unit, a method of providing a video data stream at a clock rate that is independent of a pixel clock rate. Receiving native video data from a video source at a native clock rate, storing the video data in a memory unit, reading selected portions of the video data at a memory clock rate, rasterizing the selected video data, packetizing the rasterized video data, sending the packetized video data to a display unit by way of a link at a link rate, wherein the link rate is directly related to the memory clock rate.

## 2. REPRESENTATIVE DRAWING

Fig.2

Fig. 1

Prior Art

Fig.2

Fig. 3

500

Fig. 4

High-level diagram of link traffic example