(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6139731号

(P6139731)

(45) 発行日 平成29年5月31日(2017.5.31)

(24) 登録日 平成29年5月12日(2017.5.12)

(51) Int.Cl.

F 1

H01L 31/18 (2006.01)

H01L 31/04 31/06

420 455

H01L 31/0747 (2012.01)

請求項の数 1 (全 16 頁)

(21) 出願番号 特願2016-57800 (P2016-57800)

(22) 出願日 平成28年3月23日 (2016.3.23)

(62) 分割の表示 特願2011-274196 (P2011-274196)

原出願日 平成23年12月15日 (2011.12.15)

(65) 公開番号 特開2016-106440 (P2016-106440A)

(43) 公開日 平成28年6月16日 (2016.6.16)

審査請求日 平成28年3月24日 (2016.3.24)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 一條 充弘

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 遠藤 俊弥

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 杉川 舞

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 加藤 翔

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】光電変換装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

n型の導電型を有するシリコン基板を準備する第1の工程と、

前記シリコン基板の一方の面上に、n型の導電型を有し前記シリコン基板よりもキャリア濃度の低い第1の半導体層を形成する第2の工程と、

前記第1の半導体層上に、n型の導電型を有し前記シリコン基板よりもキャリア濃度の高い第2の半導体層を形成する第3の工程と、

前記シリコン基板の他方の面上に、p型の導電型を有する第3の半導体層を形成する第4の工程と、

前記第3の半導体層上に、p型の導電型を有し前記第3の半導体層よりもキャリア濃度の高い第4の半導体層を形成する第5の工程と、 10

前記第4の半導体層上に透光性導電膜を形成する第6の工程と、

前記第2の半導体層上に第1の電極を形成する第7の工程と、

前記透光性導電膜上に第2の電極を形成する第8の工程と、

を有し、

前記第1の半導体層、前記第2の半導体層および前記第3の半導体層は、シリコンを有し、

前記第4の半導体層は、酸化モリブデンで形成され、

前記第2の工程および前記第4の工程は、原料ガスにアルゴンとモノシランを含み、両者の流量比X (X = アルゴン流量 / モノシラン流量) を  $0 < X < 0.8$ とした条件のプラ

10

20

ズマ C V D 法で行うことを特徴とする光電変換装置の作製方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ヘテロ接合型の光電変換装置の作製方法および光電変換装置に関する。

【背景技術】

【0002】

近年、二酸化炭素の排出量削減を可能にする発電手段として、光電変換装置が注目されている。その代表例としては、単結晶シリコンや多結晶シリコンなどのシリコン基板を用いた太陽電池が知られており、その変換効率を高めるための研究開発が活発に行われている

10

。

【0003】

シリコン基板を用いた太陽電池では、導電型が p 型のシリコン基板が多く用いられている。p 型シリコン基板は、n 型シリコン基板よりも拡散長が長く、基板内で発生した少数キャリアを効率良く収集しやすい。

【0004】

シリコン基板に p 型の導電型を付与する不純物としては一般的にホウ素が用いられているが、シリコン基板中にホウ素と酸素が共存していると深い準位が形成され、該準位にキャリアが捕獲されやすくなる。このため、ライフタイムが低下してしまう。この現象は、強光照射時に発生することから光劣化ともいわれ、太陽電池の変換効率を低下させる一要因となっている。

20

【0005】

上記光劣化の対策として、p 型の導電型を付与する不純物をガリウムとし、かつ低酸素濃度のシリコン基板を太陽電池に用いる技術が特許文献 1 に開示されている。

【0006】

また、n 型シリコン基板は、導電型を付与する不純物としてホウ素を含まず、光劣化の要因を有さない。さらに、シリコン基板中の不純物汚染がある場合には、電子の捕獲断面積が正孔の捕獲断面積より大きくなるため、汚染量が十分に少なければ、正孔が少数キャリアである n 型シリコン基板の方がライフタイムを大きくすることができる。したがって、最近では n 型シリコン基板を用いた太陽電池の開発も進められている。

30

【先行技術文献】

【特許文献】

【0007】

【特許文献 1】特開 2002 - 57351

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、シリコン基板の実効的なライフタイムは、バルク特性だけでなく、表面欠陥の影響も強く受ける。そのため、バルク特性改善の効果を得るには、表面欠陥の低減が重要となる。

40

【0009】

特に、光学的効果付与のためにシリコン基板に表面凹凸を設ける場合などにおいては、表面積が増加するため、表面欠陥の絶対量も増加してしまう。表面欠陥は表面再結合を促進し、実効的なライフタイムを低下させる原因となる。

【0010】

すなわち、シリコン基板の表面欠陥を極力低減させることにより、実効的なライフタイムを更に向上させることができ、光電変換装置の電気特性を向上させることができる。特に、前述の理由から、n 型シリコン基板を用いた場合に、ライフタイムを向上させやすい。

【0011】

したがって、本発明の一態様は、シリコン基板の表面欠陥を極力低減するパッシベーション

50

ン層を設けた光電変換装置の作製方法を提供することを目的の一つとする。また、当該光電変換装置を提供することを目的の一つとする。

【課題を解決するための手段】

【0012】

本明細書で開示する本発明の一態様は、シリコン基板の表面欠陥を極力低減するパッシベーション膜を設けたヘテロ接合型の光電変換装置の作製方法および当該光電変換装置に関する。

【0013】

本明細書で開示する本発明の一態様は、n型の導電型を有するシリコン基板を準備する第1の工程と、シリコン基板の一方の面上に、i型またはn型の導電型を有しシリコン基板よりもキャリア濃度の低い第1の半導体層を形成する第2の工程と、第1の半導体層上に、n型の導電型を有しシリコン基板よりもキャリア濃度の高い第2の半導体層を形成する第3の工程と、シリコン基板の他方の面上に、i型またはp型の導電型を有する第3の半導体層を形成する第4の工程と、第3の半導体層上に、p型の導電型を有し第3の半導体層よりもキャリア濃度の高い第4の半導体層を形成する第5の工程と、第4の半導体層上に透光性導電膜を形成する第6の工程と、第2の半導体層上に第1の電極を形成する第7の工程と、透光性導電膜上に第2の電極を形成する第8の工程と、を有し、第2の工程および第4の工程は、原料ガスにアルゴンとモノシランを含み、両者の流量比X(X=アルゴン流量/モノシラン流量)を $0 < X < 0.8$ とした条件のプラズマCVD法で行うことを特徴とする光電変換装置の作製方法である。

10

20

【0014】

なお、本明細書等における「第1」、「第2」などの序数詞は、構成要素の混同を避けるために付すものであり、順序や数を限定するものではないことを付記する。

【0015】

上記光電変換装置の作製方法において、第4の工程が省かれ、シリコン基板の他方の面上に第4の半導体層を形成する方法でもよい。

【0016】

上記シリコン基板に含まれる酸素の濃度は、 $8 \times 10^{17}$  atoms/cm<sup>3</sup>以下であることが好ましい。

30

【0017】

上記、第1の半導体層、第2の半導体層、第3の半導体層および第4の半導体層には、シリコン半導体層を用いることができる。または、第1の半導体層、第2の半導体層、第3の半導体層をシリコン半導体層とし、第4の半導体層を酸化物半導体層としてもよい。

【0018】

上記酸化物半導体層は、第4族乃至第8族に属する金属の酸化物で形成することが好ましい。

【0019】

また、上記酸化物半導体層は、バンドギャップが2eV以上である材料で形成することが好ましい。

【0020】

40

また、上記酸化物半導体層は、酸化バナジウム、酸化ニオブ、酸化タンタル、酸化クロム、酸化モリブデン、酸化タンゲステン、酸化マンガン、酸化レニウムで形成することが好ましい。

【0021】

本明細書で開示する本発明の他の一態様は、一对の電極間に、n型の導電型を有するシリコン基板と、シリコン基板の一方の面上に形成された、i型またはn型の導電型を有し、シリコン基板よりもキャリア濃度の低い第1の半導体層と、第1の半導体層上に形成された、n型の導電型を有し、第1の半導体層よりもキャリア濃度の高い第2の半導体層と、シリコン基板の他方の面上に形成された、i型またはp型の導電型を有する第3の半導体層と、第3の半導体層上に形成された、p型の導電型を有し、第3の半導体層よりもキャ

50

リア濃度の高い第4の半導体層と、第4の半導体層上に形成された透光性導電膜と、を有し、第1の半導体層および第3の半導体層に含有されるアルゴンの濃度は、 $1 \cdot 2 \times 10^{18}$  atoms / cm<sup>3</sup> 以上  $2 \cdot 2 \times 10^{18}$  atoms / cm<sup>3</sup> 以下であることを特徴とする光電変換装置である。

## 【0022】

上記光電変換装置の構成において、第3の半導体層が省かれ、シリコン基板の他方の面上に第4の半導体層が形成されていてもよい。

## 【0023】

上記シリコン基板に含まれる酸素の濃度は、 $8 \times 10^{17}$  atoms / cm<sup>3</sup> 以下であることが好ましい。10

## 【0024】

上記、第1の半導体層、第2の半導体層、第3の半導体層および第4の半導体層には、シリコン半導体層を用いることができる。または、第1の半導体層、第2の半導体層、第3の半導体層をシリコン半導体層とし、第4の半導体層を酸化物半導体層としてもよい。

## 【0025】

上記酸化物半導体層は、第4族乃至第8族に属する金属の酸化物で形成されていることが好ましい。

## 【0026】

また、上記酸化物半導体層は、バンドギャップが2eV以上である材料から形成されていることが好ましい。20

## 【0027】

また、上記酸化物半導体層は、酸化バナジウム、酸化ニオブ、酸化タンタル、酸化クロム、酸化モリブデン、酸化タンゲステン、酸化マンガン、酸化レニウムで形成されていることが好ましい。

## 【発明の効果】

## 【0028】

本発明の一態様を用いることにより、シリコン基板の実効的なライフタイムを向上させることができ、光電変換装置の電気特性を向上させることができる。また、電気特性が良好な光電変換装置を提供することができる。

【図面の簡単な説明】30

## 【0029】

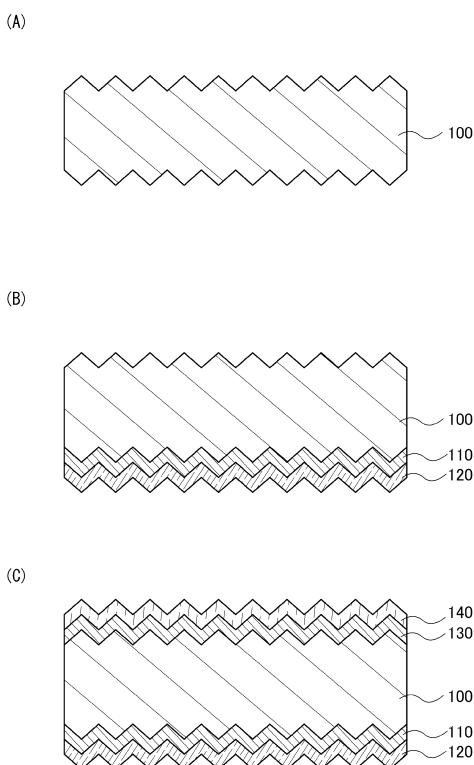

【図1】光電変換装置を説明する断面図。

【図2】光電変換装置を説明する断面図。

【図3】光電変換装置を説明する断面図。

【図4】光電変換装置を説明する断面図。

【図5】単結晶シリコン基板の両面にアルゴンを含む原料ガスで非晶質シリコン層を設けたサンプルのライフケイムを示す図。

【図6】非晶質シリコン層のTDS測定結果を示す図。

【図7】非晶質シリコン層のアルゴン濃度とライフケイムとの関係を示す図。

【図8】光電変換装置の作製方法を説明する断面図。40

【図9】光電変換装置の作製方法を説明する断面図。

【図10】シリコン基板上に酸化モリブデン膜を形成した素子のI-V特性を示す図。

【図11】酸化モリブデン膜および非晶質シリコン膜の分光透過率を示す図。

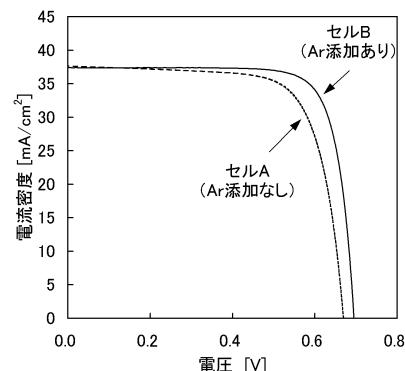

【図12】パッシベーション層へのアルゴン添加ありのセルおよびアルゴン添加なしのセルのI-V特性の比較。

## 【発明を実施するための形態】

## 【0030】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈さ50

れるものではない。なお、実施の形態を説明するための全図において、同一部分または同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略することがある。

#### 【0031】

(実施の形態1)

本実施の形態では、本発明の一態様における光電変換装置の構成および作製方法について説明する。

#### 【0032】

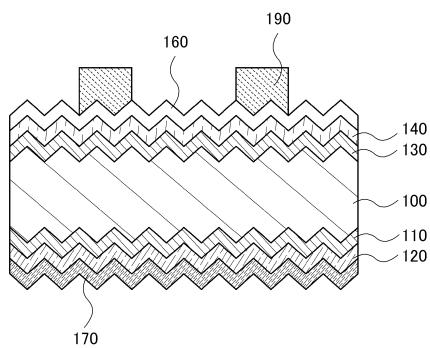

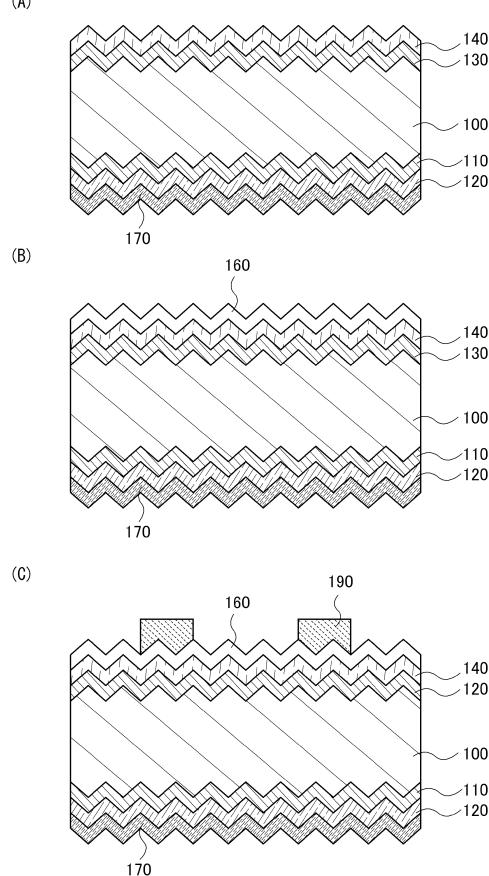

図1は、本発明の一態様における光電変換装置の断面図である。該光電変換装置は、シリコン基板100の一方の面上に第1の半導体層110、第2の半導体層120、第1の電極170が順に積層され、シリコン基板100の他方の面上には、第3の半導体層130、第4の半導体層140、透光性導電膜160、第2の電極190が順に積層された構成を有している。なお、第2の電極190はグリッド電極であり、第2の電極190が形成された面側が受光面となる。

10

#### 【0033】

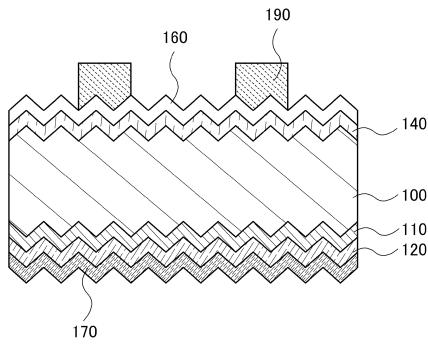

また、図2に示すように、第1の電極170もグリッド電極とし、両面を受光面とする構成としても良い。その場合は、第4の半導体層140と第1の電極170との間に、透光性導電膜180を設けることが好ましい。

#### 【0034】

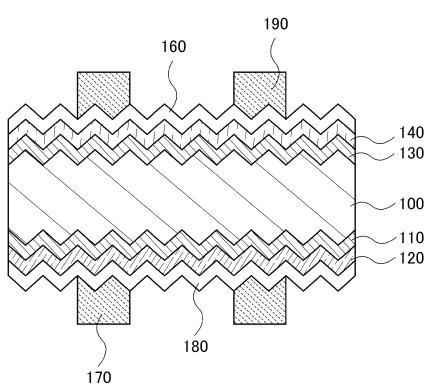

また、図3に示すように、第3の半導体層130を設けずに、シリコン基板100上に第4の半導体層140が形成される構造としてもよい。第4の半導体層140によるシリコン表面のパッシベーション効果が高い場合は、第3の半導体層130を省くことができる。

20

#### 【0035】

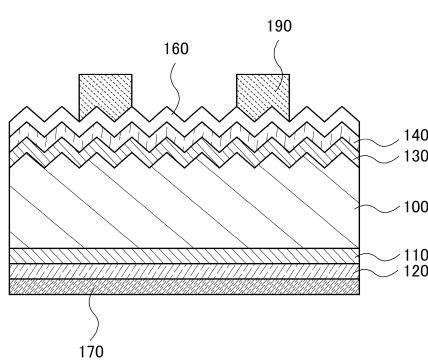

また、図1では、シリコン基板100の表裏に凹凸加工を施した例を示している。凹凸加工された面では入射光が多重反射し、光電変換領域内には光が斜めに進行することから光路長が増大する。また、裏面反射光が表面で全反射する、所謂光閉じ込め効果を起こさせることもできる。

#### 【0036】

なお、図4に例示したように、シリコン基板100の表裏のどちらか一方のみに凹凸加工を施した構成であっても良い。凹凸加工によって上記光学的効果が得られる一方で、シリコン基板の表面積が増大するため、表面欠陥の絶対量が増大してしまう。したがって、光学的効果と表面欠陥量のバランスを考慮し、より良好な電気特性が得られるように実施者が構造を決定すればよい。

30

#### 【0037】

なお、図1、図2、および図4のそれぞれの構成を任意に複合した構成、または、図2、図3、および図4のそれぞれの構成を任意に複合した構成としてもよい。

#### 【0038】

シリコン基板100には単結晶シリコン基板、または多結晶シリコン基板を用いることができる。ただし、本発明の一態様においては、n型の単結晶シリコン基板を用いることが好ましい。極力不純物を低減した単結晶シリコン基板においても少なからず不純物が含まれておあり、該不純物が形成する準位にキャリアは捕獲される。該不純物の濃度が十分に小さく、かつ同程度であるp型単結晶シリコン基板およびn型単結晶シリコン基板の比較においては、電子捕獲断面積が、正孔捕獲断面積より大きいため、正孔が少数キャリアとなるn型シリコン基板の方がライフタイムは大きくなる。

40

#### 【0039】

しかしながら、一般的な単結晶シリコン基板では、電子を少数キャリアとするp型単結晶シリコン基板の方が拡散長は大きい。そのため、n型単結晶シリコン基板を用いる場合には、拡散長を考慮して基板厚を薄くすることが好ましい。ただし、基板厚を薄くすると光の利用効率が低下するため、短絡電流密度が低下してしまう問題がある。

50

## 【0040】

基板厚を薄くせずにn型単結晶シリコン基板の拡散長を高めるには、不純物および欠陥を極力低減することが必要となる。本発明の一態様においては、低酸素濃度のn型単結晶シリコン基板を用いる。例えば、酸素濃度が $8 \times 10^{17}$  atoms / cm<sup>3</sup>以下、好ましくは $5 \times 10^{17}$  atoms / cm<sup>3</sup>以下、更に好ましくは $3 \times 10^{17}$  atoms / cm<sup>3</sup>以下のn型単結晶シリコン基板を用いる。ここで、単結晶シリコン中の酸素とは、格子間酸素を指す。このような低酸素濃度のシリコンウェハは、FZ(Floating Zone)法や、MCZ(Magnetic field applied Czochralski)法などで作製することができる。また、上記酸素濃度は、フーリエ変換赤外分光法(換算係数 $4.81 \times 10^{17} / \text{cm}^2$ )で求めることができる。

10

## 【0041】

第1の半導体層110および第3の半導体層130には、水素を含む欠陥の少ないシリコン半導体層を用いることができ、シリコン基板100の表面の欠陥を終端することができる。例えば、第1の半導体層110および第3の半導体層130には、プラズマCVD法で形成される非晶質シリコンを用いることができる。

## 【0042】

シリコン基板100の導電型がn型であるならば、第1の半導体層110には、シリコン基板100よりもキャリア濃度の低いi型またはn型のシリコン層、第3の半導体層130には、i型またはp型のシリコン層を用いることができる。

## 【0043】

なお、本明細書において、i型の半導体とは、フェルミ準位がバンドギャップの中央に位置する所謂真性半導体の他、半導体に含まれるp型を付与する不純物およびn型を付与する不純物が共に $1 \times 10^{18} \text{ cm}^{-3}$ 以下の濃度であり、暗伝導度に対して光伝導度が高い半導体を指す。

20

## 【0044】

なお、本明細書では、同じ導電型でキャリア濃度の異なる材料を区別する必要がある場合には、相対的にキャリア濃度の高いn型材料またはp型材料の導電型をn<sup>+</sup>型またはp<sup>+</sup>型、相対的にキャリア濃度の低いn型材料またはp型材料の導電型をn<sup>-</sup>型またはp<sup>-</sup>型と呼称する。

## 【0045】

第1の半導体層110にn型のシリコン層を用いる場合には、n<sup>-</sup>型のシリコン層を用いることが好ましい。このとき、n<sup>-</sup>型のシリコン層の暗伝導度は、 $1 \times 10^{-9} \text{ S / cm} \sim 1 \times 10^{-4} \text{ S / cm}$ 、好ましくは $1 \times 10^{-8} \text{ S / cm} \sim 1 \times 10^{-5} \text{ S / cm}$ 、さらに好ましくは $1 \times 10^{-8} \text{ S / cm} \sim 1 \times 10^{-6} \text{ S / cm}$ とする。

30

## 【0046】

第3の半導体層130にp型のシリコン層を用いる場合には、p<sup>-</sup>型のシリコン層を用いることが好ましい。このとき、p<sup>-</sup>型のシリコン層の暗伝導度は、 $1 \times 10^{-10} \text{ S / cm} \sim 1 \times 10^{-5} \text{ S / cm}$ 、好ましくは $1 \times 10^{-9} \text{ S / cm} \sim 1 \times 10^{-6} \text{ S / cm}$ 、さらに好ましくは $1 \times 10^{-9} \text{ S / cm} \sim 1 \times 10^{-7} \text{ S / cm}$ とする。

## 【0047】

また、本発明の一態様では、第1の半導体層110および第3の半導体層130にアルゴンを含むシリコン層を用いる。アルゴンを含む原料ガスを用いてシリコン層をパッシベーション層としてシリコン基板表面に形成することで、シリコン基板の表面欠陥を極力低減させることができる。

40

## 【0048】

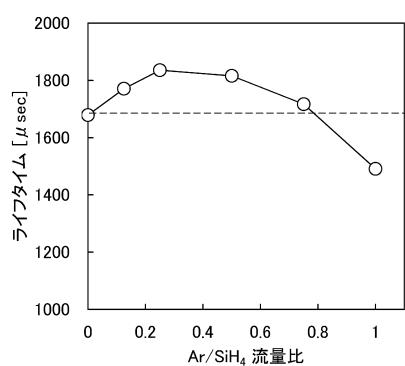

図5は、アルゴンを含む原料ガスを用いて、パッシベーション層として非晶質シリコンをn型単結晶シリコン基板の両面に形成したサンプルのライフトайムを示す図である。該非晶質シリコンは、プラズマCVDを用い、反応室に原料ガス(アルゴン：モノシラン=1:(0~1))を導入し、反応室内の圧力を160Pa、電極間隔を17mm以下、カソード電極の面積を基準とする電力密度を40mW/cm<sup>2</sup>(RF電源60MHz)、基板

50

温度を220℃以下とする条件で抵抗率約9Ω·cmのn型単結晶シリコン基板上に膜厚100nmで形成している。また、ライフタイムは、μPCD(microwave detected photoconductivity decay)法を用いて測定している。

#### 【0049】

図5に示すように、原料ガス中のアルゴン比率を変化させることで、ライフタイムは極大値を有するように変化する傾向を示す。すなわち、原料ガス中のアルゴン比率には適切な範囲があることがわかる。アルゴン添加なしで形成したサンプルを基準にすると、原料ガスの流量比X(X=アルゴン流量/モノシラン流量)は、 $0 < X < 0.8$ (0より大きく0.8より小さい値)が好ましく、 $0.1 \leq X \leq 0.7$ (0.1以上0.7以下の値)がより好ましく、 $0.1 \leq X \leq 0.6$ (0.1以上0.6以下の値)がさらに好ましいといえる。

10

#### 【0050】

アルゴンを含む原料ガスを用いた場合においては、被成膜面を適度にアルゴンが覆い、プラズマ化したモノシランからのプラズマダメージを緩和することができる。ただし、アルゴンを多く含む原料ガスでは、プラズマ化したアルゴン自身によっても被成膜面にプラズマダメージを与えるため、アルゴンは適切な上記範囲の量を添加することが好ましい。

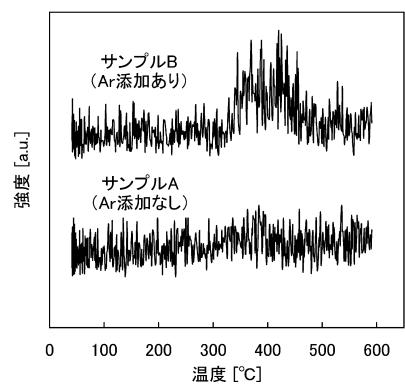

#### 【0051】

また、図6は昇温脱離ガス分析(TDS: Thermal Desorption Spectrometry)を用い、ガラス基板上に非晶質シリコン層を形成したサンプルのアルゴン(m/z=40)の挙動を調べた結果である。比較したサンプルには、モノシランのみを原料ガスとして形成したサンプルA、およびアルゴン/モノシラン=0.25の比率の原料ガスで形成したサンプルBを用いている。サンプルAでは、アルゴンは検出されず、サンプルBでは、約300~500Kの昇温でアルゴンが検出されていることがわかる。

20

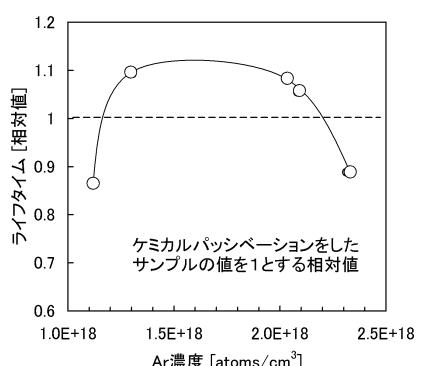

#### 【0052】

また、図7は、アルゴン添加量の異なる複数のサンプルのTDS分析とライフタイム測定を行い、非晶質シリコン層中のアルゴン濃度とライフタイムとの関係を調べた結果である。なお、非晶質シリコン層中のアルゴン濃度は、TDS分析を室温(25℃)~600Kで行い、その間に放出されるアルゴン(m/z=40)の総量、サンプル面積、およびサンプルの膜厚から算出している。また、ライフタイムは、ヨウ素アルコール溶液によるケミカルパッシベーションを行ったn型の単結晶シリコン基板のライフタイムを1として規格化した相対値で表している。

30

#### 【0053】

図5と同様に、ライフタイムは極大値を有するように変化し、膜中のアルゴン濃度には適切な範囲があることがわかる。ケミカルパッシベーションのサンプルを基準にすると、膜中のアルゴン濃度は、 $1.2 \times 10^{18}$ atoms/cm<sup>3</sup>以上 $2.2 \times 10^{18}$ atoms/cm<sup>3</sup>以下が好ましく、 $1.3 \times 10^{18}$ atoms/cm<sup>3</sup>以上 $2.1 \times 10^{18}$ atoms/cm<sup>3</sup>以下がより好ましいといえる。膜中に含まれるアルゴンはシリコンと結合を作らず、適量の場合は膜の応力緩和などの効用があり、パッシベーション層の品質向上に作用する。ただし、膜中に含まれるアルゴンが上記値より多い場合は、膜応力を誘発、シリコン同士の結合を阻害、不純物準位の形成などの不具合が生じることがあり、パッシベーション層としての品質を低下させてしまう。

40

#### 【0054】

また、本発明の一態様では、第1の半導体層110および第3の半導体層130に含まれる不純物元素を極力低減することが好ましい。プラズマCVD法等で形成されるシリコン層などには、原料ガスが高純度であっても成膜チャンバー中に残留する大気成分やクリーニングガス成分が不純物として膜中に取り込まれやすい。これらの不純物はエネルギーギャップ中に不純物準位を形成し、キャリアの捕獲などの悪影響を与える。

#### 【0055】

発明者らの実験結果では、窒素、酸素などの大気成分については、膜中の濃度を  $1 \times 10^{-7}$  atoms/cm<sup>3</sup> 以下とすることで、その影響をほとんど排除できることが判明している。また、クリーニングガスの成分であるフッ素の膜中濃度は、窒素および/または酸素の膜中濃度以下にすることが好ましいことも判明している。

#### 【0056】

上述したアルゴンを含むシリコン層を第1の半導体層110および第3の半導体層130としてシリコン基板100の表面に形成することで、該シリコン基板のライフタイムを向上させることができ、電気特性が良好な光電変換装置を形成することができる。特に、該シリコン基板の表面に凹凸を設ける場合には、その効果が顕著となる。

#### 【0057】

第2の半導体層120は、シリコン基板100と同じ導電型を有し、該シリコン基板よりもキャリア密度の高い層である。例えば、第2の半導体層120には、n型となる不純物が添加された非晶質シリコンまたは微結晶シリコンを用いることができる。

#### 【0058】

本発明の一態様において、シリコン基板100がn型である場合には、シリコン基板100と第2の半導体層120との間には、第1の半導体層110を介してn-n<sup>+</sup>接合が形成される。つまり、第2の半導体層120は、B S F層(B a c k S u r f a c e F i e l d層)として作用する。B S F層を形成することにより、少数キャリアがp-n接合側にはね返されることから、第1の電極170近傍でのキャリアの再結合を防止することができる。

#### 【0059】

第4の半導体層140は、シリコン基板100の導電型とは逆の導電型を有し、第3の半導体層130よりもキャリア密度の高い層である。シリコン基板100がn型の場合には、第4の半導体層140はp型(p<sup>+</sup>型)であり、シリコン基板100と第4の半導体層140との間には、第3の半導体層130を介してp-n接合が形成される。例えば、第4の半導体層140には、p型となる不純物が添加された非晶質シリコンまたは微結晶シリコンを用いることができる。

#### 【0060】

次に、図1に示した光電変換装置の作製方法について図8および図9を用いて説明する。

#### 【0061】

本実施の形態では、シリコン基板100にM C Z法で形成した酸素濃度が  $8 \times 10^{-7}$  atoms/cm<sup>3</sup>以下のn型単結晶シリコン基板を用いる。なお、表裏に凹凸加工を行う場合は、単結晶シリコン基板の表面に(100)面を有する基板を用いることが好ましい。

#### 【0062】

次に、シリコン基板100の表裏に凹凸加工を行う。なお、以下の説明は、表面に(100)面を有する単結晶シリコン基板をシリコン基板100として用いる場合に適用できる。シリコン基板100に多結晶シリコン基板を用いる場合は、ドライエッチング法などで凹凸加工を行えばよい。

#### 【0063】

初期のシリコン基板100がスライス加工のみである基板の場合は、シリコン基板100の表面から10~20 μmに残留するダメージ層をウエットエッチング工程にて取り除く。エッチング液には、比較的高濃度のアルカリ溶液、例えば、10~50%の水酸化ナトリウム水溶液、または同濃度の水酸化カリウム水溶液を用いることができる。または、フッ酸と硝酸を混合した混酸や、それらに酢酸を混合した混酸を用いても良い。

#### 【0064】

次に、ダメージ層除去後のシリコン基板表面に付着している不純物を酸洗浄で取り除く。酸としては、例えば、0.5%フッ酸と1%過酸化水素水の混合液(F P M)などを用いることができる。またはR C A洗浄などを行っても良い。なお、この酸洗浄工程は省いても良い。

10

20

30

40

50

## 【0065】

凹凸は、結晶シリコンのアルカリ溶液によるエッティングにおいて、面方位に対するエッティングレートの違いを利用して形成する。エッティング液には比較的低濃度のアルカリ溶液、例えば、1～5%の水酸化ナトリウム水溶液、または同濃度の水酸化カリウム水溶液を用いることができ、好ましくは、数%のイソプロピルアルコールを添加する。エッティング液の温度は70～90とし、30～60分間、シリコン基板をエッティング液に浸漬する。この処理により、シリコン基板100表面上に、微細な略四角錐状の複数の凸部、および隣接する凸部間で構成される凹部からなる凹凸を形成することができる。

## 【0066】

次に、上述の凹凸を形成するためのエッティング工程では、シリコン基板100の表層に不均一な酸化層が形成されるため、該酸化層を取り除く。また、該酸化層にはアルカリ溶液の成分が残存しやすいため、それを取り除く目的もある。アルカリ金属、例えばNaイオンやKイオンがシリコン中に侵入するとライフタイムが劣化し、光電変換装置の電気特性が著しく低下してしまう。なお、この酸化層を除去するには、1～5%の希フッ酸を用いれば良い。

10

## 【0067】

次に、フッ酸と硝酸を混合した混酸、または、それらに酢酸を混合した混酸を用いてシリコン基板100の表面をエッティングし、金属成分などの不純物を除去することが好ましい。酢酸を混合することで、硝酸の酸化力を維持し、エッティング工程を安定にする効果、およびエッティングレートを調整する効果が得られる。例えば、各酸の体積比率は、フッ酸：硝酸：酢酸=1：(1.5～3)：(2～4)とすることができる。なお、本明細書では、フッ酸、硝酸および酢酸の混酸液をフッ硝酢酸と呼ぶ。また、このフッ硝酢酸を用いたエッティング工程では、凸部の頂点の断面における角度を大きくする方向に変化させることから、表面積が低減し、表面欠陥の絶対量を低減することができる。なお、このフッ硝酢酸を用いたエッティングを行う場合は、上述の希フッ酸を用いた酸化層の除去工程を省くこともできる。ここまで工程により、図8(A)に示すシリコン基板100の断面形状が形成される。

20

## 【0068】

次いで、適切な洗浄の後、シリコン基板100の一方の面上にプラズマCVD法を用いて第1の半導体層110を形成する。第1の半導体層110の厚さは3nm以上100nm以下とすることが好ましい。本実施の形態において、第1の半導体層110は、アルゴンが添加された*i*型の非晶質シリコン層であり、膜厚は5nmとする。

30

## 【0069】

第1の半導体層110は、例えば、反応室に原料ガス（アルゴンおよびモノシラン）を導入し、反応室内の圧力を100Pa以上200Pa以下、電極間隔を10mm以上40mm以下、カソード電極の面積を基準とする電力密度を8mW/cm<sup>2</sup>以上120mW/cm<sup>2</sup>以下、基板温度を150以上300以下とする条件で形成することができる。前述したように、反応室に導入する原料ガス中のアルゴンおよびモノシランの流量比X(X=アルゴン流量/モノシラン流量)は、0<X<0.8とすることが好ましい。なお、該流量比率が遵守されていれば、原料ガスに水素などを加えてよい。また、第1の半導体層110を*n*<sup>-</sup>型のシリコン層とするには、上記原料ガスにホスフィンなどの*n*型のドーパントを含むガスを添加すればよい。

40

## 【0070】

次いで、第1の半導体層110上に第2の半導体層120を形成する（図8(B)参照）。第2の半導体層120の厚さは3nm以上100nm以下とすることが好ましい。本実施の形態において、第2の半導体層120は*n*型(*n*<sup>+</sup>型)の非晶質シリコンであり、膜厚は10nmとする。

## 【0071】

第2の半導体層120は、例えば、反応室にモノシランおよび水素ベースのホスフィン(0.5%)を1:(1~50)の流量比率で導入し、反応室内の圧力を100Pa以上2

50

0.0 Pa 以下とし、電極間隔を 10 mm 以上 40 mm 以下とし、カソード電極の面積を基準とする電力密度を  $8 \text{ mW/cm}^2$  以上  $120 \text{ mW/cm}^2$  以下、基板温度を 150 以上 300 以下とする条件で形成することができる。

#### 【0072】

次いで、シリコン基板 100 の他方の面上に、プラズマ CVD 法を用いて第 3 の半導体層 130 を形成する。第 3 の半導体層 130 の厚さは、3 nm 以上 100 nm 以下とすることが好ましい。本実施の形態において、第 3 の半導体層 130 は、アルゴンが添加された i 型の非晶質シリコン層であり、膜厚は 5 nm とする。

#### 【0073】

第 3 の半導体層 130 は、第 1 の半導体層 110 と同様の条件にて形成することができる。

10 なお、第 3 の半導体層 130 を p<sup>+</sup> 型のシリコン層とするには、上記原料ガスにジボランなどの p 型のドーパントを含むガスを添加すればよい。

#### 【0074】

次いで、第 3 の半導体層 130 上に第 4 の半導体層 140 を形成する（図 8 (C) 参照）。第 4 の半導体層 140 の厚さは 3 nm 以上 100 nm 以下とすることが好ましい。本実施の形態において、第 4 の半導体層 140 は p 型 (p<sup>+</sup> 型) の非晶質シリコンであり、膜厚は 10 nm とする。

#### 【0075】

第 4 の半導体層 140 は、例えば、反応室にモノシランおよび水素ベースのジボラン (0.1%) を 1 : (2 ~ 50) の流量比率で導入し、反応室内の圧力を 100 Pa 以上 200 Pa 以下とし、電極間隔を 8 mm 以上 40 mm 以下とし、カソード電極の面積を基準とする電力密度を  $8 \text{ mW/cm}^2$  以上  $50 \text{ mW/cm}^2$  以下、基板温度を 150 以上 300 以下とする条件で形成することができる。

20

#### 【0076】

なお、本実施の形態において、上記シリコンの層の形成に用いる電源には、原料ガスの分解効率の良い周波数 60 MHz の RF 電源を用いることが好ましい。原料ガスの分解効率を上げることで、シリコン表面の未結合手を終端しやすくなる。ただし、13.56 MHz、27.12 MHz、または 100 MHz の RF 電源を用いても良い。また、連続放電だけでなく、パルス放電にて形成を行っても良い。ON/OFF 制御、または High/Low 制御のパルス放電を行うことで、膜質の向上や気相中で発生するパーティクルを低減することができる。

30

#### 【0077】

次いで、第 2 の半導体層 120 上に第 1 の電極 170 を形成する（図 9 (A) 参照）。第 1 の電極 170 には、銀、アルミニウム、銅などの低抵抗金属を用いることができ、スパッタ法や真空蒸着法などで形成することができる。または、スクリーン印刷法を用いて、銀ペーストや、銅ペーストなどの導電性樹脂で形成しても良い。

#### 【0078】

次いで第 4 の半導体層 140 上に透光性導電膜 160 をスパッタ法で形成する（図 9 (B) 参照）。透光性導電膜 160 には、例えば、インジウム錫酸化物、珪素を含むインジウム錫酸化物、亜鉛を含む酸化インジウム、酸化亜鉛、ガリウムを含む酸化亜鉛、アルミニウムを含む酸化亜鉛、酸化錫、フッ素を含む酸化錫、アンチモンを含む酸化錫、またはグラフェン等を用いることができる。また、透光性導電膜 160 は単層に限らず、異なる膜の積層でも良い。例えば、インジウム錫酸化物とアルミニウムを含む酸化亜鉛の積層や、インジウム錫酸化物とフッ素を含む酸化錫の積層などを用いることができる。膜厚は総厚で 10 nm 以上 1000 nm 以下とする。

40

#### 【0079】

なお、シリコン基板 100 の表裏に設ける膜の形成順序は、上記の方法に限らず、図 9 (B) に示した構造が形成できればよい。例えば、第 1 の半導体層 110 を形成し、その次に第 3 の半導体層 130 を形成しても良い。

#### 【0080】

次いで、スクリーン印刷法を用いて、透光性導電膜 160 上に導電性樹脂を供給し、焼成して第 2 の電極 190 を形成する。ここで用いる導電性樹脂には、銀ペースト、銅ペースト、ニッケルペースト、モリブデンペーストなどを用いることができる。また、第 2 の電極 190 は、銀ペーストと銅ペーストを積層するなど、異なる材料の積層であっても良い。また、導電性樹脂の供給は、ディスペンス法やインクジェット法を用いてもよい。

#### 【0081】

なお、図 2 の構成の光電変換装置を形成するには、透光性導電膜 180 を第 2 の半導体層 120 上に設け、該透光性導電膜状に第 1 の電極 170 をグリッド状に形成する工程を行えばよい。

#### 【0082】

また、図 3 の構成の光電変換装置を形成するには、第 3 の半導体層 130 の形成工程を省けばよい。

10

#### 【0083】

また、図 4 の構成の光電変換装置を形成するには、凹凸加工工程前に凹凸を形成しない面にレジストマスクなどを設ければよい。

#### 【0084】

以上により、本発明の一態様である光電変換装置を作製することができる。

#### 【0085】

本実施の形態は、他の実施の形態、および実施例と自由に組み合わせることができる。

#### 【0086】

20

#### (実施の形態 2 )

本実施の形態では、実施の形態 1 とは異なる光電変換装置、およびその作製方法について説明する。なお、実施の形態 1 と共に通する点については、その詳細を省略する。

#### 【0087】

本実施の形態に示す光電変換装置は、実施の形態 1 で説明した図 1 乃至図 4 の構成における第 4 の半導体層 140 の構成材料のみが異なり、その他は同じである。

#### 【0088】

なお、本実施の形態に示す光電変換装置は、図 1、図 2、および図 4 のそれぞれの構成を任意に複合した構成、または、図 2、図 3、および図 4 のそれぞれの構成を任意に複合した構成としてもよい。

30

#### 【0089】

本実施の形態に示す光電変換装置の第 4 の半導体層 140 には、バンドギャップが 2 eV 以上、好ましくは 2.5 eV 以上の遷移金属酸化物を主成分とする酸化物半導体層を用いることができる。特に元素周期表における第 4 族乃至第 8 族に属する金属の酸化物であることが好ましい。該金属の酸化物は、シリコンが光吸収を示す波長範囲において、高い透光性を有する。

#### 【0090】

具体的に上記酸化物半導体層としては、酸化バナジウム、酸化ニオブ、酸化タンタル、酸化クロム、酸化モリブデン、酸化タンゲステン、酸化マンガン、酸化レニウムなどを用いることができる。中でも特に、酸化モリブデンは大気中でも安定であり、吸湿性が低く、扱いやすいため好ましい。

40

#### 【0091】

また、上記酸化物半導体層は、不純物を添加することにより、導電型を変化させることができる。また、上記酸化物半導体は、故意に不純物を添加しない場合においても、金属酸化物中の欠陥や成膜工程中に取り込まれた微量の不純物がドナー準位またはアクセプタ準位を形成するため、n 型または p 型の導電型を示す。

#### 【0092】

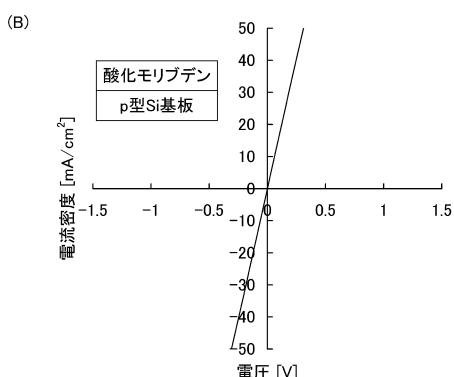

例えば、高純度化学研究所社製三酸化モリブデン粉末 (4 N M O O 3 P B) をフルウチ化学社製タンゲステンポート (B B - 3) に入れ、 $1 \times 10^{-4}$  Pa 以下の真空下で、0.2 nm / 秒の成膜速度でシリコン基板上に抵抗加熱蒸着を行うと、シリコン基板の導

50

電型の違いで I - V 特性の異なる素子が形成される。図 10 ( A ) は n 型のシリコン基板上に、図 10 ( B ) は p 型のシリコン基板上に、それぞれ上記方法で酸化モリブデン膜を形成した素子の I - V 特性である。図 10 ( A ) は整流性を示し、図 10 ( B ) はオーム性を示していることから、図 10 ( A ) の特性を示す素子は p - n 接合が形成されているといえる。したがって、上記方法で成膜した酸化モリブデン膜の導電型は p 型であることがわかる。

#### 【 0 0 9 3 】

なお、上記蒸着法によって形成した酸化モリブデン膜の電気伝導度は、 $2 \times 10^{-6} \sim 3 \cdot 8 \times 10^{-3} \text{ S/cm}$  ( 暗伝導度 ) 、屈折率 1.6 ~ 2.2 ( 波長 550 nm ) 、消衰係数  $6 \times 10^{-4} \sim 3 \times 10^{-3}$  ( 波長 550 nm ) 、 Tauc プロットから求めたバンドギャップは、2.8 ~ 3 eV であった。10

#### 【 0 0 9 4 】

また、上記酸化物半導体層はパッシベーション効果が高く、シリコン表面の欠陥を低減させることができ、キャリアのライフタイムを向上させることができる。

#### 【 0 0 9 5 】

例えば、酸化モリブデンを抵抗率約  $9 \cdot \text{cm}$  の n 型の単結晶シリコン基板の両面に成膜し、パッシベーション層としたときのキャリアのライフタイムは、約  $400 \mu\text{sec}$  であることが μPCD ( microwave detected photococonductivity decay ) 法で確かめられている。20

#### 【 0 0 9 6 】

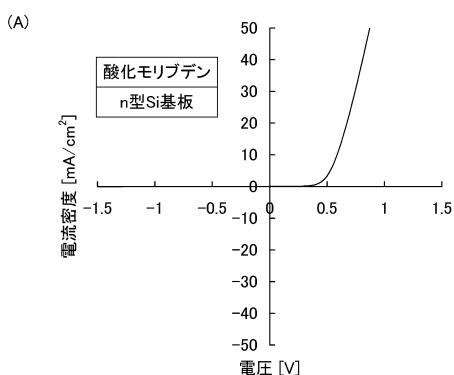

また、図 11 は、上記蒸着法でガラス基板上に形成した酸化モリブデン膜、およびプラズマ CVD 法で形成した非晶質シリコン膜の光吸収係数の比較である。酸化モリブデン膜は、広い波長範囲で光吸収係数が小さいことがわかる。

#### 【 0 0 9 7 】

上記のように広い波長範囲で光吸収係数が小さい酸化物半導体層を第 4 の半導体層 140 に用いることによって、光電変換装置の窓層での光吸収損失が低減し、光吸収領域において効率良く光電変換を行うことできるようになる。

#### 【 0 0 9 8 】

また、上述したように第 4 の半導体層 140 に用いる酸化物半導体層はシリコン表面の欠陥を低減するパッシベーション効果が高い。したがって、本実施の形態における光電変換装置は、特に第 3 の半導体層 130 が不要な図 3 の構成を含む構造とすることが好ましい。30

#### 【 0 0 9 9 】

本実施の形態における光電変換装置は、第 4 の半導体層 140 を除き、実施の形態 1 において図 8 および図 9 を説明する工程を用いて作製することができる。

#### 【 0 1 0 0 】

また、第 4 の半導体層 140 として上述した酸化物半導体層を形成するには、蒸着法、スパッタ法、またはイオンプレーティング法などの気相法により成膜することができる。膜厚は 10 ~ 100 nm とすることが好ましい。

#### 【 0 1 0 1 】

例えば、第 4 の半導体層 140 として p 型の酸化モリブデンを形成する場合、蒸着法では、酸化モリブデン材料単体の蒸着、または酸化モリブデン材料と p 型の導電型を付与する不純物を共蒸着する方法を用いればよい。共蒸着とは、一つの処理室内で複数の蒸発源から同時に蒸着を行う蒸着法である。また、スパッタ法では、酸化モリブデン、モリブデン、またはそれらに p 型の導電型を付与する不純物を含む材料をターゲットとし、酸素、または酸素とアルゴンなどの希ガスとの混合ガスをスパッタガスとする方法を用いればよい。また、イオンプレーティング法では、上記スパッタ法と同様の材料を用いて、酸素を含むプラズマ中で膜を形成すればよい。40

#### 【 0 1 0 2 】

本実施の形態は、他の実施の形態、および実施例と自由に組み合わせることができる。

10

20

30

40

50

**【実施例】****【0103】**

本実施例では、光電変換装置のセル特性について説明する。

**【0104】**

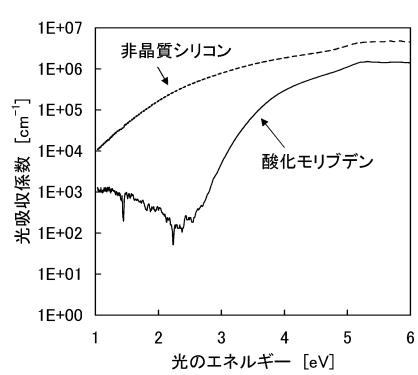

本実施例で説明する光電変換装置は、図1に示す構造であり、実施の形態1の作製方法で説明した材料および方法を用いて作製した。セルサイズは $132.25\text{ cm}^2$ であり、測定には、ソーラーシミュレータにより発生させた疑似太陽光(AM1.5、照射強度は $100\text{ mW/cm}^2$ )を用いた。

**【0105】**

図12は、パッシベーション層(第1の半導体層110および第3の半導体層130)の作製工程において、アルゴン/モノシラン流量比が0のセルAと、アルゴン/モノシラン流量比が0.25のセルBとのI-V特性を比較した図である。10

**【0106】**

セルAとセルBの比較において、特にセルBの開放電圧および曲線因子が良好であることがわかる。すなわち、パッシベーション層へのアルゴン添加によるライフタイム向上が光電変換装置の電気特性向上に寄与していることがわかる。

**【0107】**

本実施例は、他の実施の形態と自由に組み合わせることができる。

**【符号の説明】****【0108】**

|     |         |

|-----|---------|

| 100 | シリコン基板  |

| 110 | 第1の半導体層 |

| 120 | 第2の半導体層 |

| 130 | 第3の半導体層 |

| 140 | 第4の半導体層 |

| 160 | 透光性導電膜  |

| 170 | 第1の電極   |

| 180 | 透光性導電膜  |

| 190 | 第2の電極   |

10

20

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

---

フロントページの続き

(72)発明者 津屋 英樹

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 濱田 聖司

(56)参考文献 特開2010-153827(JP,A)

特開2009-152577(JP,A)

特開昭62-29180(JP,A)

特開平2-263429(JP,A)

米国特許出願公開第2009/0293948(US,A1)

特開2013-125884(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 31/00 - 31/20