(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년02월20일

(11) 등록번호 10-0804865

(24) 등록일자 2008년02월12일

(51) Int. Cl.

*H01L 21/336* (2006.01)

(21) 출원번호 10-2007-7005684(분할)

(22) 출원일자 2007년03월12일

심사청구일자 2007년03월12일

번역문제출일자 2007년03월12일

(65) 공개번호 10-2007-0034643

(43) 공개일자 2007년03월28일

(62) 원출원 특허 10-2005-7022250

원출원일자 2005년11월21일

심사청구일자 2005년11월21일

(86) 국제출원번호 PCT/US2004/015059

국제출원일자 2004년05월14일

(87) 국제공개번호 WO 2004/105090

국제공개일자 2004년12월02일

(30) 우선권주장

10/442,670 2003년05월20일 미국(US)

(56) 선행기술조사문현

US20030032274 A1

전체 청구항 수 : 총 18 항

심사관 : 김주식

## (54) 자기 정렬 구조를 갖는 반도체 디바이스 및 그 형성 방법

## (57) 요약

본 발명의 일 실시예에 의하면, 다음과 같이 반도체 디바이스가 형성된다. 실리콘이 제거될 수 있는 실리콘층의 노출된 표면 구역이 정의된다. 상기 실리콘층의 노출된 표면 구역으로부터 상기 실리콘층의 내부로 연장된 트랜치의 중간 섹션을 형성하기 위하여 상기 실리콘층의 일부가 제거된다. 실리콘이 제거될 수 있는 실리콘층의 추가적인 노출된 표면 구역이 정의된다. 상기 트랜치의 외주 섹션을 형성하기 위하여 상기 실리콘층의 추가적인 부분이 제거되어, 상기 트랜치의 외주 섹션이 상기 실리콘층의 추가적인 노출된 표면 구역으로부터 상기 실리콘층의 내부로 연장된다. 상기 트랜치의 중간 섹션은 상기 트랜치의 외주 섹션보다 상기 실리콘층의 내부로 더 깊이 연장된다.

대표도 - 도5

## 특허청구의 범위

### 청구항 1

반도체 디바이스를 형성하는 방법에 있어서,

실리콘층에 복수의 트랜치들을 형성하는 단계;

각 트랜치에 절연층을 형성하는 단계 - 각 트랜치는, 당해 트랜치에 형성된 상기 절연층이 상기 실리콘층의 당해 트랜치의 측벽에 인접한 일부분의 바로 위로 연장되도록 하는 윤곽을 가짐 -; 및

각 트랜치의 상기 절연층의 모서리를 노출시키도록 상기 트랜치들에 인접한 곳으로부터 노출된 실리콘을 제거하는 단계 - 각 트랜치의 상기 절연층의 노출된 모서리는 모든 두 개의 인접한 트랜치들 사이에 형성된 접속 개구부의 일부를 정의함 -

를 포함하는 반도체 디바이스의 형성 방법.

### 청구항 2

제1항에 있어서,

노출된 실리콘을 제거하기 전에, 상기 실리콘층에 제1 도전성 타입의 제1 영역을 형성하는 단계 - 상기 노출된 실리콘을 제거하는 단계 이후에는, 상기 제1 영역의 각 트랜치의 측벽에 인접한 부분만이 잔존하며, 각 트랜치의 측벽에 인접한 상기 제1 영역의 잔존 부분은 상기 반도체 디바이스의 소스 영역을 형성함 - 를 더 포함하되,

각 트랜치의 상기 절연층의 노출된 모서리와 함께 대응되는 소스 영역의 측벽이 모든 두 개의 인접한 트랜치들 사이의 접속 개구부의 한 측벽을 형성하는 반도체 디바이스의 형성 방법.

### 청구항 3

제1항에 있어서,

각 트랜치의 아래쪽 부분을 채우는 게이트 전극을 형성하는 단계를 더 포함하는 반도체 디바이스의 형성 방법.

### 청구항 4

반도체 디바이스를 형성하는 방법에 있어서,

실리콘층에 복수의 트랜치들을 형성하는 단계;

상기 실리콘층의 위쪽 부분에 제1 도전성 타입의 도핑된 제1 영역을 형성하는 단계;

각 트랜치에 완전히 수용된 절연층을 형성하는 단계 - 각 트랜치는, 당해 트랜치에 형성된 상기 절연층이 상기 도핑된 제1 영역의 당해 트랜치의 측벽에 인접한 일부분의 바로 위로 연장되도록 하는 윤곽을 가짐 -; 및

상기 도핑된 제1 영역의, 각 트랜치의 측벽에 인접한 부분만이 잔존할 때까지 각 트랜치에 인접한 곳으로부터 노출된 실리콘을 제거 - 상기 트랜치의 측벽에 인접한 상기 도핑된 제1 영역의 잔존 부분들이 상기 트랜치에 자기 정렬된 소스 영역들을 형성함 - 하는 단계

를 포함하는 반도체 디바이스의 형성 방법.

### 청구항 5

반도체 디바이스에 있어서,

실리콘층의 복수의 트랜치들;

각 트랜치의 위쪽 부분을 채우는 절연층 - 상기 절연층은 각 트랜치 내에 수용됨 -; 및

각 트랜치의 측벽에 인접한 상기 실리콘층에 형성된 소스 영역을 포함하되,

각 트랜치는, 당해 트랜치의 상기 절연층이 당해 트랜치의 측벽에 인접하는 상기 소스 영역의 적어도 일부분의 바로 위로 연장되도록 하는 윤곽을 갖고, 대응되는 소스 영역의 측벽과 함께 각 트랜치의 상기 절연층의 측벽이 모든 인접한 두 개의 트랜치들 사이의 접속 개구부를 형성하는 반도체 디바이스.

## 청구항 6

제5항에 있어서,

상기 접속 개구부를 통하여 적어도 상기 소스 영역들과 접속되는 금속층을 더 포함하는 반도체 디바이스.

## 청구항 7

제2항에 있어서,

상기 노출된 실리콘을 제거하는 단계는 마스크없이 수행되고, 모든 인접한 두 개의 트랜치들 사이의 접속 개구부와 각 트랜치의 측벽에 인접한 상기 도핑된 제1 영역의 잔존 부분이 자기 정렬되도록 하는 반도체 디바이스의 형성 방법.

## 청구항 8

제4항에 있어서,

상기 노출된 실리콘을 제거하는 단계는, 모든 인접한 두 개의 트랜치들 사이에 접속 개구부를 형성하는 반도체 디바이스의 형성 방법.

## 청구항 9

제8항에 있어서,

상기 노출된 실리콘을 제거하는 단계는 마스크없이 수행되고, 모든 인접한 두 개의 트랜치들 사이에 접속 개구부가 자기 정렬되도록 하는 반도체 디바이스의 형성 방법.

## 청구항 10

제8항에 있어서,

상기 도핑된 제1 영역을 형성하는 단계 이전에, 상기 실리콘층의 위쪽 부분에 제2 도전성 타입의 도핑된 제2 영역을 형성하는 단계를 더 포함하는 반도체 디바이스의 형성 방법.

## 청구항 11

제10항에 있어서,

상기 도핑된 제2 영역에 제2 도전성 타입의 고농도체 영역을 형성하기 위해 상기 접속 개구부를 통하여 불순물을 주입하는 단계를 더 포함하는 반도체 디바이스의 형성 방법.

## 청구항 12

제11항에 있어서,

상기 접속 개구부를 통해 상기 소스 영역과 상기 고농도체 영역을 전기적으로 접속시키기 위한 금속층을 형성하는 단계를 더 포함하는 반도체 디바이스의 형성 방법.

## 청구항 13

제4항에 있어서,

각 트랜치를 부분적으로 채우는 게이트 전극을 형성하는 단계를 더 포함하는 반도체 디바이스의 형성 방법.

## 청구항 14

반도체 디바이스를 제조하는 방법에 있어서,

실리콘층에 복수의 트랜치를 형성하는 단계;

각 트랜치를 부분적으로 채우는 게이트 전극을 형성하는 단계;

상기 실리콘층의 위쪽 부분에 제1 도전성 타입의 도핑된 제1 영역을 형성하는 단계;

각 트랜치에 절연층을 형성하는 단계 - 상기 절연층의 상면은 상기 도핑된 제1 영역의 상면과 실질적으로 동일 평면상에 있고, 각 트랜치는 당해 트랜치의 상기 절연층이 상기 도핑된 제1 영역 중 당해 트랜치의 측벽에 인접하는 일부분 바로 위로 연장되도록 하는 윤곽을 가짐 -; 및

1) 모든 인접한 두 개의 트랜치들 사이에 접속 개구부가 형성되고, 2) 상기 도핑된 제1 영역의, 각 트랜치 측벽에 인접하는 부분만이 잔존하도록, 트랜치들에 인접한 곳으로부터 노출된 실리콘을 제거하는 단계 - 각 트랜치의 측벽에 인접한 상기 도핑된 제1 영역의 잔존 부분은 소스 영역을 형성함 -

를 포함하는 반도체 디바이스의 제조 방법.

### 청구항 15

제14항에 있어서,

상기 노출된 실리콘을 제거하는 단계는 마스크없이 수행되고, 모든 인접한 두 개의 트랜치들 사이의 상기 접속 개구부와 각 트랜치의 측벽에 인접하는 상기 도핑된 제1 영역의 잔존 부분이 자기 정렬되도록 하는 반도체 디바이스의 제조 방법.

### 청구항 16

제14항에 있어서,

상기 도핑된 제1 영역을 형성하는 단계 이전에, 상기 실리콘층의 위쪽 부분에 제2 도전성 타입의 도핑된 제2 영역을 형성하는 단계를 더 포함하는 반도체 디바이스의 제조 방법.

### 청구항 17

제16항에 있어서,

인접한 트랜치들 사이에서 상기 도핑된 제2 영역에 제2 도전성 타입의 고농도체 영역을 형성하기 위해 상기 접속 개구부를 통하여 불순물을 주입하는 단계를 더 포함하는 반도체 디바이스의 제조 방법.

### 청구항 18

제17항에 있어서,

상기 접속 개구부를 통해 상기 소스 영역과 상기 고농도체 영역을 전기적으로 접속시키기 위한 금속층을 형성하는 단계를 더 포함하는 반도체 디바이스의 제조 방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

<6> 본 발명은 반도체 모스펫(MOSFET) 기술에 관한 것으로서, 특히 자기 정렬 구조를 갖는 트랜치 모스펫(trench MOSFET)에 관한 것이다.

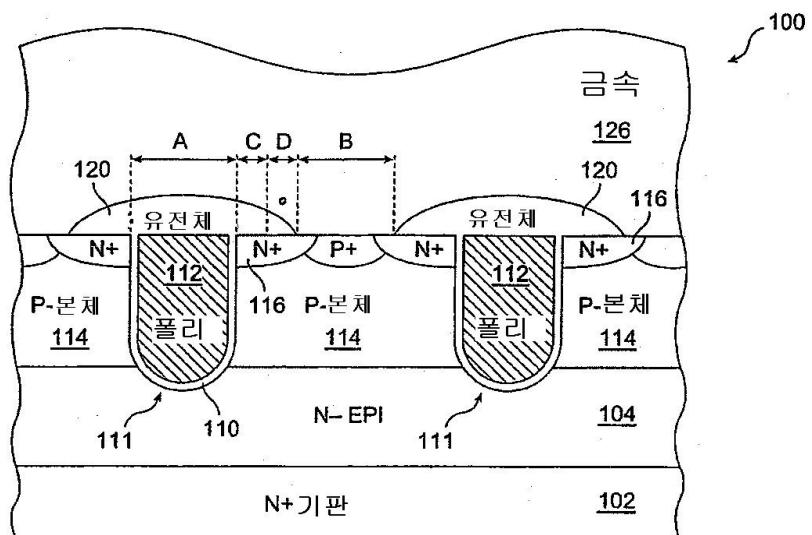

<7> 전력 모스펫(metal oxide semiconductor field effect transistor: 산화철 반도체 전계 효과 트랜지스터: "MOSFET")은 반도체 산업 분야에 널리 알려져 있다. 전력 MOSFET의 한 변형으로서, 수직 도전형 트랜치 MOSFET이 있다. 이러한 MOSFET의 단면도가 도 1에 도시되었다. MOSFET(100)은 게이트 유전체(110)에 의하여 본체 영역들(114)로부터 절연된 폴리실리콘 게이트(112)를 각각 포함하는 트랜치들(111)을 포함한다. 소스 영역들(116)은 트랜치들(111)의 각 측면에 접한다. 유전체층(dielectric layer)(120)은 그 상측에 덮이는 금속층(metal layer)(126)으로부터 게이트들(112)을 절연시킨다. 기판 영역(102) 위로 N-타입 에피택시층(104)가 확장되며, 기판 영역(102)는 MOSFET(100)의 드레인을 형성한다.

#### 발명이 이루고자 하는 기술적 과제

<8> MOSFET(100)이 온 상태로 바이어스 될 때, 전류는 소스 영역들(116)과 기판(102) 사이에서 수직으로 흐른다. 온 상태에서의 MOSFET(100)의 전류 용량은 소스 저항( $R_{ds_{on}}$ )에 대한 드레인의 함수이다. 상기 MOSFET의 전류 용량을 향상시키기 위하여, 상기  $R_{ds_{on}}$ 를 감소시킬 필요가 있다. 상기 트랜치 MOSFET의 상기  $R_{ds_{on}}$ 를 감소시키기 위한 방법의 하나로서, 트랜치의 밀도를 증가(즉, 단위 면적당 트랜치의 개수를 증가)시키는 방법이 있다. 이것은 셀 피치(cell pitch)를 감소시킴으로써 달성될 수 있다. 그러나, MOSFET의 셀 피치를 감소시키는 것은, 상기 MOSFET의 셀 구조의 상세들 및 상기 MOSFET을 제조하는 데에 사용되는 특정의 공정 레시피(recipe)에 의하여 제한된다. 상기 셀 피치를 감소시키는 것은, 포토리소그래피 장비들(photolithography tools)이 해상하도록 구성된 최소 임계 치수(minimum critical dimension), 설계 규칙에 의하여 규율되는 서로 다른 셀 영역들 사이의 최소 필요 이격(minimum required spacing), 및 오정렬 허용 오차들(misalignment tolerances) 등과 같은 제조 프로세스 기술의 제한들에 의하여 더욱 어렵게 된다.

<9> 트랜치 MOSFET(100)에 대한 최소 셀 피치를 결정하는 서로 다른 치수들이 도 1에 도시되어 있다. 치수 A는, 상기 포토리소그래피 장비들이 해상하도록 구성된 최소 트랜치 폭이며, 치수 B는, 상기 포토리소그래피 장비들이 해상하도록 구성된 최소 접속 개구부(contact opening)이며, 치수 C는 설계 규칙에 의하여 규율되는 트랜치-접속 간 최소 이격이며, 그리고, 치수 D는 접속 등록 오류 허용 오차 또는 접속 오정렬 허용 오차이다. 그러므로, MOSFET(100)에 대한 최소 셀 피치는  $A+B+2C+2D$ 이다. 프로세스 기술을 복잡하게 하지 않으면서 이러한 치수들 중의 어느 것(들)을 감소시키는 것은 이루기 어려운 일이다.

<10> 그러므로, 프로세스의 복잡성을 증가시키지 않으면서 상기 트랜치 MOSFET의 셀 피치를 감소시킬 수 있는 새로운 접근 방식이 요구된다.

### 발명의 구성 및 작용

<11> 본 발명의 일 실시예에 의하면, 반도체 디바이스가 다음과 같이 형성된다. 즉, 실리콘이 제거될 수 있는 실리콘층(silicon layer)의 노출된 표면 영역이 정의된다. 상기 실리콘층의 노출된 표면으로부터 상기 실리콘층의 내측으로 연장된 트랜치의 중간 섹션을 형성하기 위하여 상기 실리콘층의 일부가 제거된다. 실리콘이 제거될 수 있는 상기 실리콘층의 추가적인 노출된 영역이 정의된다. 트랜치의 외주 섹션을 형성하기 위하여 상기 실리콘층의 추가적인 부분이 제거되어, 상기 트랜치의 상기 외주 섹션이 상기 실리콘층의 추가적인 노출된 표면 구역으로부터 상기 실리콘층의 내측으로 연장된다. 상기 트랜치의 중간 섹션은 상기 트랜치의 외주 섹션보다 상기 실리콘층의 내측으로 더 깊이 연장된다.

<12> 본 발명의 다른 실시예에 의하면, 상기 트랜치의 상기 외주 섹션 아래까지 상기 트랜치를 부분적으로 채우는 게이트 전극이 형성된다.

<13> 본 발명의 다른 실시예에 의하면, 상기 실리콘층은 본체 영역을 포함한다. 상기 본체 영역에 제1 영역을 형성하기 위하여 불순물이 주입된다. 상기 제1 영역은, 상기 본체 영역의 표면을 따라, 또한 상기 트랜치의 외주 섹션의 바로 아래를 따라 연장된다.

<14> 본 발명의 다른 실시예에 의하면, 상기 트랜치의 상단 표면만을 가로질러 연장되는 유전체층이 형성된다. 노출된 실리콘은, (i) 상기 제1 영역의, 상기 트랜치의 외주 섹션의 바로 아래에 실질적으로 위치한 부분만이 잔존하며, 상기 제1 영역의 잔존하는 부분이 상기 반도체 디바이스의 소스 영역을 형성하며, 그리고 (ii) 상기 본체 영역의 표면 구역이 노출될 때까지 제거된다.

<15> 본 발명의 다른 실시예에 의하면, 상기 유전체층의 측벽이 노출된다. 각 소스 영역의 노출된 측벽과 함께 상기 유전체층의 노출된 측벽은, 상기 본체 영역과 소스 영역을 접속시키는 접속 개구부의 측벽을 형성한다.

<16> 본 발명의 다른 실시예에 의하면, 반도체 디바이스는 다음과 같이 형성된다. 실리콘층 위로 마스크층이 형성된다. 상기 마스크층은 그를 통해 상기 실리콘층이 노출되는 개구부를 포함한다. 상기 실리콘층은, 상기 마스크층의 개구부를 통하여 등방성으로 식각되어 상기 실리콘층의 사발 형상 부분(bowl-shaped portion)이 제거되도록, 등방성으로 식각된다. 상기 사발 형상 부분은, 실리콘층의 노출된 표면을 따라 중간 부분과, 상기 마스크층 바로 아래에 연장된 외주 부분을 포함한다. 상기 마스크층 바로 아래에 연장된, 상기 제거된 실리콘층의 외주 부분은 트랜치의 외주 섹션을 형성한다. 상기 실리콘층의 추가적인 부분이, 상기 트랜치의 상기 외주 섹션보다 상기 실리콘층의 내측으로 더 깊이 연장된 상기 트랜치의 중간 섹션을 형성하도록, 상기 마스크층의 개구부를 통하여 제거된다.

<17> 본 발명의 또 다른 실시예에 의하면, 반도체 디바이스는 다음과 같이 형성된다. 실리콘층에 복수의 트랜치들이

형성된다. 상기 실리콘층에 제1 도전성 타입(conductivity type)의 제1 영역이 형성된다. 각 트랜치의 위쪽 부분을 채우는 절연층이 형성된다. 노출된 실리콘은, 적어도 (i) 각 트랜치의 상기 절연층의 모서리가 노출되고, 그리고 (ii) 상기 제1 영역의, 각 트랜치의 측벽에 인접한 부분만이 잔존할 때까지 제거된다. 각 트랜치의 측벽에 인접한 상기 제1 영역의 잔존하는 부분은 상기 반도체 디바이스의 소스 영역을 형성한다.

<18> 본 발명의 또 다른 실시예에 의하면, 반도체 디바이스는 실리콘층의 트랜치를 포함한다. 소스 영역은 상기 트랜치의 각 측벽에 인접하여 실리콘층에 존재한다. 상기 트랜치의 측벽은 실리콘층을 따라 형성되어, 상기 트랜치의 측벽이 각 소스 영역의 적어도 일부분의 바로 위로 연장되도록 상기 트랜치의 상단 가까이에서 펼쳐지게 된다.

<19> 본 발명의 다른 실시예에 의하면, 게이트 전극이 상기 트랜치를 부분적으로 채우되, 상기 트랜치의 측벽을 따라 각 소스 영역과 중첩된다. 절연층이, 상기 게이트 전극 위로 상기 트랜치의 잔존하는 부분을 채운다. 대응되는 소스 영역의 측벽과 함께 상기 트랜치의 절연층의 측벽이, 적어도 소스 영역과의 접속을 만드는 접속 개구부의 측벽을 형성한다.

<20> 본 발명의 다른 실시예에 의하면, 본체 영역은 각 트랜치의 측벽에 인접하며, 상기 본체 영역은 상기 소스 영역들과 반대되는 도전성 타입을 갖는다. 금속층이 상기 접속 개구부를 통하여 상기 본체 영역들과 상기 소스 영역들을 접속시킨다.

<21> 본 발명의 다른 실시예에 의하면, 반도체 디바이스는 실리콘층에 복수의 트랜치들을 포함한다. 절연층이 각 트랜치의 위쪽 부분을 채운다. 각 트랜치의 측벽에 인접한 실리콘층에 소스 영역이 존재하여, 대응되는 소스 영역의 측벽과 함께 각 절연층의 측벽이 모든 인접하는 두 개의 트랜치들 사이의 접속 개구부를 형성한다.

<22> 이하의 상세한 설명과 첨부된 도면은, 본 발명의 본질과 이점에 대한 보다 깊은 이해를 제공한다.

<23> 본 발명에 의하면, 프로세스의 복잡성을 증가시키지 않으면서 셀 피치를 감소시키는 결과를 달성하는, 자기 정렬 구조를 갖는 트랜치 모스펫의 구조 및 형성 방법이 개시된다. 일 실시예에 의하면, 트랜치의 측벽들이 소스 영역들 위로 트랜치의 상단 가까이에서 펼쳐지도록 에피택시층(epitaxial layer)에 트랜치들이 형성된다. 상기 소스 영역들과 함께 각 트랜치의 상단 부분을 따라 형성된 절연층이, 상기 소스와 본체(body) 영역들을 접속시키기 위한 인접한 트랜치들 사이의 접속 개구부(contact opening)를 정의한다. 이러한 트랜치 구조 및 형성 방법은 소스 영역들과 접속 개구부들이 상기 트랜치들에 자기 정렬되도록 하는 MOSFET을 만든다. 이것은 또한, 어떠한 프로세스상의 복잡성도 야기하지 않으면서, 종래 기술의 MOSFET(100)(도 1 참조)의 셀 피치 중 2D 부분이 제거되도록 하며, 치수 B가 감소되도록 하여 결국 감소된 셀 피치를 획득하게 한다.

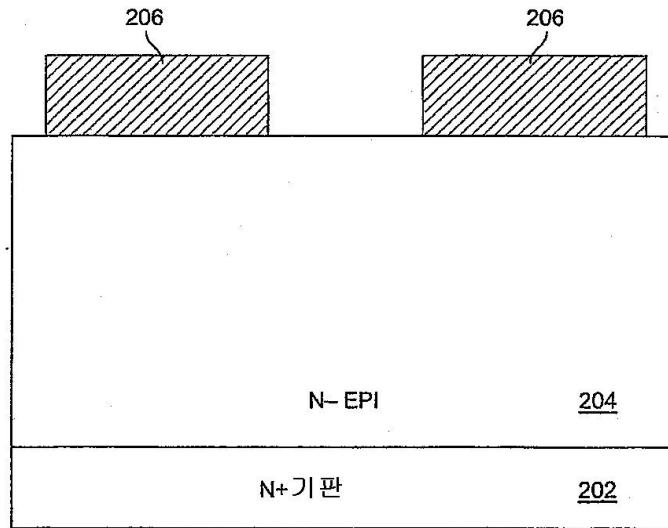

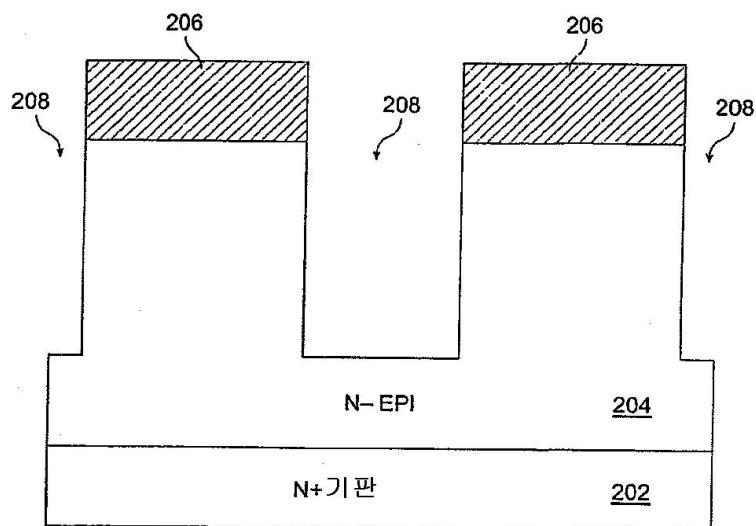

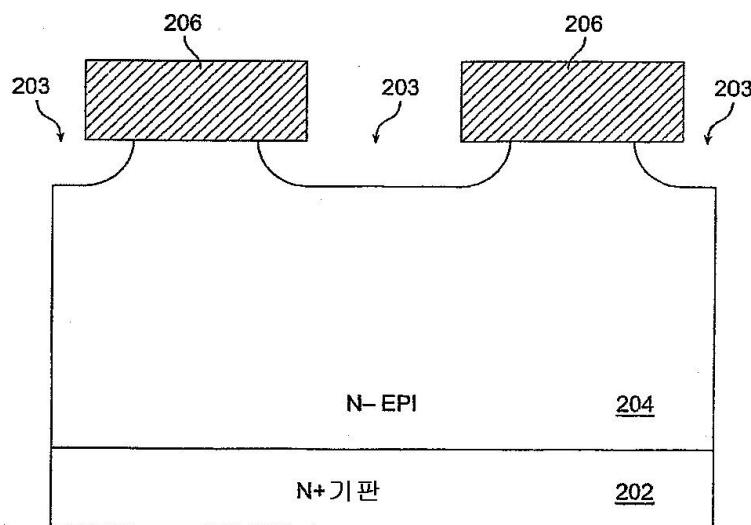

<24> 도 2a 내지 2k는 본 발명의 일실시예에 따른 트랜치 MOSFET의 제조 과정 중 서로 다른 단계들에서의 단면도이다. 도 2a를 참조하면, 저농도로 도핑된 N-타입 에피택시층(204)가 고농도로 도핑된 N-타입 기판(202) 위로 확장되어 있다. 에피택시층(204) 위에는, 2,000 내지 10,000Å 범위의 두께를 가지며, 실리콘 식각에 대하여 저항성을 갖는 물질의 층이 형성된다. 본 발명의 일 실시예에 의하면, 약 5,000Å 두께의 산화층(oxide layer)이 사용된다. 마스크 단계(masking step)를 사용하여, 실리콘 식각에 대하여 저항성인 물질의 층에서 미리 정의된 부분들이 제거되고 단지 영역들(206)만이 잔존한다. 산화층이 사용되는 실시예에 의하면, 상기 산화층의 미리 정의된 부분을 제거하는 데에, 통상적인 견식 또는 습식 식각이 사용될 수 있다.

<25> 도 2b를 참조하면, 복수의 트랜치들의 중간 섹션(mid-section)(208)을 형성하기 위하여 제1 실리콘 식각이 수행된다. 영역들(206) 사이의 간격은, 0.2 내지 2.0μm 범위의 중간 섹션(208)의 폭을 정의한다. 중간 섹션(208)은, 노출된 에피택시층(204)의 표면으로부터 0.5 내지 3.0μm 범위의 깊이까지 연장된다. 본 발명의 일 실시예에 의하면, 중간 섹션(208)의 폭과 깊이는, 각각 약 0.35μm와 0.1μm이다. 반응성 이온 식각(reactive ion etching: RIE)과 같은 실리콘 식각을 위한 통상적인 방법들이 상기 트랜치들의 중간 섹션(208)을 형성하기 위하여 사용될 수 있다.

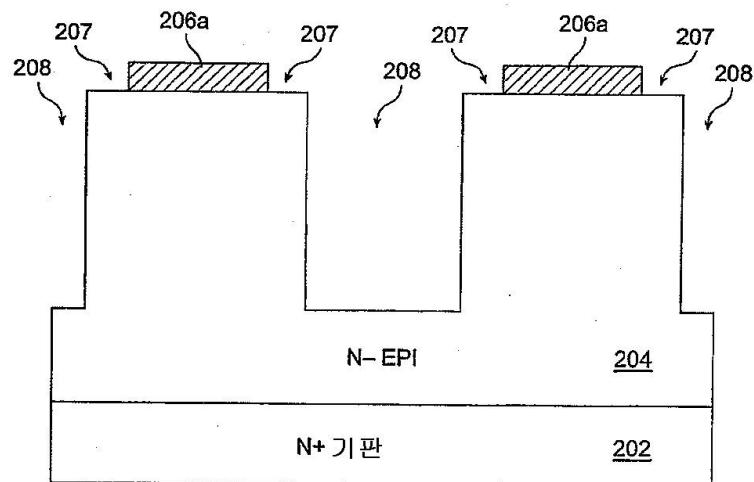

<26> 도 2c를 참조하면, 에피택시층(204)의 표면들(207)을 추가적으로 노출시키기 위하여, 영역들(206)의 부분들이 제거된다. 그리하여, 1,000 내지 9,000Å 범위의 두께를 갖는 더 좁은 영역들(206a)이 잔존한다. 영역들(206a)이 산화층에 의하여 형성되는 실시예에 의하면, 영역들(206a)은, 약 2,500Å의 두께를 갖는 더 좁은 영역들(206a)이 잔존하도록, 등방성으로 식각된다.

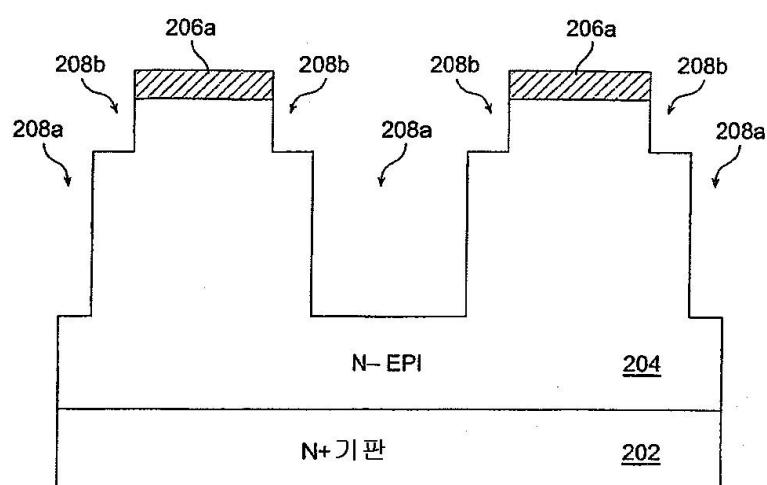

<27> 도 2d를 참조하면, 에피택시층(204)의 일부분들을 그 노출된 표면(207)을 따라 제거하여 트랜치들의 외주 섹션(208b)이 형성되도록, 제2 실리콘 식각이 수행된다. 도시된 바와 같이, 중간 섹션(208a)은 외주 섹션(208b)보다 더 깊게 연장된다. 외주 섹션(208b)은, 에피택시층(204)의 표면(208b)으로부터 0.1 내지 1.0μm 범위의 깊이

까지 연장된다. 본 발명의 일 실시예에 의하면, 외주 섹션(208b)의 깊이는 약  $0.4\mu\text{m}$ 이다. 상기 제2 실리콘 식각은, 그렇게 할 필요가 있는 것은 아니지만, 상기 중간 섹션(208)의 바닥을 따라 실리콘을 제거하기도 한다는 점을 주의하여야 한다. 제1 실리콘 식각과 마찬가지로, 상기 제2 실리콘 식각에도, 반응성 이온 식각(RIE)와 같은 통상적인 실리콘 식각 방법이 사용될 수 있다.

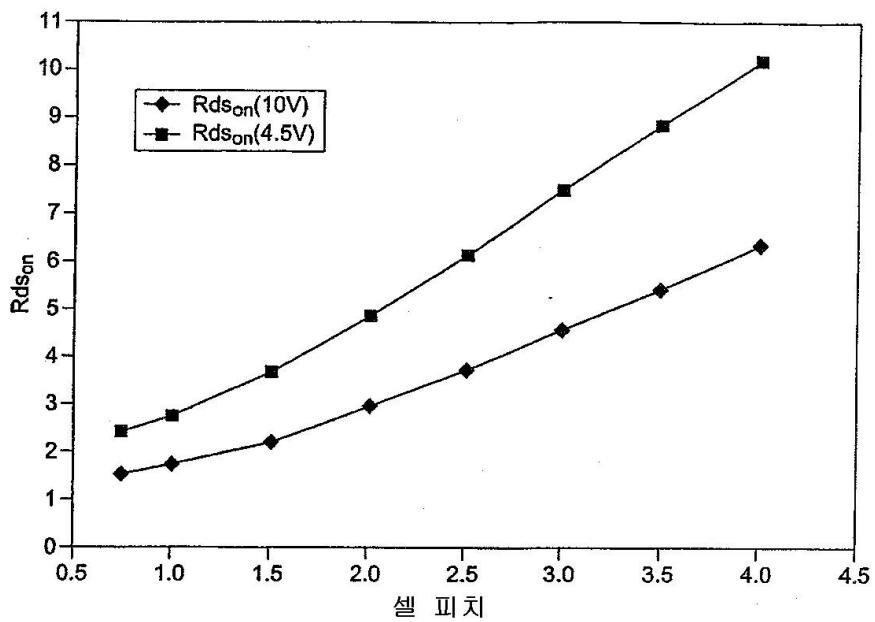

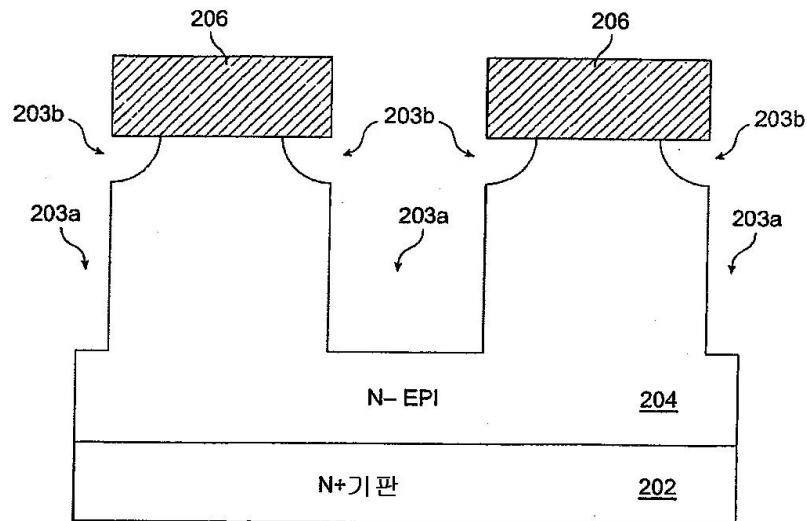

<28> 도 2a 내지 2d에서 깊은 중간 섹션과 얕은 외주 섹션을 가지는 트랜치를 형성하는 방법의 하나를 도시하였으나, 본 발명이 이 특정한 방법으로 한정되는 것은 아니다. 예를 들어, 도 4a 및 4b에 유사한 물리적 특징을 갖는 트랜치를 형성하는 다른 방법이 도시되었다. 도 2a에 도시된 바와 같이, 예컨대 산화물(oxide) 또는 포토레지스트(photoresist)를 사용하여 격리된 영역(206)을 형성한 다음, 도 4a에 도시된 바와 같이 인접한 영역들(206) 사이에서 에피택시층(204)에 개구부(203)가 형성되도록 등방성 실리콘 식각이 수행된다. 도시된 바와 같이, 상기 등방성 식각은 영역들(206) 아래의 실리콘을 제거한다. 다음으로, 영역들(206)을 그대로 유지한 채, 도 4b에 도시된 바와 같이, 상기 트랜치들의 더 깊은 중간 섹션(203a)을 형성하기 위하여 통상적인 실리콘 식각이 수행된다. 도시된 바와 같이, 각 트랜치는 깊은 중간 섹션(203a) 및 영역들(206) 아래로 연장된 얕은 외주 섹션(203b)를 갖는다.

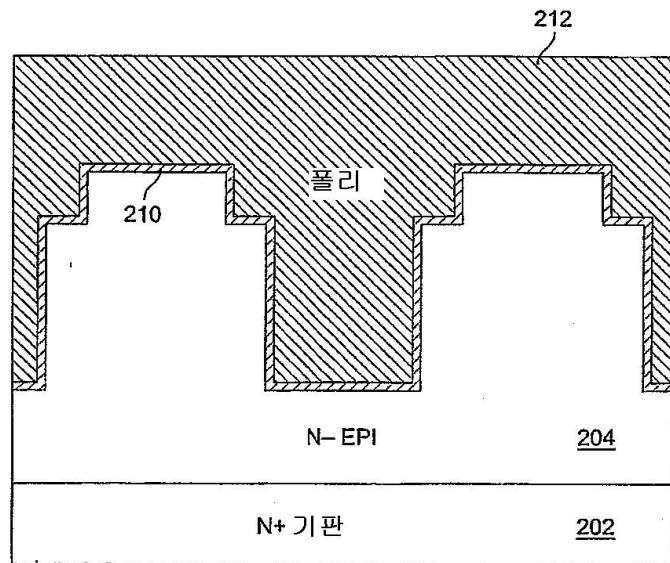

<29> 다시 도 2a 내지 2k를 참조하면, 잔존하는 영역들(206a)는, 프로세스 중 도 2e에 도시된 단계에서 선택적으로 제거될 수도 있다. 다음으로, 절연층(210)이 통상적인 방법에 의하여 에피택시층(204)의 표면을 따라 형성된다. 그리하여, 트랜치들의 측벽들이 절연층(210)으로 덮힌다. 절연층(210)은  $50\text{ nm}$  내지  $1,000\text{\AA}$  범위의 두께를 갖는다. 본 발명의 일 실시예에 의하면, 절연층(210)은 약  $400\text{\AA}$ 의 두께를 갖는 게이트 산화물(gate oxide)이다.

<30> 다음으로, 통상적인 폴리실리콘 퇴적 기술을 사용하여,  $1,000\text{ nm}$  내지  $15,000\text{\AA}$  범위의 두께를 갖는 폴리실리콘층(212)이 상기 트랜치들을 채우도록 절연층(210) 위에 퇴적된다. 본 발명의 일 실시예에 의하면, 폴리실리콘층(212)은 약  $5,500\text{\AA}$ 의 두께를 가지며, 불순물로 도핑된다. 본 발명의 다른 실시예에 의하면, 폴리실리콘층(212)을 형성하기 전에, 두꺼운 절연층이 상기 트랜치들의 중간 섹션(208a)의 바닥을 따라 형성된다. 이것은 바람직하게 상기 MOSFET의 게이트 캐apasitance(capcitance)를 감소시킨다.

<31> 도 2f를 참조하면, 폴리실리콘층(212)는 상기 트랜치의 중간 섹션(208a) 내에서 게이트들(212a)을 형성하도록 식각된다. 폴리실리콘층(212)은, 그의 상면이 상기 트랜치의 외주 섹션(208b)의 아래로 내려가도록 식각된다. 이것은, 게이트와 소스 사이를 단락시키기도 하며 이후의 프로세스에서 수행되는 소스 및 본체로의 불순물 주입을 방해하는 폴리실리콘이 상기 트랜치의 외주 섹션(208b)에 잔존하지 않도록 보장한다. 그러나, 상기 폴리실리콘층(212)가 식각되는 정도는, 이후 단계에서 형성되는 소스 영역들과 상기 게이트의 적어도 일부분이 확실히 중첩되도록 주의 깊게 제어되어야 한다. 통상적인 폴리실리콘 식각 기술이 폴리실리콘층(212)의 식각에 사용될 수 있다.

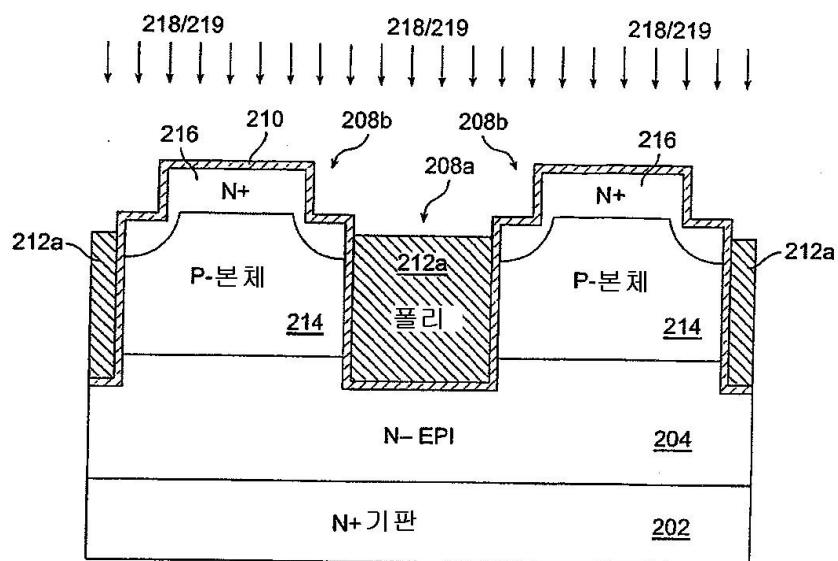

<32> 다음으로, 인접한 트랜치들 사이에 보론과 같은 P-타입의 불순물을 주입함으로써 P-타입 본체 영역(214)이 에피택시층(204)에 형성된다. 상기 P-타입 불순물의 주입은 마스크가 필요하지 않다는 것을 알려주는 화살표들(218)에 의하여 상징적으로 도시되었다. 본체 영역(214)은, 목표 채널 길이에 의하여 주로 규율되는 깊이까지 에피택시층(204) 내로 연장된다. 다음으로, 고동도로 도핑된 N-타입 영역들(216)이, 비소 또는 인과 같은 N-타입 불순물들을 주입함으로써 본체 영역들(214) 내에 형성된다. N-타입 영역들(216)은, 본체 영역들(214)의 상단 표면과, 상기 트랜치들의 외주 섹션들(208b)의 바로 아래를 따라 연장된다. 상기 N-타입 불순물의 주입은, 이 불순물 주입도 역시 마스크 작업이 필요하지 않다는 것을 알려주는 화살표들(219)에 의하여 상징적으로 도시되었다. 통상적인 이온 주입 기술이 두 불순물 주입 단계에 사용될 수 있다.

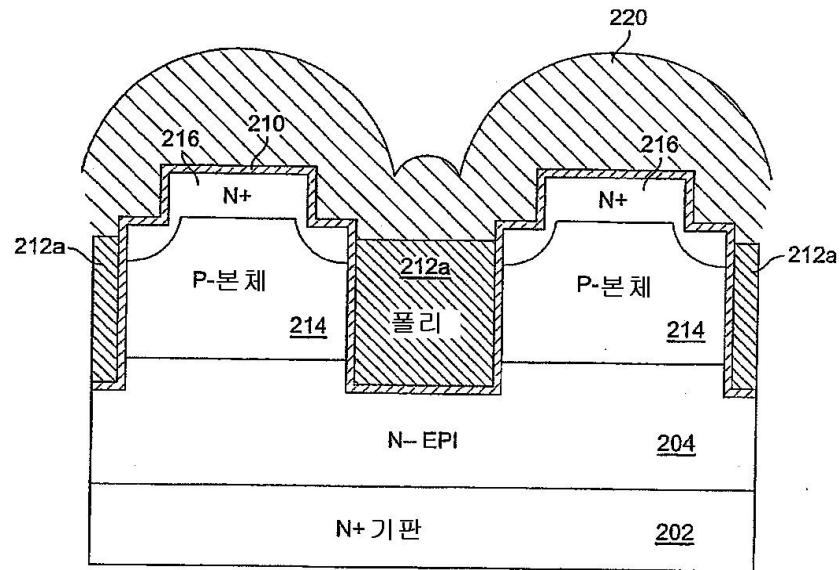

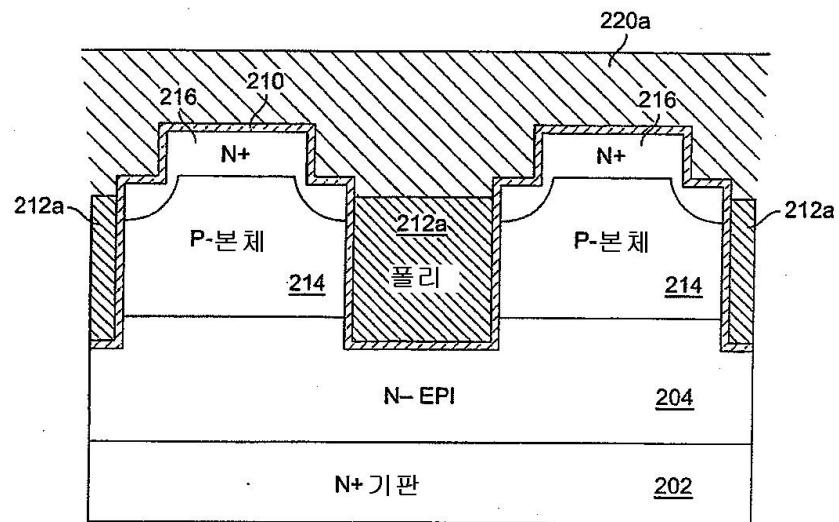

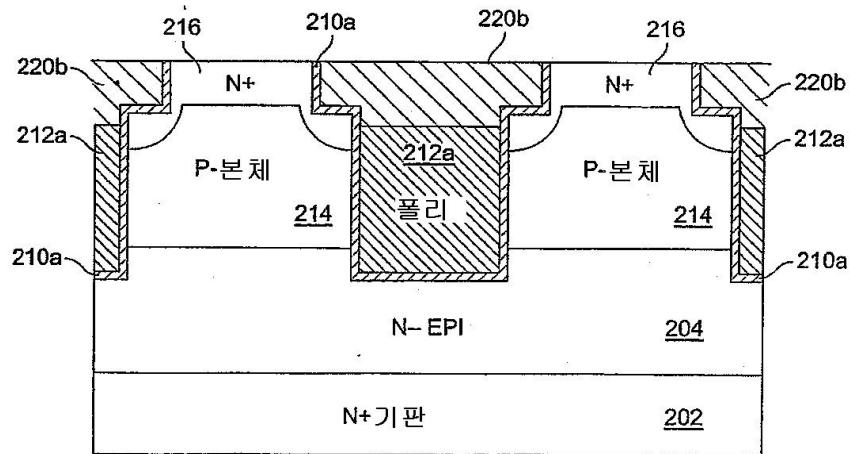

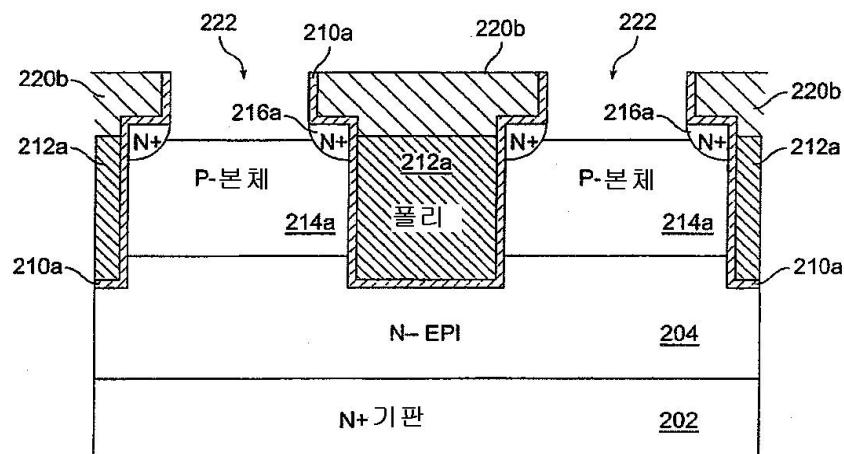

<33> 도 2g를 참조하면, BPSG와 같은 유전체층(220)이, 통상적인 기술을 사용하여 전체 구조 위에 형성된다. 유전체층(220)은  $2,000\text{ nm}$  내지  $15,000\text{\AA}$  범위의 두께를 가진다. 본 발명의 일 실시예에 의하면, 유전체층(220)의 두께는 약  $8,000\text{\AA}$ 이다. 다음으로, 도 2h에 도시된 바와 같이, 평평한 표면을 획득하기 위하여 통상적인 유전체 유동화 단계가 수행된다. 다음으로, 유전체층(220a)은, 실리콘이 도 2i에 도시된 구조에 도달할 때까지 식각된다. 유전체 식각 이후에, 상기 트랜치에 완전히 수용된 유전체 영역들(220b)가 잔존하는 한편 트랜치의 측벽을 따라 연장되는 절연층(210a)가 잔존하고, N-타입 영역들(216)의 표면이 노출된다.

<34> 도 2j를 참조하면, 접속 개구부들(222)을 형성하기 위하여 통상적인 실리콘 식각이 수행된다. 본체 영역들(214)의 상층인 N-타입 영역들(216)도 또한 제거되도록, 충분한 양의 실리콘이 제거된다. 이것은 다음을 보장한다. 즉, (i) 본체 영역들(214a)의 상측 표면이 노출되어 본체 영역들(214a)로의 접속이 만들어 질 수 있으며, (ii) 본체 영역들(214a)에 의하여 분리된 소스 영역들(216a)인 N-타입 영역(216)이 잔존하며, 그리고

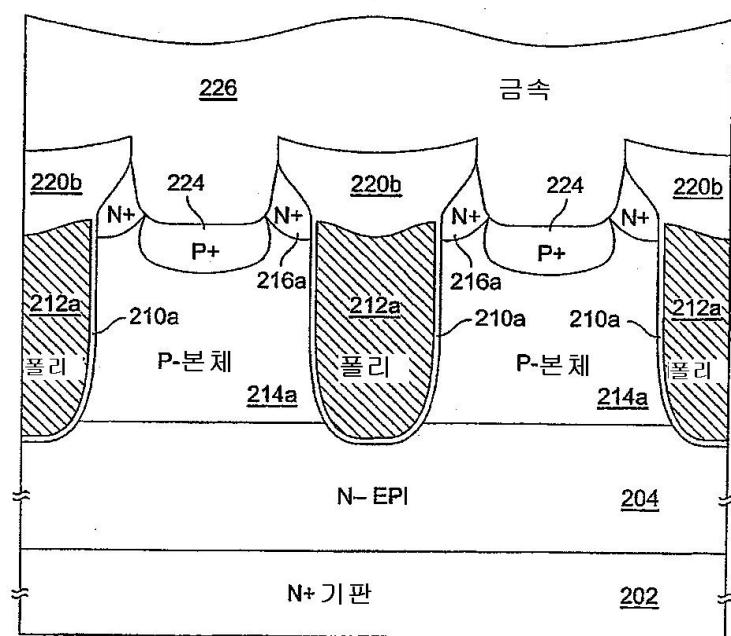

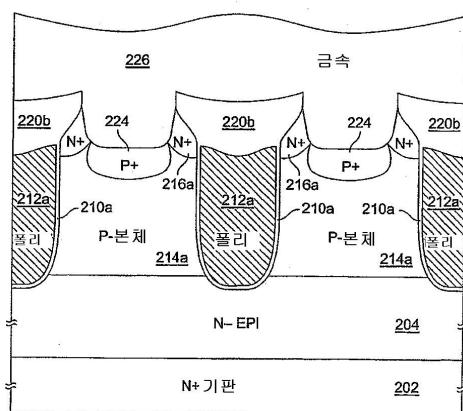

(iii) 소스 영역들(216a)의 측벽이 노출되어 소스 영역들(216a)로의 접속이 만들어 질 수 있다. 도 2k를 참조하면, 금속층(226)이, 본체 영역들(214a)와 소스 영역들(216a)을 접속시키도록 퇴적된다. 금속층(226)이 퇴적되기 전에 초고농도로 도핑된 P-타입 영역(224)의 층이, 통상적인 이온 주입 기술을 사용하여 본체 영역들(214a)의 상측 표면을 따라 선택적으로 형성될 수도 있다. 상기 초고농도로 도핑된 영역(224)은 금속(226) 및 본체 영역(214a) 사이에 오옴 접속(ohmic contact)이 완성되는 것을 돋는다. 도시된 바와 같이, 금속층(224)은, 각 트랜치의 상면을 따라 연장된 유전체층(220b)에 의하여 게이트들(212a)과는 절연된다.

<35> 도 2j를 다시 참조하면, 접속 개구부들(222)을 형성하기 위하여 수행된 실리콘 식각은, 상기 트랜치들의 외주 셙션들(208b)의 측벽들을 따라 연장된 절연층(210a)의 부분들을 노출시킨다. 도시된 바와 같이, 소스 영역들(216a)의 노출된 측벽 구역들과 함께 절연층(210a)의 노출된 부분들은, 인접된 트랜치들 사이의 접속 개구부들(222)를 유익하게 정의한다. 그러므로, 소스 영역들(216a) 또는 접속 개구부들(222)의 어느 것을 형성하기 위하여 사용되는 마스크 작업 단계 없이도, 상기 트랜치들에 자기-정렬된 소스 영역들(216a) 및 접속 개구부들(222)가 형성된다.

<36> 소스 영역들(216a) 및 접속 개구부들(222)가 상기 트랜치들에 자기-정렬되어 있기 때문에, 통상적인 기술들(도 1의 치수 D)에서와 같이 접속 오정렬을 처리할 필요가 없게 된다. 게다가, 상기 접속 개구부들(도 1에서의 치수 B)은, 통상적인 포토리소그래피 장비들(photolithography tools)이 해상하도록 구성된 것보다 더 작게 만들어질 수 있다. 그러므로, 도 1에 도시된 상기 통상적인 트랜치 MOSFET의 최소 셀 피치인  $A+B+2C+2D$ 로부터 상기 2D 항이 제거될 뿐만 아니라, B 항도 훨씬 작아질 수 있다. 그러므로, 동일한 프로세스 기술에 대하여, 프로세스상의 복잡성을 증가시키지 않으면서도 훨씬 작은 셀 피치를 달성할 수 있다.

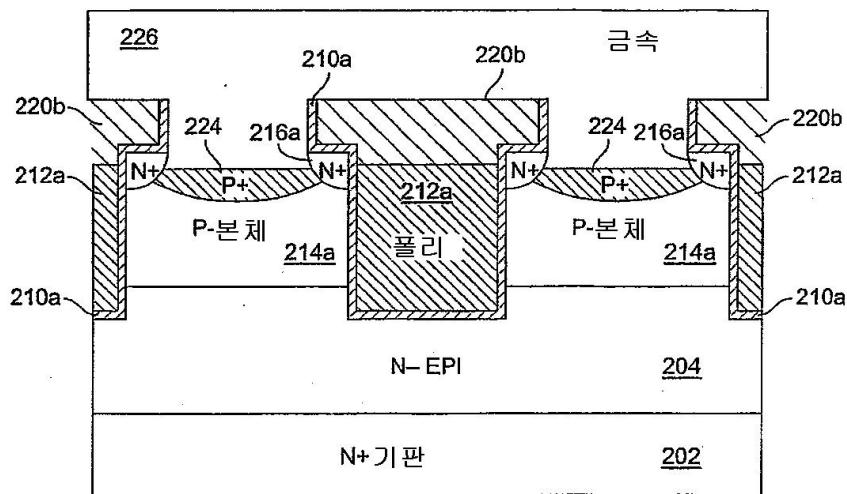

<37> 작은 셀 피치는 단위 면적당 트랜치의 개수를 증가시키는 결과를 낳으며, 이것은 다시 상기  $R_{ds_{on}}$ 를 저하시키는 바람직한 효과를 가져온다. 이것은 도 3에 더욱 명확히 도시되어 있다. 도 3은 셀 피치의 감소가  $R_{ds_{on}}$ 에 미치는 영향을 도시한 그래프이다. 수직축은  $R_{ds_{on}}$ 를 나타내며, 수평축은 셀 피치를 나타낸다. 수직축 상의 숫자는 단지 설명을 위한 것일 뿐이며,  $R_{ds_{on}}$ 의 실제 값을 반영한 것은 아니다. 두 개의 곡선이 도시되어 있는데, 위쪽의 곡선은 게이트-소스 바이어스가 4.5V인 경우에 해당하며, 아래쪽의 곡선은 게이트-소스 바이어스가 10V인 경우에 해당한다. 동일한 프로세스 기술에 대하여, 본 발명에 의한 자기-정렬 구조가 셀 피치를  $1.8\mu m$ 로부터  $1.0\mu m$ 로 감소시키는 결과를 야기한다. 이러한 셀 피치의 감소는,  $R_{ds_{on}}$ 를 10V 바이어스의 경우에 약 30% 감소시키며, 4.5V 바이어스의 경우에 약 25% 감소시키는 결과를 가져온다.

<38> 도 2a 내지 2k에 도시된 단면도들은 단지 설명을 위한 것들일 뿐이며, 셀 배열의 레이아웃이나 다른 구조적 국면을 한정시키려는 것은 아니다. 나아가, 이러한 도면들은, 모든 다양한 영역들의 실제 형상을 그들이 실제의 장치에서 보이는 대로 정확히 반영한 것은 아닐 수도 있다. 도 5는, 도 2k에 대응되는 전형적인 단면도로서, 본 발명의 일실시예에 의한 트랜치의 외형에 대한 보다 정확한 표현을 위하여 제공된 도면이다. 일부 영역들의 작은 치수들 및 온도 주기(temperature cycles)와 같은 프로세스 단계들의 영향들 때문에, 모서리들 중 많은 것들이 프로세스 동안 둥글게 된다. 결과적으로, 트랜치들은, 도 2k에 도시된 바와 같이 T자 형상이 아니라, 도 5에 도시된 바와 같이 Y자 형상으로 보이게 된다. 그러나, 본 발명이 특정한 형상의 트랜치로 한정되는 것이 아님을 이해하여야 한다.

<39> 상기한 내용은 본 발명의 실시예에 관한 온전한 기술이지만, 다양한 변경, 수정 및 균등물이 사용될 수 있다. 예를 들어, 도 2a 내지 2k에 도시된 프로세스 단계들은 N-채널 MOSFET을 제조하기 위한 것들이다. 균등한 P-채널 MOSFET을 얻기 위하여 이러한 프로세스 단계들을 수정하는 것은, 상기의 기술 내용에 비추어 본 발명의 기술 분야에서 통상의 지식을 가진 자에게 용이한 일이다. 유사하게, 절연 게이트 바이폴라 트랜지스터(IGBT)와 같은 다른 형식의 반도체 디바이스를 얻기 위하여 상기 프로세스 단계들을 수정하는 것도 또한, 상기의 기술 내용에 비추어 본 발명의 기술 분야에서 통상의 지식을 가진 자에게 용이한 일이다.

<40> 또한, 본체 영역(214)(도 2f 참조)는 프로세스 시퀀스의 더욱 초기에 형성될 수도 있다. 예를 들어, 도 2a에 도시된 바와 같이, 영역들(206)을 형성하기 전에, P-타입 불순물들이 에파텍시층(204)에 주입될 수도 있으며, 또는 P-타입 에파텍시층이 에파텍시층(204) 위에 성장될 수도 있다. 이와 유사하게, N-타입 영역들(216)(도 2f 참조)은 프로세스 시퀀스의 더욱 초기에 형성될 수도 있다. 예를 들어, 트랜치들을 형성하기 전에, 본체 영역의 고농도로 도핑된 N-타입 영역을 형성하기 위하여, N-타입 불순물의 전면적 주입(blaket implant)이 수행될 수도 있다. 그러나, 상기 고농도로 도핑된 N-타입 영역은, 상기 트랜치들이 형성된 후에 적어도 상기 N-타입 영역의 일부가 상기 트랜치들의 외주 셙션들보다 밑으로 연장되도록, 도 2f에 도시된 것보다 상기 본체 영역 내

부로 더욱 깊이 연장될 필요가 있다. 또한, 도 2j의 단계에서는 본체 영역의 표면에 도달하기 위하여, 더욱 깊은 실리콘 식각이 요구될 것이다.

<41> 또 다른 변형으로서는, 에피택시층(204)가 고정된 도핑 농도 대신에, 점차 변화하는 도핑 농도를 가질 수도 있으며, 서로 다른 도핑 농도를 갖는 복수의 에피택시층으로 이루어지거나, 설계 목표에 따라서는 완전히 제거될 수도 있다. 게다가, 트랜치들은 에피택시층(204)를 완전히 통과하여 기판(202) 내에서 끝날 수도 있다.

<42> 그러므로, 본 발명의 범위는 상기한 설명을 참조하여 결정되어서는 아니 되며, 전 범위의 균등물과 함께 첨부된 청구의 범위를 참조하여 결정되어야 한다.

### 발명의 효과

<43> 본 발명에 의하면, 프로세스의 복잡성을 증가시키지 않으면서 트랜치 MOSFET의 셀 피치를 감소시킬 수 있다.

### 도면의 간단한 설명

<1> 도 1은 통상적인 트랜치 MOSFET의 단면도이다.

<2> 도 2a 내지 2k는 본 발명의 일실시예에 따른 트랜치 MOSFET의 제조 과정 중의 서로 다른 단계들에서의 단면도이다.

<3> 도 3은 셀 피치의 감소가  $R_{ds(on)}$ 에 미치는 영향을 도시한 그래프이다.

<4> 도 4a 내지 4b는 본 발명의 다른 실시예에 따라 트랜치를 형성하는 다른 방법을 도시한다.

<5> 도 5는 도 2k에 대응되는 전형적인 단면도로서, 본 발명의 일실시예에 의한 트랜치의 외형에 대한 보다 정확한 표현을 위하여 제공된 도면이다.

### 도면

#### 도면1

도면2a

도면2b

도면2c

도면2d

도면2e

도면2f

도면2g

도면2h

도면2i

도면2j

도면2k

도면3

도면4a

도면4b

도면5