(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년04월14일

(11) 등록번호 10-1383480

(24) 등록일자 2014년04월02일

(51) 국제특허분류(Int. Cl.)

H03F 3/38 (2006.01) H04B 1/02 (2006.01)

H04B 1/18 (2006.01)

(21) 출원번호 10-2008-7028739

(22) 출원일자(국제) 2007년03월12일

심사청구일자 2012년03월12일

(85) 번역문제출일자 2008년11월24일

(65) 공개번호 10-2009-0013803

(43) 공개일자 2009년02월05일

(86) 국제출원번호 PCT/US2007/006197

(87) 국제공개번호 WO 2007/133323

국제공개일자 2007년11월22일

(30) 우선권주장

11/508,970 2006년08월24일 미국(US)

(뒷면에 계속)

(56) 선행기술조사문헌

US20040185805 A1\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

파커비전, 임크.

미국 32256 플로리다주 잭슨빌 베이메도우즈 웨이

7915

(72) 발명자

소렐즈, 레이비드, 에프.

미국 32068 플로리다주 미들버그 라이드아웃 레인

3129

톨린스, 그레고리, 에스.

미국 32746 플로리다주 히스로 하스턴 코트 155

톨린스, 마이클, 더블유.

미국 32746 플로리다주 레이크 메리 스프루스우드

로드 349

(74) 대리인

백만기, 양영준

전체 청구항 수 : 총 22 항

심사관 : 김남인

(54) 발명의 명칭 R F 전력 전송, 변조 및 증폭 시스템 및 방법

**(57) 요 약**

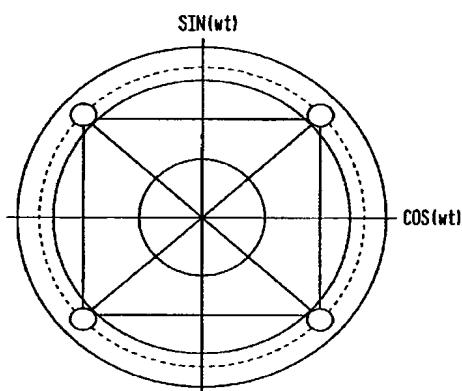

벡터 결합 전력 증폭 방법과 시스템이 개시된다. 일 실시예에서 복수의 신호가 개별적으로 증폭된 다음에 합산되어 원하는 시변 복소 포락선 신호를 구성한다. 이 신호들 중 하나 또는 그 이상의 위상 및/또는 주파수 특성은 원하는 시변 복소 포락선 신호의 원하는 위상, 주파수 및/또는 진폭 특성을 제공하도록 제어된다. 다른 실시예에서 시변 복소 포락선 신호는 복수의 일정 포락선 성분 신호로 분해된다. 이 성분 신호들은 동일하게 또는 실질적으로 동일하게 증폭된 다음 합산되어 원래의 시변 포락선 신호의 증폭 버전을 구성한다. 또한 실시예들은 주파수 상향 변환도 수행한다.

**대 표 도 - 도1**

(30) 우선권주장

11/508,989 2006년08월24일 미국(US)

11/509,031 2006년08월24일 미국(US)

60/794,121 2006년04월24일 미국(US)

60/797,653 2006년05월05일 미국(US)

60/798,705 2006년05월09일 미국(US)

---

## 특허청구의 범위

### 청구항 1

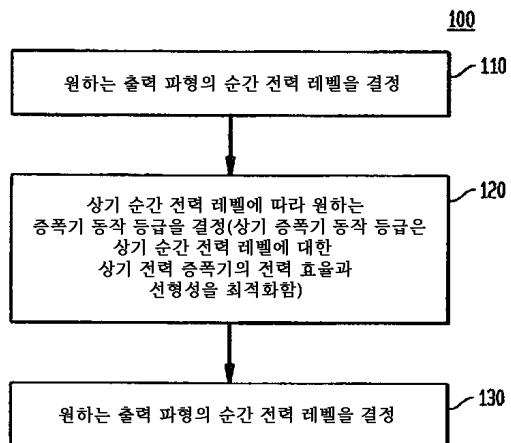

전력 증폭기에서의 실시간 증폭기 등급 제어 방법에 있어서,

출력 파형의 전력 레벨을 결정하는 단계;

상기 결정된 전력 레벨에 따라서, 상기 결정된 전력 레벨에 대한 상기 전력 증폭기의 전력 효율과 선형성 중 하나 또는 그 이상을 향상시키는 원하는 증폭기 동작 등급을 결정하는 단계; 및

상기 전력 증폭기가 상기 원하는 증폭기 동작 등급에 따라서 동작하도록 제어하는 단계

를 포함하는 실시간 증폭기 등급 제어 방법.

### 청구항 2

제1항에 있어서,

상기 제어하는 단계는 상기 전력 증폭기가 상기 출력 파형의 상기 결정된 전력 레벨에 따라서 복수의 증폭기 동작 등급 사이에서 변화하도록 제어하는 단계를 포함하는 실시간 증폭기 등급 제어 방법.

### 청구항 3

제1항에 있어서,

상기 제어하는 단계는 상기 전력 증폭기의 바이어스를 제어하는 단계를 포함하는 실시간 증폭기 등급 제어 방법.

### 청구항 4

제1항에 있어서,

상기 제어하는 단계는 상기 전력 증폭기의 하나 또는 그 이상의 입력 신호들의 진폭을 제어하는 단계를 포함하는 실시간 증폭기 등급 제어 방법.

### 청구항 5

제1항에 있어서,

상기 제어하는 단계는 (a) 상기 전력 증폭기의 하나 또는 그 이상의 입력 신호들의 위상을 제어하는 단계, (b) 상기 전력 증폭기의 바이어스를 제어하는 단계, 및 (c) 상기 전력 증폭기의 하나 또는 그 이상의 입력 신호들의 진폭을 제어하는 단계 중 하나 또는 그 이상을 포함하는 실시간 증폭기 등급 제어 방법.

### 청구항 6

제5항에 있어서,

상기 (a), (b) 및 (c)의 이용은 하나 또는 그 이상의 결정된 제어 영역들과 상기 출력 파형의 상기 결정된 전력 레벨에 기초하는 실시간 증폭기 등급 제어 방법.

### 청구항 7

제6항에 있어서,

상기 제어 영역들의 경계들은 상기 출력 파형의 보상 누적 밀도 함수(Complementary Cumulative Density Function: CCDF)와 측대역 성능 기준(sideband performance criteria)에 기초하여 결정되는 실시간 증폭기 등급 제어 방법.

### 청구항 8

제1항에 있어서,

상기 제어하는 단계는 상기 출력 파형의 궤적(trajectory)의 변화들에 따라서 상기 원하는 증폭기 동작 등급을 제어하는 단계를 포함하는 실시간 증폭기 등급 제어 방법.

### 청구항 9

제1항에 있어서,

상기 전력 증폭기는 상기 출력 파형의 복소 포락선(complex envelope)이 증가함에 따라 상기 원하는 증폭기 동작 등급과 연관된 현재의 증폭기 동작 등급보다 전력 효율 면에서 더 높은 동작 등급으로 전환하는 실시간 증폭기 등급 제어 방법.

### 청구항 10

제1항에 있어서,

상기 전력 증폭기는 상기 출력 파형의 복소 포락선이 감소함에 따라 상기 원하는 증폭기 동작 등급과 연관된 현재의 증폭기 동작 등급보다 전력 효율 면에서 더 낮은 동작 등급으로 전환하는 실시간 증폭기 등급 제어 방법.

### 청구항 11

제1항에 있어서,

상기 출력 파형의 상기 전력 레벨이 결정된 임계치를 초과할 때에 상기 전력 증폭기의 하나 또는 그 이상의 입력 신호들의 위상을 제어하는 단계를 더 포함하는 실시간 증폭기 등급 제어 방법.

### 청구항 12

제1항에 있어서,

상기 출력 파형의 상기 결정된 전력 레벨이 제1 임계치를 초과하고 제2 임계치 아래일 때에, (a) 상기 전력 증폭기의 하나 또는 그 이상의 입력 신호들의 위상, (b) 상기 전력 증폭기의 바이어스, 및 (c) 상기 전력 증폭기의 하나 또는 그 이상의 입력 신호들의 진폭 중 하나 또는 그 이상을 제어하는 단계를 더 포함하는 실시간 증폭기 등급 제어 방법.

### 청구항 13

제1항에 있어서,

상기 출력 파형의 상기 결정된 전력 레벨이 결정된 임계치 아래일 때에, (a) 상기 전력 증폭기의 바이어스 및 (b) 상기 전력 증폭기의 하나 또는 그 이상의 입력 신호들의 진폭 중 하나 또는 그 이상을 제어하는 단계를 더 포함하는 실시간 증폭기 등급 제어 방법.

### 청구항 14

제1항에 있어서,

상기 출력 파형의 상기 결정된 전력 레벨에 따라서 상기 전력 증폭기의 출력 전류를 제어하는 단계를 더 포함하는 실시간 증폭기 등급 제어 방법.

### 청구항 15

전력 증폭 장치에 있어서,

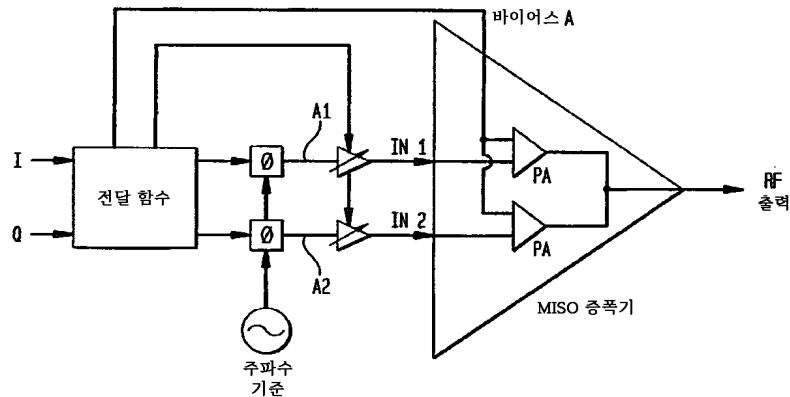

정보를 수신하고, 상기 수신된 정보로부터 복수의 제어 신호들을 발생하는 입력 회로;

상기 입력 회로에 결합되어, 상기 복수의 제어 신호들 및 주파수 기준 신호를 수신하고, 상기 주파수 기준 신호 및 상기 복수의 제어 신호들을 이용하여 복수의 포락선 신호들을 발생하는 백터 변조 회로;

상기 포락선 신호들을 수신하고, 상기 포락선 신호들을 증폭한 다음에 결합하여 출력 신호를 생성하는 전력 증폭기; 및

상기 전력 증폭기가 상기 출력 신호의 전력 레벨에 따라서 하나 또는 그 이상의 증폭기 동작 등급 사이에서 변화하도록 제어하는 수단

을 포함하는 전력 증폭 장치.

### 청구항 16

제15항에 있어서,

상기 제어하는 수단은 상기 전력 증폭기가 상기 출력 신호의 파형 궤적에 따라서 하나 또는 그 이상의 증폭기 동작 등급 사이에서 변화하도록 제어하는 수단을 포함하는 전력 증폭 장치.

### 청구항 17

제15항에 있어서,

상기 제어하는 수단은 상기 전력 증폭기의 하나 또는 그 이상의 입력 신호들의 위상을 제어하는 수단을 포함하는 전력 증폭 장치.

### 청구항 18

제15항에 있어서,

상기 제어하는 수단은 상기 전력 증폭기의 바이어스를 제어하는 수단을 포함하는 전력 증폭 장치.

### 청구항 19

제15항에 있어서,

상기 제어하는 수단은 상기 전력 증폭기의 하나 또는 그 이상의 입력 신호들의 진폭을 제어하는 수단을 포함하는 전력 증폭 장치.

### 청구항 20

제15항에 있어서,

상기 제어하는 수단은 상기 출력 신호의 복소 포락선이 증가함에 따라 상기 전력 증폭기가 원하는 증폭기 동작 등급과 연관된 현재의 증폭기 동작 등급보다 전력 효율 면에서 더 높은 동작 등급으로 전환하도록 제어하는 수단을 포함하는 전력 증폭 장치.

### 청구항 21

제15항에 있어서,

상기 제어하는 수단은 상기 출력 신호의 복소 포락선이 감소함에 따라 상기 전력 증폭기가 원하는 증폭기 동작 등급과 연관된 현재의 증폭기 동작 등급보다 전력 효율 면에서 더 낮은 동작 등급으로 전환하도록 제어하는 수단을 포함하는 전력 증폭 장치.

### 청구항 22

제15항에 있어서,

상기 제어하는 수단은 상기 출력 신호의 상기 전력 레벨에 따라서 상기 전력 증폭기의 출력 전류를 제어하는 수단을 포함하는 전력 증폭 장치.

### 청구항 23

삭제

### 청구항 24

삭제

청구항 25

삭제

청구항 26

삭제

청구항 27

삭제

청구항 28

삭제

청구항 29

삭제

청구항 30

삭제

청구항 31

삭제

청구항 32

삭제

청구항 33

삭제

청구항 34

삭제

청구항 35

삭제

청구항 36

삭제

청구항 37

삭제

청구항 38

삭제

청구항 39

삭제

청구항 40

삭제

청구항 41

삭제

청구항 42

삭제

청구항 43

삭제

청구항 44

삭제

청구항 45

삭제

청구항 46

삭제

청구항 47

삭제

청구항 48

삭제

청구항 49

삭제

청구항 50

삭제

청구항 51

삭제

청구항 52

삭제

청구항 53

삭제

청구항 54

삭제

청구항 55

삭제

청구항 56

삭제

청구항 57

삭제

청구항 58

삭제

청구항 59

삭제

청구항 60

삭제

청구항 61

삭제

청구항 62

삭제

청구항 63

삭제

청구항 64

삭제

청구항 65

삭제

청구항 66

삭제

청구항 67

삭제

청구항 68

삭제

청구항 69

삭제

청구항 70

삭제

청구항 71

삭제

청구항 72

삭제

청구항 73

삭제

청구항 74

삭제

청구항 75

삭제

청구항 76

삭제

청구항 77

삭제

청구항 78

삭제

청구항 79

삭제

청구항 80

삭제

청구항 81

삭제

청구항 82

삭제

청구항 83

삭제

청구항 84

삭제

청구항 85

삭제

청구항 86

삭제

청구항 87

삭제

청구항 88

삭제

청구항 89

삭제

청구항 90

삭제

청구항 91

삭제

청구항 92

삭제

청구항 93

삭제

청구항 94

삭제

청구항 95

삭제

청구항 96

삭제

청구항 97

삭제

청구항 98

삭제

청구항 99

삭제

청구항 100

삭제

청구항 101

삭제

청구항 102

삭제

청구항 103

삭제

청구항 104

삭제

청구항 105

삭제

청구항 106

삭제

청구항 107

삭제

청구항 108

삭제

청구항 109

삭제

청구항 110

삭제

청구항 111

삭제

청구항 112

삭제

청구항 113

삭제

청구항 114

삭제

청구항 115

삭제

청구항 116

삭제

청구항 117

삭제

청구항 118

삭제

청구항 119

삭제

청구항 120

삭제

청구항 121

삭제

청구항 122

삭제

청구항 123

삭제

청구항 124

삭제

청구항 125

삭제

청구항 126

삭제

청구항 127

삭제

청구항 128

삭제

청구항 129

삭제

청구항 130

삭제

청구항 131

삭제

청구항 132

삭제

청구항 133

삭제

청구항 134

삭제

청구항 135

삭제

청구항 136

삭제

청구항 137

삭제

청구항 138

삭제

청구항 139

삭제

청구항 140

삭제

청구항 141

삭제

청구항 142

삭제

청구항 143

삭제

청구항 144

삭제

청구항 145

삭제

청구항 146

삭제

청구항 147

삭제

청구항 148

삭제

청구항 149

삭제

청구항 150

삭제

청구항 151

삭제

청구항 152

삭제

**청구항 153**

삭제

**청구항 154**

삭제

**청구항 155**

삭제

## 명세서

### 기술분야

[0001] 본 발명은 일반적으로 RF 전력 전송, 변조 및 증폭에 관한 것이다. 특히 본 발명은 벡터 결합 전력 증폭 방법 및 시스템에 관한 것이다.

### 배경기술

[0002] 전력 증폭기에서는 통상적으로 선형성과 전력 효율 간에 복잡한 절충(tradeoff)이 존재한다.

[0003] 선형성은 전력 증폭기의 입력 변수를 그 출력 변수에 관련시키는 특성 곡선 상의 전력 증폭기 동작 범위에 의해 결정되는데, 동작 범위가 선형적일수록 전력 증폭기는 더 선형적이다라고 말한다. 선형성은 전력 증폭기의 원하는 특성이다. 일 양상에서 예컨대 전력 증폭기는 진폭, 및/또는 위상 및/또는 주파수가 변화하는 신호를 균일하게 증폭시키는 것이 바람직하다. 따라서 선형성은 전력 증폭기의 출력 신호 품질을 결정짓는 중요한 요소이다.

[0004] 전력 효율은 부하에 전달된 총 전력을 증폭기에 공급된 총전력으로 나눈 것을 이용하여 계산될 수 있다. 이상적인 증폭기의 경우에는 전력 효율은 100%이다. 통상적으로 전력 증폭기는 증폭기의 이론적인 최대 전력 효율을 결정하는 등급으로 나누어 진다. 특히 전력 증폭기가 전력을 많이 소모하는 무선 통신 시스템에서는 전력 효율은 전력 증폭기의 원하는 특성이다.

[0005] 그러나 전력 증폭기에서 선형성과 효율 간의 종래의 절충은 전력 증폭기가 선형적일수록 전력 효율은 낮아지는 것이었다. 예컨대 가장 선형적인 증폭기는 증폭기의 최저 효율 등급인 A 등급 동작으로 치우친다. 반면에 등급 B, C, D, E 등과 같이 증폭기 등급이 높을수록 전력 효율은 높아지지만 비선형적으로 되어 스펙트럼상 출력 신호가 왜곡될 수 있다.

[0006] 전술한 절충은 통상의 무선 신호에서 더 두드러진다. 예컨대 OFDM, CDMA 및 W-CDMA와 같은 무선 통신 신호는 일반적으로 피크 대 평균 전력비에 의해 특징지워진다. 신호의 피크 대 평균 전력비가 클수록 비선형 증폭기 채용시에 비선형 왜곡이 더 많이 생길 것이다.

[0007] RF 증폭기 설계를 위해 아웃페이징(outphasing) 증폭 기술이 제안되어 있다. 그러나 몇 가지 양상에서 기존의 아웃페이징 기술은 특히 예컨대 무선 통신 표준에 따라 정해지는 복잡한 신호 증폭 요건을 충족시키기에는 불충분하다.

[0008] 일 양상에서 기존의 아웃페이징 기술은 원하는 출력 신호의 일정 포락선(envelope) 성분을 결합할 때에 고립(isolating) 및/또는 결합(combining) 요소를 이용한다. 예컨대 성분 신호를 결합하는데는 흔히 전력 결합기가 이용된다. 그러나 이 결합 방식에 의하면 통상적으로 삽입 손실과 제한된 대역폭으로 인해 출력 신호의 전력이 저하되고, 따라서 전력 효율이 감소된다.

[0009] 다른 양상에서 결합 요소는 통상적으로 사이즈가 크기 때문에 모놀리식 증폭기 설계에서 채용하기 어렵다.

[0010] 따라서 전력 효율을 최대화하고 비선형 왜곡을 최소화하면서 기존의 전력 증폭 기술의 결함을 해소하는 전력 증폭 방법 및 시스템이 필요하다. 더욱이 종래의 전력 결합 회로 및 기술의 제한없이 구현될 수 있는 전력 증폭 방법 및 시스템이 필요하다.

### 발명의 상세한 설명

- [0011] 본 명세서에서는 벡터 결합 전력 증폭에 대한 실시예들이 개시된다.

- [0012] 일 실시예에서 복수의 실질적으로 일정한 포락선 신호가 개별적으로 증폭된 다음에 결합되어 원하는 시변 복소 포락선 신호를 구성한다. 이 신호들 중 하나 또는 그 이상의 위상 및/또는 주파수 특성은 원하는 시변 복소 포락선 신호의 원하는 위상, 주파수 및/또는 진폭 특성을 제공하도록 제어된다.

- [0013] 다른 실시예에서 시변 복소 포락선 신호는 복수의 실질적으로 일정한 포락선 성분 신호로 분해된다. 이 성분 신호들은 증폭된 다음 재결합되어 원래의 시변 포락선 신호의 증폭 버전을 구성한다.

- [0014] 본 발명의 실시예는 변조 반송파 신호와 기저대역 정보 및 클록 신호를 가지고 실시될 수 있다. 또한 본 발명의 실시예는 주파수 상향 변환을 달성한다. 따라서 본 발명의 실시예는 주파수 상향 변환, 증폭 및 변조를 위한 통합된 솔루션을 나타낸다.

- [0015] 본 발명의 실시예는 아날로그 및/또는 디지털 제어로 구현될 수 있다. 본 발명은 아날로그 성분 또는 아날로그 성분과 디지털 성분의 조합으로 구현될 수 있다. 후자의 실시예에서 디지털 신호 처리는 추가 비용의 절감을 위해 기존의 기저대역 프로세서에서 구현될 수 있다.

- [0016] 본 발명의 추가적인 특성과 이점에 대해서는 하기의 상세한 설명에서 설명될 것이다. 또 다른 특성과 이점은 하기의 상세한 설명에 기초하여 당업자에게 명백하거나 본 발명의 실시에 따라 알 수 있다. 본 발명의 이점은 상세한 설명과 청구범위는 물론 첨부된 도면에서 특정된 구조와 방법에 따라 실현되고 달성될 수 있다.

- [0017] 위에서 설명한 요약과 하기의 상세한 설명은 예시적이고 설명적인 것이며 본 발명의 실시예를 자세히 설명하기 위한 것임은 물론이다.

## 실시예

- [0116] 목차

- [0117] 1. 소개

- [0118] 1.1. 시변 복소 포락선 입력 신호의 예시적인 생성

- [0119] 1.2. 일정 포락선 신호로부터의 시변 복소 포락선 신호의 예시적인 생성

- [0120] 1.3. 벡터 전력 증폭 개관

- [0121] 2. 일반적인 수학적 개관

- [0122] 2.1. 페이저 신호 표기

- [0123] 2.2. 시변 복소 포락선 신호

- [0124] 2.3. 시변 포락선 신호의 일정 포락선 분해

- [0125] 3. 벡터 전력 증폭(VPA) 방법 및 시스템

- [0126] 3.1. 직교 4-분기 벡터 전력 증폭기

- [0127] 3.2. 직교-극-직교-극 (CPCP) 2-분기 벡터 전력 증폭기

- [0128] 3.3. 직접 직교 2-분기 벡터 전력 증폭기

- [0129] 3.4. I 및 Q 데이터-벡터 변조기 전달 함수

- [0130]     3.4.1. 직교 4-분기 VPA 전달 함수

- [0131]     3.4.2. CPCP 2-분기 VPA 전달 함수

- [0132]     3.4.3. 직접 직교 2-분기 VPA 전달 함수

- [0133]     3.4.4. 크기-위상 천이 변환

- [0134]         3.4.4.1. 정현파 신호에 대한 크기-위상 천이 변환

- [0135]         3.4.4.2. 구형파 신호에 대한 크기-위상 천이 변환

- [0136] 3.4.5. 과형 왜곡 보상

- [0137] 3.5. 출력단

- [0138] 3.5.1. 출력단 실시예

- [0139] 3.5.2. 출력단 전류 정형

- [0140] 3.5.3. 출력단 보호

- [0141] 3.6. 고조파 제어

- [0142] 3.7. 전력 제어

- [0143] 3.8. 예시적인 벡터 전력 증폭기 실시예

- [0144] 4. 추가 예시적인 실시예 및 구현

- [0145] 4.1. 개관

- [0146] 4.1.1. 출력 전력 및 전력 효율의 제어

- [0147] 4.1.2. 에러 보상 및/또는 보정

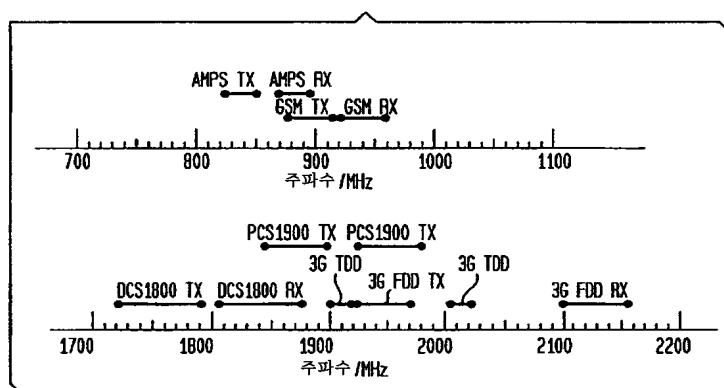

- [0148] 4.1.3. 다중대역 다중모드 동작

- [0149] 4.2. 디지털 제어 모듈

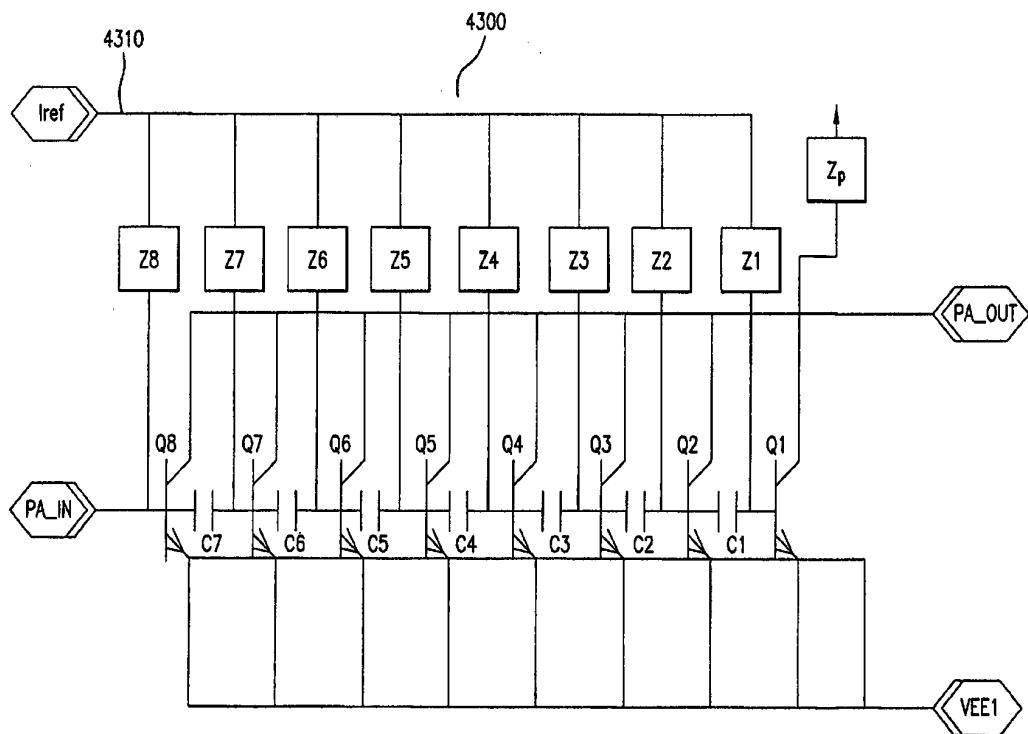

- [0150] 4.3. VPA 아날로그 코어

- [0151] 4.3.1. VPA 아날로그 코어 구현 A

- [0152] 4.3.2. VPA 아날로그 코어 구현 B

- [0153] 4.3.3. VPA 아날로그 코어 구현 C

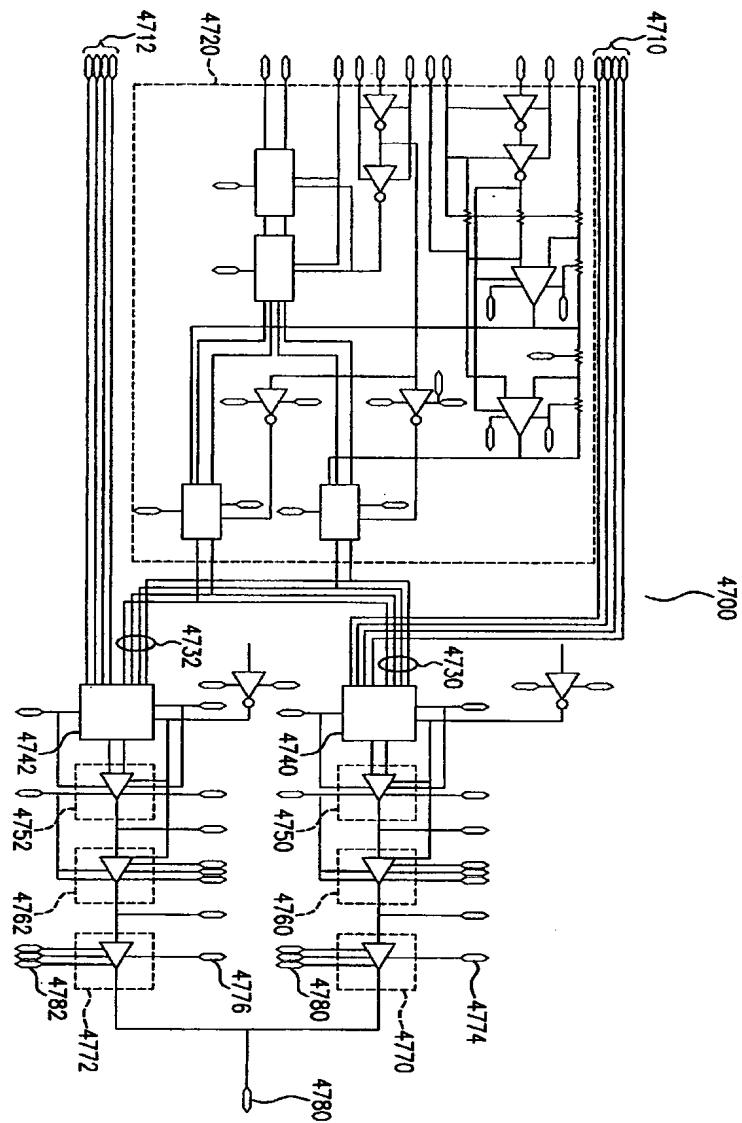

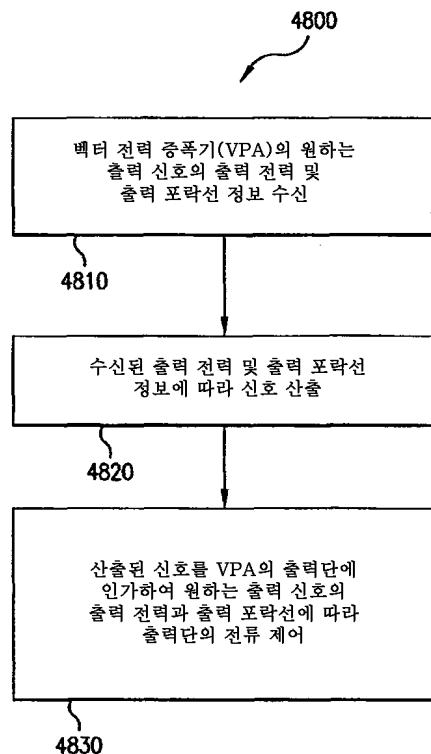

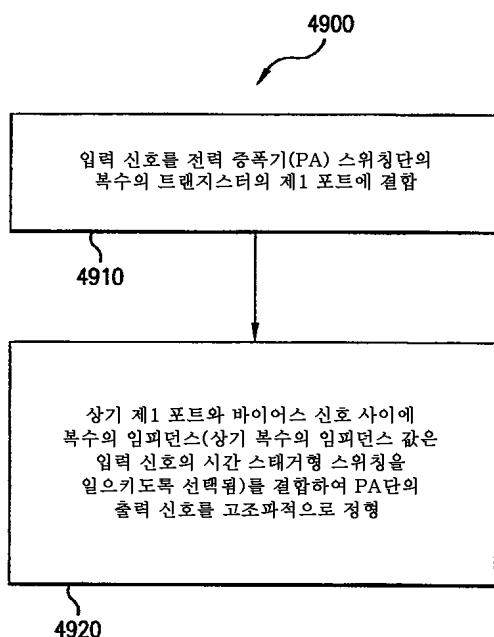

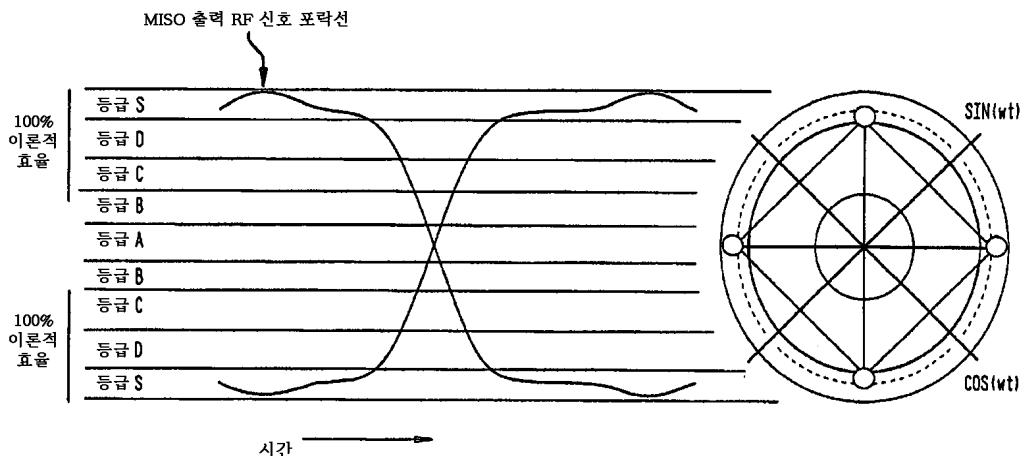

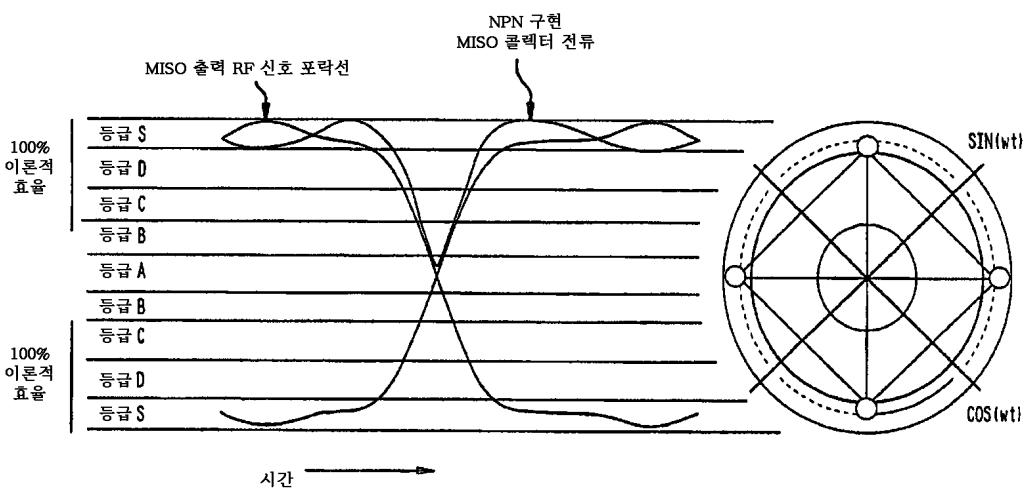

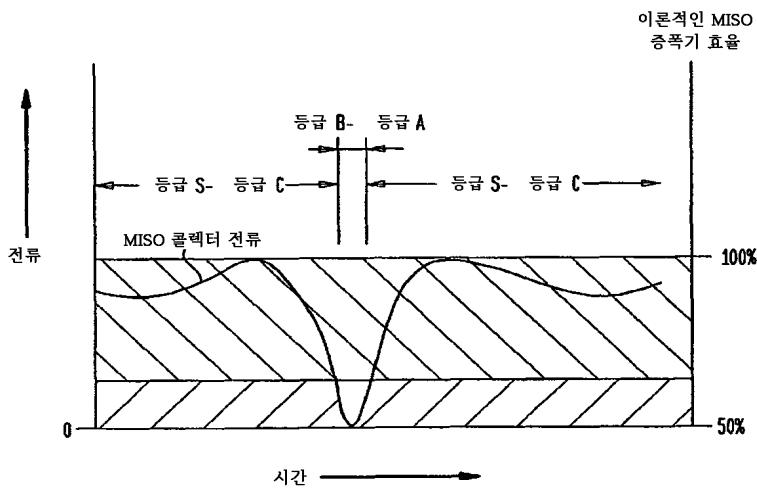

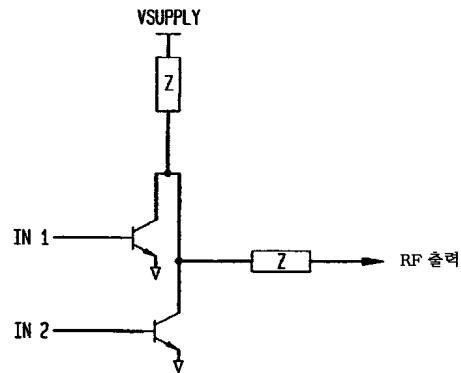

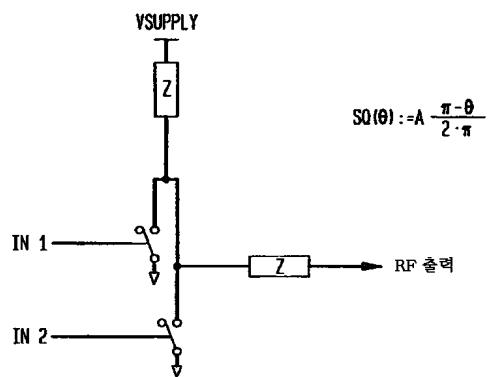

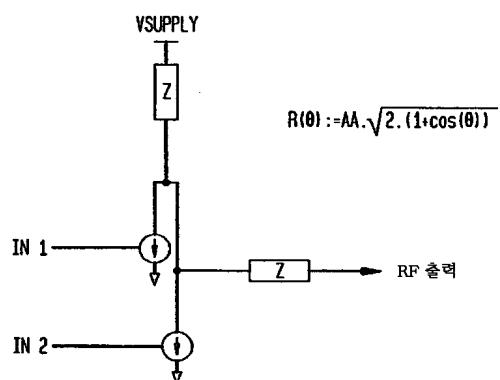

- [0154] 5. VPA 출력단의 실시간 증폭기 등급 제어

- [0155] 6. 요약

- [0156] 7. 결론

## 0157] 소개

본 명세서에서는 벡터 결합 전력 증폭 방법, 장치 및 시스템이 개시된다.

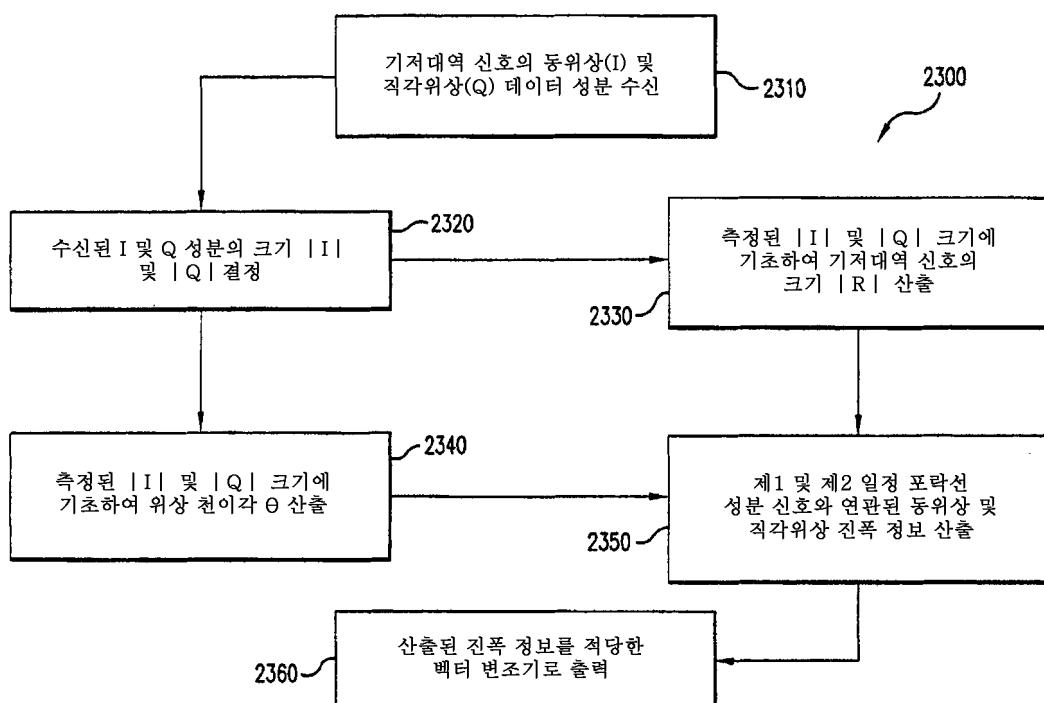

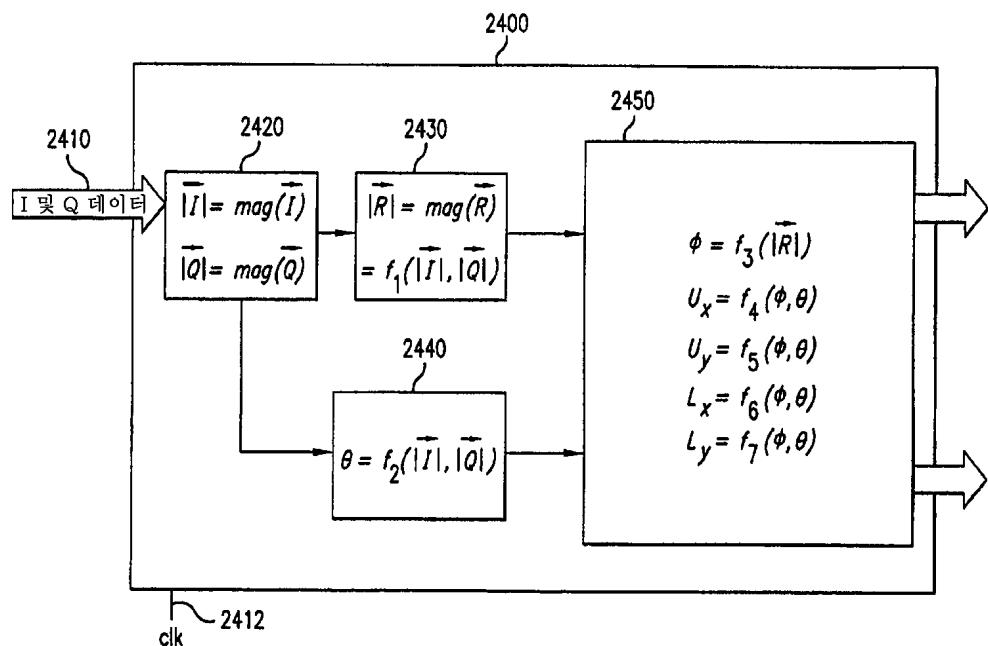

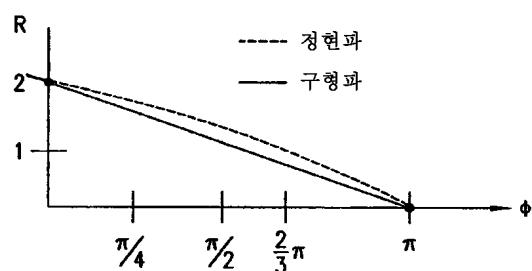

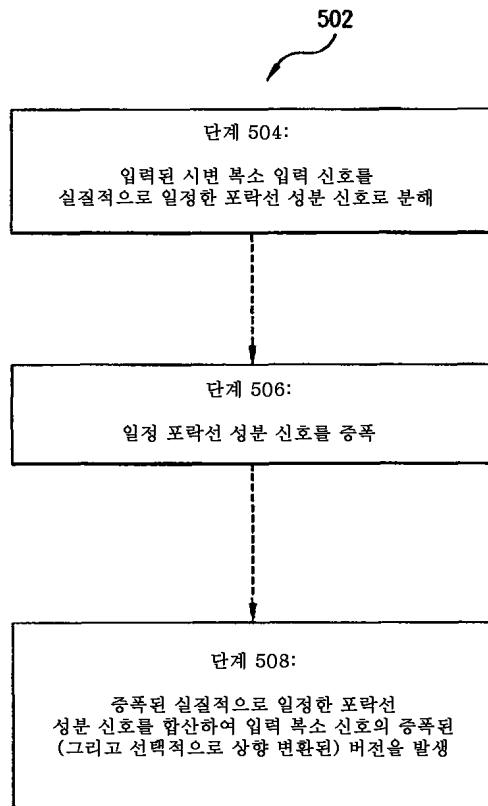

벡터 결합 전력 증폭은 선형성과 전력 효율을 동시에 최적화하는 방식이다. 일반적으로 말하여, 도 50의 플로우차트(502)를 참조로 설명하면, 단계(504)에서 진폭과 위상이 변하는 시변 복소 포락선 입력 신호는 일정 포락선 성분 신호들로 분해된다. 단계(506)에서 일정 포락선 성분 신호들은 증폭되고, 단계(508)에서 합산되어 입력 복소 포락선 신호의 증폭 신호를 생성한다. 실질적으로 일정한 포락선 신호는 비선형 왜곡이 거의 없이 증폭될 수 있기 때문에 일정 포락선 신호들을 합산한 결과도 비선형 왜곡이 거의 없이 최적 효율을 제공한다.

따라서 벡터 결합 전력 증폭에 의해서 비선형 전력 증폭기라도 비선형 왜곡 레벨을 최소화하면서 복소 신호를 효율적으로 증폭하는데 사용될 수 있다.

편의상 제한없이 본 명세서에서는 본 발명의 방법 및 시스템은 때로는 벡터 전력 증폭(VPA) 방법 및 시스템이라고 한다.

이제 본 발명의 실시예들에 따른 VPA 방법 및 시스템에 대해서 자세히 설명하기로 한다. 명확하게 하기 위하여 먼저 특정 용어들에 대해서 정의한다. 이 절에서 기술된 정의는 단순히 편의상 제공하는 것이며 제한적인 것이 아니다. 이를 용어들의 의미는 본 발명의 교시에 따라 당업자에게 명백하게 될 것이다. 이를 용어는 명세서 전체에서 추가적인 세부사항을 가지고 설명될 수 있다.

여기서 사용되는 용어 "신호 포락선"은 신호가 시간 영역에서 변동할 때에 포함되는 진폭 경계를 말한다. 직교변조 신호는  $r(t)=i(t) \cdot \cos(\omega_c \cdot t) + q(t) \cdot \sin(\omega_c \cdot t)$ 로 표현될 수 있다. 이 식에서  $i(t)$ 와  $q(t)$ 는 신호 포

락선( $e(t) = \sqrt{i(t)^2 + q(t)^2}$ )을 가진 동위상 및 직각 위상 신호를 나타내며,  $r(t)$ 와 연관된 위상 신호는  $\arctan(q(t)/i(t))$ 와 관계된다.

[0164] 여기서 사용되는 용어 "일정 포락선 신호"는  $e(t) = \sqrt{i(t)^2 + q(t)^2}$  가 비교적 또는 거의 일정한 값을 가진 동위상 및 직각 위상 신호를 말한다.

[0165] 여기서 사용되는 용어 "시변 포락선 신호"는 시변 신호 포락선을 가진 신호를 말한다. 시변 포락선 신호는 동

위상 및 직각 위상 신호의 관점에서 시변값을 가진  $e(t) = \sqrt{i(t)^2 + q(t)^2}$  로서 표현될 수 있다.

[0166] 여기서 사용된 용어 "위상 천이(phase shifting)"는 시변 또는 일정 포락선 신호의 위상 성분이 기준 위상에 대해 지상(delaying) 또는 진상(advancing)하는 것을 말한다.

[0167] 1.1) 시변 복소 포락선 입력 신호의 예시적인 생성

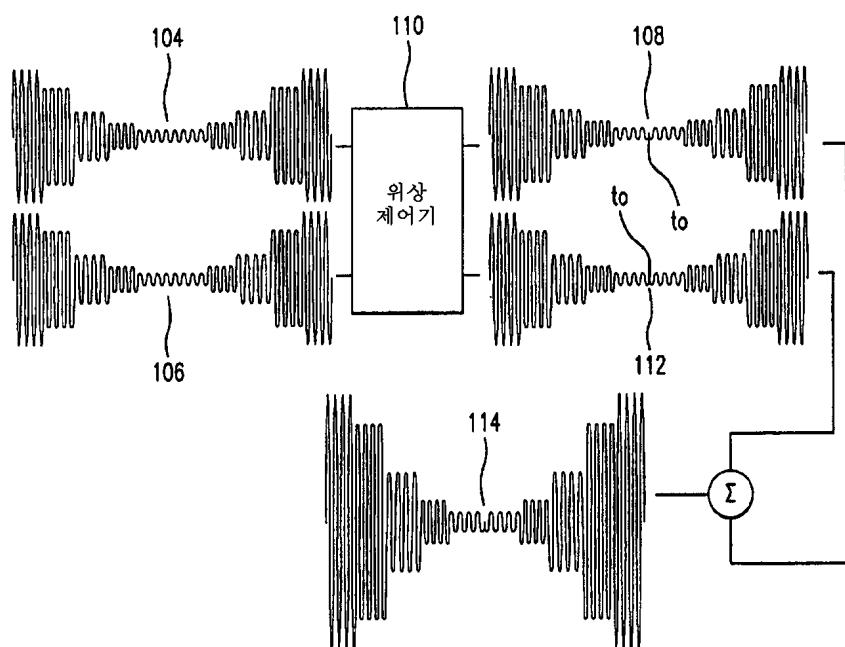

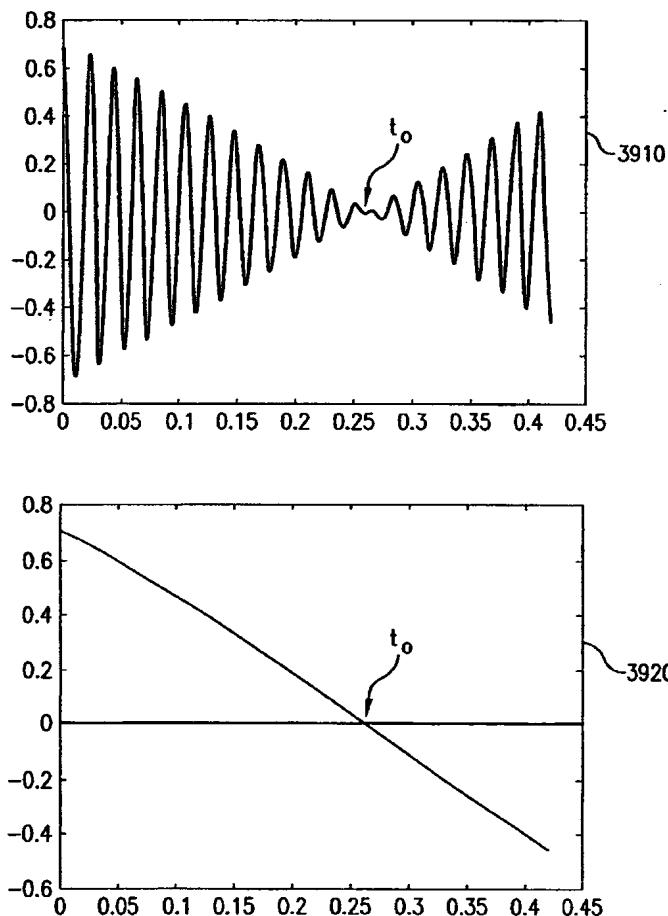

[0168] 도 1A 및 도 1B는 시변 포락선 및 위상 복소 입력 신호의 생성을 나타낸 예시도이다. 도 1A에서, 시변 포락선 반송파 신호(104, 106)는 위상 제어기(110)에 입력된다. 위상 제어기(110)는 신호(104, 106)의 위상 성분을 조작한다. 즉, 위상 제어기(110)는 신호(104, 106)의 위상을 천이시킬 수 있다. 따라서 도출된 신호(108, 112)는 신호(104, 106)에 대해 위상이 천이될 수 있다. 도 1A의 예에서 위상 제어기(110)는 신호(108, 112)로부터 알 수 있듯이 시상수( $t_0$ )에서 신호(104, 106)의 위상을 반전(180도 위상 천이)시킨다. 신호(108, 112)는 시변 복소 반송파 신호를 나타낸다. 신호(108, 112)는 시변 포락선 및 위상 성분 둘 다를 갖고 있다. 신호(108, 112)는 합쳐져서 신호(114)가 된다. 신호(114)도 시변 복소 신호를 나타낸다. 신호(114)는 본 발명의 VPA 실시예에서의 예시적인 입력 신호(예컨대 도 50의 단계(504)에서의 예시적인 입력)일 수 있다.

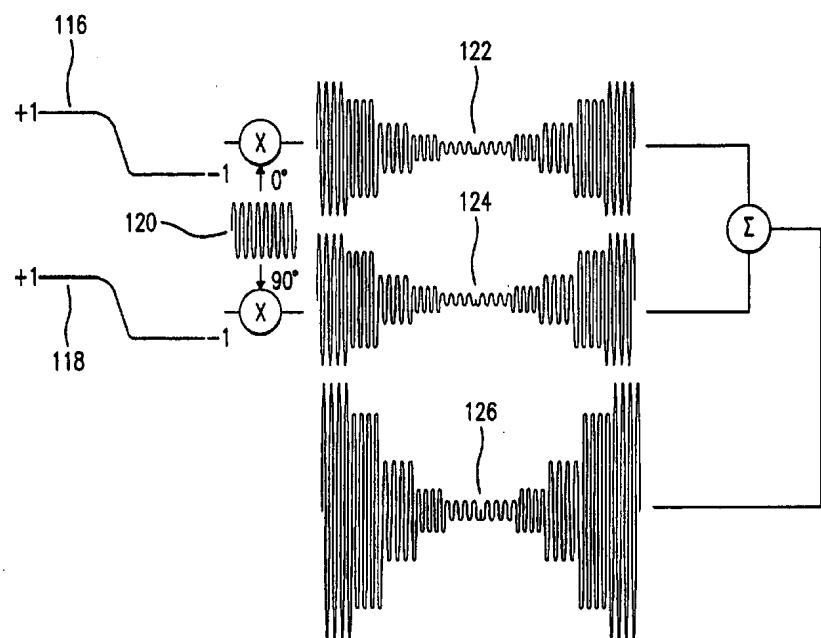

[0169] 시변 복소 신호는 또한 도 1B에 도시된 바와 같이 생성될 수 있다. 도 1B에서 신호(116, 118)는 기저대역 신호를 나타낸다. 예컨대 신호(116, 118)는 신호의 동위상(I) 및 직각위상(Q) 기저대역 성분일 수 있다. 도 1B의 예에서 신호(116, 118)는 +1에서 -1로 전이함에 따라 영교차(zero crossing)한다. 신호(116, 118)에는 신호(120) 또는 90도 위상 천이된 신호(120)가 곱해진다. 신호(116)에는 0도 천이된 버전의 신호(120)가 곱해진다. 신호(118)에는 90도 천이된 버전의 신호(120)가 곱해진다. 이렇게 해서 도출된 신호(122, 124)는 시변 복소 반송파 신호를 나타낸다. 여기서 신호(122, 124)는 신호(116, 118)의 시변 진폭에 따라 변하는 포락선을 갖고 있음을 유의한다. 더욱이 신호(122, 124)는 모두 신호(116, 118)의 영교차에서 위상 반전을 겪는다. 신호(122, 124)는 합산되어 신호(126)가 된다. 신호(126)는 시변 복소 신호를 나타낸다. 신호(126)는 본 발명의 VPA 실시예에서 예시적인 입력 신호를 나타낼 수 있다. 게다가 신호(116, 118)는 본 발명의 VPA 실시예에서 예시적인 입력 신호들을 나타낼 수 있다.

[0170] 1.2) 일정 포락선 신호로부터의 시변 복소 포락선 신호의 예시적인 생성

[0171] 이 절에서의 설명은 일반적으로 도 50에서 단계(508)의 동작에 관한 것이다. 도 1C는 2 또는 그 이상의 실질적으로 일정한 포락선 신호의 합으로부터의 시변 복소 신호의 생성의 3가지 예를 나타낸다. 그러나 당업자라면 본 발명의 교시에 따라서 도 1C의 예에 나타난 개념은 마찬가지로 2보다 많은 일정 포락선 신호의 경우에 확장될 수 있음을 잘 알 것이다.

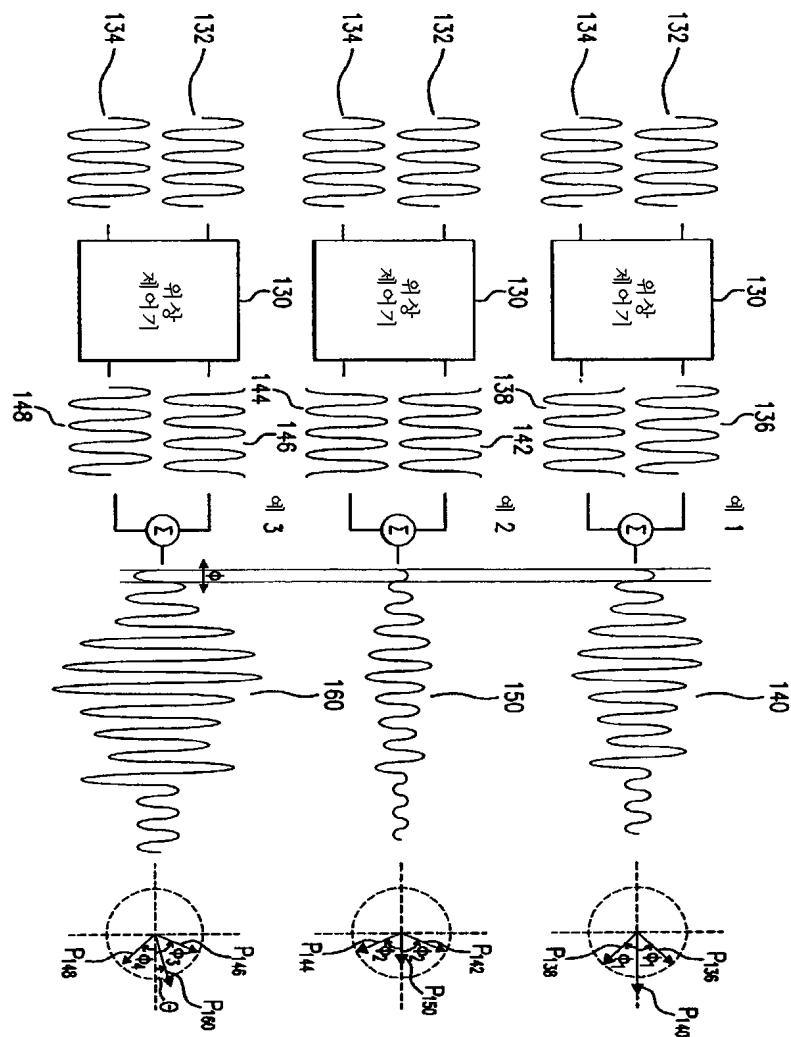

[0172] 도 1C의 예 1에서 일정 포락선 신호(132, 134)는 위상 제어기(130)에 입력된다. 위상 제어기(130)는 신호(132, 134)의 위상 성분을 조작하여 각각 신호(136, 138)를 생성한다. 신호(136, 138)는 실질적으로 일정한 포락선 신호를 나타내며, 합산되어 신호(140)를 생성한다. 도 1C의 예 1과 관련된 페이저 표기는 신호(136, 138)를 각각 페이저( $P_{136}, P_{138}$ )로서 나타낸다. 신호(140)는 페이저( $P_{140}$ )로서 나타낸다. 예 1에서  $P_{136}$ 과  $P_{138}$ 은 페이저 표기의 실축에 맞추어지도록 가정된 기준 신호에 대해 각도( $\phi_1$ )만큼 대칭적으로 위상 천이되어 있다. 이에 대응하여 시간 영역 신호(136, 138)는 기준 신호에 대해 양은 동일하나 방향은 반대로 위상이 천이되어 있다. 따라서  $P_{136}$ 과  $P_{138}$ 의 합인  $P_{140}$ 은 기준 신호와 위상이 같다.

[0173] 도 1C의 예 2에서 실질적으로 일정한 포락선 신호(132, 134)는 위상 제어기(130)에 입력된다. 위상 제어기

(130)는 신호(132, 134)의 위상 성분을 조작하여 각각 신호(142, 144)를 생성한다. 신호(142, 144)는 실질적으로 일정한 포락선 신호를 나타내며, 합산되어 신호(150)를 생성한다. 예 2와 관련된 페이저 표기는 신호(142, 144)를 각각 페이저( $P_{142}$ ,  $P_{144}$ )로서 나타낸다. 신호(150)는 페이저( $P_{150}$ )로서 나타낸다. 예 2에서  $P_{142}$ 과  $P_{144}$ 는 기준 신호에 대해 대칭적으로 위상 천이되어 있다. 따라서  $P_{140}$ 과 마찬가지로  $P_{150}$ 도 기준 신호와 위상이 같다. 그러나  $P_{142}$ 과  $P_{144}$ 는 기준 신호에 대해 소정 각도( $\phi_2 \neq \phi_1$ )만큼 위상 천이된다. 그 결과,  $P_{150}$ 은 예 1의  $P_{140}$ 과는 크기가 다르다. 시간 영역 표기에서는 신호(140, 150)는 동위상이지만 진폭은 서로 다르다.

[0174] 도 1C의 예 3에서 실질적으로 일정한 포락선 신호(132, 134)는 위상 제어기(130)에 입력된다. 위상 제어기(130)는 신호(132, 134)의 위상 성분을 조작하여 각각 신호(146, 148)를 생성한다. 신호(146, 148)는 실질적으로 일정한 포락선 신호를 나타내며, 합산되어 신호(160)를 생성한다. 예 3과 관련된 페이저 표기는 신호(146, 148)를 각각 페이저( $P_{146}$ ,  $P_{148}$ )로서 나타낸다. 신호(160)는 페이저( $P_{160}$ )로서 나타낸다. 예 3에서  $P_{146}$ 은 기준 신호에 대해 각도( $\phi_3$ )만큼 위상 천이되어 있다.  $P_{148}$ 은 기준 신호에 대해 각도( $\phi_4$ )만큼 위상 천이되어 있다.  $\phi_3$ 과  $\phi_4$ 는 같을 수도 같지 않을 수도 있다. 따라서  $P_{146}$ 과  $P_{148}$ 의 합인  $P_{160}$ 은 기준 신호와 더 이상 동위상이 아니다.  $P_{160}$ 은 기준 신호에 대해 각도( $\theta$ )만큼 위상 천이된다. 마찬가지로  $P_{160}$ 은 예 1과 2의  $P_{140}$ 과  $P_{150}$ 에 대해  $\theta$ 만큼 위상 천이된다.  $P_{160}$ 은 예 3에 도시된 바와 같이  $P_{140}$ 에 대해 진폭이 변화될 수도 있다.

[0175] 요약하면, 도 1C의 예들은 2 또는 그 이상의 실질적으로 일정한 포락선 신호의 합에 의해 시변 진폭 신호가 얻어질 수 있다는 것(예 1)을 보여준다. 더욱이 2 또는 그 이상의 실질적으로 일정한 포락선 신호를 반대 방향에서 동일하게 천이시킴으로써 위상 변화없이 진폭만 변화시킬 수 있다(예 2). 2 또는 그 이상의 일정한 포락선 성분 신호를 동일 방향에서 동일하게 천이시킴으로써 시변 신호는 진폭 변화없이 위상만 변화시킬 수 있다. 2 또는 그 이상의 실질적으로 일정한 포락선 신호를 이용하여 임의의 시변 진폭 및 위상 신호를 생성할 수 있다(예 3).

[0176] 도 1C의 예에서의 신호들은 단지 설명을 위해 정현파형으로 도시한 점에 유의한다. 당업자라면 본 발명의 교시에 따라 임의 형태의 과형이 이용될 수 있음을 잘 알 것이다. 또한 도 1C의 예는 단지 설명을 위해 제공된 것이며 본 발명의 특정 실시예에 해당될 수도 있고 해당되지 않을 수도 있음에 유의한다.

### 1.3) 벡터 전력 증폭 개관

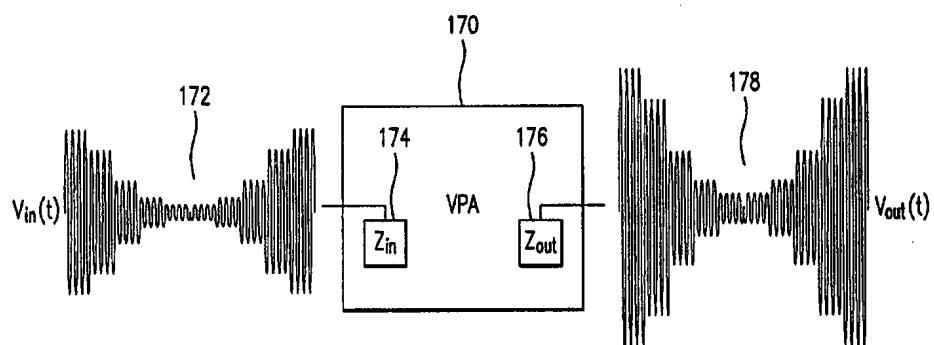

[0178] 이제 벡터 전력 증폭에 대해 자세히 개관한다. 도 1D는 예시적인 시변 복소 입력 신호(172)의 전력 증폭을 나타낸다. 도 1A와 1B에 도시된 신호(114, 126)는 신호(172)의 예일 수 있다. 더욱이 신호(172)는 104와 106(도 1A), 108과 112(도 1A), 116과 118(도 1B), 및 122와 124(도 1B)와 같은 2 또는 그 이상의 성분 신호에 의해 생성되거나 이 신호들로 구성될 수 있다.

[0179] 도 1D의 예에서 VPA(170)는 본 발명에 따른 VPA 시스템 실시예를 나타낸다. VPA(170)는 신호(172)를 증폭하여 증폭 출력 신호(178)를 생성한다. 출력 신호(178)는 왜곡을 최소화하면서 효율적으로 증폭된다.

[0180] 도 1D의 예에서 신호(172, 178)는 각각 전압 신호( $V_{in}(t)$ ,  $V_{out}(t)$ )를 나타낸다. 임의 시각에서 도 1D의 예에서  $V_{in}(t)$ 와  $V_{out}(t)$ 는  $V_{out}(t)=KeV_{in}(tat')$ 의 관계를 갖는다. 여기서, K는 스케일 팩터이고  $t'$ 는 VPA 시스템에서

$$\frac{V_{out}^2(t)}{Z_{out}} > \frac{V_{in}^2(t)}{Z_{in}}$$

있을 수 있는 시간 지연을 나타낸다. 전력 표시로는  $V_{out}(t)=KeV_{in}(tat')$ 이며, 여기서 출력 신호(178)는 입력 신호(172)의 전력이 증폭된 것이다.

[0181] 도 1D에 도시된 바와 같이 시변 복소 신호의 선형적(또는 실질적으로 선형적) 전력 증폭은 도 1E에 도시된 본 발명의 실시예에 따라 이루어진다.

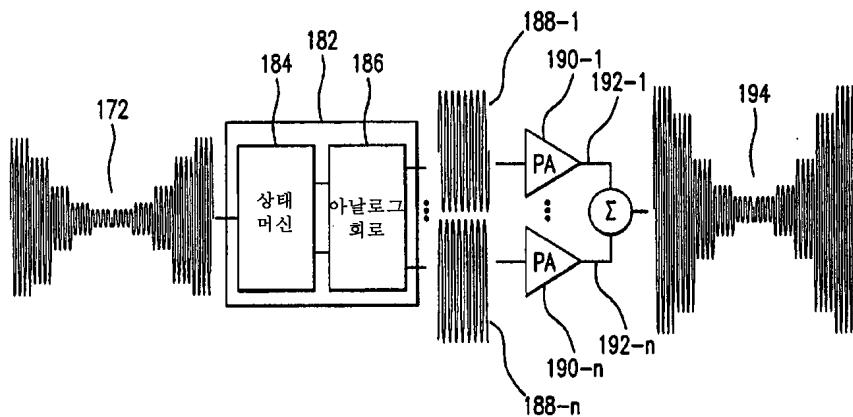

[0182] 도 1E는 본 발명의 실시예에 따른 벡터 전력 증폭 실시예를 개념적으로 나타낸 예시적인 블록도이다. 도 1E에서 입력 신호(172)는 시변 복소 신호를 나타낸다. 예컨대 입력 신호(172)는 도 1A 및 1B에 도시된 바와 같이 생성될 수 있다. 실시예에서 신호(172)는 디지털 또는 아날로그 신호일 수 있다. 더욱이, 신호(172)는 기저대역 또는 반송파 방식 신호일 수 있다.

[0183] 도 1E를 참조로 설명하면, 본 발명의 실시예에 따라 입력 신호(172) 또는 그 등가 신호는 VPA(182)에 입력된다.

도 1E의 실시예에서 VPA(182)는 상태 머신(184)과 아날로그 회로(186)를 포함한다. 상태 머신(184)은 디지털 및/또는 아날로그 성분을 포함할 수 있다. 아날로그 회로(186)는 아날로그 성분을 포함한다. VPA(182)는 입력 신호(172)를 처리하여 도 1E에 도시된 바와 같이 2 또는 그 이상의 신호(188-{1,...,n})를 생성한다. 도 1C에서 신호(136, 138, 142, 144, 146, 148)에 대해서 설명한 바와 같이, 신호(188-{1,...,n})는 서로 다른 주기에 걸쳐 서로에 대해 위상 천이될 수도 있고 천이되지 않을 수도 있다. 더욱이 VPA(182)는 신호(188-{1,...,n})의 합이 신호(194)가 되도록 신호(188-{1,...,n})를 생성하며, 이 신호(194)는 특정 실시예에서 신호(172)가 증폭된 것일 수 있다.

[0184] 계속해서 도 1E를 참조로 설명하면, 신호(188-{1,...,n})는 실질적으로 일정한 포락선 신호이다. 따라서 이전 단락에서의 설명은 도 50의 단계(504)에 해당한다.

[0185] 도 50의 단계(506)에 일반적으로 해당하는 도 1E의 예에서 일정 포락선 신호(188-{1,...,n})는 해당 전력 증폭기(PA)(190-{1,...,n})에 의해 각각 독립적으로 증폭되어 증폭 신호(192-{1,...,n})를 생성한다. 실시예에서 PA(190-{1,...,n})는 실질적으로 똑 같은 각자의 일정 포락선 신호(188-{1,...,n})를 증폭한다. 증폭 신호(192-{1,...,n})는 실질적으로 일정한 포락선 신호이며, 단계(508)에서 합산되어 출력 신호(194)를 생성한다. 출력 신호(194)는 입력 신호(172)가 선형적으로(또는 실질적으로 선형적으로) 증폭된 것일 수 있음에 유의한다. 출력 신호(194)는 여기서 설명하는 바와 같이 입력 신호(172)를 주파수 상향 변환한 것일 수도 있다.

[0186] 일반적인 수학적 개관

[0187] 2.1) 페이저 신호 표기

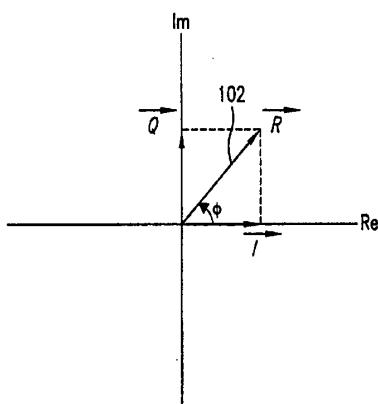

[0188] 도 1은 신호( $r(t)$ )의 페이저 표기( $\vec{R}$ )(102)를 나타낸다. 신호의 페이저 표기는 기준 신호에 대한 신호의 포락선의 크기와 신호의 위상 천이를 명확하게 나타낸다. 본 명세서에서는 편의상 제한없이 기준 신호는 페이저 표기의 직교 공간의 실축(Re)에 맞추어져 있는 것으로 정의된다. 그러나 본 발명은 이 실시예에 한정되는 것은 아니다. 신호의 주파수 정보는 이 표기에서 함축적으로 나타나 있으며 기준 신호의 주파수에 의해 주어진다.

예컨대 도 1을 참조로 실축이  $\cos(\omega t)$  기준 신호에 대응한다고 가정하면 페이저( $\vec{R}$ )는 함수( $r(t)=R(t)\cos(\omega t+\phi(t))$ )로 변환된다. 여기서  $R$ 은  $\vec{R}$ 의 크기이다.

[0189] 계속해서 도 1을 참조로 설명하면, 페이저( $\vec{R}$ )는 실수부 페이저( $\vec{I}$ )와 허수부 페이저( $\vec{Q}$ )로 분해될 수 있음에 주목한다.  $\vec{I}$  와  $\vec{Q}$ 는 기준 신호에 대해 각각  $\vec{R}$ 의 동위상과 직각 위상 페이저 성분이라고 한다.

더욱이  $\vec{I}$  와  $\vec{Q}$ 에 대응하는 신호는  $r(t)$ 와 각각  $I(t)=R(t) \cdot \cos(\phi(t))$  및  $Q(t)=R(t) \cdot \sin(\phi(t))$ 로서 관련된다. 시간 영역에서 신호( $r(t)$ )는 다음과 같이 동위상 성분과 직각 위상 성분으로 기술될 수도 있다.

$$\begin{aligned} r(t) &= I(t) \cdot \cos(\omega t) + Q(t) \cdot \sin(\omega t) = \\ &= R(t) \cdot \cos(\phi(t)) \cdot \cos(\omega t) + R(t) \cdot \sin(\phi(t)) \cdot \sin(\omega t) \end{aligned} \quad (1)$$

[0190] 도 1의 예에서  $R(t)$ 는 특정 순간에서 나타낸 것임에 유의한다.

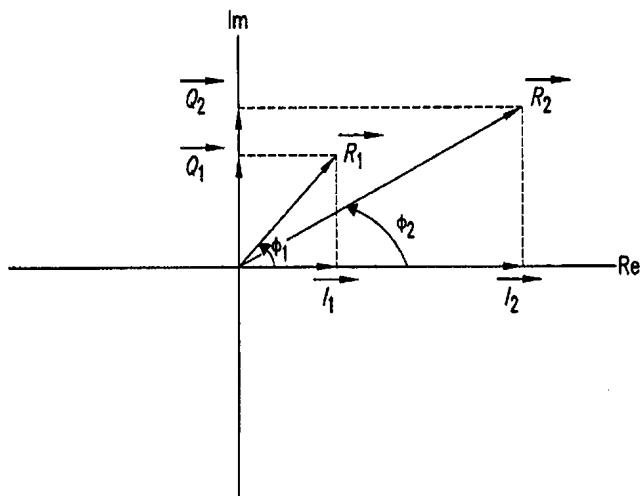

[0192] 2.2) 시변 복소 포락선 신호

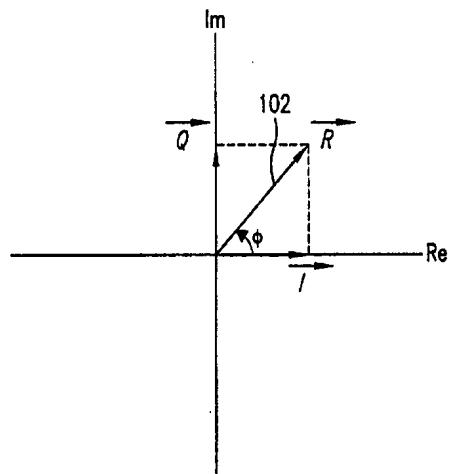

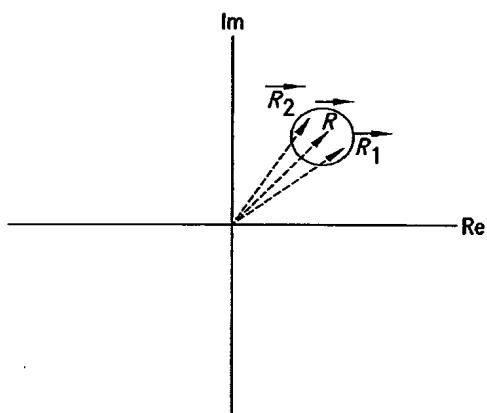

[0193] 도 2는 두 개의 서로 다른 순간( $t_1, t_2$ )에서의 신호( $r(t)$ )의 페이저 표기를 나타낸다. 신호의 포락선의 크기와 그 상대적인 위상 천이를 나타내는 이 페이저의 크기는 모두 각각  $t_1$ 에서 시작  $t_2$ 로 변한다는 것에 유의한다.

도 2에서는 이것은 페이저  $\vec{R}_1$  와  $\vec{R}_2$ 의 변화하는 크기와 이에 대응하는 위상 천이각  $\phi_1$ 과  $\phi_2$ 에 의해 도시

된다. 따라서 신호( $r(t)$ )는 시변 복소 포락선 신호이다.

[0194] 더욱이, 도 2로부터 신호( $r(t)$ )의 실수 및 헤수 페이저 성분은 진폭이 시간에 따라 변한다는 것을 유의한다. 따라서 그 대응하는 시간 영역 신호도 시변 포락선을 갖는다.

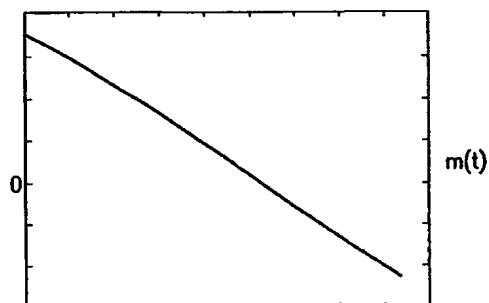

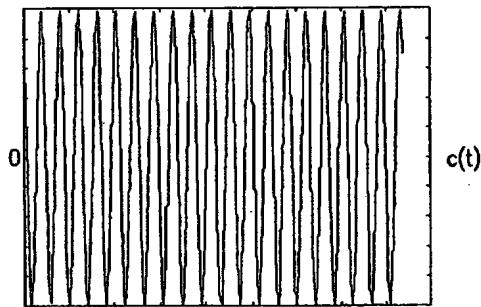

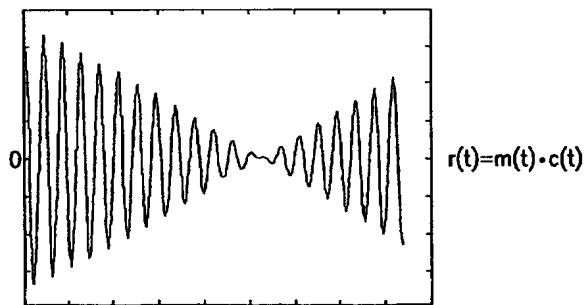

[0195] 도 3A 내지 3C는 시변 복소 포락선 신호를 발생하는 예시적인 변조를 나타낸다. 도 3A는 신호( $m(t)$ )를 나타낸 것이다. 도 3B는 반송파 신호( $c(t)$ )의 일부를 나타낸 것이다. 도 3C는 신호들( $m(t)$ ,  $c(t)$ )을 곱하여 생성한 신호( $r(t)$ )를 나타낸 것이다.

[0196] 도 3A의 예에서 신호( $m(t)$ )는 시변 크기 신호이다. 더욱이  $m(t)$ 는 영교차된다. 도 3B의 예에서 반송파 신호( $c(t)$ )는 통상적으로는 신호( $m(t)$ ) 주파수보다 높은 특정 반송파 주파수로 진동한다.

[0197] 도 3C로부터, 도출된 신호( $r(t)$ )는 시변 포락선을 갖고 있음을 알 수 있다. 더욱이 도 3C로부터  $r(t)$ 는 변조 신호( $m(t)$ )가 영교차하는 순간에 위상이 반전됨을 알 수 있다. 포락선과 위상이 일정하지 않으면  $r(t)$ 는 시변 복소 포락선 신호라고 한다.

[0198] 2.3) 시변 포락선 신호의 일정 포락선 분해

[0199] 시변 크기 및 위상의 페이저는 기준 페이저에 대해 적당히 특정된 위상 천이를 갖는 2 또는 그 이상의 일정 크기 페이저의 합에 의해 얻을 수 있다.

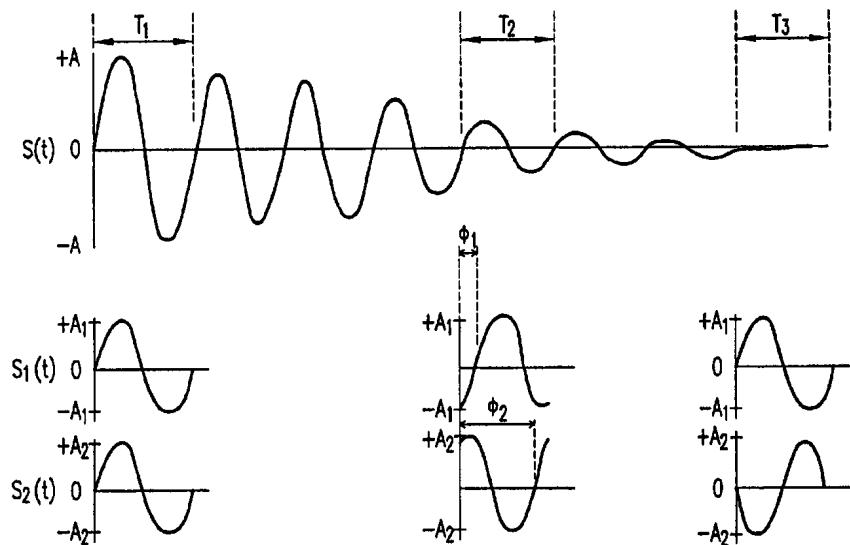

[0200] 도 3D는 예시적인 시변 포락선 및 위상 신호( $S(t)$ )를 나타낸 것이다. 설명을 쉽게 하기 위하여 신호( $S(t)$ )는 최대 포락선 크기( $A$ )를 가진 정현파 신호라고 가정한다. 도 3D는 두 개의 일정 포락선 신호( $S_1(t)$ ,  $S_2(t)$ )의 합에 의해 임의의 순간에 신호( $S(t)$ )가 어떻게 얻어질 수 있는가의 예를 더 보여준다. 일반적으로  $S_1(t)=A_1\sin((\omega t+\phi_1(t)))$ 이고  $S_2(t)=A_2\sin((\omega t+\phi_2(t)))$ 이다.

[0201] 설명 목적상 도 3D에는 신호  $S(t)$ 에 대해  $S_1(t)$ 와  $S_2(t)$ 를 적당히 조정하여  $S(t)=K(S_1(t)+S_2(t))$ (여기서,  $K$ 는 상수)가 되도록 신호  $S_1(t)$  및  $S_2(t)$ 가 어떻게 합산될 수 있는지를 보여주는 3개의 그림이 제공된다. 즉, 신호  $S(t)$ 는 임의 순간에 2 또는 그 이상의 신호로 분해될 수 있다. 도 3D로부터 주기  $T_1$ 에서는  $S_1(t)$ 와  $S_2(t)$ 는 신호  $S(t)$ 에 대해 동위상이며, 따라서 합산되어 신호  $S(t)$ 의 최대 포락선 크기  $A$ 가 된다. 그러나 주기  $T_3$ 에서는 신호  $S_1(t)$ 와  $S_2(t)$ 는 서로에 대해 위상이 180도 어긋나며, 따라서 합산되어 신호  $S(t)$ 의 최소 포락선 크기가 된다.

[0202] 도 3D의 예는 정현파 신호의 경우를 설명한 것이다. 그러나 당업자라면 푸리에 급수 또는 푸리에 변환으로 나타낼 수 있는 반송파 신호를 변조하는 임의의 시변 포락선도 마찬가지로 2 또는 그 이상의 실질적으로 일정한 포락선 신호로 분해될 수 있음을 잘 알 것이다. 따라서 복수의 실질적으로 일정한 포락선 신호의 위상을 조정함으로써 임의의 시변 복소 포락선 신호가 생성될 수 있다.

[0203] 벡터 전력 증폭 방법 및 시스템

[0204] 본 발명의 실시예에 따른 벡터 전력 증폭 방법 및 시스템은 임의의 시변 포락선 신호를 2 또는 그 이상의 실질적으로 일정한 포락선 성분 신호로 분해하거나, 그와 같은 성분 신호를 수신 또는 생성하고, 그 성분 신호를 증폭한 다음에 증폭된 신호를 합산하여 시변 복소 포락선 신호를 증폭시키는 능력에 의존한다.

[0205] 3.1 내지 3.3 절에서는 4-분기 및 2-분기 실시예를 포함하여 본 발명의 벡터 전력 증폭(VPA) 실시예가 제공된다. 하기 설명에서는 먼저 실시예의 기본 개념의 수학적 유도를 이용하여 각 VPA 실시예를 개념적으로 제시한다. 그 후 VPA 실시예의 동작 방법의 실시예가 제시되고 나서 VPA 실시예의 각종 시스템 레벨 실시예가 제시된다.

[0206] 3.4 절에서는 본 발명의 실시예에 따른 제어 모듈의 여러 가지 실시예를 제시한다. 본 발명의 실시예에 따른 제어 모듈은 본 발명의 특정 VPA 실시예를 구현하는데 이용될 수 있다. 일부 실시예에서 제어 모듈은 VPA 실시예의 입력단과 VPA 실시예의 후속 벡터 변조단 사이의 중간 매개이다.

[0207] 3.5 절은 본 발명의 실시예에 따른 VPA 출력단 실시예에 대해서 설명한다. 출력단 실시예는 VPA 실시예의 출력 신호를 생성하는 것에 관한 것이다.

[0208] 3.6 절은 본 발명의 실시예에 따른 고조파 제어에 관한 것이다. 고조파 제어는 본 발명의 특정 실시예에서 VPA 실시예의 고조파의 실수부 전력과 허수부 전력을 조작하여 출력에서의 기본 주파수에 나타나는 전력을 증가시키도록 구현될 수 있다.

[0209] 3.7 절은 본 발명의 실시예에 따른 전력 제어에 관한 것이다. 전력 제어는 본 발명의 VPA 실시예가 채용될 수 있는 응용의 전력 레벨 요건을 만족시키기 위해 본 발명의 특정 실시예에서 구현될 수 있다.

[0210] 3.1. 직교 4-분기 벡터 전력 증폭기

[0211] 여기서는 제한없이 설명을 쉽게하기 위해 직교 4-분기 VPA 실시예라 불리는 본 발명의 일 실시예에 따라서 시변 복소 포락선 신호는 4개의 실질적으로 일정한 포락선 성분 신호로 분해된다. 성분 신호는 개별적으로 똑같이 또는 거의 똑같이 증폭된 다음에 합산되어 원래의 시변 복소 포락선 신호의 증폭 신호를 구성한다.

[0212] 이 실시예에서는 설명 목적상 제한없이 4 분기가 채용됨에 유의한다. 본 발명의 범위는 다른 분기 수의 이용을 포함하며, 그와 같은 변경의 구현은 본 발명의 교시에 따라 당업자에게 명백할 것이다.

[0213] 일 실시예에서 먼저 시변 복소 포락선 신호는 그 동위상 및 직각위상 벡터 성분으로 분해된다. 페이저 표기에 동위상 및 직각위상 벡터 성분은 각각 신호의 실수부와 허수부 페이저에 해당한다.

[0214] 전술한 바와 같이, 신호의 동위상 및 직각위상 벡터 성분의 크기는 그 신호의 크기에 비례하여 변하며, 따라서 그 신호가 시변 포락선 신호라면 일정 포락선이 아니다. 따라서 4 분기 VPA 실시예는 신호의 동위상 및 직각위상 벡터 성분 각각을 4개의 실질적으로 일정한 포락선 성분(즉, 동위상 신호 성분을 위해 2개, 직각위상 신호 성분을 위해 2개)으로 더 분해한다. 이 개념은 페이저 신호 표기를 이용하여 도 4에 나타나 있다.

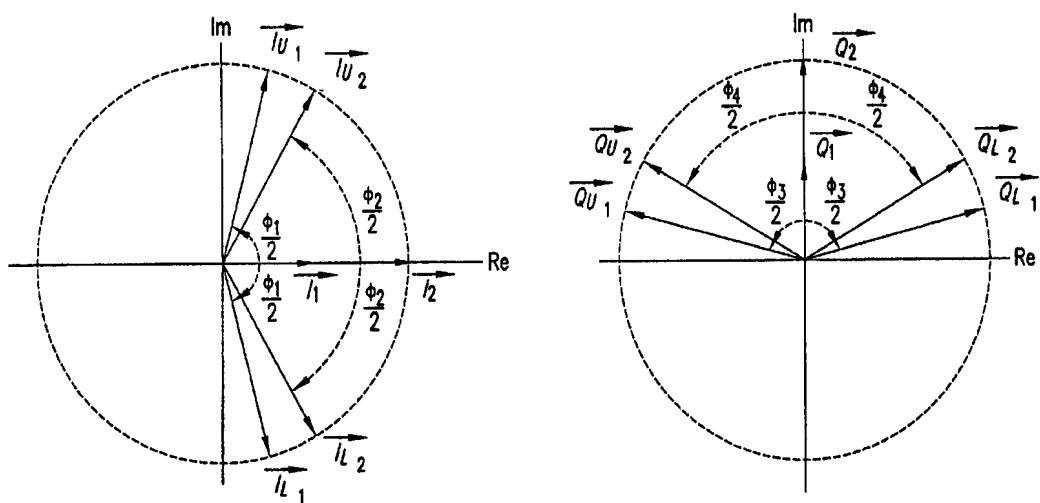

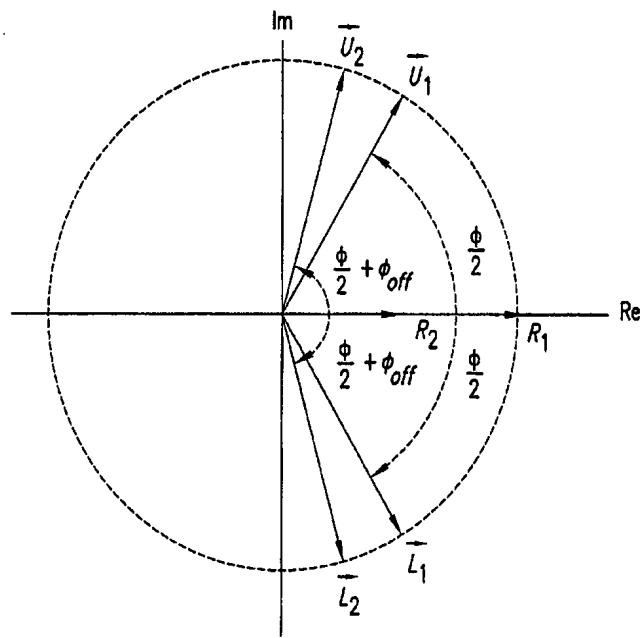

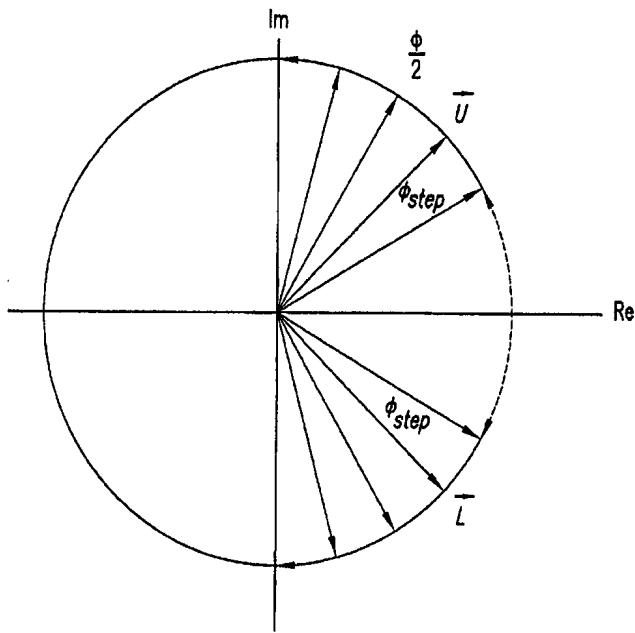

[0215] 도 4의 예에서, 페이저  $\vec{I}_1$  와  $\vec{I}_2$  는 각각 2개의 순간  $t_1$ 과  $t_2$ 에서 예시적인 시변 복소 포락선 신호의 실수부 페이저에 해당한다. 페이저  $\vec{I}_1$  와  $\vec{I}_2$  는 크기가 서로 다름에 유의한다.

[0216] 계속해서 도 4를 참조로 설명하면, 순간  $t_1$ 에서 페이저  $\vec{I}_1$  은 상위 페이저  $\overline{I}_{U_1}$  및 하위 페이저  $\overline{I}_{L_1}$  의 합으로 구해질 수 있다. 마찬가지로 순간  $t_2$ 에서 페이저  $\vec{I}_2$  는 상위 페이저  $\overline{I}_{U_2}$  와 하위 페이저  $\overline{I}_{L_2}$  의 합으로 구해질 수 있다. 페이저  $\overline{I}_{U_1}$  와  $\overline{I}_{U_2}$  는 크기가 동일 또는 실질적으로 동일하다. 마찬가지로 페이저  $\overline{I}_{L_1}$  과  $\overline{I}_{L_2}$  도 크기가 실질적으로 동일하다.

[0217] 따라서 시변 포락선 신호의 실수부 페이저는 적어도 2개의 실질적으로 일정한 포락선 성분의 합에 의해 임의의 순간에 구해질 수 있다. 페이저  $\vec{I}_1$  에 대한  $\overline{I}_{U_1}$  과  $\overline{I}_{L_1}$  의 위상 천이와 페이저  $\vec{I}_2$  에 대한  $\overline{I}_{U_2}$  와  $\overline{I}_{L_2}$  의 위상 천이는 각 페이저  $\vec{I}_1$  과  $\vec{I}_2$  의 원하는 크기에 따라 설정된다. 일 경우에 상위 및 하위 페이저가 동일한 크기를 갖도록 선택되면, 그 상위 및 하위 페이저는 페이저에 대해 위상이 대칭적으로 천이된다. 이것은 도 4의 예에 나타나 있으며, 크기가 모두 같은  $\overline{I}_{U_1}$ ,  $\overline{I}_{L_1}$ ,  $\overline{I}_{U_2}$  및  $\overline{I}_{L_2}$  에 해당한다. 두 번째 경우에 상위 및 하위 페이저의 위상 천이는 페이저에 대해 위상이 실질적으로 대칭적으로 천이된다. 여기서의 설명에 따라서 당업자

라면 상위 및 하위 페이저의 크기와 위상 천이는 그 값이 정확하게 같을 필요가 없음을 잘 알 것이다.

$$\frac{\phi_1}{2} \quad \frac{\phi_2}{2}$$

[0218] 일례로서 도 4에 도시된 경우에 도 4에서  $\frac{\phi_1}{2}$  과  $\frac{\phi_2}{2}$ 로 나타낸 상대적 위상 천이는 다음과 같이 정규화된

페이저  $\vec{I}_1$  과  $\vec{I}_2$ 의 크기에 관련된다.

$$\frac{\phi_1}{2} = \cot^{-1} \left( \frac{I_1}{2\sqrt{1 - \frac{I_1^2}{4}}} \right); \text{ and} \quad (2)$$

$$\frac{\phi_2}{2} = \cot^{-1} \left( \frac{I_2}{2\sqrt{1 - \frac{I_2^2}{4}}} \right), \quad (3)$$

[0219]

$$\vec{I}_1 \quad \vec{I}_2$$

[0220] 여기서,  $I_1$ 과  $I_2$ 는 각각 페이저의 정규화 크기를 나타내며,  $I_1$ 과  $I_2$ 의 영역은 상기 수학식 (2)와 (3)이 유효한 영역에 따라 적당히 제한된다. 수학식 (2)와 (3)은 상대적 위상 천이를 정규화 크기에 관련시키는 하나의 표현이다. 수학식 (2)와 (3)의 다른 해, 등가적 표현, 및/또는 단순화된 표현도 이용될 수 있다. 상대적 위상 천이를 정규화 크기에 관련시키는 탐색표도 이용될 수 있다.

[0221]

상기 설명된 개념은 마찬가지로 도 4에 도시된 신호  $r(t)$ 의 허수부 페이저, 즉 직각위상 성분에 적용될 수

있다. 따라서 임의의 시각  $t$ 에서 신호  $r(t)$ 의 허수부 페이저  $\vec{Q}$ 는 크기가 실질적으로 같고 일정한 상위 및

하위 페이저 성분  $\vec{Q}_U$ 와  $\vec{Q}_L$ 을 합함으로써 구해질 수 있다. 이 예에서  $\vec{Q}_U$ 와  $\vec{Q}_L$ 은 시각  $t$ 에서  $\vec{Q}$

의 크기에 따라 설정된 각도만큼  $\vec{Q}$ 에 대해 대칭적으로 위상 천이된다. 원하는 페이저  $\vec{Q}$ 에 대한  $\vec{Q}_U$ 와

$\vec{Q}_L$ 의 관계는 수학식 (2)와 (3)에서 각각  $I_1$ 과  $I_2$ 를  $Q_1$ 과  $Q_2$ 로 대체함으로써 정해지는 것으로 관계된다.

[0222]

상기 설명으로부터 페이저 표기에서 가변 크기와 위상의 임의 페이저  $\vec{R}$ 은 4개의 실질적으로 일정한 크기 페이저 성분의 합으로 구성될 수 있음을 알 수 있다.

$$\vec{R} = \vec{I}_U + \vec{I}_L + \vec{Q}_U + \vec{Q}_L;$$

$$\vec{I}_U + \vec{I}_L = \vec{I};$$

$$\vec{Q}_U + \vec{Q}_L = \vec{Q};$$

(4)

$$I_U = I_L = \text{일정};$$

$$Q_U = Q_L = \text{일정};$$

[0223]

$$\vec{I}_U, \vec{I}_L, \vec{Q}_U \text{ 및 } \vec{Q}_L$$

[0224] 여기서,  $I_U$ ,  $I_L$ ,  $Q_U$  및  $Q_L$ 은 각각 페이저  $\vec{I}_U$ ,  $\vec{I}_L$ ,  $\vec{Q}_U$  및  $\vec{Q}_L$ 의 크기를 나타낸다.

[0225] 이에 대응하여, 시간 영역에서 시변 복소 포락선 정현파 신호  $r(t) = R(t)\cos(\omega t + \phi)$ 는 다음과 같이 4개의 일정 포락선 신호의 합으로 구성된다.

$$\begin{aligned} r(t) &= I_U(t) + I_L(t) + Q_U(t) + Q_L(t); \\ I_U(t) &= \text{sgn}(\bar{I}) \times I_U \times \cos\left(\frac{\phi_I}{2}\right) \times \cos(\omega t) + I_U \times \sin\left(\frac{\phi_I}{2}\right) \times \sin(\omega t); \\ I_L(t) &= \text{sgn}(\bar{I}) \times I_L \times \cos\left(\frac{\phi_I}{2}\right) \times \cos(\omega t) - I_L \times \sin\left(\frac{\phi_I}{2}\right) \times \sin(\omega t); \quad (5) \\ Q_U(t) &= -\text{sgn}(\bar{Q}) \times Q_U \times \cos\left(\frac{\phi_Q}{2}\right) \times \sin(\omega t) + Q_U \times \sin\left(\frac{\phi_Q}{2}\right) \times \cos(\omega t); \\ Q_L(t) &= -\text{sgn}(\bar{Q}) \times Q_L \times \cos\left(\frac{\phi_Q}{2}\right) \times \sin(\omega t) - Q_L \times \sin\left(\frac{\phi_Q}{2}\right) \times \cos(\omega t). \end{aligned}$$

[0226]

[0227] 여기서,  $\bar{I}$  가 양의 실수 축에 대해 동위상인지 위상이  $180^\circ$  어긋나는지 여부에 따라  $\text{sgn}(\bar{I}) = \pm 1$

다. 마찬가지로  $\bar{Q}$  가 허수축에 대해 동위상인지 위상이  $180^\circ$  어긋나는지 여부에 따라  $\text{sgn}(\bar{Q}) = \pm 1$

이다.  $\frac{\phi_I}{2}$  은 실수축에 대한  $\overline{I_U}$  와  $\overline{I_L}$  의 위상 천이에 해당한다. 마찬가지로  $\frac{\phi_Q}{2}$  은 허수축에 대한  $\overline{Q_U}$  와  $\overline{Q_L}$  의 위상 천이에 해당한다.  $\frac{\phi_I}{2}$  와  $\frac{\phi_Q}{2}$  는 수학식 (2)와 (3)을 이용하여 계산될 수 있다.

[0228]

상기 수학식 (5)는 다음과 같이 더 간단하게 될 수 있다.

$$\begin{aligned} r(t) &= I_U(t) + I_L(t) + Q_U(t) + Q_L(t); \\ I_U(t) &= \text{sgn}(\bar{I}) \times I_{UX} \times \cos(\omega t) + I_{UY} \times \sin(\omega t); \\ I_L(t) &= \text{sgn}(\bar{I}) \times I_{UX} \times \cos(\omega t) - I_{UY} \times \sin(\omega t); \quad (6) \\ Q_U(t) &= -Q_{UX} \times \cos(\omega t) + \text{sgn}(\bar{Q}) \times Q_{UY} \times \sin(\omega t); \\ Q_L(t) &= Q_{UY} \times \cos(\omega t) - \text{sgn}(\bar{Q}) \times Q_{UX} \times \sin(\omega t). \end{aligned}$$

[0229]

[0230] 여기서,

$$I_{UX} = I_U \times \cos\left(\frac{\phi_I}{2}\right) = I_L \times \cos\left(\frac{\phi_I}{2}\right),$$

$$I_{UY} = I_U \times \sin\left(\frac{\phi_I}{2}\right) = I_L \times \sin\left(\frac{\phi_I}{2}\right),$$

[0232]

$$Q_{UX} = Q_U \times \sin\left(\frac{\phi_Q}{2}\right) = Q_L \times \sin\left(\frac{\phi_Q}{2}\right),$$

[0233]

$$Q_{UR} = Q_U \times \cos\left(\frac{\phi_Q}{2}\right) = Q_L \times \cos\left(\frac{\phi_Q}{2}\right)$$

[0234]

이다.

[0235]

당업자라면 수학식 (5)와 (6)의 시간 영역 표현은 정현파형의 경우에 대해 제공되었지만 적당한 기본 함수를 이용하여 비정현파형에 대해서도 동등한 표현이 전개될 수 있음을 잘 알 것이다. 더욱이 본 발명의 교시에 따라 당업자라면 잘 알겠지만 전술한 실질적으로 동일한 포락선 신호로의 2차원 분해는 다차원 분해로 적당히 확장될 수 있다.

[0236]

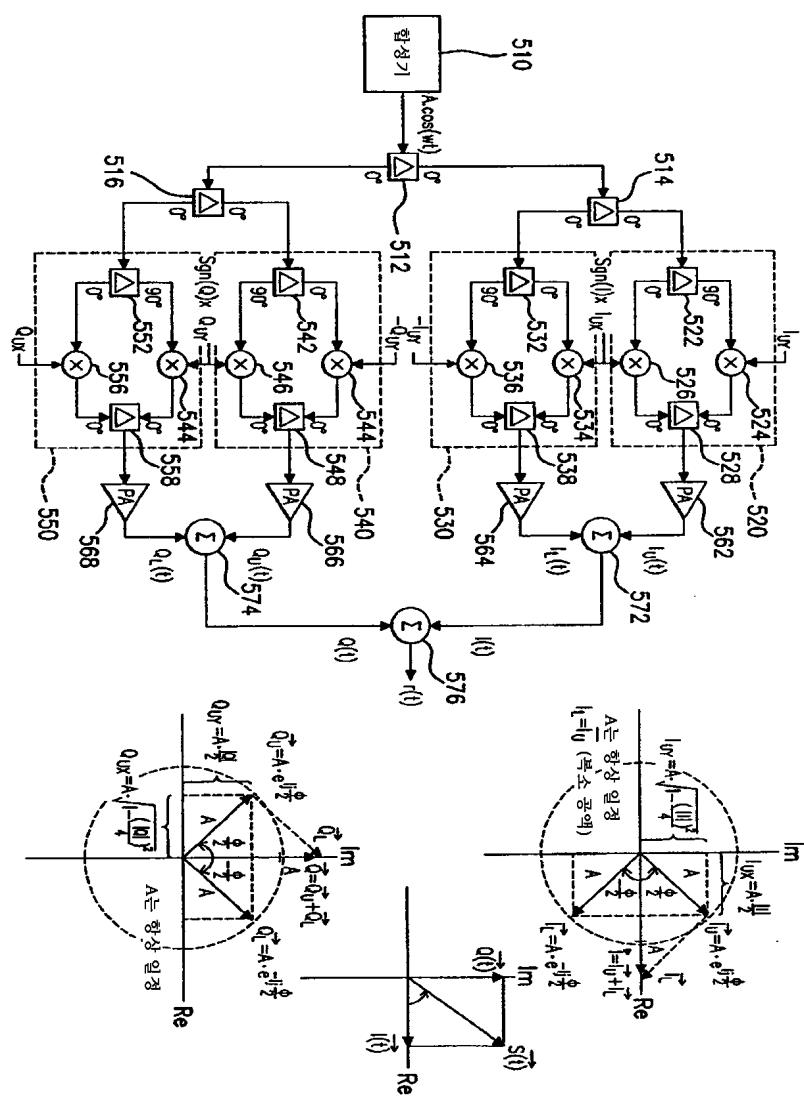

도 5는 직교 4-분기 VPA 실시예를 나타낸 예시적인 블록도이다. 원하는 전력 레벨과 주파수 특성의 출력 신호  $r(t)$ (578)는 직교 4-분기 VPA 실시예에 따라 기저대역 동위상 및 직각위상 성분으로부터 생성된다.

[0237]

도 5의 예에서 합성기(510)와 같은 주파수 발생기는 출력 신호  $r(t)$ (578)의 주파수와 동일한 주파수를 가진 기준 신호  $A \cdot \cos(\omega t)$ (511)를 발생한다. 당업자라면 기준 신호는 원하는 출력 신호에 따라 선택됨을 잘 알 수 있을 것이다. 예컨대 원하는 출력 신호의 원하는 주파수가 2.4 GHz라면, 기준 신호의 주파수는 2.4 GHz로 설정된다. 이런 식으로 본 발명의 실시예에는 주파수 상향 변환을 달성한다.

[0238]

도 5를 참조로 설명하면, 하나 또는 그 이상의 위상 분할기를 이용하여 기준 신호(511)에 기초하여 신호들(521, 531, 541, 551)을 생성한다. 도 5의 예에서 이것은 위상 분할기(512, 514, 516)를 이용하고 각 위상 분할기에서  $0^\circ$  위상 천이를 적용함으로써 달성된다. 그러나 당업자라면 기준 신호(511)의 신호들(521, 531, 541, 551)을 생성하는데는 여러 가지 기법이 이용될 수 있음을 잘 알 것이다. 예컨대 1:4 위상 분할기를 이용하여 하나의 단계에서 4개의 복제 신호(521, 531, 541, 551)를 생성할 수 있으며, 또는 도 5의 예시적인 실시예에서는 신호(511)가 신호들(521, 531, 541, 551)에 바로 결합될 수 있다. 실시예에 따라서는 여러 가지 위상 천이를 적용하여 원하는 신호들(521, 531, 541, 551)을 생성할 수 있다.

[0239]

계속해서 도 5를 참조로 설명하면, 신호(521, 531, 541, 551)는 각각 해당 벡터 변조기(520, 530, 540, 550)에 제공된다. 벡터 변조기(520, 530, 540, 550)는 그들의 적당한 입력 신호와 관련하여 상기 수학식 (6)에 따라서 신호  $r(t)$ 의 4개의 일정 포락선 성분을 생성한다. 도 5의 예시적인 실시예에서 벡터 변조기(520, 530)는 각각 신호  $r(t)$ 의  $I_U(t)$ 와  $I_L(t)$  성분을 생성한다. 마찬가지로 벡터 변조기(540, 550)는 각각 신호  $r(t)$ 의  $Q_U(t)$ 와  $Q_L(t)$  성분을 생성한다.

[0240]

벡터 변조기(520, 530, 540, 550) 각각의 실제 구현은 다를 수 있다. 예컨대 당업자라면 수학식 (6)에 따라 일정 포락선 성분을 생성하는데는 여러 가지 기법이 존재함을 잘 알 것이다.

[0241]

도 5의 예시적인 실시예에서 벡터 변조기(520, 530, 540, 550) 각각은 신호(521, 531, 541, 551)를 위상 조정(phasing)하는 입력 위상 분할기(522, 532, 542, 552)를 포함한다. 따라서 입력 위상 분할기(522, 532, 542, 552)를 이용하여 동위상 및 직각위상 성분 또는 그들 각자의 입력 신호를 생성한다.

[0242]

각 벡터 변조기(520, 530, 540, 550)에서는 동위상 및 직각위상 성분은 진폭 정보와 곱해진다. 도 5에서 예컨대 승산기(524)는 신호(521)의 직각위상 성분에  $I_U(t)$ 의 직각위상 진폭( $I_{UY}$ )를 곱한다. 그와 동시에 승산기(526)는 동위상 복제 신호에  $I_U(t)$ 의 동위상 진폭 정보( $\text{sgn}(I) \times I_{UX}$ )를 곱한다.

[0243]

$I_U(t)$ 를 생성하기 위하여 일정 포락선 성분 신호(525, 527)는 위상 분할기(528) 또는 다른 합산 기술을 이용하여 합산된다. 합산 결과 신호(529)는 신호  $r(t)$ 의  $I_{U(t)}$  성분에 해당한다.

[0244]

전술한 것과 유사한 방식으로, 벡터 변조기(530, 540, 550)는 각각 신호  $r(t)$ 의  $I_L(t)$ ,  $Q_U(t)$  및  $Q_L(t)$  성분을 생성한다.  $I_L(t)$ ,  $Q_U(t)$  및  $Q_L(t)$ 는 각각 도 5에서 신호(539, 549, 559)에 해당한다.

[0245]

더욱이, 전술한 바와 같이, 신호(529, 539, 549, 559)는 실질적으로 동일하고 일정한 크기 포락선을 갖는 것을 특징으로 한다. 따라서 신호(529, 539, 549, 559)가 해당 전력 증폭기(PA)(562, 564, 566, 568)에 입력되면, 해당 증폭 신호(563, 565, 567, 569)는 실질적으로 일정한 포락선 신호이다.

[0246]

전력 증폭기(562, 564, 566, 568)는 각각 신호(529, 539, 549, 559)를 증폭한다. 일 실시예에서, 실질적으로 동일한 전력 증폭이 각 신호(529, 539, 549, 559)에 적용된다. 일 실시예에서 PA(562, 564, 566, 568)의 전력 증폭도는 출력 신호  $r(t)$ 의 원하는 전력 레벨에 따라 설정된다.

[0247]

계속하여 도 5를 참조로 설명하면, 증폭 신호(563, 565)는 합산기(572)를 이용하여 합산되어 신호  $r(t)$ 의 동위

상 성분  $\bar{I}(t)$  의 증폭 성분(573)을 생성한다. 마찬가지로 증폭 신호(567, 569)는 합산기(574)를 이용하여 합산되어 신호  $r(t)$ 의 직각위상 성분  $\bar{Q}(t)$  의 증폭 성분(575)을 생성한다.

[0248] 신호(573, 575)는 도 5에 도시된 바와 같이 합산기(576)를 이용하여 합산되며, 합산 결과 신호가 원하는 출력 신호  $r(t)$ 에 대응한다.

[0249] 도 5의 예에서 합산기(572, 574, 576)는 단지 설명 목적상 사용되는 것임에 유의한다. 증폭 신호(563, 565, 567, 569)를 합산하는데는 여러 가지 기법이 이용될 수 있다. 예컨대 증폭 신호(563, 565, 567, 569)는 전부가 한 단계에서 합산되어 신호(578)를 생성할 수 있다. 실제로 본 발명의 여러 가지 VPA 실시예에 따라서 증폭후에 합산이 행해지는 것으로 충분하다. 후에 더 자세히 설명하겠지만, 본 발명의 특정 VPA 실시예는 와이어를 통한 직접 결합과 같은 최소 손실 합산 기법을 이용한다. 대안으로서 특정 VPA 실시예는 종래의 전력 결합 기법을 이용한다. 다른 실시예에서는, 후에 더 자세히 설명하겠지만, 전력 증폭기(562, 564, 566, 568)는 다중입력 단일출력 전력 증폭기로서 구현될 수 있다.

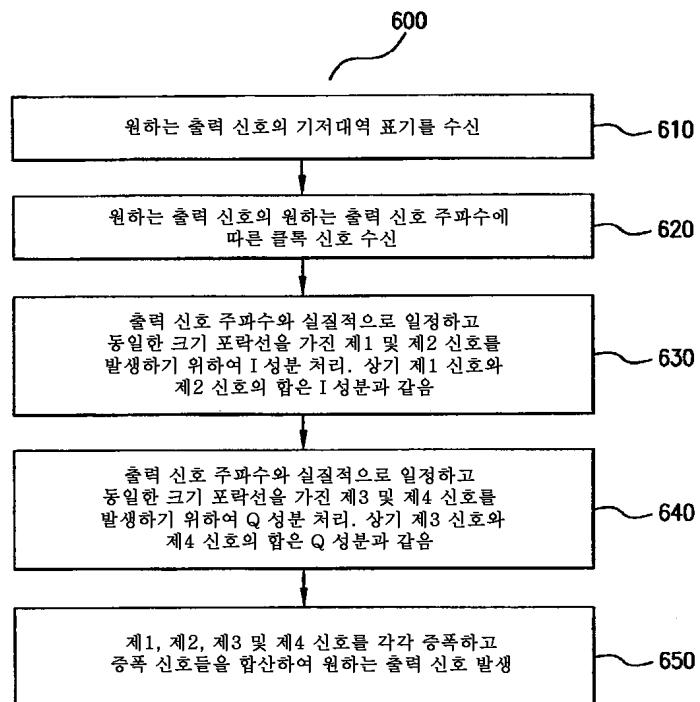

[0250] 이제 도 6의 프로세스 플로우차트를 참조로 직교 4-분기(Cartesian 4-Branch) VPA 실시예의 동작에 대해 자세히 설명한다. 프로세스는 원하는 출력 신호의 기저대역 표기를 수신하는 것을 포함하는 단계(610)에서 개시한다. 일 실시예에서 이것은 원하는 출력 신호의 동위상(I) 성분과 직각위상(Q) 성분을 수신하는 것을 포함한다. 다른 실시예에서 이것은 원하는 출력 신호의 크기와 위상을 수신하는 것을 포함한다. 직교 4-분기 VPA 실시예의 일 실시예에서 I와 Q는 기저대역 성분이다. 다른 실시예에서 I와 Q는 RF 성분이며, 기저대역으로 하향 변환된다.

[0251] 단계(620)는 원하는 출력 신호의 원하는 출력 신호 주파수에 따라 설정된 클록 신호를 수신하는 것을 포함한다. 도 5의 예에서 단계(620)는 기준 신호(511)를 수신함으로써 달성된다.

[0252] 단계(630)는 출력 신호 주파수를 가진 제1 및 제2 신호를 생성하기 위하여 I 성분을 처리하는 것을 포함한다. 제1 및 제2 신호는 실질적으로 일정하고 동일한 크기 포락선을 가지며 그 합은 I 성분과 같다. 제1 및 제2 신호는 전술한  $I_U(t)$  및  $I_L(t)$  일정 포락선 성분에 해당한다. 도 5의 예에서 단계(630)는 벡터 변조기(520, 530)에 의해 그 적당한 입력 신호와 관련하여 달성된다.

[0253] 단계(640)는 출력 신호 주파수를 가진 제3 및 제4 신호를 생성하기 위하여 Q 성분을 처리하는 것을 포함한다. 제3 및 제4 신호는 실질적으로 일정하고 동일한 크기 포락선을 가지며 그 합은 Q 성분과 같다. 제3 및 제4 신호는 전술한  $Q_U(t)$  및  $Q_L(t)$  일정 포락선 성분에 해당한다. 도 5의 예에서 단계(630)는 벡터 변조기(540, 550)에 의해 그 적당한 입력 신호와 관련하여 달성된다.

[0254] 단계(650)는 제1, 제2, 제3 및 제4 신호 각각을 개별적으로 증폭하고, 원하는 출력 신호를 생성하기 위하여 그 증폭 신호를 합산하는 것을 포함한다. 일 실시예에서 제1, 제2, 제3 및 제4 신호의 증폭은 실질적으로 동일하며, 원하는 출력 신호의 원하는 전력 레벨에 따른다. 도 5의 예에서 단계(650)는 각자의 신호(529, 539, 549, 559)를 증폭하는 전력 증폭기(562, 564, 566, 568)와 출력 신호(578)를 생성하기 위해 증폭 신호(563, 565, 567, 569)를 합산하는 합산기(572, 574, 576)에 의해 달성된다.

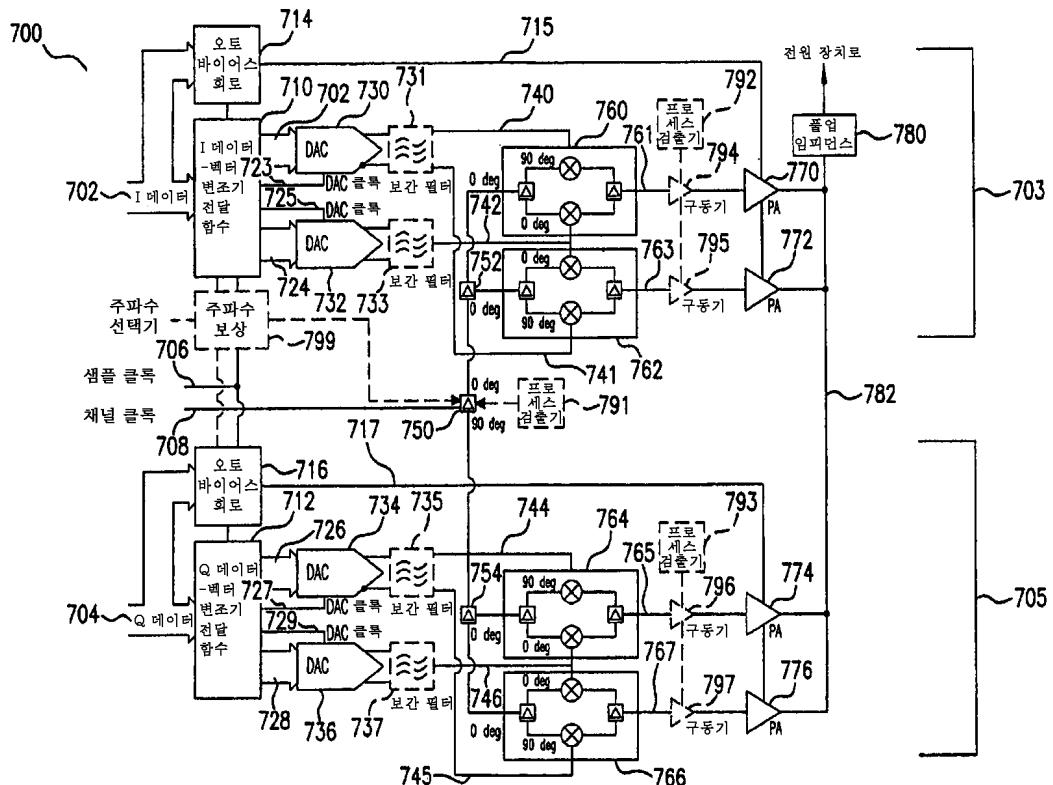

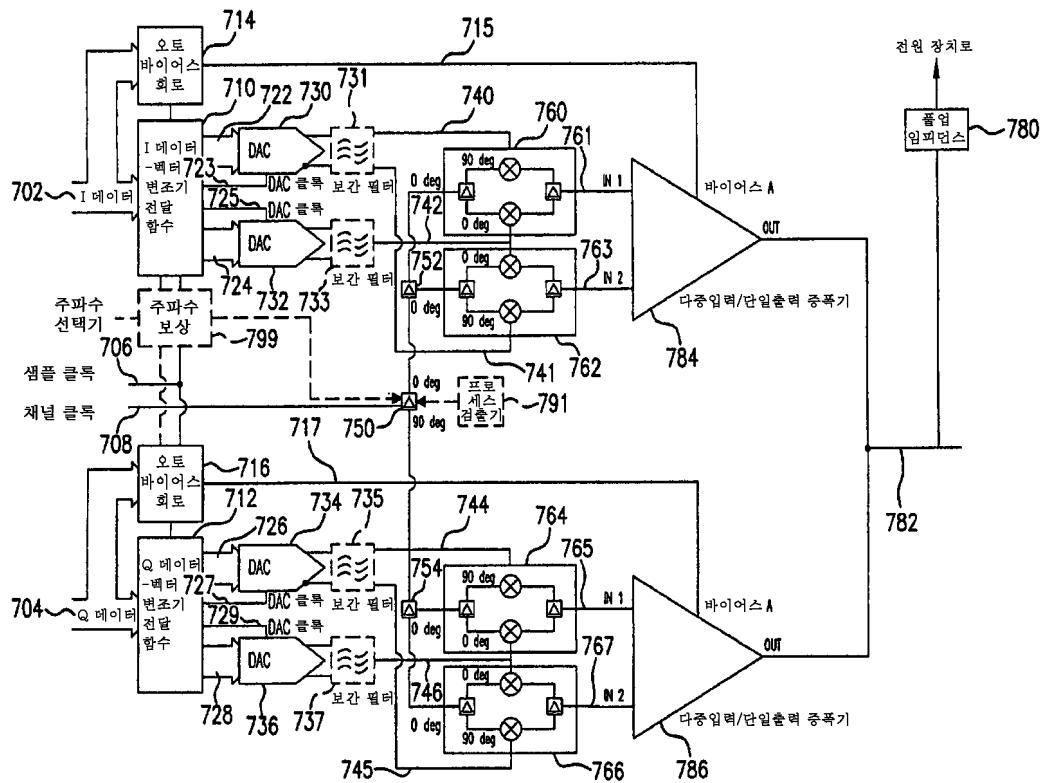

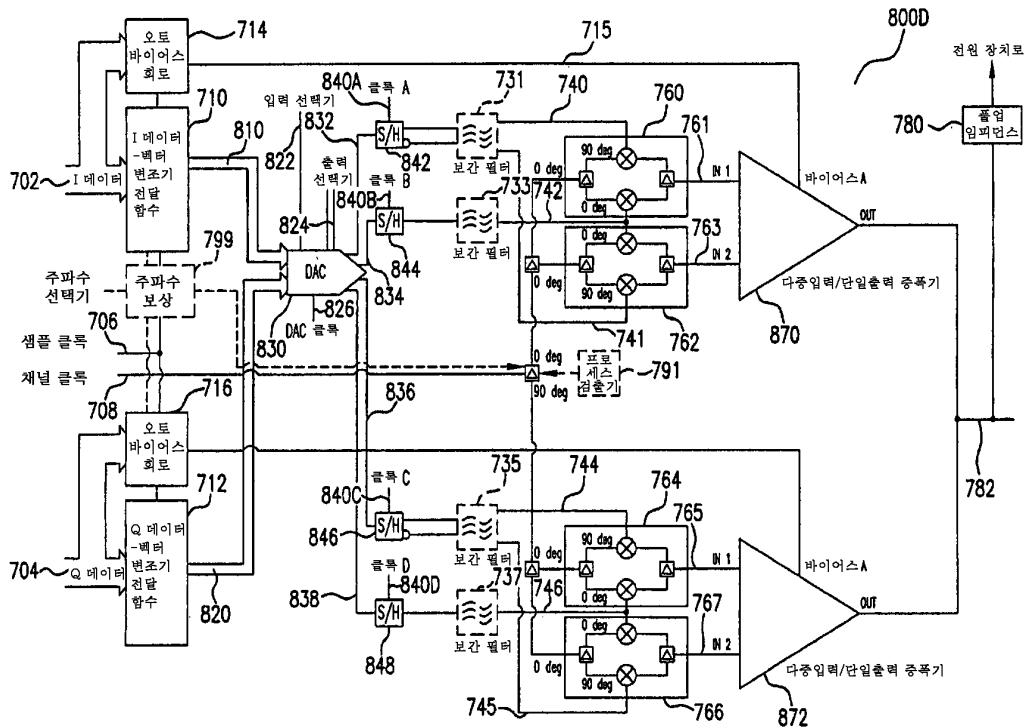

[0255] 도 7A는 도 6의 프로세스 플로우차트(600)를 구현하는 벡터 전력 증폭기(700)의 예시적인 실시예를 나타낸 블록도이다. 도 7A의 예에서 선택 성분은 과선으로 나타낸다. 다른 실시예에서 추가적인 성분이 선택적일 수 있다.

[0256] 벡터 전력 증폭기(700)는 동위상(I) 분기(703)와 직각위상(Q) 분기(705)를 포함한다. I 및 Q 분기 각각은 제1 분기와 제2 분기를 더 포함한다.

[0257] 동위상(I) 정보 신호(702)는 I 데이터 전달 함수 모듈(710)에 의해 수신된다. 일 실시예에서 I 정보 신호(702)는 디지털 기저대역 신호를 포함한다. 일 실시예에서 I 데이터 전달 함수 모듈(710)은 샘플 클록(706)에 따라서 I 정보 신호(702)를 샘플링한다. 다른 실시예에서 I 정보 신호(702)는 아날로그 기저대역 신호를 포함하며, 이 아날로그 기저대역 신호는 I 데이터 전달 함수 모듈(710)에 입력되기 전에 아날로그-디지털 변환기(ADC)(도 7A에는 미도시)를 이용하여 디지털로 변환된다. 다른 실시예에서 I 정보 신호(702)는 아날로그 회로를 포함하는 I 데이터 전달 함수 모듈(710)에 아날로그 형태로 입력되는 아날로그 기저대역 신호를 포함한다.

다른 실시예에서 I 정보 신호(702)는 전술한 임의의 실시예를 이용하여 I 데이터 전달 함수 모듈(710)에 입력되기 전에 기저대역으로 하향 변환되는 RF 신호를 포함한다.

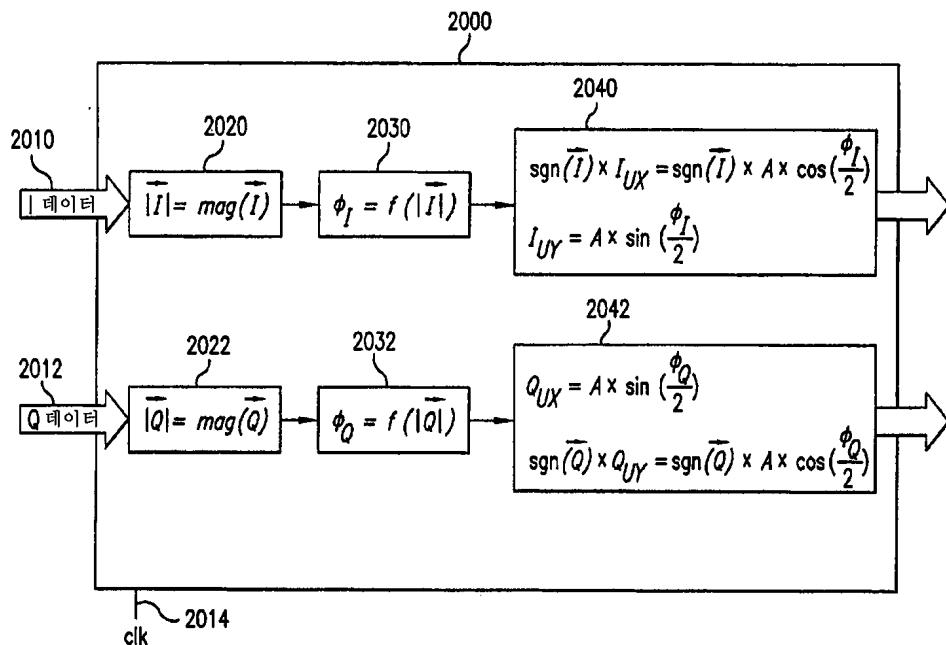

[0258] I 데이터 전달 함수 모듈(710)은 I 정보 신호(702)를 처리하고, I 정보 신호(702)의 적어도 2개의 일정 포락선 성분 신호의 동위상 및 직각위상 진폭 정보를 결정한다. 도 5를 참조로 전술한 바와 같이, 동위상 및 직각위상 벡터 변조기 입력 진폭 정보는 각각  $\text{sgn}(I) \times I_{\text{UX}}$  및  $I_{\text{UY}}$ 에 해당한다. I 데이터 전달 함수 모듈(710)의 동작에 대해서는 뒤에 3.4 절에서 자세히 설명한다.

[0259] I 데이터 전달 함수 모듈(710)은 벡터 변조기(760, 762)의 동위상 및 직각위상 진폭 성분을 제어하는데 이용되는 정보 신호(722, 724)를 출력한다. 일 실시예에서 신호(722, 724)는 디지털 신호이다. 따라서 각 신호(722, 724)는 각각 해당 디지털-아날로그 변환기(DAC)(730, 732)에 공급된다. DAC(730, 732)의 분해능과 샘플 레이트는 출력 신호(782)의 원하는 I 성분을 얻도록 선택된다. DAC(730, 732)는 각각 DAC 클록 신호(723, 725)에 의해 제어된다. DAC 클록 신호(723, 725)는 같은 클록 신호로부터 도출되거나 서로 독립적일 수 있다.

[0260] 다른 실시예에서 신호(722, 724)는 아날로그 신호이며, DAC(730, 732)는 필요하지 않다.

[0261] 도 7A의 예시적인 실시예에서 DAC(730, 732)는 디지털 정보 신호(722, 724)는 대응하는 아날로그 신호로 변환하며, 이를 아날로그 신호를 각각 선택적인 보간 필터(731, 733)에 입력한다. 앤티앨리어싱(anti-aliasing) 필터로도 기능하는 보간 필터(731, 733)는 원하는 출력 과형을 만들기 위하여 DAC 출력을 정형(shaping)한다. 보간 필터(731, 733)는 각각 신호(740, 742)를 생성한다. 신호(741)는 신호(740)의 반전을 나타낸다. 신호(740-742)는 벡터 변조기(760, 762)에 입력된다.

[0262] 벡터 변조기(760, 762)는 I 정보 신호(702)의 일정 포락선 성분을 생성하기 위하여 신호(740-742)를 적당히 위상 조정된 클록 신호에 곱한다. 이 클록 신호는 원하는 출력 신호 주파수에 따른 레이트를 가진 채널 클록 신호(708)로부터 도출된다. 예컨대 750과 752와 같은 복수의 위상 분할기와, 벡터 변조기 승산기와 연관된 페이저를 이용하여 적당히 위상 조정된 클록 신호를 생성할 수 있다.

[0263] 도 7A의 실시예에서, 예컨대 벡터 변조기(760)는 직각위상 진폭 정보 신호(740)를 가지고  $90^\circ$  천이된 채널 클록 신호를 변조한다. 이와 동시에 벡터 변조기(760)는 동위상 진폭 정보 신호(742)를 가지고 동위상 채널 클록 신호를 변조한다. 벡터 변조기(760)는 이 2개의 변조 신호를 결합하여 I 정보 신호(702)의 제1 변조 일정 포락선 성분(761)을 생성한다. 마찬가지로 벡터 변조기(762)는 신호(741, 742)를 이용하여 I 정보 신호(702)의 제2 변조 일정 포락선 성분(763)을 생성한다. 신호(761, 763)는 각각 도 5를 참조로 설명된  $I_U(t)$  및  $I_L(t)$  일정 포락선 성분에 해당한다.

[0264] 이와 동시에 그리고 이와 유사한 방식으로 벡터 전력 증폭기(700)의 q 분기는 직각위상(Q) 정보 신호(704)의 적어도 2개의 일정 포락선 성분 신호를 생성한다.

[0265] 도 7A의 실시예에서, 예컨대 벡터 변조기(764)는 신호(744, 746)를 이용하여 Q 정보 신호(704)의 제1 일정 포락선 성분(765)을 생성한다. 마찬가지로 벡터 변조기(766)는 신호(745, 746)를 이용하여 Q 정보 신호(704)의 제2 일정 포락선 성분(767)을 생성한다.

[0266] 도 5를 참조로 전술한 바와 같이, 성분 신호(761, 763, 765, 767)는 실질적으로 동일하고 일정한 크기 포락선을 갖고 있다. 도 7A의 예시적인 실시예에서 신호(761, 763, 765, 767)는 각각 해당 전력 증폭기(PA)(770, 772, 774, 776)에 입력된다. PA(770, 772, 774, 776)는 선형 또는 비선형 전력 증폭기일 수 있다. 일 실시예에서 PA(770, 772, 774, 776)는 스위칭 전력 증폭기를 포함한다.

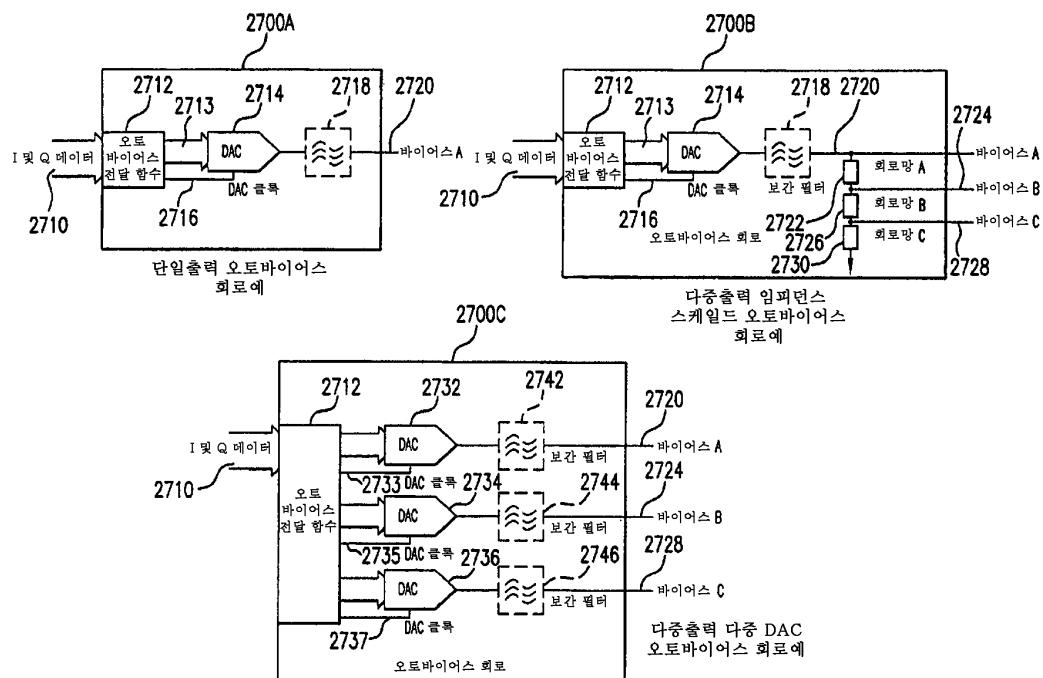

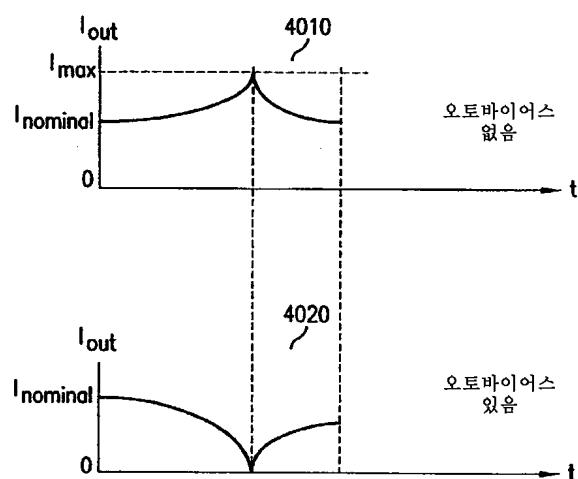

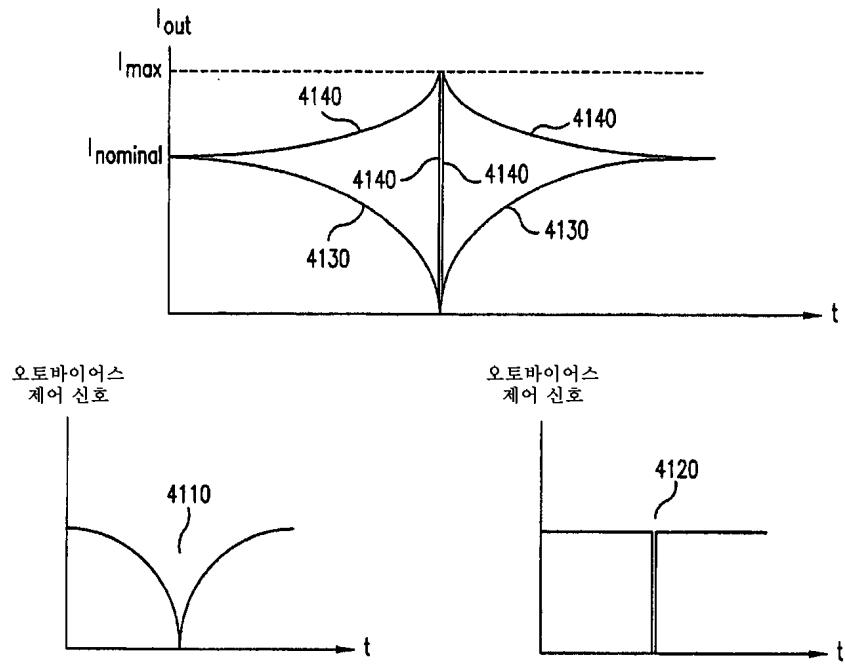

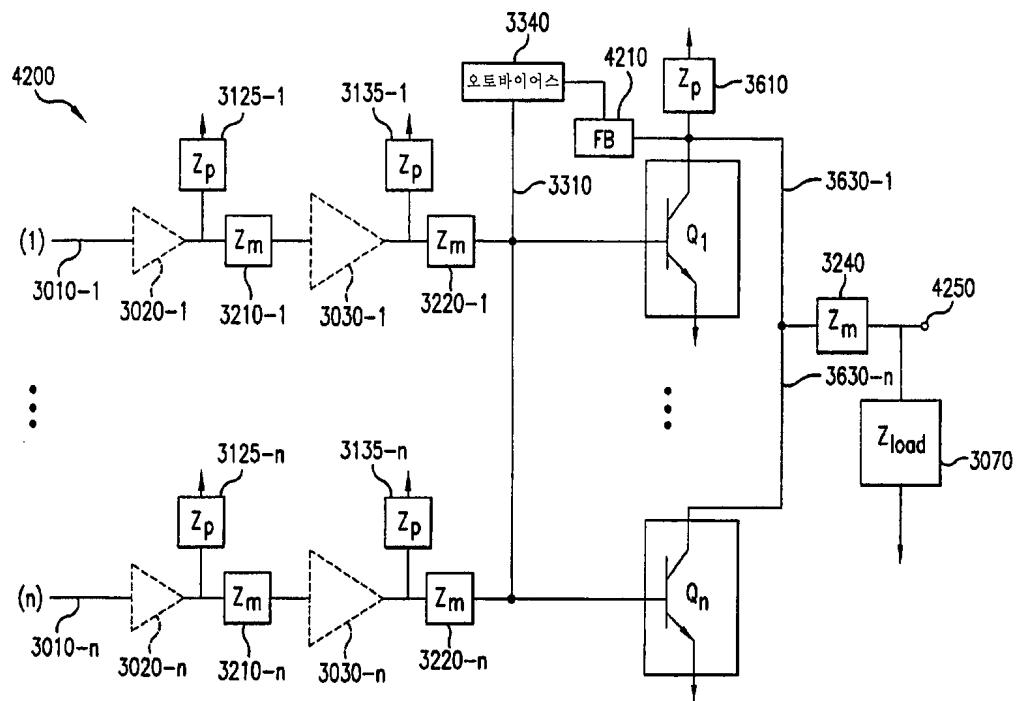

[0267] 이 실시예에서 회로(714, 716)(여기서는 참조가 용이하게 "오토바이어스(autobias) 회로"라 칭하지만 이에 제한되지 않음)는 I 및 Q 정보 신호(702, 704)에 따라 PA(770, 772, 774, 776)의 바이어스를 제어한다. 도 7A의 실시예에서 오토바이어스 회로(714, 716)는 각각 PA(770, 772)와 PA(774, 776)에 바이어스 신호(715, 717)를 제공한다. 오토바이어스 회로(714, 716)에 대해서는 이후 3.5 절에서 자세히 설명한다. PA(770, 772, 774, 776)의 실시예에 대해서도 이후 3.5 절에서 설명한다.

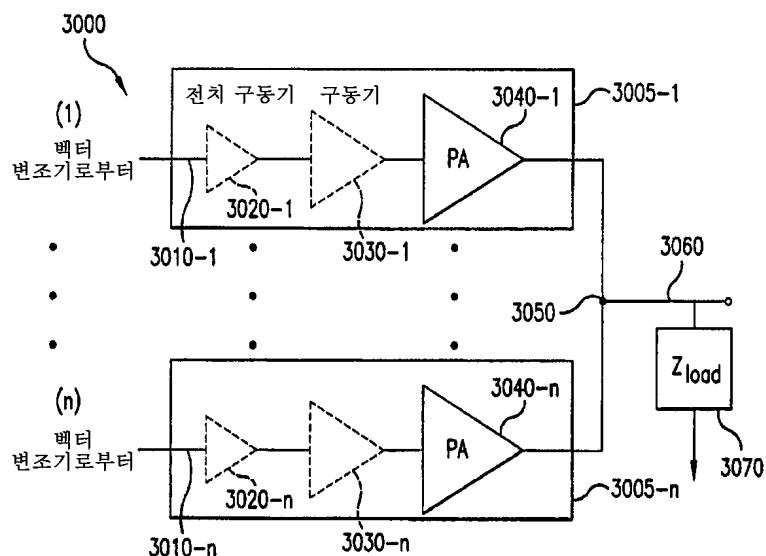

[0268] 일 실시예에서 PA(770, 772, 774, 776)는 실질적으로 동일한 전력 증폭을 각자의 실질적으로 일정한 포락선 신호(761, 763, 765, 767)에 인가한다. 다른 실시예에서는 PA 구동기를 추가적으로 채용하여 추가적인 전력 증폭을 제공한다. 도 7A의 실시예에서 PA 구동기(794, 795, 796, 797)는 벡터 전력 증폭기(700)의 각 분기에서 각자의 벡터 변조기(760, 762, 764, 766)와 각자의 PA(770, 772, 774, 776) 사이에 선택적으로 부가된다.

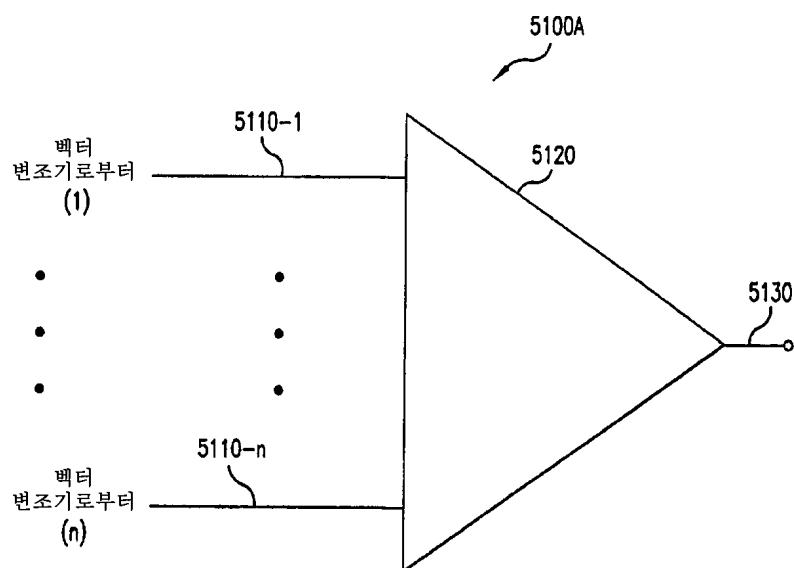

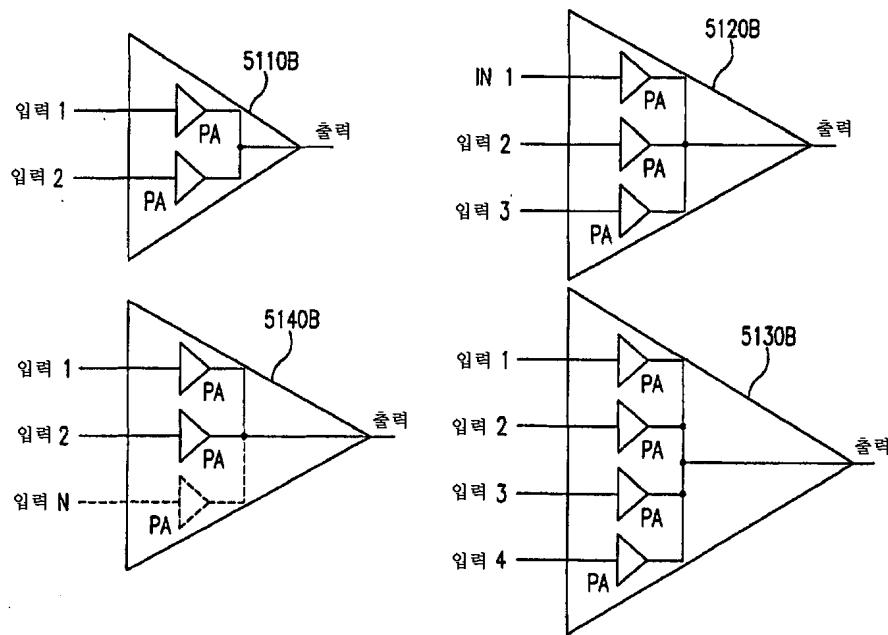

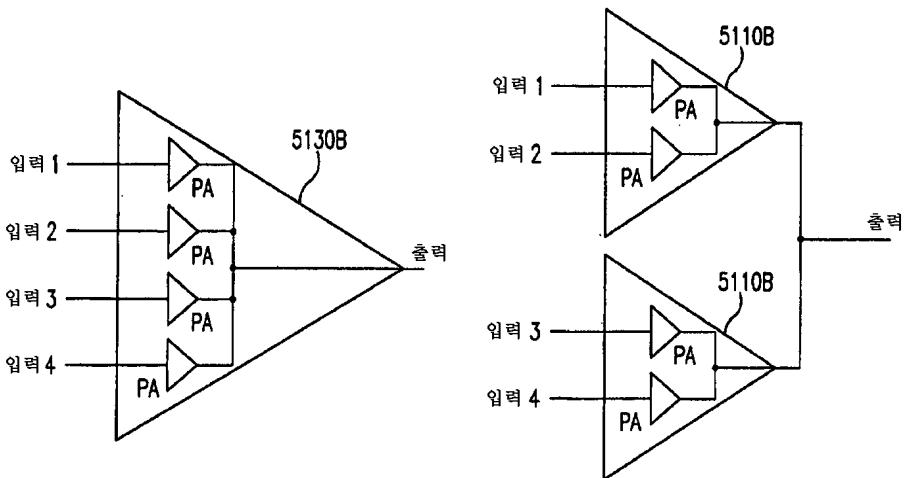

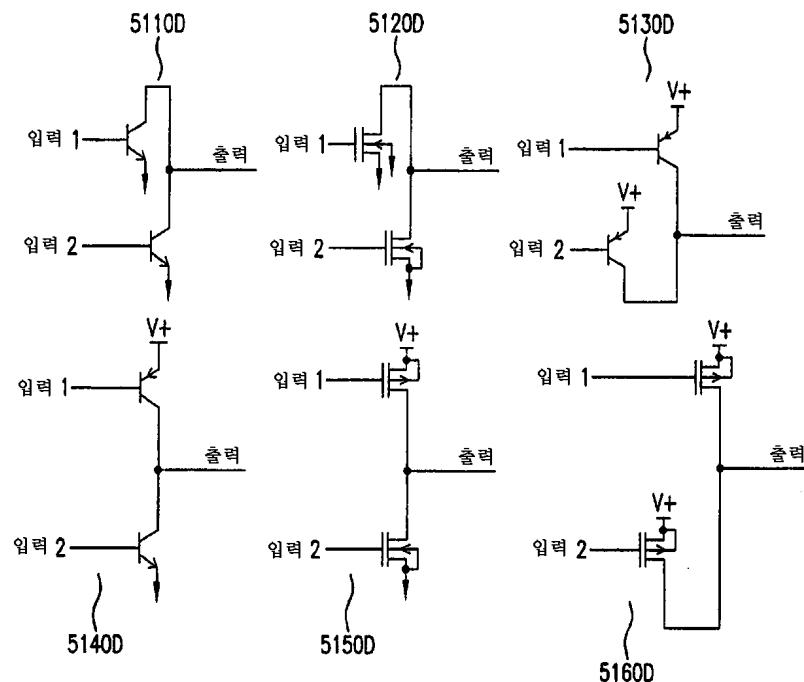

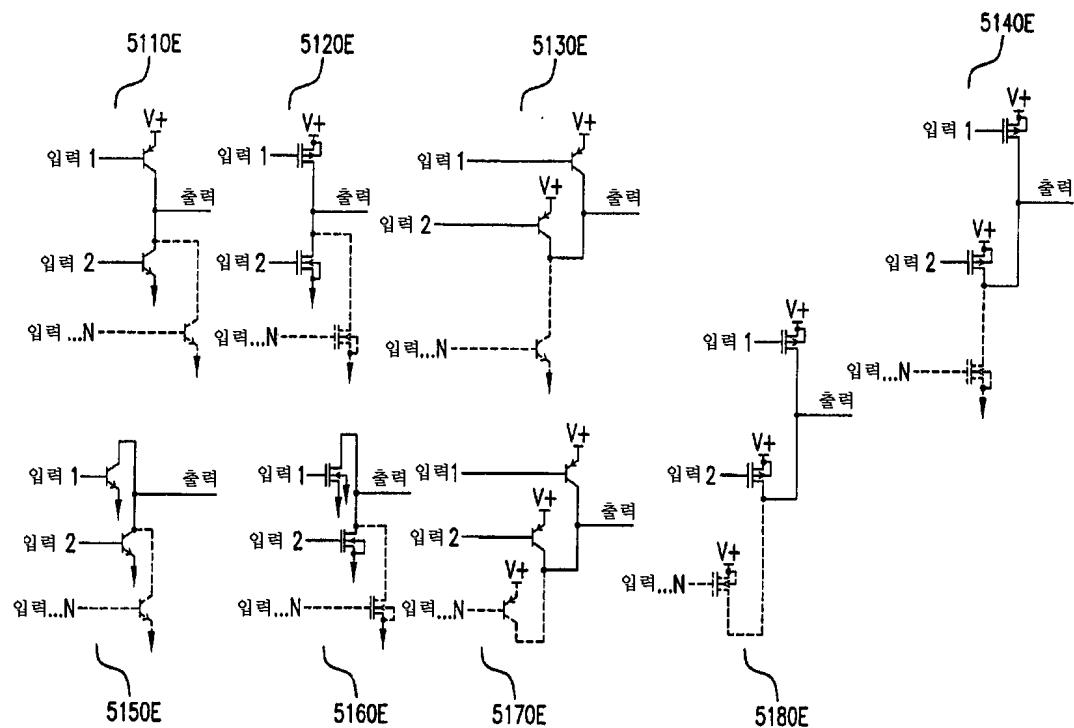

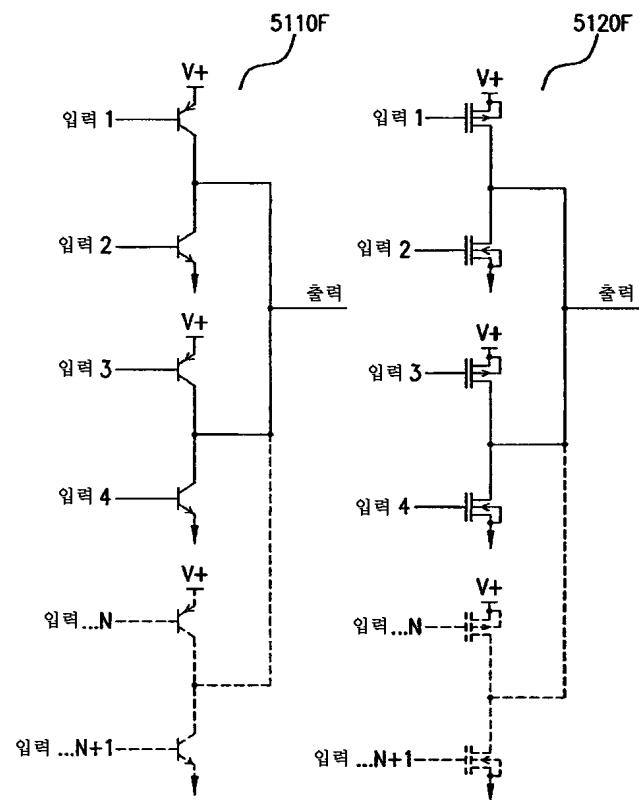

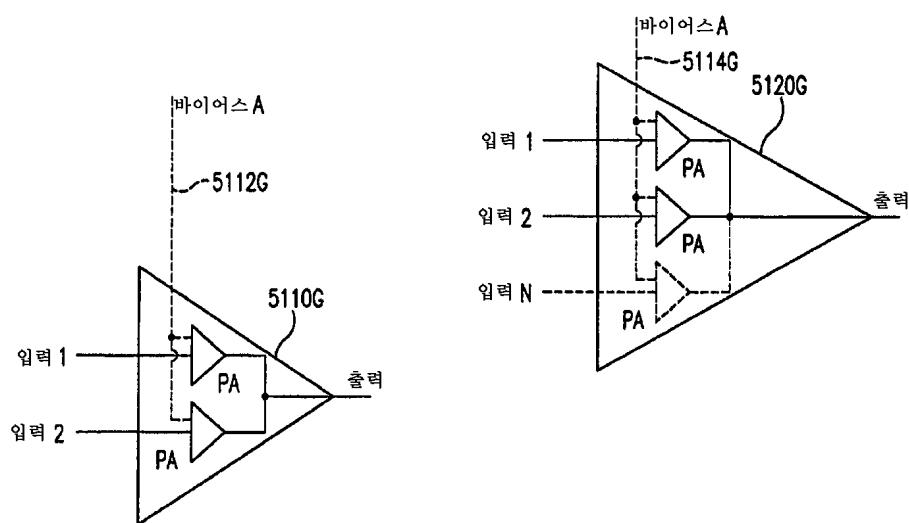

- [0269] PA(770, 772, 774, 776)의 출력은 함께 결합되어 벡터 전력 증폭기(700)의 출력 신호(782)를 생성한다. 일 실시예에서 PA(770, 772, 774, 776)의 출력은 와이어를 이용하여 함께 직접 결합된다. 이런 식의 직접 결합은 PA(770, 772, 774, 776)의 출력들 간에 저항성, 유도성 또는 용량성 결합이 극소이거나 없다는 것을 의미한다. 즉, PA(770, 772, 774, 776)의 출력은 성분 간섭 없이 함께 결합된다. 대안으로서, 일 실시예에서 PA(770, 772, 774, 776)의 출력은 임피던스 연결을 작게하거나 최소화하는 인더턴스 및/또는 커패시턴스를 통해, 그리고 /또는 절연과 전력 손실을 최소화하는 소정 연결부를 통해 간접적으로 함께 결합된다. 대안으로서, PA(770, 772, 774, 776)의 출력은 윌킨슨(Wilkinson), 하이브리드, 변압기 또는 공자의 능동 결합기와 같은 공자의 결합 기술을 이용하여 결합된다. 일 실시예에서 PA(770, 772, 774, 776)는 한 번의 동작으로 통합된 증폭과 전력 결합을 제공한다. 일 실시예에서 여기서 설명된 전력 증폭기 및/또는 구동기를 중 하나 또는 그 이상은 다중입력 단일출력 전력 증폭 기술을 이용하여 구현되며, 그 예는 도 7B 및 도 51A 내지 51H에 나타나 있다.

- [0270] 출력 신호(782)는 I 및 Q 정보 신호(702, 704)의 I 및 Q 특성을 포함한다. 더욱이, 출력 신호(782)는 그 성분과 주파수가 동일하며, 따라서 원하는 상향 변환 출력 주파수를 갖는다. 벡터 전력 증폭기(700)의 실시예에서 풀업 임피던스(780)는 벡터 증폭기(700)의 출력과 전원 장치 사이에 연결된다. 본 발명의 전력 증폭 방법 및 시스템에 따른 출력단 실시예에 대해서는 이후의 3.5 절에서 자세히 설명한다.

- [0271] 벡터 전력 증폭기(700)의 다른 실시예에서는 프로세스 검출기를 채용하여 증폭기의 회로에서의 임의의 프로세스 변동을 보상한다. 도 7A의 실시예에서, 예컨대 프로세스 검출기(791-793)는 선택적으로 추가되어 PA 구동기(794-797)와 위상 분할기(750)에서의 변동을 모니터한다. 또 다른 실시예에서는 주파수 보상 회로(799)를 채용하여 주파수 변동을 보상할 수 있다.

- [0272] 도 7B는 벡터 전력 증폭기(700)의 다른 예시적인 실시예를 나타낸 블록도이다. 선택적 성분은 파선으로 나타내며, 다른 실시예에서는 이러한 선택적 성분은 가감될 수 있다.

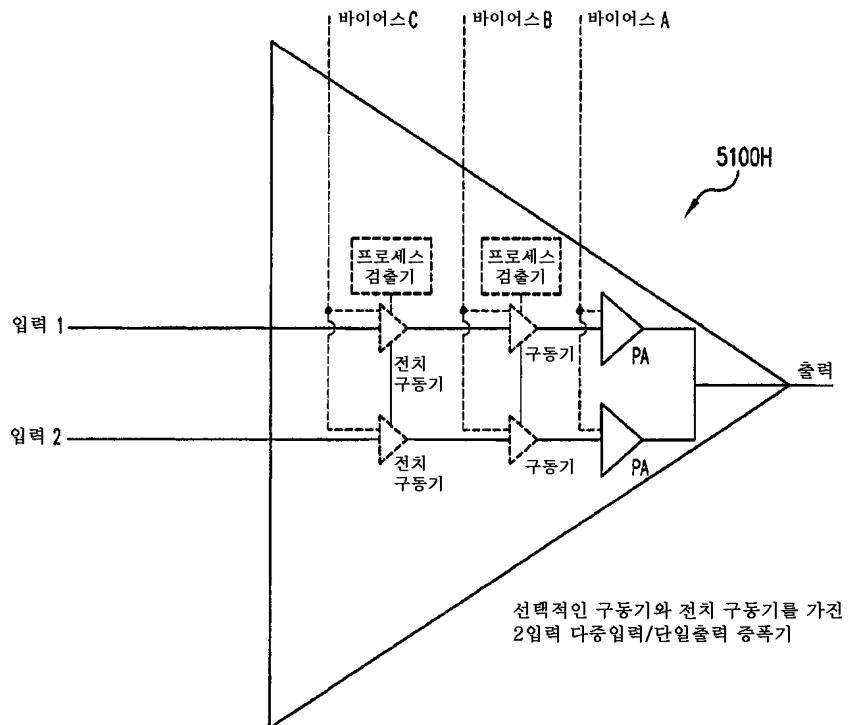

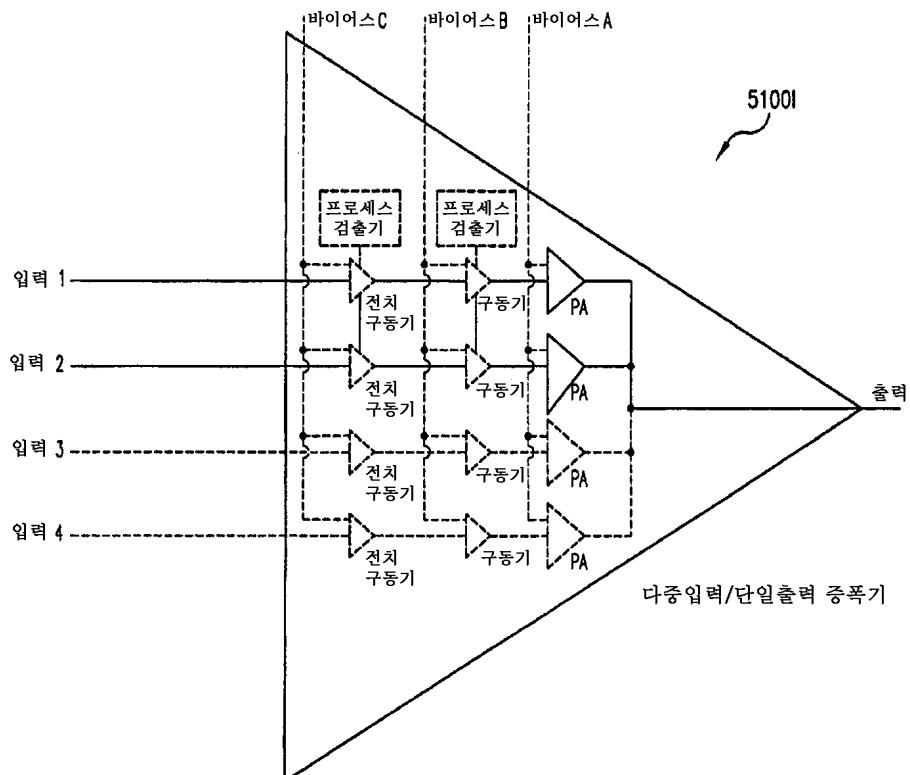

- [0273] 이 실시예는 도 7A의 증폭기의 다중입력 단일출력(MISO) 구현을 보여준다. 도 7B의 실시예에서 벡터 변조기(760, 762, 764, 766)로부터 출력된 일정 포락선 신호(761, 763, 765, 767)는 MISO PA(784, 786)에 입력된다. MISO PA(784, 786)는 2-입력 단일출력 전력 증폭기이다. 일 실시예에서 MISO PA(784, 786)는 도 7A의 실시예에 나타난 요소(770, 772, 774, 776, 794-797) 또는 그 기능적 등가물을 포함한다. 다른 실시예에서 MISO PA(784, 786)는 선택적인 전치 구동기와 선택적인 프로세스 검출 회로와 같은 다른 요소를 포함할 수 있다. 더욱이 MISO PA(784, 786)는 도 7B에 도시된 2-입력 PA에 한정되지 않는다. 다른 실시예에서, 이후 도 51A 내지 51H를 참조로 자세히 설명되겠지만, PA(784, 786)는 임의 수의 입력과 출력을 가질 수 있다.

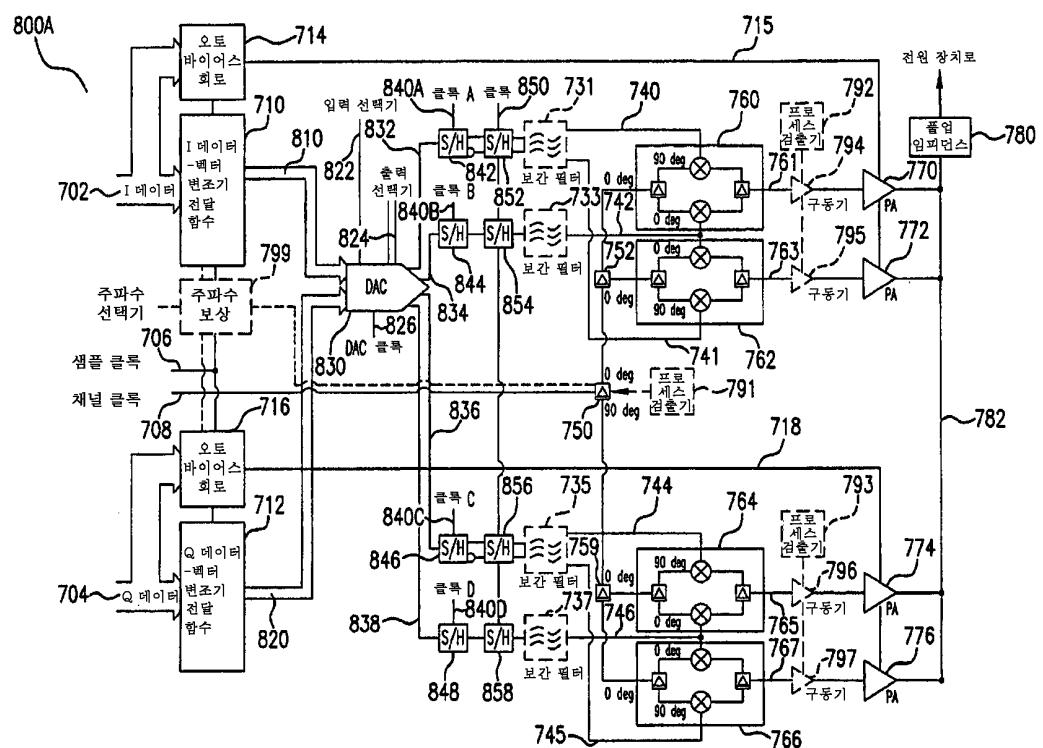

- [0274] 도 8A는 도 6에 도시된 직교 4-분기 VPA법에 따른 벡터 전력 증폭기의 다른 예시적인 실시예(800A)를 나타낸 블록도이다. 선택적 성분은 파선으로 나타내며, 다른 실시예에서는 이러한 선택적 성분은 가감될 수 있다.

- [0275] 도 8A의 실시예에서는 충분한 분해능과 샘플 레이트를 가진 DAC(830)는 도 7A의 실시예의 DAC(730, 732, 734, 736)를 대체한다. DAC(830)의 샘플 레이트는 DAC 클록 신호(826)에 의해 제어된다.

- [0276] DAC(830)는 전술한 바와 같이 I 데이터 전달 함수 모듈(710) 및 Q 데이터 전달 함수 모듈(712)로부터 각각 동위상 및 직각위상 정보 신호(810, 820)를 수신한다. 일 실시예에서 입력 선택기(822)는 DAC(830)에 입력되는 신호(810, 820)의 순서를 선택한다.

- [0277] DAC(830)는 한 번에 하나의 아날로그 신호를 출력할 수 있다. 일 실시예에서는 샘플 홀드 구조를 이용하여 도 8A에 도시된 바와 같이 증폭기의 4개 분기에 대한 적당한 신호 타이밍을 보장할 수 있다.

- [0278] DAC(830)는 아날로그 신호(832, 834, 836, 838)를 제1 샘플 홀드 회로 세트(842, 844, 846, 848)에 순차적으로 출력한다. 일 실시예에서 DAC(830)는 도 7A의 실시예의 DAC(730, 732, 734, 736)의 동작을 에뮬레이트하기에 충분한 레이트로 클록된다. 출력 선택기(824)는 출력 신호(832, 834, 836, 838) 중 어느 것이 출력으로 선택되어야 하는지를 판단한다.

- [0279] DAC(830)의 DAC 클록 신호(826), 출력 선택기 신호(824), 입력 선택기 신호(822) 및 샘플 홀드 클록(840A-D, 850)은 독립적이거나 또는 전달 함수 모듈(710 및/또는 712)에 접속될 수 있는 제어 모듈에 의해 제어된다.

- [0280] 일 실시예에서 샘플 홀드 회로(S/H)(842, 844, 846, 848)는 클록 신호(840A-D)에 따라서 DAC(830)로부터 수신된 아날로그값을 샘플링하여 홀드한다. 샘플 홀드 회로(852, 854, 856, 858)는 각각 샘플 홀드 회로(842, 844, 846, 848)로부터의 아날로그값을 샘플링하여 홀드한다. 이어서, 샘플 홀드 회로(852, 854, 856, 858)는 수신된 아날로그값을 홀드하고, 공통 클록 신호(850)에 따라서 그 값을 벡터(760, 762, 764, 766)에 동시에 방출한다.

다른 실시예에서 샘플 홀드 회로(852, 854, 856, 858)는 그 값을 선택적인 보간 필터(731, 733, 735, 737)(안티앨리어싱 필터라고도 함)에 방출한다. 일 실시예에서 공통 클록 신호(850)는 S/H(852, 854, 856, 858)의 출력이 시간 정렬되는 것을 보장하도록 이용된다.

[0281] 벡터 전력 증폭기(800A)의 다른 양상은 벡터 전력 증폭기(700)에 대해 전술한 것과 거의 같다.

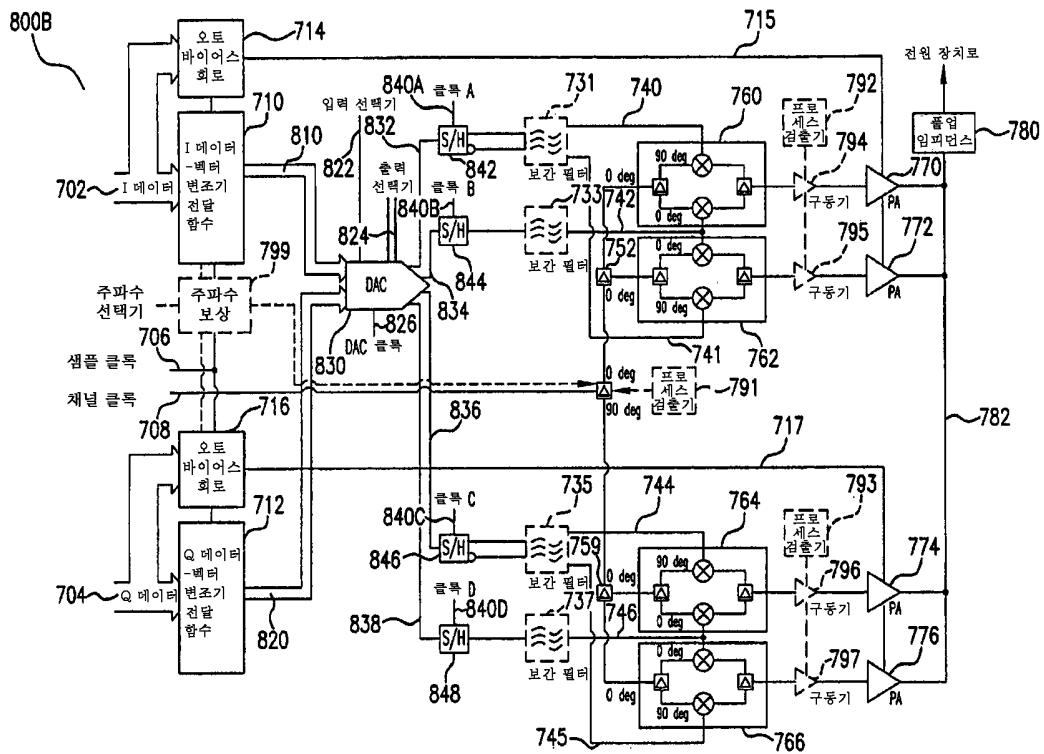

[0282] 도 8B는 도 6에 도시된 직교 4-분기 VPA법에 따른 벡터 전력 증폭기의 다른 예시적인 실시예(800B)를 나타낸 블록도이다. 선택적 성분은 파선으로 나타내며, 다른 실시예에서는 이러한 선택적 성분은 가감될 수 있다.

[0283] 실시예(800B)는 벡터 전력 증폭기의 다른 하나의 DAC 구현을 보여준다. 그러나 도 8A의 실시예와는 달리, 샘플 홀드 구조는 단일 세트의 샘플 홀드(S/H) 회로를 포함한다. 도 8B에 도시된 바와 같이 S/H(842, 844, 846, 848)는 DAC(830)로부터 신호(832, 834, 836, 838)로 나타낸 아날로그값을 수신한다. S/H 회로(842, 844, 846, 848) 각각은 그 수신값을 도시된 바와 같은 여러 가지 클록(840A-D)에 따라서 방출한다. 신호(740, 741, 742, 744, 745, 746)를 생성하는데 이용되는 아날로그 샘플들 간의 시간차는 전달 함수(710, 712)에서 보상될 수 있다. 도 8B의 실시예에 따르면 도 8A의 실시예에 비해 한 레벨의 S/H 회로가 생략될 수 있어 증폭기의 크기와 복잡성을 저감할 수 있다.

[0284] 벡터 전력 증폭기(800B)의 다른 양상은 벡터 전력 증폭기(700, 800A)에 대해 전술한 것과 거의 같다.

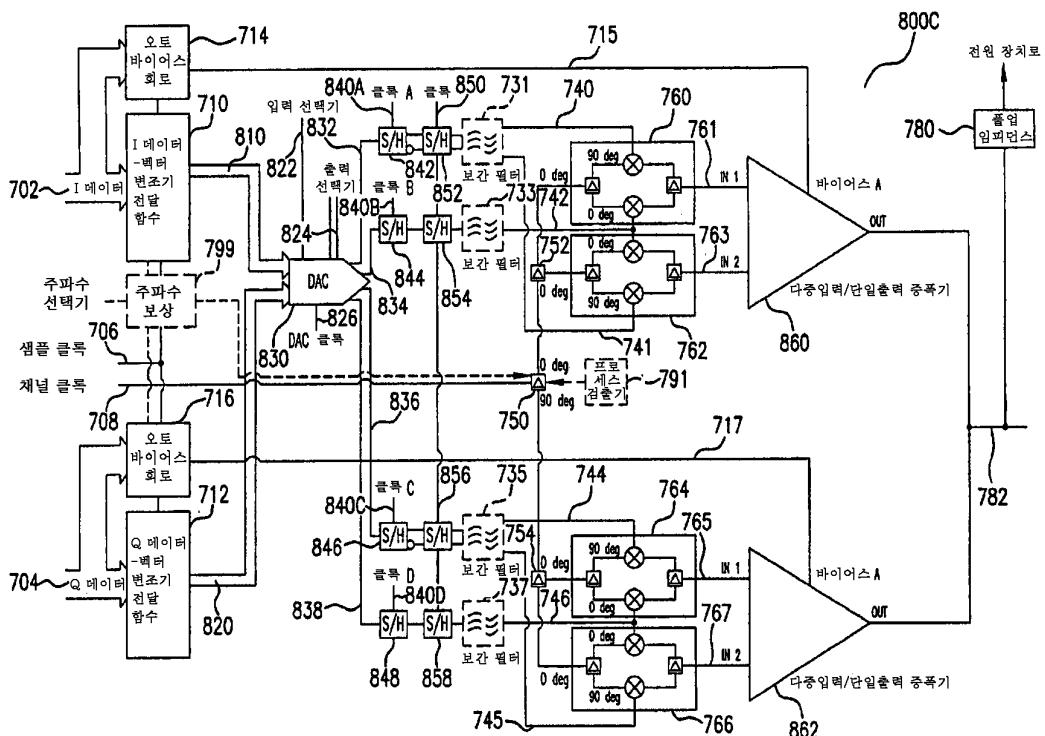

[0285] 도 8C는 벡터 전력 증폭기(700)의 다른 예시적인 실시예(800C)를 나타낸 블록도이다. 선택적 성분은 파선으로 나타내며, 다른 실시예에서는 이러한 선택적 성분은 가감될 수 있다. 도 8C의 실시예는 도 8A의 증폭기의 다중 입력 단일출력(MISO) 구현을 보여준다. 도 8C의 실시예에서 벡터 변조기(760, 762, 764, 766)로부터 출력된 일정 포락선 신호(761, 763, 765, 767)는 MISO PA(860, 862)에 입력된다. MISO PA(860, 862)는 2-입력 단일출력 전력 증폭기이다. 일 실시예에서 MISO PA(860, 862)는 도 7A의 실시예에 나타난 요소(770, 772, 774, 776, 794-797) 또는 그 기능적 등가물을 포함한다. 다른 실시예에서 MISO PA(860, 862)는 선택적인 전치 구동기와 선택적인 프로세스 검출 회로와 같은 다른 요소를 포함할 수 있다. 다른 실시예에서 MISO PA(860, 862)는 도 7A의 실시예에는 없는 전치 구동기와 같은 다른 요소를 포함할 수 있다. 더욱이 MISO PA(860, 862)는 도 8C에 도시된 2-입력 PA에 한정되지 않는다. 다른 실시예에서, 이후 도 51A 내지 51H를 참조로 자세히 설명되겠지만, PA(860, 862)는 임의 수의 입력과 출력을 가질 수 있다.

[0286] 벡터 전력 증폭기(800C)의 다른 양상은 벡터 전력 증폭기(700, 800A)에 대해 전술한 것과 거의 같다.

[0287] 도 8D는 벡터 전력 증폭기(700)의 다른 예시적인 실시예(800D)를 나타낸 블록도이다. 선택적 성분은 파선으로 나타내며, 다른 실시예에서는 이러한 선택적 성분은 가감될 수 있다. 도 8D의 실시예는 도 8B의 증폭기의 다중 입력 단일출력(MISO) 구현을 보여준다. 도 8D의 실시예에서 벡터 변조기(760, 762, 764, 766)로부터 출력된 일정 포락선 신호(761, 763, 765, 767)는 MISO PA(870, 872)에 입력된다. MISO PA(870, 872)는 2-입력 단일출력 전력 증폭기이다. 일 실시예에서 MISO PA(870, 872)는 도 7A의 실시예에 나타난 요소(770, 772, 774, 776, 794-797) 또는 그 기능적 등가물을 포함한다. 다른 실시예에서 MISO PA(870, 872)는 선택적인 전치 구동기와 선택적인 프로세스 검출 회로와 같은 다른 요소를 포함할 수 있다. 다른 실시예에서 MISO PA(870, 872)는 도 7A의 실시예에는 없는 전치 구동기와 같은 다른 요소를 포함할 수 있다. 더욱이 MISO PA(870, 872)는 도 8D에 도시된 2-입력 PA에 한정되지 않는다. 다른 실시예에서, 이후 도 51A 내지 51H를 참조로 자세히 설명되겠지만, PA(870, 872)는 임의 수의 입력과 출력을 가질 수 있다.

[0288] 벡터 전력 증폭기(800D)의 다른 양상은 벡터 전력 증폭기(700, 800B)에 대해 전술한 것과 거의 같다.

[0289] 3.2) 직교-극-직교-극 2-분기 벡터 전력 증폭기

[0290] 이제 직교-극-직교-극(CPCP) 2-분기 VPA 실시예에 대해 설명한다(이러한 실시예 명칭은 참조를 용이하게 하기 위해 제시된 것이며 이에 한정되는 것은 아니다).

[0291] 직교-극-직교-극(CPCP) 2-분기 VPA법에 따라서 시변 복소 포락선 신호는 2개의 실질적으로 일정한 포락선 성분 신호로 분해된다. 이 성분 신호들은 개별적으로 증폭된 다음에 합산되어 원래의 시변 복소 포락선 신호의 증폭 신호를 구성한다. 게다가 시변 복소 포락선 신호의 위상각은 확정되어 있으며, 성분 신호의 합산 결과는 적당한 각도만큼 위상 천이된다.

[0292] CPCP 2-분기 VPA법의 일 실시예에서 시변 복소 포락선 신호의 크기와 위상각은 신호의 동위상 및 직각위상 성분

으로부터 산출된다. 크기 정보가 주어지면 2개의 실질적으로 일정한 포락선 성분은 원하는 시변 포락선 신호의 정규화 베전으로부터 산출되는데, 이 정규화는 위상 및/또는 진폭의 구현 특정 조작을 포함한다. 그러면, 이 2개의 실질적으로 일정한 포락선 성분은 원하는 시변 포락선 신호의 위상 천이에 관련된 적당한 각도만큼 위상 천이된다. 그 다음 이 실질적으로 일정한 포락선 성분들은 개별적으로 거의 똑같이 증폭된 다음에 합산되어 원래의 원하는 시변 포락선 신호의 증폭 베전을 생성한다.

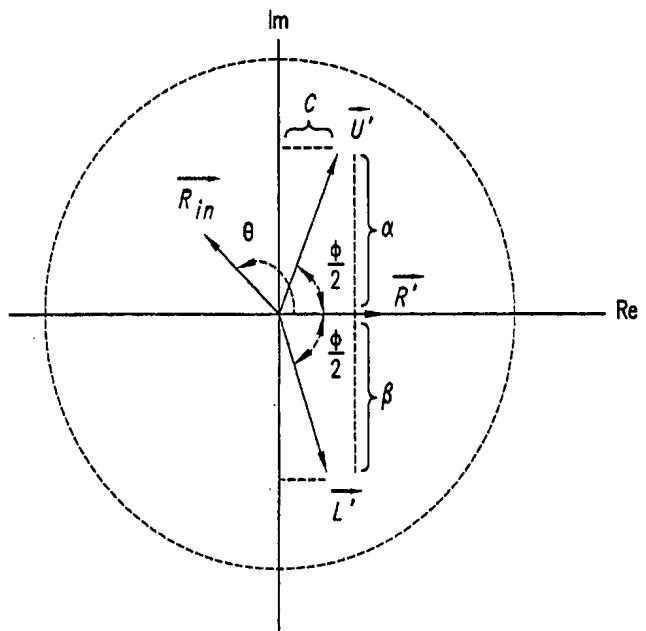

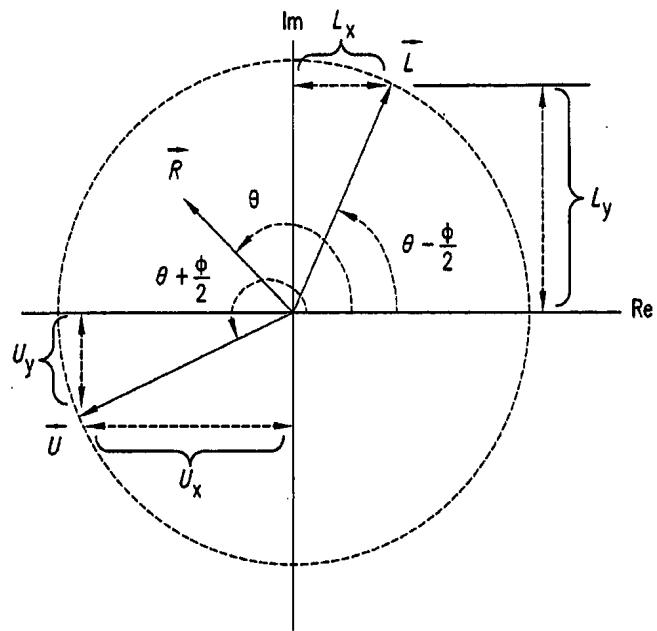

[0293] 도 9A 및 9B는 페이저 신호 표기를 이용한 CPCP 2-분기 VPA 실시예를 개념적으로 보여준다. 도 9A에서 페이저

$\overleftrightarrow{R}_{in}$ 은 시변 복소 포락선 입력 신호  $r(t)$ 를 나타낸다. 임의 순간에서  $\overleftrightarrow{R}_{in}$ 은 신호  $r(t)$ 의 크기와 위상 천이 각을 반영한다. 도 9A에 도시된 예에서  $\overleftrightarrow{R}_{in}$ 은 크기  $R$ 과 위상 천이각  $\phi$ 로 특징지워진다. 전술한 바와 같이 위상 천이각은 기준 신호에 대해 측정된다.

[0294] 도 9A를 참조로 설명하면,  $\overleftrightarrow{R}'$ 은  $\bar{U}'$ 와  $\bar{L}'$ 에 의해 발생된  $\overleftrightarrow{R}_{in}$ 의 상대적 진폭 성분을 나타낸다.

[0295] 계속해서 도 9A를 참조로 설명하면, 임의 순간에서  $\overleftrightarrow{R}'$ 은 상위 페이저  $\bar{U}'$ 와 하위 페이저  $\bar{L}'$ 의 합에 의해 구해질 수 있음에 유의한다. 더욱이  $\bar{U}'$ 와  $\bar{L}'$ 는 실질적으로 일정한 크기를 갖도록 유지될 수 있다. 따라서 페이저  $\bar{U}'$ 와  $\bar{L}'$ 는 2개의 실질적으로 일정한 포락선 신호를 나타낸다. 따라서 임의 순간에서  $r'(t)$ 는 페이저  $\bar{U}'$ 와  $\bar{L}'$ 에 해당하는 2개의 실질적으로 일정한 포락선 신호의 합에 의해 구해질 수 있다.

[0296]  $\overleftrightarrow{R}'$ 에 대한 페이저  $\bar{U}'$ 와  $\bar{L}'$ 의 위상 천이는  $\overleftrightarrow{R}'$ 의 원하는 크기  $R$ 에 따라서 설정된다. 가장 간단한 경우로서, 상위 및 하위 페이저  $\bar{U}'$ 와  $\bar{L}'$ 가 동일한 크기를 갖도록 선택되면, 상위 및 하위 페이저  $\bar{U}'$ 와  $\bar{L}'$ 는  $\overleftrightarrow{R}'$ 에 대해 위상이 실질적으로 대칭적으로 천이된다. 이것은 도 9A의 예에 나타나 있다. "상위와 하위"(이에 한정되지 않음)와 같이 방향을 나타내거나 암시하는 용어나 구절은 여기서는 참조를 용이하게 하기 위해 사용되는 것이며, 기능적으로 또는 구조적으로 제한하는 것은 아님에 유의한다.

[0297] 도 9A에 나타낸 경우에 있어서  $\overleftrightarrow{R}'$ 에 대한 페이저  $\bar{U}'$ 와  $\bar{L}'$ 의 위상 천이(도 9A에서 각도  $\frac{\phi}{2}$ 로 나타냄)는 다음과 같이  $\overleftrightarrow{R}'$ 의 크기에 관련됨을 검증할 수 있다.

$$\frac{\phi}{2} = \cot^{-1} \left( \frac{R}{2\sqrt{1 - \frac{R^2}{4}}} \right) \quad (7)$$

[0298] 여기서  $R$ 은 페이저  $\overleftrightarrow{R}'$ 의 정규화된 크기를 나타낸다.

[0300] 수학식 (7)은 다음과 같이 더 간단하게 될 수 있다.

$$\frac{\phi}{2} = \cos^{-1}\left(\frac{R}{2}\right) \quad (7.10)$$

[0301]

[0302] 여기서  $\vec{R}$ 은 페이저  $\vec{R}$ 의 정규화된 크기를 나타낸다.

[0303] 대안으로서, 임의의 실질적으로 등가적인 수학식이나 탐색표와 같은 다른 실질적으로 등가적인 수학적 기법이 이용될 수 있다.

[0304] 상기 설명으로부터 페이저 표기에서 가변 크기와 위상의 임의 페이저  $\vec{R}$ 는 2개의 일정 크기 페이저 성분의 합으로 구성될 수 있음을 알 수 있다.

$$\vec{R} = \vec{U} + \vec{L} \quad (8)$$

[0305]

[0306] 이에 대응하여, 시간 영역에서 시변 복소 포락선 정현파 신호  $r'(t) = R(t) \times \cos(\omega t)$ 은 다음과 같이 2개의 일정 포락선 신호의 합으로 구성된다.

$$\begin{aligned} r'(t) &= U'(t) + L'(t); \\ U'(t) &= A \times \cos(\omega t + \frac{\phi}{2}); \\ L'(t) &= A \times \cos(\omega t - \frac{\phi}{2}); \end{aligned} \quad (9)$$

[0307]

$$\frac{\phi}{2}$$

[0308] 여기서  $A$ 는 상수이며,  $\frac{\phi}{2}$ 는 수학식 (7)에 나타낸 바와 같다.

[0309]

도 9A로부터 수학식(9)은 다음과 같이 다시 쓸 수 있음을 검증할 수 있다.

$$\begin{aligned} r'(t) &= U'(t) + L'(t); \\ U'(t) &= C \cos(\omega t) + \alpha \sin(\omega t); \\ L'(t) &= C \cos(\omega t) - \beta \sin(\omega t); \end{aligned} \quad (10)$$

[0310]

[0311] 여기서  $C$ 는 페이저 페이저  $\vec{U}$ 와  $\vec{L}$ 의 실수부 성분을 나타내며  $A \times \cos(\frac{\phi}{2})$ 이다.  $C$ 는  $\vec{U}$ 와  $\vec{L}$ 의 공통 성분임에 유의한다.  $\alpha$ 와  $\beta$ 는 각각 페이저  $\vec{U}$ 와  $\vec{L}$ 의 헤수부 성분을 나타낸다.  $\alpha = \beta = A \times \sin(\frac{\phi}{2})$ .

따라서 수학식 (12)로부터  $r'(t) = 2C \times \cos(\omega t) = 2A \times \cos(\frac{\phi}{2}) \times \cos(\omega t)$ 이다. 당업자라면 본 발명의 교시에 따라 잘 이해하겠지만, 예컨대 탐색표를 포함하여 양(quantity)  $A$ ,  $B$  및  $C$ 의 상기 표현의 다른 등가적인 및/또는 간단화된 표현도 이용될 수 있다.

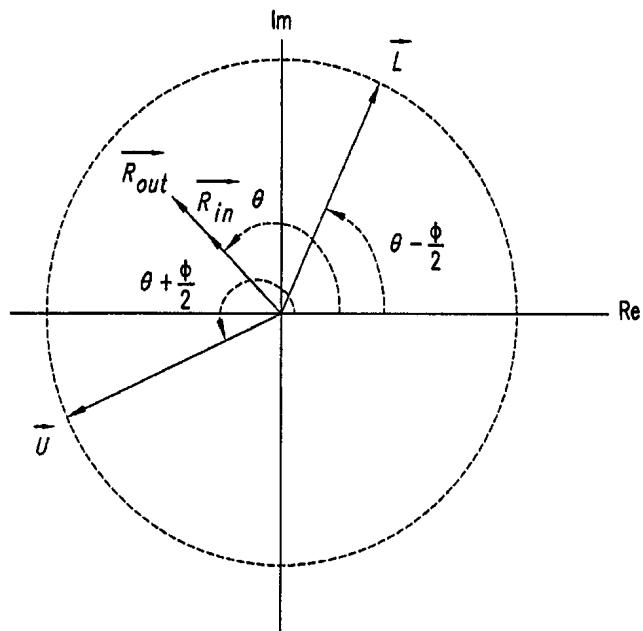

[0312]

$\vec{R}_{in}$ 은  $\vec{R}$ 에 대해  $\theta$ 도만큼 천이됨에 유의한다. 따라서 수학식 (8)을 이용하면 다음과 같이 추론될 수

있다.

$$\overrightarrow{R_{in}} = \overrightarrow{R} e^{j\theta} = (\overrightarrow{U} + \overrightarrow{L}) e^{j\theta} = \overrightarrow{U} e^{j\theta} + \overrightarrow{L} e^{j\theta} \quad (11)$$

[0313]

수학식 (11)은  $\overrightarrow{R_{in}}$ 의 표기가  $\theta$ 도만큼 천이된 전술한 페이저  $\overrightarrow{U}$  와  $\overrightarrow{L}$  를 합산함으로써 구해질 수 있음을 의미한다. 더욱이  $\overrightarrow{R_{in}}$ 의 증폭 출력 버전인  $\overrightarrow{R_{out}}$ 은 페이저  $\overrightarrow{U}$  와  $\overrightarrow{L}$ 의  $\theta$ 도 천이 버전 각각을 실질적으로 똑같이 별도로 증폭하고 이들을 합산함으로써 구해질 수 있다. 도 9B는 이 개념을 보여준다. 도 9B에서

페이저  $\overrightarrow{U}$  와  $\overrightarrow{L}$ 은 페이저  $\overrightarrow{U}$  와  $\overrightarrow{L}$ 의  $\theta$ 도 천이 및 증폭 버전을 나타낸다.  $\overrightarrow{U}$  와  $\overrightarrow{L}$ 는 일정 크기 페이저이므로  $\overrightarrow{U}$  와  $\overrightarrow{L}$ 도 일정 크기 페이저임에 유의한다. 페이저  $\overrightarrow{U}$  와  $\overrightarrow{L}$ 은 도 9B에 도시된 바와 같이 이 합산되어, 입력 신호  $\overrightarrow{R_{in}}$ 의 전력 증폭 버전인 페이저  $\overrightarrow{R_{out}}$ 이 된다.

[0315]

등가적으로 시간 영역에서 다음과 같이 될 수 있다.

$$\begin{aligned} r_{out}(t) &= U(t) + L(t); \\ U(t) &= K[C \cos(\omega t + \theta) + \alpha \sin(\omega t + \theta)]; \\ L(t) &= K[C \cos(\omega t + \theta) - \beta \sin(\omega t + \theta)]. \end{aligned} \quad (12)$$

[0316]

여기서  $r_{out}(t)$ 는 페

이자  $\overrightarrow{R_{out}}$ 으로 나타낸 시간 영역 신호에 해당하고,  $U(t)$ 와  $L(t)$ 는 페이저  $\overrightarrow{U}$  와  $\overrightarrow{L}$ 로 나타낸 시간 영역 신호에 해당하고,  $K$ 는 전력 증폭 계수이다.

[0317]

당업자라면 수학식 (9)와 (10)의 시간 영역 표현은 정현파형의 경우에 대해 제공되었지만 적당한 기본 함수를 이용하여 비정현파형에 대해서도 동등한 표현이 전개될 수 있음을 잘 알 것이다.

[0318]

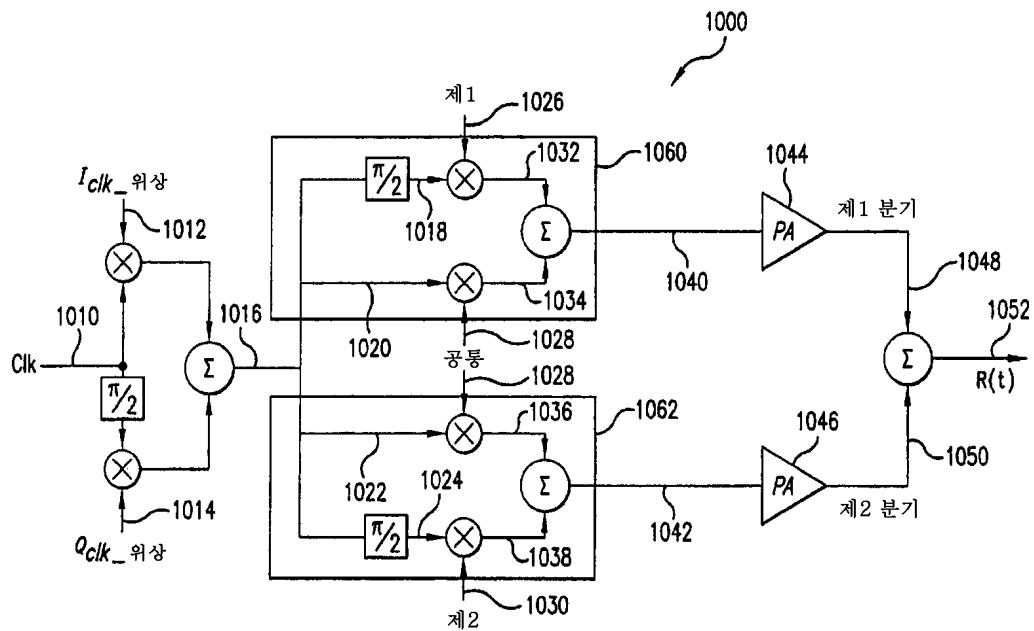

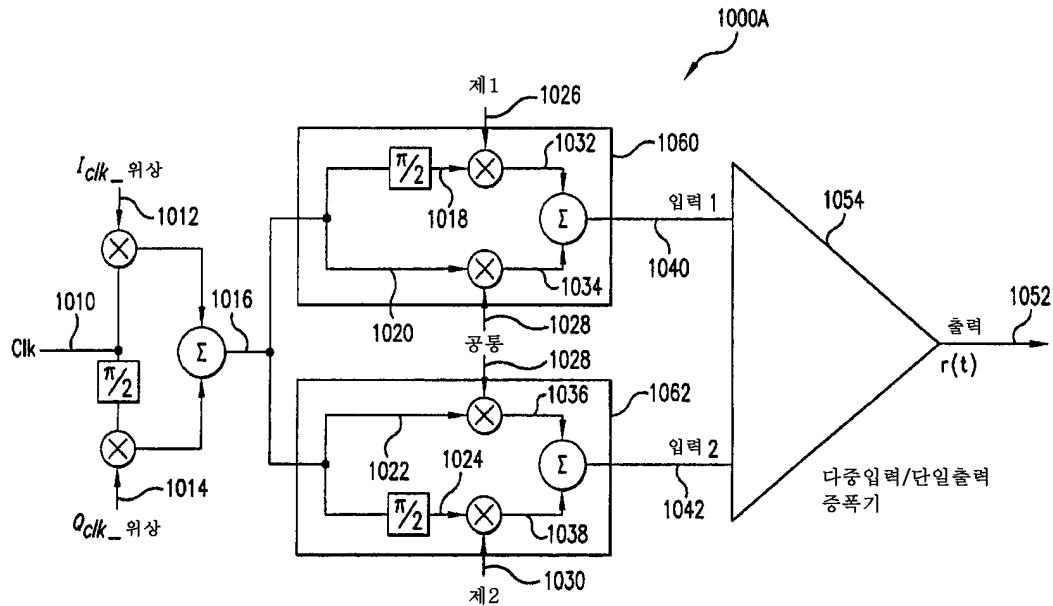

도 10은 CPCP 2-분기 VPA 실시예의 예시적인 실시예(1000)를 개념적으로 나타낸 블록도이다. 원하는 전력 레벨과 주파수 특성을 갖는 출력 신호  $r(t)$ 는 CPCP 2-분기 VPA 실시예에 따라 동위상 및 직각위상 성분으로부터 생성된다.

[0319]

도 10의 예에서 클록 신호(1010)는 출력 신호  $r(t)$ 를 생성하기 위한 기준 신호를 나타낸다. 클록 신호(1010)는 원하는 출력 신호  $r(t)$ 와 주파수가 동일하다.

[0320]

도 10을 참조로 설명하면, Iclk\_위상 신호(1012)와 Qclk\_위상 신호(1014)는 Clk 신호(1010)의 동위상 및 직각위상 성분이 곱해진 진폭 아날로그값을 나타내며 기저대역 I 및 Q 신호로부터 산출된다.

[0321]

계속해서 도 10을 참조로 설명하면, 클록 신호(1010)에 Iclk\_위상 신호(1012)가 곱해진다. 이와 동시에 클록 신호(1010)의  $90^\circ$  천이된 버전에 Qclk\_위상 신호(1014)가 곱해진다. 이 2개의 곱해진 신호는 결합되어 Rclk 신호(1016)를 생성한다. Rclk 신호(1016)는 클록 신호(1010)와 주파수가 같다. 더욱이 Rclk 신호(1016)는 Q(t)와 I(t)의 비에 따른 위상 천이각에 의해 특징지워진다. Rclk 신호(1016)의 크기는  $R^2 \text{clk} = I^2 \text{clk}_\text{위상} + Q^2 \text{clk}_\text{위상}$ 과 같다. 따라서 Rclk 신호(1016)는 원하는 출력 신호  $r(t)$ 의 위상 특성을 가진 실질적으로 일정한 포락선 신호를 나타낸다.

[0322]

계속해서 도 10을 참조로 설명하면, Rclk 신호(1016)는 2개의 벡터 변조기(1060, 1062)에 동시에 입력된다. 벡터 변조기(1060, 1062)는 각각 수학식 (12)에 기술된 원하는 출력 신호  $r(t)$ 의 실질적으로 일정한  $U(t)$  및  $L(t)$  포락선 성분을 생성한다. 벡터 변조기(1060)에서는 공통 신호(1028)가 곱해진 동위상 Rclk 신호(1020)가, 제1 신호(1026)가 곱해진 Rclk 신호의  $90^\circ$  천이된 버전(1018)과 결합된다. 이와 동시에, 벡터 변조기(1062)에서는

공통 신호(1028)가 곱해진 동위상 Rclk 신호(1022)가, 제2 신호(1030)가 곱해진 Rclk 신호의  $90^\circ$  천이된 버전(1024)과 결합된다. 공통 신호(1028), 제1 신호(1026) 및 제2 신호(1030)는 각각 수학식 (12)에 기술된 실수부 C, 헤수부  $\alpha$  및  $\beta$ 에 해당한다.

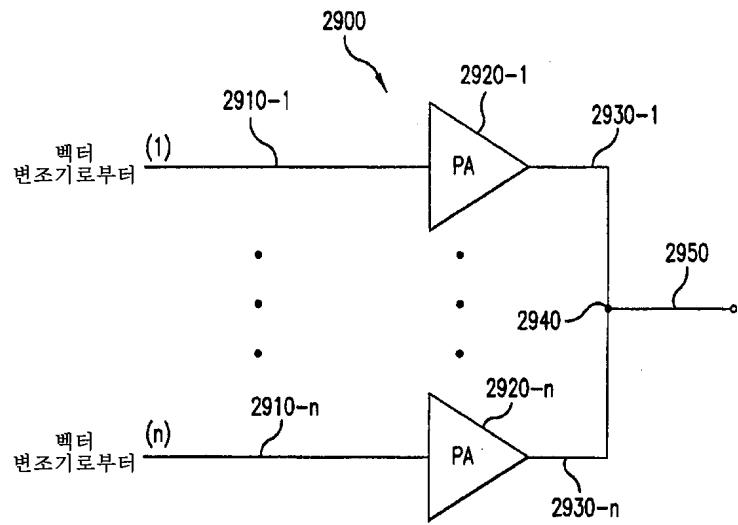

- [0323] 각자의 벡터 변조기(1060, 1062)의 출력 신호(1040, 1042)는 각각 입력 신호  $r(t)$ 의  $U(t)$  및  $L(t)$  일정 포락선 성분에 해당한다.

- [0324] 전술한 바와 같이 신호(1040, 1042)는 실질적으로 동일하고 일정한 크기 포락선을 갖는 것을 특징으로 한다. 따라서 신호(1040, 1042)가 해당 전력 증폭기(PA)(1044, 1046)에 입력되면, 해당 증폭 신호(1048, 1050)는 실질적으로 일정한 포락선 신호이다.

- [0325] 전력 증폭기(1044, 1046)는 실질적으로 동일한 전력 증폭을 각각 신호(1040, 1042)에 적용한다. 일 실시예에서 PA(1044, 1046)의 전력 중 레벨을 출력 신호  $r(t)$ 의 원하는 전력 레벨에 따라 설정된다. 더욱이 증폭 신호(1048, 1050)는 서로에 대해 동위상이다. 따라서 도 10에 도시된 바와 같이 증폭 신호들이 합산되면, 그 합산 결과 신호(1052)는 원하는 출력 신호  $r(t)$ 에 해당한다.

- [0326] 도 10A는 CPCP 2-분기 VPA 실시예의 다른 예시적인 실시예(1000A)를 보여준다. 실시예(1000A)는 도 10의 실시예(1000)의 다중입력 단일출력(MISO) 구현을 나타낸다.

- [0327] 실시예(1000A)에서 벡터 변조기(1060, 1062)로부터 출력된 일정 포락선 신호(1040, 1042)는 MISO PA(1054)에 입력된다. MISO PA(1054)는 2-입력 단일출력 전력 증폭기이다. 일 실시예에서 MISO PA(1054)는 예컨대 전치 구동기, 구동기, 전력 증폭기 및 프로세스 검출기(도 10A에는 미도시)와 같은 여러 가지 요소를 포함할 수 있다. 더욱이 MISO PA(1054)는 도 10A에 도시된 2-입력 PA에 한정되지 않는다. 다른 실시예에서, 이후 도 51A 내지 51H를 참조로 자세히 설명되겠지만, PA(1054)는 임의 수의 입력을 가질 수 있다.

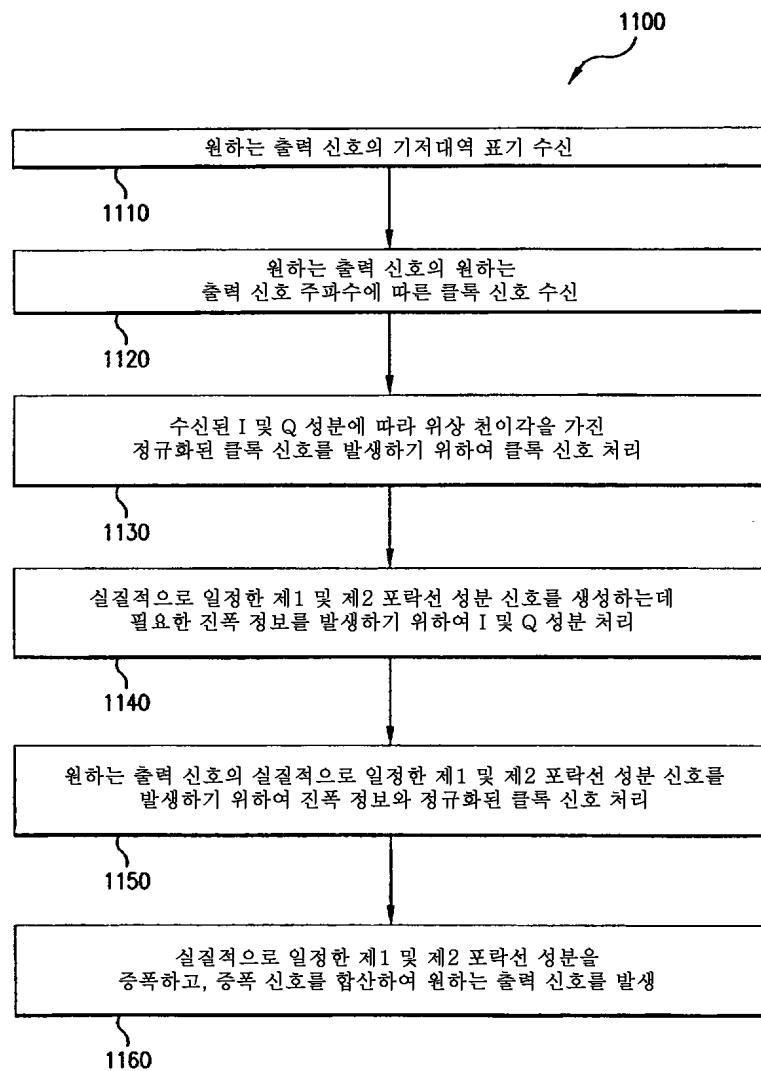

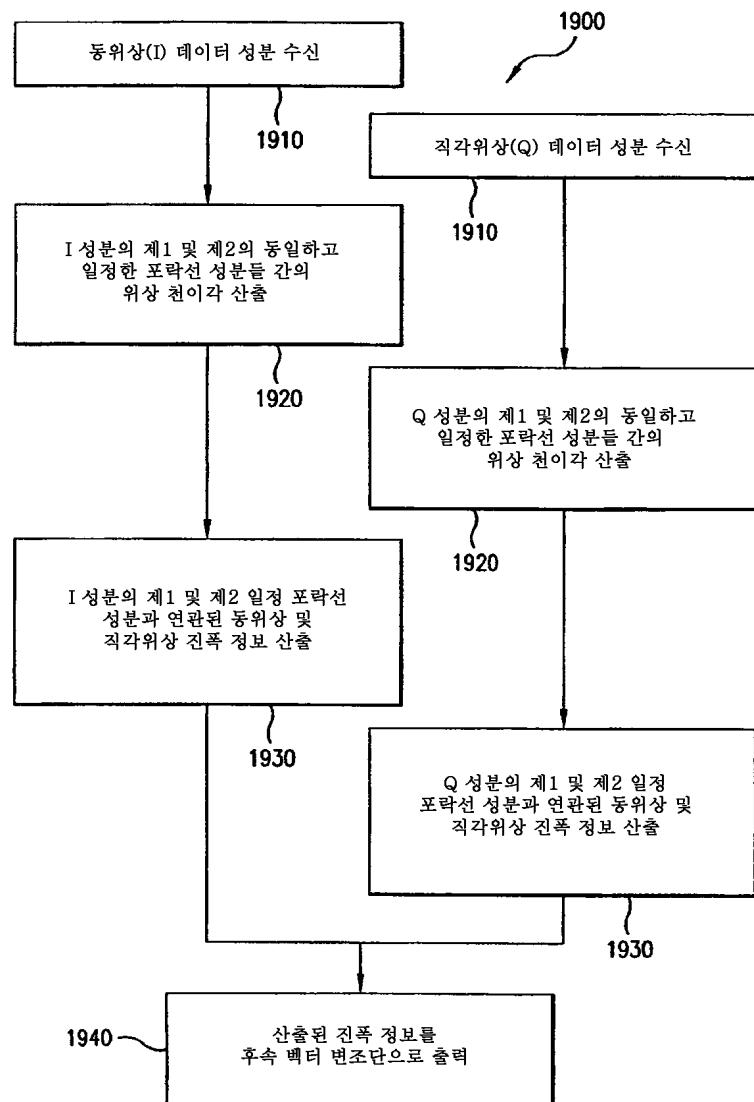

- [0328] CPCP 2-분기 VPA 실시예의 동작은 도 11의 프로세스 플로우차트(1100)에 나타나 있다.

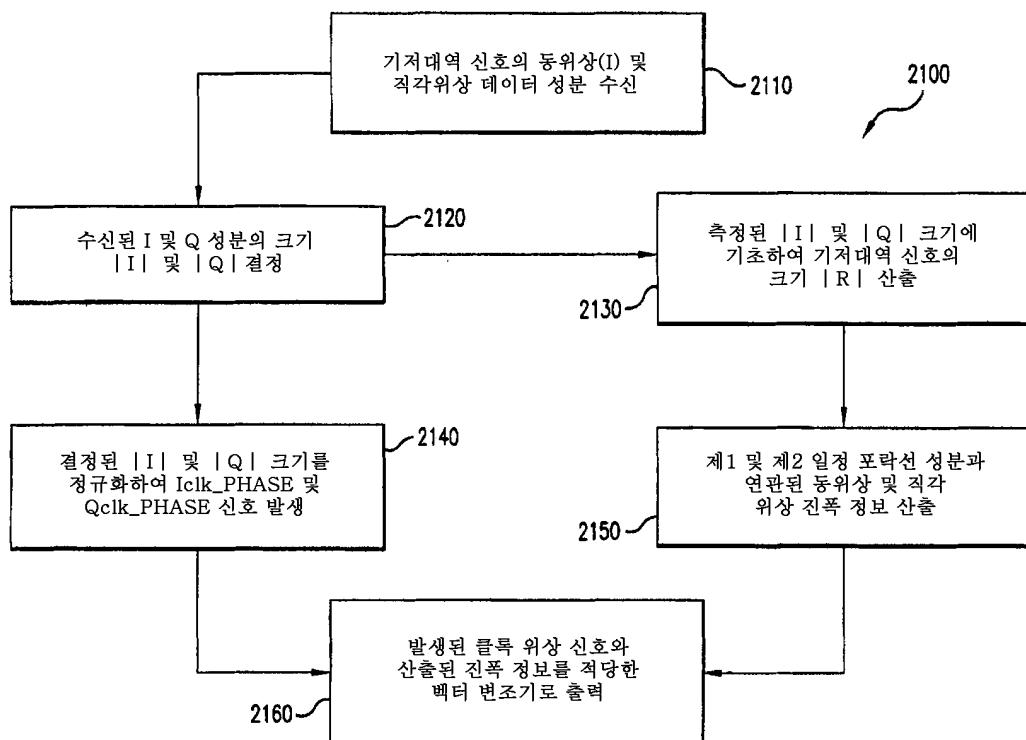

- [0329] 프로세스는 원하는 출력 신호의 기저대역 표기를 수신하는 것을 포함하는 단계(1110)에서 개시한다. 일 실시예에서 이것은 원하는 출력 신호의 동위상(I) 성분과 직각위상(Q) 성분을 수신하는 것을 포함한다. 다른 실시예에서 이것은 원하는 출력 신호의 크기와 위상을 수신하는 것을 포함한다.

- [0330] 단계(1120)는 원하는 출력 신호의 원하는 출력 신호 주파수에 따라 설정된 클록 신호를 수신하는 것을 포함한다. 도 10의 예에서 단계(1120)는 클록 신호(1010)를 수신함에 의해 달성된다.

- [0331] 단계(1130)는 수신된 I 및 Q 성분에 따라서 위상 천이각을 가진 정규화된 클록 신호를 생성하기 위하여 클록 신호를 처리하는 것을 포함한다. 일 실시예에서 정규화된 클록 신호는 I와 Q 성분의 비에 따라서 위상 천이각을 가진 일정 포락선 신호이다. 정규화된 클록의 위상 천이각은 원래의 클록 신호에 대한 것이다. 도 10의 예에서 단계(1130)는 클록 신호(1010)의 동위상 및 직각위상 성분을 Iclk\_위상(1012) 및 Qclk\_위상(1014) 신호에 곱한 다음에, 곱해진 신호를 합산하여 Rclk 신호(1016)를 생성함으로써 달성된다.

- [0332] 단계(1140)는 제1 및 제2의 실질적으로 일정한 포락선 성분 신호를 생성하는데 필요한 진폭 정보를 발생하기 위하여 I 및 Q 성분을 처리하는 것을 포함한다.

- [0333] 단계(1150)는 원하는 출력 신호의 제1 및 제2 일정 포락선 성분을 생성하기 위하여 단계(1140)의 진폭 정보와 정규화된 클록 신호 Rclk를 처리하는 것을 포함한다. 일 실시예에서 단계(1150)는 원하는 출력 신호의 제1 및 제2 일정 포락선 성분을 정규화된 클록 신호의 위상 천이각만큼 위상 천이하는 것을 포함한다. 도 10의 예에서 단계(1150)는 신호(1040, 1042)를 생성하기 위하여 제1 신호(1026), 제2 신호(1030) 및 공통 신호(1028)를 가지고 Rclk 신호(1016)를 변조하는 벡터 변조기(1060, 1062)에 의해 달성된다.

- [0334] 단계(1160)는 제1 및 제2 일정 포락선 성분을 개별적으로 증폭하고, 원하는 출력 신호를 생성하기 위하여 이 증폭된 신호를 합산하는 것을 포함한다. 일 실시예에서 제1 및 제2 일정 포락선 성분의 증폭은 거의 같으며, 원하는 출력 신호의 원하는 전력 레벨에 따른다. 도 10의 예에서 단계(1160)는 증폭된 신호(1048, 1050)를 생성하기 위하여 신호(1040, 1042)를 증폭하는 PA(1044, 1046)에 의해 달성된다.

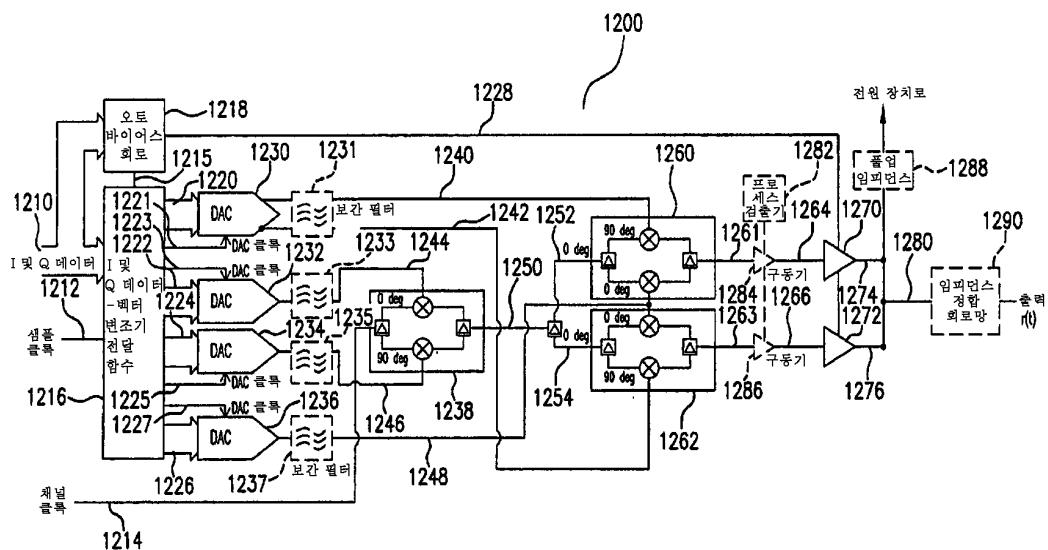

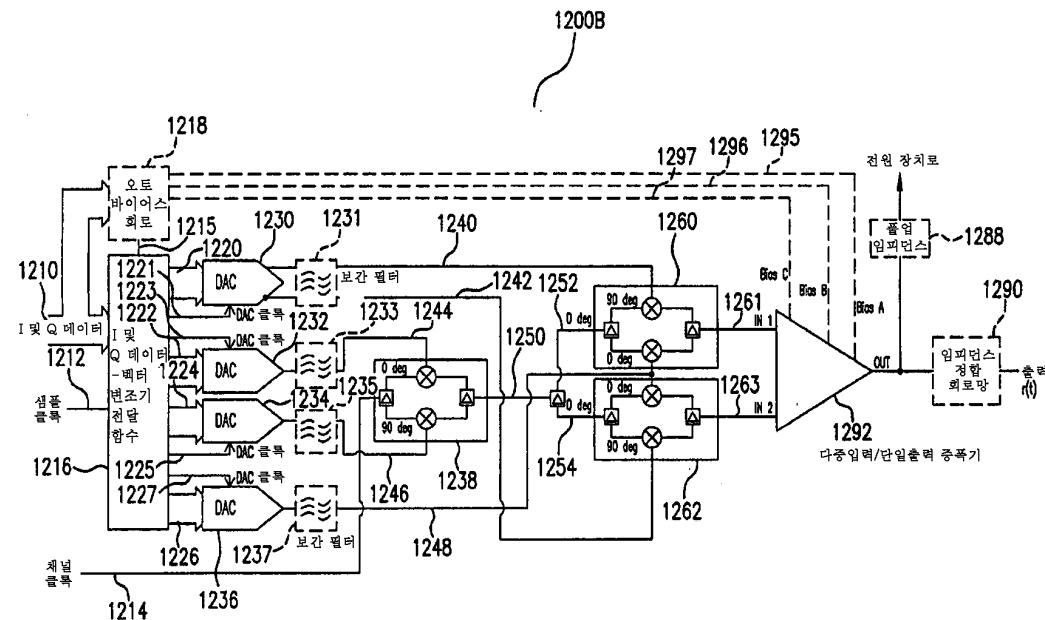

- [0335] 도 12는 프로세스 플로우차트(1100)를 구현하는 벡터 전력 증폭기(1200)의 예시적인 실시예를 나타낸 블록도이다. 선택적 성분은 파선으로 나타내며, 다른 실시예에서는 이러한 선택적 성분은 가감될 수 있다.

- [0336] 도 12를 참조로 설명하면, 동위상(I) 및 직각위상(Q) 정보 신호(1210)는 I 및 Q 데이터 전달 함수 모듈(1216)에 의해 수신된다. 일 실시예에서 I 및 Q 데이터 전달 함수 모듈(1216)은 샘플 클록(1212)에 따라 신호(1210)를

샘플링한다. I 및 Q 정보 신호(1210)는 원하는 출력 신호  $r(t)$ 의 기저대역 I 및 Q 정보를 포함한다.

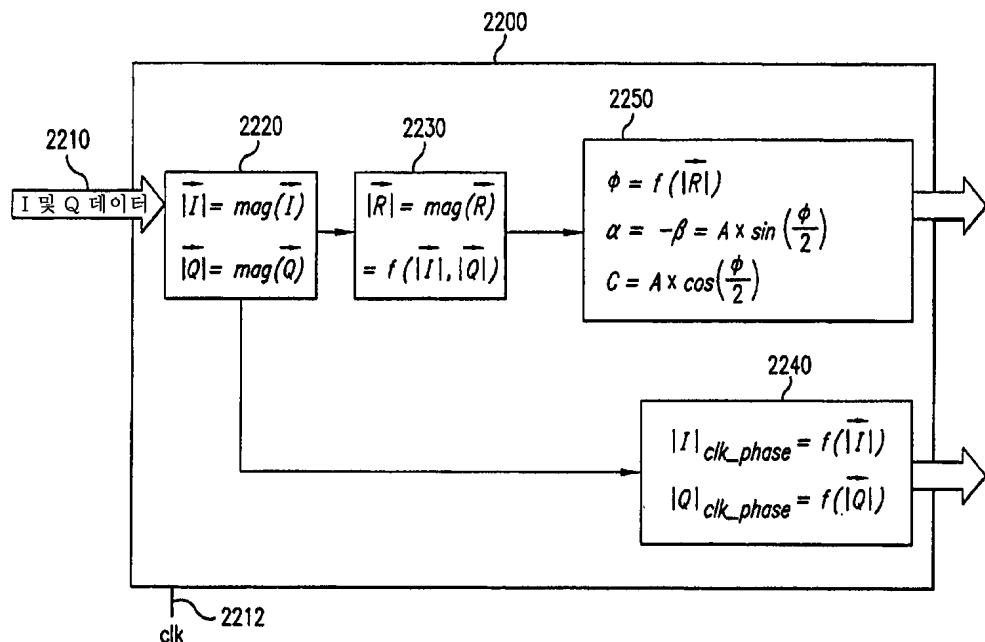

[0337] 일 실시예에서 I 및 Q 데이터 전달 함수 모듈(1216)은 정보 신호(1210)를 처리하여 정보 신호(1220, 1222, 1224, 1226)를 생성한다. I 및 Q 데이터 전달 함수 모듈(1216)의 동작에 대해서는 이후의 3.4 절에서 자세히 설명한다.

[0338] 도 12를 참조로 설명하면, 정보 신호(1220)는 원하는 출력 신호  $r(t)$ 의 기저대역 버전의 제1 및 제2 일정 포락선 성분의 직각위상 진폭 정보를 포함한다. 도 9A를 참조하면, 예컨대 정보 신호(1220)는  $\alpha$  및  $\beta$  직각위상 성분을 포함한다. 다시 도 12를 참조하여 설명하면, 정보 신호(1226)는 신호  $r(t)$ 의 기저대역 버전의 제1 및 제2 일정 포락선 성분의 동위상 진폭 정보를 포함한다. 도 9A를 참조하면, 예컨대 정보 신호(1226)는 공통 C 동위상 성분을 포함한다.

[0339] 계속해서 도 12를 참조로 설명하면, 정보 신호(1222, 1224)는 각각 정규화된 동위상  $I_{clk\_위상}$  및 직각위상  $Q_{clk\_위상}$  신호를 포함한다.  $I_{clk\_위상}$  및  $Q_{clk\_위상}$ 은 신호(1210)에 포함된 I 및 Q 정보 신호의 정규화된 버전이다. 일 실시예에서  $I_{clk\_위상}$  및  $Q_{clk\_위상}$ 은 ( $I^2_{clk\_위상}+Q^2_{clk\_위상}=일정$ )이 되도록 정규화된다. 신호(1250)의 위상은 원하는 출력 신호의 위상에 해당하며  $I_{clk\_위상}$  및  $Q_{clk\_위상}$ 으로부터 생성됨에 유의한다. 도 9B를 참조로 설명하면,  $I_{clk\_위상}$  및  $Q_{clk\_위상}$ 은 다음과 같이 I 및 Q에 관련된다.

$$\theta = \tan^{-1}\left(\frac{Q}{I}\right) = \tan^{-1}\left(\frac{Q_{clk\_phase}}{I_{clk\_phase}}\right) \quad (12.1)$$

[0340]

$$\overline{R_{out}}$$

[0341] 여기서  $\theta$ 는 도 9B에서 페이저로 나타낸 원하는 출력 신호의 위상을 나타낸다. 모든 4분면에 대해  $\theta$ 를 산출하기 위해서는 기저대역 I 및 Q 정보의 부호 정보를 고려해야 한다.

[0342] 도 12의 예시적인 실시예에서 정보 신호(1220, 1222, 1224, 1226)는 디지털 신호이다. 따라서 각 신호(1220, 1222, 1224, 1226)는 해당 디지털-아날로그 변환기(DAC)(1230, 1232, 1234, 1236)에 공급된다. DAC(1230, 1232, 1234, 1236)의 분해능과 샘플 레이트는 특정 시그널링 방식에 따라 선택된다. DAC(1230, 1232, 1234, 1236)는 각각 DAC 클록 신호(1221, 1223, 1225, 1227)에 의해 제어된다. DAC 클록 신호(1221, 1223, 1225, 1227)는 동일한 클록 신호로부터 도출되거나 독립적일 수 있다.

[0343] 다른 실시예에서 정보 신호(1220, 1222, 1224, 1226)는 아날로그 형식으로 생성되며, DAC는 필요치 않다.

[0344] 도 12를 참조로 설명하면, DAC(1230, 1232, 1234, 1236)는 디지털 정보 신호(1220, 1222, 1224, 1226)를 대응하는 아날로그 신호로 변환하고, 이를 아날로그 신호를 각각 선택적인 보간 필터(1231, 1233, 1235, 1237)에 입력한다. 안티앨리어싱 필터로도 기능하는 보간 필터(1231, 1233, 1235, 1237)는 DAC 출력 신호를 정형하여 원하는 출력 파형을 생성한다. 보간 필터(1231, 1233, 1235, 1237)는 각각 신호(1240, 1244, 1246, 1248)를 생성한다. 신호(1242)는 신호(1240)의 반전을 나타낸다.

[0345] 계속해서 도 12를 참조로 설명하면,  $I_{clk\_위상}$  및  $Q_{clk\_위상}$  정보를 포함하는 신호(1244, 1246)는 벡터 변조기(1238)에 입력된다. 벡터 변조기(1238)는 신호(1244)를 채널 클록 신호(1214)에 곱한다. 채널 클록 신호(1214)는 원하는 출력 신호 주파수에 따라 선택된다. 이와 동시에 벡터 변조기(1238)는 신호(1246)를 채널 클록 신호(1214)의  $90^\circ$  천이된 베전에 곱한다. 즉 벡터 변조기(1238)는  $I_{clk\_위상}$ 의 진폭을 가진 동위상 성분과  $Q_{clk\_위상}$ 의 진폭을 가진 직각위상 성분을 생성한다.

[0346] 벡터 변조기(1238)는 이 2개의 변조 신호를 결합하여  $R_{clk}$  신호(1250)를 생성한다.  $R_{clk}$  신호(1250)는 신호(1210)에 포함된 I 및 Q 데이터에 따라 원하는 출력 주파수와 위상 천이각을 가진 실질적으로 일정한 포락선 신호이다.

[0347] 계속해서 도 12를 참조로 설명하면, 신호(1240, 1242, 1248)는 각각 신호  $r(t)$ 의 복소 포락선의 U, L 및 공통 C 진폭 성분을 포함한다. 신호(1240, 1242, 1248)는  $R_{clk}$  신호(1250)와 함께 벡터 변조기(1260, 1262)에 입력된다.

[0348] 벡터 변조기(1260)는  $R_{clk}$  신호(1250)의  $90^\circ$  천이된 베전이 곱해진 신호(1240)와  $R_{clk}$  신호(1250)의  $0^\circ$  천이된 베전이 곱해진 신호(1248)를 결합하여 출력 신호(1264)를 생성한다. 이와 동시에 벡터 변조기(1262)는  $R_{clk}$  신호(1250)의  $90^\circ$  천이된 베전이 곱해진 신호(1242)와  $R_{clk}$  신호(1250)의  $0^\circ$  천이된 베전이 곱해진 신호

(1248)를 결합하여 출력 신호(1266)를 생성한다.

[0349] 출력 신호(1264, 1266)는 실질적으로 일정한 포락선 신호를 나타낸다. 더욱이 Rclk 신호(1250)에 대한 출력 신호(1264, 1266)의 위상 천이는 각각 비  $\alpha/C$  및  $\beta/C$ 와 연관된 각도 관계에 따라 결정된다. 일 실시예에서  $\alpha = \beta$ 이며, 따라서 출력 신호(1264, 1266)는 Rclk 신호(1250)에 대해 대칭적으로 위상 천이된다. 도 9B를 참조하

면, 예컨대 출력 신호(1264, 1266)는 각각 와 일정 크기 페이저에 해당한다.

[0350] 출력 신호(1264, 1266)는 합산되어 기저대역 신호  $r(t)$ 의 I 및 Q 특성을 가진 채널 클록 변조 신호가 된다. 그러나 벡터 전력 증폭기(1200)의 출력에서 원하는 전력 레벨을 얻기 위해서 신호(1264, 1266)는 증폭되어 증폭 출력 신호를 생성한다. 도 12의 실시예에서 신호(1264, 1266)는 각각 전력 증폭기(PA)(1270, 1272)에 입력되어 증폭된다. 일 실시예에서 PA(1270, 1272)는 스위칭 전력 증폭기를 포함한다. 오토바이어스 회로(1218)는 후에 3.5.2 절에서 자세히 설명하는 바와 같이 PA(1270, 1272)의 바이어스를 제어한다. 도 12의 실시예에서, 예컨대 오토바이어스 회로(1218)는 바이어스 전압(1228)을 PA(1270, 1272)에 공급한다.

[0351] 일 실시예에서 PA(1270, 1272)는 실질적으로 동일한 전력 증폭을 각자의 일정 포락선 신호(1264-1266)에 적용한다. 일 실시예에서 전력 증폭은 원하는 출력 전력 레벨에 따라 설정된다. 벡터 전력 증폭기(1200)의 다른 실시예에서, PA 구동기 및/또는 전자 구동기를 추가적으로 채용하여 증폭기에 추가적인 전력 증폭 능력을 제공한다. 도 12의 실시예에서, 예컨대 PA 구동기(1284, 1286)는 각각 벡터 변조기(1260, 1262)와 그 다음의 PA(1270, 1272) 사이에 선택적으로 추가된다.

[0352] PA(1270, 1272)의 각자의 출력 신호(1274, 1276)는 실질적으로 일정한 포락선 신호이다. 더욱이 출력 신호(1274, 1276)가 합산되면, 그 합산 결과 신호는 최소의 비선형 왜곡을 갖는다. 도 12의 실시예에서 출력 신호(1274, 1276)는 함께 결합되어 벡터 전력 증폭기(1200)의 출력 신호(1280)를 생성한다. 일 실시예에서 PA(1270, 1272)의 출력을 결합하는데 절연이 이용되지 않는다. 따라서 결합에 의한 전력 손실은 최소가 된다. 일 실시예에서 PA(1270, 1272)의 출력은 와이어를 이용하여 함께 직접 결합된다. 이런 식으로의 직접 결합은 PA(1270, 1272)의 출력들 간에 저항성, 유도성 또는 용량성 절연이 최소이거나 없다는 것을 의미한다. 즉 PA(1270, 1272)의 출력은 중간에 개입하는 성분없이 함께 결합된다. 대안으로서 일 실시예에서 PA(1270, 1272)의 출력은 임피던스 연결을 작게하거나 최소화하는 인더티스 및/또는 커패시턴스를 통해, 그리고/또는 절연과 전력 손실을 최소화하는 소정 연결부를 통해 간접적으로 함께 결합된다. 대안으로서, PA(1270, 1272)의 출력은 월킨슨, 하이브리드 결합기, 변압기 또는 공지의 능동 결합기와 같은 공지의 결합 기술을 이용하여 결합된다. 일 실시예에서 PA(1270, 1272)는 한 번의 동작으로 통합된 증폭과 전력 결합을 제공한다. 일 실시예에서 여기서 설명된 전력 증폭기 및/또는 구동기를 중 하나 또는 그 이상은 다중입력 단일출력 전력 증폭 기술을 이용하여 구현되며, 그 예는 도 12A, 12B 및 도 51A 내지 51H에 나타나 있다.

[0353] 출력 신호(1280)는 기저대역 신호  $r(t)$ 의 I 및 Q 특성과 원하는 출력 전력 레벨 및 주파수를 가진 신호를 나타낸다. 벡터 전력 증폭기(1200)의 실시예에서 풀업(pull-up) 임피던스(1288)는 벡터 전력 증폭기(1200)의 출력과 전원 장치 사이에 연결된다. 다른 실시예에서 임피던스 정합 회로망(1290)은 벡터 전력 증폭기(1200)의 출력에 연결된다. 본 발명의 전력 증폭 방법 및 시스템에 따른 출력단 실시예에 대해서는 이후의 3.5 절에서 자세히 설명한다.

[0354] 벡터 전력 증폭기(1200)의 다른 실시예에서는 프로세스 검출기를 채용하여 증폭기의 회로에서의 프로세스 변동을 보상한다. 도 12의 예시적인 실시예에서, 예컨대 프로세스 검출기(1282)는 선택적으로 추가되어 PA 구동기(1284, 1286)에서의 변동을 모니터한다.

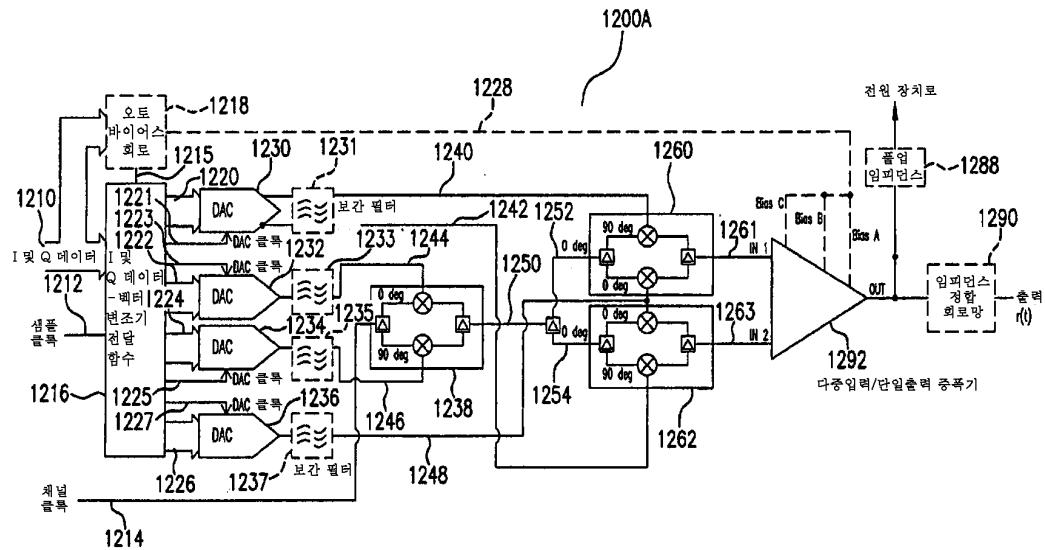

[0355] 도 12A는 프로세스 플로우차트(1100)를 구현하는 벡터 전력 증폭기(1200A)의 다른 예시적인 실시예를 나타낸 블록도이다. 선택적 성분은 파선으로 나타내며, 다른 실시예에서는 이러한 선택적 성분은 가감될 수 있다.

[0356] 실시예(1200A)는 실시예(1200)의 다중입력 단일출력(MISO) 구현을 나타낸다. 실시예(1200A)에서 벡터 변조기(1260, 1262)로부터 출력된 일정 포락선 신호(1261, 1263)는 MISO PA(1292)에 입력된다. MISO PA(1292)는 2-입력 단일출력 전력 증폭기이다. 일 실시예에서 MISO PA(1292)는 도 12의 실시예에 나타낸 요소(1270, 1272, 1282, 1284, 1286)를 포함한다. 다른 실시예에서 MISO PA(1292)는 도 12의 실시예에는 나타나 있지 않은 전자 구동기와 같은 다른 요소를 포함할 수 있다. 더욱이 MISO PA(1292)는 도 12A에 도시된 2-입력 PA에 한정되지 않는다. 다른 실시예에서, 이후 도 51A 내지 51H를 참조로 자세히 설명되겠지만, PA(1292)는 임의 수의 입력과

출력을 가질 수 있다.

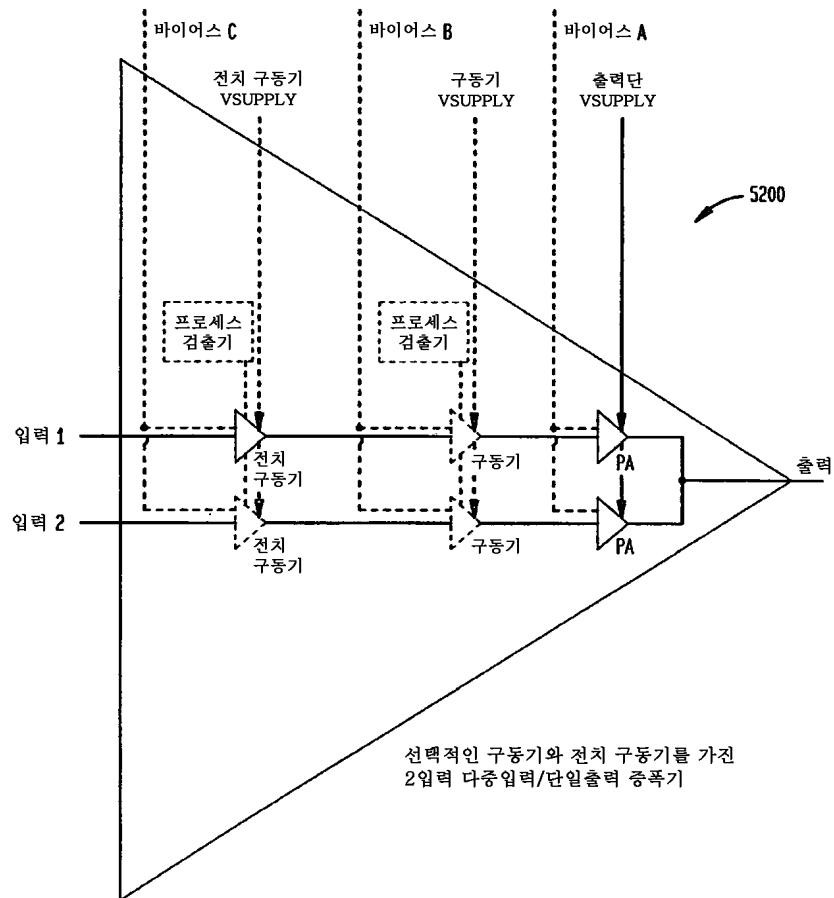

[0357] 계속해서 도 12A를 참조로 설명하면, 실시예(1200A)는 오토바이어스 신호를 MISO PA(1292)에 전달하는 일 구현을 보여준다. 도 12A의 실시예에서 오토바이어스 회로(1218)에 의해 생성된 오토바이어스 신호(1228)는 이 신호로부터 도출되어 MISO PA(1292)의 여러 가지 단을 바이어스시키는 하나 또는 그 이상의 신호를 갖고 있다. 도 12A의 예에서 보는 바와 같이, 3개의 바이어스 제어 신호(바이어스 A, 바이어스 B, 바이어스 C)가 오토바이어스 신호(1228)로부터 도출되어 MISO PA(1292)의 여러 가지 단에 입력된다. 예컨대 바이어스 C는 MISO PA(1292)의 전치 구동기단에 입력되는 바이어스 신호일 수 있다. 마찬가지로 바이어스 B와 바이어스 A는 MISO PA(1292)의 구동기와 PA단에 입력되는 바이어스 신호일 수 있다.

[0358] 도 12B의 실시예(1200B)에 보여진 다른 구현에서 오토바이어스 회로(1218)는 각각 바이어스 A, 바이어스 B 및 바이어스 C에 대응하는 독립적인 오토바이어스 신호(1295, 1296, 1297)를 생성한다. 신호(1295, 1296, 1297)는 오토바이어스 회로(1218) 내에서 독립적으로 생성될 수도 되지 않을 수도 있으나, 도시된 바와 같이 독립적으로 출력된다. 더욱이 신호(1295, 1296, 1297)는 MISO PA(1294)의 여러 가지 단의 바이어싱에 의해 결정되는 것으로 관련될 수도 되지 않을 수도 있다.

[0359] 벡터 전력 증폭기(1200A, 1200B)의 다른 양상은 벡터 전력 증폭기(1200)에 대해 전술한 것과 거의 같다.

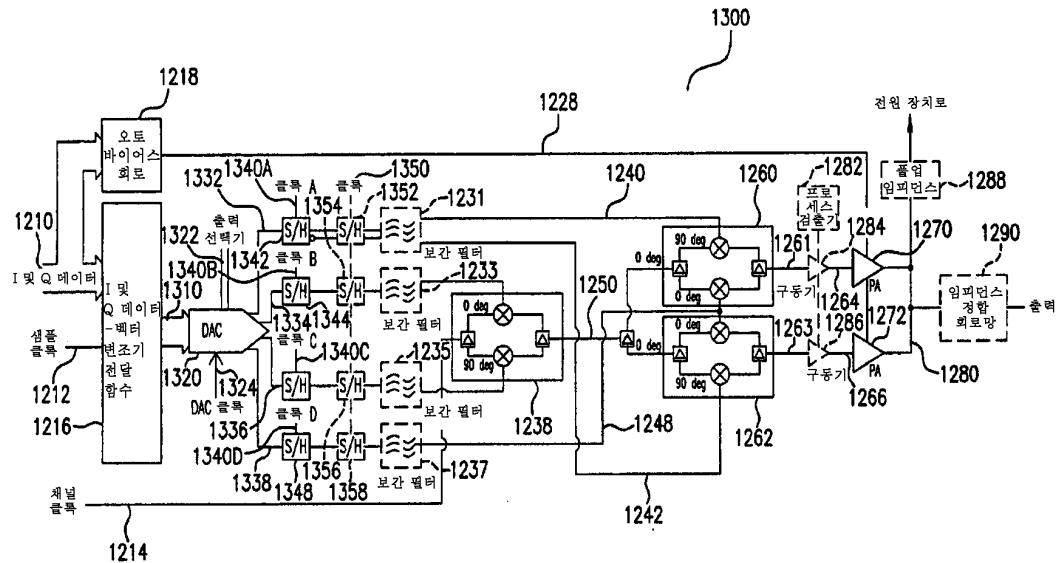

[0360] 도 13은 CPCP 2-분기 VPA 실시예에 따른 벡터 전력 증폭기의 다른 예시적인 실시예(1300)를 나타낸 블록도이다. 선택적 성분은 파선으로 나타내며, 다른 실시예에서는 이러한 선택적 성분은 가감될 수 있다.

[0361] 도 13의 예시적인 실시예에서는 충분한 분해능과 샘플 레이트를 가진 DAC(1320)가 도 12의 실시예의 DAC(1230, 1232, 1234, 1236)를 대체한다. DAC(1320)는 DAC 클록(1324)에 의해 제어된다.

[0362] DAC(1320)는 I 및 Q 데이터 전달 함수 모듈(1216)로부터 정보 신호(1310)를 수신한다. 정보 신호(1310)는 도 12의 실시예에서의 신호(1220, 1222, 1224, 1226)와 동일한 정보 내용을 포함한다.

[0363] DAC(1320)는 한 번에 하나의 아날로그 신호를 출력할 수 있다. 따라서 도 13에 도시된 바와 같이 샘플 홀드 구조가 이용될 수 있다.

[0364] DAC(1320)는 제1 세트의 샘플 홀드 회로(1342, 1344, 1346, 1348)에 아날로그 신호(1332, 1334, 1336, 1338)를 순차적으로 출력한다. 일 실시예에서 DAC(1320)는 도 12의 실시예의 DAC(1230, 1232, 1234, 1236)를 대체하기에 충분한 레이트로 클록된다. 출력 선택기(1322)는 출력 신호(1332, 1334, 1336, 1338) 중 어느 것이 출력되도록 선택되어야 하는지를 판단한다.

[0365] DAC(1320)의 DAC 클록 신호(1324), 출력 선택기 신호(1322) 및 샘플 홀드 클록(1340A-D, 1350)은 독립적이거나 또는 전달 함수 모듈(1216)에 통합될 수 있는 제어 모듈에 의해 제어된다.

[0366] 일 실시예에서 샘플 홀드 회로(S/H)(1342, 1344, 1346, 1348)는 수신된 아날로그값을 홀드하고, 클록 신호(1340A-D)에 따라서 그 값을 제2 세트의 샘플 홀드 회로(1352, 1354, 1356, 1358)로 방출한다. 예컨대 S/H(1342)는 수신된 클록 신호(1340A)에 따라서 그 값을 S/H(1352)로 방출한다. 차례로 샘플 홀드 회로(1352, 1354, 1356, 1358)는 수신된 아날로그값을 홀드하고, 공통 클록 신호(1350)에 따라서 그 값을 보간 필터(1231, 1233, 1235, 1237)로 동시에 방출한다. 공통 클록 신호(1350)는 S/H(1352, 1354, 1356, 1358)의 출력이 시간 정렬되도록 하는데 이용된다.

[0367] 다른 실시예에서는 S/H(1342, 1344, 1346, 1348)를 포함하는 단일층의 S/H 회로가 채용될 수 있다. 따라서 S/H 회로(1342, 1344, 1346, 1348)는 DAC(1320)로부터 아날로그값을 수신하며, 각 회로는 그 수신된 값을 다른 클록들과 독립된 소정의 클록에 따라서 방출한다. 예컨대 S/H(1342)는 S/H(1344)를 제어하는 클록(1340B)와 동기화되지 않을 수 있는 클록(1340A)에 의해 제어된다. S/H 회로(1342, 1344, 1346, 1348)의 출력이 시간 정렬되도록 보장하기 위하여 클록들(1340A-D) 간의 지연은 증폭기의 전단(period stages)에서 미리 보상된다. 예컨대 DAC(1320)는 클록들(1340A-D) 간의 시간차를 보상하기 위하여 적당히 선택된 지연을 가진 신호(1332, 1334, 1336, 1338)를 S/H 회로(1342, 1344, 1346, 1348)에 출력한다.

[0368] 벡터 전력 증폭기(1300)의 다른 양상은 벡터 전력 증폭기(1200)에 대해 전술한 것과 거의 같다.

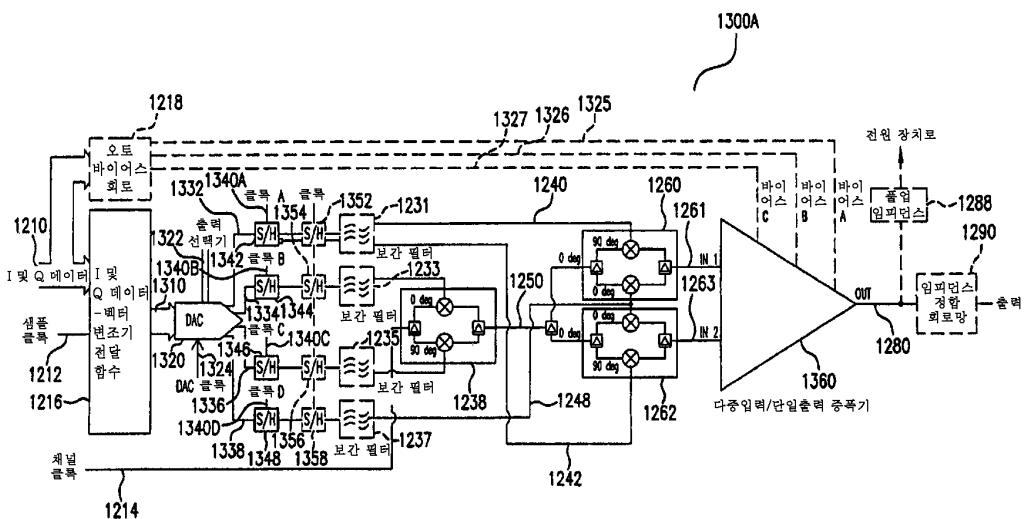

[0369] 도 13A는 CPCP 2-분기 VPA 실시예에 따른 벡터 전력 증폭기의 다른 예시적인 실시예(1300A)를 나타낸 블록도이다. 선택적 성분은 파선으로 나타내며, 다른 실시예에서는 이러한 선택적 성분은 가감될 수 있다. 실시예(1300A)는 도 13의 실시예(1300)의 MISO 구현이다.

[0370] 도 13A의 실시예에서 벡터 변조기(1260, 1262)로부터 출력된 일정 포락선 신호(1261, 1263)는 MISO PA(1360)에 입력된다. MISO PA(1360)는 2-입력 단일출력 전력 증폭기이다. 일 실시예에서 MISO PA(1360)는 도 13의 실시예에 나타낸 요소(1270, 1272, 1282, 1284, 1286)를 포함한다. 다른 실시예에서 MISO PA(1360)는 도 13의 실시예에는 나타나 있지 않은 전치 구동기와 같은 다른 요소 또는 그 기능적 등가물을 포함할 수 있다. 더욱이 MISO PA(1360)는 도 13A에 도시된 2-입력 PA에 한정되지 않는다. 다른 실시예에서, 이후 도 51A 내지 51H를 참조로 자세히 설명되겠지만, PA(1360)는 임의 수의 입력을 가질 수 있다.

[0371] 도 13A의 실시예는 도시된 바와 같이 단일 또는 2 레벨의 S/H 회로를 가진 2개의 서로 다른 샘플 훌드 구조를 더 보여준다. 이 2개의 구현은 도 13을 참조로 전술하였다.

[0372] 실시예(1300A)는 선택적인 바이어스 제어 회로(1218)와 이와 관련된 바이어스 제어 신호(1325, 1326, 1327)도 보여준다. 특정 실시예에서 신호(1325, 1326, 1327)는 MISO PA(1360)의 여러 가지 단을 바이어스하는데 이용될 수 있다.

[0373] 벡터 전력 증폭기(1300A)의 다른 양상은 벡터 전력 증폭기(1200, 1300)에 대해 전술한 것과 같다.

### 3.3) 직접 직교 2-분기 벡터 전력 증폭기

[0375] 이제 직접 직교 2-분기 VPA 실시예에 대해서 설명한다. 이 명칭은 참조를 용이하게 하기 위해 제시된 것이며 이에 기능적으로 또는 구조적으로 한정되는 것은 아니다.

[0376] 직접 직교 2-분기 VPA 실시예에 따라서 시변 포락선 신호는 2개의 일정 포락선 성분 신호로 분해된다. 이 성분 신호들은 개별적으로 동일하게 또는 실질적으로 동일하게 증폭된 다음에 합산되어 원래의 시변 포락선 신호의 증폭 신호를 구성한다.

[0377] 직접 직교 2-분기 VPA 실시예의 일 실시예에서 시변 포락선 신호의 크기와 위상각은 입력 신호의 동위상 및 직각위상 성분으로부터 산출된다. 크기와 위상 정보를 이용하여 시변 포락선 신호의 2개의 일정 포락선 성분에 대해 동위상 및 직각위상 진폭 성분이 산출된다. 그러면, 이 2개의 일정 포락선 성분이 생성되고, 동일하게 또는 거의 동일하게 증폭된 다음에 합산되어 원래의 시변 포락선 신호( $R_{in}$ )의 증폭 버전을 생성한다.

[0378] 이제 직접 직교 2-분기 VPA의 개념에 대해 도 9A 및 도 14를 참조로 설명한다.

[0379] 도 9A를 참조로 전술하고 검증된 바와 같이, 페이저  $\vec{R}'$  은  $\vec{R}'$  를 생성하기 위해 적당히 위상 천이된 상위 페이저  $\vec{U}'$  와 하위 페이저  $\vec{L}'$  의 합에 의해 구해질 수 있다.  $\vec{R}'$  는 크기  $R_{in}$ 에 비례하는 것으로 산출된다. 더욱이  $\vec{U}'$  와  $\vec{L}'$  는 실질적으로 일정한 크기를 갖도록 유지될 수 있다. 시간 영역에서  $\vec{U}'$  와  $\vec{L}'$  는 2개의 실질적으로 일정한 포락선 신호를 나타낸다.

[0380] 따라서 임의의 순간에  $\vec{R}'$  의 시간 영역 등가  $r'(t)$ 는 2개의 실질적으로 일정한 포락선 신호의 합으로 구해질 수 있다.

[0381] 도 9A에 나타낸 경우에 있어서  $\vec{R}'$  에 대한  $\vec{U}'$  와  $\vec{L}'$  의 위상 천이(도 9A에서 각도  $\frac{\phi}{2}$ 로 나타냄)는 다음과 같이  $\vec{R}'$  의 크기에 관련된다.

$$\frac{\phi}{2} = \cot^{-1} \left( -\frac{R}{2\sqrt{1 - \frac{R^2}{4}}} \right) \quad (13)$$

[0382]

[0383] 여기서  $R$ 은 폐이저  $\overrightarrow{R}$ 의 정규화된 크기를 나타낸다.

[0384] 시간 영역에서 예컨대 시변 포락선 신호  $r'(t)=R(t)\cos(\omega t)$ 는 다음과 같이 2개의 일정 포락선 신호의 합으로 구성될 수 있다.

$$\begin{aligned} r'(t) &= U'(t) + L'(t); \\ U'(t) &= C \times \cos(\omega t) + \alpha \times \sin(\omega t); \\ L'(t) &= C \times \cos(\omega t) - \beta \times \sin(\omega t). \end{aligned} \quad (14)$$

[0385]

[0386] 여기서  $C$ 는 폐이저 폐이저  $\overrightarrow{U}$  와  $\overrightarrow{L}$ 의 동위상 진폭 성분을 나타내며  $A \times \cos(\frac{\phi}{2})$  ( $A$ 는 상수)와 같거나 실질

적으로 같다.  $\alpha$ 와  $\beta$ 는 각각 폐이저  $\overrightarrow{U}$  와  $\overrightarrow{L}$ 의 직각위상 진폭 성분을 나타낸다.  $\alpha = \beta = A \times \sin(\frac{\phi}{2})$ . 수학식 (14)는 기본 함수를 정현파 함수로부터 원하는 함수로 변경함으로써 비정현파 신호를 위해 변경될 수 있음에 유의한다.

[0387] 도 14는  $\overrightarrow{R}$ 과 그 2개의 일정 크기 성분 폐이저  $\overrightarrow{U}$  와  $\overrightarrow{L}$ 를 보여준다.  $\overrightarrow{R}$ 은 도 9A에서의  $\overrightarrow{R}$ 에 대해  $\theta$ 도 만큼 천이된다. 따라서 다음과 같이 검증될 수 있다.

$$\begin{aligned} \overrightarrow{R} &= \overrightarrow{R} \times e^{j\theta} = (\overrightarrow{U} + \overrightarrow{L}) \times e^{j\theta} = \overrightarrow{U} + \overrightarrow{L}; \\ \overrightarrow{U} &= \overrightarrow{U} \times e^{j\theta}; \\ \overrightarrow{L} &= \overrightarrow{L} \times e^{j\theta}. \end{aligned} \quad (15)$$

[0388]

[0389] 수학식 (15)로부터 다음과 같이 더 나타낼 수 있다.

$$\begin{aligned} \overrightarrow{U} &= \overrightarrow{U} \times e^{j\theta} = (C + j\alpha) \times e^{j\theta}; \\ \Rightarrow \overrightarrow{U} &= (C + j\alpha)(\cos\theta + j\sin\theta) = (C \cos\theta - \alpha \sin\theta) + j(C \sin\theta + \alpha \cos\theta). \end{aligned} \quad (16)$$

[0390]

[0391] 마찬가지로 다음과 같이 나타날 수 있다.

$$\begin{aligned} \overrightarrow{L} &= \overrightarrow{L} \times e^{j\theta} = (C + j\beta) \times e^{j\theta}; \\ \Rightarrow \overrightarrow{L} &= (C + j\beta)(\cos\theta + j\sin\theta) = (C \cos\theta - \beta \sin\theta) + j(C \sin\theta + \beta \cos\theta). \end{aligned} \quad (17)$$

[0392]

[0393] 수학식 (16)과 (17)은 다음과 같이 다시 쓸 수 있다.

$$\begin{aligned}\vec{U} &= (C \cos \theta - \alpha \sin \theta) + j(C \sin \theta + \alpha \cos \theta) = U_x + jU_y; \\ \vec{L} &= (C \cos \theta - \beta \sin \theta) + j(C \sin \theta + \beta \cos \theta) = L_x + jL_y.\end{aligned}\quad (18)$$

[0394] 등가적으로 시간 영역에서,

$$\begin{aligned}U(t) &= U_x \varphi_1(t) + U_y \varphi_2(t); \\ L(t) &= L_x \varphi_1(t) + L_y \varphi_2(t);\end{aligned}\quad (19)$$

[0395] 여기서  $\varphi_1(t)$  과  $\varphi_2(t)$  는 적당히 선택된 직교 기본 함수를 나타낸다.

[0396] 수학식 (18)과 (19)로부터, 시변 포락선 신호  $r(t)$ 의 2개의 일정 포락선 성분을 결정하기 위하여  $a$ ,  $\beta$ ,  $C$ ,  $\sin(\theta)$  및  $\cos(\theta)$ 의 값을 산출하기에 충분하다는 것에 유의한다. 더욱이  $a$ ,  $\beta$  및  $C$ 는 신호  $r(t)$ 의 크기 및 위상 정보, 등가적으로는  $I$  및  $Q$  성분으로부터 전적으로 결정될 수 있다.

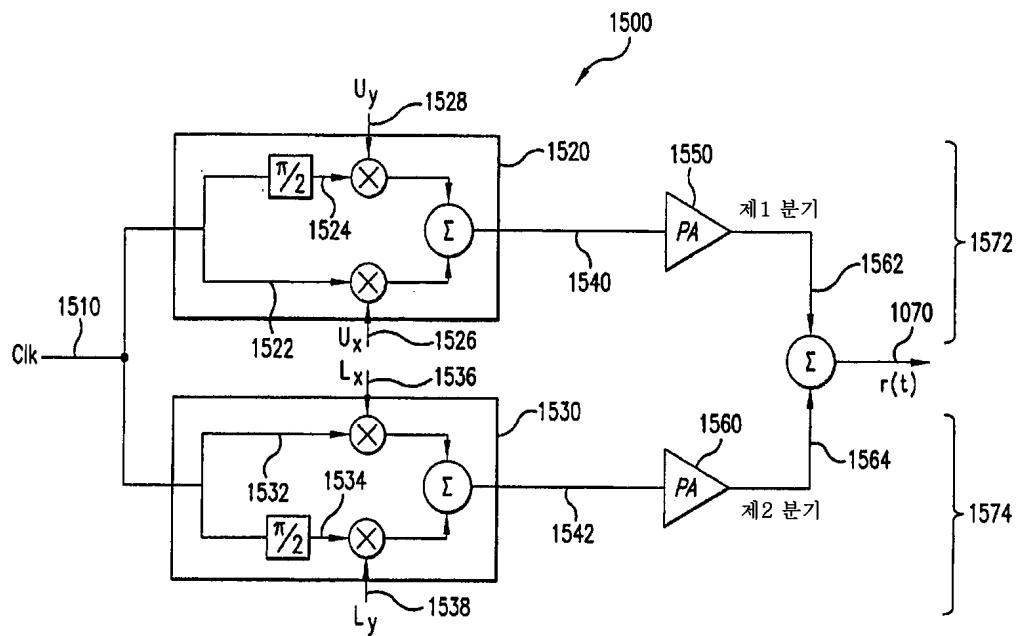

[0397] 도 15는 직접 직교 2-분기 VPA 실시예의 예시적인 실시예(1500)를 나타낸 블록도이다. 원하는 전력 레벨과 주파수 특성을 갖는 출력 신호  $r(t)$ 는 직접 직교 2-분기 VPA 실시예에 따라 동위상 및 직각위상 성분으로부터 생성된다.

[0398] 도 15의 예에서 클록 신호(1510)는 출력 신호  $r(t)$ 를 생성하기 위한 기준 신호를 나타낸다. 클록 신호(1510)는 원하는 출력 신호  $r(t)$ 와 주파수가 동일하다.

[0399] 도 15를 참조로 설명하면, 예시적인 실시예(1500)는 제1 분기(1572)와 제2 분기(1574)를 포함한다. 제1 분기(1572)는 벡터 변조기(1520)와 전력 증폭기(PA)(1550)를 포함한다. 마찬가지로 제2 분기(1574)는 벡터 변조기(1530)와 전력 증폭기(PA)(1560)를 포함한다.

[0400] 계속해서 도 15를 참조로 설명하면, 클록 신호(1510)는 벡터 변조기(1520, 1530)에 동시에 입력된다. 벡터 변조기(1520)에서는  $U_x$  신호(1526)가 곱해진 클록 신호(1510)의 동위상 신호(1522)가,  $U_y$  신호(1528)가 곱해진 클록 신호(1510)의  $90^\circ$  천이된 버전(1524)과 합산된다. 이와 동시에, 벡터 변조기(1530)에서는  $L_x$  신호(1536)가 곱해진 클록 신호(1510)의 동위상 신호(1532)가,  $L_y$  신호(1538)가 곱해진 클록 신호(1510)의  $90^\circ$  천이된 버전(1534)과 합산된다.  $U_x$  신호(1526)와  $U_y$  신호(1528)는 각각 수학식 (19)에서의 신호  $r(t)$ 의  $U(t)$  일정 포락선 성분의 동위상 및 직각위상 진폭 성분에 해당한다. 마찬가지로  $L_x$  신호(1536)와  $L_y$  신호(1538)는 각각 수학식 (19)에서의 신호  $r(t)$ 의  $L(t)$  일정 포락선 성분의 동위상 및 직각위상 진폭 성분에 해당한다.

[0401] 따라서 벡터 변조기(1520, 1530)의 각자의 출력 신호(1540, 1542)는 각각 수학식 (19)에서 전술한 신호  $r(t)$ 의  $U(t)$  및  $L(t)$  일정 포락선 성분에 해당한다. 전술한 바와 같이 신호(1540, 1542)는 동일하고 일정한 또는 실질적으로 동일하고 일정한 크기 포락선을 갖는 것으로 특징지워진다.

[0402] 도 15를 참조로 설명하면, 출력 신호  $r(t)$ 의 원하는 전력 레벨을 발생하기 위하여 신호(1540, 1542)는 해당 전력 증폭기(1550, 1560)에 입력된다.

[0403] 일 실시예에서 전력 증폭기(1550, 1560)는 각각 동일 또는 실질적으로 동일한 전력 증폭을 신호(1540, 1542)에 적용한다. 일 실시예에서 PA(1550, 1560)의 전력 증폭 레벨은 출력 신호  $r(t)$ 의 원하는 전력 레벨에 따라 설정된다.

[0404] 증폭된 출력 신호(1562, 1564)는 실질적으로 일정한 포락선 신호이다. 따라서 도 15에 도시된 바와 같이 증폭 신호들이 합산되면, 그 합산 결과 신호(1570)는 원하는 출력 신호  $r(t)$ 에 해당한다.

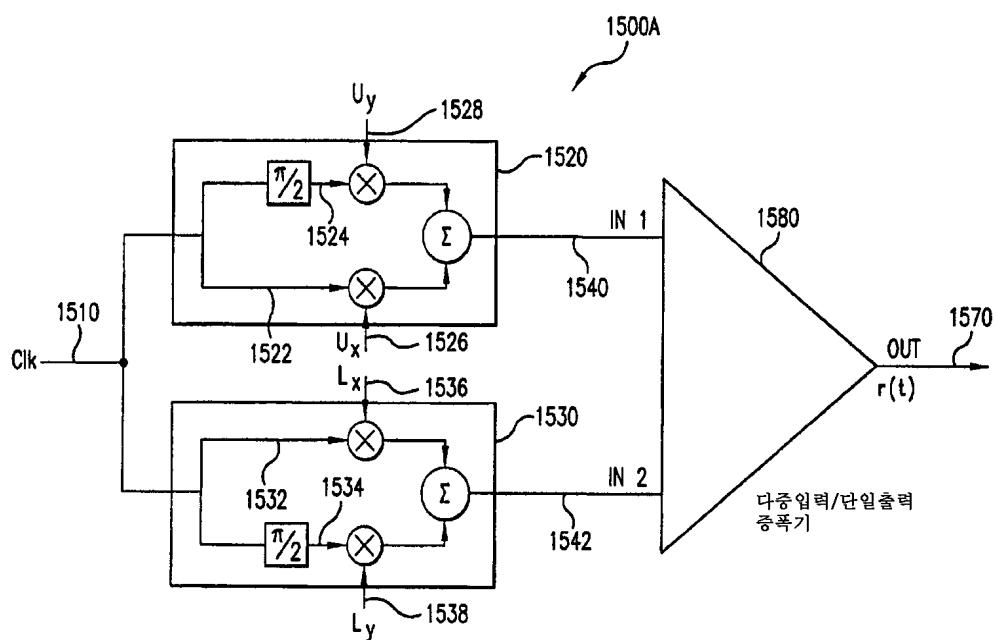

[0405] 도 15A는 직접 직교 2-분기 VPA 실시예의 다른 예시적인 실시예(1500A)를 나타낸 블록도이다. 실시예(1500A)는 도 15의 실시예(1500)의 다중입력 단일출력(MISO) 구현을 나타낸다.

[0406] 실시예(1500A)에서 벡터 변조기(1520, 1530)로부터 출력된 일정 포락선 신호(1540, 1542)는 MISO PA(1580)에

입력된다. MISO PA(1580)는 2-입력 단일출력 전력 증폭기이다. 일 실시예에서 MISO PA(1580)는 예컨대 전치 구동기, 구동기, 전력 증폭기 및 프로세스 검출기(도 15A에는 미도시)와 같은 여러 가지 요소를 포함할 수 있다. 더욱이 MISO PA(1580)는 도 15A에 도시된 2-입력 PA에 한정되지 않는다. 다른 실시예에서, 이후 도 51A 내지 51H를 참조로 자세히 설명되겠지만, PA(1580)는 임의 수의 입력을 가질 수 있다.

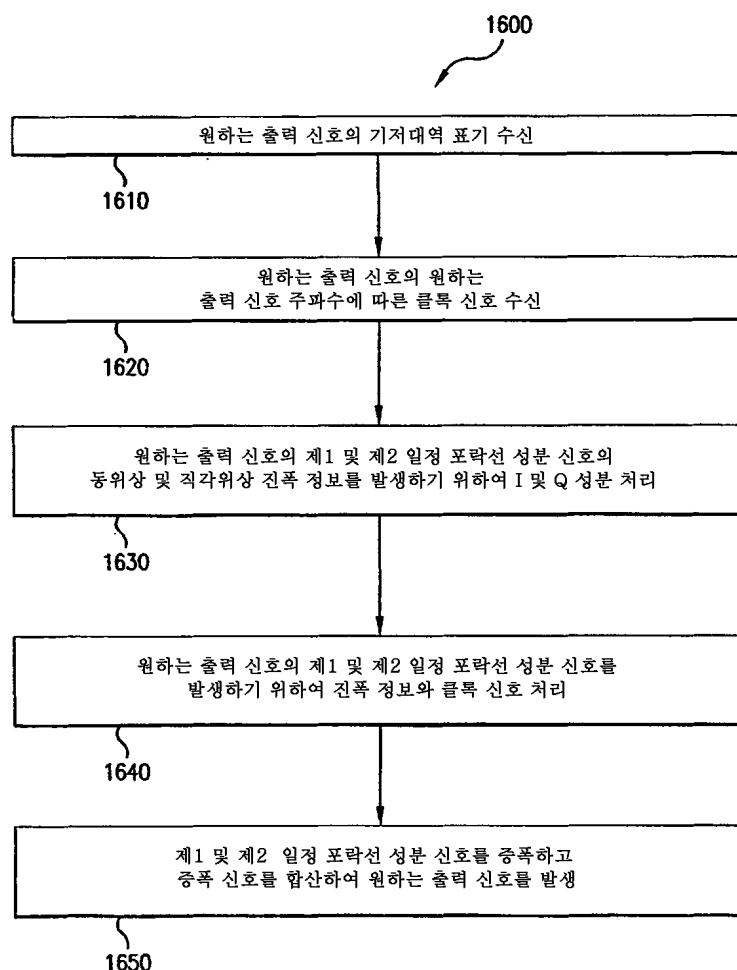

[0409] 직접 직교 2-분기 VPA 실시예의 동작은 도 16의 프로세스 플로우차트(1600)에 나타나 있다. 프로세스는 원하는 출력 신호의 기저대역 표기를 수신하는 것을 포함하는 단계(1610)에서 개시한다. 일 실시예에서 기저대역 표기는 I 및 Q 성분을 포함한다. 다른 실시예에서 I 및 Q 성분은 기저대역으로 하향 변환된 RF 성분이다.

[0410] 단계(1620)는 원하는 출력 신호의 원하는 출력 신호 주파수에 따라 설정된 클록 신호를 수신하는 것을 포함한다. 도 15의 예에서 단계(1620)는 클록 신호(1510)를 수신함에 의해 달성된다.

[0411] 단계(1630)는 원하는 출력 신호의 제1 및 제2 일정 포락선 성분 신호의 동위상 및 직각위상 진폭 정보를 생성하기 위하여 I 및 Q 성분을 처리하는 것을 포함한다. 도 15의 예에서 동위상 및 직각위상 진폭 정보는  $U_x$ ,  $U_y$ ,  $L_x$  및  $L_y$ 로 나타낸다.

[0412] 단계(1640)는 원하는 출력 신호의 제1 및 제2 일정 포락선 성분 신호를 생성하기 위하여 진폭 정보와 클록 신호를 처리하는 것을 포함한다. 일 실시예에서 제1 및 제2 일정 포락선 성분 신호는 원하는 출력 신호 주파수에 따라서 변조된다. 도 15의 예에서 단계(1640)은 신호(1540, 1542)를 생성하기 위하여 벡터 변조기(1520, 1530), 클록 신호(1510) 및 진폭 정보 신호(1526, 1528, 1536, 1538)에 의해 달성된다.

[0413] 단계(1650)는 제1 및 제2 일정 포락선 성분을 증폭하고, 원하는 출력 신호를 생성하기 위하여 이 증폭된 신호를 합산하는 것을 포함한다. 일 실시예에서 제1 및 제2 일정 포락선 성분의 증폭은 원하는 출력 신호의 원하는 전력 레벨에 따른다. 도 15의 예에서 단계(1650)는 각자의 신호(1540, 542)를 증폭하는 PA(1550, 1560)에 의해, 그리고 이어서 출력 신호(1574)를 생성하기 위하여 증폭 신호(1562, 1564)를 합산함으로써 달성된다.

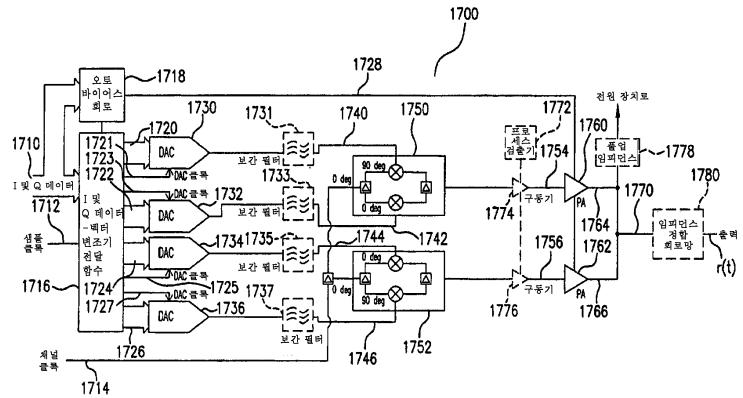

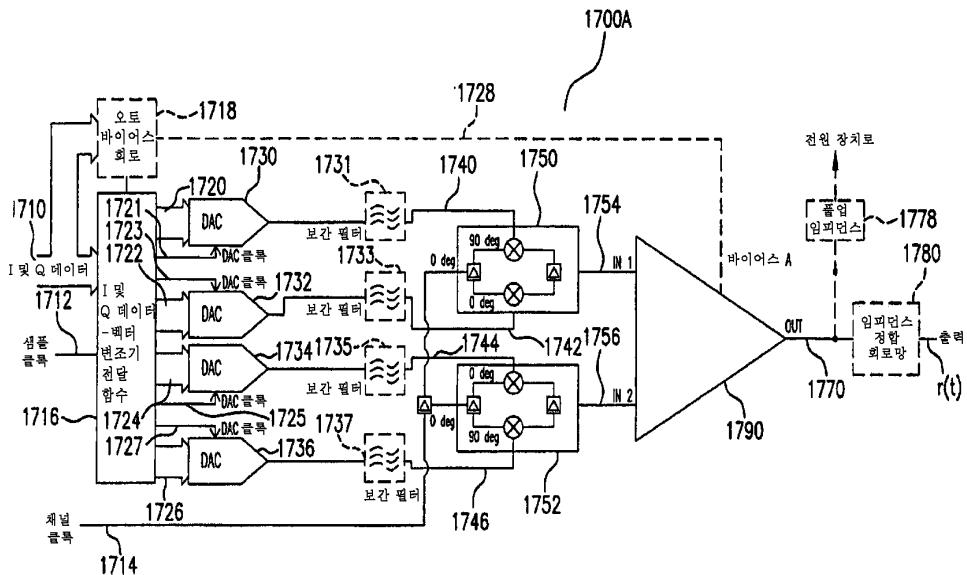

[0414] 도 17은 프로세스 플로우차트(1600)를 구현하는 벡터 전력 증폭기(1700)의 예시적인 실시예를 나타낸 블록도이다. 선택적 성분은 파선으로 나타내며, 다른 실시예에서는 이러한 선택적 성분은 가감될 수 있다.

[0415] 도 17을 참조로 설명하면, 동위상(I) 및 직각위상(Q) 정보 신호(1710)는 I 및 Q 데이터 전달 함수 모듈(1716)에 의해 수신된다. 일 실시예에서 I 및 Q 데이터 전달 함수 모듈(1716)은 샘플 클록(1212)에 따라 신호(1710)를 샘플링한다. I 및 Q 정보 신호(1710)는 기저대역 I 및 Q 정보를 포함한다.

[0416] 일 실시예에서 I 및 Q 데이터 전달 함수 모듈(1716)은 정보 신호(1710)를 처리하여 정보 신호(1720, 1722, 1724, 1726)를 생성한다. I 및 Q 데이터 전달 함수 모듈(1716)의 동작에 대해서는 이후의 3.4 절에서 자세히 설명한다.

[0417] 도 17을 참조로 설명하면, 정보 신호(1720)는 신호(1740)를 생성하기 위하여 DAC(1730)를 통해 처리되는 벡터 변조기(1750) 직각위상 진폭 정보를 포함한다. 정보 신호(1722)는 신호(1742)를 생성하기 위하여 DAC(1732)를 통해 처리되는 벡터 변조기(1750) 동위상 진폭 정보를 포함한다. 신호(1740, 1742)는 실질적으로 일정한 포락선 신호(1754)를 생성하기 위하여 산출된다. 도 14를 참조하면, 예컨대 정보 신호(1720, 1722)는 각각 상위 직각위상 및 동위상 성분  $U_y$  및  $U_x$ 를 포함한다.

[0418] 계속해서 도 17을 참조로 설명하면, 정보 신호(1726)는 신호(1746)를 생성하기 위하여 DAC(1736)를 통해 처리되는 벡터 변조기(1752) 직각위상 진폭 정보를 포함한다. 정보 신호(1724)는 신호(1744)를 생성하기 위하여 DAC(1734)를 통해 처리되는 벡터 변조기(1752) 동위상 진폭 정보를 포함한다. 신호(1744, 1746)는 실질적으로 일정한 포락선 신호(1756)를 생성하기 위하여 산출된다. 도 14를 참조하면, 예컨대 정보 신호(1724, 1726)는 각각 하위 동위상 및 직각위상 성분  $L_x$  및  $L_y$ 를 포함한다.

[0419] 도 17의 예시적인 실시예에서 정보 신호(1720, 1722, 1724, 1726)는 디지털 신호이다. 따라서 각 신호(1720, 1722, 1724, 1726)는 해당 디지털-아날로그 변환기(DAC)(1730, 1732, 1734, 1736)에 공급된다. DAC(1730, 1732, 1734, 1736)의 분해능과 샘플 레이트는 특정 원하는 시그널링 방식에 따라 선택된다. DAC(1730, 1732, 1734, 1736)는 각각 DAC 클록 신호(1721, 1723, 1725, 1727)에 의해 제어된다. DAC 클록 신호(1721, 1723, 1725, 1727)는 동일한 클록으로부터 도출되거나 서로 독립적일 수 있다.

[0420] 다른 실시예에서 정보 신호(1720, 1722, 1724, 1726)는 아날로그 형식으로 생성되며, DAC는 필요치 않다.

- [0421] 도 17을 참조로 설명하면, DAC(1730, 1732, 1734, 1736)는 디지털 정보 신호(1720, 1722, 1724, 1726)를 대응하는 아날로그 신호로 변환하고, 이들 아날로그 신호를 각각 선택적인 보간 필터(1731, 1733, 1735, 1737)에 입력한다. 안티엘리어싱 필터로도 기능하는 보간 필터(1731, 1733, 1735, 1737)는 DAC 출력 신호를 정형하여 원하는 출력 과정을 생성한다. 보간 필터(1731, 1733, 1735, 1737)는 각각 신호(1740, 1742, 1744, 1746)를 생성한다.

- [0422] 계속해서 도 17을 참조로 설명하면, 신호(1740, 1742, 1744, 1746)는 벡터 변조기(1750, 1752)에 입력된다. 벡터 변조기(1750, 1752)는 제1 및 제2 일정 포락선 성분을 생성한다. 도 17의 실시예에서 채널 클록(1714)은 원하는 출력 신호 주파수에 따라 설정되어 그에 따라 출력 신호(1770)의 주파수를 설정한다.

- [0423] 도 17을 참조로 설명하면, 벡터 변조기(1750)는 채널 클록 신호(1714)의  $90^\circ$  천이된 버전이 곱해진 신호(1740)와, 채널 클록 신호(1714)의  $0^\circ$  천이된 버전이 곱해진 신호(1742)를 결합하여 출력 신호(1754)를 생성한다. 그 와 동시에, 벡터 변조기(1752)는 채널 클록 신호(1714)의  $90^\circ$  천이된 버전이 곱해진 신호(1746)와, 채널 클록 신호(1714)의  $0^\circ$  천이된 버전이 곱해진 신호(1744)를 결합하여 출력 신호(1756)를 생성한다.

- [0424] 출력 신호(1754, 1756)는 일정 포락선 신호를 나타낸다. 출력 신호(1754, 1756)를 합산하면 원래 기저대역 신호의 I 및 Q 특성을 가진 반송파 신호가 된다. 실시예에서 벡터 전력 증폭기(1700)의 출력에서 원하는 전력 레벨을 발생하기 위하여 신호(1754, 1756)는 증폭된 다음에 합산된다. 도 17의 실시예에서, 예컨대 신호(1754, 1756)는 각각 해당 전력 증폭기(PA)(1760, 1762)에 입력된다. 일 실시예에서 PA(1760, 1762)는 스위칭 전력 증폭기를 포함한다. 오토바이어스 회로(1718)는 PA(1760, 1762)의 바이어스를 제어한다. 도 17의 실시예에서, 예컨대 오토바이어스 회로(1718)는 바이어스 전압(1728)을 PA(1760, 1762)에 공급한다.

- [0425] 일 실시예에서 PA(1760, 1762)는 동일한 또는 실질적으로 동일한 전력 증폭을 각자의 일정 포락선 신호(1754, 1756)에 적용한다. 일 실시예에서 전력 증폭은 원하는 출력 전력 레벨에 따라 설정된다. 벡터 전력 증폭기(1700)의 다른 실시예에서 PA 구동기를 추가적으로 채용하여 증폭기에 추가적인 전력 증폭 능력을 제공한다. 도 17의 실시예에서, 예컨대 PA 구동기(1774, 1776)는 각각 벡터 변조기(1750, 1752)과 그 다음의 PA(1760, 1762) 사이에 선택적으로 추가된다.

- [0426] PA(1760, 1762)의 각자의 출력 신호(1764, 1766)는 실질적으로 일정한 포락선 신호이다. 도 17의 실시예에서 출력 신호(1764, 1766)는 함께 결합되어 벡터 전력 증폭기(1700)의 출력 신호(1770)를 생성한다. 실시예에서 PA(1760, 1762)의 출력은 직접 결합됨에 유의한다. 여러 식의 직접 결합은 PA(1760, 1762)의 출력들 간에 저항성, 유효성 또는 용량성 절연이 최소이거나 없다는 것을 의미한다. 즉 PA(1760, 1762)의 출력은 중간에 개입하는 성분없이 함께 결합된다. 대안으로서 일 실시예에서 PA(1760, 1762)의 출력은 임피던스 연결을 작게하거나 최소화하는 인더티너 및/또는 커패시티너를 통해, 그리고/또는 절연과 전력 손실을 최소화하는 소정 연결부를 통해 간접적으로 함께 결합된다. 대안으로서, PA(1760, 1762)의 출력은 월킨슨, 하이브리드 결합기, 변압기 또는 공지의 능동 결합기와 같은 공지의 결합 기술을 이용하여 결합된다. 일 실시예에서 PA(1760, 1762)는 한 번의 동작으로 집적된 증폭과 전력 결합을 제공한다. 일 실시예에서 여기서 설명된 전력 증폭기 및/또는 구동기들 중 하나 또는 그 이상은 다중입력 단일출력(MISO) 전력 증폭 기술을 이용하여 구현되며, 그 예는 도 17A, 17B 및 도 51A 내지 51H에 나타나 있다.

- [0427] 출력 신호(1770)는 기저대역 신호의 원하는 I 및 Q 특성과 원하는 출력 전력 레벨 및 주파수를 가진 신호를 나타낸다. 벡터 전력 증폭기(1700)의 실시예에서 풀업 임피던스(1778)는 벡터 증폭기(1700)의 출력과 전원 장치 사이에 연결된다. 다른 실시예에서 임피던스 정합 회로망(1780)은 벡터 전력 증폭기(1700)의 출력에 연결된다. 본 발명의 전력 증폭 방법 및 시스템에 따른 출력단 실시예에 대해서는 이후의 3.5 절에서 자세히 설명한다.

- [0428] 벡터 전력 증폭기(1700)의 다른 실시예에서는 프로세스 검출기를 채용하여 증폭기의 회로에서의 임의의 프로세스 변동 및/또는 온도 변동을 보상한다. 도 17의 예시적인 실시예에서, 예컨대 프로세스 검출기(1772)는 선택적으로 추가되어 PA 구동기(1774, 1776)에서의 변동을 모니터한다.

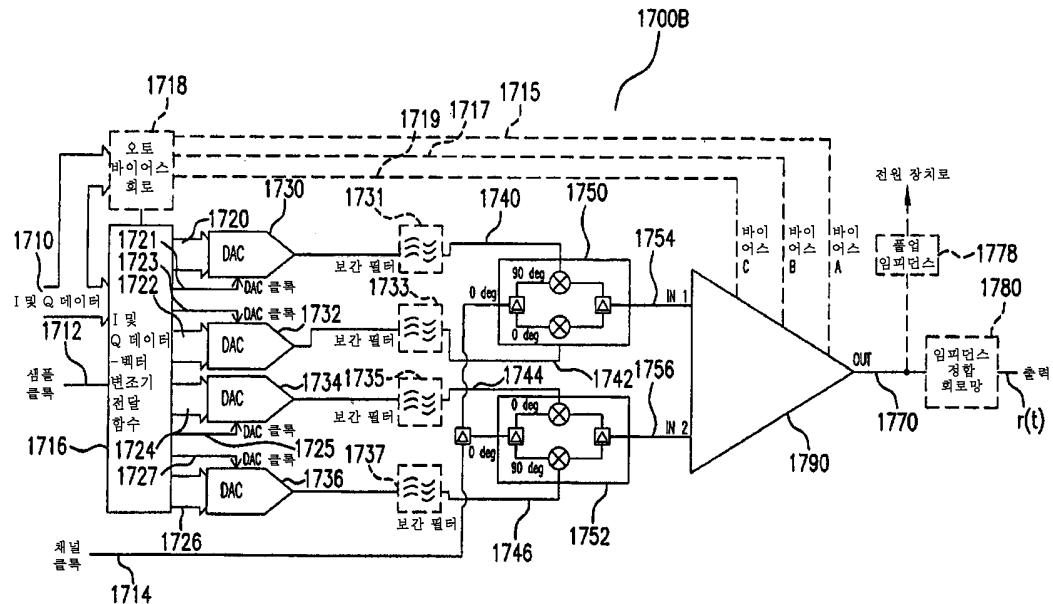

- [0429] 도 17A는 프로세스 플로우차트(1600)를 구현하는 벡터 전력 증폭기의 다른 예시적인 실시예(1700A)를 나타낸 블록도이다. 선택적 성분은 파선으로 나타내며, 다른 실시예에서는 이러한 선택적 성분은 가감될 수 있다. 실시예(1700A)는 도 17의 증폭기의 다중입력 단일출력(MISO) 구현을 나타낸다. 도 17A의 실시예에서 벡터 변조기(1750, 1760)로부터 출력된 일정 포락선 신호(1754, 1756)는 MISO PA(1790)에 입력된다. MISO PA(1790)는 2-입력 단일출력 전력 증폭기이다. 일 실시예에서 MISO PA(1790)는 도 17의 실시예에 나타낸 요소(1760, 1762, 1772, 1774, 1776) 또는 그 기능적 등가물을 포함한다. 다른 실시예에서 MISO PA(1790)는 도 17의 실시예에는

나타나 있지 않은 전치 구동기와 같은 다른 요소를 포함할 수 있다. 더욱이 MISO PA(1790)는 도 17A에 도시된 2-입력 PA에 한정되지 않는다. 다른 실시예에서, 이후 도 51A 내지 51H를 참조로 자세히 설명되겠지만, PA(1790)는 임의 수의 입력을 가질 수 있다.

[0430] 도 17B의 실시예(1700B)에 보여진 실시예(1700)의 다른 실시예에서 선택적인 오토바이어스 회로(1218)는 각각 바이어스 A, 바이어스 B 및 바이어스 C에 대응하는 독립적인 바이어스 제어 신호(1715, 1717, 1719)를 생성한다. 신호(1715, 1717, 1719)는 오토바이어스 회로(1718) 내에서 독립적으로 생성될 수도 되지 않을 수도 있으나, 도시된 바와 같이 독립적으로 출력된다. 더욱이 신호(1715, 1717, 1719)는 MISO PA(1790)의 여러 가지 단에 필요한 바이어싱에 의해 결정되는 것으로 관련될 수도 되지 않을 수도 있다.

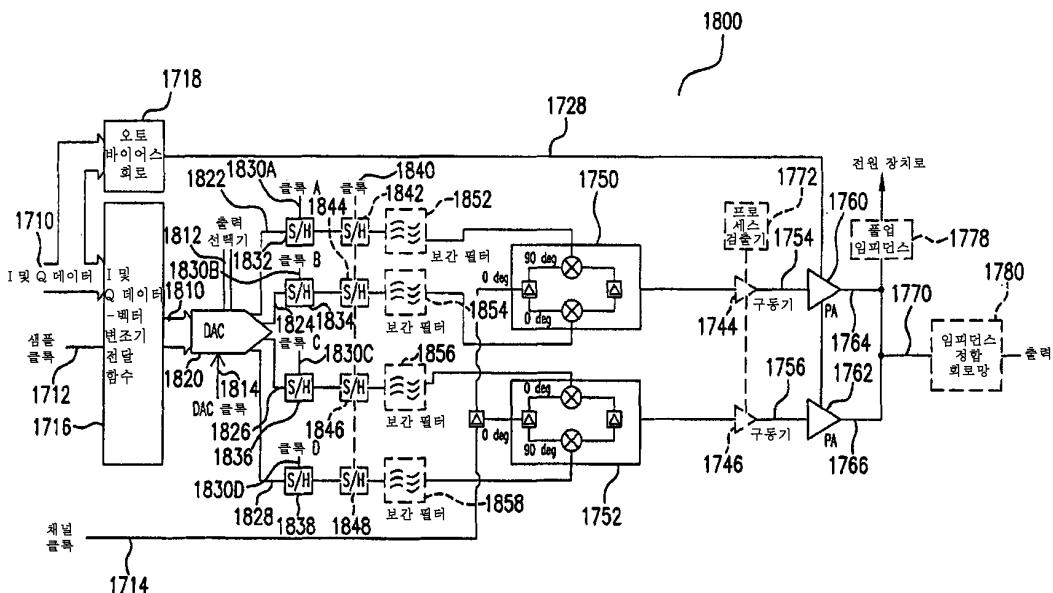

[0431] 도 18은 도 16의 직접 직교 2-분기 VPA 실시예에 따른 벡터 전력 증폭기의 다른 예시적인 실시예(1800)를 나타낸 블록도이다. 선택적 성분은 파선으로 나타내며, 다른 실시예에서는 이러한 선택적 성분은 가감될 수 있다.

[0432] 도 18의 예시적인 실시예에서는 충분한 분해능과 샘플 레이트를 가진 DAC(1820)가 도 17의 실시예의 DAC(1730, 1732, 1734, 1736)를 대체한다. DAC(1820)는 DAC 클록(1814)에 의해 제어된다.

[0433] DAC(1820)는 I 및 Q 데이터 전달 함수 모듈(1716)로부터 정보 신호(1810)를 수신한다. 정보 신호(1810)는 도 17의 실시예에서의 신호(1720, 1722, 1724, 1726)와 동일한 정보 내용을 포함한다.

[0434] DAC(1820)는 한 번에 하나의 아날로그 신호를 출력할 수 있다. 따라서 도 18에 도시된 바와 같이 샘플 홀드 구조가 이용될 수 있다.

[0435] 도 18의 실시예에서 DAC(1820)는 샘플 홀드 회로(1832, 1834, 1836, 1838)에 아날로그 신호(1822, 1824, 1826, 1828)를 각각 순차적으로 출력한다. 일 실시예에서 DAC(1820)는 도 17의 실시예의 DAC(1720, 1722, 1724, 1726)를 대체하기에 충분한 분해능과 샘플 레이트를 갖고 있다. 출력 선택기(1812)는 출력 신호(1822, 1824, 1826, 1828) 중 어느 것이 출력되도록 선택되어야 하는지를 판단한다.

[0436] DAC(1820)의 DAC 클록 신호(1814), 출력 선택기 신호(1812) 및 샘플 홀드 클록(1830A-D, 1840)은 독립적이거나 또는 전달 함수 모듈(1716)에 통합될 수 있는 제어 모듈에 의해 제어된다.

[0437] 일 실시예에서 샘플 홀드 회로(1832, 1834, 1836, 1838)는 각자의 값을 샘플링 및 홀드하고, 클록 신호(1830A-D)에 따라서 그 값을 제2 세트의 샘플 홀드 회로(1842, 1844, 1846, 1848)로 방출한다. 예컨대 S/H(1832)는 수신된 클록 신호(1830A)에 따라서 그 값을 S/H(1842)로 방출한다. 차례로 샘플 홀드 회로(1842, 1844, 1846, 1848)는 수신된 아날로그값을 홀드하고, 공통 클록 신호(1840)에 따라서 그 값을 보간 필터(1852, 1854, 1856, 1858)로 동시에 방출한다.

[0438] 다른 실시예에서는 S/H(1832, 1834, 1836, 1838)를 포함하는 단일 세트의 S/H 회로가 채용될 수 있다. 따라서 S/H 회로(1832, 1834, 1836, 1838)는 DAC(1820)로부터 아날로그값을 수신하며, 각 회로는 그 수신된 값을 독립적인 클록들(1830A-D)에 따라서 샘플링 및 홀드한다. 예컨대 S/H(1832)는 S/H(1834)를 제어하는 클록(1830B)과 동기화되지 않을 수 있는 클록(1830A)에 의해 제어된다. 예컨대 DAC(1820)는 클록들(1830A-D) 간의 시간차를 보상하기 위하여 전달 함수 모듈(1716)에 의해 산출된 적당히 선택된 아날로그값을 가진 신호(1822, 1824, 1826, 1828)를 S/H 회로(1832, 1834, 1836, 1838)에 출력한다.

[0439] 벡터 전력 증폭기(1800)의 다른 양상은 벡터 전력 증폭기(1700)에 대해 전술한 것과 거의 같다.

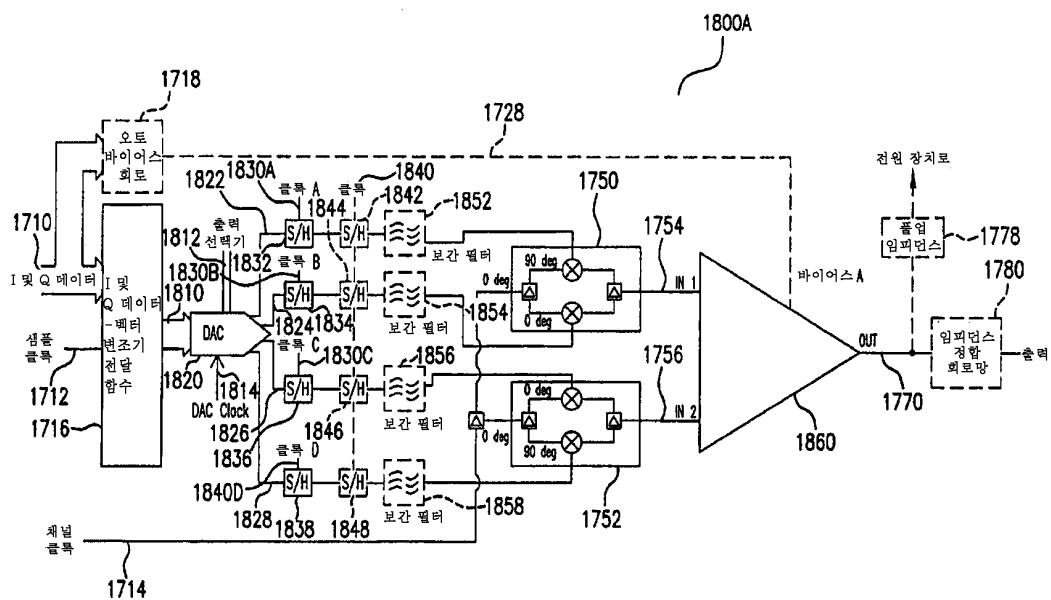

[0440] 도 18A는 직접 직교 2-분기 VPA 실시예에 따른 벡터 전력 증폭기의 다른 예시적인 실시예(1800A)를 나타낸 블록도이다. 선택적 성분은 파선으로 나타내며, 다른 실시예에서는 이러한 선택적 성분은 가감될 수 있다. 실시예(1800A)는 도 18의 실시예(1800)의 다중입력 단일출력(MISO) 구현이다.

[0441] 도 18A의 실시예에서 벡터 변조기(1750, 1752)로부터 출력된 일정 포락선 신호(1754, 1756)는 MISO PA(1860)에 입력된다. MISO PA(1860)는 2-입력 단일출력 전력 증폭기이다. 일 실시예에서 MISO PA(1860)는 도 18의 실시예에 나타낸 요소(1744, 1746, 1760, 1762, 1772) 또는 그 기능적 등가물을 포함한다. 다른 실시예에서 MISO PA(1860)는 도 17의 실시예에는 나타나 있지 않은 전치 구동기와 같은 다른 요소를 포함할 수 있다. 더욱이 MISO PA(1860)는 도 18A에 도시된 2-입력 PA에 한정되지 않는다. 다른 실시예에서, 이후 도 51A 내지 51H를 참조로 자세히 설명되겠지만, PA(1860)는 임의 수의 입력을 가질 수 있다.

[0442] 도 18A의 실시예는 도시된 바와 같이 단일 또는 2 레벨의 S/H 회로를 가진 2개의 서로 다른 샘플 홀드 구조를 더 보여준다. 이 2개의 구현은 도 18을 참조로 전술하였다.

[0443] 벡터 전력 증폭기(1800A)의 다른 양상은 벡터 전력 증폭기(1700, 1800)에 대해 전술한 것과 같다.

[0444] 3.4) I 및 Q 데이터-벡터 변조기 전달 함수

[0445] 전술한 실시예들중 일부에서는 I 및 Q 데이터 전달 함수는 수신된 I 및 Q 데이터를 벡터 변조 및 증폭의 후속단에 대한 진폭 정보 입력으로 변환하기 위해 제공된다. 예컨대 도 17의 실시예에서 I 및 Q 데이터 전달 함수 모듈(1716)은 I 및 Q 정보 신호(1710)를 처리하여 신호  $r(t)$ 의 제1 및 제2 일정 포락선 성분(1754, 1756)의 동위상 및 직각위상 진폭 정보 신호(1720, 1722, 1724, 1726)를 생성한다. 이어서 벡터 변조기(1750, 1752)는 생성된 진폭 정보 신호(1720, 1722, 1724, 1726)를 이용하여 제1 및 제2 일정 포락선 성분 신호(1754, 1756)를 생성한다. 다른 예는 도 7, 8, 12 및 13의 모듈(710, 712, 1216)을 포함한다. 이들 모듈은 I 및/또는 Q 데이터를 벡터 변조 및 증폭의 후속단에 대한 진폭 정보 입력으로 변환하는 전달 함수를 구현한다.

[0446] 본 발명에 따라서 I 및 Q 데이터 전달 함수 모듈은 디지털 회로, 아날로그 회로, 소프트웨어, 펌웨어 또는 이들의 조합을 이용하여 구현될 수 있다.

[0447] 본 발명에 따른 전달 함수의 실제 구현에 영향을 주는 주는 요소는 몇 가지 있는데, 이들 요소는 실시예마다 다르다. 일 양상에서, 선택된 VPA 실시예는 전달 함수의 진폭 정보 출력과 그 관련 모듈을 제어한다. 예컨대 CPCP 2-분기 VPA 실시예(1200)의 I 및 Q 데이터 전달 함수 모듈(1216)은 직접 직교 2-분기 VPA 실시예(1700)의 I 및 Q 데이터 전달 함수 모듈(1716)과는 출력이 다름은 명백하다.

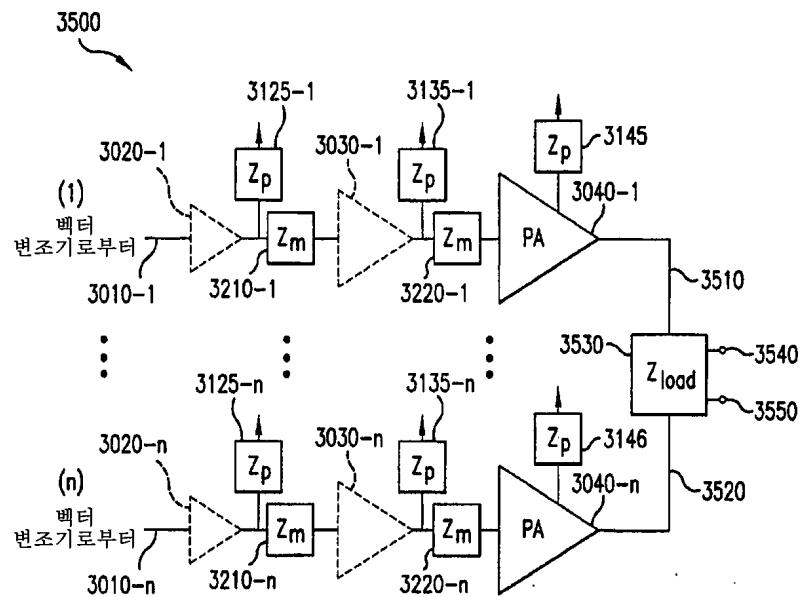

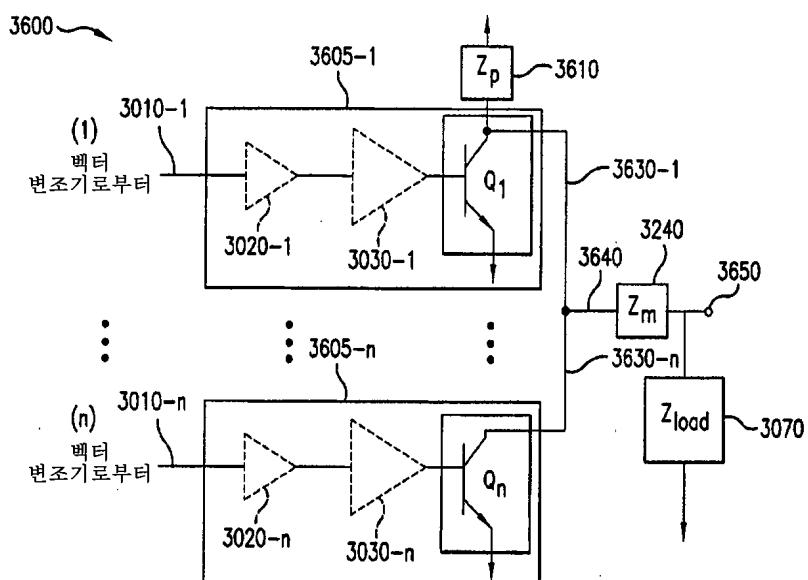

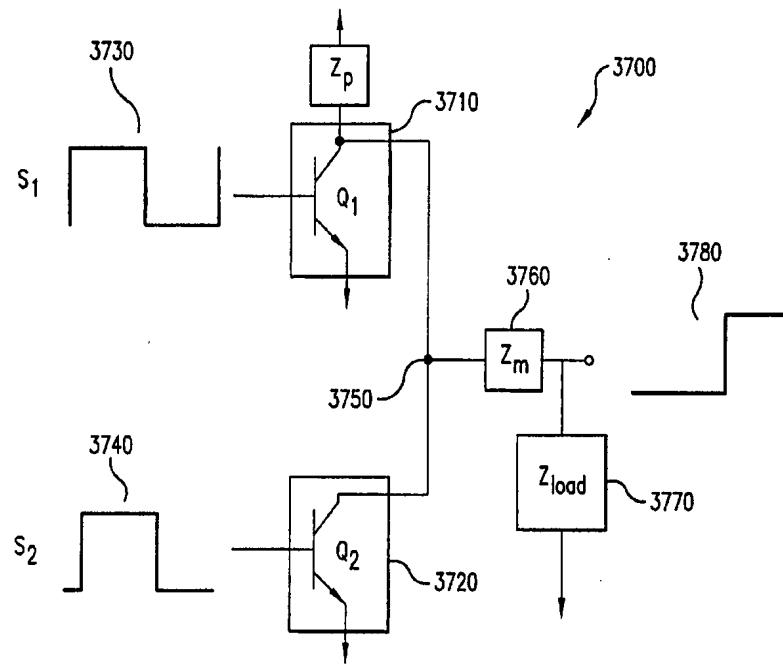

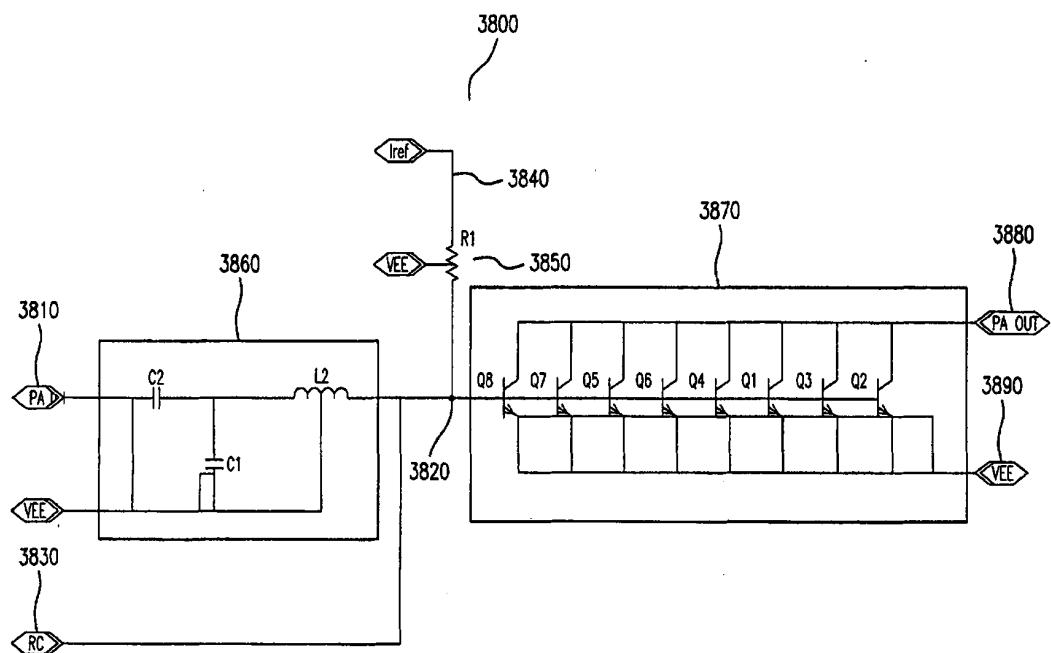

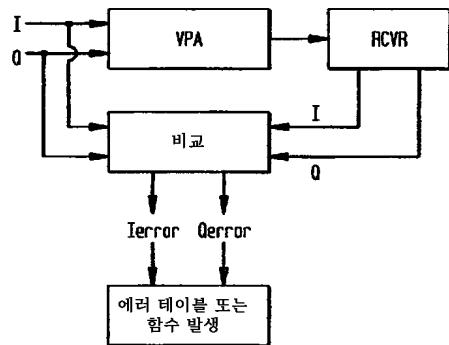

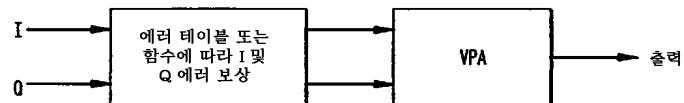

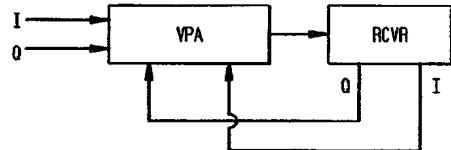

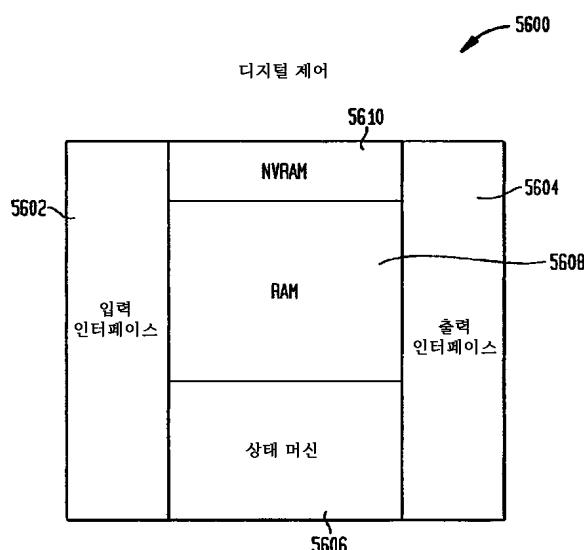

[0448] 다른 양상에서, 전달 함수의 복잡성은 VPA 구현이 지원하는데 필요한 원하는 변조 방식(들)에 따라 다르다. 예컨대 샘플 클록, DAC 샘플 레이트, 및 DAC 분해능은 원하는 출력 파형(들)을 구성하는 적당한 전달 함수에 따라 선택된다.