(12)发明专利

(10)授权公告号 CN 106340319 B

(45)授权公告日 2020.05.12

(21)申请号 201610108842.8

(51)Int.CI.

(22)申请日 2016.02.26

G11C 7/24(2006.01)

(65)同一申请的已公布的文献号

G11C 11/4078(2006.01)

申请公布号 CN 106340319 A

G11C 11/412(2006.01)

(43)申请公布日 2017.01.18

(56)对比文件

(30)优先权数据

CN 205692570 U, 2016.11.16,

1556621 2015.07.10 FR

EP 1873649 A1, 2008.01.02,

(73)专利权人 意法半导体(鲁塞)公司

CN 1825296 A, 2006.08.30,

地址 法国鲁塞

US 5787481 A, 1998.07.28,

(72)发明人 E·贝尔纳斯科尼 R·奥科诺尔

US 2012/0144277 A1, 2012.06.07,

(74)专利代理机构 北京市金杜律师事务所

审查员 白桦

11256

代理人 王茂华

权利要求书2页 说明书7页 附图4页

(54)发明名称

用于保护和验证地址数据的方法和电路

(57)摘要

提出用于保护和验证地址数据的方法和电路。本发明涉及一种用于保护存储器地址数据的电路，该电路被适配为：在输入数据总线(126)上接收要被写入存储器设备(104)的写入数据，并且在地址总线(122)上接收相应的写入地址；基于写入地址生成地址保护值；以及在输出数据总线(128)上生成修改的写入数据(WRITE DATA')，该修改的写入数据包括写入数据和地址保护值，其中，输出数据总线(128)的宽度大于输入数据总线的宽度。

1. 一种用于保护存储器地址数据的电路,所述电路被适配为:

在输入数据总线(126)上接收要被写入存储器设备(104)的写入数据,并且在地址总线(122)上接收对应的写入地址;

基于所述写入地址生成地址保护值;

在输出数据总线(128)上生成修改的写入数据(WRITE DATA'),所述修改的写入数据包括所述写入数据和所述地址保护值,其中,所述输出数据总线(128)的宽度大于所述输入数据总线的宽度;以及

基于所述写入地址来在输出地址总线(124)上生成到所述存储器设备的修改的写入地址(WRITE ADDR')。

2. 根据权利要求1所述的电路,其中,所述电路进一步被适配为基于所述写入数据来生成数据保护值,所述修改的写入数据进一步包括所述数据保护值。

3. 根据权利要求1所述的电路,进一步包括地址生成电路(404),所述地址生成电路(404)被适配为在所述输出地址总线(124)上生成到所述存储器设备的所述修改的写入地址(WRITE ADDR')。

4. 根据权利要求3所述的电路,其中,所述地址生成电路(404)被适配为通过将所述写入地址向左移位一个比特来生成所述修改的写入地址(WRITE ADDR')。

5. 根据权利要求1所述的电路,其中,所述写入数据的比特数目N小于输入数据总线(126)的宽度M,并且所述地址保护值是基于与所述地址总线的宽度内的N个比特的写入数据的位置相对应的子地址来生成的。

6. 根据权利要求1所述的电路,其中,所述输入数据总线(126)的宽度M等于所述写入数据的比特数目N的P倍,所述电路包括P个地址编码器,每一个地址编码器被适配为基于子地址中的对应子地址来生成所述地址保护值。

7. 根据权利要求1所述的电路,其中,保护数据生成电路(410)被适配为通过对所述写入地址进行编码以生成Y比特值来生成所述地址保护值,其中Y小于所述写入地址的比特数目。

8. 根据权利要求1所述的电路,进一步包括地址范围过滤电路(402),所述地址范围过滤电路(402)被适配为确定所述写入地址是否在要保护的地址范围内,其中仅当地址在所述要保护的地址范围内时,生成所述地址保护值。

9. 根据权利要求8所述的电路,进一步包括旁路路径,所述旁路路径用于如果所述写入地址没有在要保护的地址范围内,则将所述写入数据直接提供至所述写入数据输出总线(128),所述旁路路径包括桥电路(418),所述桥电路(418)被适配为将N个比特的写入数据转换成至少N+Y个比特的写入数据。

10. 一种用于验证存储器地址数据的电路,所述电路被适配为:

在地址总线(130)上接收读取地址;

基于所述读取地址来在输出地址总线(132)上生成到存储器设备(104)的修改的读取地址;

基于所述读取地址来生成参考地址保护值(REF ADDR PROT);

在读取数据输入总线(134)上接收来自所述存储器设备(104)的读取数据和从存储器设备读取的地址保护值;以及

通过将从所述存储器设备读取的所述地址保护值与所述参考地址保护值作比较来验证所述存储器地址数据。

11. 根据权利要求10所述的电路,其中,所述读取数据的比特数目N小于所述读取数据输入总线(134)的读取数据部分的宽度M,并且基于与所述读取数据输入总线(134)的所述读取数据部分的宽度内的N个比特的读取数据的位置相对应的子地址来生成所述参考地址保护值。

12. 根据权利要求11所述的电路,其中,所述读取数据输入总线(134)的所述读取数据部分的宽度M等于所述读取数据的比特数目N的P倍,所述电路包括P个地址编码器,每一个地址编码器被适配为基于子地址的相应一个来生成所述地址保护值。

13. 一种地址保护/验证电路(112),包括根据权利要求1所述的电路(112)和根据权利要求10所述的电路。

14. 一种保护存储器地址数据的方法,包括:

在输入数据总线(126)上接收要被写入至存储器设备(104)的写入数据,并且在地址总线(122)上接收对应的写入地址;

基于所述写入地址生成地址保护值;

在输出数据总线(128)上生成修改的写入数据(WRITE DATA'),所述修改的写入数据包括所述写入数据和所述地址保护值,其中,所述输出数据总线(128)的宽度大于所述输入数据总线的宽度;以及

基于所述写入地址来在输出地址总线(124)上生成到所述存储器设备的修改的写入地址(WRITE ADDR')。

15. 一种验证存储器地址数据的方法,包括:

在地址总线(130)上接收读取地址;

基于所述读取地址来在输出地址总线(132)上生成到存储器设备(104)的修改的读取地址;

基于所述读取地址来生成参考地址保护值(REF ADDR PROT);

在读取数据输入总线(134)上接收来自所述存储器设备(104)的读取数据和从所述存储器设备读取的地址保护值;以及

通过将从所述存储器设备读取的所述地址保护值与所述参考地址保护值作比较来验证所述存储器地址数据。

## 用于保护和验证地址数据的方法和电路

[0001] 相关申请的交叉引用

[0002] 本申请要求2015年7月10日提交的法国专利申请号15/56621的优先权权益,其全部内容在法律可允许的最大程度上通过引用合并于此。

### 技术领域

[0003] 本公开涉及存储器接口的领域,并且具体地涉及提供用于保护和验证地址数据的方法和电路的存储器接口。

### 背景技术

[0004] 当对诸如DRAM(动态随机存取存储器)或SRAM(静态随机存取存储器)设备的任何存储器设备进行写入时,例如作为单个事件扰乱的结果,通过输入和/或输出线传递到存储器的信号可能被损坏。

[0005] 尽管存储器接口通常包括用于写入存储器和从存储器读取数据的保护和/或校正机制,但是还存在地址数据可能被破坏的问题。难以检测地址数据何时已经被损坏,因为这导致了数据被写入不正确的地址或从不正确的地址读取。存储在不正确的地址处的数据可能不被损坏,并且因此关于数据信号的保护机制将无法识别/纠正错误。

[0006] 对存储器的输入/输出线上的地址数据的损坏很可能相对罕见。然而,对于诸如汽车应用、航空和/或空间应用的特定应用,期望提供极为可靠的存储器设备,如人体安全可以取决于正确操作。

[0007] 因此,在本领域中需要用于保护和验证通过存储器的输入/输出线传送的地址数据的方法和设备。

### 发明内容

[0008] 本公开的实施例的目的在于至少部分地解决现有技术中的一个或多个需要。

[0009] 根据一个方面,提供了一种用于保护存储器地址数据的电路,该电路被适配为:在输入数据总线上接收要被写入存储器设备的写入数据,并且在地址总线上接收相应的写入地址;基于写入地址生成地址保护值;以及在输出数据总线上生成修改的写入数据,该修改的写入数据包括写入数据和地址保护值,其中,输出数据总线的宽度大于输入数据总线的宽度。

[0010] 根据一个实施例,电路进一步被适配为基于写入数据来生成的数据保护值,所修改的写入数据进一步包括数据保护值。

[0011] 根据一个实施例,该电路进一步包括地址生成电路,地址生成电路被适配为生成在对存储器设备的输出地址总线上的修改的写入地址。

[0012] 根据一个实施例,地址生成电路被适配为通过将写入地址向左移位一个比特来生成修改的写入地址。

[0013] 根据一个实施例,写入数据的比特数目N小于输入数据总线的宽度M,并且地址保

护值是基于与地址总线的宽度内的写入数据的N个比特的位置相对应的子地址来生成的。

[0014] 根据一个实施例,输入数据总线的宽度M等于写入数据的比特数目N的倍数P,电路包括P个地址编码器,每一个被适配为基于子地址中的相应一个来生成地址保护值。

[0015] 根据一个实施例,保护数据生成电路被适配为通过对写入地址进行编码以生成Y-比特值来生成地址保护值,其中Y小于写入地址的比特数目。

[0016] 根据一个实施例,该电路进一步包括地址范围过滤电路,地址范围过滤电路被适配为确定写入地址是否在要保护的地址范围内,其中仅当地址在要保护的地址范围内时,生成地址保护值。

[0017] 根据一个实施例,该电路进一步包括旁路路径,用于如果写入地址没有在要保护的地址范围内,则将写入数据直接提供至写入数据输出总线,旁路路径包括桥电路,被适配为将N个比特的写入数据转换成至少N+Y个比特的写入数据。

[0018] 根据另一方面,提供了一种用于验证存储器地址数据的电路,该电路被适配为:在地址总线上接收读取地址;基于所读取的地址来生成参考地址保护值;在读取数据输入总线上从存储器设备接收读取数据和从存储器设备读取的地址保护值;以及通过将从存储器设备读取的地址保护值与参考地址保护值作比较来验证存储器地址数据。

[0019] 根据一个实施例,读取数据的比特数目N小于读取数据输入总线的读取数据部分的宽度M,并且基于与读取数据输入总线的读取数据部分的宽度内的N个比特的读取数据的位置相对应的子地址来生成参考地址保护值。

[0020] 根据一个实施例,读取数据输入总线的读取数据部分的宽度M等于读取数据的比特数目N的倍数P,该电路包括P个地址编码器,每一个被适配为基于与子地址的对应的地址编码器来生成地址保护值。

[0021] 根据另一方面,提供了一种地址保护/验证电路,包括用于保护存储器地址数据的上述电路和用于验证存储器地址数据的上述电路。

[0022] 根据又一方面,提供了一种保护存储器地址数据的方法,包括:在输入数据总线上接收要被写入存储器设备的写入数据,并且在地址总线上接收相应的写入地址;基于写入地址生成地址保护值;以及在输出数据总线上生成修改的写入数据,该修改的写入数据包括写入数据和地址保护值,其中,输出数据总线的宽度大于输入数据总线的宽度。

[0023] 根据又一方面,提供了一种验证存储器地址数据的方法,包括:在地址总线上接收读取地址;基于所读取的地址来生成参考地址保护值;在读取数据输入总线上从存储器设备接收读取数据和从存储器设备读取的地址保护值;以及通过将从存储器设备读取的地址保护值与参考地址保护值作比较来验证存储器地址数据。

## 附图说明

[0024] 前述和其他的特征和优点将参考附图,从通过图示给出并且没有限制的以下实施例的具体描述变得显而易见,在附图中:

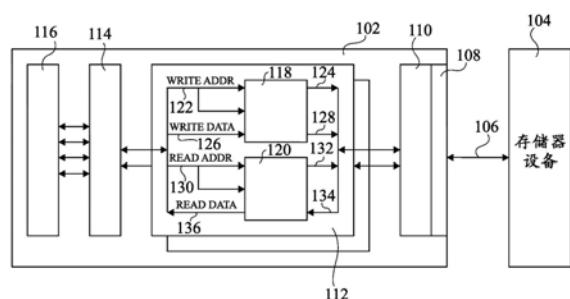

[0025] 图1示意性地图示了根据示例性实施例的与存储器设备通信的集成电路;

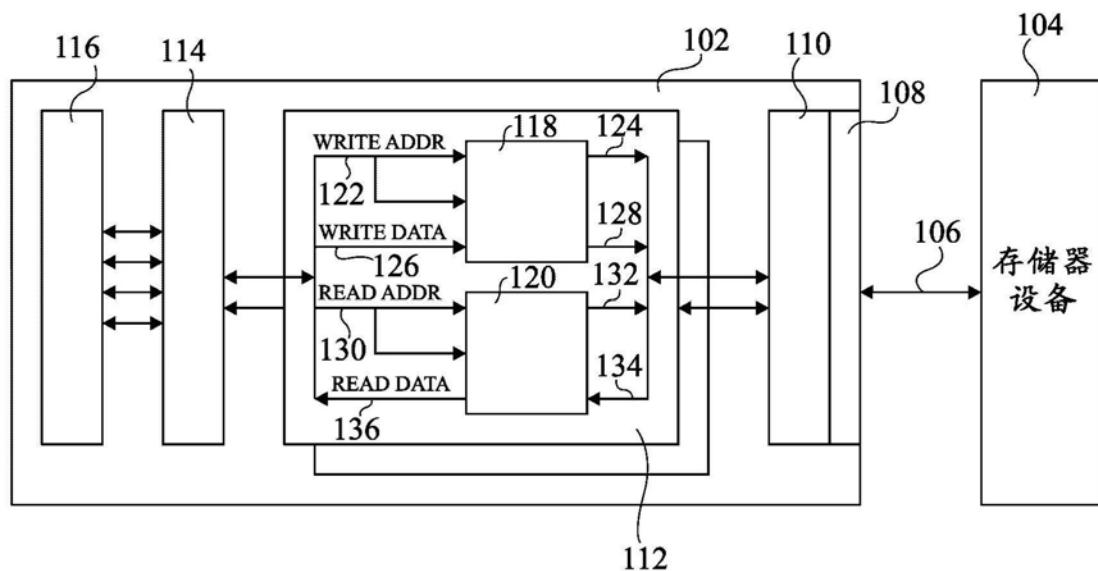

[0026] 图2表示根据示例性实施例的修改的写入数据;

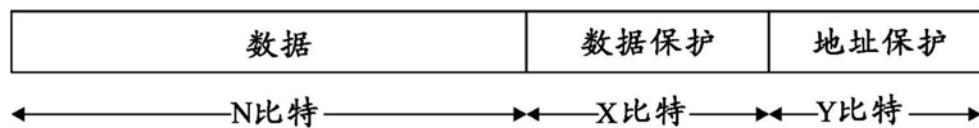

[0027] 图3是图示根据示例性实施例的保护地址数据的方法中的操作的流程图;

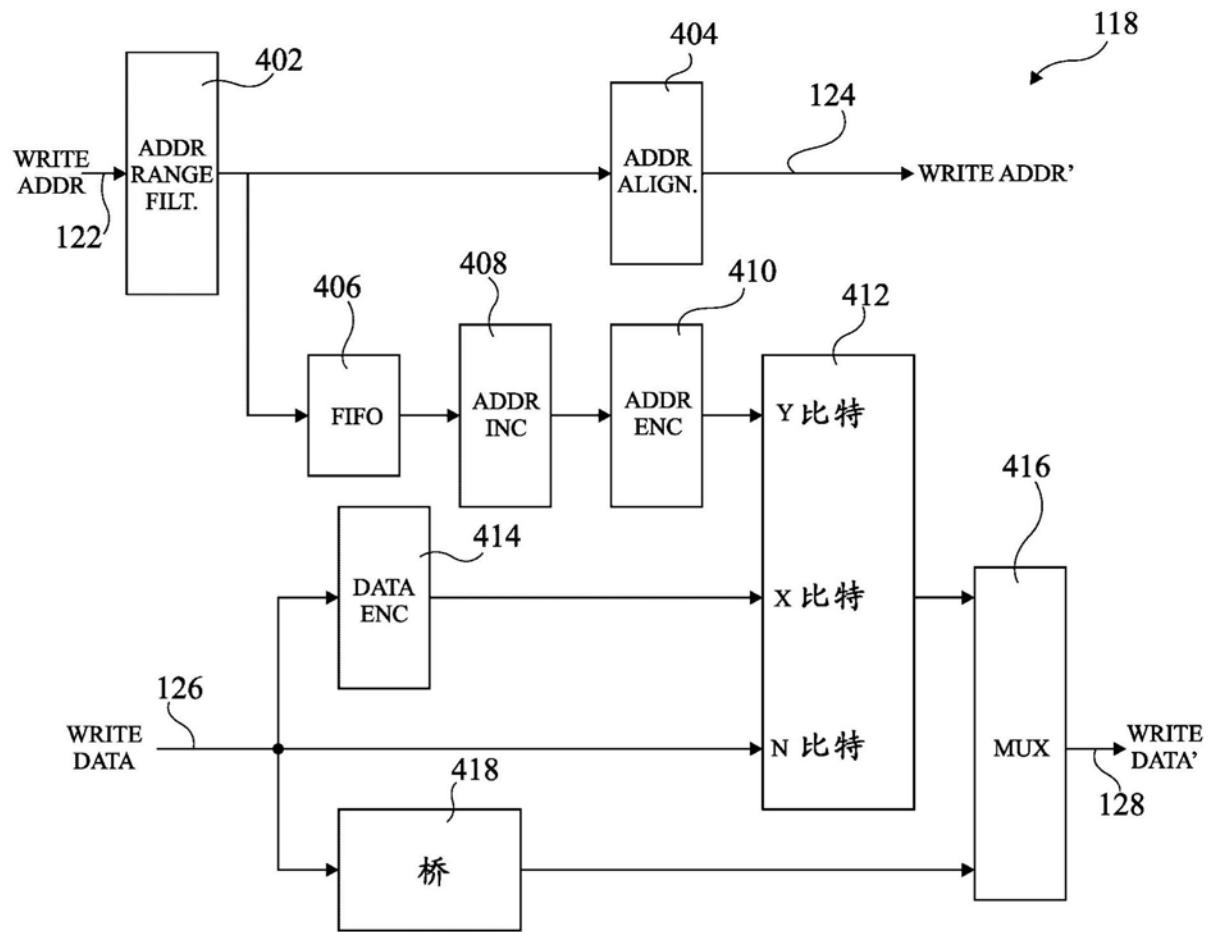

[0028] 图4示意性地更具体地图示了根据示例实施例的图1的写入地址保护电路;

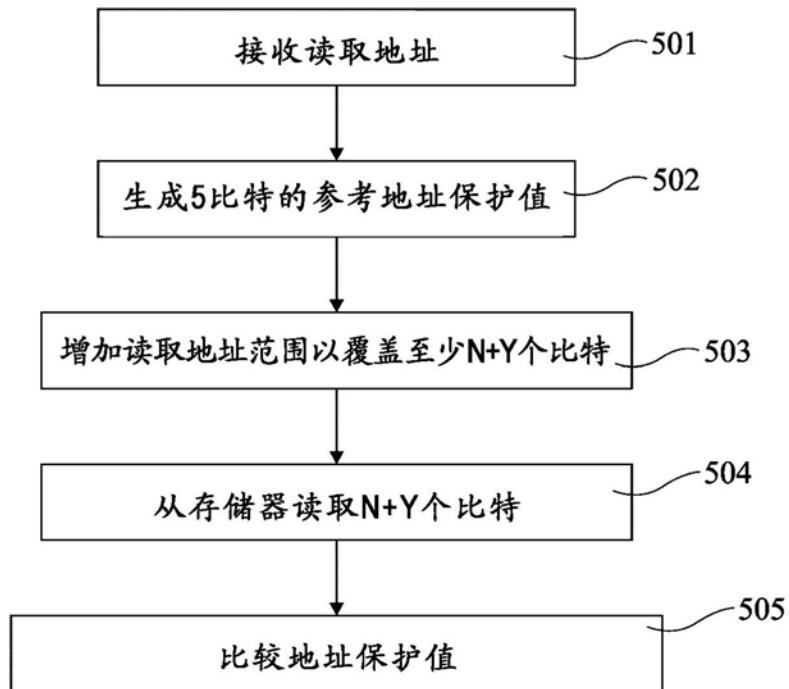

[0029] 图5是图示根据本公开的示例性实施例的在验证地址数据的方法中的操作的流程图;以及

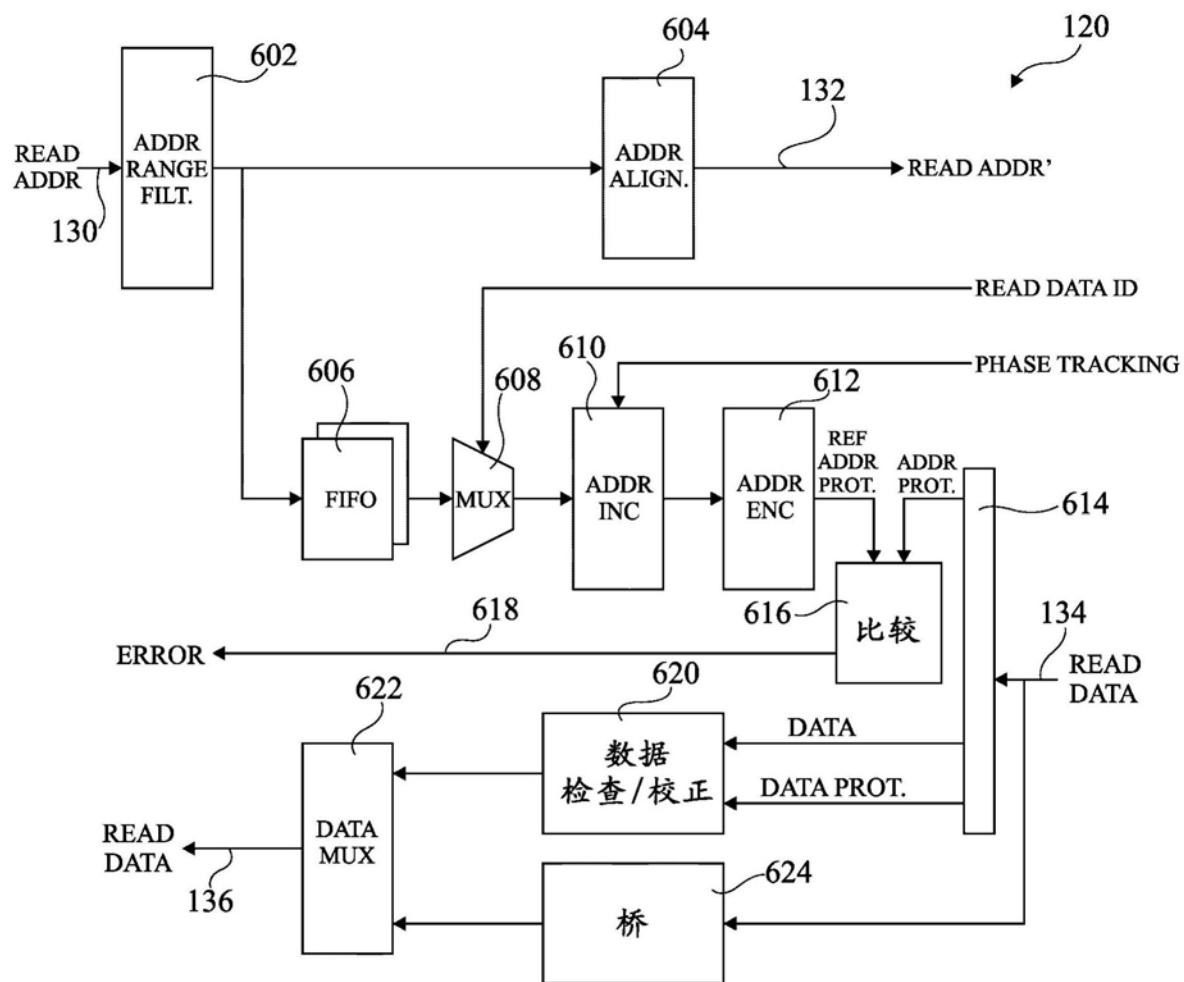

[0030] 图6示意性地更具体地图示了根据示例性实施例的图1的地址验证电路。

## 具体实施方式

[0031] 图1示意性地表示集成电路102和存储器设备104。存储器设备104是例如DRAM或SRAM设备、或其他类型的可寻址存储器设备。存储器设备104例如位于片外,这意味着在集成电路102和存储器设备104之间的输入/输出线路106具有导线和/或导电轨道的形式。在替代实施例中,存储器设备104可以集成在片上,作为集成电路102的一部分。

[0032] 集成电路102包括用于与存储器设备104对接的电路,并且例如包括耦合到输入/输出线路106的物理接口层108、耦合到物理接口层108的存储器控制器110、地址保护/验证电路112、SoC(片上系统)互连114和处理设备116。处理设备116例如是CPU(中央处理单元)、GPU(图形处理单元)、DMA(直接存储器存取)单元等。

[0033] 处理设备116例如经由SoC互连114并且经由地址保护/验证电路112被耦合到存储器控制器110。然而,在替代实施例中,地址保护/验证电路112可以被并入存储器控制器110中或处理设备116中,将电路112置于处理设备116和存储器控制器110之间的优点是,能够使用现有处理设备116和存储控制器110,并且电路112可以使得其对现有电路透明的方式被实现。

[0034] 例如,电路112包括地址保护电路118和地址验证电路120。

[0035] 地址保护电路118在输入总线122上接收写入地址(WRITE ADDR),写入地址例如在两个路径上被提供给地址保护电路。路径中的一个用于在输出总线124上生成要供应到存储器设备104的修改的地址。修改的地址例如具有增加的地址范围。另一路径例如用于基于写入地址来生成地址保护值。电路118还在输入总线126上接收写入数据(WRITE DATA),并且在输出总线128上提供要被写入存储器设备104中的修改的地址的数据,其包括写入数据和地址保护值。

[0036] 地址验证电路120在输入总线130上接收读取地址(READ ADDR),读取地址例如在两个路径上被提供给地址验证电路120。路径中的一个用于在输出总线124上生成要供应到存储器设备104的修改的地址。修改的地址例如具有增加的地址范围。另一路径例如用于基于读取地址来生成参考地址保护值。作为读取操作的结果,电路120在输入总线134从存储器设备104接收读取数据,其包括与数据同时写入的地址保护值。电路120例如将从存储器设备104读取的地址保护值与基于读取地址生成的参考地址保护值作比较。电路120在输出总线136上输出读取数据(READ DATA),但是该数据例如仅在地址保护值匹配参考地址保护值时被输出。作为替代,读取数据可以总是被输出,但是单独的错误信号(图1中未示出)可以在地址验证电路120的输出处被断言以指示地址数据被损坏。事实上,如果写入地址被损坏,并且数据被错误地写入到读取地址,或者如果读取地址被损坏,并且因此读取了不期望的地址,则从存储器设备读取的地址保护值将不匹配参考地址保护值。

[0037] 每个地址保护/验证电路112可以实现切片,使得数据总线的总宽度以N个比特的较小宽度被处理。例如,假设数据总线具有M比特的宽度,数据总线例如以N个比特的P个切片被处理,其中M=P×N。

[0038] 此外,如图1中表示的,在一些实施例中,可以存在并行操作的多个地址保护/验证电路112,每个电路112与存储器控制器110的单独端口相关联。

[0039] 图2表示设置在总线128上的要被写入存储器设备104的存储器地址的写入数据的内容的示例。相同的内容也将在读取操作期间被读取。

[0040] 如示,写入数据包括N个比特的系统数据(DATA),其对应于由处理设备116供应的要被写入存储器地址的数据。N例如是等于至少4的整数,并且例如是等于8或更大的2的幂。在一些实施例中,N等于图1的电路118的数据输入总线126的宽度M。然而,在替代实施例中,更精确的地址验证可以有利地通过使N小于总线宽度来实现。例如,在一些实施例中,总线126的宽度为64比特,并且N等于8。更一般地,N例如等于M/P,其中P等于2或更大的整数。

[0041] 写入数据例如还包括形成数据保护值(DATA PROTECTION)的X比特以及形成地址保护值(ADDRESS PROTECTION)的Y比特。数据保护值是可选的,因为在一些实施例中,不实现数据保护,或者这通过不同的电路来实现,诸如通过存储器控制器110来实现。

[0042] 在一些实施例中, $X+Y=N$ ,使得 $N+X+Y=2N$ ,其中X等于零或正整数,并且Y等于至少1。用于生成地址保护值的具体编码方案例如基于可用比特来选择。单个比特的地址保护值例如是简单的奇偶校验值。Y例如具有Q的上限,其中Q是对应于N比特数据的地址的比特数目。在这样的情况下,地址被简单地复制,而不通过编码减少比特数目。

[0043] 在一个实施例中,N等于8,X等于5,并且Y等于3。

[0044] 图3是示出根据示例性实施例的由电路118实现的保护地址数据的方法的操作的流程图。

[0045] 在操作301,电路118接收要写入存储器设备的N个比特的数据和相应的写入地址。

[0046] 在随后的操作302中,电路118基于该写入地址来生成Y个比特的地址保护值。在一些实施例中,生成写入地址的导数,并且基于该导数来生成地址保护值。例如,如果写入数据总线126具有M个比特,其中M等于P乘以N,则基于写入地址来生成P个子地址,并且针对子地址中的每一个生成不同的地址保护值。地址保护值是例如允许以至少特定水平的确定性来验证的地址数据的准确性的任何值。例如,地址保护值可以包括一个或多个奇偶校验值、诸如汉明码的纠错码、循环冗余校验码(CRC)或者甚至地址比特中的一些或全部的副本。

[0047] 在随后的操作303中,写入地址范围例如被增加以覆盖至少 $N+Y$ 个比特的数据块。实际上,在地址总线122上提供的地址例如基于系统数据的N比特的块。因此,该地址空间的大小例如通过电路118来增加,使得除了系统数据之外,可以存储地址保护值。例如,在数据总线的宽度加倍的情况下,并且假定地址的最小有效比特(1sb)对应于字节,加倍地址将产生覆盖两个字节而不是单个字节的地址。然而,在替代实施例中,这可能不修改地址,并且替代地使每个地址覆盖在数据总线上供应的每个字的宽度的两倍的字。

[0048] 在操作304中,N+Y个比特被写入存储器设备中的修改的写入地址。

[0049] 图4示意性地更具体地图示了根据示例性实施例的图1的写入地址保护电路118。

[0050] 输入地址总线(WRITE ADDR)122例如耦合到地址范围过滤器(ADDR RANGE FILT)402,其例如允许地址保护/验证被提供给仅存储器设备中的特定地址范围。例如,存储器装置可以被细分成要对其提供地址保护/验证的第一部分以及不对其提供地址保护/验证的另一部分。

[0051] 电路402的输出被耦合到地址对齐电路(ADDR ALIGN)404,其例如增加写入地址范

围,以允许地址保护值以及可选地数据保护值被插入。作为简单示例,存储器器件可以具有从0x00到0xFF的寻址范围(以十六进制表示),但是处理设备116可以仅看到总数的一半的可寻址范围,例如0x00至0x7F的范围。因此,这些地址中的每一个例如被翻译成存储器设备中的两个相邻的物理地址,在地址0x7F成为0xFE的情况下,地址0x01成为0x02,地址0x02成为0x04等等。这些翻译对应于每个地址的一个比特的简单向左移位。在输出地址总线124上提供修改的写入地址WRITE ADDR'。

[0052] 来自地址滤波器402的写入地址也例如被提供到先入先出(FIFO)缓冲器406,其例如存储一个或多个地址,并且在请求时将其提供给地址增量器(ADDR INC)408,其例如用于基于写入地址来生成在写入操作期间要存取的地址。地址增量器408例如被适配为使地址增加与写入数据总线122的宽度相对应的宽度。例如,如果写入数据总线122是8字节的宽度,并且地址的最小有效比特指定一个字节,则在写入数据的每个新的块在写入数据总线126上的情况下,地址增量器408例如被适配为使地址增加增量8。

[0053] 地址增量器408的输出被提供给地址编码器(ADDR ENC)410,其例如基于地址值来生成Y比特的地址保护值,并且将该Y比特的值提供给级联电路412。地址编码器410例如基于相应的N比特数据值的地址来生成地址保护值。在数据总线宽度M等于N的情况下,地址编码器410将简单地基于由地址增量器408提供的地址来生成地址保护值。然而,如果M等于PxN,其中P是2或更大的整数,则地址编码器例如生成P个不同的保护值,一个用于跨数据总线的宽度的N个比特的每个块。

[0054] 例如,在该数据总线宽度等于2N的情况下,地址编码器408例如基于由地址增量器408提供的地址来生成用于写入数据的第一N个比特的第一地址保护值,并且然后基于由地址增量器408递增了1所提供的地址来生成用于写入数据的第二N个比特的第二地址保护值。

[0055] 级联电路412还接收在输入写入数据总线126上提供的N个比特的系统数据。在图4的示例中,总线126还耦合到数据编码器电路414(DATA ENC),其例如对数据进行编码以生成X比特的数据保护值,还提供给级联电路412。

[0056] 电路412级联N、X和Y比特的值,以形成要写入存储器设备的写入数据。级联电路412的输出例如耦合到复用器416的输入,其在其输出处提供数据总线128上的写入数据(WRITE DATA')。复用器416的另一输入例如被耦合以从输入总线126接收写入数据,而不添加地址保护值或数据保护值。例如,经由桥电路(BRIDGE)418来提供写入数据,桥电路418通过两个存储器存取循环将在信号存储器存取循环上提供的N个比特的写入数据转换成2N个比特的写入数据。例如,在第一循环时,写入数据的N个比特由桥418存储,并且在随后的循环时,当已经接收到其他N个比特时,在总线128上输出2N个比特。例如,复用器416被适配为,如果写入操作考虑不具有添加的地址和数据保护的地址范围,则选择具有桥418的路径。

[0057] 在一些实施例中,地址保护/验证电路112实现切片,使得数据总线宽度的不同部分被并行处理。在这样的情况下,基于切片的数目来多次地例如实例化地址编码器410、连接电路412和数据编码器414中的每一个。每个切片的元素410、412、414例如处理N个比特的数据总线的相应块。地址编码器410的实例中的每一个例如对表示数据总线的宽度内的N个比特数据的位置的地址的相应固定偏移进行操作。此外,在一些实施例中,读取或写入存取

的粒度低于数据总线的宽度，并且例如对应于字节，而数据总线具有等于多个字节的宽度。因此，读取或写入操作可以跨数据总线的宽度指向特定开始字节。

[0058] 作为具体示例，在一个实施例中，M等于2N，并且N等于8。存在例如2个切片，这意味着地址编码器410、级联电路412和数据编码器414中的每一个被实例化两次。在这样的实施例中，下表提供了由地址增量器(ADDR INC)408提供并且由地址编码器中的第一个(ADDR ENC#1)410并且由地址编码器中的第二个(ADDR ENC#2)编码的连续地址的示例：

|        | ADDR INC 408<br>(输出) | ADDR ENC#1 410<br>(输入) | ADDR ENC#2 410<br>(输入) |

|--------|----------------------|------------------------|------------------------|

| [0059] | 0000 0110            | 0000 0110              | 0000 0111              |

|        | 0000 1000            | 0000 1000              | 0000 1001              |

| [0060] | 0000 1010            | 0000 1010              | 0000 1011              |

|        | 0000 1100            | 0000 1100              | 0000 1101              |

[0061] 图5是图示根据示例性实施例的验证地址的方法中的操作的流程图。

[0062] 在操作501中，接收读取地址。

[0063] 在随后的操作502中，处理读取地址以生成Y比特参考地址保护值。在操作502中应用与图3的操作302中应用的相同的编码算法。

[0064] 在随后的操作503中，读取存取的地址范围被增加以覆盖至少N+Y个比特的块。这涉及与关于图3的操作303描述的相同的修改，除了其被应用于读取地址，而不是写入地址。

[0065] 在随后的操作504中，执行存储器存取，并且从存储器设备读取N+Y个比特。

[0066] 在随后的操作505中，将从存储器设备读取的Y比特地址保护值与参考地址保护值作比较。如果存在匹配，则例如认为没有发生地址损坏。然而，如果存在不匹配，则例如生成警报，并且读取数据可以被丢弃。

[0067] 图6更具体地图示了根据示例性实施例的图1的地址验证电路120。

[0068] 如图所示，地址路径130的读取地址(READ ADDR)例如被提供给地址范围过滤器(ADDR RANGE FILT)602，其例如类似于图4的电路402。

[0069] 地址范围过滤器602的输出例如被提供给地址对齐电路(ADDR ALIGN)604，这也例如通过增加读取地址的地址范围以覆盖系统数据和相应的地址保护值二者，以与图4的电路404相同的方式进行操作。电路604在输出地址总线132上提供读取地址READ ADDR'。

[0070] 地址范围过滤器602的输出也例如被提供到FIFO 606，其经由复用器(MUX)608耦合到地址增量器(ADDR INC)610。地址增量器610的输出被耦合到地址编码器(ADDR ENC)612，其基于读取地址来生成参考地址保护值(REF ADDR PROT)。地址增量器610和地址编码器612例如以与地址增量器408和地址编码器410类似的方式进行操作。

[0071] 复用器608例如通过来自存储器设备104的信号READ DATA ID来控制，其例如指示在总线134上提供哪个读取数据，使得复用器608从FIFO 606中选择相应的读取地址。地址增量器610例如接收一个或多个相位跟踪信号(PAHSE TRACK)，并且用于确保由增量器610生成的地址对应于在总线134上出现的读取数据。在与存储器设备的对接是AXI连接的情况下

下,一个或多个相位跟踪信号例如包括信号RVALID、RREADY和RLAST,这些信号对本领域技术人员是已知的。

[0072] 电路120还包括分离器电路614,其在总线134上从存储器设备接收从地址READ ADDR'读取的数据,并且提取地址保护值。该地址保护值(ADDR PROT)被提供给比较器(COMPARE)616,其还从地址编码器612接收参考地址保护值。比较器616将地址保护值与参考地址保护值作比较,并且生成在比较器的输出线618上的错误信号(ERROR)。如果地址保护值匹配,则错误信号不被激活。然而,如果在值之间存在差异,则错误信号被激活。在一些实施例中,线路618被耦合到执行存储器存取的处理设备116,并且鉴于对地址信号的损坏,错误信号向处理设备116指示读取数据无法被依赖。

[0073] 在一些实施例中,数据检查/校正电路(DATA CHECKING/CORRECTING)620也被提供,其从分离器电路614接收由分离器614从读取数据中提取的系统数据(DATA)以及从由分离器614从读取数据中提取的X比特数据保护值(DATA PROT)。电路620的输出例如耦合到数据复用器(DATA MUX)622,其提供输出总线136上的读取数据。

[0074] 复用器622还经由桥电路(BRIDGE)624从输入总线134接收读取数据,其允许如果读取操作的地址不对应于受保护的地址范围,则绕过电路614、616和620。例如,桥电路624通过两个存储器存取周期将在单个存储器存取周期上提供的2N个比特的读取数据转换成N个比特的读取数据。例如,在第一周期上,来自总线134的2N比特的读取数据通过桥624来存储,并且通过两个周期在总线136上输出。复用器622例如被适配为,如果读取操作涉及没有添加地址和数据保护的地址范围,则选择具有桥624的路径。

[0075] 在一些实施例中,切片可以在地址验证电路120中以与以上关于图4描述的类似的方式被实现。在图6的实施例中,元素612、614、616和620例如被复制,使得这些元素的每次实例化处理相应的N比特块。

[0076] 本文描述的实施例的优点是,以相对简单的方式提供地址保护,同时保持与存储器设备的标准对接。事实上,例如,通过倍增其宽度,仅修改例如用于增加对存储器设备的数据总线的宽度。

[0077] 因此已经描述了至少一个说明性实施例,对本领域技术人员来说,各种替代、修改和改进将容易发生。

[0078] 具体地,尽管已经描述了数据保护值的X比特和地址保护值的Y比特的和等于系统数据的比特数目N的示例,但是很多其他格式是可能的。例如,能够使X+Y等于N/2或N/4。

图1

图2

图3

图4

图5

图6